CIS 720 Distributed Shared Memory Shared Memory Shared

CIS 720 Distributed Shared Memory

Shared Memory • Shared memory programs are easier to write • Multiprocessor systems • Message passing systems: - no physically shared memory - need to provide an abstraction of shared memory: Distributed Shared Memory

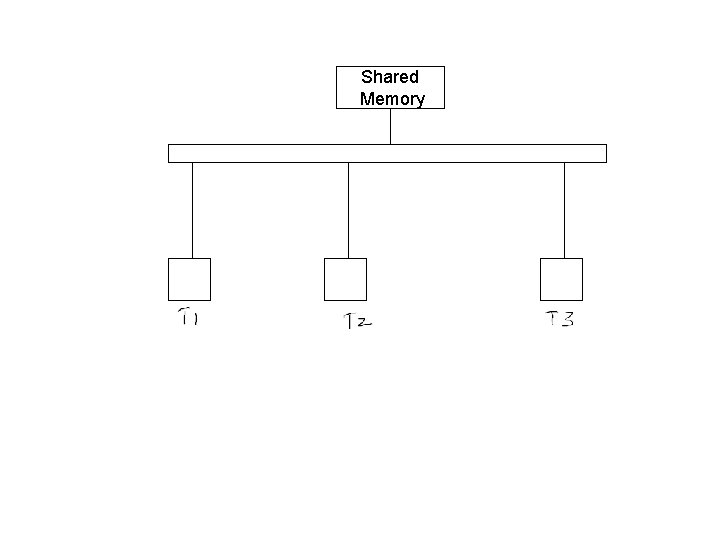

Shared Memory

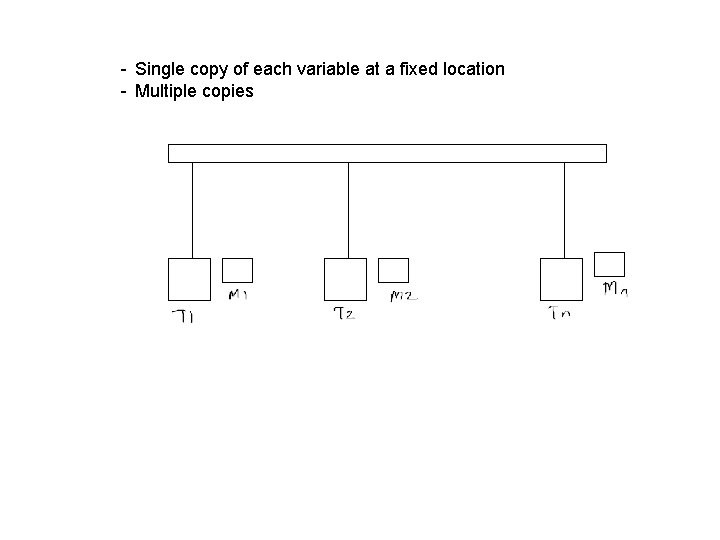

- Single copy of each variable at a fixed location - Multiple copies

Consistency Models • w(x)v: write value v into x • r(x)v: read of x return value v • Uniprocess programs: - all operations are totally ordered - read operations return the value written by the most recent write operation w(y)2 w(x)2 r(y)2 w(x)1 r(x)

Migratory protocol • Each page (variable) has a single copy • Initially, pages are distributed among the processes. • To read/write a variable: If page is locally available, perform the operation; Otherwise, DSM layer sends request for the page to be moved locally.

• Migratory protocol can suffer from trashing. • Solution: Maintain multiple copies

Consistency model • In the presence of multiple copies, we need to look at values written by other processes

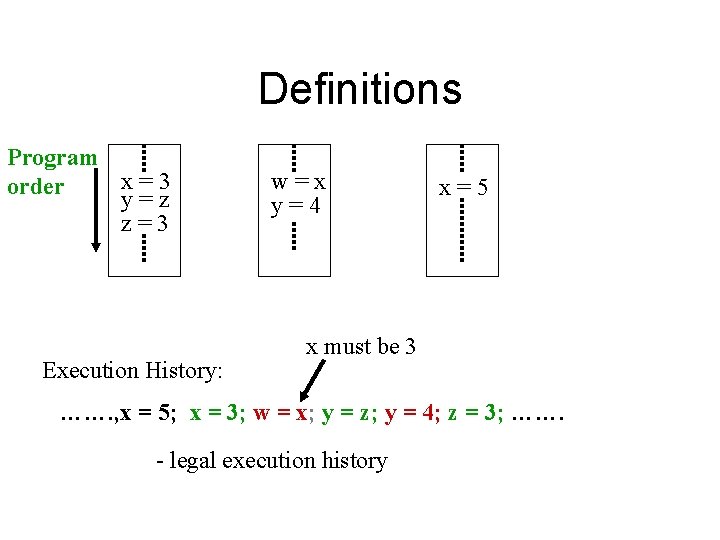

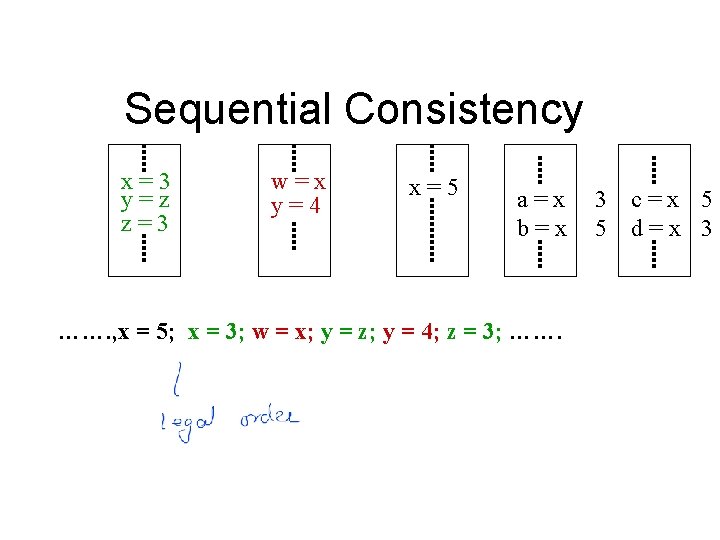

Definitions Program x=3 order y=z z=3 Execution History: w=x y=4 x=5 x must be 3 ……. , x = 5; x = 3; w = x; y = z; y = 4; z = 3; ……. - legal execution history

Atomic consistency • Any read to a memory location x must return the value stored by the most recent write on x that has been done. • The order of events must coincide with the real-time occurrence of non-overlapping events

Write-invalidate Protocol • Each page has an owner; • Protection modes: read, read_and_write, none • Read operation: if not locally available, then obtain a read-only copy. Set protection mode to read. • Write operation: Contact the current owner; get the page and its ownership; send invalidate messages to nodes that have copies; sets the protection to read_and_write;

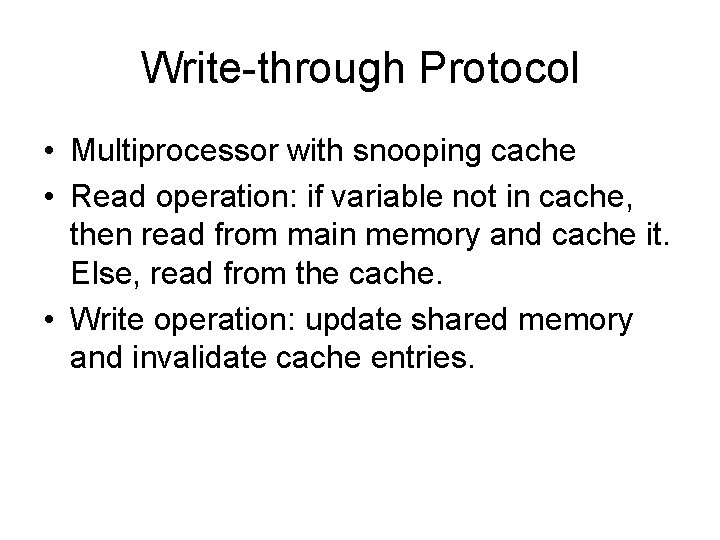

Write-through Protocol • Multiprocessor with snooping cache • Read operation: if variable not in cache, then read from main memory and cache it. Else, read from the cache. • Write operation: update shared memory and invalidate cache entries.

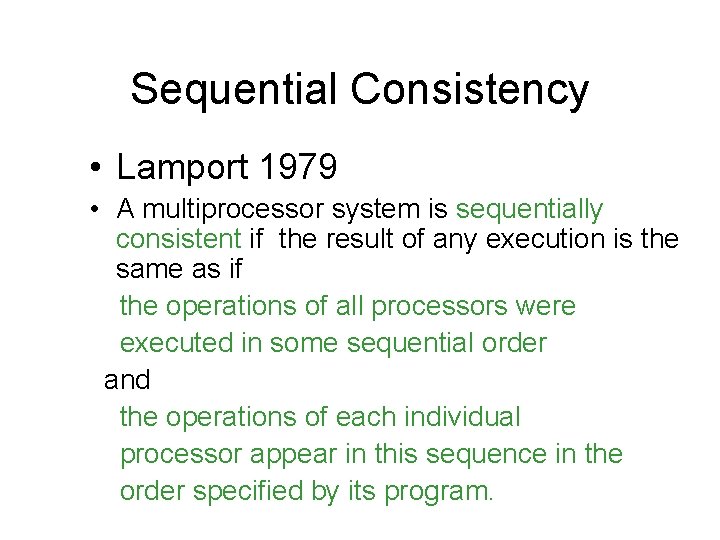

Sequential Consistency • Lamport 1979 • A multiprocessor system is sequentially consistent if the result of any execution is the same as if the operations of all processors were executed in some sequential order and the operations of each individual processor appear in this sequence in the order specified by its program.

Sequential Consistency x=3 y=z z=3 w=x y=4 x=5 a=x b=x ……. , x = 5; x = 3; w = x; y = z; y = 4; z = 3; ……. 3 5 c=x 5 d=x 3

Brown’s Algorithm • Each process has a queue Ini of invalidation requests

Brown’s algorithm • w(x)v: perform all invalidations in In queue; update main memory; place invalidation request in In queue of each process • r(x): if x in cache then read x; else perform all invalidation in Ini read from the main memory

• Whenever main memory is accessed, all outstanding invalidations must be performed. • Sequential consistency is maintained.

Distributed implementation • All processes maintain a local copy • Write w(x)v: send message to all processor updating x to v • Read r(x): read local copy

Ordered Broadcasting • For any two messages m 1 and m 2 that are broadcast (possibly by different processes), they are delivered in the same order (m 1 followed by m 2 or m 2 followed by m 1) to all processes

- Slides: 25