Circuitos Digitales I MDULOS COMBINACIONALES Sesin 8 Mdulos

Circuitos Digitales I MÓDULOS COMBINACIONALES Sesión 8

Módulos combinacionales básicos MSI • Conjunto de compuertas que realizan una tarea específica. • Pueden implementar funciones booleanas. • MSI : (Medium Size of Integration) con un número de compuertas entre 10 y 100. • Circuitos MSI: • Multiplexores, decodificadores, demultiplexores, sumadores y comparadores.

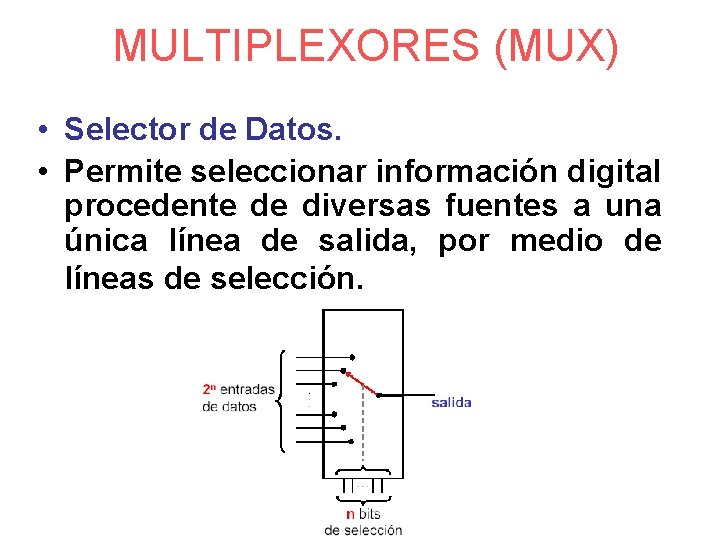

MULTIPLEXORES (MUX) • Selector de Datos. • Permite seleccionar información digital procedente de diversas fuentes a una única línea de salida, por medio de líneas de selección.

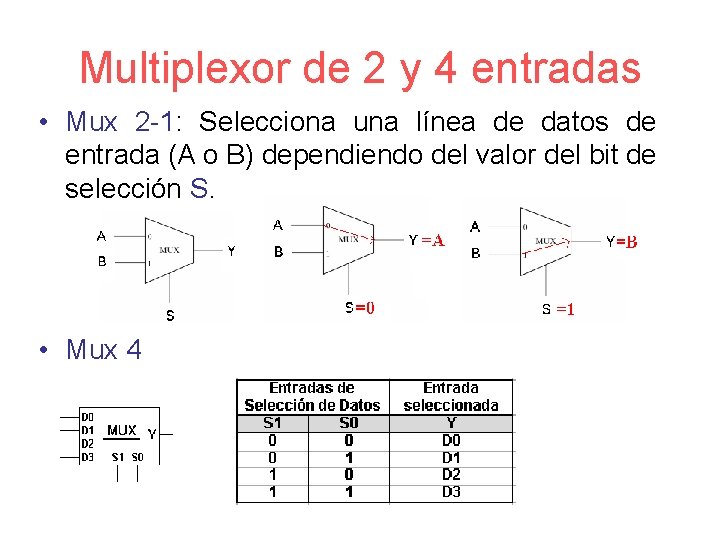

Multiplexor de 2 y 4 entradas • Mux 2 -1: Selecciona una línea de datos de entrada (A o B) dependiendo del valor del bit de selección S. • Mux 4

Configuración interna Mux 2 a 1 Controla el paso del dato Mux 4 a 1

Multiplexor Comercial • 74151 • Mux 8 a 1 Salida Habilitación (encendido) 3 líneas de selección 8 entradas de datos Salida negada

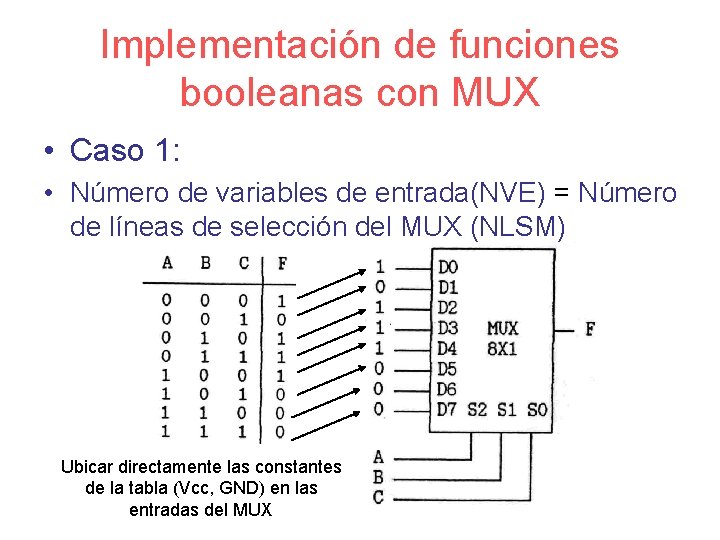

Implementación de funciones booleanas con MUX • Caso 1: • Número de variables de entrada(NVE) = Número de líneas de selección del MUX (NLSM) Ubicar directamente las constantes de la tabla (Vcc, GND) en las entradas del MUX

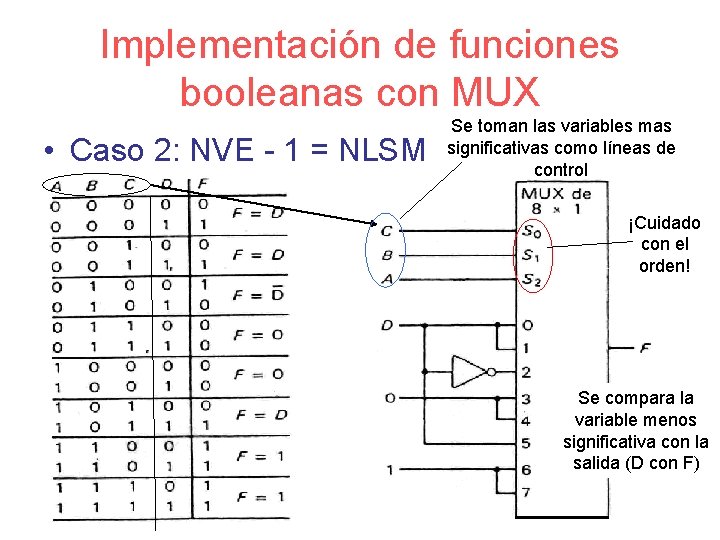

Implementación de funciones booleanas con MUX • Caso 2: NVE - 1 = NLSM Se toman las variables mas significativas como líneas de control ¡Cuidado con el orden! Se compara la variable menos significativa con la salida (D con F)

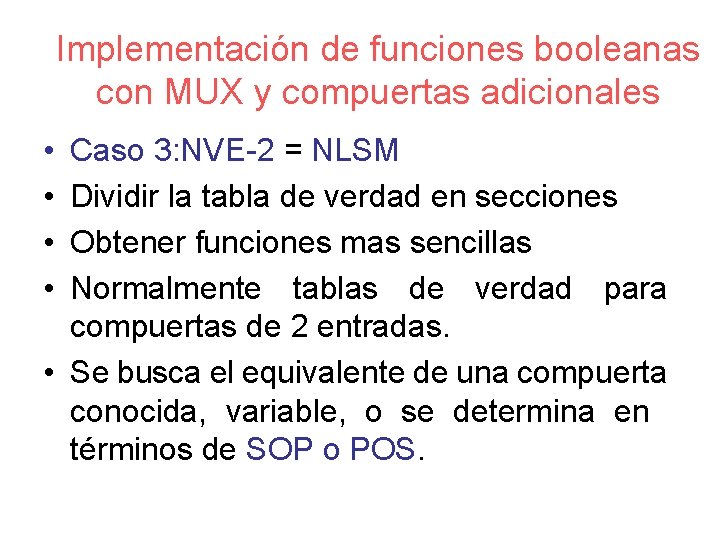

Implementación de funciones booleanas con MUX y compuertas adicionales • • Caso 3: NVE-2 = NLSM Dividir la tabla de verdad en secciones Obtener funciones mas sencillas Normalmente tablas de verdad para compuertas de 2 entradas. • Se busca el equivalente de una compuerta conocida, variable, o se determina en términos de SOP o POS.

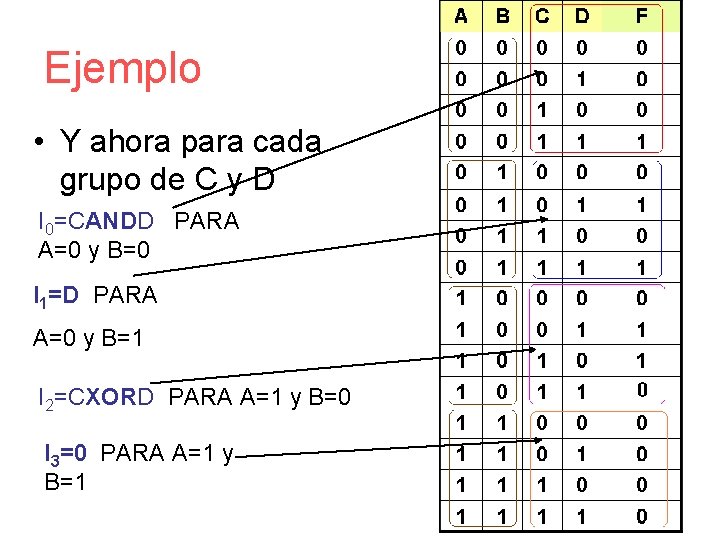

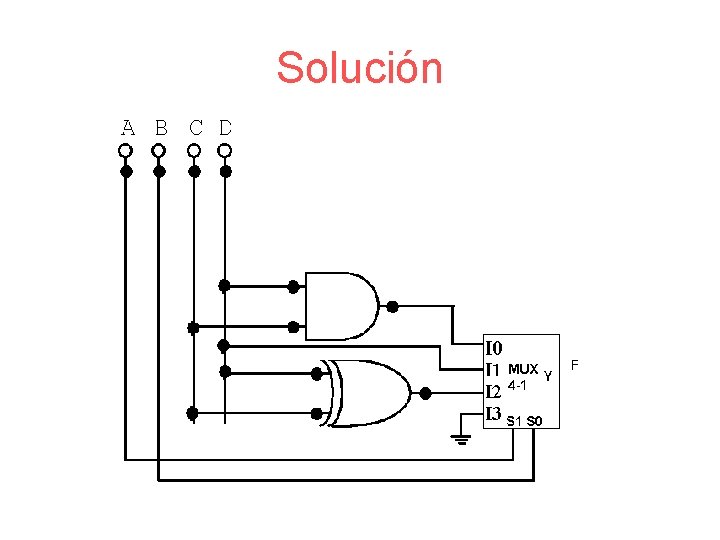

Ejemplo Tablas de verdad de 2 variables • F(A, B, C, D)=Sm(3, 5, 7, 9, 10) • Sean A y B , S 1 y S 0 respectivamente. • Observe como cambia la tabla. I 0 I 1 I 2 I 3

Ejemplo • Y ahora para cada grupo de C y D I 0=CANDD PARA A=0 y B=0 I 1=D PARA A=0 y B=1 I 2=CXORD PARA A=1 y B=0 I 3=0 PARA A=1 y B=1

Solución

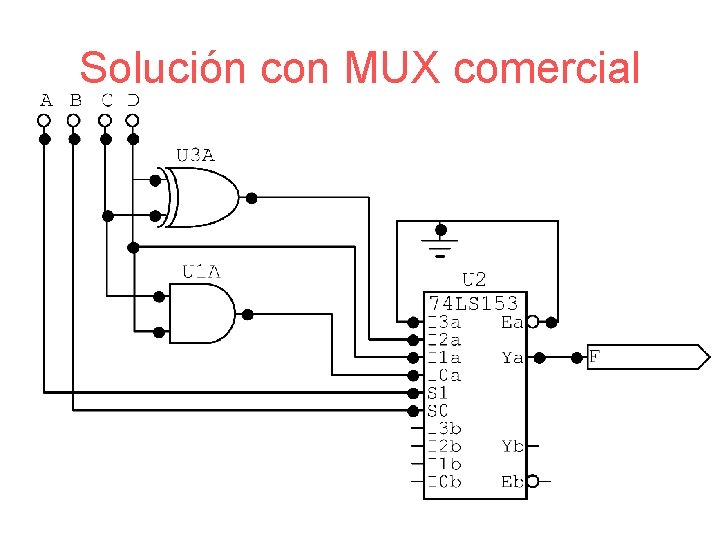

Solución con MUX comercial

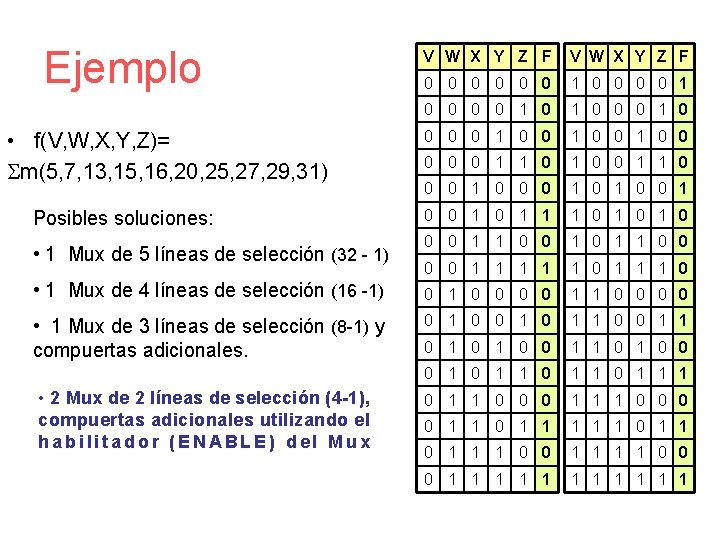

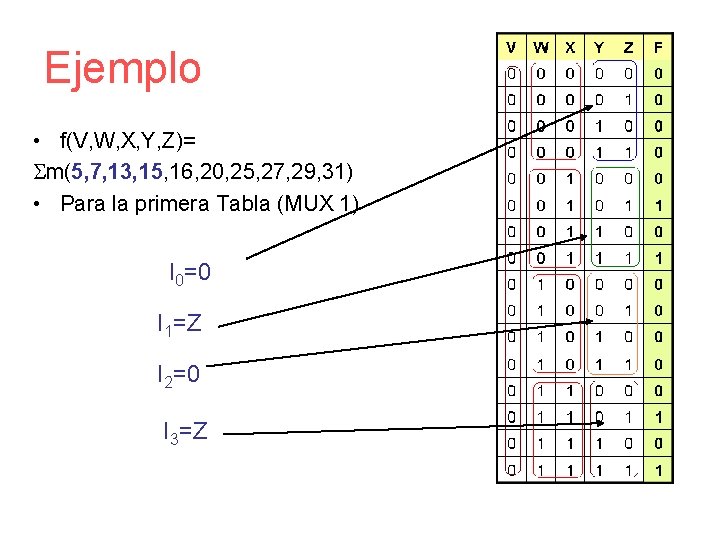

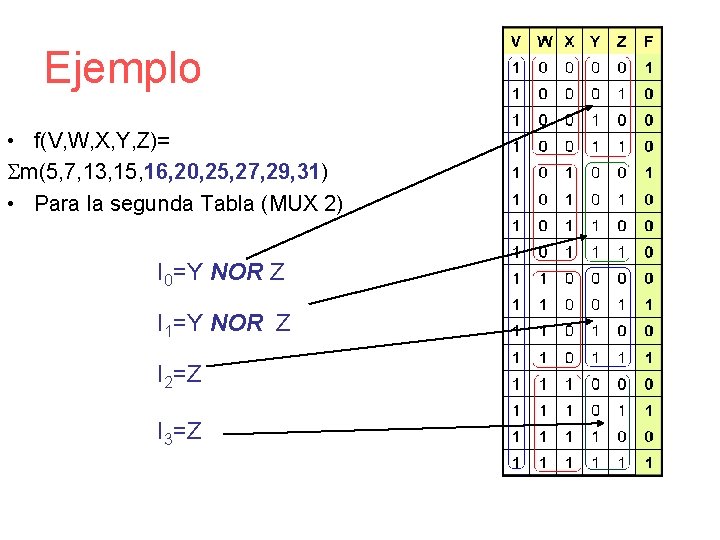

Ejemplo V W X Y Z F 0 0 0 1 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 1 0 • 1 Mux de 4 líneas de selección (16 -1) 0 1 0 0 1 1 0 0 • 1 Mux de 3 líneas de selección (8 -1) y compuertas adicionales. 0 1 0 1 1 0 1 0 0 0 1 1 1 0 0 0 1 1 1 0 0 1 1 1 0 1 1 1 0 0 0 1 1 1 • f(V, W, X, Y, Z)= Sm(5, 7, 13, 15, 16, 20, 25, 27, 29, 31) Posibles soluciones: • 1 Mux de 5 líneas de selección (32 - 1) • 2 Mux de 2 líneas de selección (4 -1), compuertas adicionales utilizando el habilitador (ENABLE) del Mux

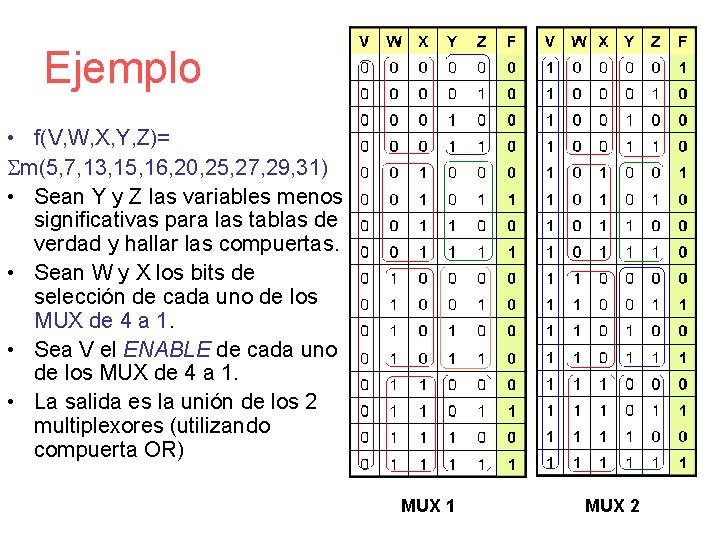

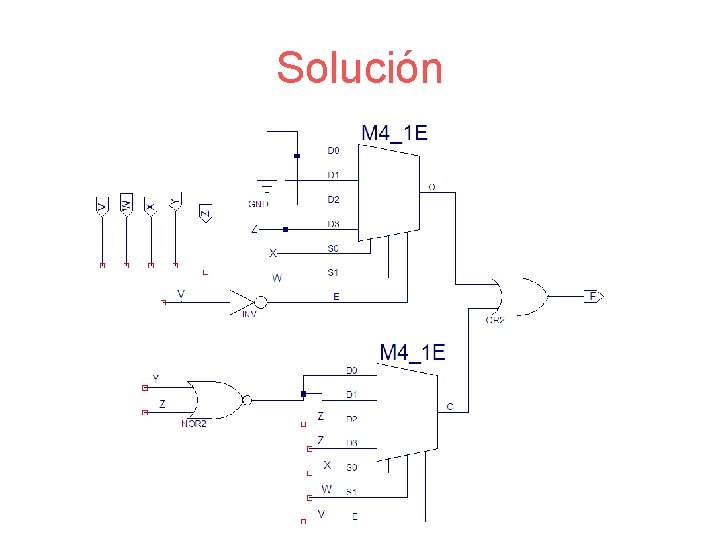

Ejemplo • f(V, W, X, Y, Z)= Sm(5, 7, 13, 15, 16, 20, 25, 27, 29, 31) • Sean Y y Z las variables menos significativas para las tablas de verdad y hallar las compuertas. • Sean W y X los bits de selección de cada uno de los MUX de 4 a 1. • Sea V el ENABLE de cada uno de los MUX de 4 a 1. • La salida es la unión de los 2 multiplexores (utilizando compuerta OR) MUX 1 MUX 2

Ejemplo • f(V, W, X, Y, Z)= Sm(5, 7, 13, 15, 16, 20, 25, 27, 29, 31) • Para la primera Tabla (MUX 1) I 0=0 I 1=Z I 2=0 I 3=Z

Ejemplo • f(V, W, X, Y, Z)= Sm(5, 7, 13, 15, 16, 20, 25, 27, 29, 31) • Para la segunda Tabla (MUX 2) I 0=Y NOR Z I 1=Y NOR Z I 2=Z I 3=Z

Solución

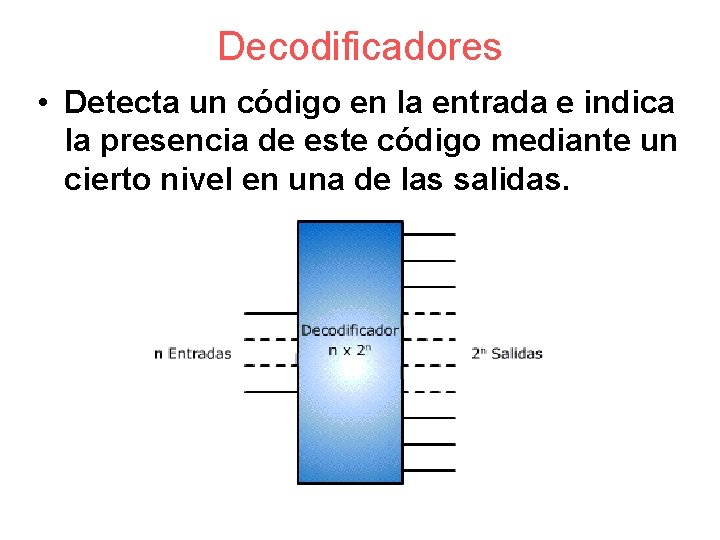

Decodificadores • Detecta un código en la entrada e indica la presencia de este código mediante un cierto nivel en una de las salidas.

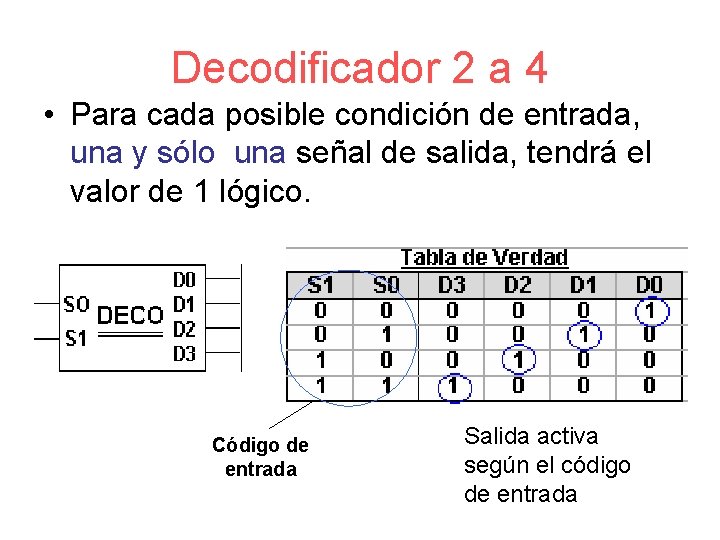

Decodificador 2 a 4 • Para cada posible condición de entrada, una y sólo una señal de salida, tendrá el valor de 1 lógico. Código de entrada Salida activa según el código de entrada

Decodificador 2 a 4 • Una salida solo es 1, en una combinación de S 1 y S 0 : • Aplicaciones: *Convertir códigos *Direccionar memorias y periféricos. *Implementar funciones lógicas

Decodificador 2 a 4(Salidas negadas) Habilitador EN S 1 S 0 D 1 D 2 D 3 1 X X 1 1 0 0 1 1 0 1 1 0

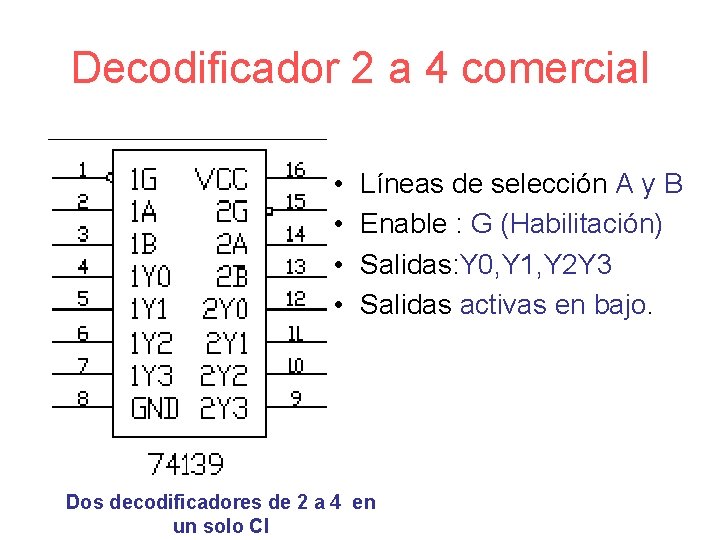

Decodificador 2 a 4 comercial • • Líneas de selección A y B Enable : G (Habilitación) Salidas: Y 0, Y 1, Y 2 Y 3 Salidas activas en bajo. Dos decodificadores de 2 a 4 en un solo CI

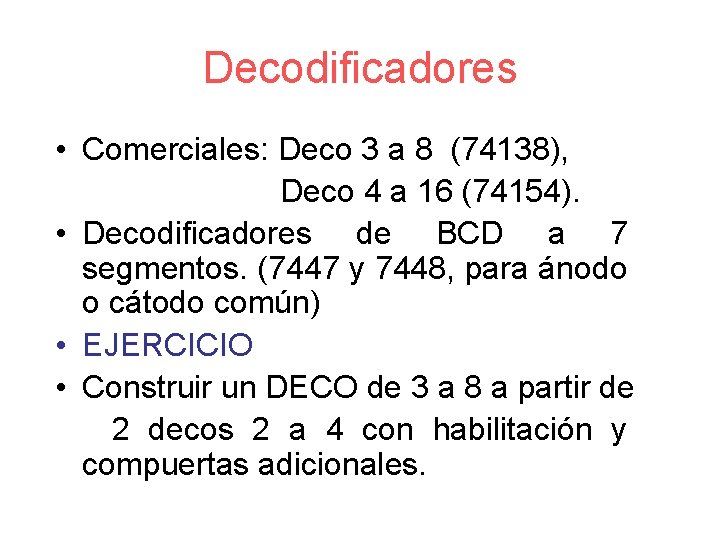

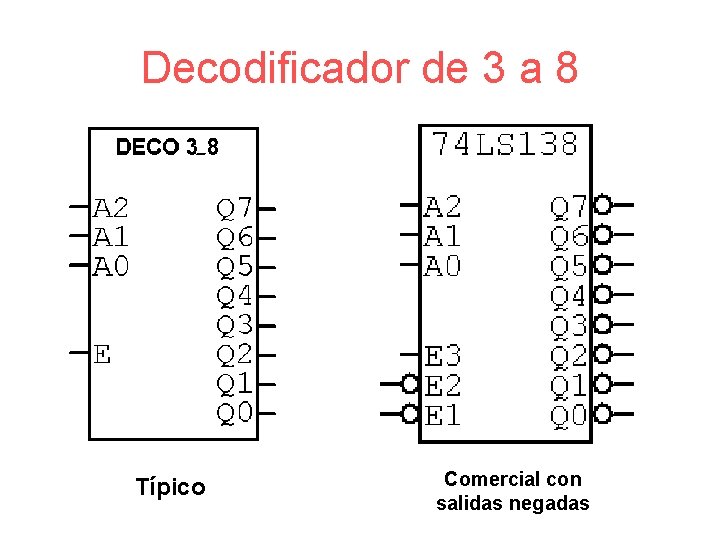

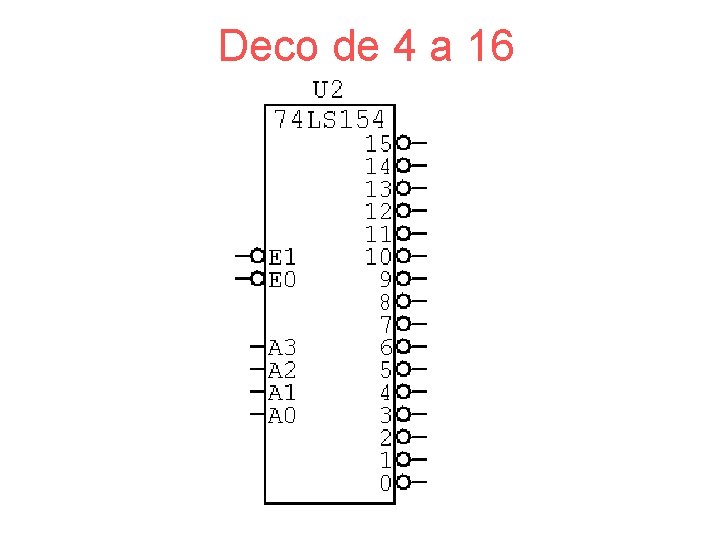

Decodificadores • Comerciales: Deco 3 a 8 (74138), Deco 4 a 16 (74154). • Decodificadores de BCD a 7 segmentos. (7447 y 7448, para ánodo o cátodo común) • EJERCICIO • Construir un DECO de 3 a 8 a partir de 2 decos 2 a 4 con habilitación y compuertas adicionales.

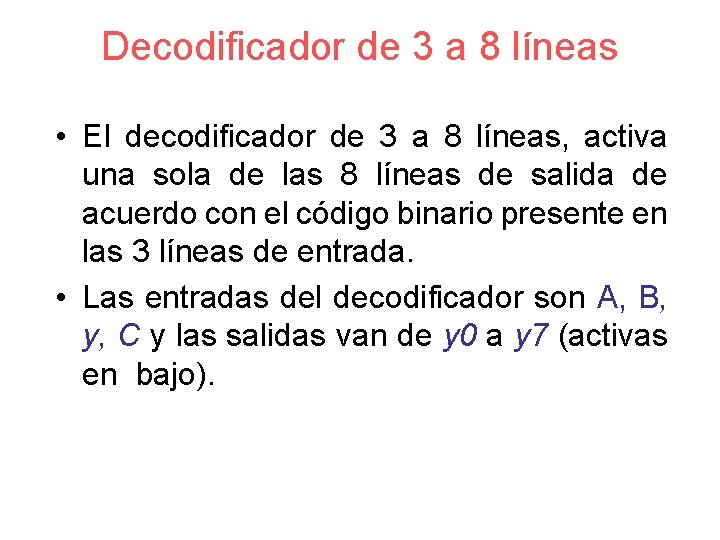

Decodificador de 3 a 8 líneas • El decodificador de 3 a 8 líneas, activa una sola de las 8 líneas de salida de acuerdo con el código binario presente en las 3 líneas de entrada. • Las entradas del decodificador son A, B, y, C y las salidas van de y 0 a y 7 (activas en bajo).

Decodificador de 3 a 8 Típico Comercial con salidas negadas

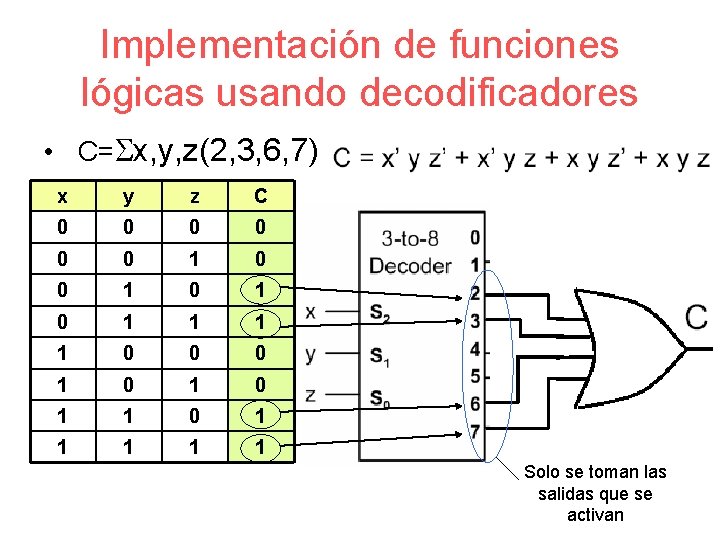

Implementación de funciones lógicas usando decodificadores • C=Sx, y, z(2, 3, 6, 7) x y z C 0 0 0 1 0 1 1 0 0 0 1 0 1 1 1 1 1 Solo se toman las salidas que se activan

Ejemplo SOP Teorema de De. Morgan (X’Y’)’=X+Y POS

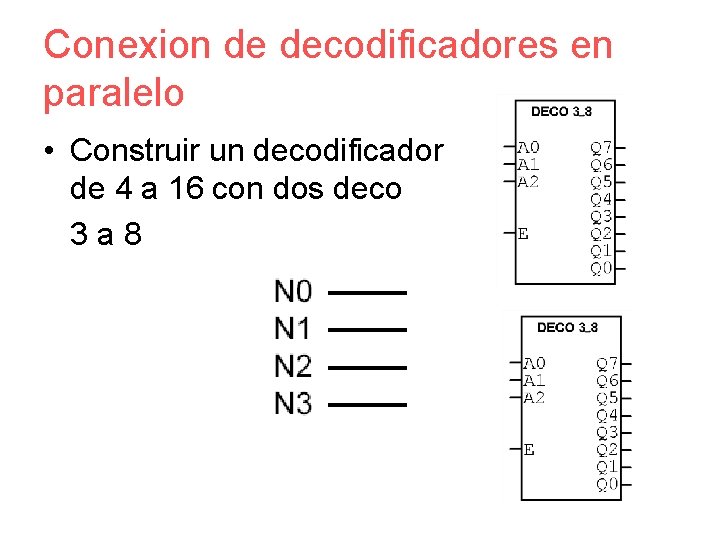

Conexion de decodificadores en paralelo • Construir un decodificador de 4 a 16 con dos deco 3 a 8

Deco de 4 a 16

- Slides: 30