Circuit Simplification and Karnaugh Map Sahar Mosleh California

- Slides: 18

Circuit Simplification and Karnaugh Map Sahar Mosleh California State University San Marcos Page 1

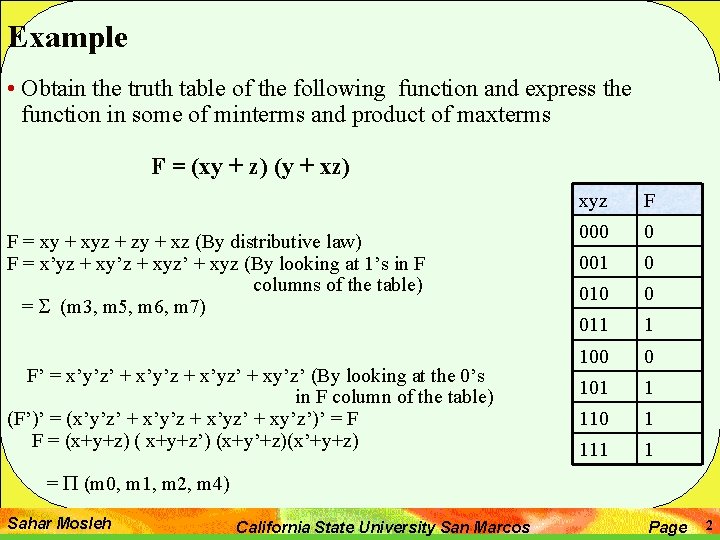

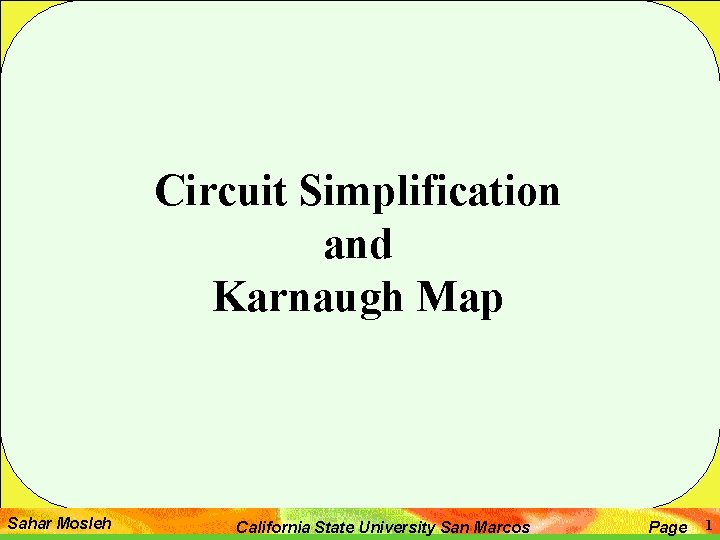

Example • Obtain the truth table of the following function and express the function in some of minterms and product of maxterms F = (xy + z) (y + xz) F = xy + xyz + zy + xz (By distributive law) F = x’yz + xy’z + xyz’ + xyz (By looking at 1’s in F columns of the table) = S (m 3, m 5, m 6, m 7) F’ = x’y’z’ + x’y’z + x’yz’ + xy’z’ (By looking at the 0’s in F column of the table) (F’)’ = (x’y’z’ + x’y’z + x’yz’ + xy’z’)’ = F F = (x+y+z) ( x+y+z’) (x+y’+z)(x’+y+z) xyz F 000 0 001 0 010 0 011 1 100 0 101 1 110 1 111 1 = P (m 0, m 1, m 2, m 4) Sahar Mosleh California State University San Marcos Page 2

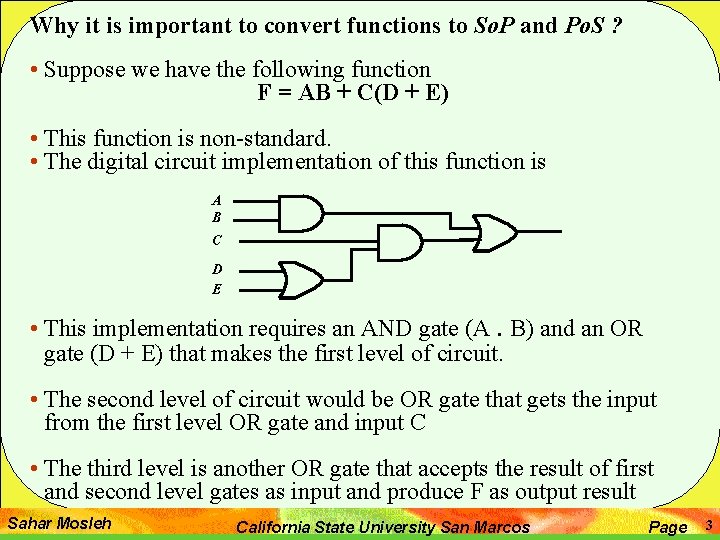

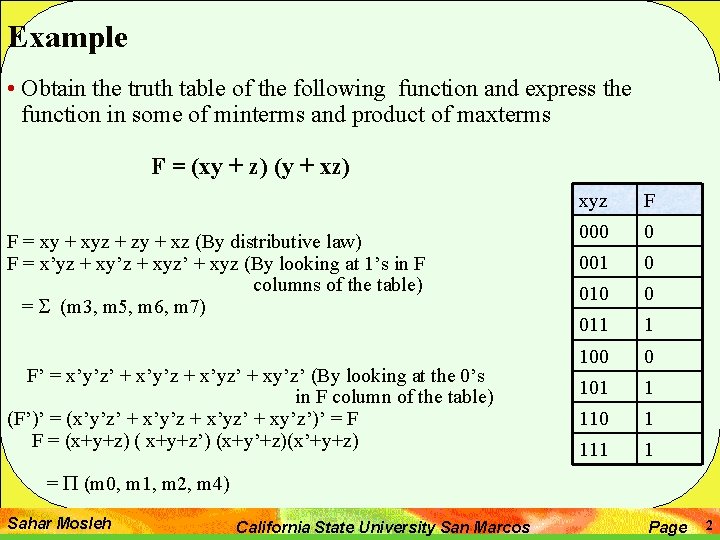

Why it is important to convert functions to So. P and Po. S ? • Suppose we have the following function F = AB + C(D + E) • This function is non-standard. • The digital circuit implementation of this function is A B C D E • This implementation requires an AND gate (A. B) and an OR gate (D + E) that makes the first level of circuit. • The second level of circuit would be OR gate that gets the input from the first level OR gate and input C • The third level is another OR gate that accepts the result of first and second level gates as input and produce F as output result Sahar Mosleh California State University San Marcos Page 3

• Now the function F can be changed to standard form by using the distributive law to remove the parenthesis F = AB + C (D+E) = AB + CD + CE • The So. P expression can be implemented as follows: A B C D F = AB + CD + CE C E Sahar Mosleh California State University San Marcos Page 4

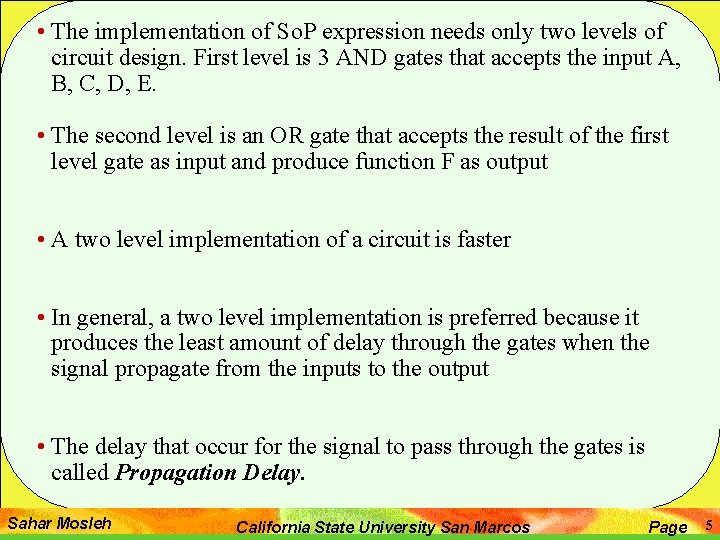

• The implementation of So. P expression needs only two levels of circuit design. First level is 3 AND gates that accepts the input A, B, C, D, E. • The second level is an OR gate that accepts the result of the first level gate as input and produce function F as output • A two level implementation of a circuit is faster • In general, a two level implementation is preferred because it produces the least amount of delay through the gates when the signal propagate from the inputs to the output • The delay that occur for the signal to pass through the gates is called Propagation Delay. Sahar Mosleh California State University San Marcos Page 5

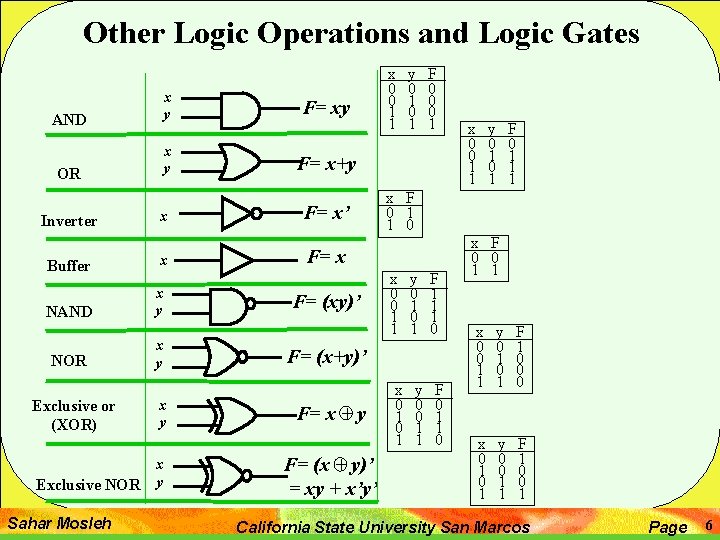

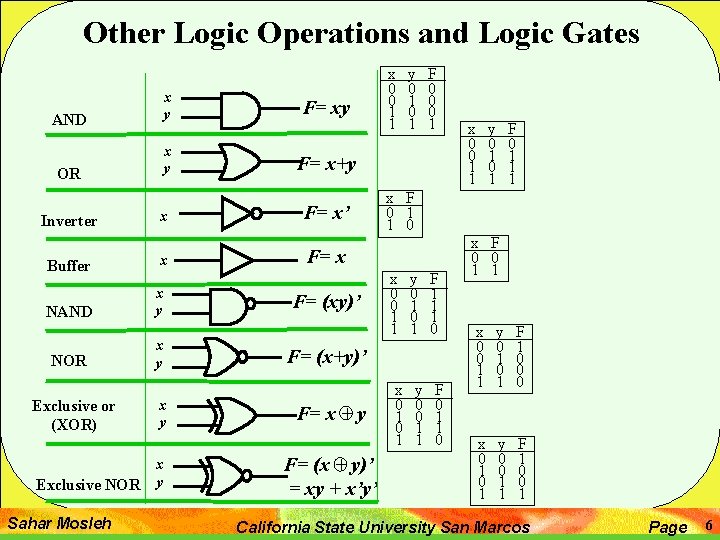

Other Logic Operations and Logic Gates AND x y F= xy OR x y F= x+y x F= x’ Buffer x F= x NAND x y NOR x y Inverter Exclusive or (XOR) Exclusive NOR Sahar Mosleh x y F= (xy)’ x 0 0 1 1 y 0 1 F 0 0 0 1 F= (x + y)’ = xy + x’y’ y 0 1 F 0 1 1 1 x F 0 1 1 0 x 0 0 1 1 y 0 1 F 1 1 1 0 F= (x+y)’ F= x + y x 0 0 1 1 x 0 1 y 0 0 1 1 F 0 1 1 0 x F 0 0 1 1 x 0 0 1 1 y 0 1 F 1 0 0 0 x 0 1 y 0 0 1 1 F 1 0 0 1 California State University San Marcos Page 6

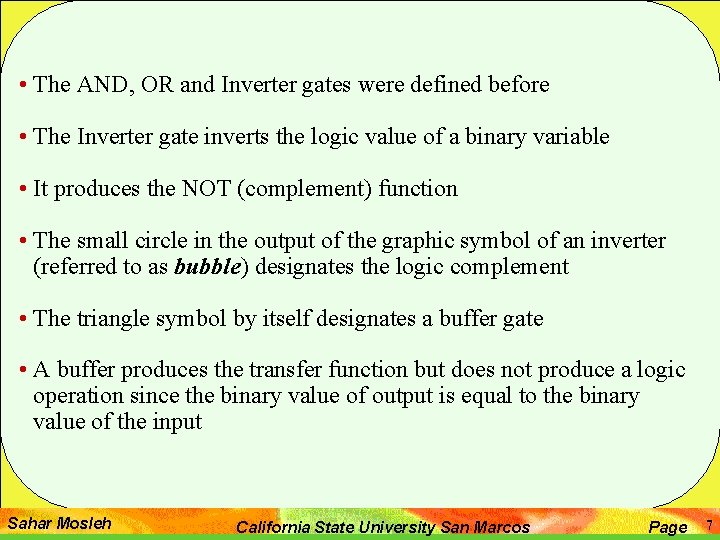

• The AND, OR and Inverter gates were defined before • The Inverter gate inverts the logic value of a binary variable • It produces the NOT (complement) function • The small circle in the output of the graphic symbol of an inverter (referred to as bubble) designates the logic complement • The triangle symbol by itself designates a buffer gate • A buffer produces the transfer function but does not produce a logic operation since the binary value of output is equal to the binary value of the input Sahar Mosleh California State University San Marcos Page 7

• The NAND function is the complement of the AND function as indicated by graphic symbol that consists of an AND graphic symbol followed by a bubble (symbol of inverter ) • The NOR function is the complement of the OR function as indicated by graphic symbol that consists of an OR graphic symbol followed by a bubble (symbol of inverter) • The NAND and NOR gates are extensively used as standard logic gates and are in fact far more popular than the AND and OR gates • This is because NAND and NOR gates are easier and cheaper to make (compare to AND or OR gates) and digital circuits can be easily implemented with them • The exclusive or (XOR) gate has a graphic symbol similar to OR gate except for addition curved line on the input site. • Exclusive NOR gate (XNOR) is complement of XOR, as indicated by small circle on the output side of the graphic symbol Sahar Mosleh California State University San Marcos Page 8

Optimization of Logic Functions • As was stated earlier, all logic functions can be expressed in canonical form directly from a truth table. • However, implementing directly from the canonical form doesn’t necessarily yield the most efficient circuit. • Simplification via algebraic manipulation is not always obvious or practical for functions with a large number of variables. • Though a truth table is a unique representation for a function, the algebraic and physical implementations are non-unique. As a result, we want to determine which implementation will yield an optimal circuit. • The complexity of a digital circuit that implements a Boolean function is directly related to the complexity of its algebraic expression. Thus we want to be able to generate the simplest algebraic expression possible. Sahar Mosleh California State University San Marcos Page 9

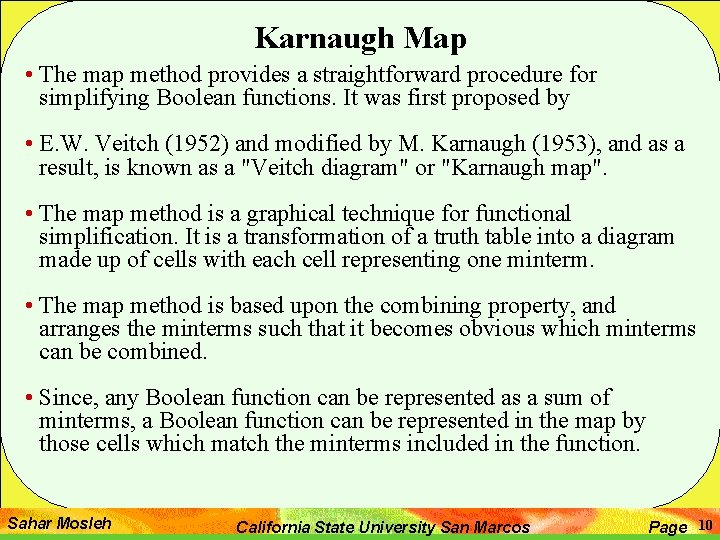

Karnaugh Map • The map method provides a straightforward procedure for simplifying Boolean functions. It was first proposed by • E. W. Veitch (1952) and modified by M. Karnaugh (1953), and as a result, is known as a "Veitch diagram" or "Karnaugh map". • The map method is a graphical technique for functional simplification. It is a transformation of a truth table into a diagram made up of cells with each cell representing one minterm. • The map method is based upon the combining property, and arranges the minterms such that it becomes obvious which minterms can be combined. • Since, any Boolean function can be represented as a sum of minterms, a Boolean function can be represented in the map by those cells which match the minterms included in the function. Sahar Mosleh California State University San Marcos Page 10

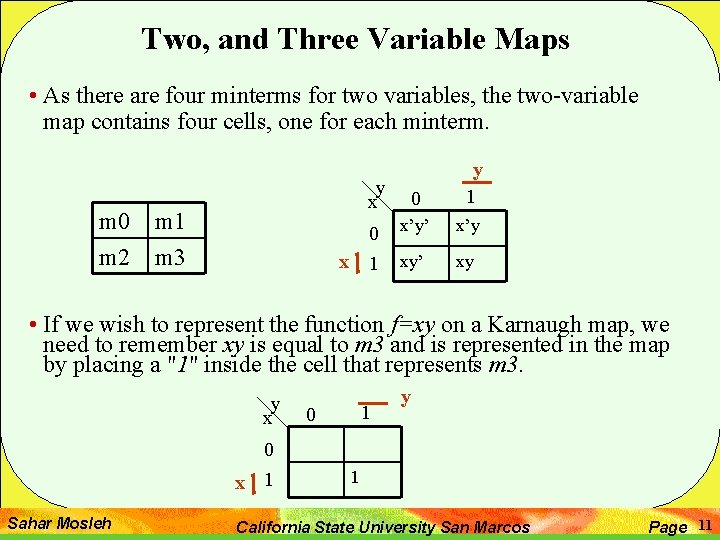

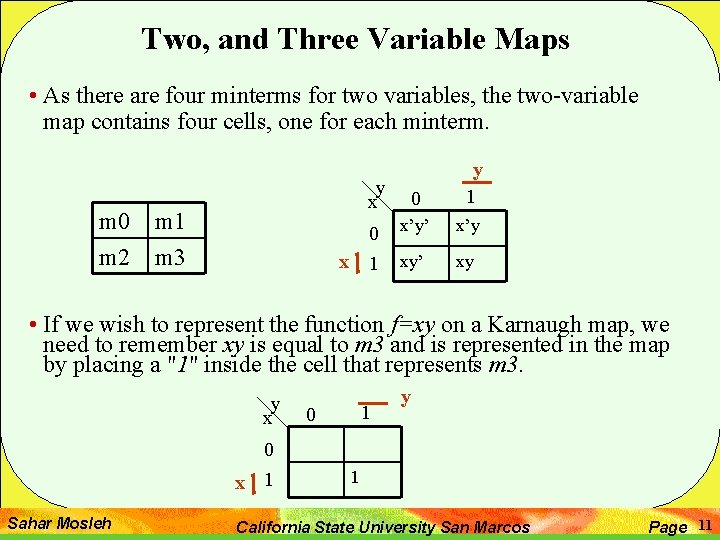

Two, and Three Variable Maps • As there are four minterms for two variables, the two-variable map contains four cells, one for each minterm. m 0 m 2 m 1 m 3 x y 1 y x 0 0 x’y’ x’y 1 xy’ xy • If we wish to represent the function f=xy on a Karnaugh map, we need to remember xy is equal to m 3 and is represented in the map by placing a "1" inside the cell that represents m 3. y x 0 x 1 Sahar Mosleh 1 0 y 1 California State University San Marcos Page 11

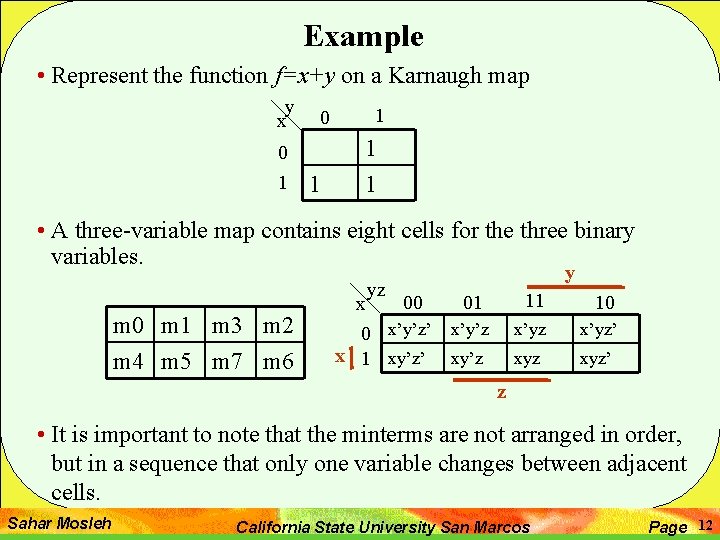

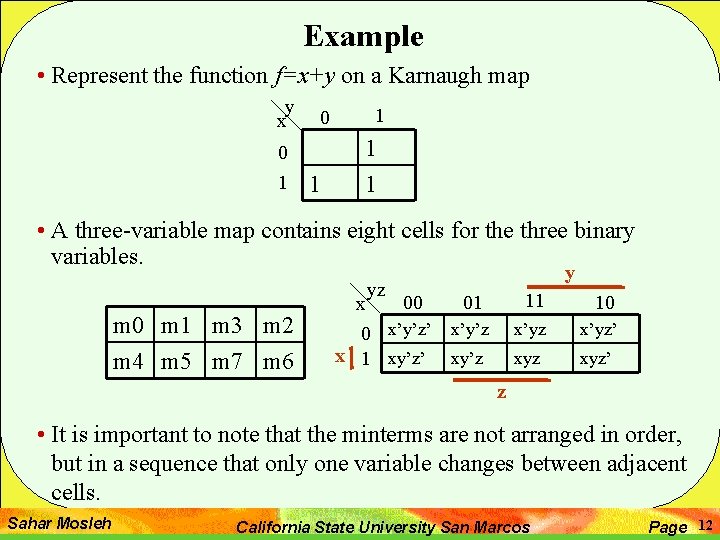

Example • Represent the function f=x+y on a Karnaugh map y x 0 1 1 1 1 • A three-variable map contains eight cells for the three binary variables. m 0 m 1 m 3 m 2 m 4 m 5 m 7 m 6 y yz 00 01 x 0 x’y’z’ x’y’z x 1 xy’z’ xy’z 11 10 x’yz’ xyz’ z • It is important to note that the minterms are not arranged in order, but in a sequence that only one variable changes between adjacent cells. Sahar Mosleh California State University San Marcos Page 12

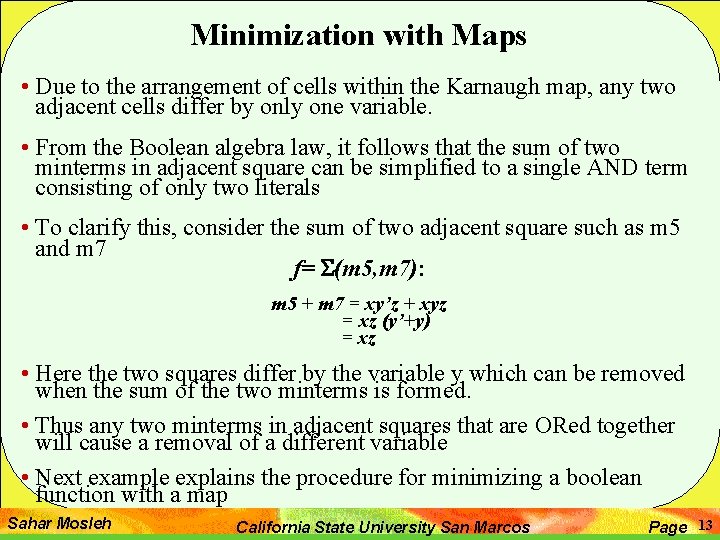

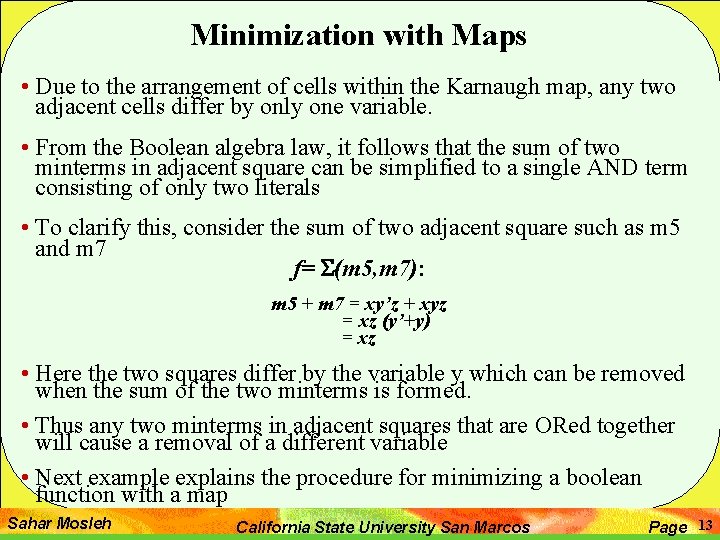

Minimization with Maps • Due to the arrangement of cells within the Karnaugh map, any two adjacent cells differ by only one variable. • From the Boolean algebra law, it follows that the sum of two minterms in adjacent square can be simplified to a single AND term consisting of only two literals • To clarify this, consider the sum of two adjacent square such as m 5 and m 7 f= S(m 5, m 7): m 5 + m 7 = xy’z + xyz = xz (y’+y) = xz • Here the two squares differ by the variable y which can be removed when the sum of the two minterms is formed. • Thus any two minterms in adjacent squares that are ORed together will cause a removal of a different variable • Next example explains the procedure for minimizing a boolean function with a map Sahar Mosleh California State University San Marcos Page 13

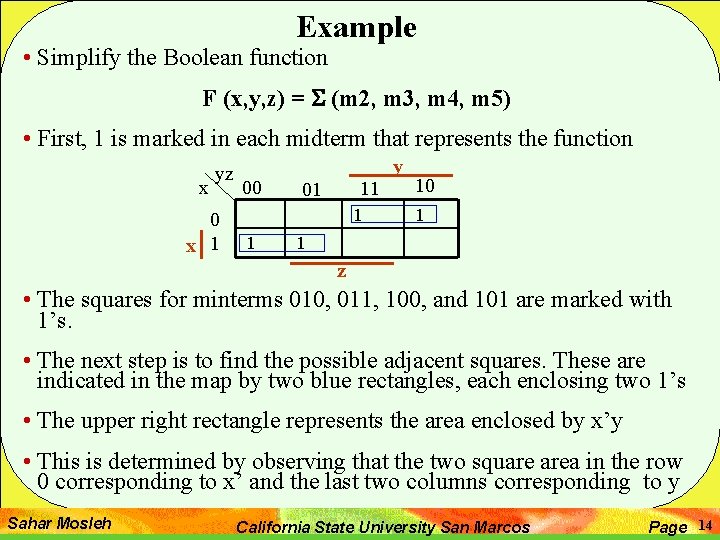

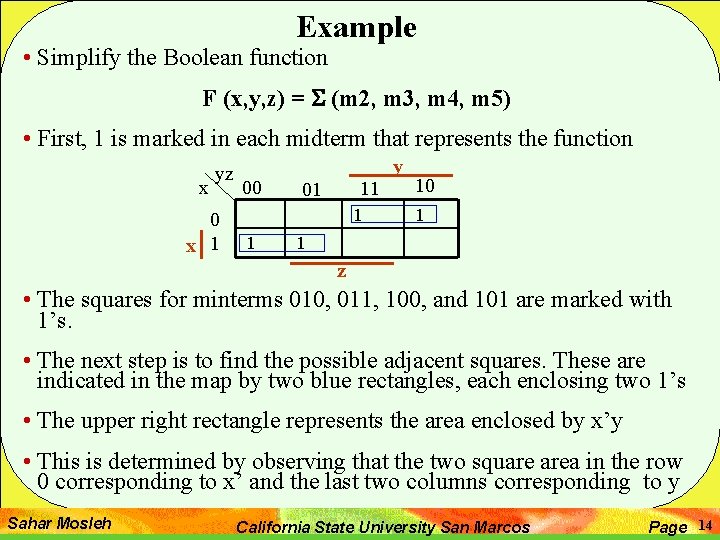

Example • Simplify the Boolean function F (x, y, z) = S (m 2, m 3, m 4, m 5) • First, 1 is marked in each midterm that represents the function x yz 0 x 1 00 11 01 1 1 y 10 1 1 z • The squares for minterms 010, 011, 100, and 101 are marked with 1’s. • The next step is to find the possible adjacent squares. These are indicated in the map by two blue rectangles, each enclosing two 1’s • The upper right rectangle represents the area enclosed by x’y • This is determined by observing that the two square area in the row 0 corresponding to x’ and the last two columns corresponding to y Sahar Mosleh California State University San Marcos Page 14

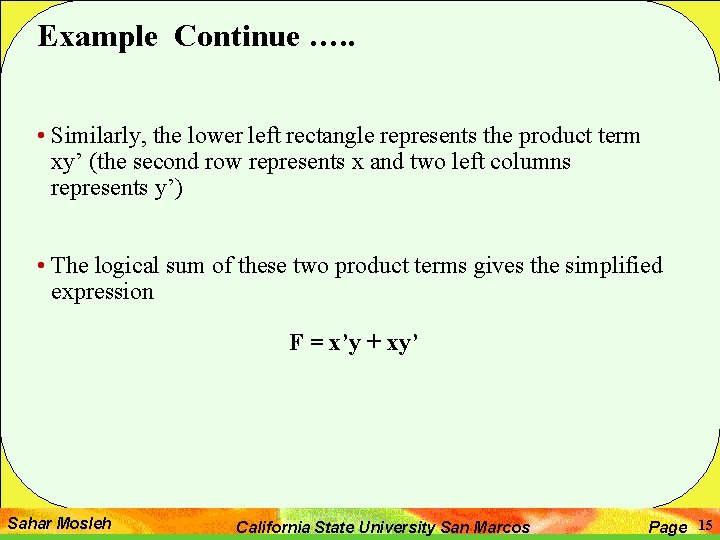

Example Continue …. . • Similarly, the lower left rectangle represents the product term xy’ (the second row represents x and two left columns represents y’) • The logical sum of these two product terms gives the simplified expression F = x’y + xy’ Sahar Mosleh California State University San Marcos Page 15

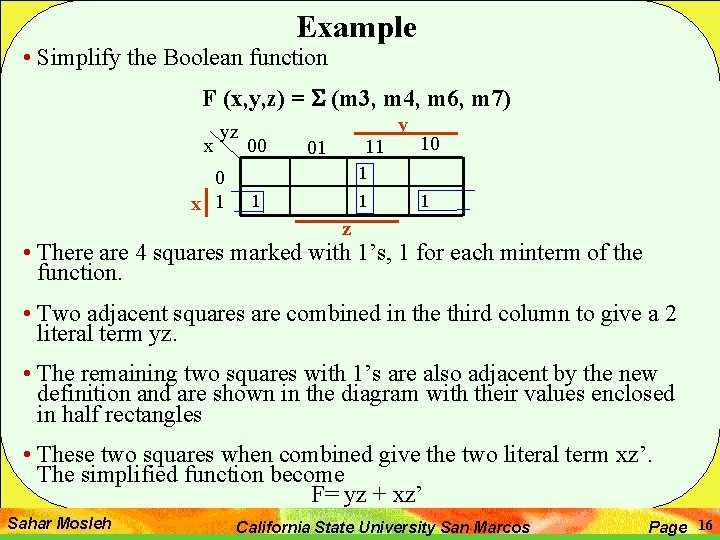

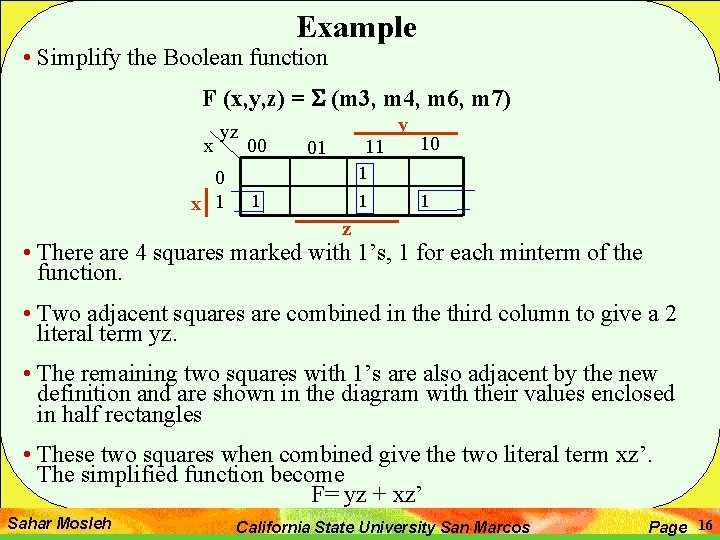

Example • Simplify the Boolean function F (x, y, z) = S (m 3, m 4, m 6, m 7) x yz 0 x 1 00 11 01 y 10 1 1 z • There are 4 squares marked with 1’s, 1 for each minterm of the function. • Two adjacent squares are combined in the third column to give a 2 literal term yz. • The remaining two squares with 1’s are also adjacent by the new definition and are shown in the diagram with their values enclosed in half rectangles • These two squares when combined give the two literal term xz’. The simplified function become F= yz + xz’ Sahar Mosleh California State University San Marcos Page 16

• Consider now any combination of four adjacent square in three variable map • Any such combination represents the logical sum of four minterms and results in a expression of only one literal • As an example, the logical sum four adjacent minterms m 0, m 2, m 4, m 6 reduces to a single literal term z’ • m 0 + m 2 + m 4 + m 6 = x’y’z’ + x’yz’ + xy’z’ + xyz’ = x’z’(y’+y) + xz’(y’+y) = x’z’ + xz’ = z’(x’+x) = z’ • The number of adjacent square that may be combined must be always represent a number that is a power of 2 such as 1, 2, 4, and 8 Sahar Mosleh California State University San Marcos Page 17

• As a larger number of adjacent squares combined, we obtain a product term with fewer literal • One square represents one minterm given a term of three literals • Two adjacent squares represents a term of two literals • Four adjacent squares represents a term of one literal • Eight adjacent squares takes the entire map and produce the function that always equal to 1 Sahar Mosleh California State University San Marcos Page 18