Chip measurements Giovanni Darbo INFN Genova Email Giovanni

Chip measurements Giovanni Darbo / INFN - Genova E-mail: Giovanni. Darbo@ge. infn. it Talk highlights: Test setups; Parametric tests (IDD, VDD, timing); Power up reset; Functional tests: FIFOs, FE config, Event Builder, …; Yield… very preliminary; Test vectors & wafer probing; Post irradiation measurements. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002

MCC-I: The chipto be tested. . . G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 2

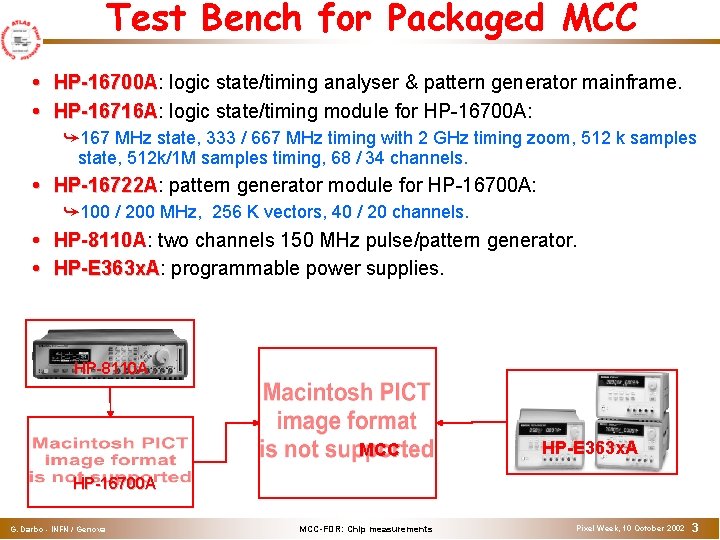

Test Bench for Packaged MCC HP-16700 A: HP-16700 A logic state/timing analyser & pattern generator mainframe. HP-16716 A: HP-16716 A logic state/timing module for HP-16700 A: 167 MHz state, 333 / 667 MHz timing with 2 GHz timing zoom, 512 k samples state, 512 k/1 M samples timing, 68 / 34 channels. HP-16722 A: HP-16722 A pattern generator module for HP-16700 A: 100 / 200 MHz, 256 K vectors, 40 / 20 channels. HP-8110 A: HP-8110 A two channels 150 MHz pulse/pattern generator. HP-E 363 x. A: HP-E 363 x. A programmable power supplies. HP-8110 A MCC HP-E 363 x. A HP-16700 A G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 3

IDD vs VDD Simulation explains measures G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 4

IDD vs CK frequency Linear behaviour of IDD with respect to clock frequency; The zero frequency IDD current is due to the LVDS I/O pads. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 5

IDD vs VDD (CK = 40 MHz) The 114 m. A for IDD at 2. 0 V could be reduced by 10 -15 m. A if the AMS compatibility pads will not be implemented; For comparison: MCC-AMS: IDD=55 m. A @ VDD=3. 3 V MCC-D 2: IDD=100 m. A @ VDD=3. 3 V G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 6

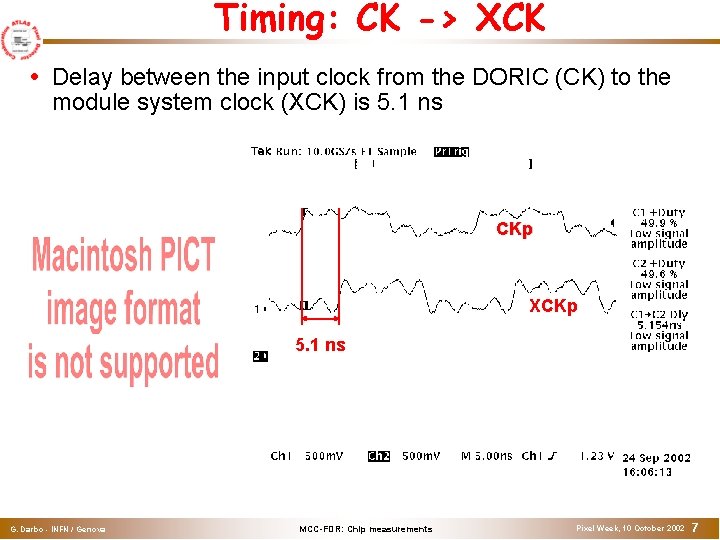

Timing: CK -> XCK Delay between the input clock from the DORIC (CK) to the module system clock (XCK) is 5. 1 ns CKp XCKp 5. 1 ns G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 7

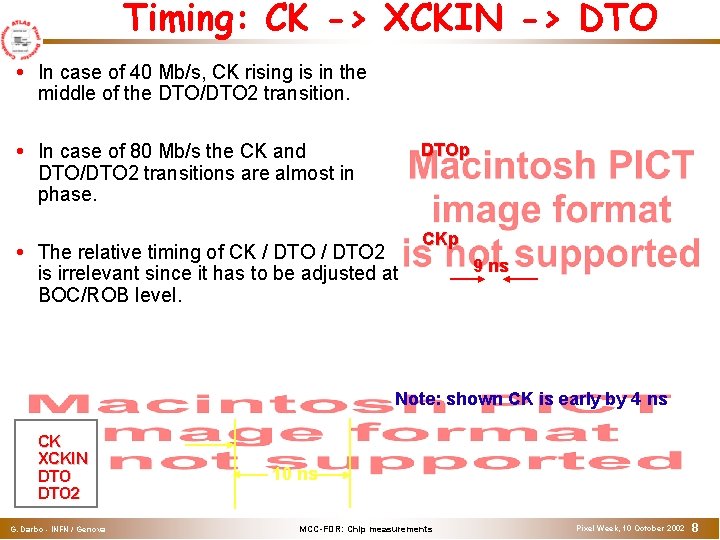

Timing: CK -> XCKIN -> DTO In case of 40 Mb/s, CK rising is in the middle of the DTO/DTO 2 transition. In case of 80 Mb/s the CK and DTO/DTO 2 transitions are almost in phase. DTOp The relative timing of CK / DTO 2 is irrelevant since it has to be adjusted at BOC/ROB level. CKp 9 ns Note: shown CK is early by 4 ns CK XCKIN DTO 2 G. Darbo - INFN / Genova 10 ns MCC-FDR: Chip measurements Pixel Week, 10 October 2002 8

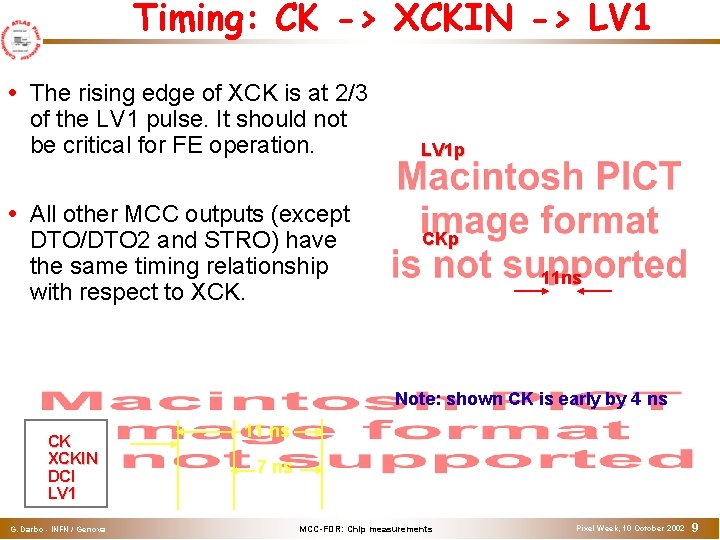

Timing: CK -> XCKIN -> LV 1 The rising edge of XCK is at 2/3 of the LV 1 pulse. It should not be critical for FE operation. All other MCC outputs (except DTO/DTO 2 and STRO) have the same timing relationship with respect to XCK. LV 1 p CKp 11 ns Note: shown CK is early by 4 ns CK XCKIN DCI LV 1 G. Darbo - INFN / Genova 11 ns 7 ns MCC-FDR: Chip measurements Pixel Week, 10 October 2002 9

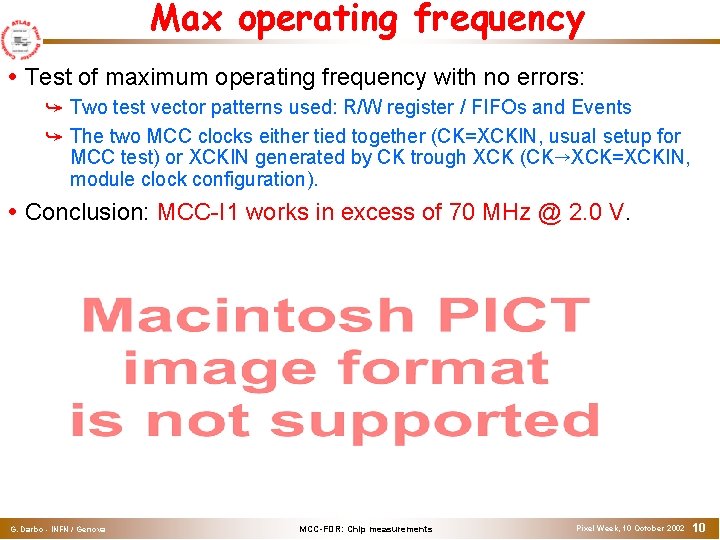

Max operating frequency Test of maximum operating frequency with no errors: Two test vector patterns used: R/W register / FIFOs and Events The two MCC clocks either tied together (CK=XCKIN, usual setup for MCC test) or XCKIN generated by CK trough XCK (CK XCK=XCKIN, module clock configuration). Conclusion: MCC-I 1 works in excess of 70 MHz @ 2. 0 V. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 10

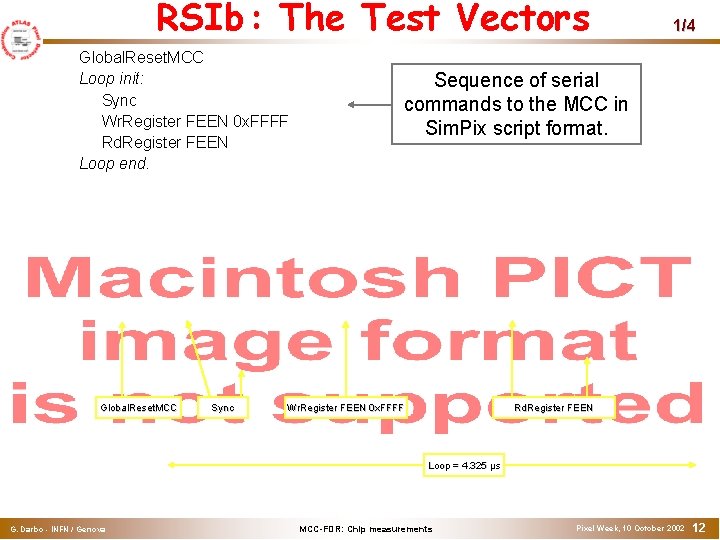

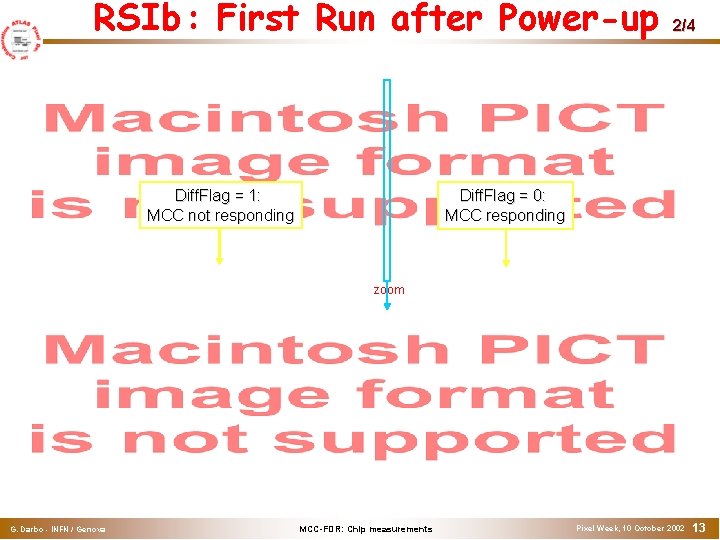

RSIb: Considerations on the Test vectors have Init part repeated only once and a Loop repeated indefinitely. In the Init either a Global. Reset. MCC or no command is inserted. In the Loop both a fast command (Sync) and a Wr. Register and a Rd. Register are executed. When the MCC responds to both commands, the command decoder is “alive” and the MCC works in normal way (it my need a Global. Reset. MCC to reset the other MCC blocks). Waveforms: (see next pages) [1/4] Shows the command sequence; [2/4] First run after power up. The MCC responds correctly to the Read/Write and to the Sync command after 131 k. States (the LSA samples the signals twice per clock cycles). This means that after 131132/8000 = 1. 63 µs the MCC is alive (8000 is the number of LSA samples/µs). [3/4] If the test is run a second time without a power cycle, the MCC always respond. [4/4] If the same test is executed dropping the initial Global. Reset. MCC the behaviour is the same. The Global. Restet. MCC is not able to reset the command decoder itself. Conclusion: The MCC has been designed with the command decoder that always go to the “idle state” after a finite time. The longest time is about 64 k states because it has a free running 16 -bit counter that only when it pass from ‘ 0’ allows the command decoder to exit from some internal states and to reach the idle state. The waveforms in the next pages, documents the behaviour for MCC-0302. Not all the MCC tested need so long wakeup time, this depends on the configuration of the command decoder at power-up. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 11

RSIb: The Test Vectors Global. Reset. MCC Loop init: Sync Wr. Register FEEN 0 x. FFFF Rd. Register FEEN Loop end. Global. Reset. MCC Sync 1/4 Sequence of serial commands to the MCC in Sim. Pix script format. Wr. Register FEEN 0 x. FFFF Rd. Register FEEN Loop = 4. 325 µs G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 12

RSIb: First Run after Power-up Diff. Flag = 1: MCC not responding 2/4 Diff. Flag = 0: MCC responding zoom G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 13

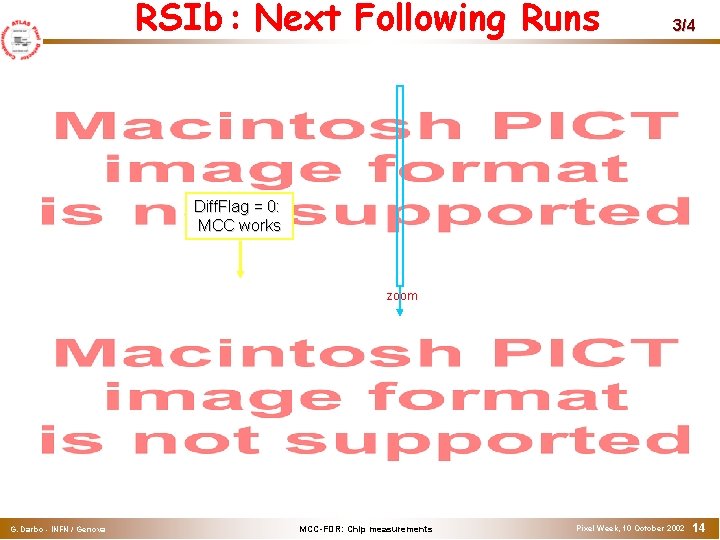

RSIb: Next Following Runs 3/4 Diff. Flag = 0: MCC works zoom G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 14

RSIb: No Global. Reset. MCC 4/4 Without an initial RSIb the MCC behaves in the way. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 15

RSIb vs Global. Reset. MCC RSIb resets every single FF in the MCC in a single clock cycle, while the Global. Reset. MCC is able to reset all the MCC blocks but the command decoder. The command decoder “auto resets itself” (go to idle state) in a definite time of < ~ 64 k clock cycles. Only after the command decoder is in the idle state the MCC is able to respond to any command (Global. Reset. MCC included). With the test done, that confirm the design strategy for the command decoder used in the chip, we believe that the pin reset (RSIb) is not needed for system operation in the ATLAS detector. Another confirm to that, it is the operation of 7 MCC at the PS irradiation for several days and with many single event upsets: neither sign of dead lock has been seen or need of a pin reset have been necessary to restart the chip. We still need the RSIb for testability of the chip. The RSIb puts the MCC in a well defined condition in a clock cycle after it is issued and it makes the test vectors more effective. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 16

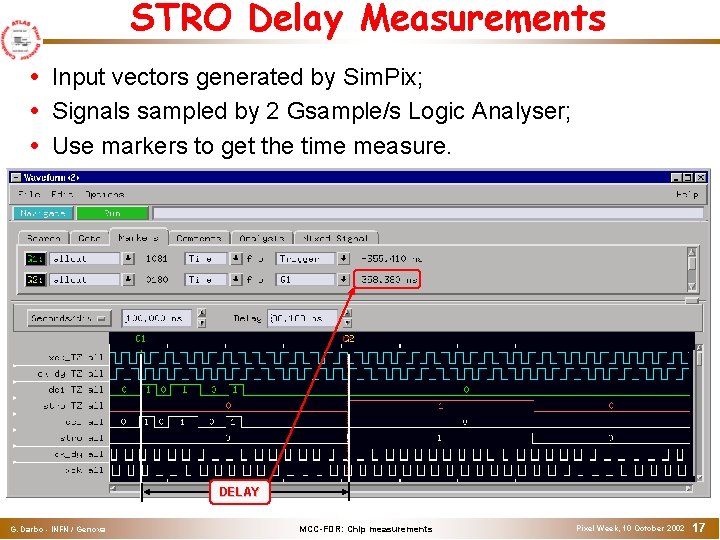

STRO Delay Measurements Input vectors generated by Sim. Pix; Signals sampled by 2 Gsample/s Logic Analyser; Use markers to get the time measure. DELAY G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 17

STRO Delay: Delayvs Set Value & Range G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 18

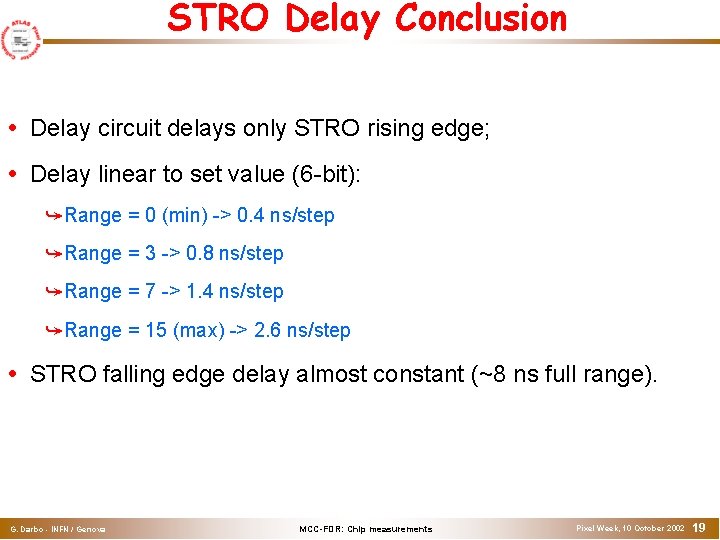

STRO Delay Conclusion Delay circuit delays only STRO rising edge; Delay linear to set value (6 -bit): Range = 0 (min) -> 0. 4 ns/step Range = 3 -> 0. 8 ns/step Range = 7 -> 1. 4 ns/step Range = 15 (max) -> 2. 6 ns/step STRO falling edge delay almost constant (~8 ns full range). G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 19

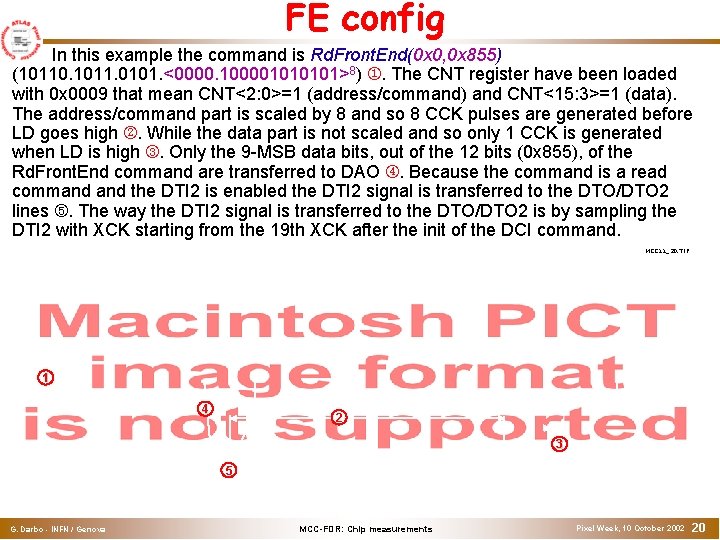

FE config In this example the command is Rd. Front. End(0 x 0, 0 x 855) (10110. 1011. 0101. <0000. 10000101>8) . The CNT register have been loaded with 0 x 0009 that mean CNT<2: 0>=1 (address/command) and CNT<15: 3>=1 (data). The address/command part is scaled by 8 and so 8 CCK pulses are generated before LD goes high . While the data part is not scaled and so only 1 CCK is generated when LD is high . Only the 9 -MSB data bits, out of the 12 bits (0 x 855), of the Rd. Front. End command are transferred to DAO . Because the command is a read command the DTI 2 is enabled the DTI 2 signal is transferred to the DTO/DTO 2 lines . The way the DTI 2 signal is transferred to the DTO/DTO 2 is by sampling the DTI 2 with XCK starting from the 19 th XCK after the init of the DCI command. MCC 11_20. TIF 1 4 2 3 5 G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 20

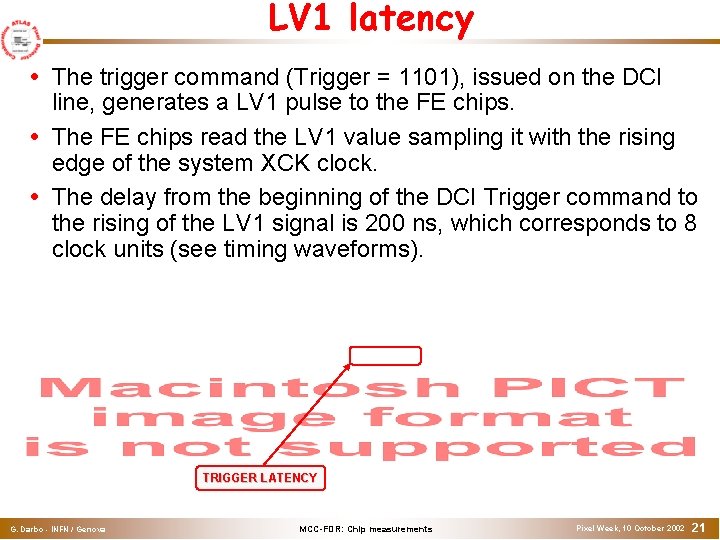

LV 1 latency The trigger command (Trigger = 1101), issued on the DCI line, generates a LV 1 pulse to the FE chips. The FE chips read the LV 1 value sampling it with the rising edge of the system XCK clock. The delay from the beginning of the DCI Trigger command to the rising of the LV 1 signal is 200 ns, which corresponds to 8 clock units (see timing waveforms). TRIGGER LATENCY G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 21

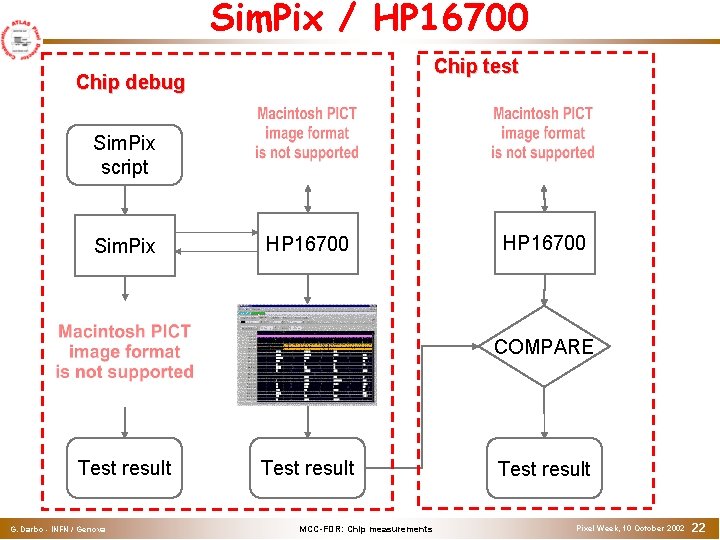

Sim. Pix / HP 16700 Chip test Chip debug Sim. Pix script Sim. Pix HP 16700 COMPARE Test result G. Darbo - INFN / Genova Test result MCC-FDR: Chip measurements Test result Pixel Week, 10 October 2002 22

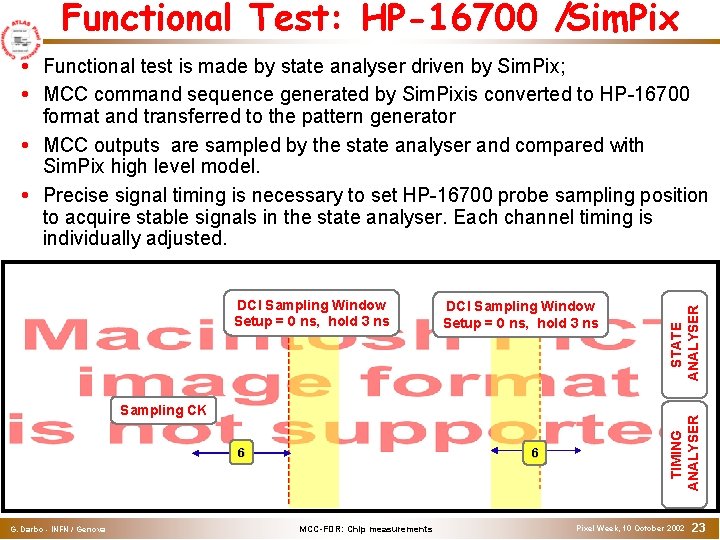

Functional Test: HP-16700 /Sim. Pix DCI Sampling Window Setup = 0 ns, hold 3 ns Sampling CK 6 G. Darbo - INFN / Genova 6 MCC-FDR: Chip measurements TIMING ANALYSER DCI Sampling Window Setup = 0 ns, hold 3 ns STATE ANALYSER Functional test is made by state analyser driven by Sim. Pix; MCC command sequence generated by Sim. Pixis converted to HP-16700 format and transferred to the pattern generator MCC outputs are sampled by the state analyser and compared with Sim. Pix high level model. Precise signal timing is necessary to set HP-16700 probe sampling position to acquire stable signals in the state analyser. Each channel timing is individually adjusted. Pixel Week, 10 October 2002 23

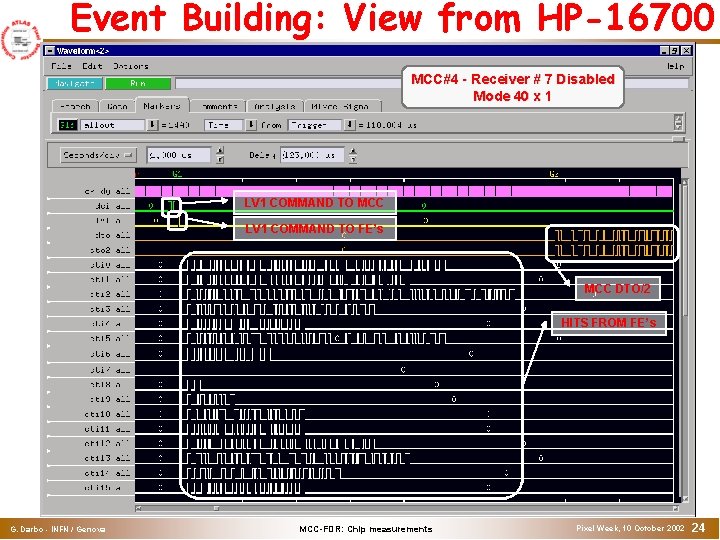

Event Building: View from HP-16700 MCC#4 - Receiver # 7 Disabled Mode 40 x 1 LV 1 COMMAND TO MCC LV 1 COMMAND TO FE’s MCC DTO/2 HITS FROM FE’s G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 24

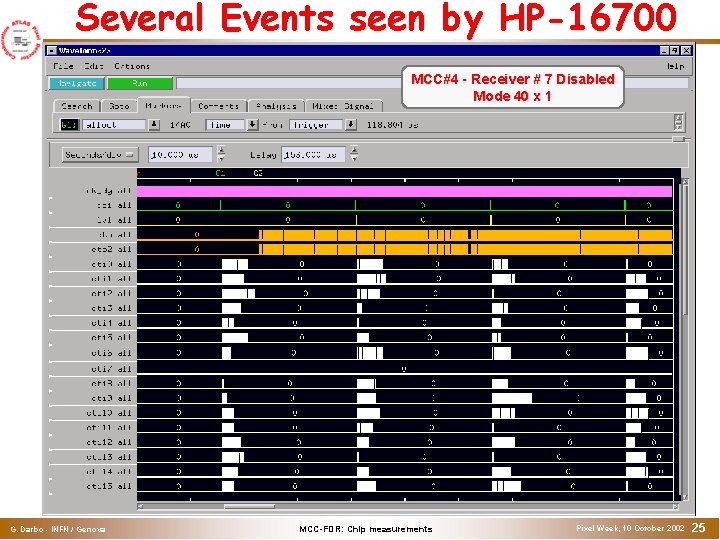

Several Events seen by HP-16700 MCC#4 - Receiver # 7 Disabled Mode 40 x 1 G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 25

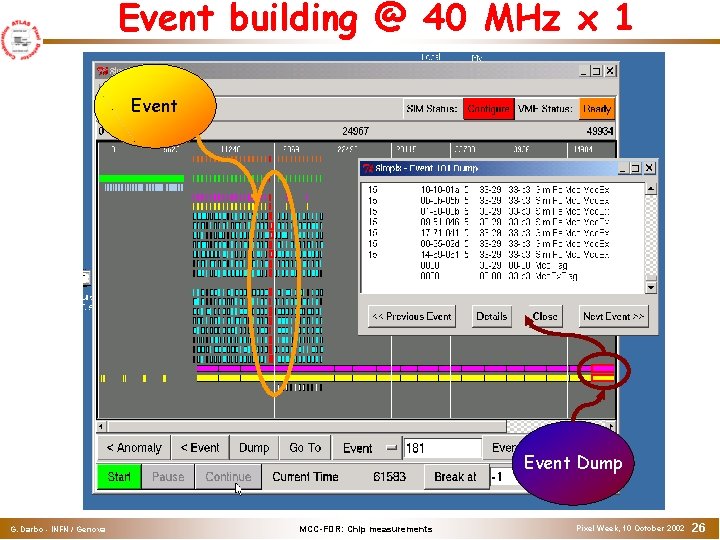

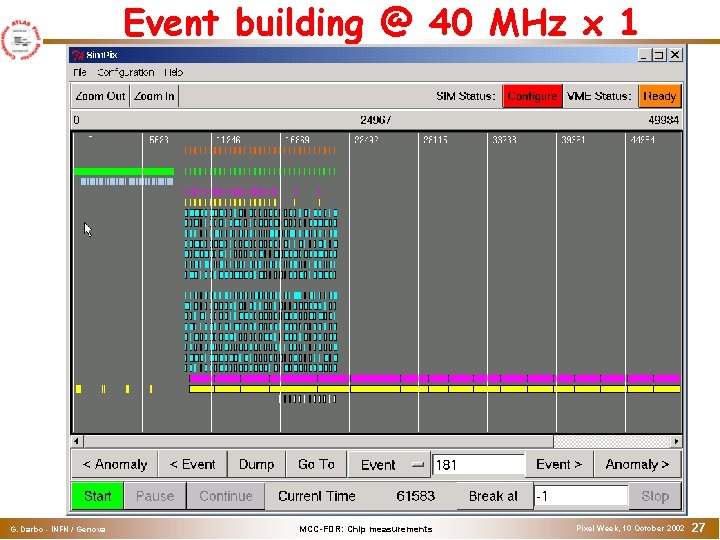

Event building @ 40 MHz x 1 Event Dump G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 26

Event building @ 40 MHz x 1 G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 27

Event Building @ 40 MHz x 2 Same input events G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 28

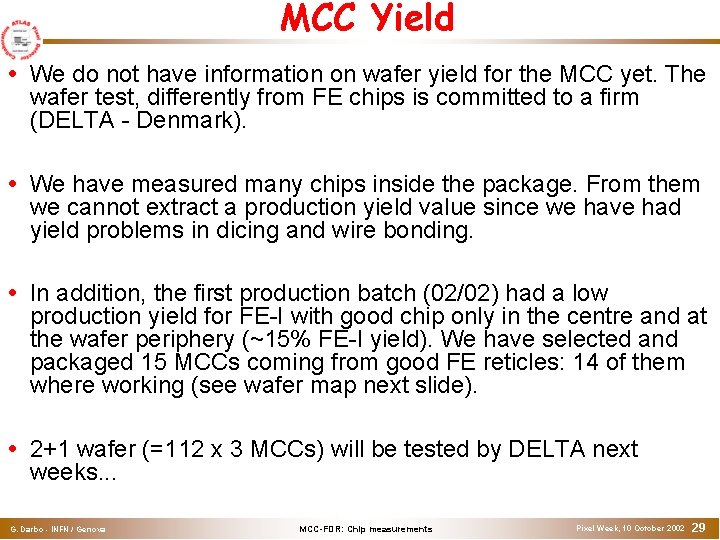

MCC Yield We do not have information on wafer yield for the MCC yet. The wafer test, differently from FE chips is committed to a firm (DELTA - Denmark). We have measured many chips inside the package. From them we cannot extract a production yield value since we have had yield problems in dicing and wire bonding. In addition, the first production batch (02/02) had a low production yield for FE-I with good chip only in the centre and at the wafer periphery (~15% FE-I yield). We have selected and packaged 15 MCCs coming from good FE reticles: 14 of them where working (see wafer map next slide). 2+1 wafer (=112 x 3 MCCs) will be tested by DELTA next weeks. . . G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 29

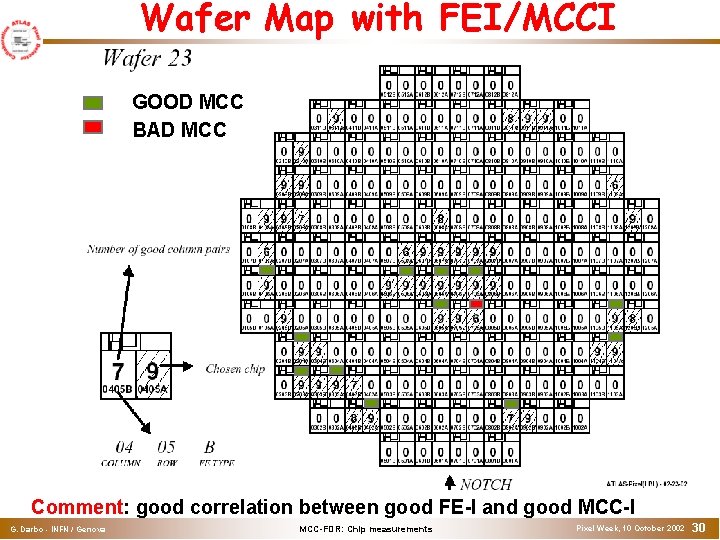

Wafer Map with FEI/MCCI GOOD MCC BAD MCC Comment: good correlation between good FE-I and good MCC-I G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 30

Wafer and Production test We decided to not test ourselves the chips on wafer, but to do it outside. We did the same for the MCC-AMS that were tested from AMS. Since IBM do not provide testing for they wafers we found DELTA as a possible solution. DELTA will do parametric and functional tests (see test flow). The functional test will be executed at nominal 40 MHz clock speed (we do not think it is necessary to use higher speed). It is our responsibility produce the whole set of vectors. Only 3 wafers from MCC-I 1 will be tested for the moment, while all production wafers will be tested by them. The 3 wafers are from the second IBM batch (6/02) which had high yield (70%÷ 80%) for FE-I. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 31

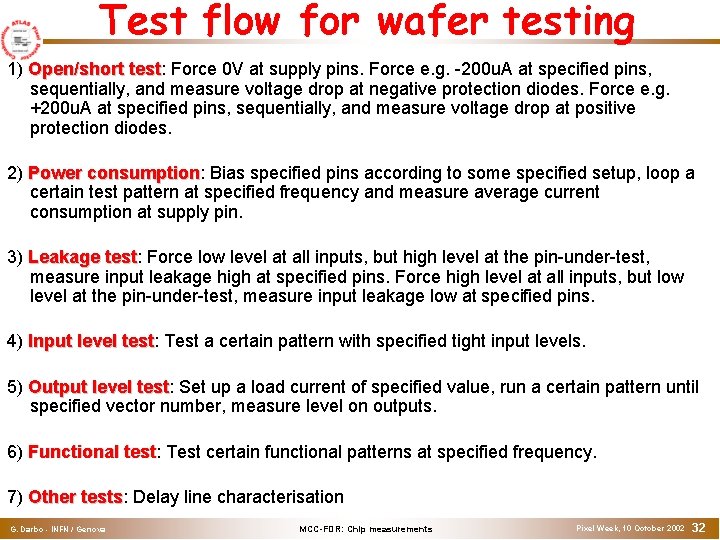

Test flow for wafer testing 1) Open/short test: test Force 0 V at supply pins. Force e. g. -200 u. A at specified pins, sequentially, and measure voltage drop at negative protection diodes. Force e. g. +200 u. A at specified pins, sequentially, and measure voltage drop at positive protection diodes. 2) Power consumption: consumption Bias specified pins according to some specified setup, loop a certain test pattern at specified frequency and measure average current consumption at supply pin. 3) Leakage test: test Force low level at all inputs, but high level at the pin-under-test, measure input leakage high at specified pins. Force high level at all inputs, but low level at the pin-under-test, measure input leakage low at specified pins. 4) Input level test: test Test a certain pattern with specified tight input levels. 5) Output level test: test Set up a load current of specified value, run a certain pattern until specified vector number, measure level on outputs. 6) Functional test: test Test certain functional patterns at specified frequency. 7) Other tests: tests Delay line characterisation G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 32

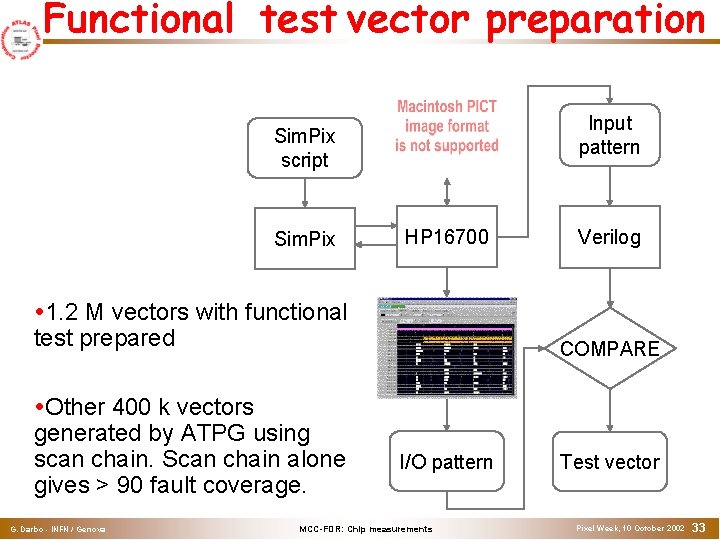

Functional test vector preparation Input pattern Sim. Pix script Sim. Pix HP 16700 1. 2 M vectors with functional test prepared Other 400 k vectors generated by ATPG using scan chain. Scan chain alone gives > 90 fault coverage. G. Darbo - INFN / Genova Verilog COMPARE I/O pattern MCC-FDR: Chip measurements Test vector Pixel Week, 10 October 2002 33

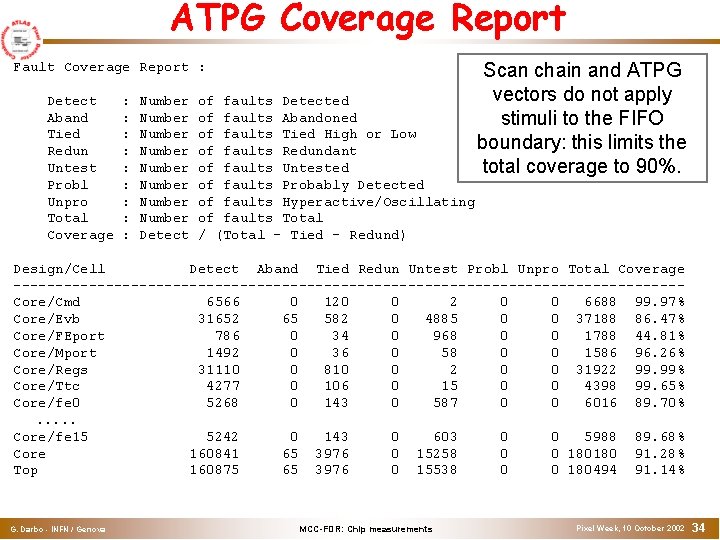

ATPG Coverage Report Fault Coverage Report : Detect Aband Tied Redun Untest Probl Unpro Total Coverage : : : : : Number Number Detect of faults Detected of faults Abandoned of faults Tied High or Low of faults Redundant of faults Untested of faults Probably Detected of faults Hyperactive/Oscillating of faults Total / (Total - Tied - Redund) Scan chain and ATPG vectors do not apply stimuli to the FIFO boundary: this limits the total coverage to 90%. Design/Cell Detect Aband Tied Redun Untest Probl Unpro Total Coverage ----------------------------------------Core/Cmd 6566 0 120 0 2 0 0 6688 99. 97% Core/Evb 31652 65 582 0 4885 0 0 37188 86. 47% Core/FEport 786 0 34 0 968 0 0 1788 44. 81% Core/Mport 1492 0 36 0 58 0 0 1586 96. 26% Core/Regs 31110 0 810 0 2 0 0 31922 99. 99% Core/Ttc 4277 0 106 0 15 0 0 4398 99. 65% Core/fe 0 5268 0 143 0 587 0 0 6016 89. 70%. . . Core/fe 15 5242 0 143 0 603 0 0 5988 89. 68% Core 160841 65 3976 0 15258 0 0 180180 91. 28% Top 160875 65 3976 0 15538 0 0 180494 91. 14% G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 34

Irradiation Test Rad-hard behaviour of the MCC-I has been tested at PS last spring. Seven MCC powered (3 at 1. 8 V / 4 at 2. 2 V) and operated: one chip in turn was continuously R/W during spill, while the other 6 were loaded before spill and read back after. MCCex (see Paolo’s talk) with additional hardware extensions used for the test. Single Event Upset (SEU) results are reported by Guido. The 7 MCC have been characterised again after 73 Mrad dose in the lab (see next slide) G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 35

Post Irradiation Characterisation The 7 MCC irradiated at PS (7/02) have been recharacterised: Chips have slightly increased the IDD(see table), while the maximum operating frequency looks pretty the same as not irradiated parts. Only one chip is no more working, probably due to destroyed wirebonds (the cover lid was removed and substituted by a kapton scotch). All of them worked for the whole PS run. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 36

- Slides: 36