ChihHung Wang Chapter 1 Background Part1 Leland L

Chih-Hung Wang Chapter 1: Background (Part-1) 參考書目 Leland L. Beck, System Software: An Introduction to Systems Programming (3 rd), Addison-Wesley, 1997. 1

Outline of Chapter 1 § System Software and Machine Architecture § The Simplified Instructional Computer (SIC) § Traditional (CISC) Machines § Complex Instruction Set Computers § RISC Machines § Reduced Instruction Set Computers 2

System Software vs. Machine Architecture § Machine dependent § The most important characteristic in which most system software differ from application software § e. g. assembler translate mnemonic instructions into machine code § e. g. compilers must generate machine language code § Machine architecture differs in: § Machine code § Instruction formats § Addressing mode § Registers § Machine independent § There aspects of system software that do not directly depend upon the type of computing system § e. g. general design and logic of an assembler § e. g. code optimization techniques 3

System Software and Architecture § System software will be discussed: § The basic functions § Machine-dependent functions § Machine-independent functions § Design options (single-pass vs. multi-pass) § Examples of implementations 4

The Simplified Instructional Computer (SIC) § SIC is a hypothetical computer that includes the hardware features most often found on real machines. § Why the simplified instructional computer § To avoid various unique features and idiosyncrasies of a particular machine. § To focus on central, fundamental, and commonly encountered features and concepts. § Two versions of SIC § standard model (SIC) § extension version (SIC/XE) § Upward compatible § Programs for SIC can run on SIC/XE 5

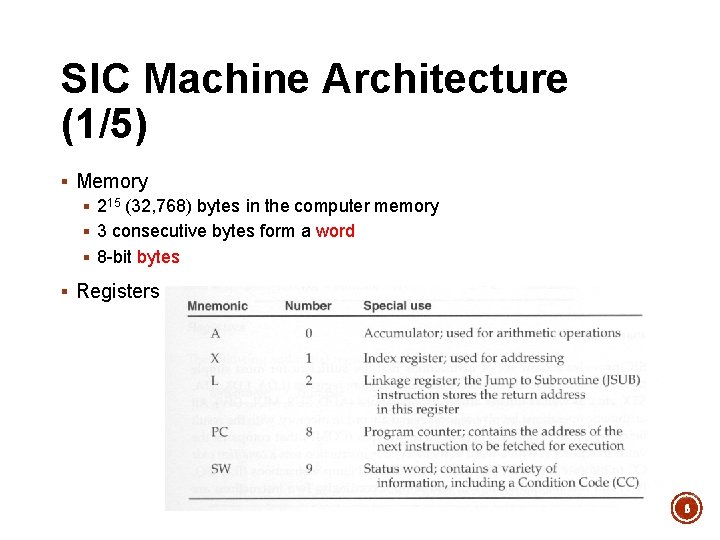

SIC Machine Architecture (1/5) § Memory § 215 (32, 768) bytes in the computer memory § 3 consecutive bytes form a word § 8 -bit bytes § Registers 6

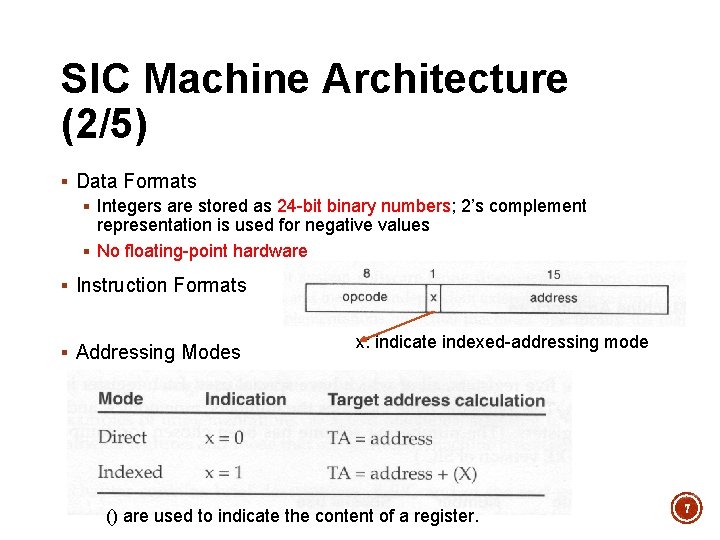

SIC Machine Architecture (2/5) § Data Formats § Integers are stored as 24 -bit binary numbers; 2’s complement representation is used for negative values § No floating-point hardware § Instruction Formats § Addressing Modes x: indicate indexed-addressing mode () are used to indicate the content of a register. 7

SIC Machine Architecture (3/5) § Instruction Set § load and store: LDA, LDX, STA, STX, etc. § integer arithmetic operations: ADD, SUB, MUL, DIV, etc. § All arithmetic operations involve register A and a word in memory, with the result being left in the register § comparison: COMP § COMP compares the value in register A with a word in memory, this instruction sets a condition code CC to indicate the result 8

SIC Machine Architecture (4/5) § Instruction Set § conditional jump instructions: JLT, JEQ, JGT § these instructions test the setting of CC and jump accordingly § subroutine linkage: JSUB, RSUB § JSUB jumps to the subroutine, placing the return address in register L § RSUB returns by jumping to the address contained in register L 9

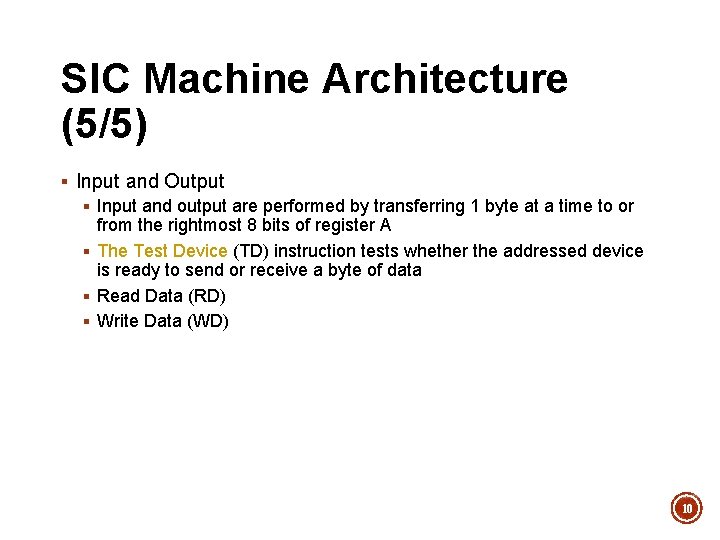

SIC Machine Architecture (5/5) § Input and Output § Input and output are performed by transferring 1 byte at a time to or from the rightmost 8 bits of register A § The Test Device (TD) instruction tests whether the addressed device is ready to send or receive a byte of data § Read Data (RD) § Write Data (WD) 10

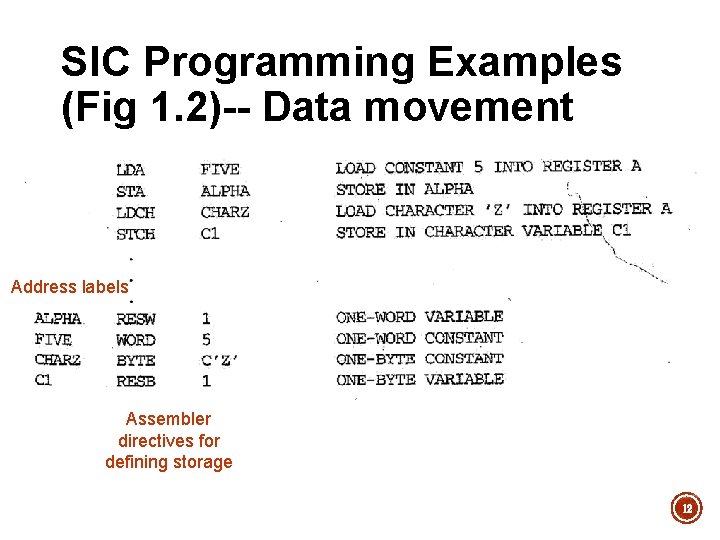

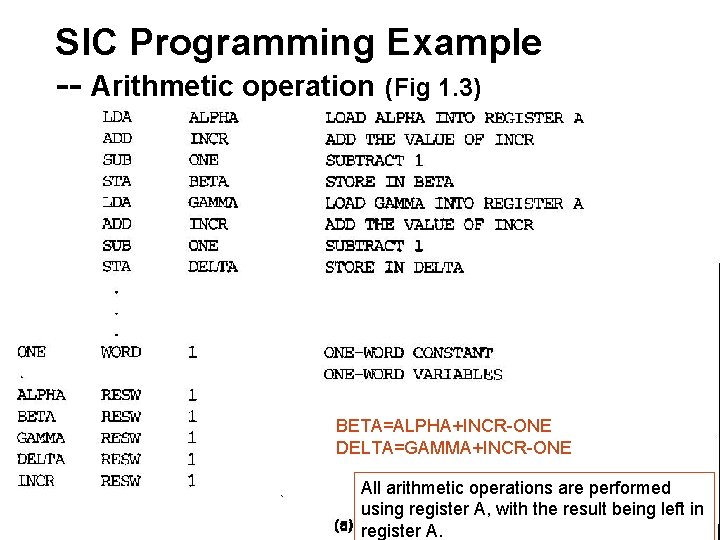

SIC Programming Examples § Data movement Fig. 1. 2 § Arithmetic operation Fig. 1. 3 § Looping and indexing Fig. 1. 4, Fig. 1. 5 § Input and output Fig. 1. 6 § Subroutine call Fig. 1. 7 11

SIC Programming Examples (Fig 1. 2)-- Data movement Address labels Assembler directives for defining storage 12

SIC Programming Example -- Arithmetic operation (Fig 1. 3) BETA=ALPHA+INCR-ONE DELTA=GAMMA+INCR-ONE All arithmetic operations are performed using register A, with the result being left 13 in register A.

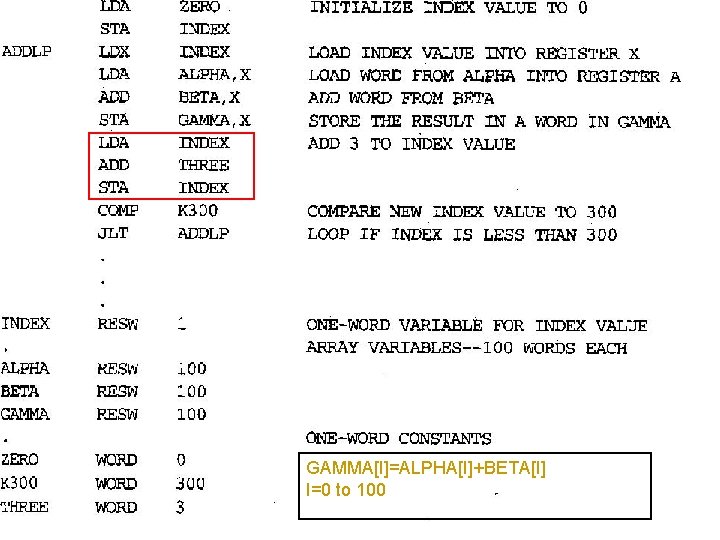

SIC Programming Example -- Looping and indexing (Fig. 1. 4) 14

SIC Programming Example -- Looping and indexing (Fig. 1. 5) § Arithmetic operations are performed using register A, with the result being left in register A § Looping (TIX) § (X)=(X)+1 § compare with operand § set CC GAMMA[I]=ALPHA[I]+BETA[I] I=0 to 100 15

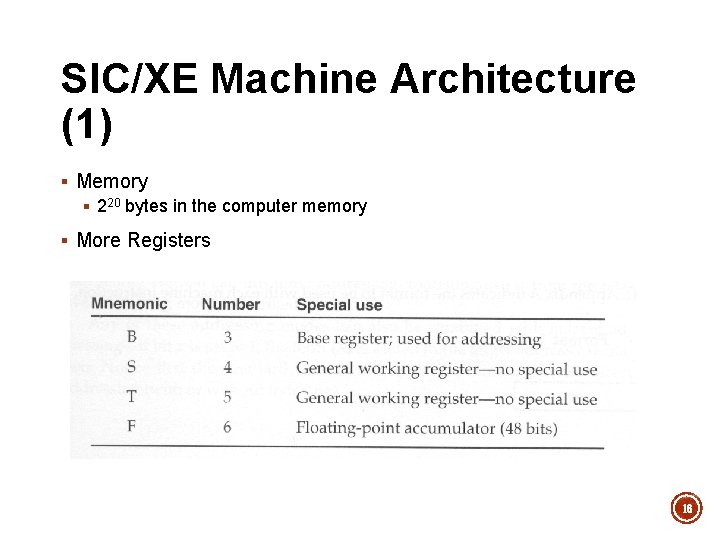

SIC/XE Machine Architecture (1) § Memory § 220 bytes in the computer memory § More Registers 16

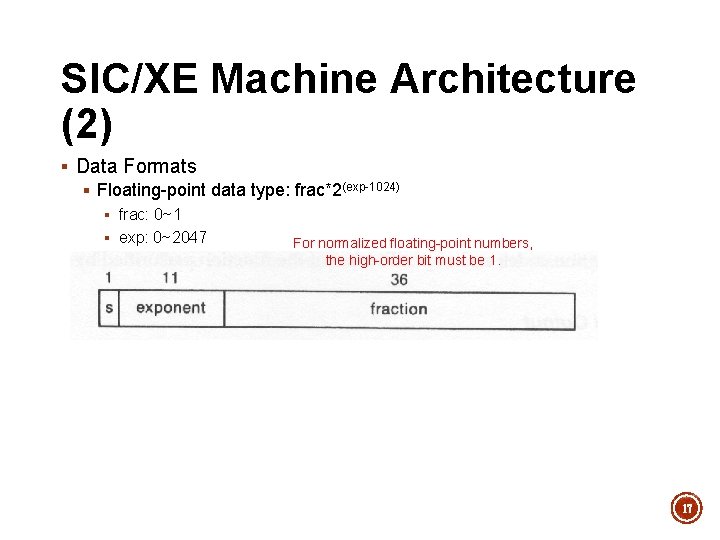

SIC/XE Machine Architecture (2) § Data Formats § Floating-point data type: frac*2(exp-1024) § frac: 0~1 § exp: 0~2047 For normalized floating-point numbers, the high-order bit must be 1. 17

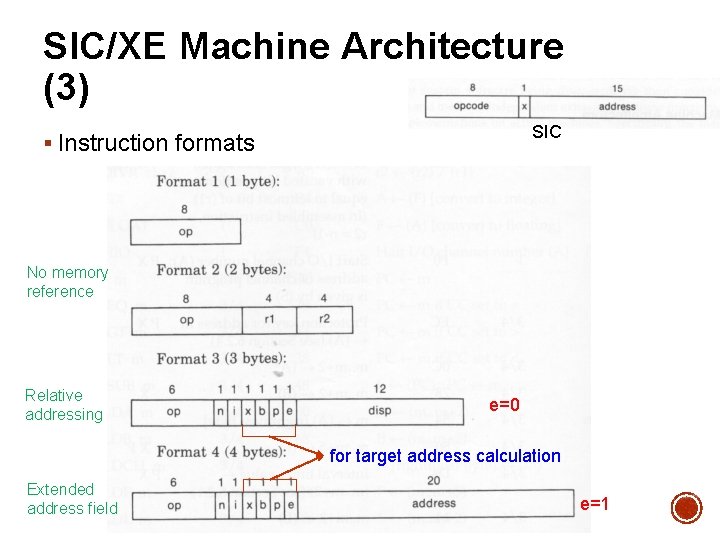

SIC/XE Machine Architecture (3) SIC § Instruction formats No memory reference Relative addressing e=0 for target address calculation Extended address field e=1 18

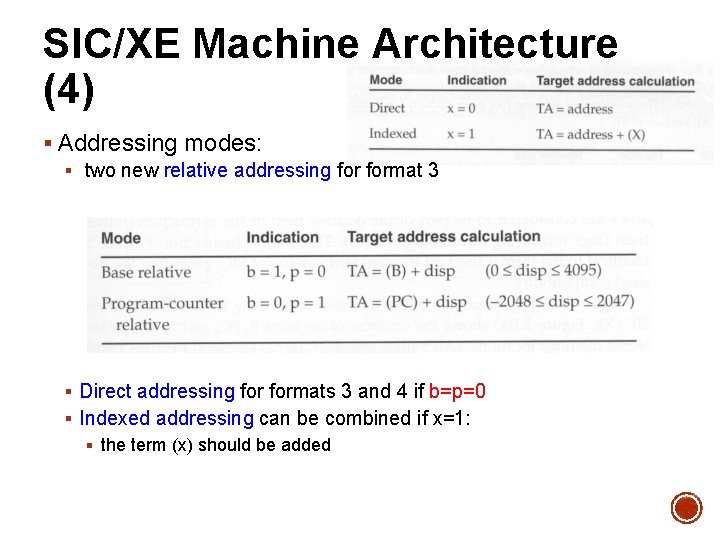

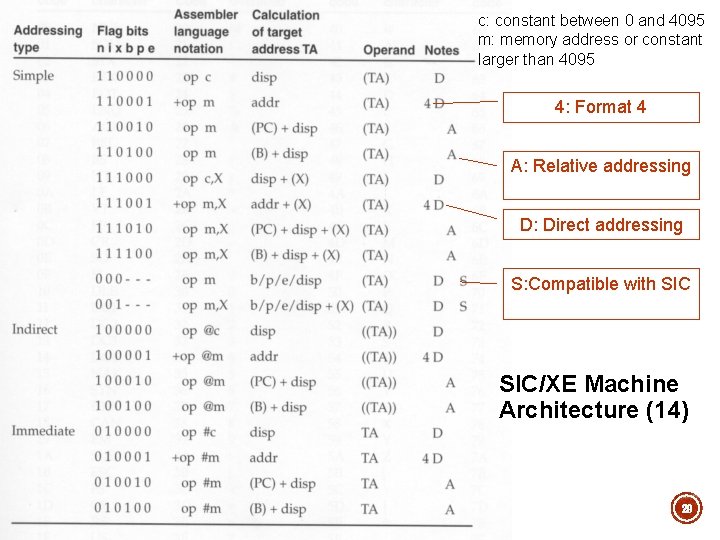

SIC/XE Machine Architecture (4) § Addressing modes: § two new relative addressing format 3 § Direct addressing formats 3 and 4 if b=p=0 § Indexed addressing can be combined if x=1: § the term (x) should be added 19

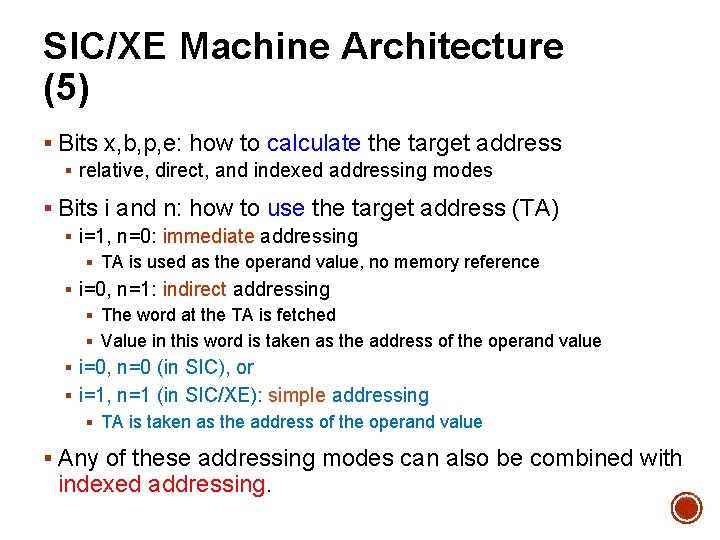

SIC/XE Machine Architecture (5) § Bits x, b, p, e: how to calculate the target address § relative, direct, and indexed addressing modes § Bits i and n: how to use the target address (TA) § i=1, n=0: immediate addressing § TA is used as the operand value, no memory reference § i=0, n=1: indirect addressing § The word at the TA is fetched § Value in this word is taken as the address of the operand value § i=0, n=0 (in SIC), or § i=1, n=1 (in SIC/XE): simple addressing § TA is taken as the address of the operand value § Any of these addressing modes can also be combined with indexed addressing. 20

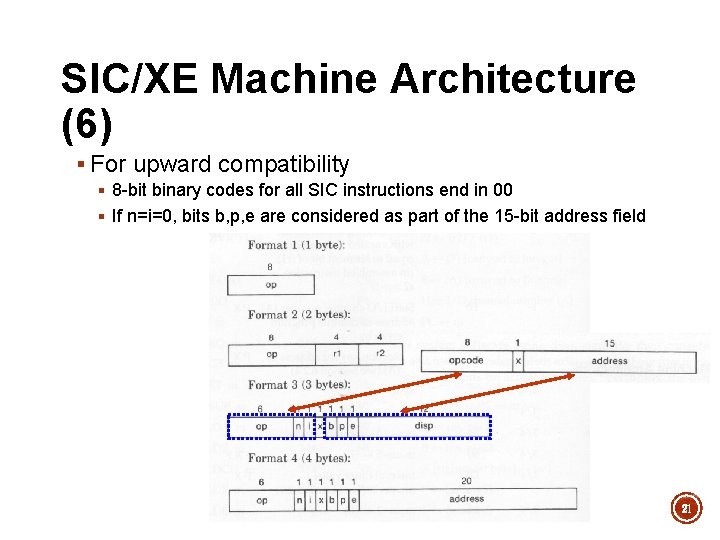

SIC/XE Machine Architecture (6) § For upward compatibility § 8 -bit binary codes for all SIC instructions end in 00 § If n=i=0, bits b, p, e are considered as part of the 15 -bit address field 21

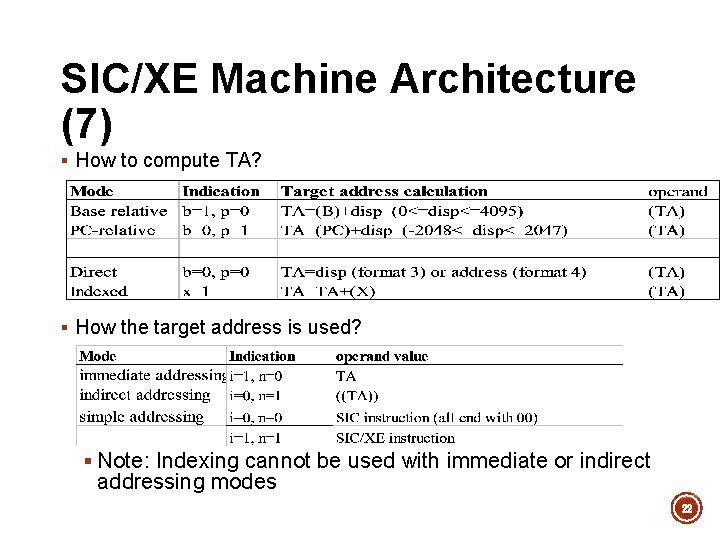

SIC/XE Machine Architecture (7) § How to compute TA? § How the target address is used? § Note: Indexing cannot be used with immediate or indirect addressing modes 22

SIC/XE Machine Architecture (8) § Instruction Set § new registers: LDB, STB, etc. § floating-point arithmetic: ADDF, SUBF, MULF, DIVF § register move: RMO § register-register arithmetic: ADDR, SUBR, MULR, DIVR § supervisor call: SVC § generates an interrupt for OS (Chap 6) § Input/Output § SIO, TIO, HIO: start, test, halt the operation of I/O device (Chap 6) 23

SIC/XE Machine Architecture (9) § Example. RSUB § Example. COMPR A, S § Example. LDA #3 (Format 3) 24

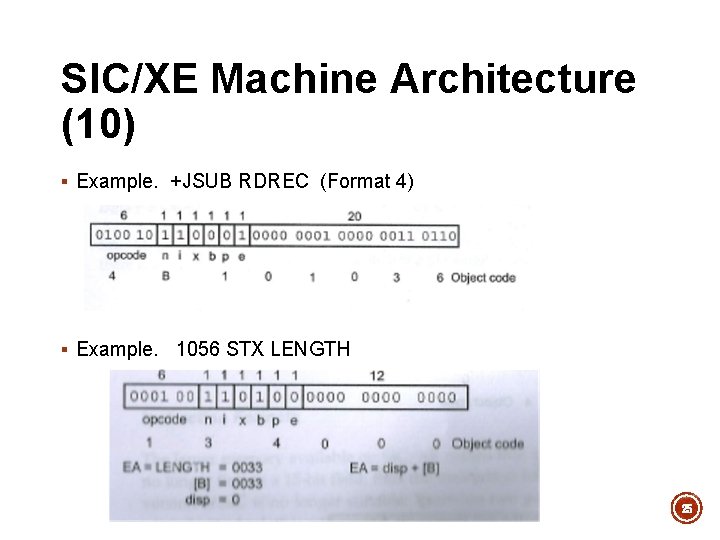

SIC/XE Machine Architecture (10) § Example. +JSUB RDREC (Format 4) § Example. 1056 STX LENGTH 25

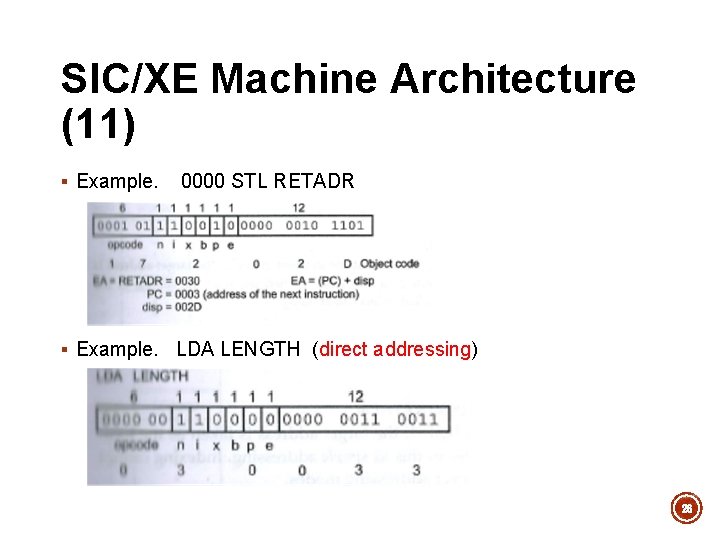

SIC/XE Machine Architecture (11) § Example. 0000 STL RETADR § Example. LDA LENGTH (direct addressing) 26

![SIC/XE Machine Architecture (12) § Example. STCH BUFFER, X [B]=0033 disp=3 § Example. LDA SIC/XE Machine Architecture (12) § Example. STCH BUFFER, X [B]=0033 disp=3 § Example. LDA](http://slidetodoc.com/presentation_image_h/b6cb71586f50222ea0702cea1491f997/image-27.jpg)

SIC/XE Machine Architecture (12) § Example. STCH BUFFER, X [B]=0033 disp=3 § Example. LDA #9 27

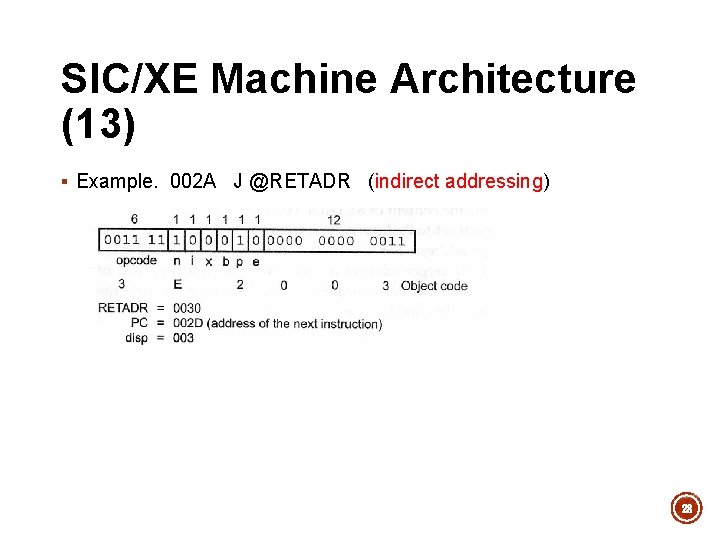

SIC/XE Machine Architecture (13) § Example. 002 A J @RETADR (indirect addressing) 28

c: constant between 0 and 4095 m: memory address or constant larger than 4095 4: Format 4 A: Relative addressing D: Direct addressing S: Compatible with SIC/XE Machine Architecture (14) 29

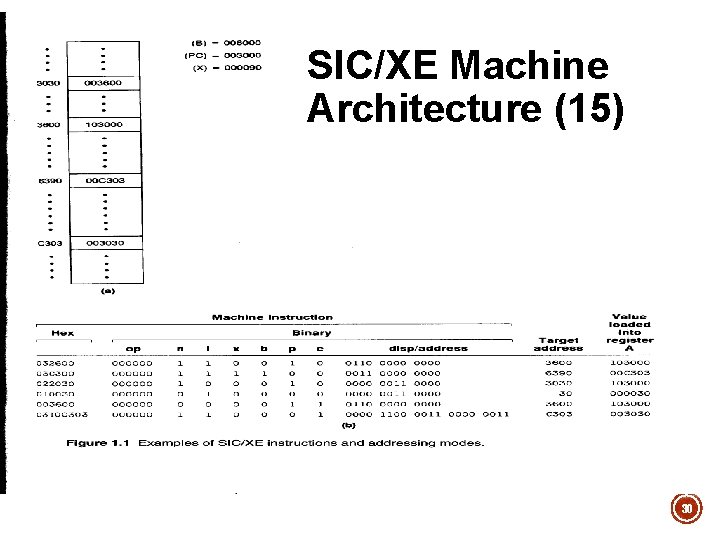

SIC/XE Machine Architecture (15) 30

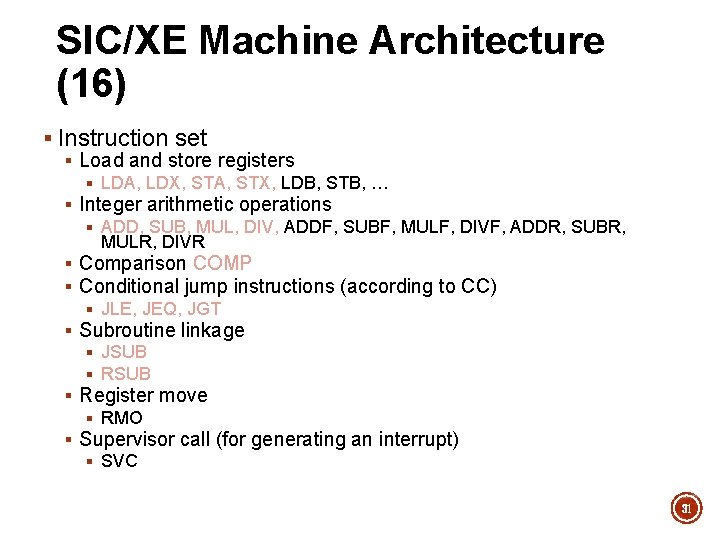

SIC/XE Machine Architecture (16) § Instruction set § Load and store registers § LDA, LDX, STA, STX, LDB, STB, … § Integer arithmetic operations § ADD, SUB, MUL, DIV, ADDF, SUBF, MULF, DIVF, ADDR, SUBR, MULR, DIVR § Comparison COMP § Conditional jump instructions (according to CC) § JLE, JEQ, JGT § Subroutine linkage § JSUB § Register move § RMO § Supervisor call (for generating an interrupt) § SVC 31

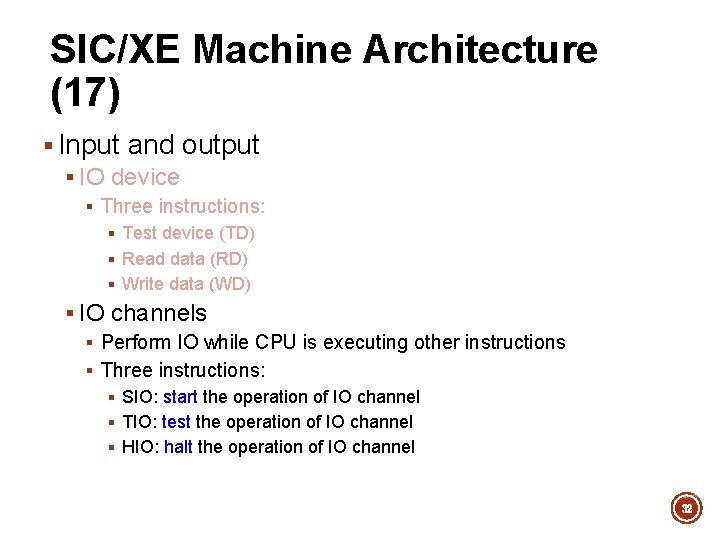

SIC/XE Machine Architecture (17) § Input and output § IO device § Three instructions: § Test device (TD) § Read data (RD) § Write data (WD) § IO channels § Perform IO while CPU is executing other instructions § Three instructions: § SIO: start the operation of IO channel § TIO: test the operation of IO channel § HIO: halt the operation of IO channel 32

SIC/XE Machine Architecture (18): I/O Mechanisms § Polling I/O § Interrupt-Driven I/O § DMA (Direct Memory Access) I/O 33

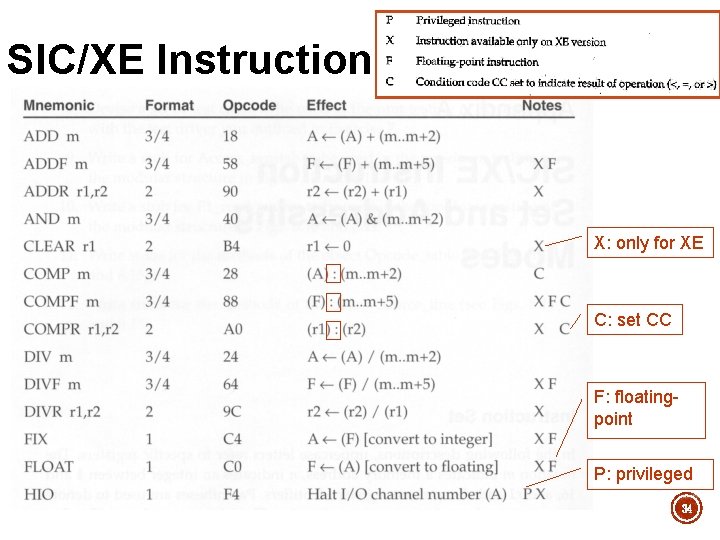

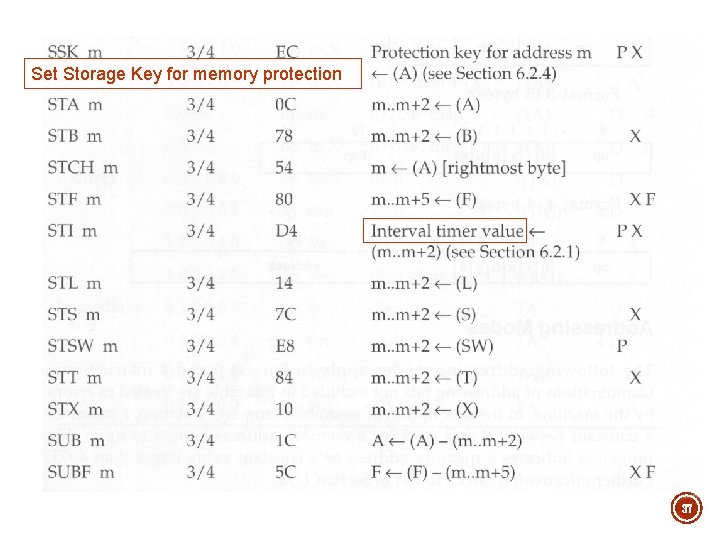

SIC/XE Instruction Set X: only for XE C: set CC F: floatingpoint P: privileged 34

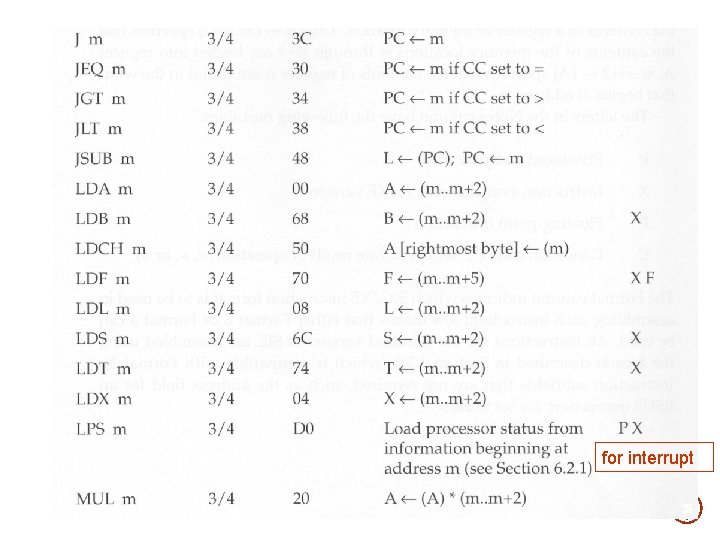

for interrupt 35

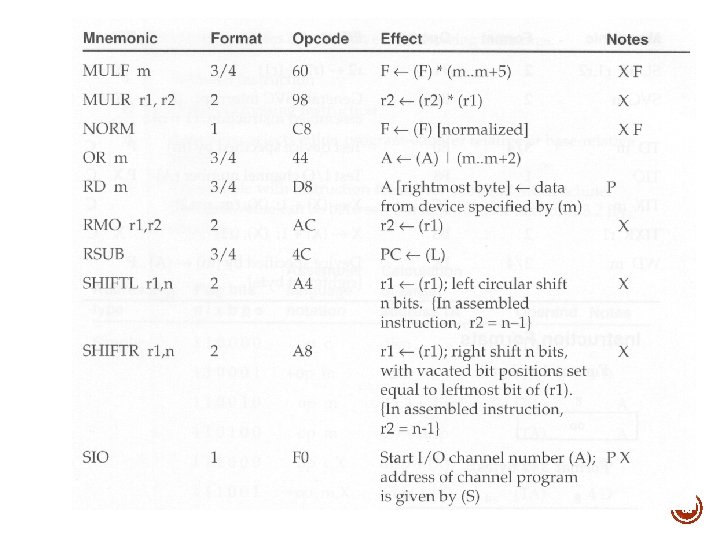

36

Set Storage Key for memory protection 37

38

SIC/XE Programming Example (1) 39

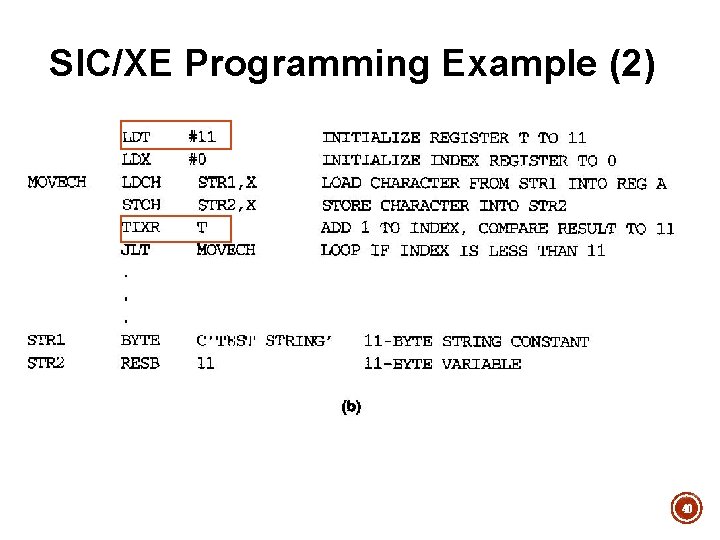

SIC/XE Programming Example (2) 40

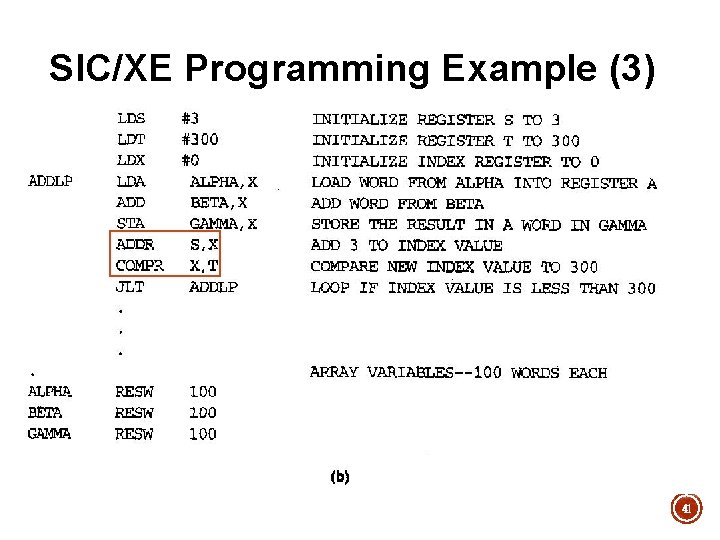

SIC/XE Programming Example (3) 41

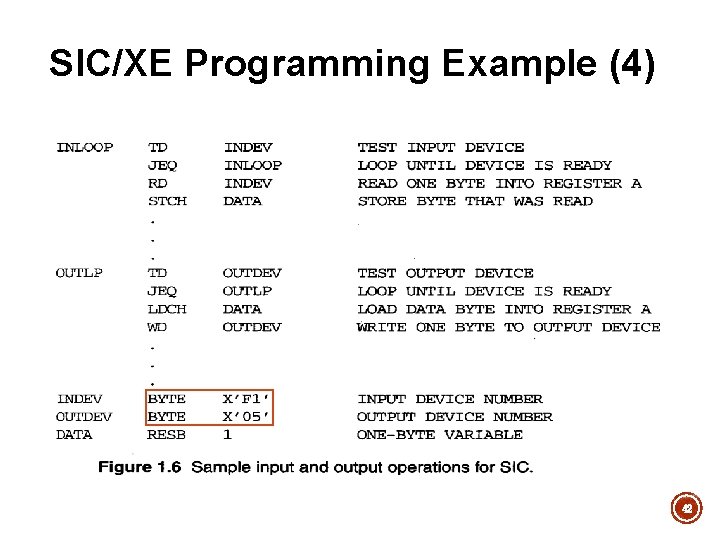

SIC/XE Programming Example (4) 42

Real Machine: two Categories § Complex Instruction Set Computers (CISC) § Relative large and complicated instruction set, more instruction formats, instruction lengths, and addressing modes § Hardware implementation is complex § Examples: § VAX § Intel x 86 § Reduced Instruction Set Computers (RISC) § Simplified design, faster and less expensive processor development, greater reliability, faster instruction execution times § Examples: § Sun SPARC § Power. PC 43

VAX Architecture § Memory: 232 bytes in virtual address space § consists of 8 -bit bytes: § word: 2 bytes § longword: 4 bytes § quadword: 8 bytes § octaword: 16 bytes § can be divided into § System space (OS and shared space) § Process space (defined separately for each process) 44

VAX Architecture § 32 -bit registers § 16 general-purpose registers § R 0 -R 11: no special functions § AP: argument pointer (address of arguments when making a procedure call) § FP: frame pointer (address of the stack frame when making a procedure call) § SP: stack pointer (top of stack in program’s process space) § PC: program counter § PSL: processor status longword § Control registers to support OS 45

VAX Architecture § Data formats § Characters: 8 -bit ASCII codes § Integers: § 2, 4, 8, 16 -byte binary numbers § 2’s complement for negative values § Floating-point numbers: § 4 different floating-point data ranging in length from 4 to 16 bytes § Packed decimal data format § Each byte represents two decimal digits § Numeric format § To represent numeric values with one digit per byte § Queues and variable-length bit strings 46

VAX Architecture § Instruction formats § Variable-length instruction format § Each instruction consists of § OP code (1 or 2 bytes) § Up to 6 operand specifiers (depends on instruction) 47

VAX Architecture § Addressing modes § Register mode § Register deferred mode § Autoincrement and autodecrement modes § Base relative modes § PC relative modes § Index modes § Indirect modes § Immediate mode § etc 48

VAX Architecture § Instruction set § Mnemonics format (e. g. , ADDW 2, MULL 3) § Prefix: type of operation § Suffix: data type of the operands § Modifier: number of operands involved § In addition to computation, data movement and conversion, comparison, branching, VAX provides instructions that are hardware realizations of frequently occurring sequences of codes § Load and store multiple registers § Manipulate queues and variable-length bit fields § Powerful instructions for calling and returning from procedure 49

VAX Architecture § Input and output § Each I/O device has a set of registers, which are assigned locations in the physical address space, called I/O space. § Association of these registers with addresses in I/O space is handled by memory management routines. § Device driver read/write values into these registers. § Software routines read/write values in I/O space using standard instructions. 50

Ultra. SPARC Architecture § Memory: 264 bytes in virtual address space § consists of 8 -bit bytes: § halfword: 2 bytes § word: 4 bytes § doubleword: 8 bytes § can be divided into pages § Virtual address is automatically translated into a physical address by the Ultra. SPARC Memory Management Unit. 51

Ultra. SPARC Architecture § A large register file (>100 general-purpose registers) § 32 bits for original SPARC, 64 bits for Ultra. SPARC § Each procedure can access only 32 registers § 8 global registers § 24 registers in overlapped window § Floating-point computations are performed using a special floating-point unit (FPU). § Program counter PC 52

Ultra. SPARC Architecture § Data formats § Characters: 8 -bit ASCII codes § Integers: § 1, 2, 4, 8 -byte binary numbers § 2’s complement for negative values § Big- and little-endian and byte ordering § Floating-point numbers: § Single-precision: 32 bits § Double-precision: 64 bits § Quad-precision: 80 bits 53

Ultra. SPARC Architecture § Instruction formats § Fix-length instruction format (32 bits long) § Can speed the process of instruction fetching and decoding § 3 basic instruction formats § Call instruction § Branch instruction § Register loads and stores, and three-operands arithmetic operations § Each instruction consists of § First 2 bits: identify formats § OP code § Operands 54

Ultra. SPARC Architecture § Addressing modes § Immediate mode § Register direct mode § PC relative mode only for branch instructions § Register indirect with displacement § Register indirect indexed 55

Ultra. SPARC Architecture § Instruction set (<100 instructions) § Register-to-register instructions § Load and store instructions (only instructions that access memory) § Instruction execution is pipelined. § Branch instructions are delayed branches § Instructions immediately following the branch instruction is actually executed before the branch is taken. 56

Ultra. SPARC Architecture § Input and output § A range of memory locations is logically replaced by device registers. § Device driver read/write values into these registers. § Software routines read/write values in this area using standard instructions. 57

- Slides: 57