Characterization of silicon interfaces obtained by CMOS compatible

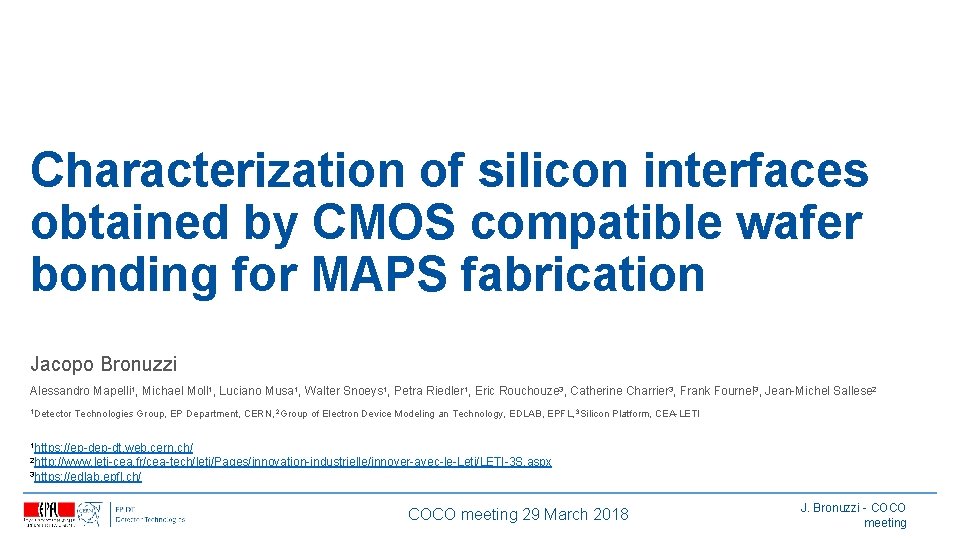

Characterization of silicon interfaces obtained by CMOS compatible wafer bonding for MAPS fabrication Jacopo Bronuzzi Alessandro Mapelli 1, Michael Moll 1, Luciano Musa 1, Walter Snoeys 1, Petra Riedler 1, Eric Rouchouze 3, Catherine Charrier 3, Frank Fournel 3, Jean-Michel Sallese 2 1 Detector Technologies Group, EP Department, CERN, 2 Group of Electron Device Modeling an Technology, EDLAB, EPFL, 3 Silicon Platform, CEA-LETI 1 https: //ep-dt. web. cern. ch/ 2 http: //www. leti-cea. fr/cea-tech/leti/Pages/innovation-industrielle/innover-avec-le-Leti/LETI-3 S. aspx 3 https: //edlab. epfl. ch/ COCO meeting 29 March 2018 J. Bronuzzi - COCO meeting

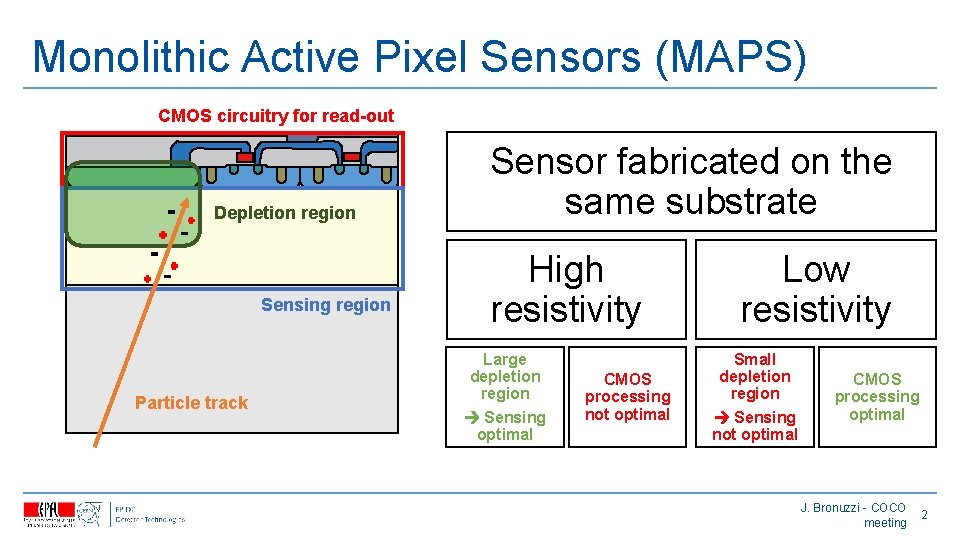

Monolithic Active Pixel Sensors (MAPS) CMOS circuitry for read-out Depletion region Sensing region Particle track Sensor fabricated on the same substrate High resistivity Large depletion region Sensing optimal CMOS processing not optimal Low resistivity Small depletion region Sensing not optimal CMOS processing optimal J. Bronuzzi - COCO meeting 2

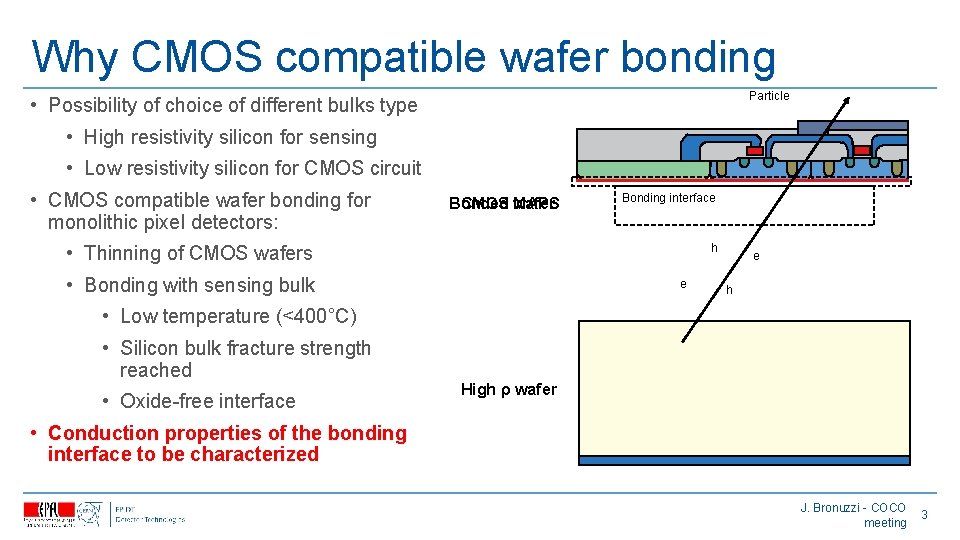

Why CMOS compatible wafer bonding Particle • Possibility of choice of different bulks type • High resistivity silicon for sensing • Low resistivity silicon for CMOS circuit • CMOS compatible wafer bonding for monolithic pixel detectors: Bonded MAPS CMOS wafer Bonding interface h • Thinning of CMOS wafers • Bonding with sensing bulk e e h • Low temperature (<400°C) • Silicon bulk fracture strength reached • Oxide-free interface High ρ wafer • Conduction properties of the bonding interface to be characterized J. Bronuzzi - COCO meeting 3

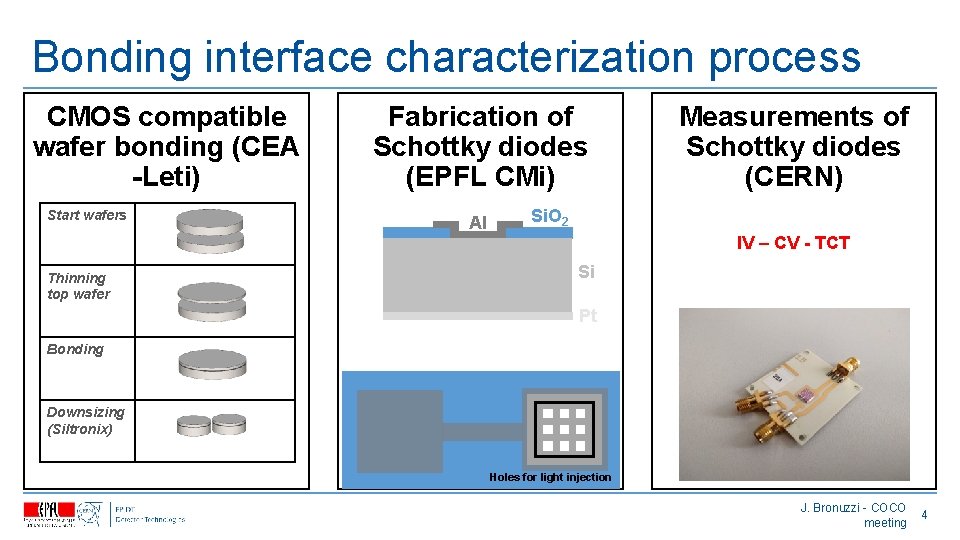

Bonding interface characterization process CMOS compatible wafer bonding (CEA -Leti) Start wafers Thinning top wafer Fabrication of Schottky diodes (EPFL CMi) Al Measurements of Schottky diodes (CERN) Si. O 2 IV – CV - TCT Si Pt Bonding Downsizing (Siltronix) Holes for light injection J. Bronuzzi - COCO meeting 4

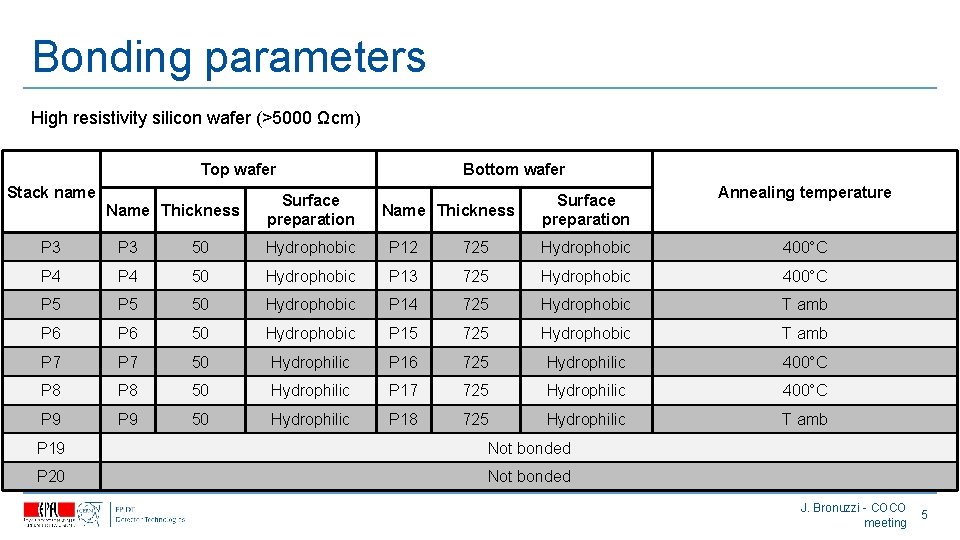

Bonding parameters High resistivity silicon wafer (>5000 Ωcm) Top wafer Stack name Name Thickness Surface preparation Bottom wafer Name Thickness Surface preparation Annealing temperature P 3 50 Hydrophobic P 12 725 Hydrophobic 400°C P 4 50 Hydrophobic P 13 725 Hydrophobic 400°C P 5 50 Hydrophobic P 14 725 Hydrophobic T amb P 6 50 Hydrophobic P 15 725 Hydrophobic T amb P 7 50 Hydrophilic P 16 725 Hydrophilic 400°C P 8 50 Hydrophilic P 17 725 Hydrophilic 400°C P 9 50 Hydrophilic P 18 725 Hydrophilic T amb P 19 Not bonded P 20 Not bonded J. Bronuzzi - COCO meeting 5

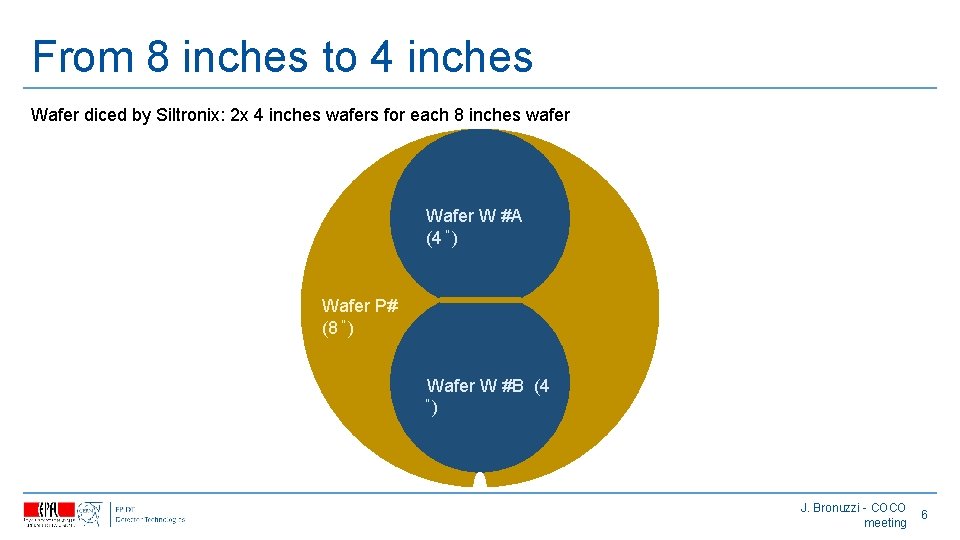

From 8 inches to 4 inches Wafer diced by Siltronix: 2 x 4 inches wafers for each 8 inches wafer W #A (4 ) Wafer P# (8 ) Wafer W #B (4 ) J. Bronuzzi - COCO meeting 6

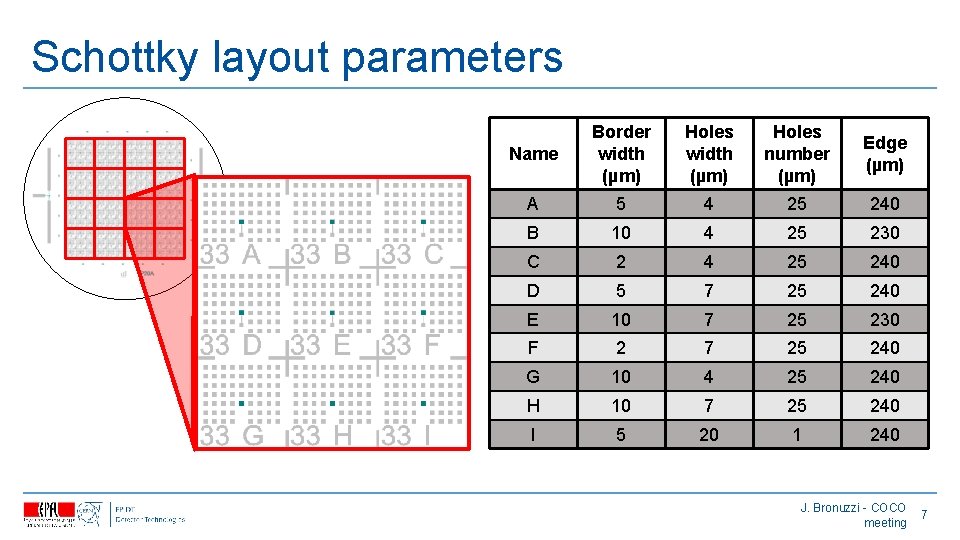

Schottky layout parameters Name Border width (µm) Holes number (µm) Edge (µm) A 5 4 25 240 B 10 4 25 230 C 2 4 25 240 D 5 7 25 240 E 10 7 25 230 F 2 7 25 240 G 10 4 25 240 H 10 7 25 240 I 5 20 1 240 J. Bronuzzi - COCO meeting 7

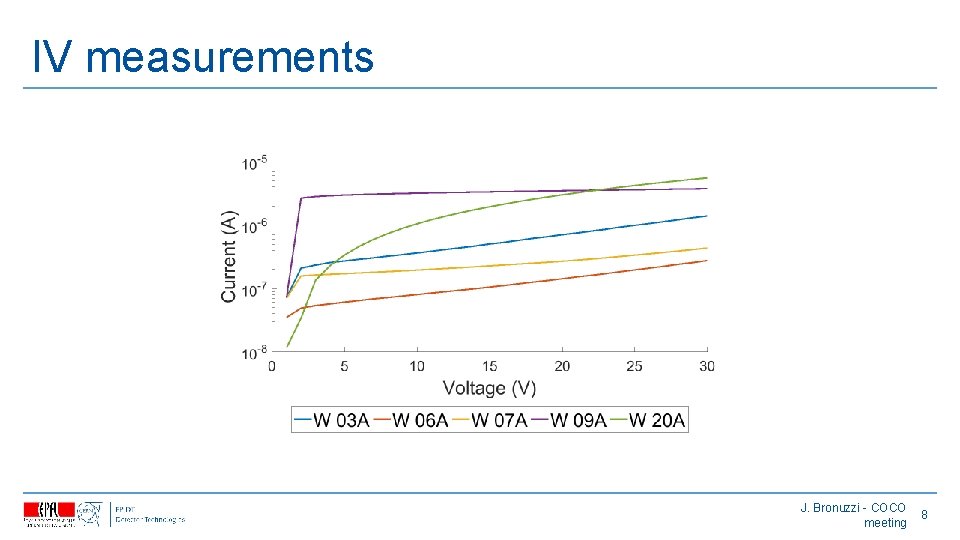

IV measurements J. Bronuzzi - COCO meeting 8

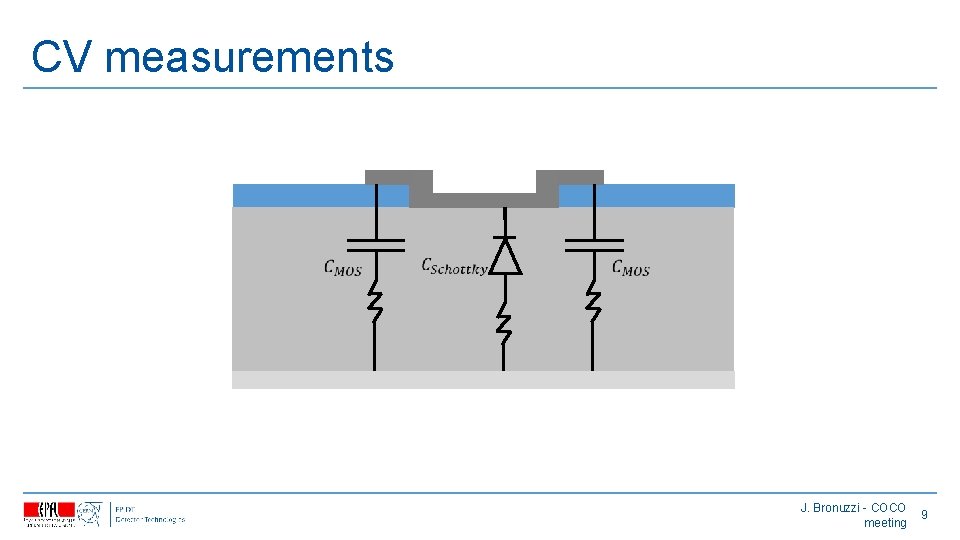

CV measurements J. Bronuzzi - COCO meeting 9

MOS contribution to CV To eliminate MOS contribution from Schottky measurements, an indepentent MOS has been measured. Therefore: Parasitic MOS Schottky diode J. Bronuzzi - COCO meeting 10

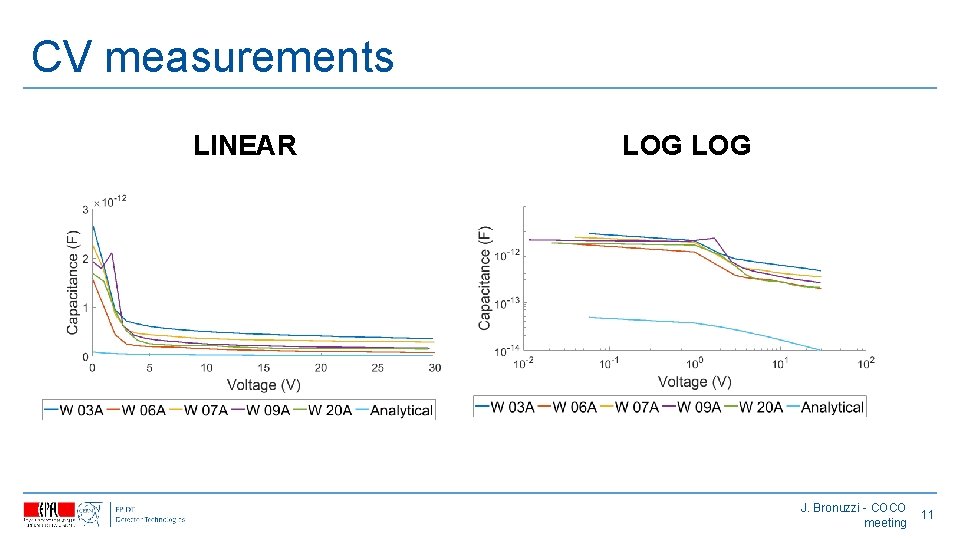

CV measurements LINEAR LOG J. Bronuzzi - COCO meeting 11

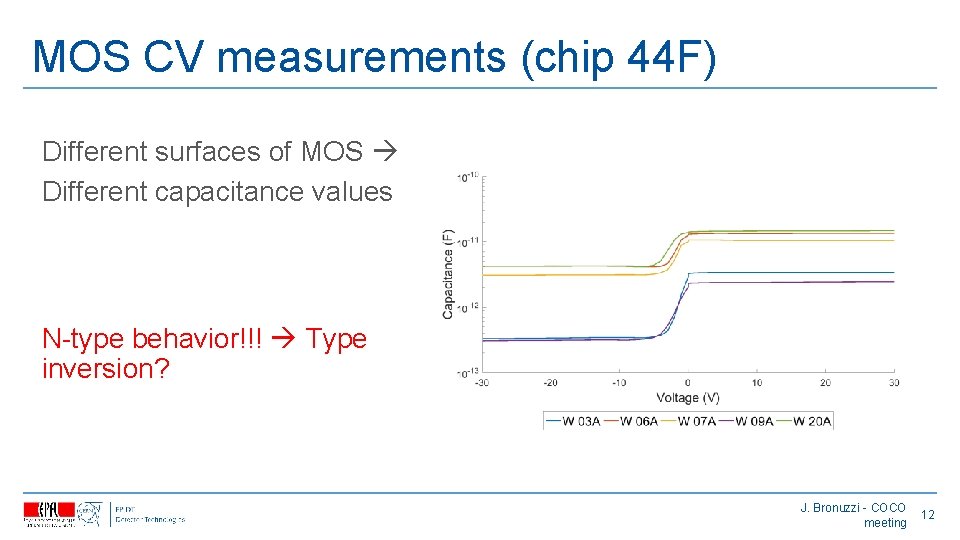

MOS CV measurements (chip 44 F) Different surfaces of MOS Different capacitance values N-type behavior!!! Type inversion? J. Bronuzzi - COCO meeting 12

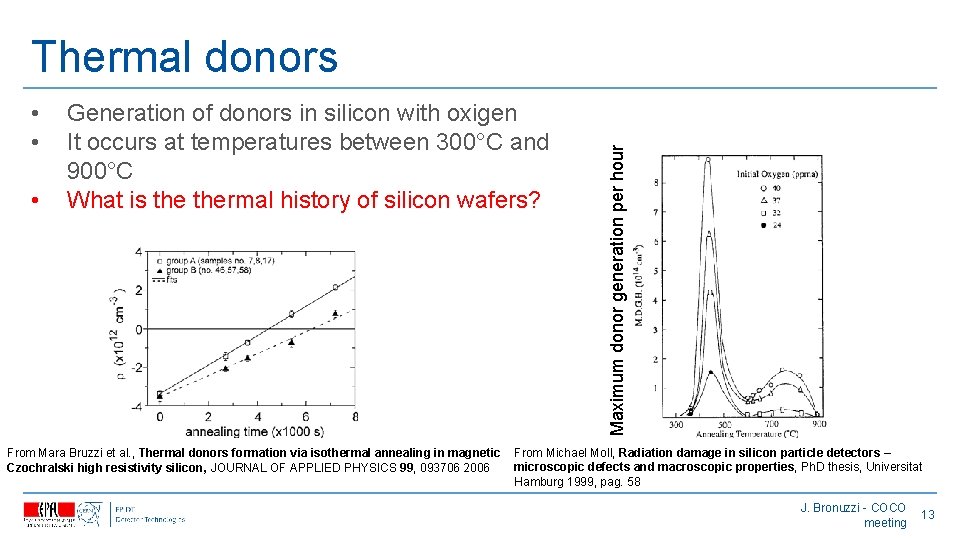

• • • Generation of donors in silicon with oxigen It occurs at temperatures between 300°C and 900°C What is thermal history of silicon wafers? From Mara Bruzzi et al. , Thermal donors formation via isothermal annealing in magnetic Czochralski high resistivity silicon, JOURNAL OF APPLIED PHYSICS 99, 093706 2006 Maximum donor generation per hour Thermal donors From Michael Moll, Radiation damage in silicon particle detectors – microscopic defects and macroscopic properties, Ph. D thesis, Universitat Hamburg 1999, pag. 58 J. Bronuzzi - COCO meeting 13

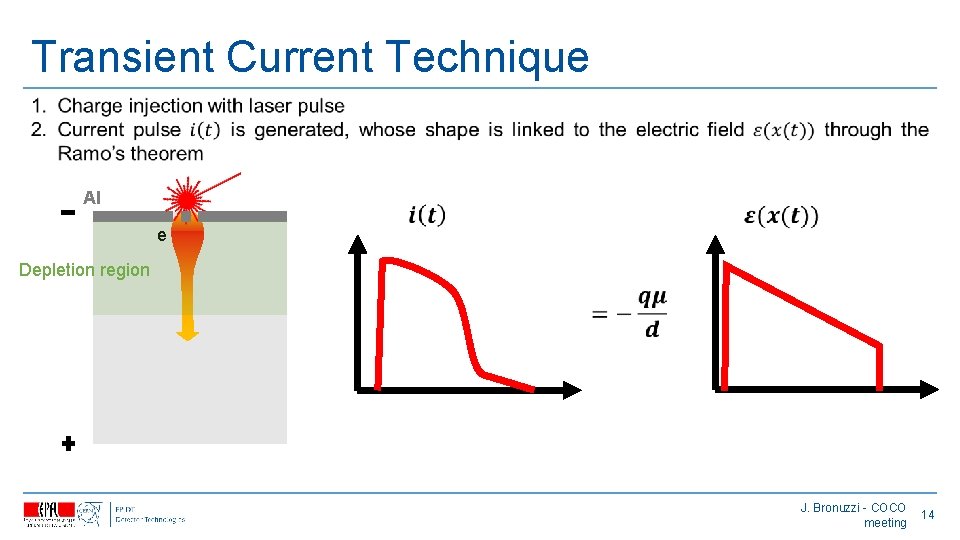

Transient Current Technique Al e Depletion region J. Bronuzzi - COCO meeting 14

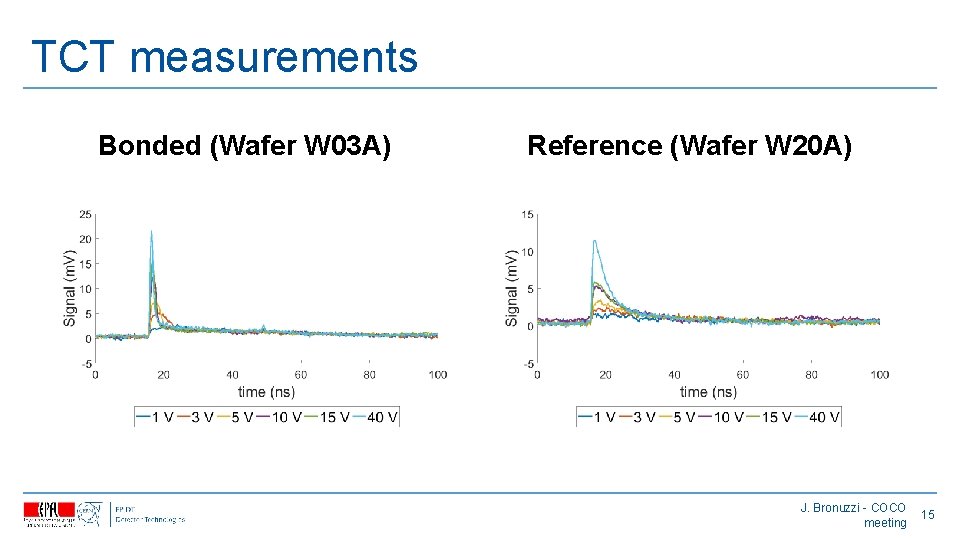

TCT measurements Bonded (Wafer W 03 A) Reference (Wafer W 20 A) J. Bronuzzi - COCO meeting 15

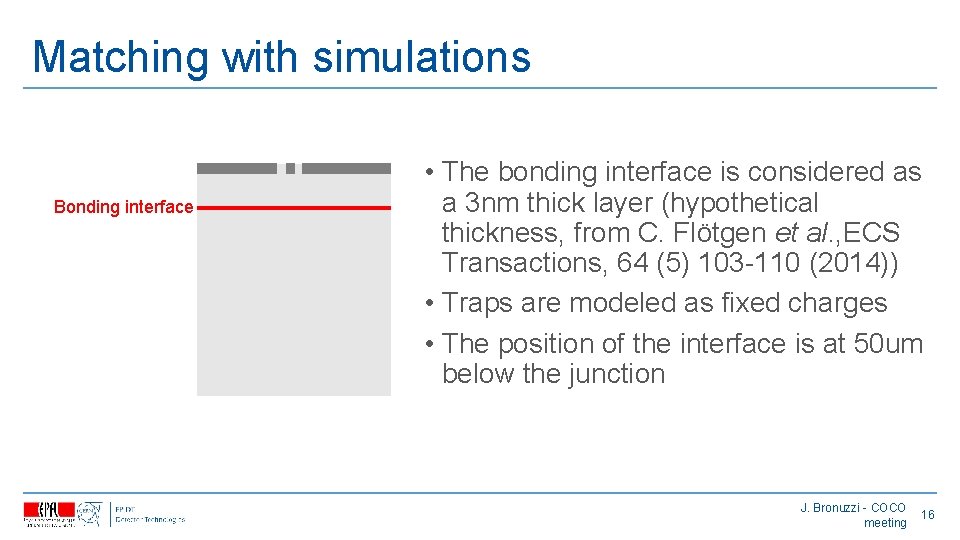

Matching with simulations Bonding interface • The bonding interface is considered as a 3 nm thick layer (hypothetical thickness, from C. Flötgen et al. , ECS Transactions, 64 (5) 103 -110 (2014)) • Traps are modeled as fixed charges • The position of the interface is at 50 um below the junction J. Bronuzzi - COCO meeting 16

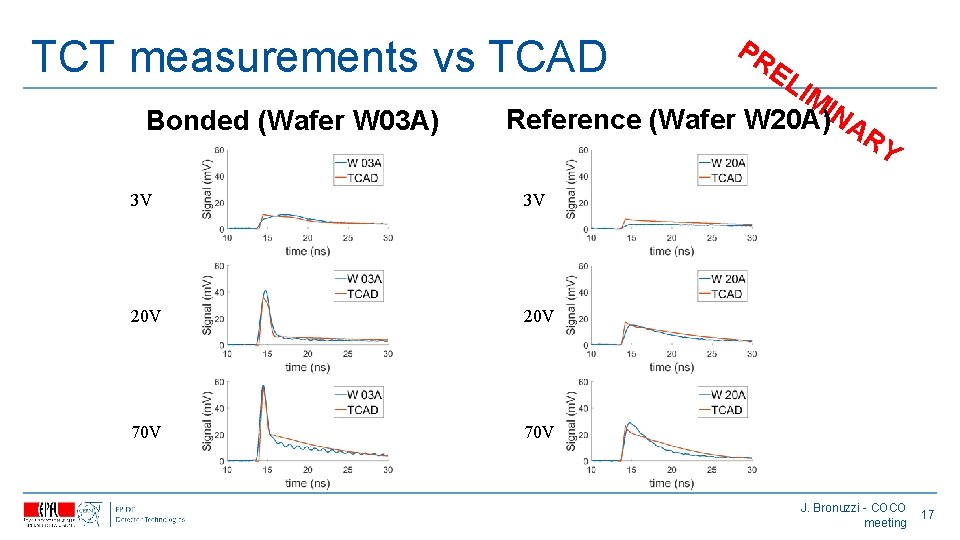

TCT measurements vs TCAD Bonded (Wafer W 03 A) PR EL IM I Reference (Wafer W 20 A)NAR Y 3 V 3 V 20 V 70 V J. Bronuzzi - COCO meeting 17

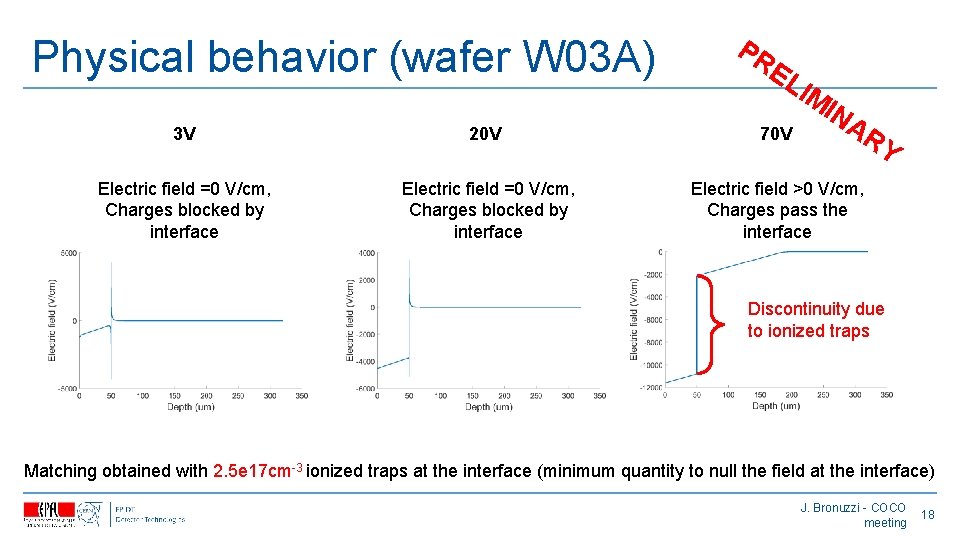

Physical behavior (wafer W 03 A) PR EL IM IN AR Y 3 V 20 V 70 V Electric field =0 V/cm, Charges blocked by interface Electric field >0 V/cm, Charges pass the interface Discontinuity due to ionized traps Matching obtained with 2. 5 e 17 cm-3 ionized traps at the interface (minimum quantity to null the field at the interface) J. Bronuzzi - COCO meeting 18

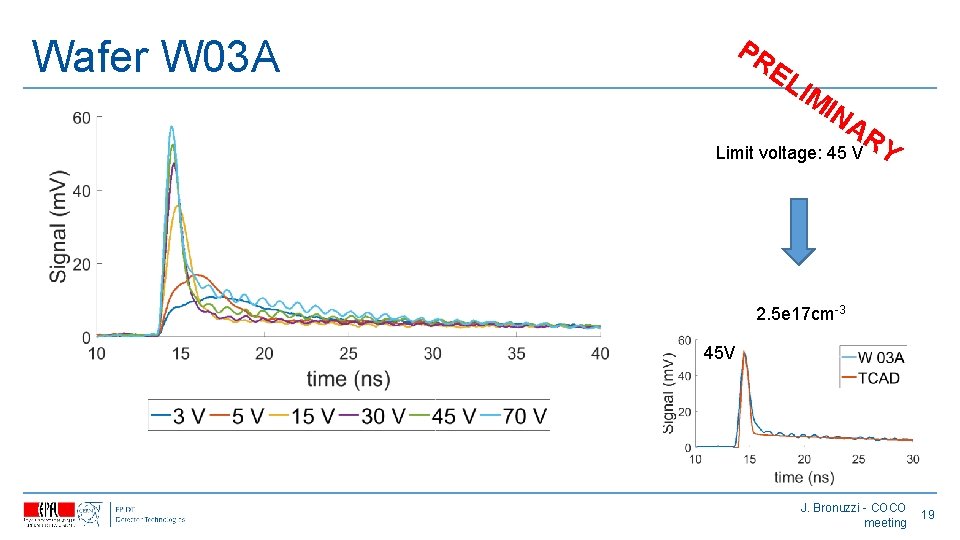

Wafer W 03 A PR EL IM IN AR Y Limit voltage: 45 V 2. 5 e 17 cm-3 45 V J. Bronuzzi - COCO meeting 19

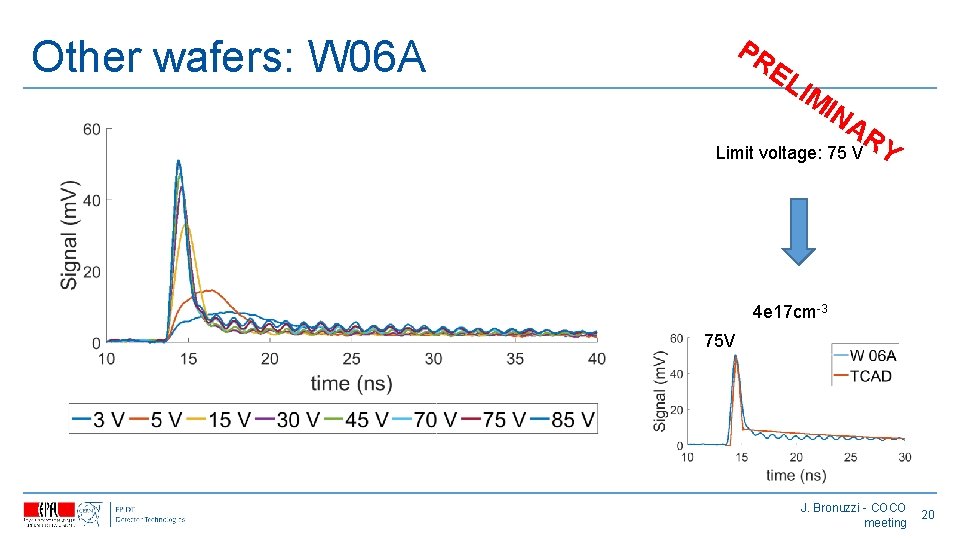

Other wafers: W 06 A PR EL IM IN AR Y Limit voltage: 75 V 4 e 17 cm-3 75 V J. Bronuzzi - COCO meeting 20

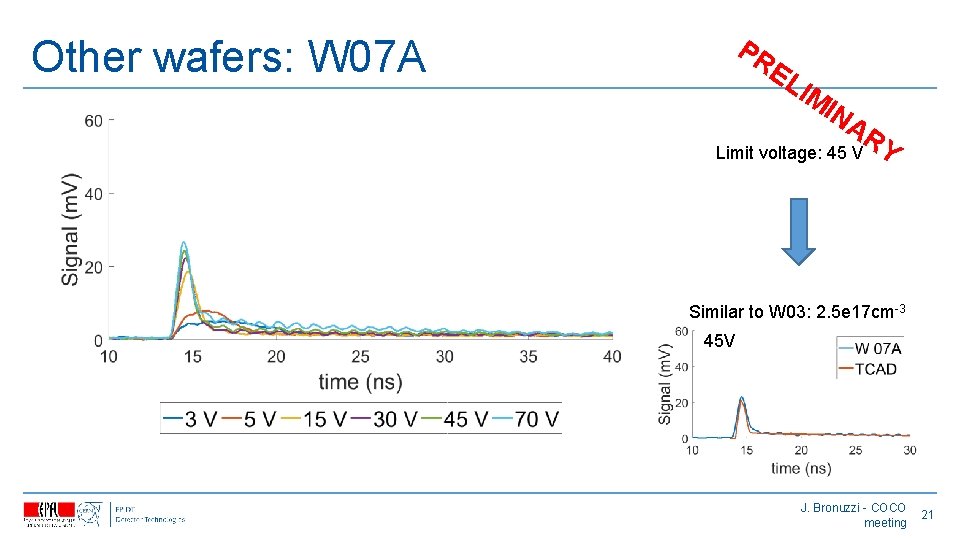

Other wafers: W 07 A PR EL IM IN AR Y Limit voltage: 45 V Similar to W 03: 2. 5 e 17 cm-3 45 V J. Bronuzzi - COCO meeting 21

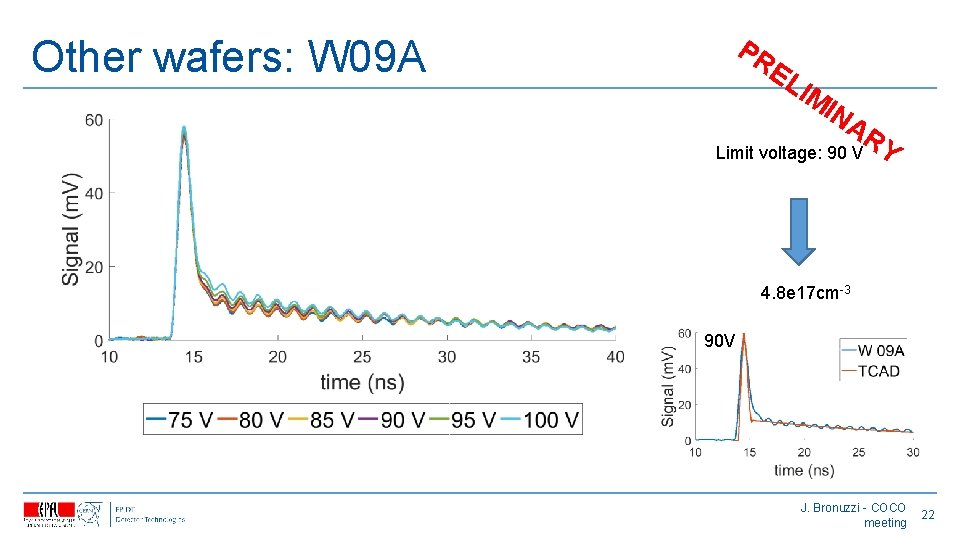

Other wafers: W 09 A PR EL IM IN AR Y Limit voltage: 90 V 4. 8 e 17 cm-3 90 V J. Bronuzzi - COCO meeting 22

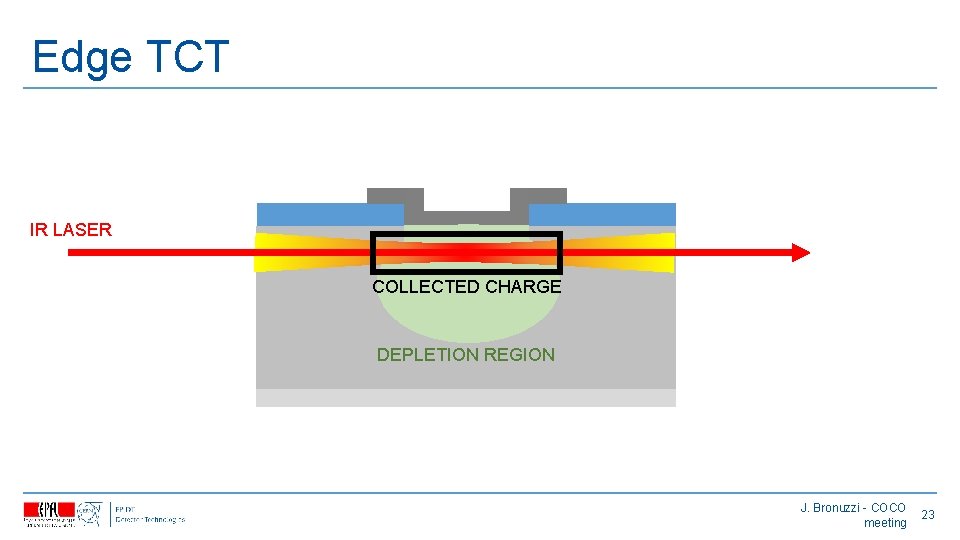

Edge TCT IR LASER COLLECTED CHARGE DEPLETION REGION J. Bronuzzi - COCO meeting 23

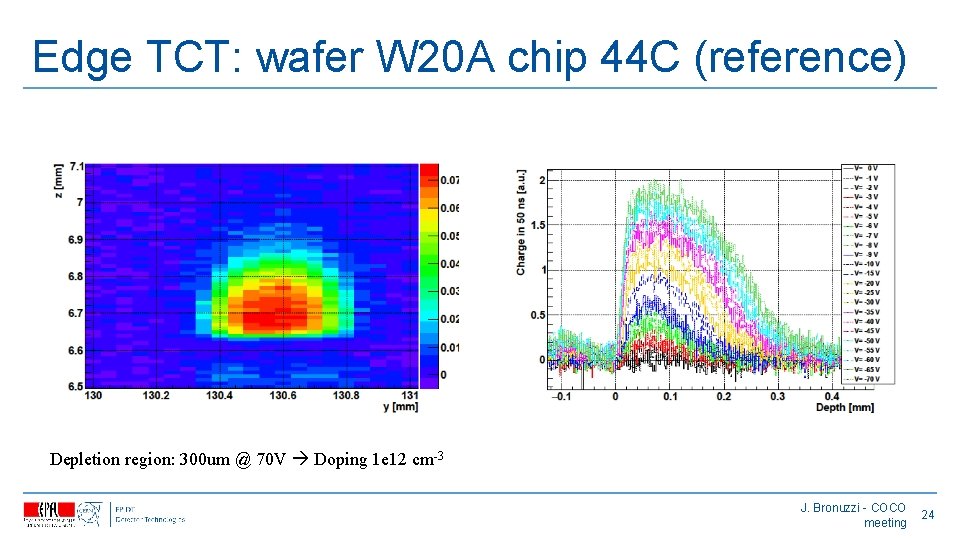

Edge TCT: wafer W 20 A chip 44 C (reference) Depletion region: 300 um @ 70 V Doping 1 e 12 cm-3 J. Bronuzzi - COCO meeting 24

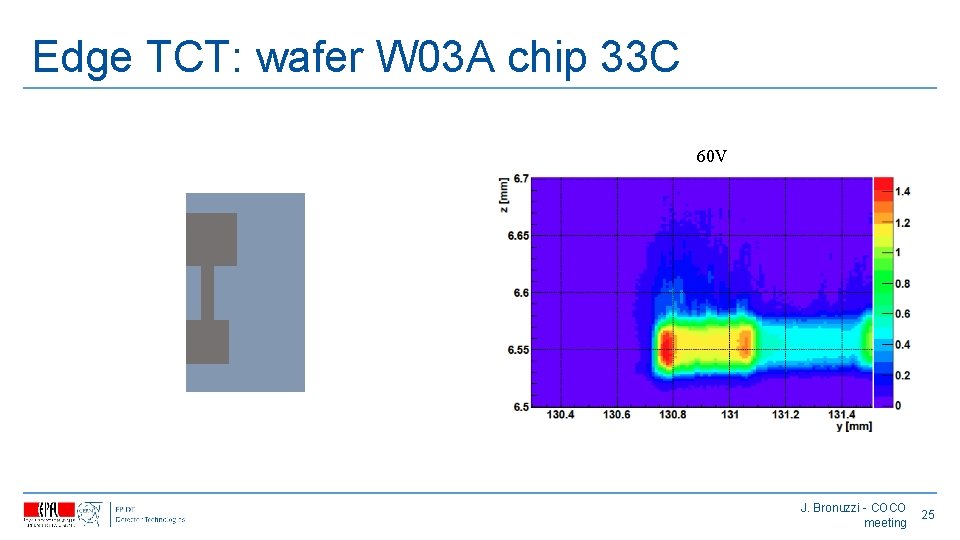

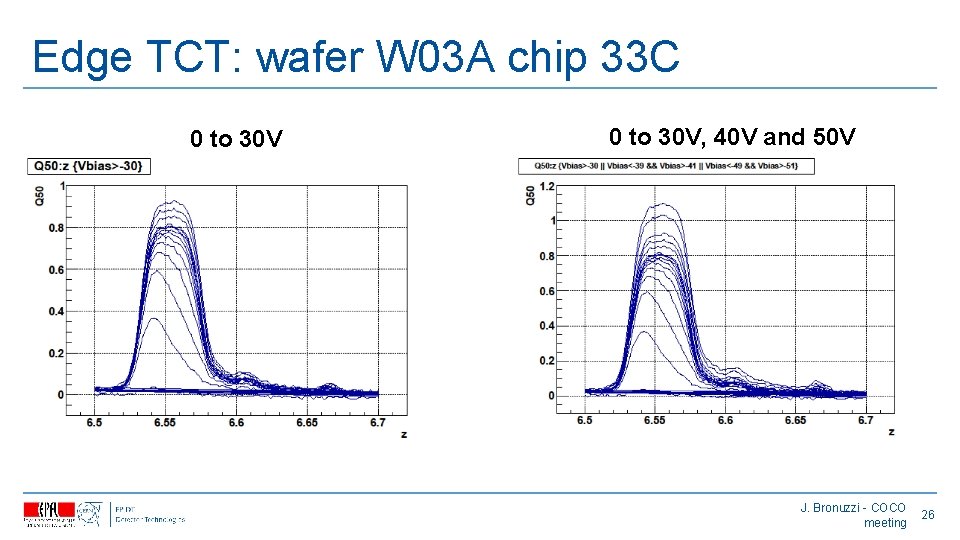

Edge TCT: wafer W 03 A chip 33 C 60 V J. Bronuzzi - COCO meeting 25

Edge TCT: wafer W 03 A chip 33 C 0 to 30 V, 40 V and 50 V J. Bronuzzi - COCO meeting 26

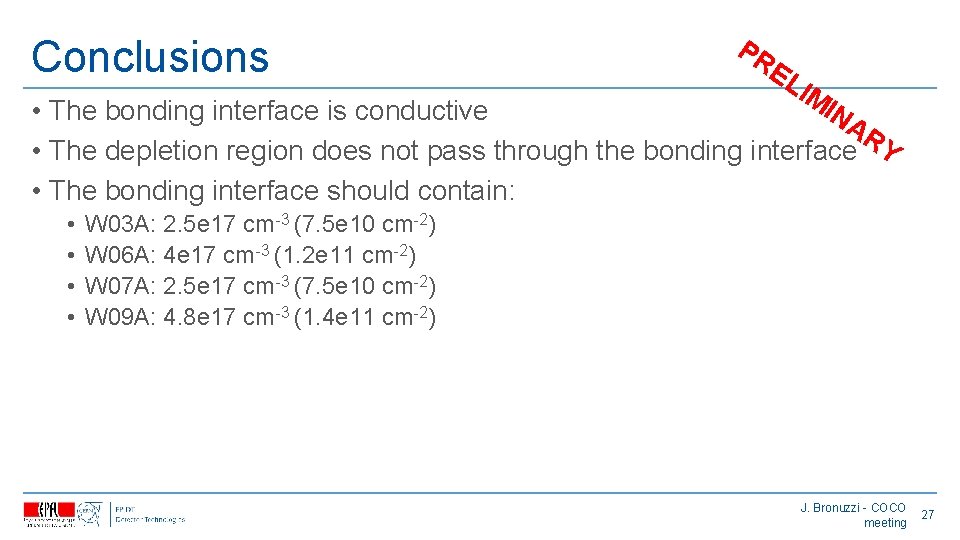

Conclusions PR EL IM IN • The bonding interface is conductive AR • The depletion region does not pass through the bonding interface Y • The bonding interface should contain: • • W 03 A: 2. 5 e 17 cm-3 (7. 5 e 10 cm-2) W 06 A: 4 e 17 cm-3 (1. 2 e 11 cm-2) W 07 A: 2. 5 e 17 cm-3 (7. 5 e 10 cm-2) W 09 A: 4. 8 e 17 cm-3 (1. 4 e 11 cm-2) J. Bronuzzi - COCO meeting 27

- Slides: 27