CHAPTER V 1 Oscillators 2 Interrupts 3 timers

- Slides: 36

CHAPTER V 1 - Oscillators, 2 - Interrupts, 3 - timers, 4 -Inputs/Outputs . Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 1

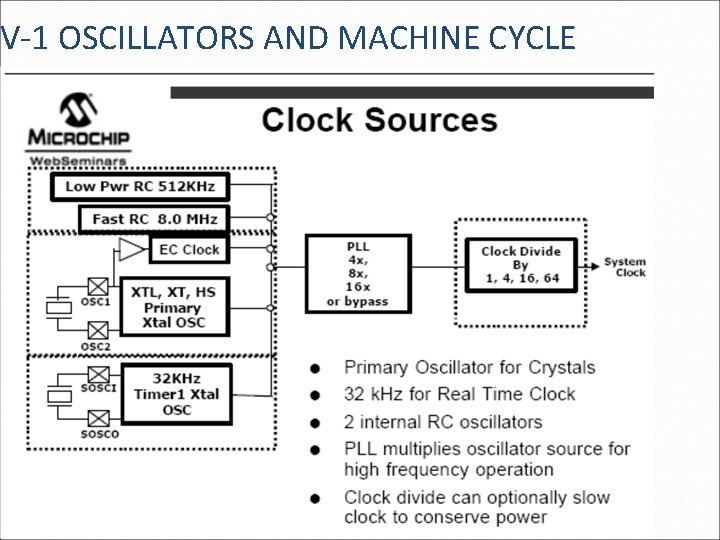

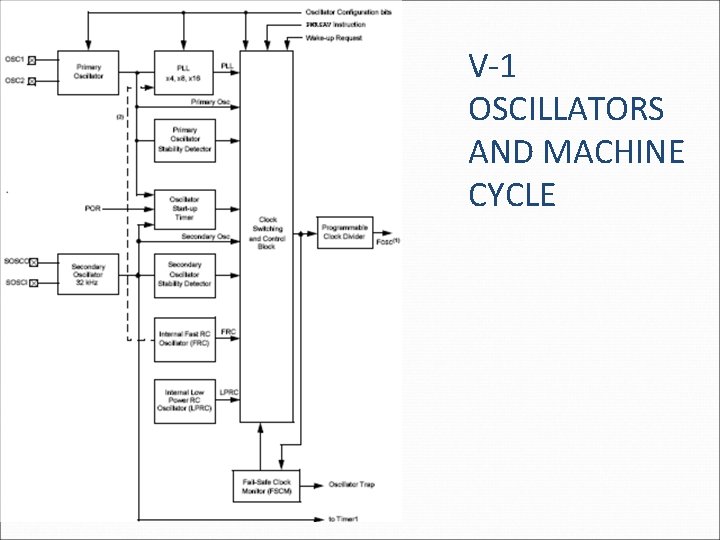

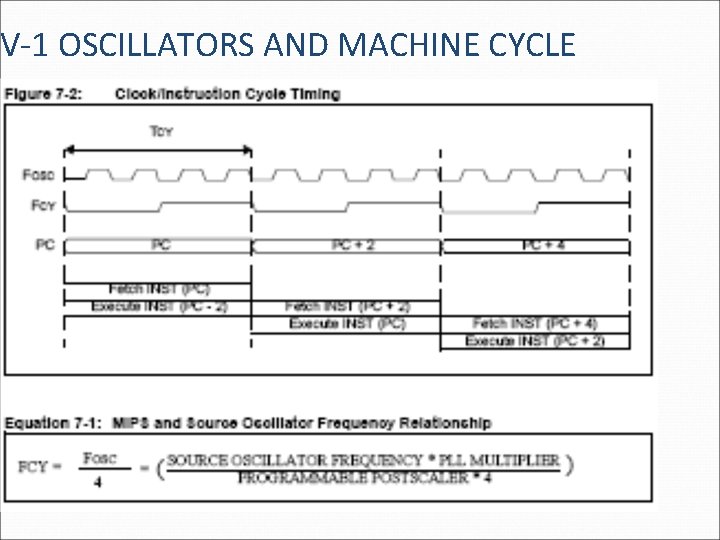

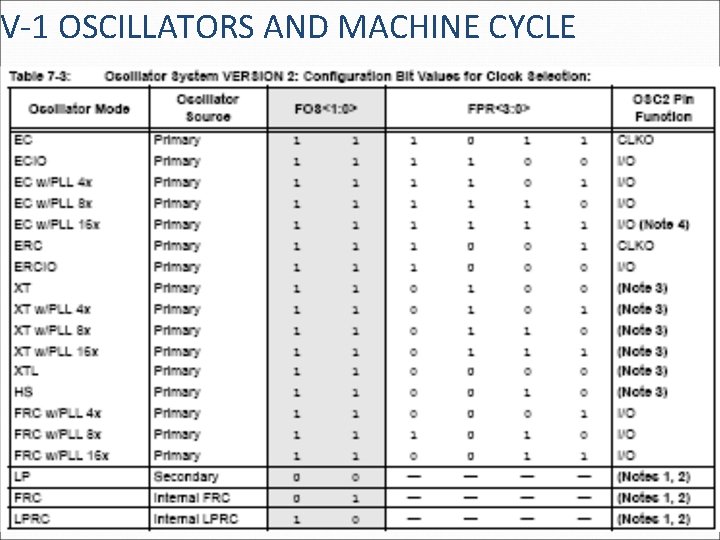

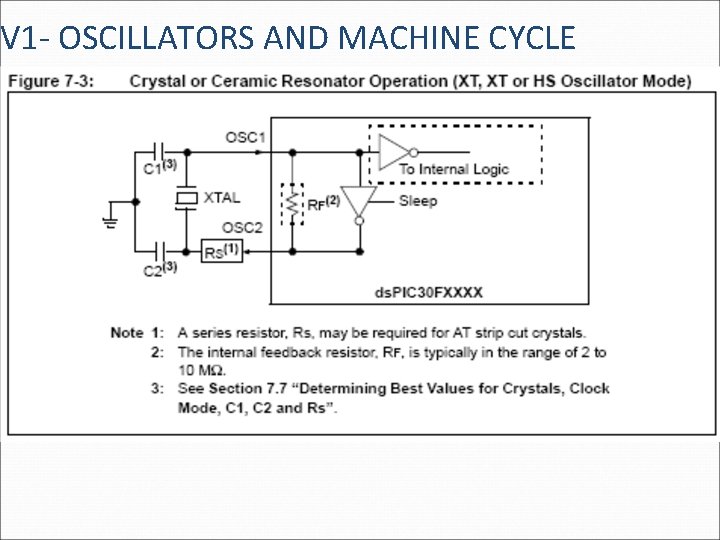

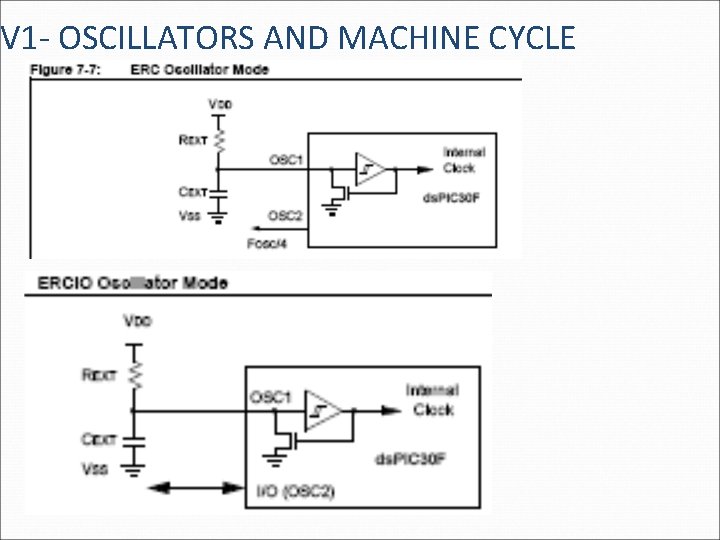

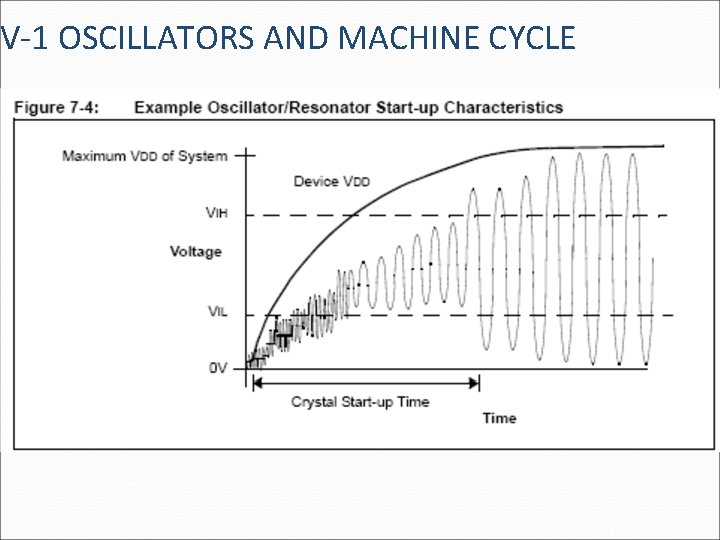

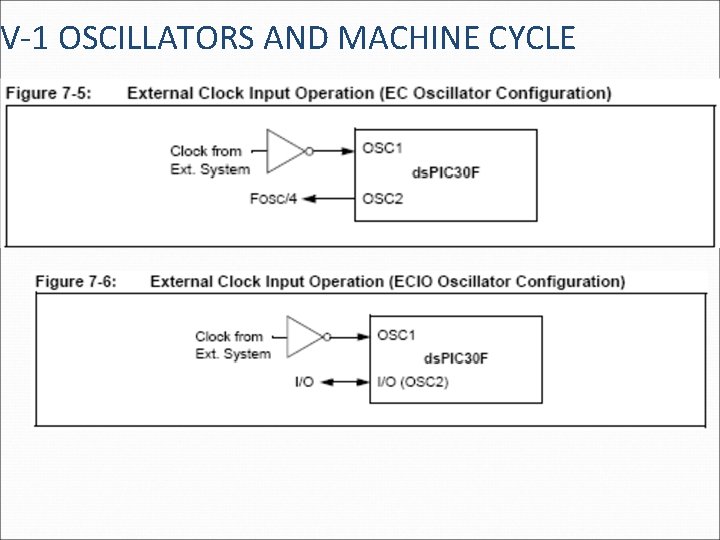

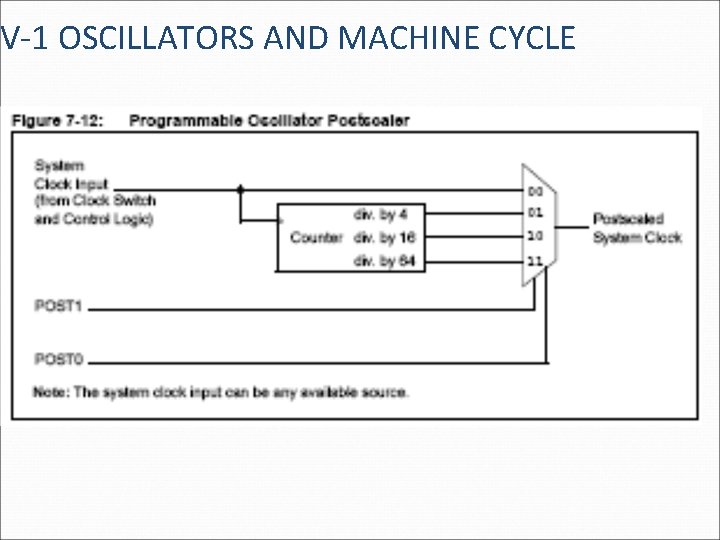

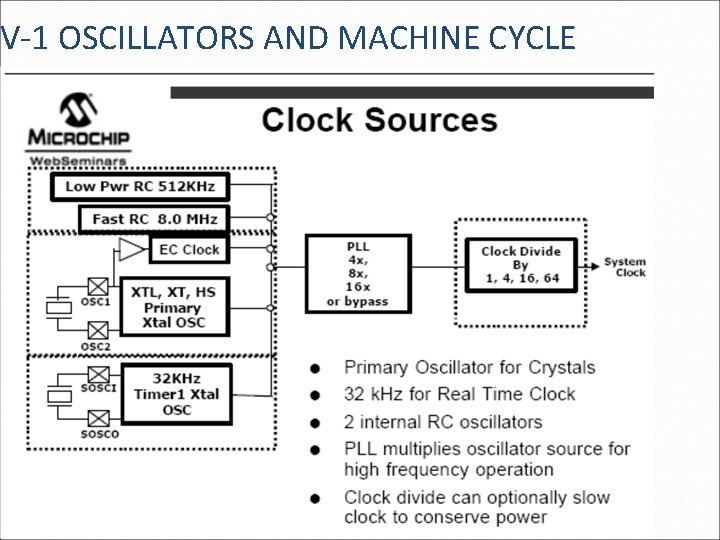

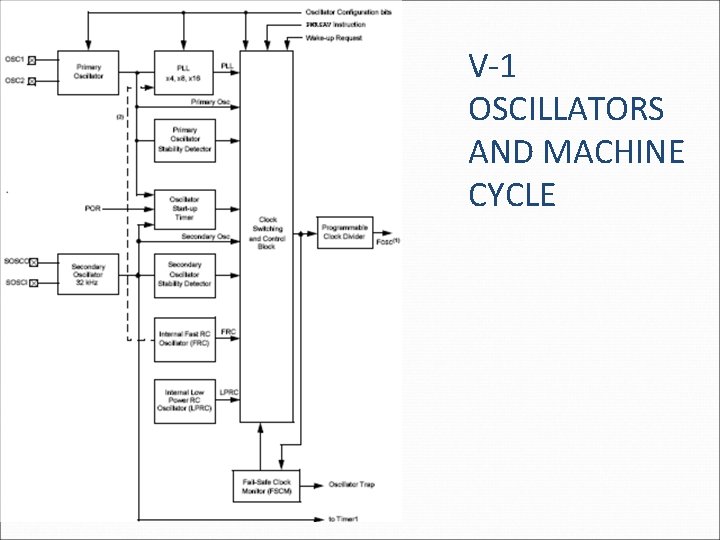

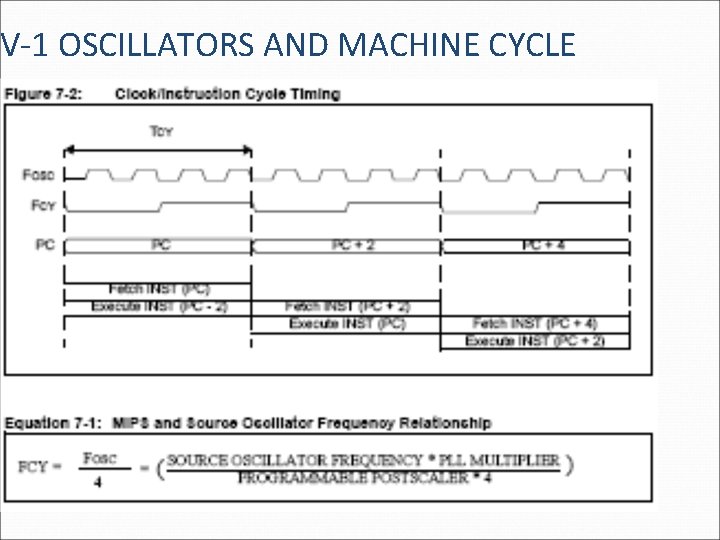

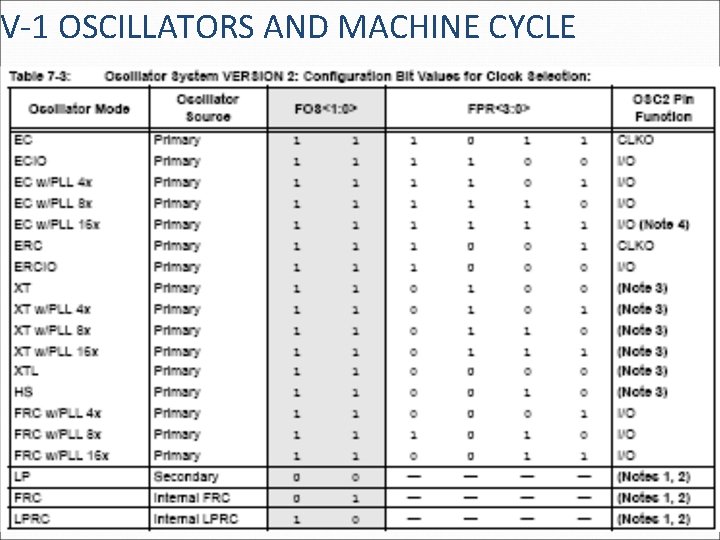

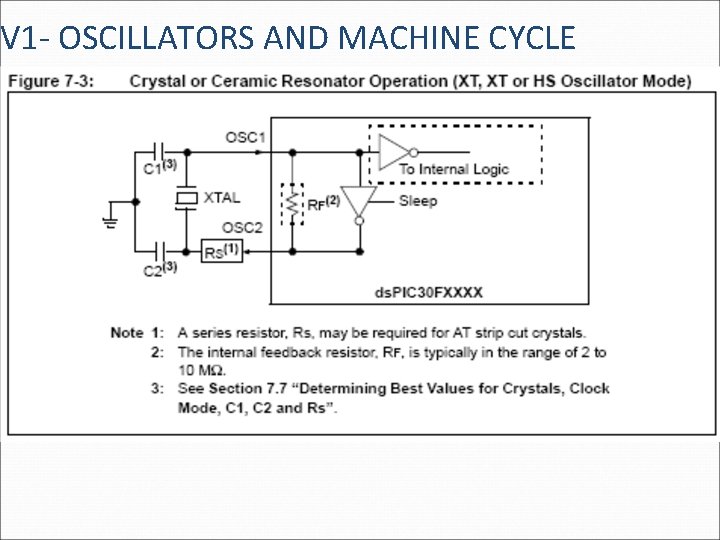

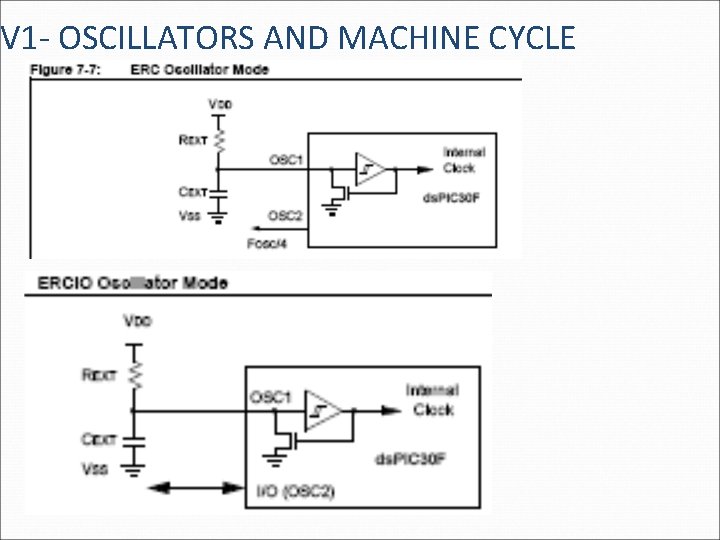

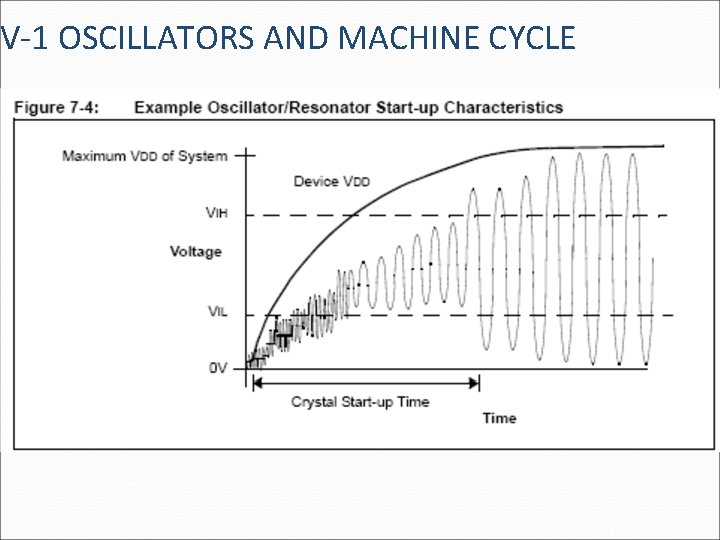

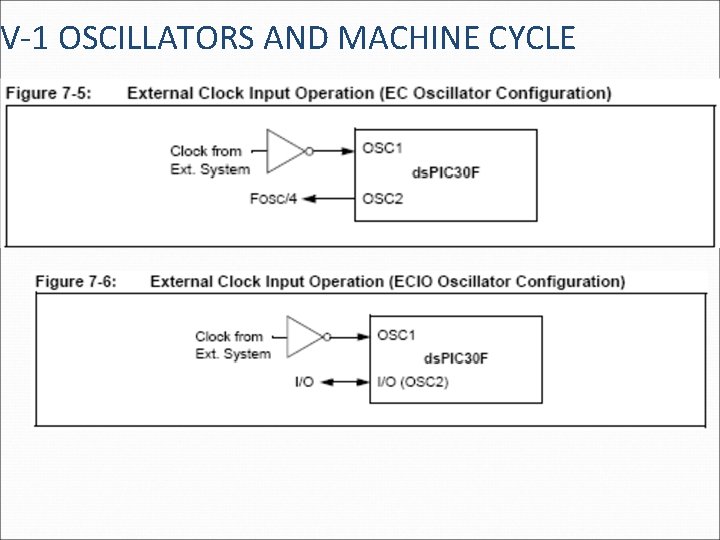

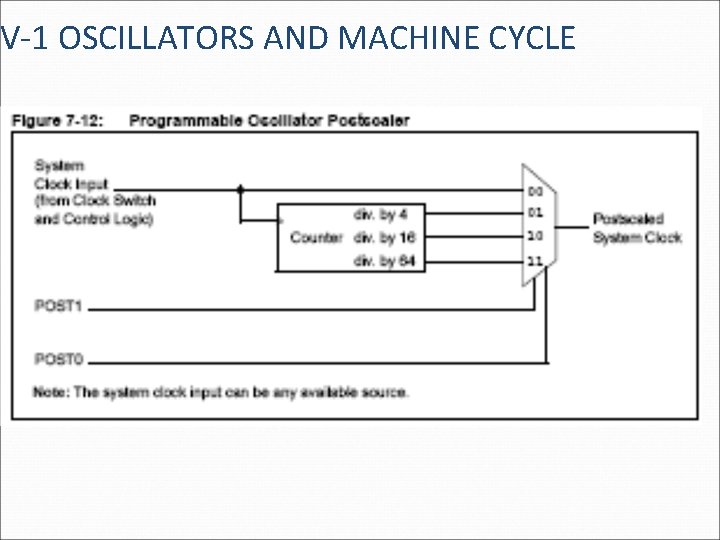

V-1 OSCILLATORS AND MACHINE CYCLE

V-1 OSCILLATORS AND MACHINE CYCLE

V-1 OSCILLATORS AND MACHINE CYCLE

V-1 OSCILLATORS AND MACHINE CYCLE

V 1 - OSCILLATORS AND MACHINE CYCLE

V 1 - OSCILLATORS AND MACHINE CYCLE

V-1 OSCILLATORS AND MACHINE CYCLE

V-1 OSCILLATORS AND MACHINE CYCLE

V-1 OSCILLATORS AND MACHINE CYCLE

V-2 - Interrupts Interrupt is a process where an external device can get the attention of the microprocessor. The process starts from the I/O device The process is asynchronous. Interrupts can be classified into two types: Maskable (can be delayed) Non-Maskable (can not be delayed) Interrupts can also be classified into: Vectored (the address of the service routine is hard-wired) Non-vectored (the address of the service routine needs to be supplied externally) Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 11

V-2 Interrupts An interrupt is considered to be an emergency signal. The Microprocessor should respond, to it, as soon as possible. When the Microprocessor receives an interrupt signal, it suspends the currently executing program and jumps to an Interrupt Service Routine (ISR) to respond to the incoming interrupt. Each interrupt will most probably have its own ISR. Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 12

V-1 Responding to Interrupts Responding to an interrupt may be immediate or delayed depending on whether the interrupt is maskable or non-maskable and whether interrupts are being masked or not. There are two ways of redirecting the execution to the ISR depending on whether the interrupt is vectored or non-vectored. The vector is already known to the Microprocessor The device will have to supply the vector to the Microprocessor Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 13

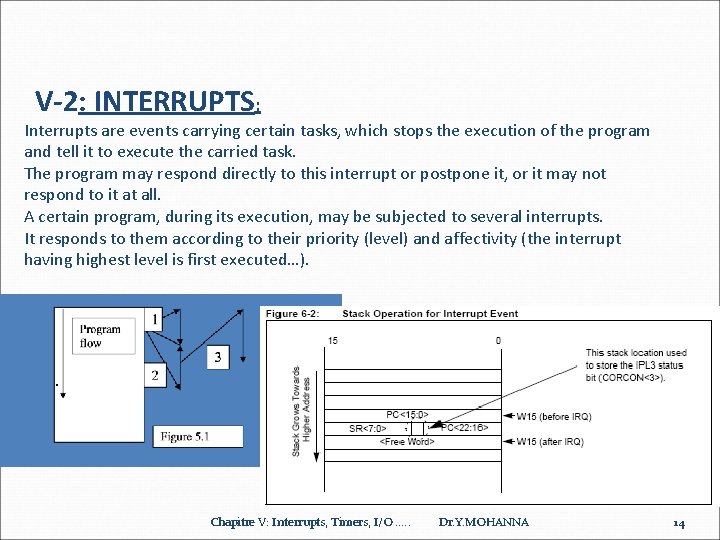

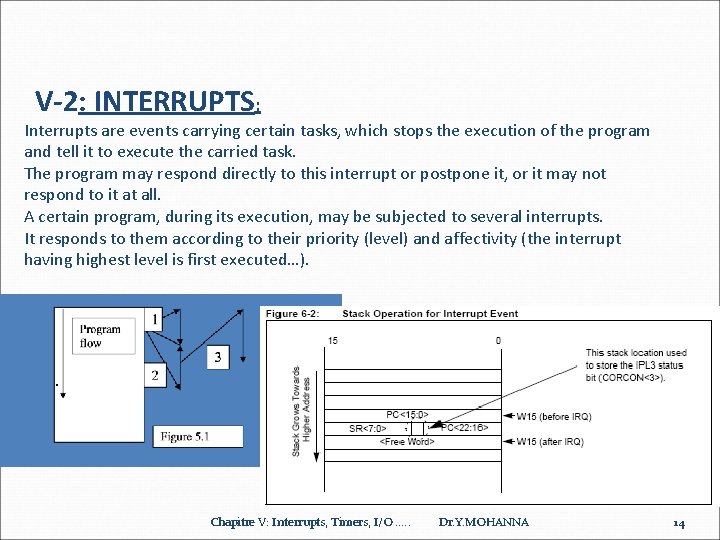

V-2: INTERRUPTS: Interrupts are events carrying certain tasks, which stops the execution of the program and tell it to execute the carried task. The program may respond directly to this interrupt or postpone it, or it may not respond to it at all. A certain program, during its execution, may be subjected to several interrupts. It responds to them according to their priority (level) and affectivity (the interrupt having highest level is first executed…). . Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 14

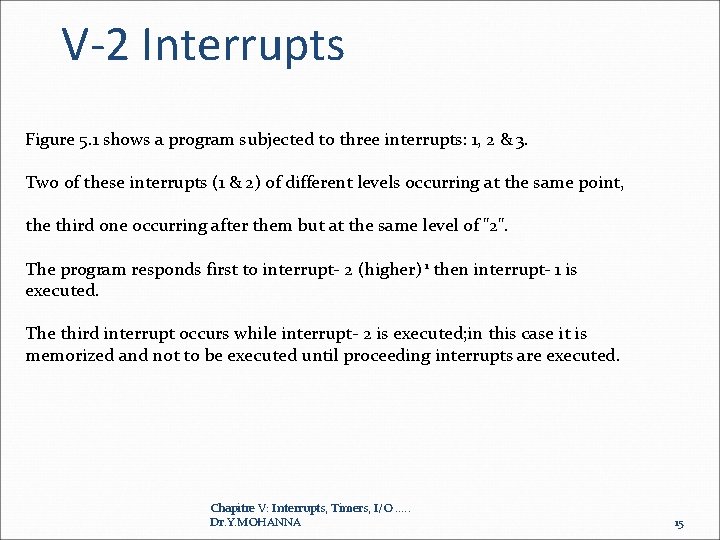

V-2 Interrupts Figure 5. 1 shows a program subjected to three interrupts: 1, 2 & 3. Two of these interrupts (1 & 2) of different levels occurring at the same point, the third one occurring after them but at the same level of "2". The program responds first to interrupt- 2 (higher) 1 then interrupt- 1 is executed. The third interrupt occurs while interrupt- 2 is executed; in this case it is memorized and not to be executed until proceeding interrupts are executed. Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 15

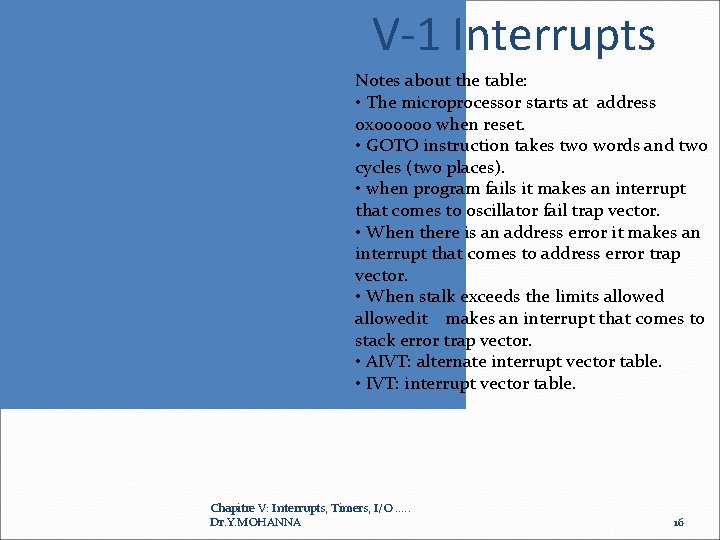

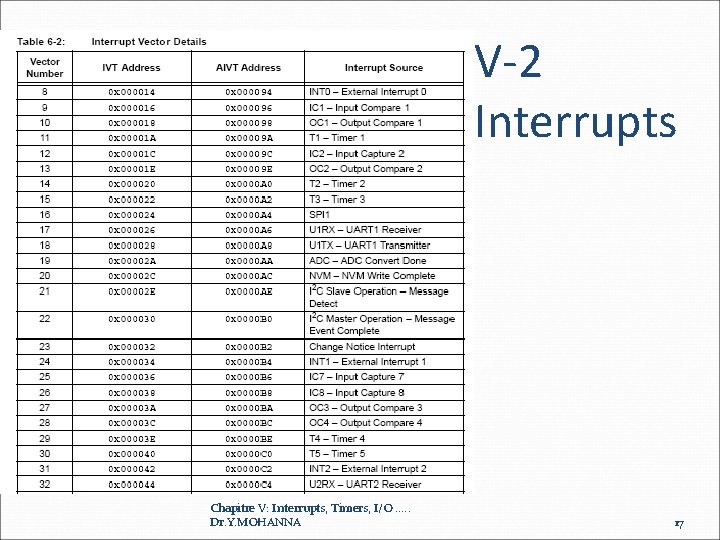

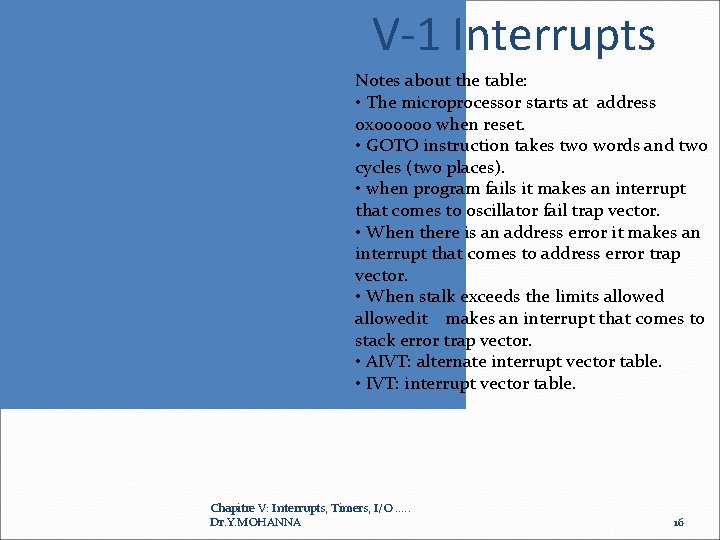

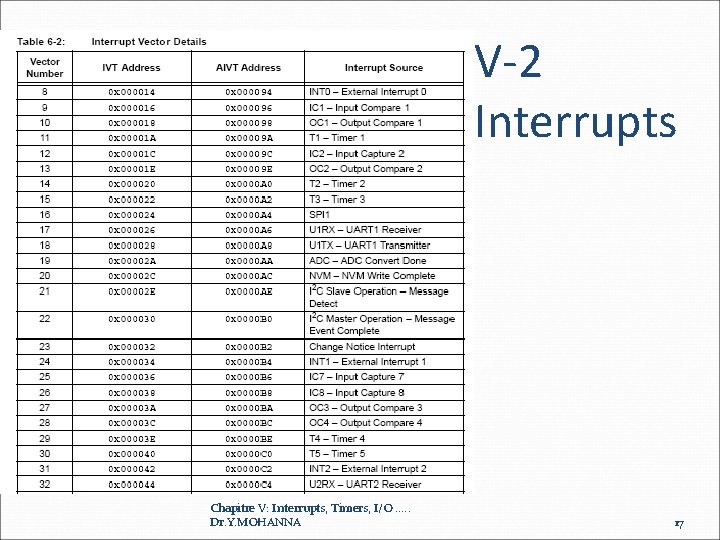

V-1 Interrupts Notes about the table: • The microprocessor starts at address 0 x 000000 when reset. • GOTO instruction takes two words and two cycles (two places). • when program fails it makes an interrupt that comes to oscillator fail trap vector. • When there is an address error it makes an interrupt that comes to address error trap vector. • When stalk exceeds the limits allowedit makes an interrupt that comes to stack error trap vector. • AIVT: alternate interrupt vector table. • IVT: interrupt vector table. Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 16

V-2 Interrupts Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 17

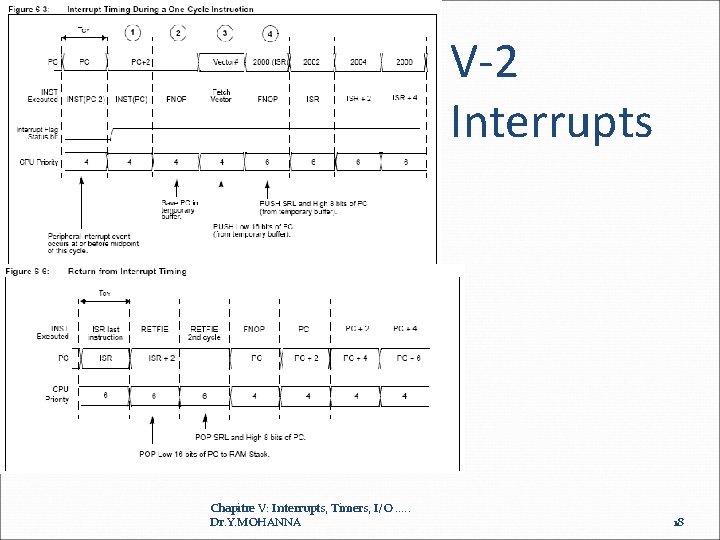

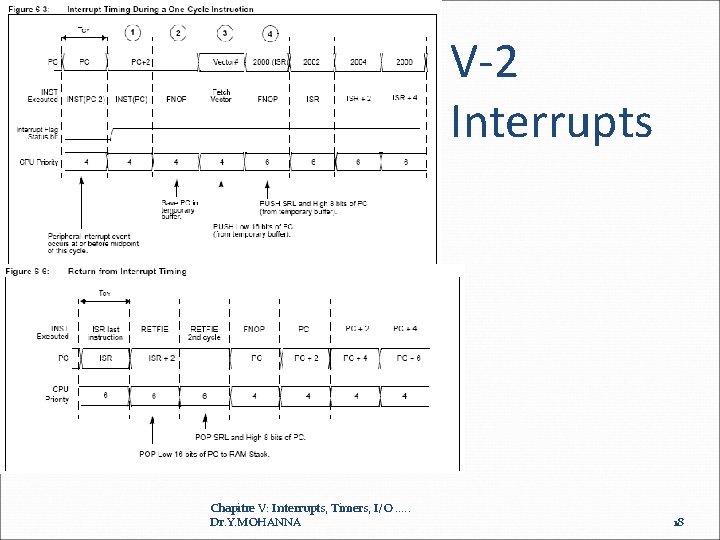

V-2 Interrupts Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 18

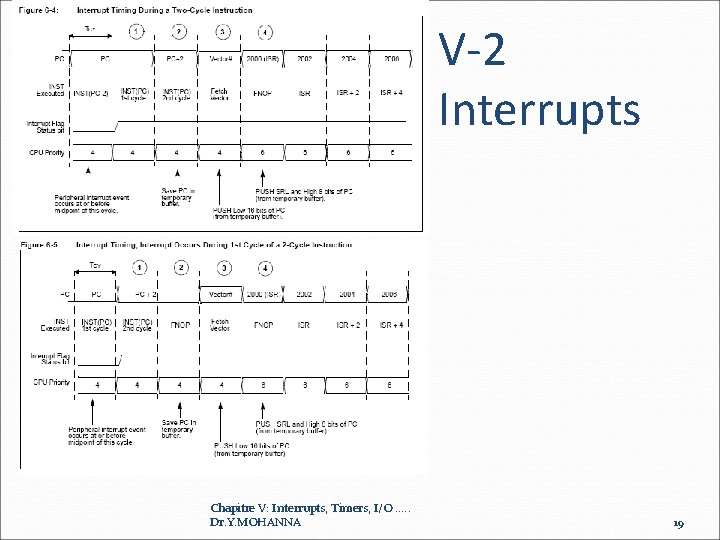

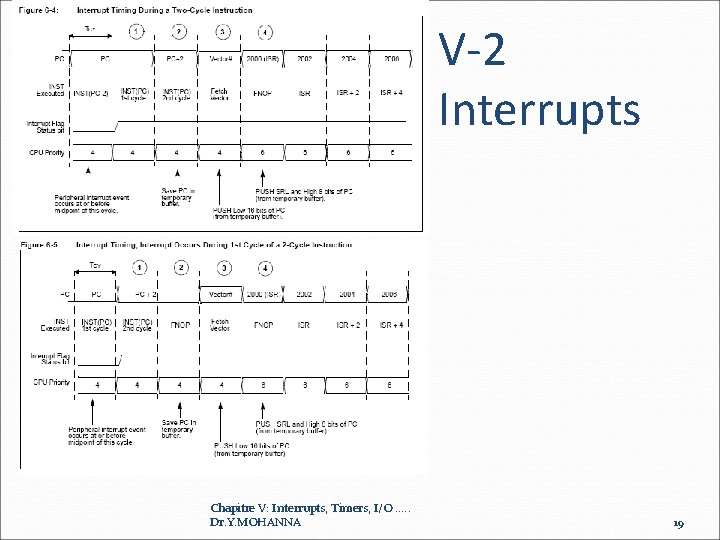

V-2 Interrupts Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 19

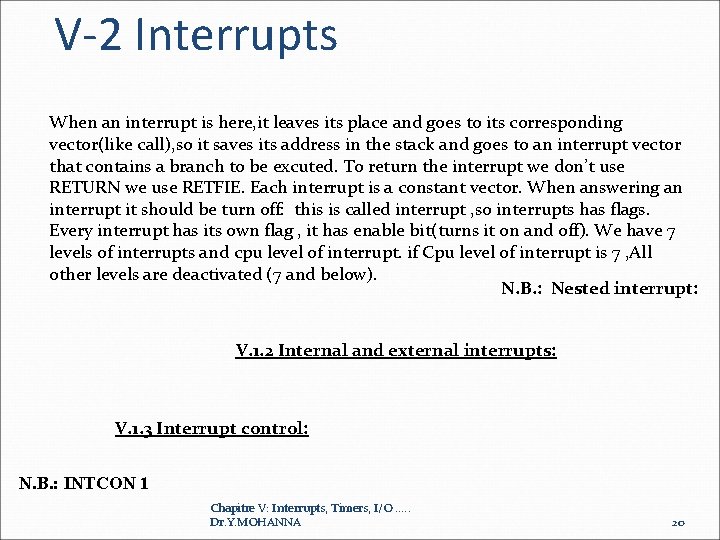

V-2 Interrupts When an interrupt is here, it leaves its place and goes to its corresponding vector(like call), so it saves its address in the stack and goes to an interrupt vector that contains a branch to be excuted. To return the interrupt we don’t use RETURN we use RETFIE. Each interrupt is a constant vector. When answering an interrupt it should be turn off: this is called interrupt , so interrupts has flags. Every interrupt has its own flag , it has enable bit(turns it on and off). We have 7 levels of interrupts and cpu level of interrupt. if Cpu level of interrupt is 7 , All other levels are deactivated (7 and below). N. B. : Nested interrupt: V. 1. 2 Internal and external interrupts: V. 1. 3 Interrupt control: N. B. : INTCON 1 Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 20

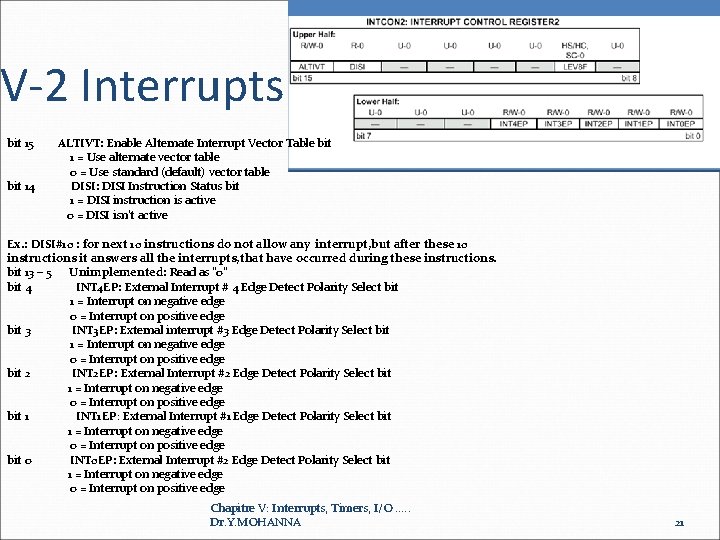

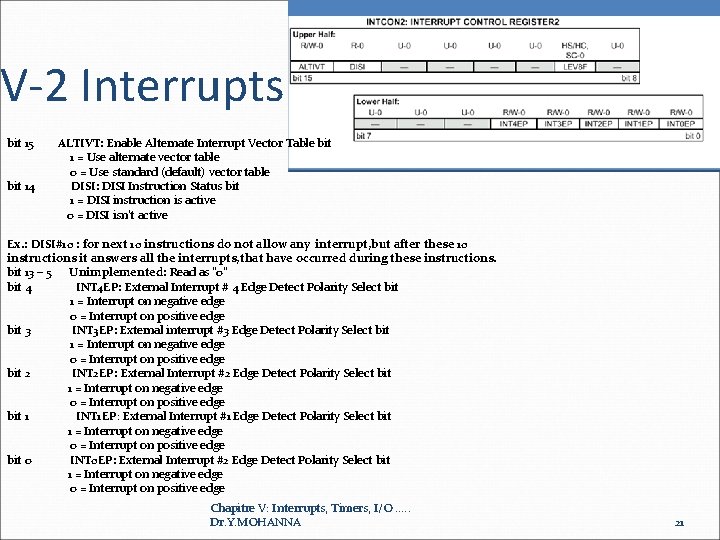

V-2 Interrupts bit 15 ALTIVT: Enable Alternate Interrupt Vector Table bit 1 = Use alternate vector table 0 = Use standard (default) vector table bit 14 DISI: DISI Instruction Status bit 1 = DISI instruction is active 0 = DISI isn't active Ex. : DISI#10 : for next 10 instructions do not allow any interrupt, but after these 10 instructions it answers all the interrupts, that have occurred during these instructions. bit 13 – 5 Unimplemented: Read as "0" bit 4 INT 4 EP: External Interrupt # 4 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on positive edge bit 3 INT 3 EP: External interrupt #3 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on positive edge bit 2 INT 2 EP: External Interrupt #2 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on positive edge bit 1 INT 1 EP: External Interrupt #1 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on positive edge bit 0 INT 0 EP: External Interrupt #2 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on positive edge Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 21

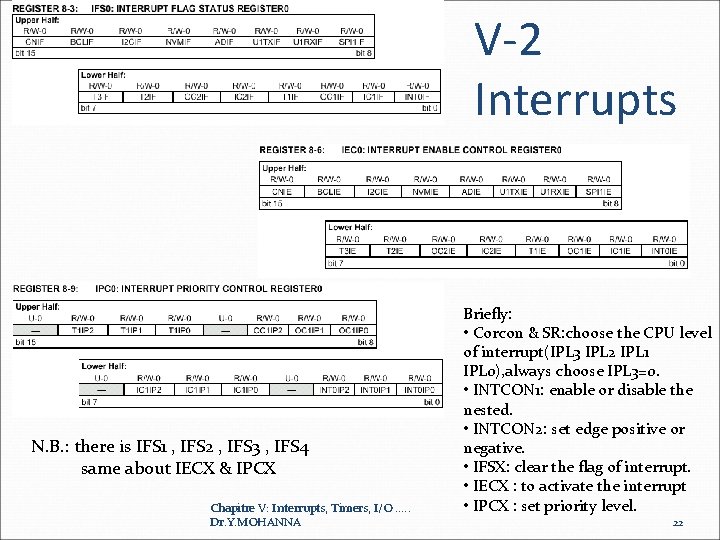

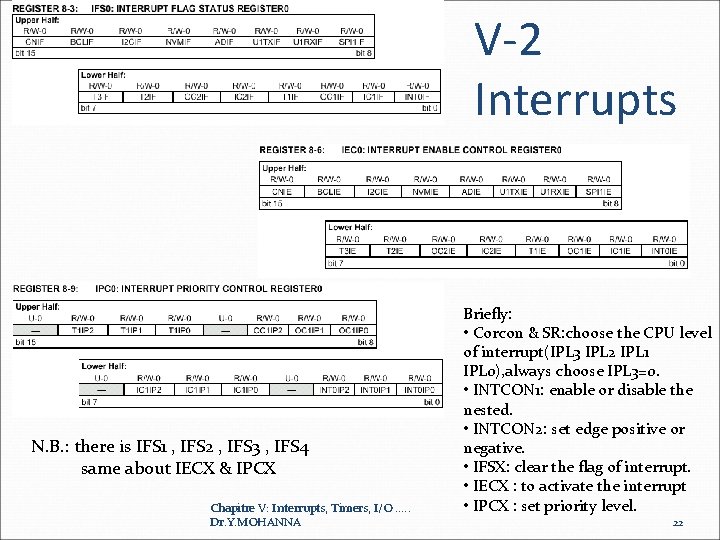

V-2 Interrupts N. B. : there is IFS 1 , IFS 2 , IFS 3 , IFS 4 same about IECX & IPCX Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA Briefly: • Corcon & SR: choose the CPU level of interrupt(IPL 3 IPL 2 IPL 1 IPL 0), always choose IPL 3=0. • INTCON 1: enable or disable the nested. • INTCON 2: set edge positive or negative. • IFSX: clear the flag of interrupt. • IECX : to activate the interrupt • IPCX : set priority level. 22

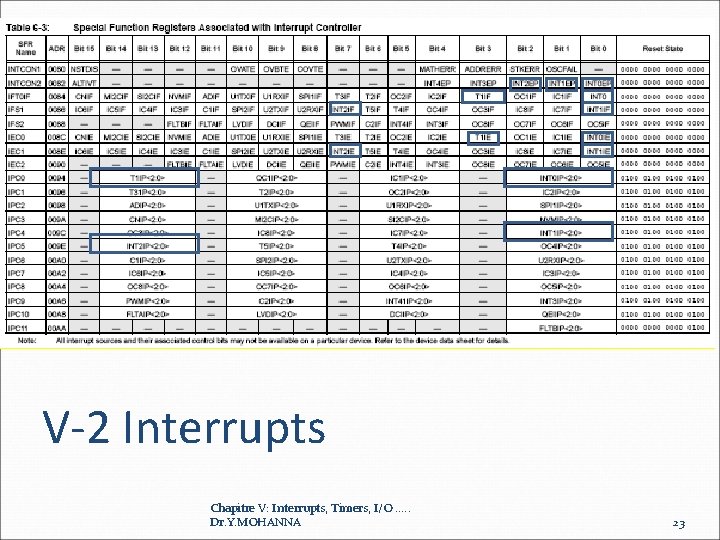

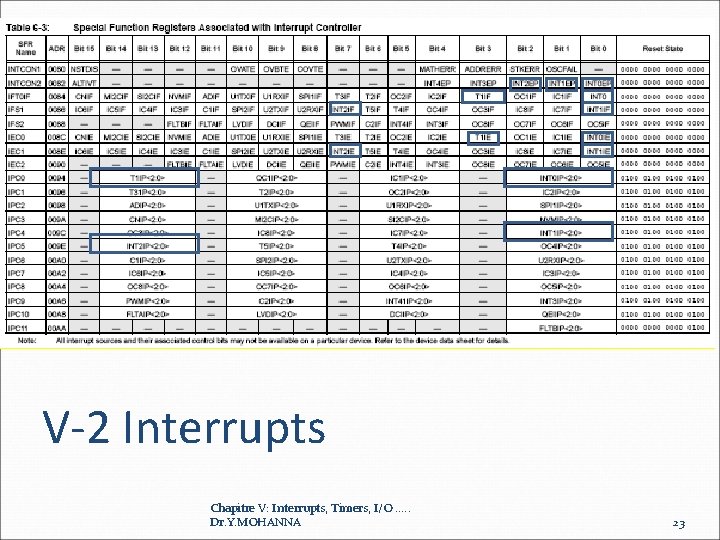

V-2 Interrupts Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 23

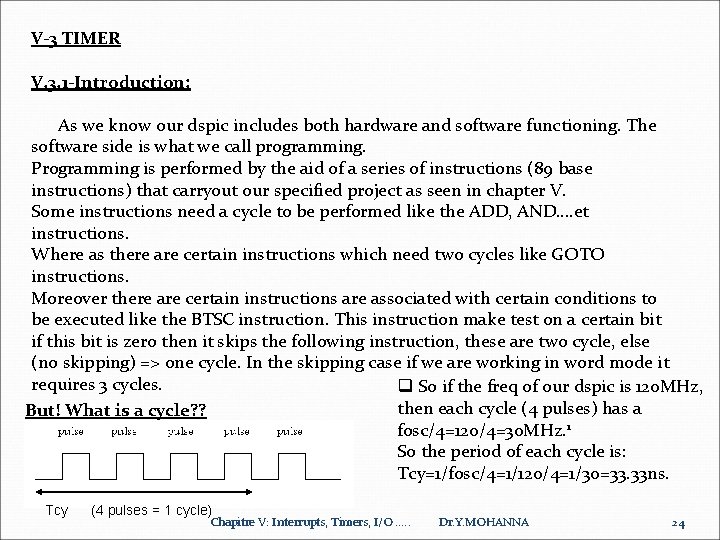

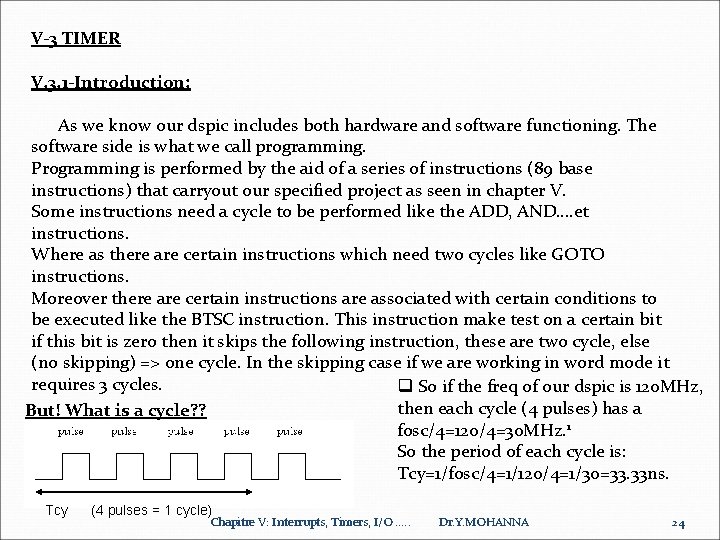

V-3 TIMER V. 3. 1 -Introduction: As we know our dspic includes both hardware and software functioning. The software side is what we call programming. Programming is performed by the aid of a series of instructions (89 base instructions) that carryout our specified project as seen in chapter V. Some instructions need a cycle to be performed like the ADD, AND…. et instructions. Where as there are certain instructions which need two cycles like GOTO instructions. Moreover there are certain instructions are associated with certain conditions to be executed like the BTSC instruction. This instruction make test on a certain bit if this bit is zero then it skips the following instruction, these are two cycle, else (no skipping) => one cycle. In the skipping case if we are working in word mode it requires 3 cycles. q So if the freq of our dspic is 120 MHz, then each cycle (4 pulses) has a But! What is a cycle? ? fosc/4=120/4=30 MHz. 1 So the period of each cycle is: Tcy=1/fosc/4=1/120/4=1/30=33. 33 ns. Tcy (4 pulses = 1 cycle) Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 24

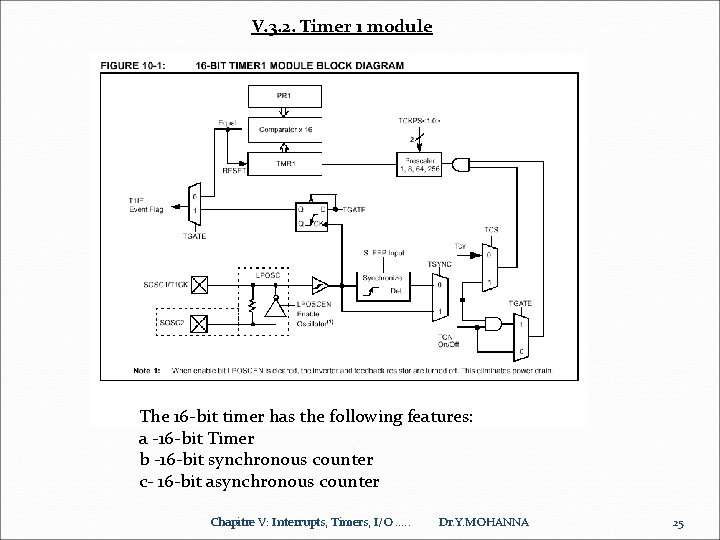

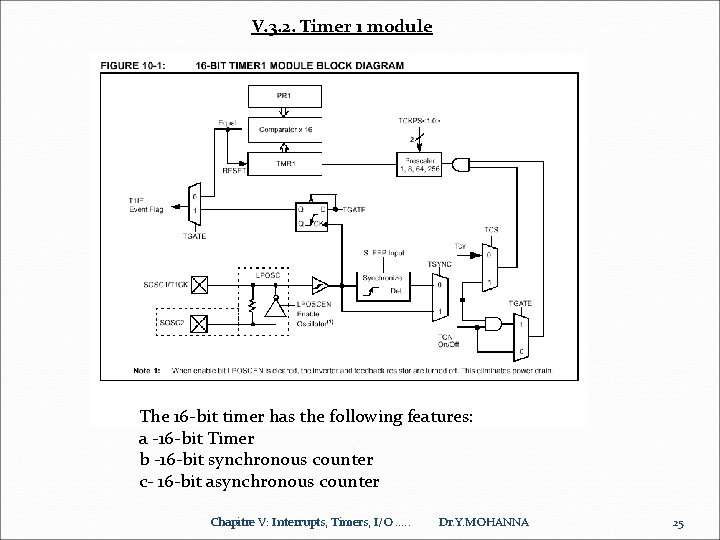

V. 3. 2. Timer 1 module The 16 -bit timer has the following features: a -16 -bit Timer b -16 -bit synchronous counter c- 16 -bit asynchronous counter Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 25

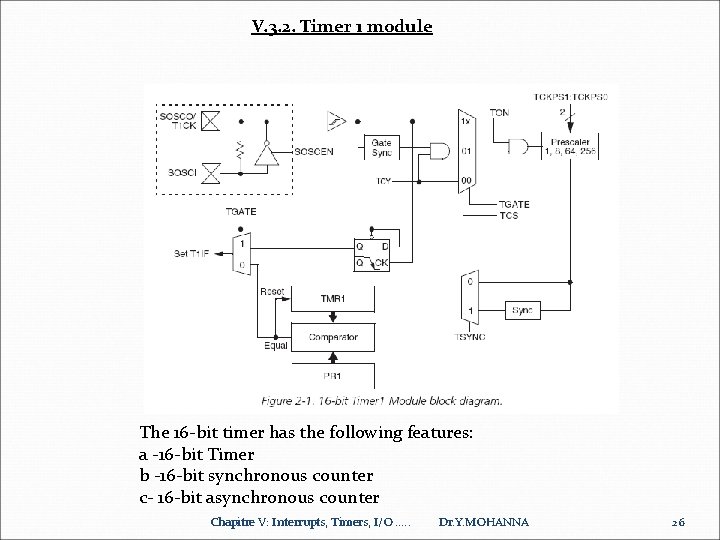

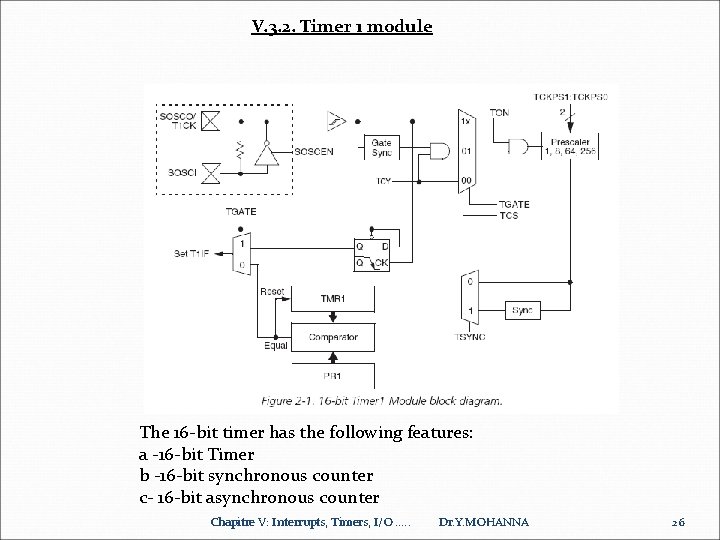

V. 3. 2. Timer 1 module The 16 -bit timer has the following features: a -16 -bit Timer b -16 -bit synchronous counter c- 16 -bit asynchronous counter Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 26

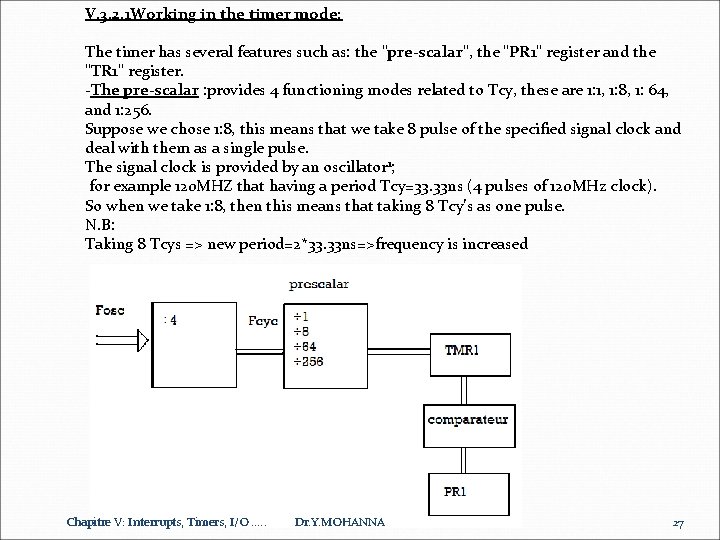

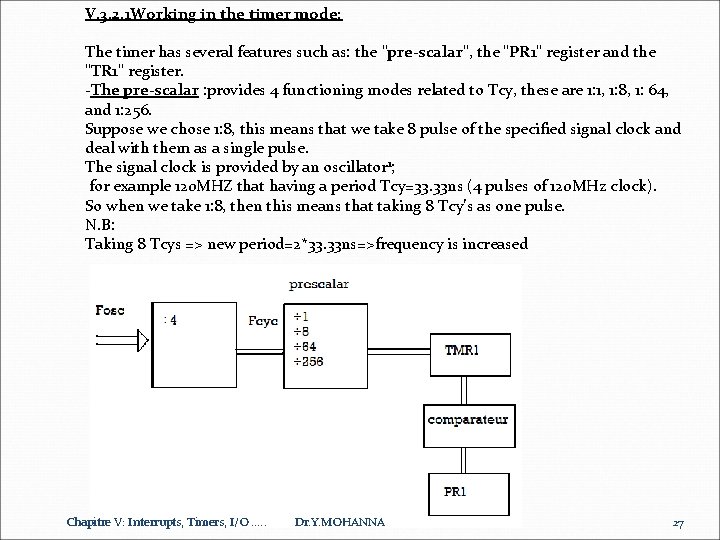

V. 3. 2. 1 Working in the timer mode: The timer has several features such as: the "pre-scalar", the "PR 1" register and the "TR 1" register. -The pre-scalar : provides 4 functioning modes related to Tcy, these are 1: 1, 1: 8, 1: 64, and 1: 256. Suppose we chose 1: 8, this means that we take 8 pulse of the specified signal clock and deal with them as a single pulse. The signal clock is provided by an oscillator 1; for example 120 MHZ that having a period Tcy=33. 33 ns (4 pulses of 120 MHz clock). So when we take 1: 8, then this means that taking 8 Tcy’s as one pulse. N. B: Taking 8 Tcys => new period=2*33. 33 ns=>frequency is increased Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 27

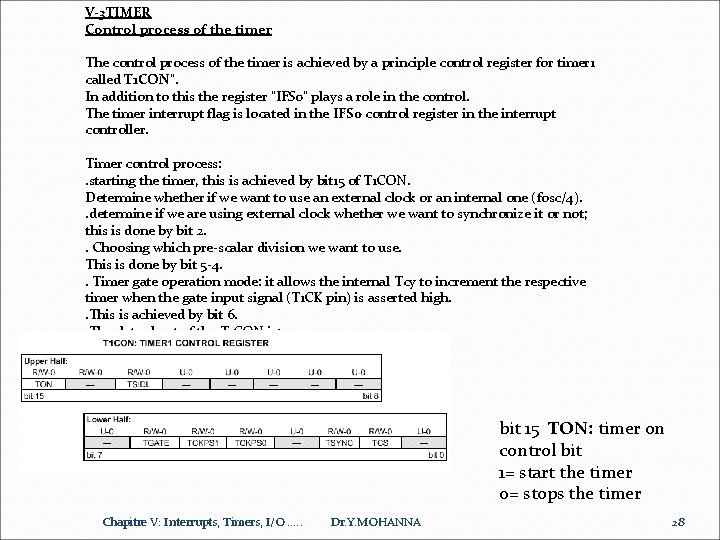

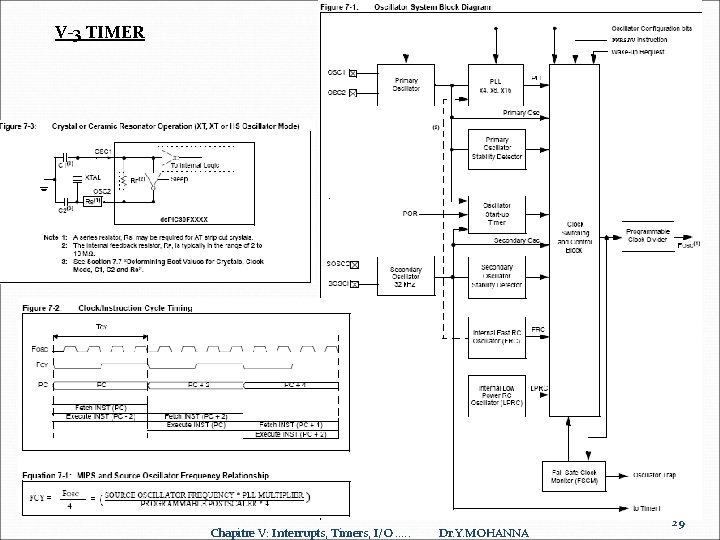

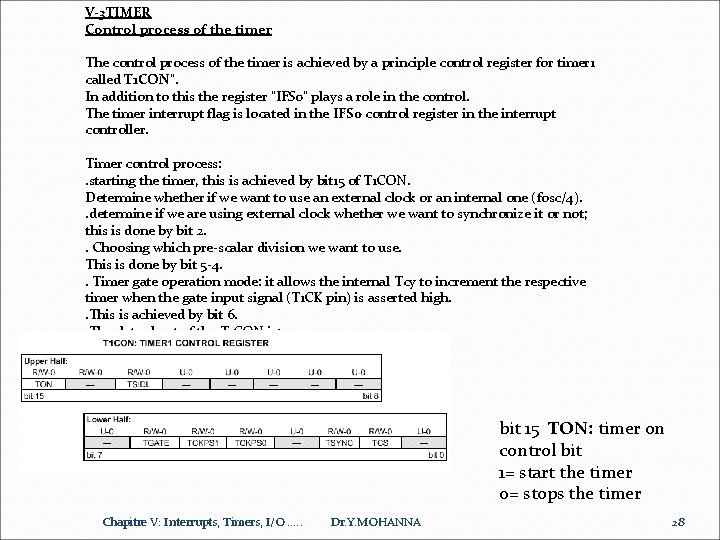

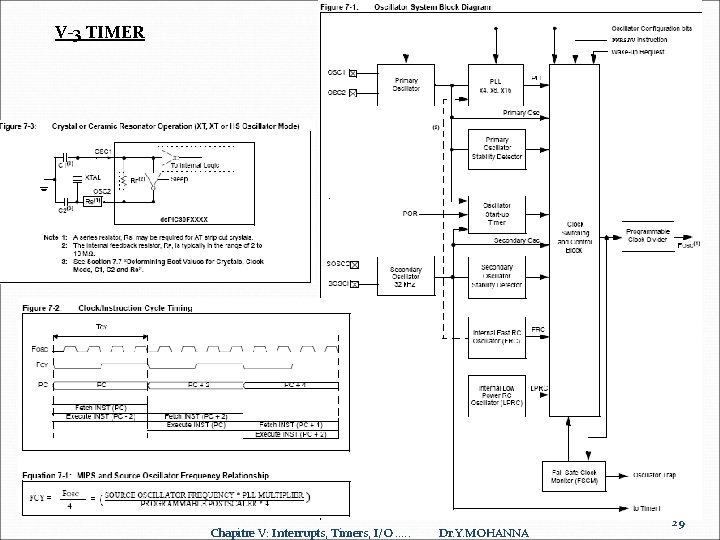

V-3 TIMER Control process of the timer The control process of the timer is achieved by a principle control register for timer 1 called T 1 CON". In addition to this the register "IFS 0" plays a role in the control. The timer interrupt flag is located in the IFS 0 control register in the interrupt controller. Timer control process: . starting the timer, this is achieved by bit 15 of T 1 CON. Determine whether if we want to use an external clock or an internal one (fosc/4). . determine if we are using external clock whether we want to synchronize it or not; this is done by bit 2. . Choosing which pre-scalar division we want to use. This is done by bit 5 -4. . Timer gate operation mode: it allows the internal Tcy to increment the respective timer when the gate input signal (T 1 CK pin) is asserted high. . This is achieved by bit 6. . The data sheet of the T 1 CON is: bit 15 TON: timer on control bit 1= start the timer 0= stops the timer Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 28

V-3 TIMER Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 29

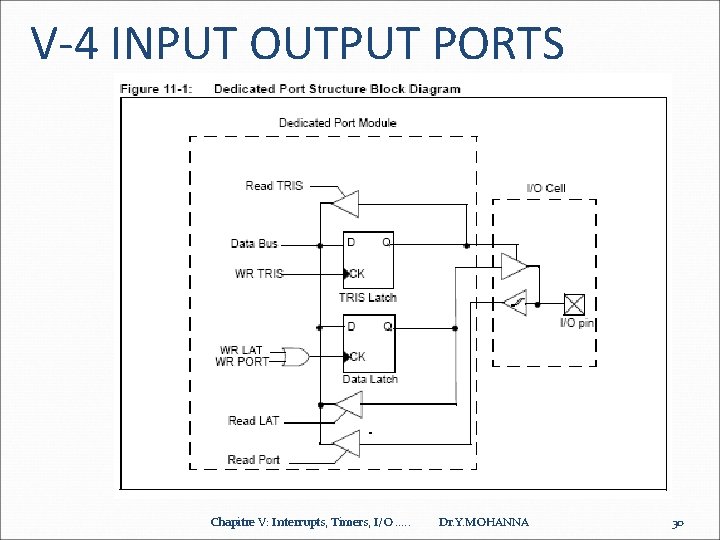

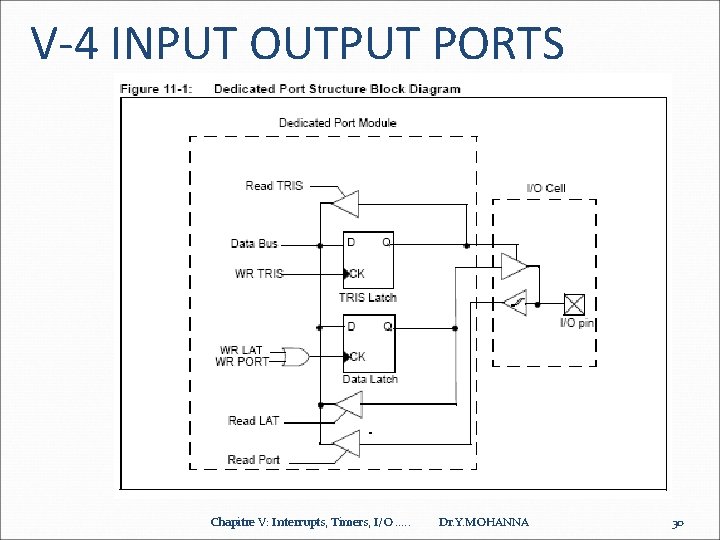

V-4 INPUT OUTPUT PORTS Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 30

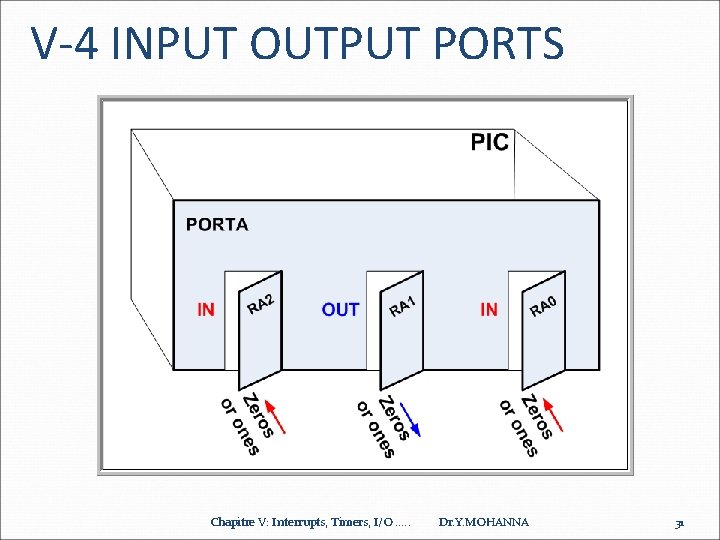

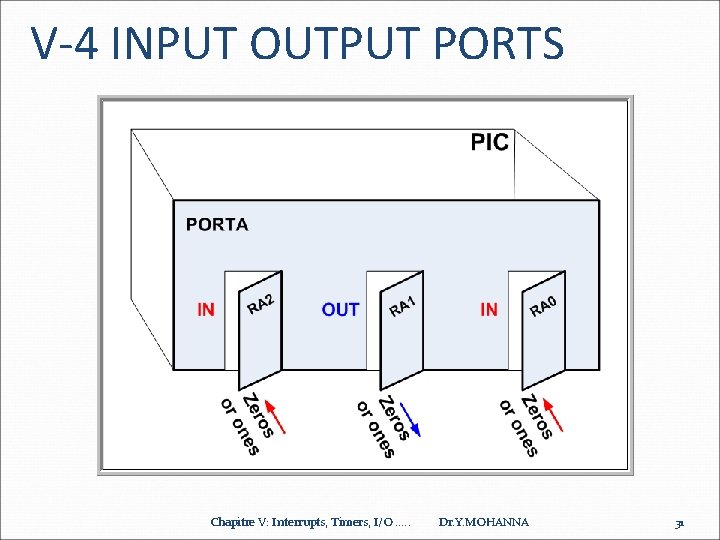

V-4 INPUT OUTPUT PORTS Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 31

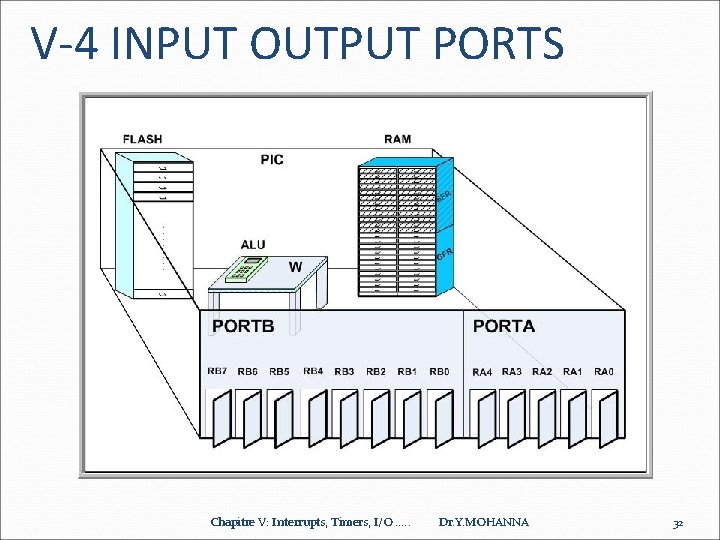

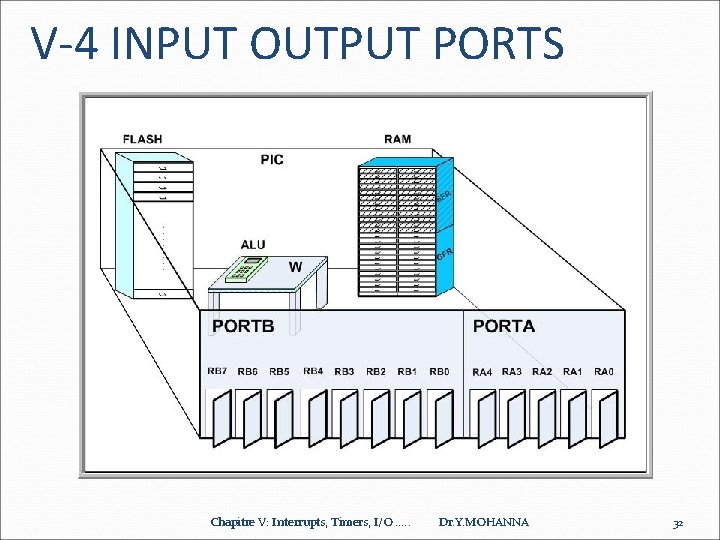

V-4 INPUT OUTPUT PORTS Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 32

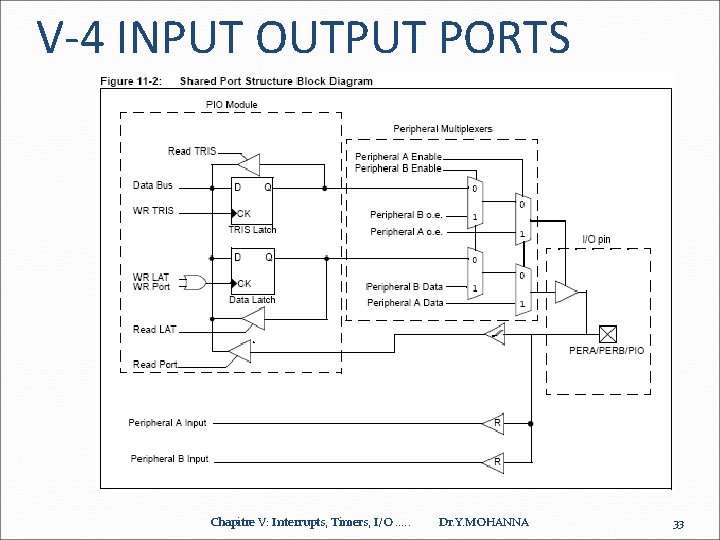

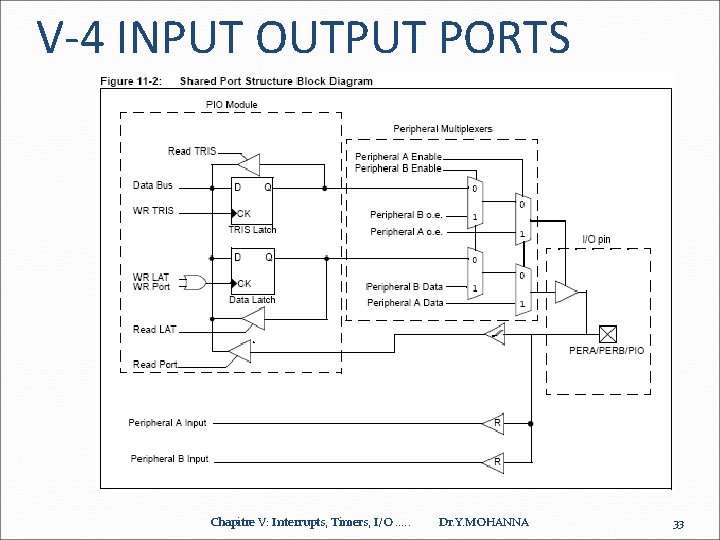

V-4 INPUT OUTPUT PORTS Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 33

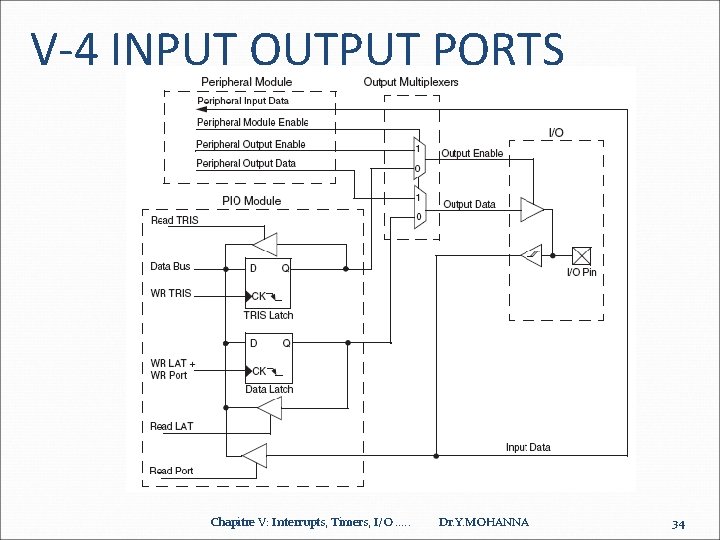

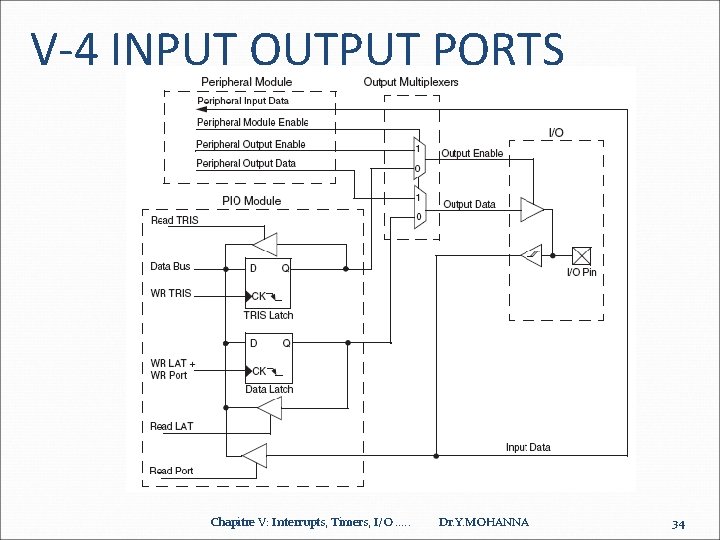

V-4 INPUT OUTPUT PORTS Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 34

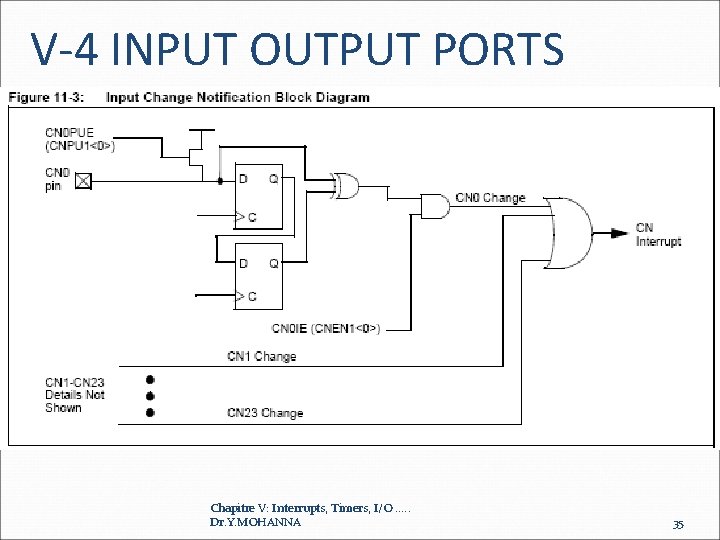

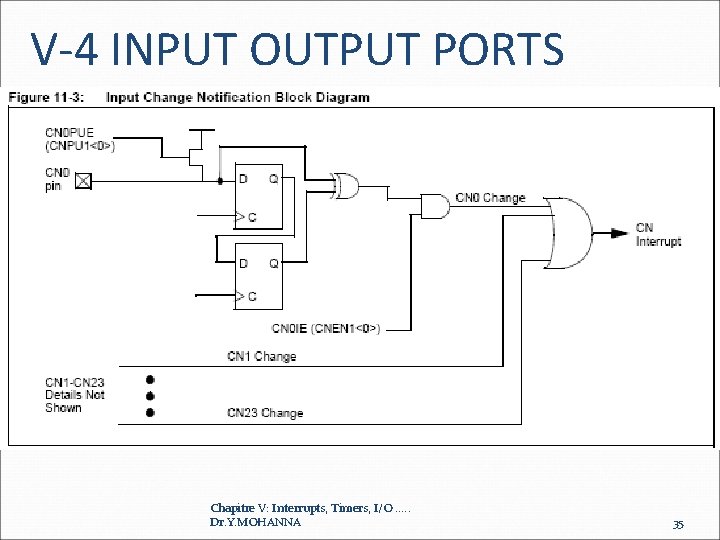

V-4 INPUT OUTPUT PORTS Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 35

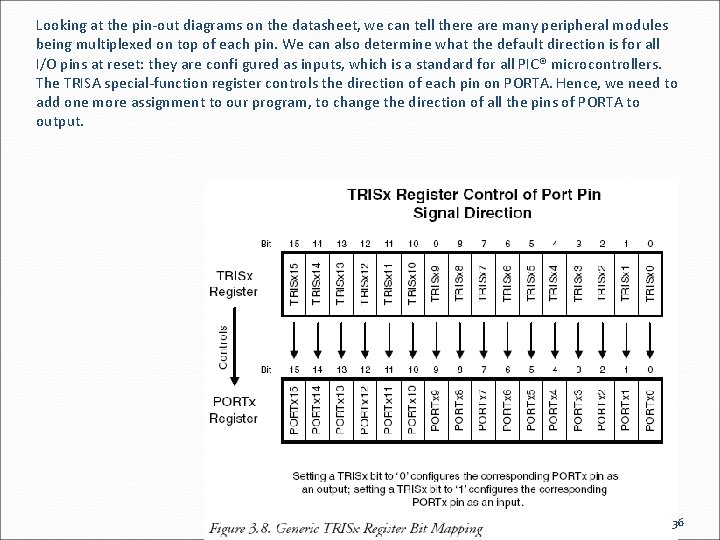

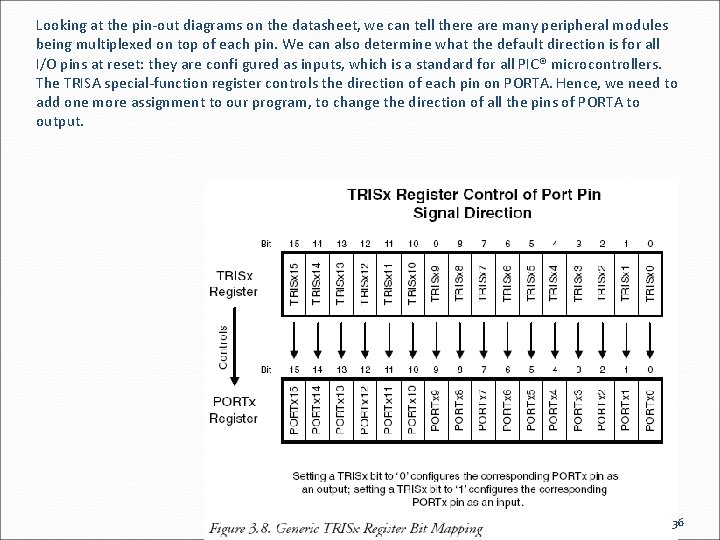

Looking at the pin-out diagrams on the datasheet, we can tell there are many peripheral modules being multiplexed on top of each pin. We can also determine what the default direction is for all I/O pins at reset: they are confi gured as inputs, which is a standard for all PIC® microcontrollers. The TRISA special-function register controls the direction of each pin on PORTA. Hence, we need to add one more assignment to our program, to change the direction of all the pins of PORTA to output. Chapitre V: Interrupts, Timers, I/O. . . Dr. Y. MOHANNA 36