Chapter Overview Modes of operation Intel Microprocessor early

- Slides: 26

Chapter Overview • Modes of operation • Intel Microprocessor early History • Registers ü General Purpose Registers 1. Data Registers 2. Pointer/Index/Base Registers ü Segment Registers ü Instruction Pointer ü Flag Registers ü Segment Registers • Floating-point unit • Intel Microprocessor history 1

The 8086/8088 Microprocessors: Registers • Registers are in the CPU and are referred to by specific names • High speed storage locations inside Microprocessor. • Categories of Registers ü General Purpose Registers 1. Data Registers 2. Pointer/Index/Base Registers ü Segment Registers ü Instruction Pointer ü Flags Pointer 2

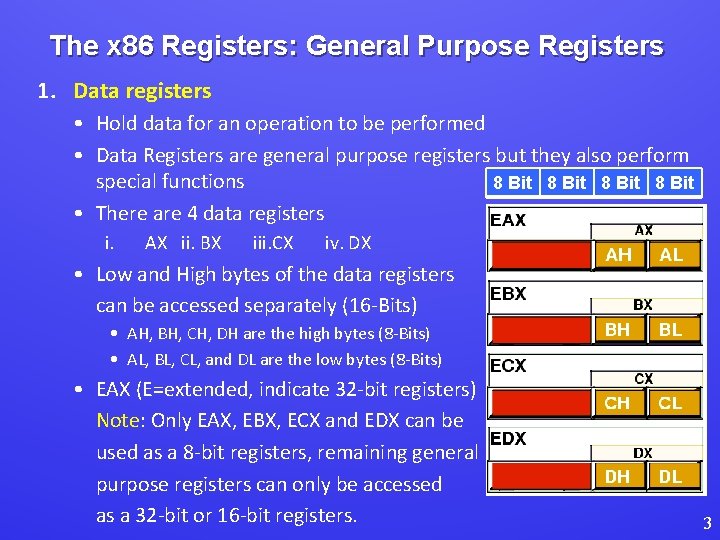

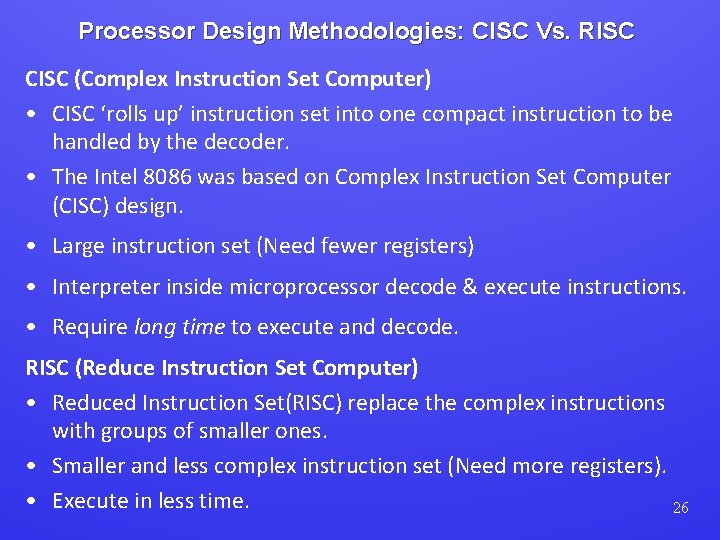

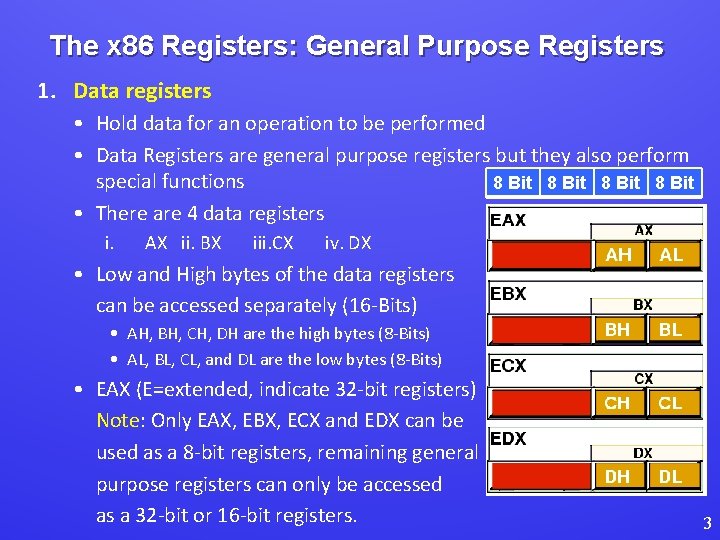

The x 86 Registers: General Purpose Registers 1. Data registers • Hold data for an operation to be performed • Data Registers are general purpose registers but they also perform special functions 8 Bit • There are 4 data registers i. AX ii. BX iii. CX iv. DX • Low and High bytes of the data registers can be accessed separately (16 -Bits) • AH, BH, CH, DH are the high bytes (8 -Bits) • AL, BL, CL, and DL are the low bytes (8 -Bits) • EAX (E=extended, indicate 32 -bit registers) Note: Only EAX, EBX, ECX and EDX can be used as a 8 -bit registers, remaining general purpose registers can only be accessed as a 32 -bit or 16 -bit registers. 3

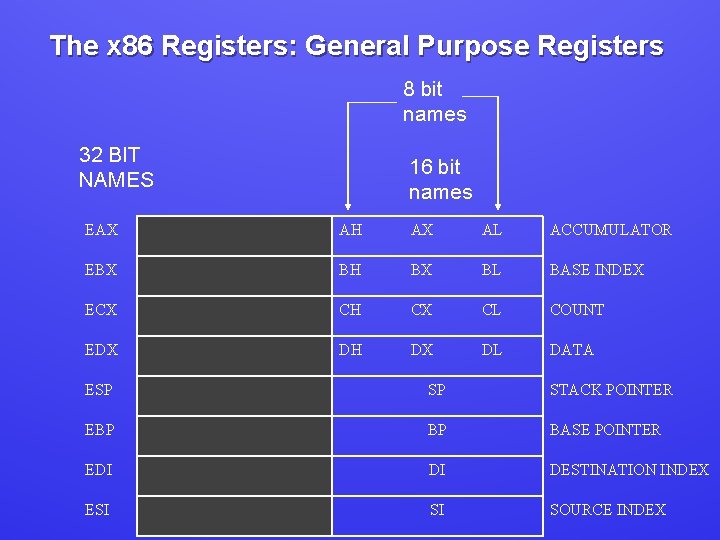

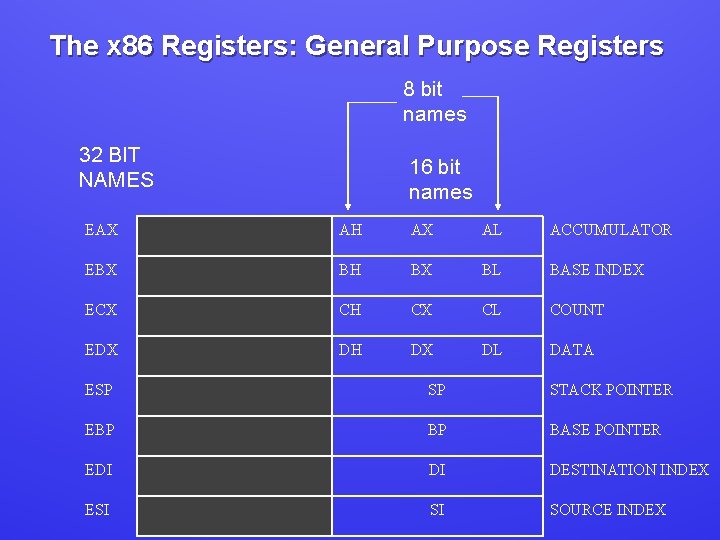

The x 86 Registers: General Purpose Registers 8 bit names 32 BIT NAMES 16 bit names EAX AH AX AL ACCUMULATOR EBX BH BX BL BASE INDEX ECX CH CX CL COUNT EDX DH DX DL DATA ESP SP STACK POINTER EBP BP BASE POINTER EDI DI DESTINATION INDEX ESI SI SOURCE INDEX

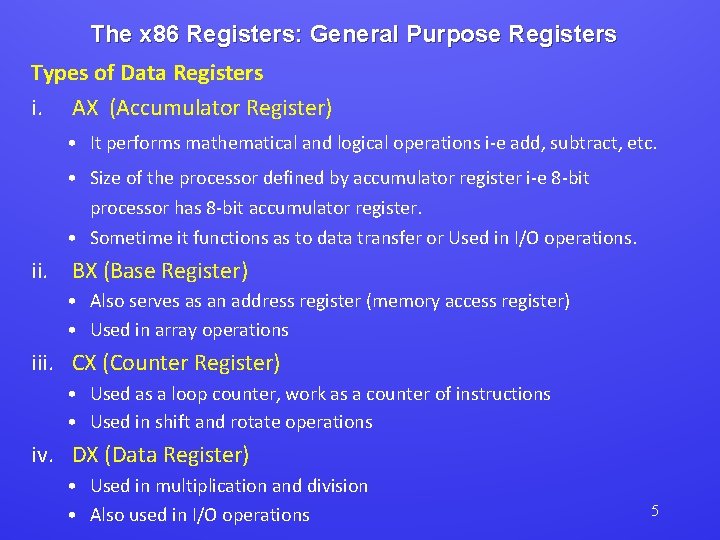

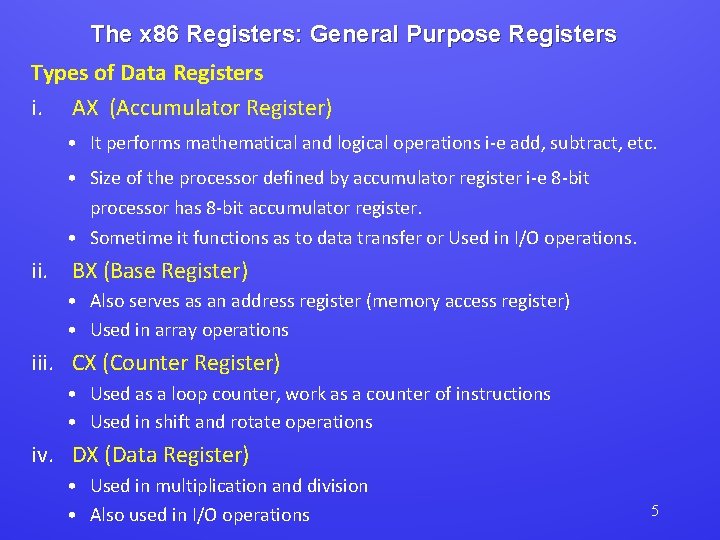

The x 86 Registers: General Purpose Registers Types of Data Registers i. AX (Accumulator Register) • It performs mathematical and logical operations i-e add, subtract, etc. • Size of the processor defined by accumulator register i-e 8 -bit processor has 8 -bit accumulator register. • Sometime it functions as to data transfer or Used in I/O operations. ii. BX (Base Register) • Also serves as an address register (memory access register) • Used in array operations iii. CX (Counter Register) • Used as a loop counter, work as a counter of instructions • Used in shift and rotate operations iv. DX (Data Register) • Used in multiplication and division • Also used in I/O operations 5

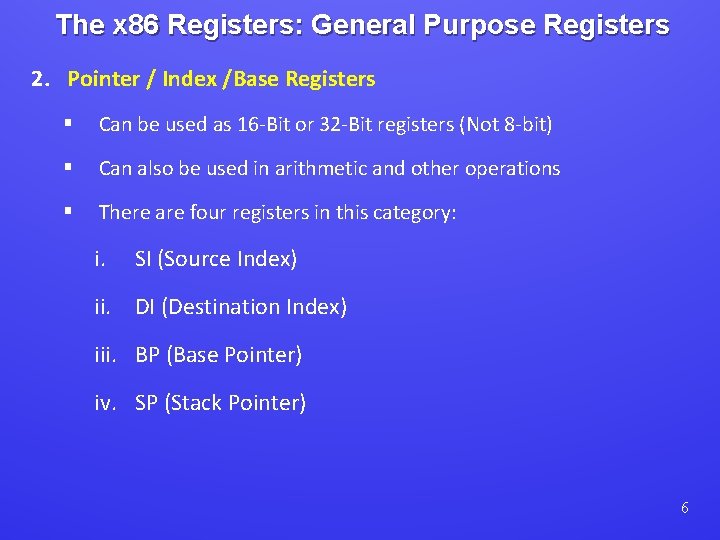

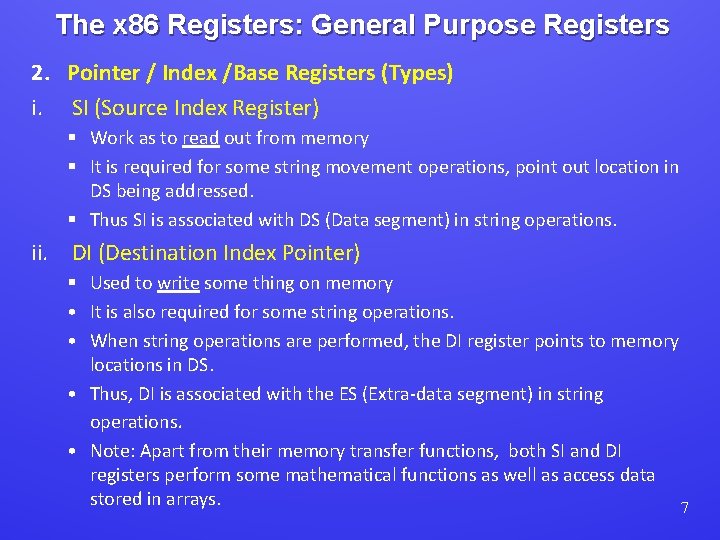

The x 86 Registers: General Purpose Registers 2. Pointer / Index /Base Registers § Can be used as 16 -Bit or 32 -Bit registers (Not 8 -bit) § Can also be used in arithmetic and other operations § There are four registers in this category: i. SI (Source Index) ii. DI (Destination Index) iii. BP (Base Pointer) iv. SP (Stack Pointer) 6

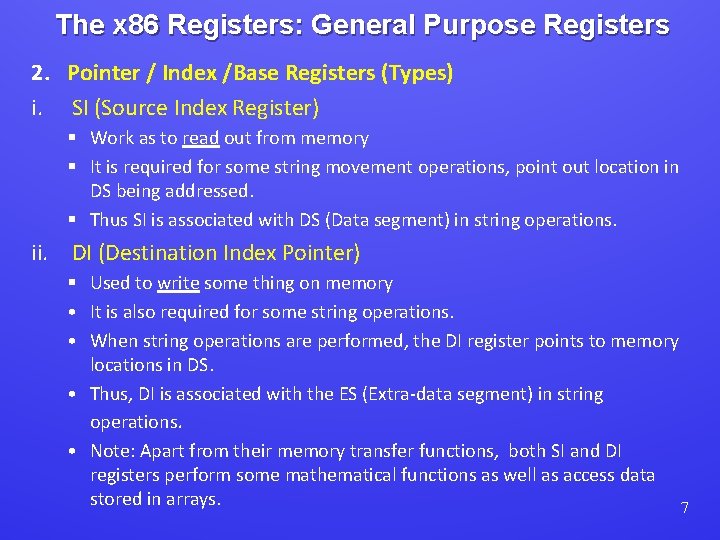

The x 86 Registers: General Purpose Registers 2. Pointer / Index /Base Registers (Types) i. SI (Source Index Register) § Work as to read out from memory § It is required for some string movement operations, point out location in DS being addressed. § Thus SI is associated with DS (Data segment) in string operations. ii. DI (Destination Index Pointer) § Used to write some thing on memory • It is also required for some string operations. • When string operations are performed, the DI register points to memory locations in DS. • Thus, DI is associated with the ES (Extra-data segment) in string operations. • Note: Apart from their memory transfer functions, both SI and DI registers perform some mathematical functions as well as access data stored in arrays. 7

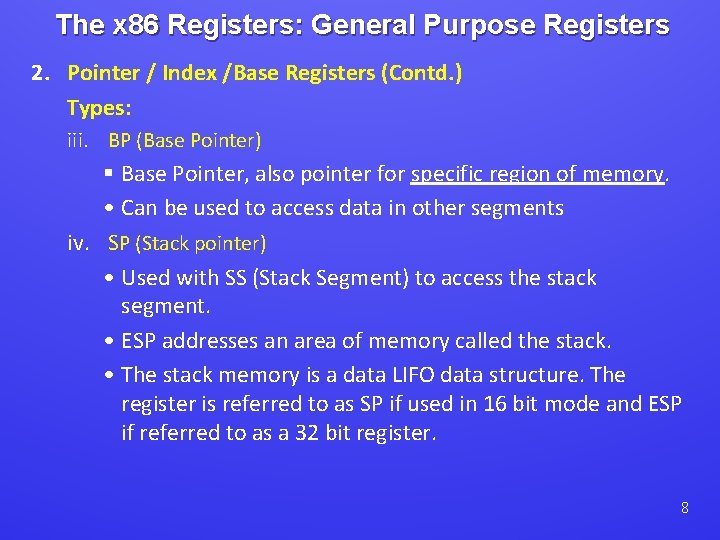

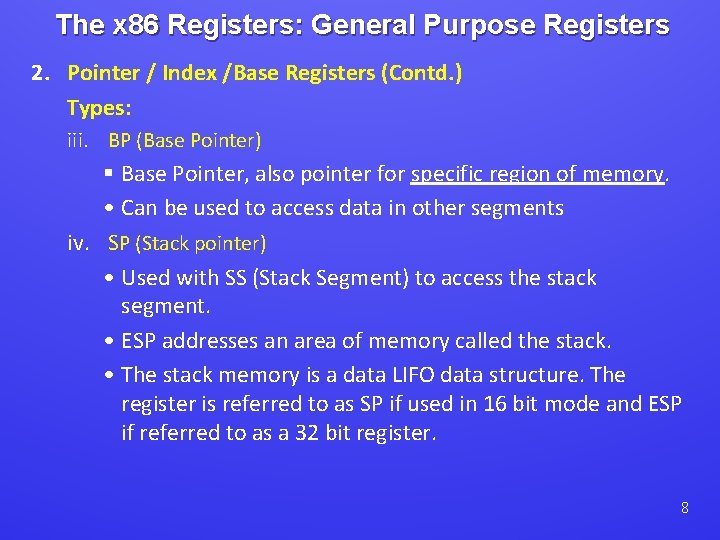

The x 86 Registers: General Purpose Registers 2. Pointer / Index /Base Registers (Contd. ) Types: iii. BP (Base Pointer) § Base Pointer, also pointer for specific region of memory. • Can be used to access data in other segments iv. SP (Stack pointer) • Used with SS (Stack Segment) to access the stack segment. • ESP addresses an area of memory called the stack. • The stack memory is a data LIFO data structure. The register is referred to as SP if used in 16 bit mode and ESP if referred to as a 32 bit register. 8

3. IP (Instruction Pointer) Register § Contains address of next instruction to be executed. § Not used for mathematical operations, very rare controlled by user. § Mostly controlled and used by microprocessor. 9

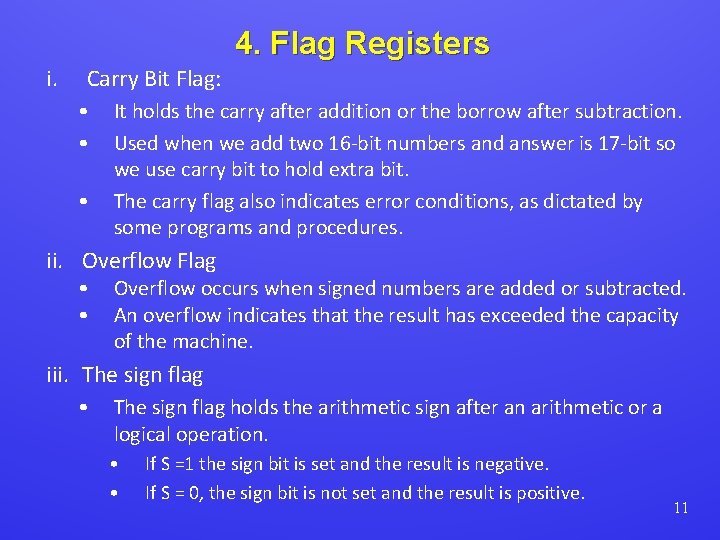

4. Flag Registers • Flags indicates the status of the microprocessor • Programs can set individual bits in the Flag registers to control CPU’s operations. • Example: • Interrupt when arithmetic overflow is detected, entering to protected mode, etc • There are two types of flags • Status Flags • Reflect the results of instructions that are executed (Zero Flag, Carry Flag, etc) • Control Flags • Are used to enable or to disable certain microprocessor operations (Interrupt Flag, Trap Flag) 10

4. Flag Registers i. Carry Bit Flag: • • • It holds the carry after addition or the borrow after subtraction. Used when we add two 16 -bit numbers and answer is 17 -bit so we use carry bit to hold extra bit. The carry flag also indicates error conditions, as dictated by some programs and procedures. ii. Overflow Flag • • Overflow occurs when signed numbers are added or subtracted. An overflow indicates that the result has exceeded the capacity of the machine. iii. The sign flag • The sign flag holds the arithmetic sign after an arithmetic or a logical operation. • • If S =1 the sign bit is set and the result is negative. If S = 0, the sign bit is not set and the result is positive. 11

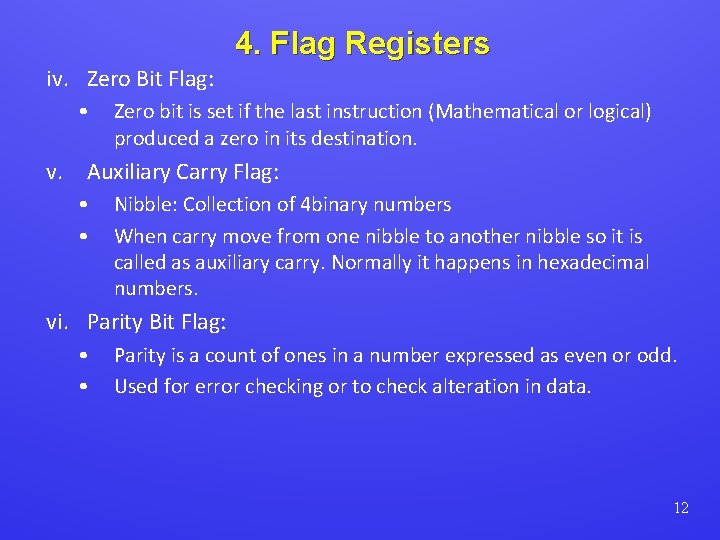

4. Flag Registers iv. Zero Bit Flag: • Zero bit is set if the last instruction (Mathematical or logical) produced a zero in its destination. v. Auxiliary Carry Flag: • • Nibble: Collection of 4 binary numbers When carry move from one nibble to another nibble so it is called as auxiliary carry. Normally it happens in hexadecimal numbers. vi. Parity Bit Flag: • • Parity is a count of ones in a number expressed as even or odd. Used for error checking or to check alteration in data. 12

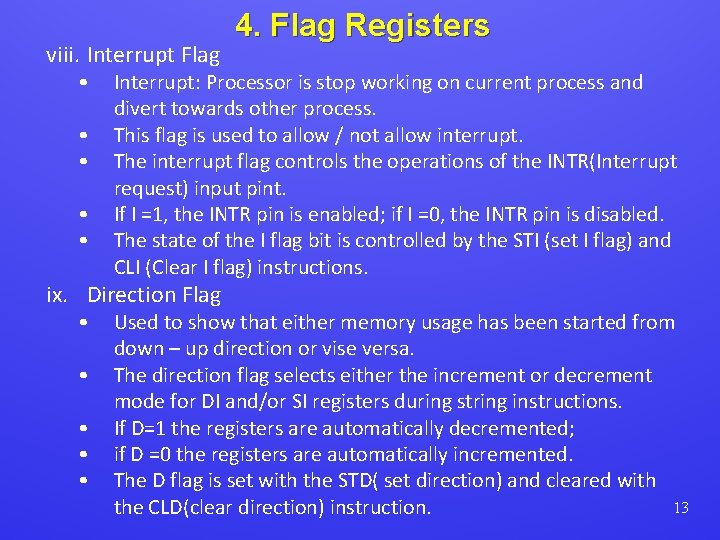

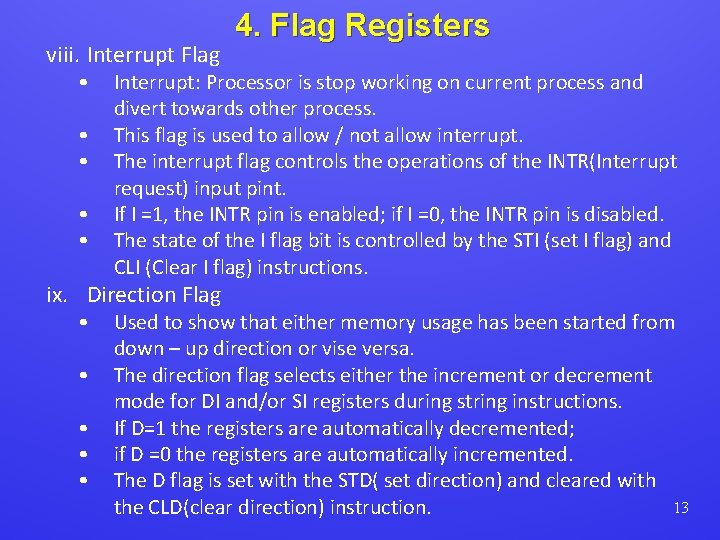

viii. Interrupt Flag • • • Interrupt: Processor is stop working on current process and divert towards other process. This flag is used to allow / not allow interrupt. The interrupt flag controls the operations of the INTR(Interrupt request) input pint. If I =1, the INTR pin is enabled; if I =0, the INTR pin is disabled. The state of the I flag bit is controlled by the STI (set I flag) and CLI (Clear I flag) instructions. ix. Direction Flag • • • 4. Flag Registers Used to show that either memory usage has been started from down – up direction or vise versa. The direction flag selects either the increment or decrement mode for DI and/or SI registers during string instructions. If D=1 the registers are automatically decremented; if D =0 the registers are automatically incremented. The D flag is set with the STD( set direction) and cleared with 13 the CLD(clear direction) instruction.

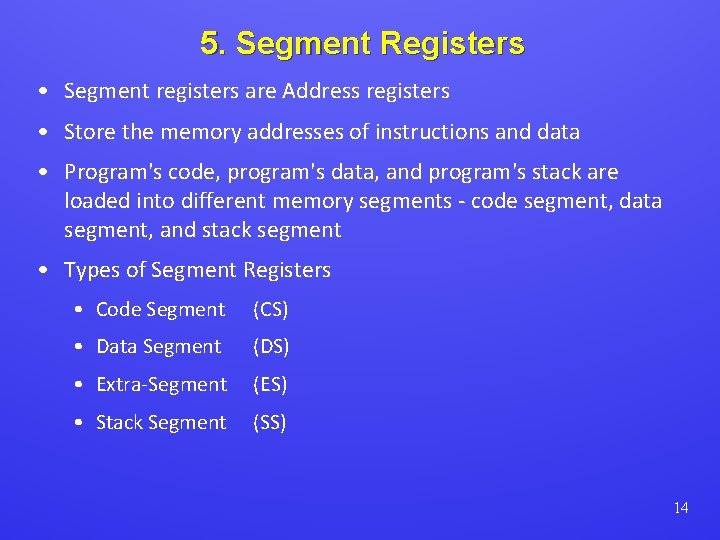

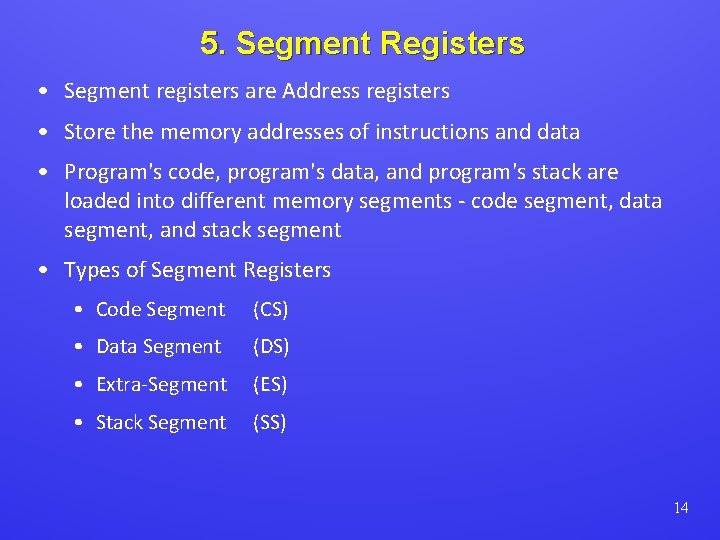

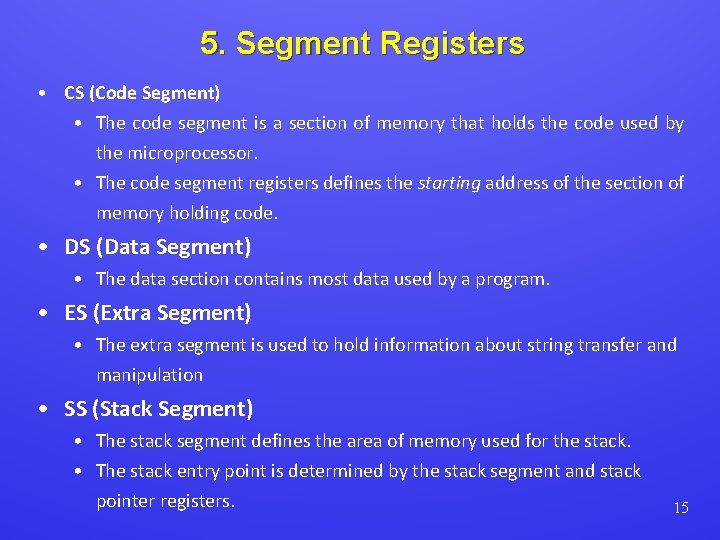

5. Segment Registers • Segment registers are Address registers • Store the memory addresses of instructions and data • Program's code, program's data, and program's stack are loaded into different memory segments - code segment, data segment, and stack segment • Types of Segment Registers • Code Segment (CS) • Data Segment (DS) • Extra-Segment (ES) • Stack Segment (SS) 14

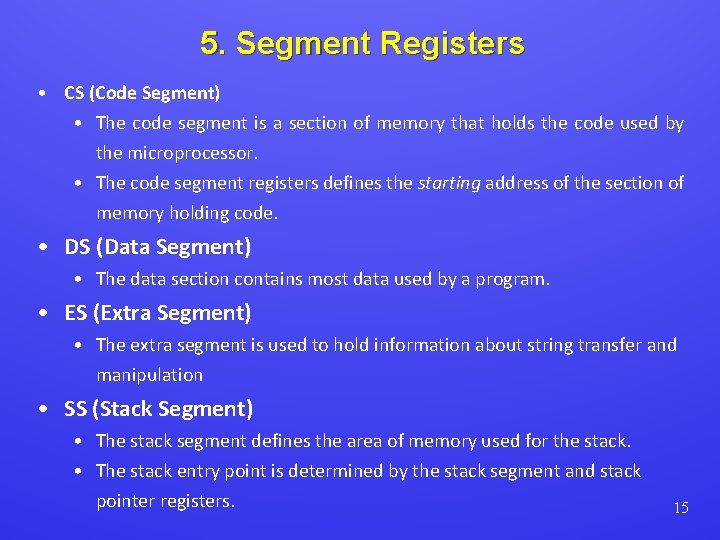

5. Segment Registers • CS (Code Segment) • The code segment is a section of memory that holds the code used by the microprocessor. • The code segment registers defines the starting address of the section of memory holding code. • DS (Data Segment) • The data section contains most data used by a program. • ES (Extra Segment) • The extra segment is used to hold information about string transfer and manipulation • SS (Stack Segment) • The stack segment defines the area of memory used for the stack. • The stack entry point is determined by the stack segment and stack pointer registers. 15

Chapter Overview • • Modes of operation Basic execution environment Floating-point unit Intel Microprocessor history 16

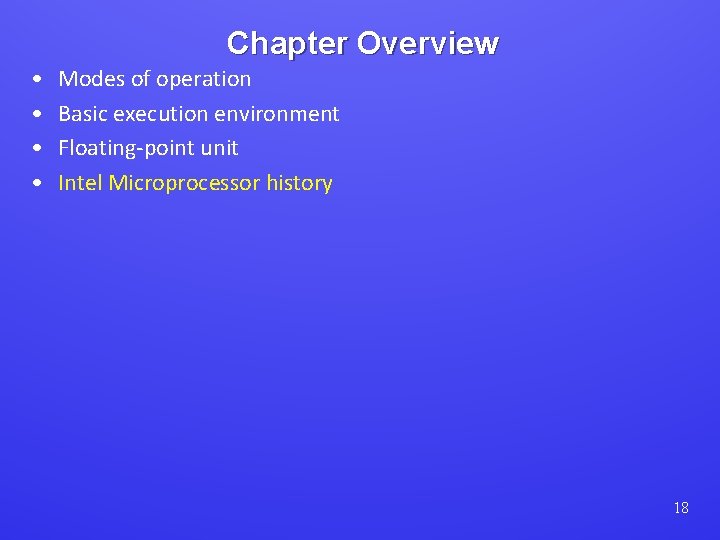

Floating Point Unit • The part of Microprocessor which perform high speed calculations of floating point values. • It was separate chip added to microprocessor, but from Intel 486 onwards, it is integrated into microprocessor. • There are eight floating point registers. • ST(0) ST(1) ST(2) ST(3) ST(4) ST(5) ST(6) ST(7) • Control and Pointer registers are also included. 17

Chapter Overview • • Modes of operation Basic execution environment Floating-point unit Intel Microprocessor history 18

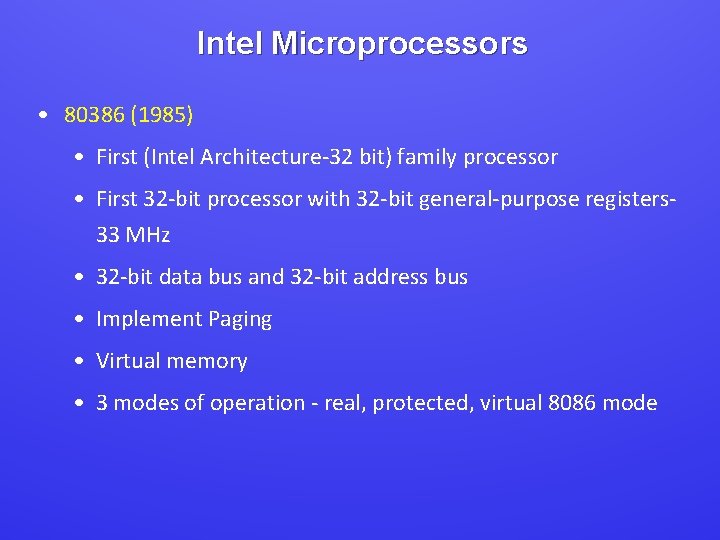

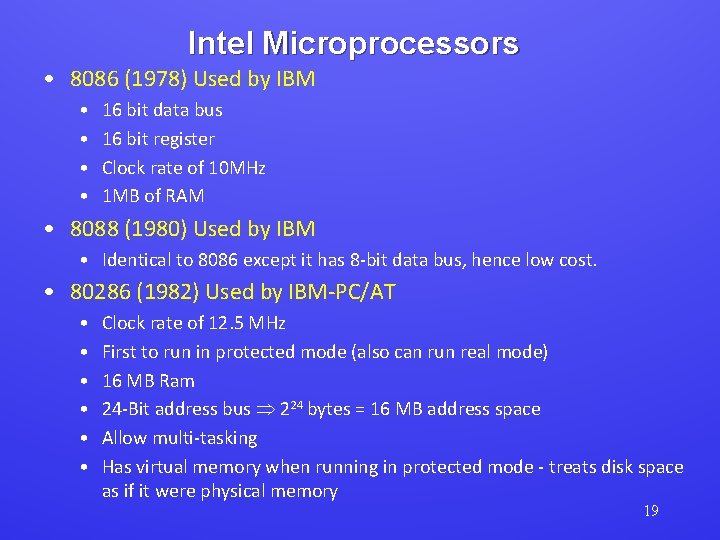

Intel Microprocessors • 8086 (1978) Used by IBM • • 16 bit data bus 16 bit register Clock rate of 10 MHz 1 MB of RAM • 8088 (1980) Used by IBM • Identical to 8086 except it has 8 -bit data bus, hence low cost. • 80286 (1982) Used by IBM-PC/AT • • • Clock rate of 12. 5 MHz First to run in protected mode (also can run real mode) 16 MB Ram 24 -Bit address bus 224 bytes = 16 MB address space Allow multi-tasking Has virtual memory when running in protected mode - treats disk space as if it were physical memory 19

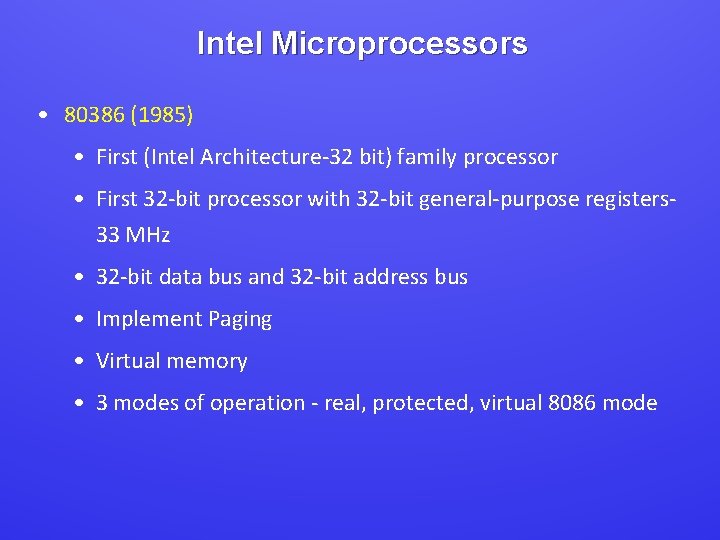

Intel Microprocessors • 80386 (1985) • First (Intel Architecture-32 bit) family processor • First 32 -bit processor with 32 -bit general-purpose registers 33 MHz • 32 -bit data bus and 32 -bit address bus • Implement Paging • Virtual memory • 3 modes of operation - real, protected, virtual 8086 mode

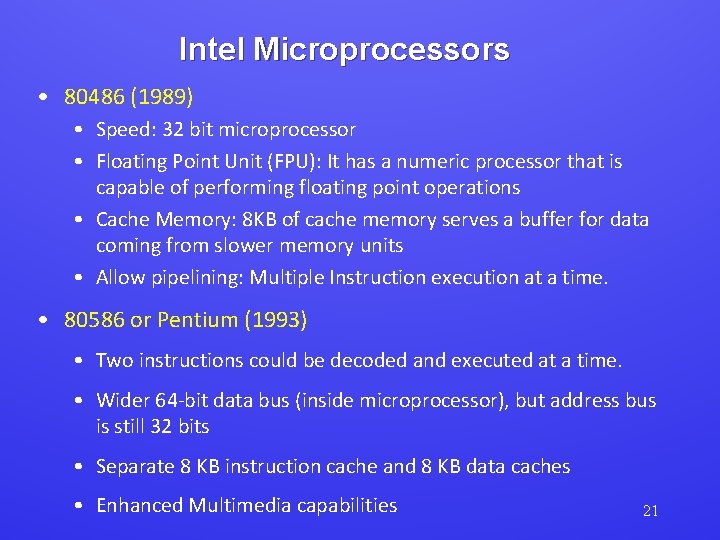

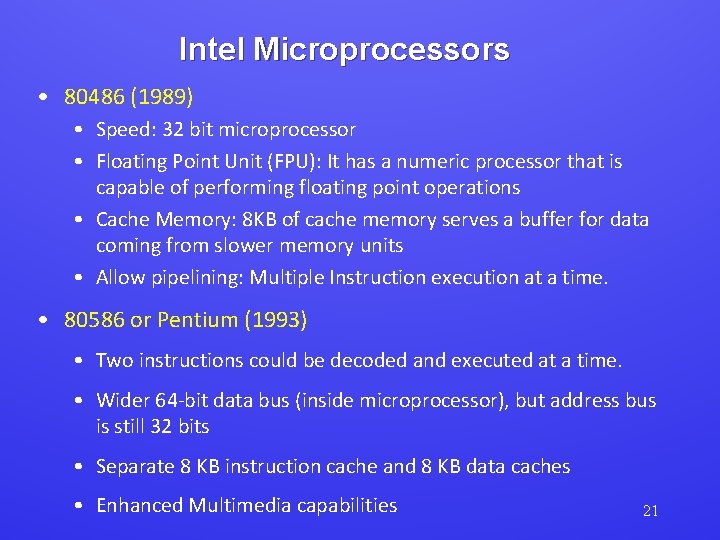

Intel Microprocessors • 80486 (1989) • Speed: 32 bit microprocessor • Floating Point Unit (FPU): It has a numeric processor that is capable of performing floating point operations • Cache Memory: 8 KB of cache memory serves a buffer for data coming from slower memory units • Allow pipelining: Multiple Instruction execution at a time. • 80586 or Pentium (1993) • Two instructions could be decoded and executed at a time. • Wider 64 -bit data bus (inside microprocessor), but address bus is still 32 bits • Separate 8 KB instruction cache and 8 KB data caches • Enhanced Multimedia capabilities 21

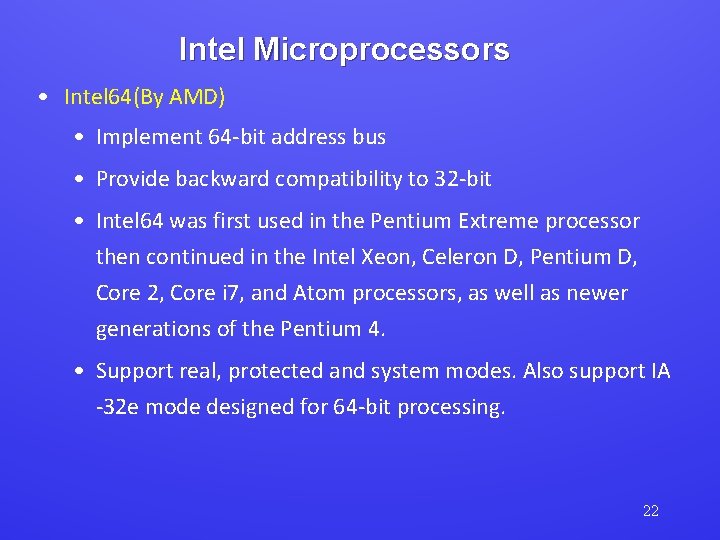

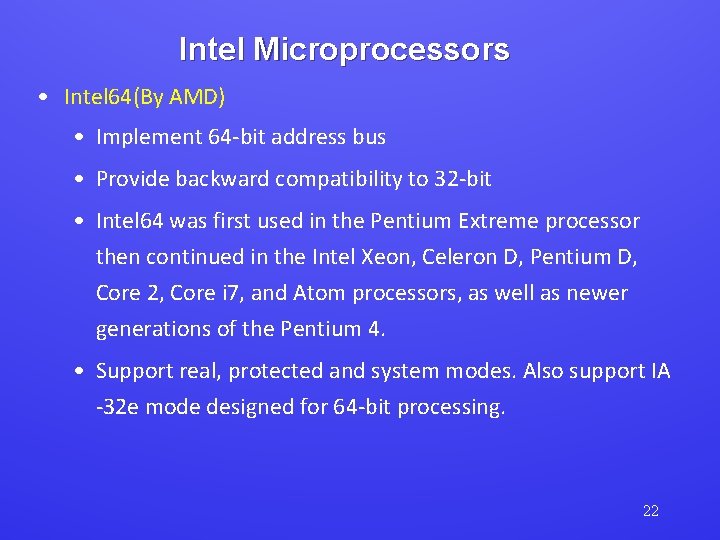

Intel Microprocessors • Intel 64(By AMD) • Implement 64 -bit address bus • Provide backward compatibility to 32 -bit • Intel 64 was first used in the Pentium Extreme processor then continued in the Intel Xeon, Celeron D, Pentium D, Core 2, Core i 7, and Atom processors, as well as newer generations of the Pentium 4. • Support real, protected and system modes. Also support IA -32 e mode designed for 64 -bit processing. 22

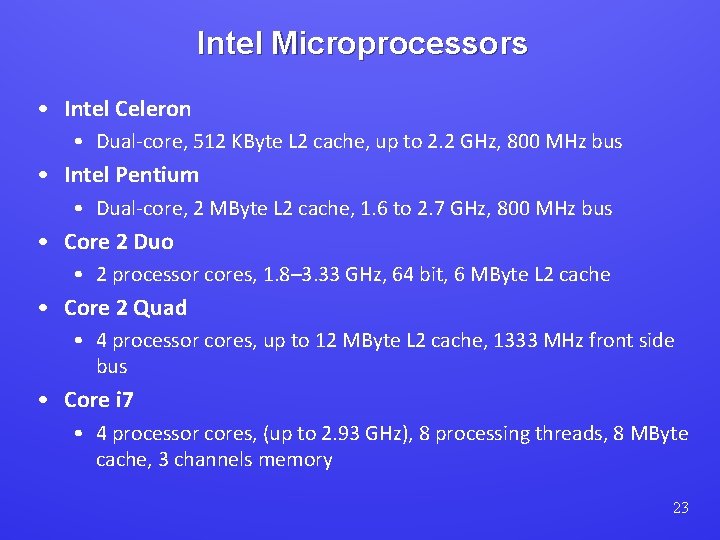

Intel Microprocessors • Intel Celeron • Dual-core, 512 KByte L 2 cache, up to 2. 2 GHz, 800 MHz bus • Intel Pentium • Dual-core, 2 MByte L 2 cache, 1. 6 to 2. 7 GHz, 800 MHz bus • Core 2 Duo • 2 processor cores, 1. 8– 3. 33 GHz, 64 bit, 6 MByte L 2 cache • Core 2 Quad • 4 processor cores, up to 12 MByte L 2 cache, 1333 MHz front side bus • Core i 7 • 4 processor cores, (up to 2. 93 GHz), 8 processing threads, 8 MByte cache, 3 channels memory 23

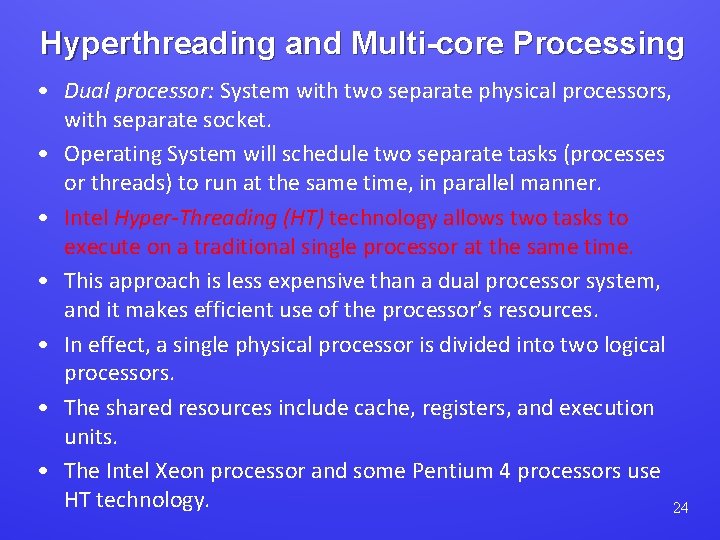

Hyperthreading and Multi-core Processing • Dual processor: System with two separate physical processors, with separate socket. • Operating System will schedule two separate tasks (processes or threads) to run at the same time, in parallel manner. • Intel Hyper-Threading (HT) technology allows two tasks to execute on a traditional single processor at the same time. • This approach is less expensive than a dual processor system, and it makes efficient use of the processor’s resources. • In effect, a single physical processor is divided into two logical processors. • The shared resources include cache, registers, and execution units. • The Intel Xeon processor and some Pentium 4 processors use HT technology. 24

Hyperthreading and Multi-core Processing • The term Dual Core refers to integrated circuit (IC) chips that contain two complete physical computer processor chips in the same IC package. • Each processor has its own resources, and each has its own communication path to the computer system’s bus. • Sometimes, dual-core processors also incorporate HT technology, causing them to appear as four logical processors, running four tasks simultaneously. 25

Processor Design Methodologies: CISC Vs. RISC CISC (Complex Instruction Set Computer) • CISC ‘rolls up’ instruction set into one compact instruction to be handled by the decoder. • The Intel 8086 was based on Complex Instruction Set Computer (CISC) design. • Large instruction set (Need fewer registers) • Interpreter inside microprocessor decode & execute instructions. • Require long time to execute and decode. RISC (Reduce Instruction Set Computer) • Reduced Instruction Set(RISC) replace the complex instructions with groups of smaller ones. • Smaller and less complex instruction set (Need more registers). • Execute in less time. 26