Chapter Five The Processor Datapath and Control Parte

- Slides: 12

Chapter Five The Processor: Datapath and Control (Parte C: microprogramação) Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-1

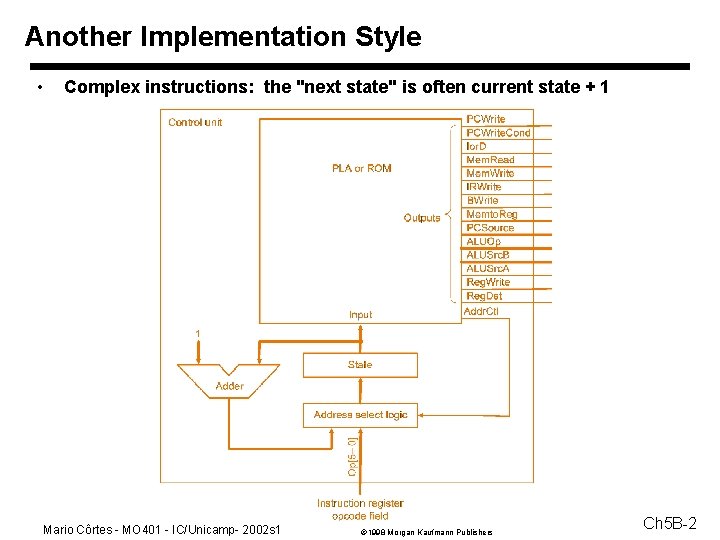

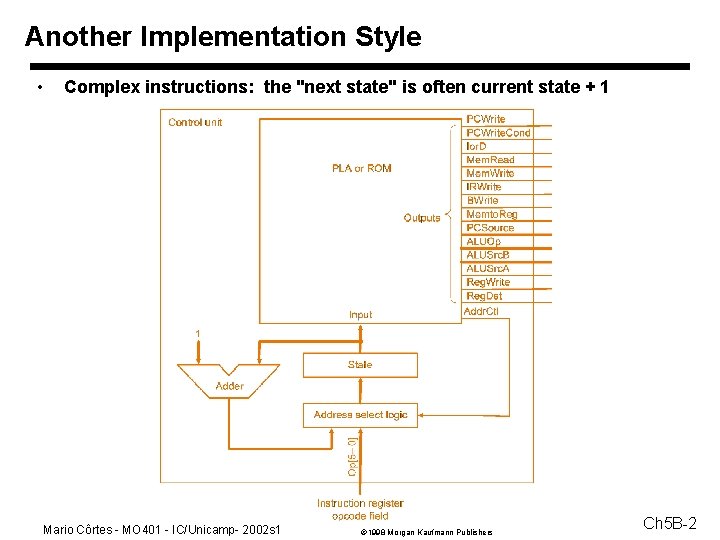

Another Implementation Style • Complex instructions: the "next state" is often current state + 1 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-2

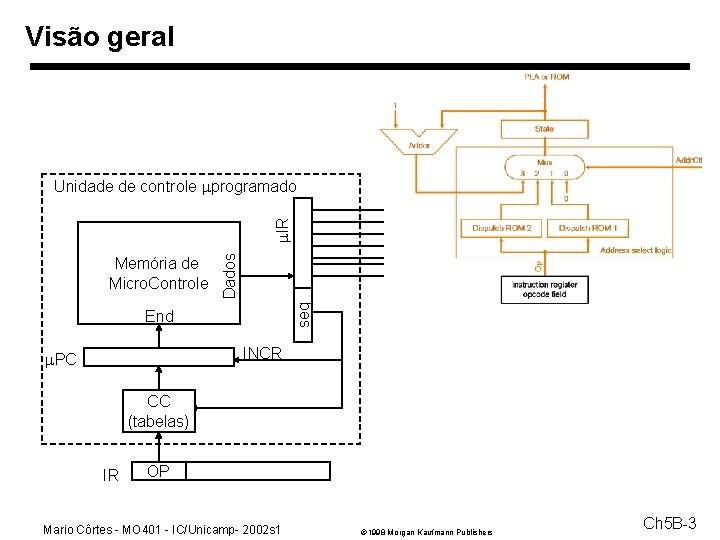

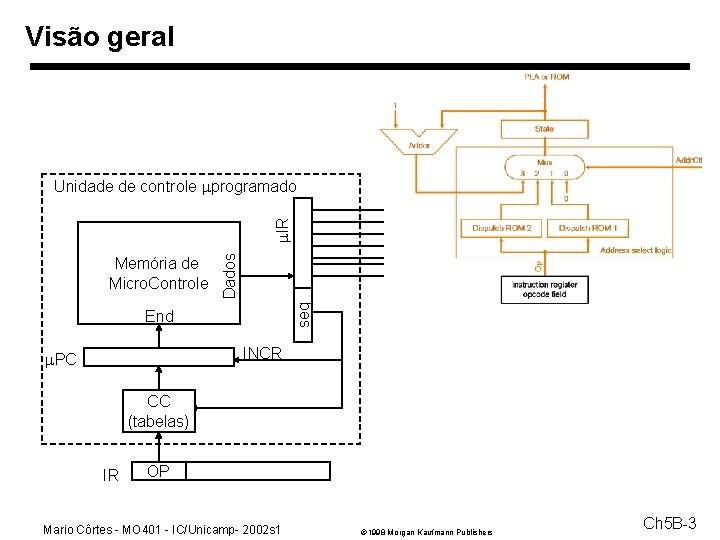

Visão geral seq Memória de Micro. Controle Dados m. IR Unidade de controle mprogramado End INCR m. PC CC (tabelas) IR OP Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-3

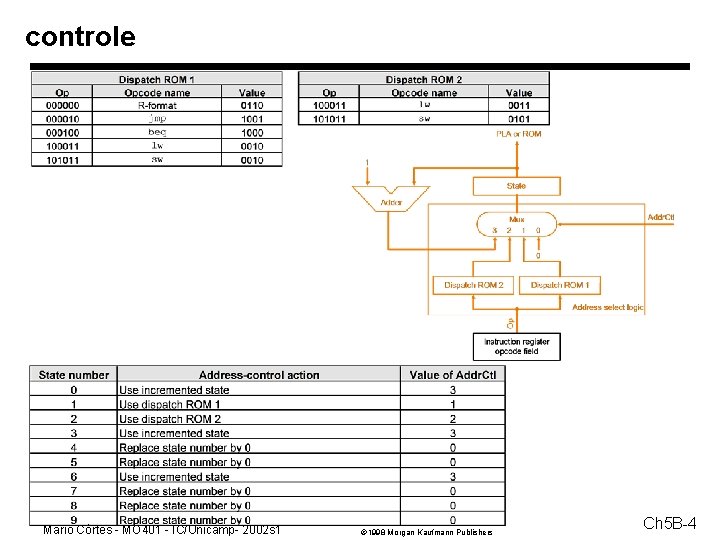

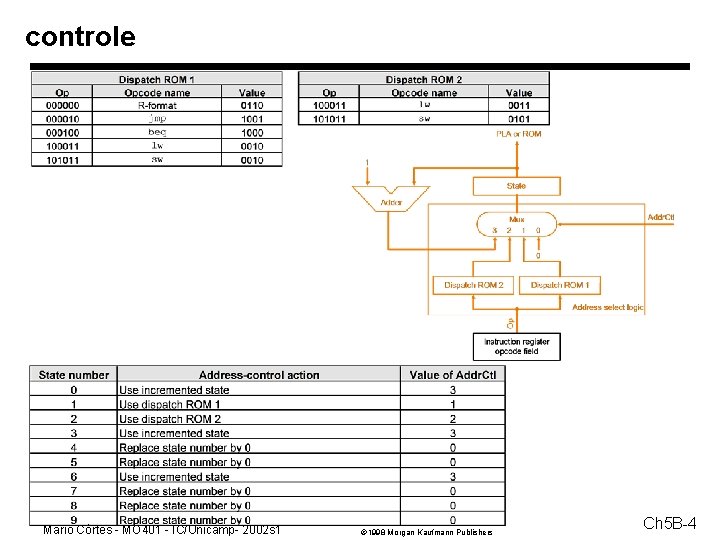

controle Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-4

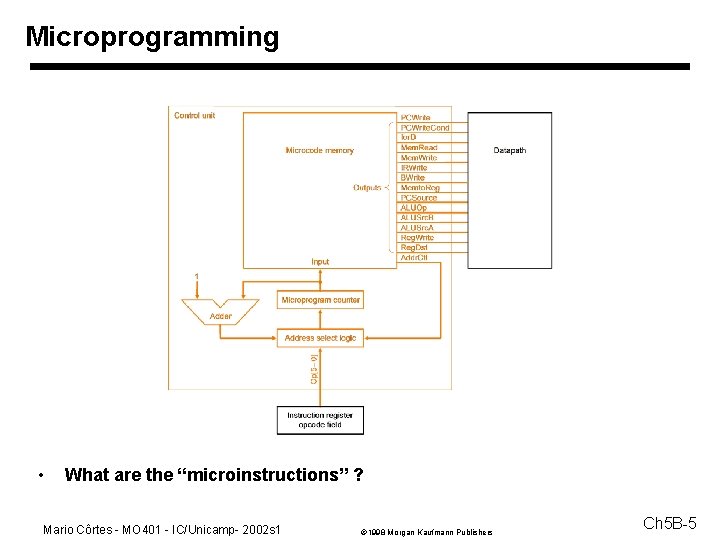

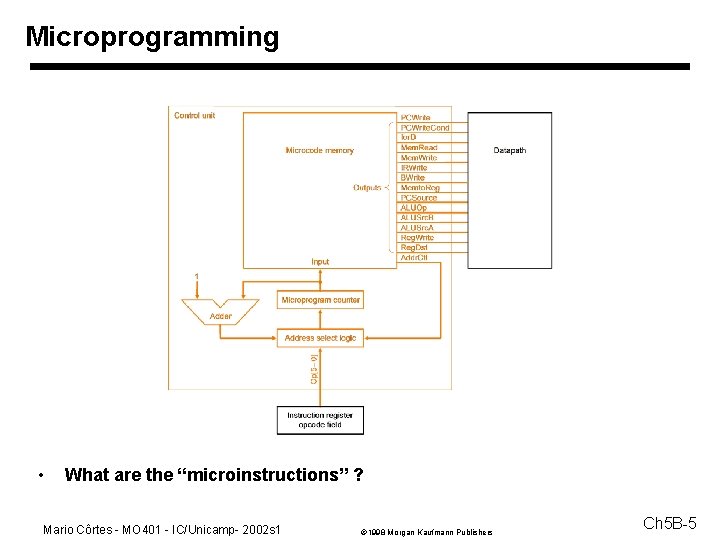

Microprogramming • What are the “microinstructions” ? Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-5

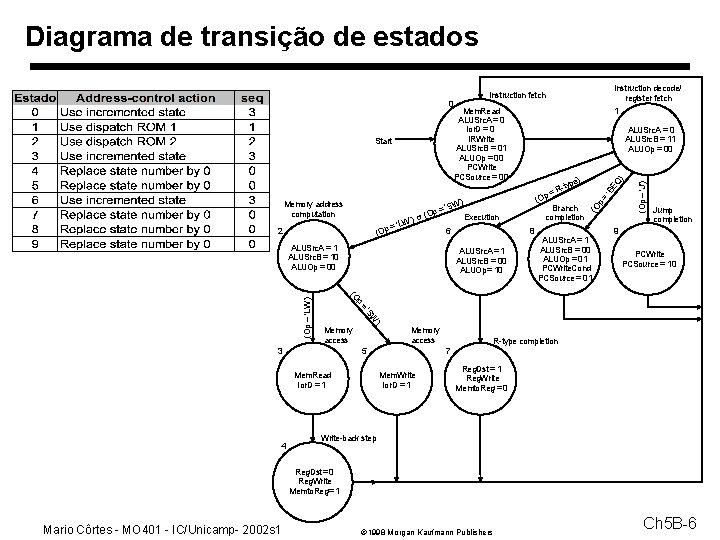

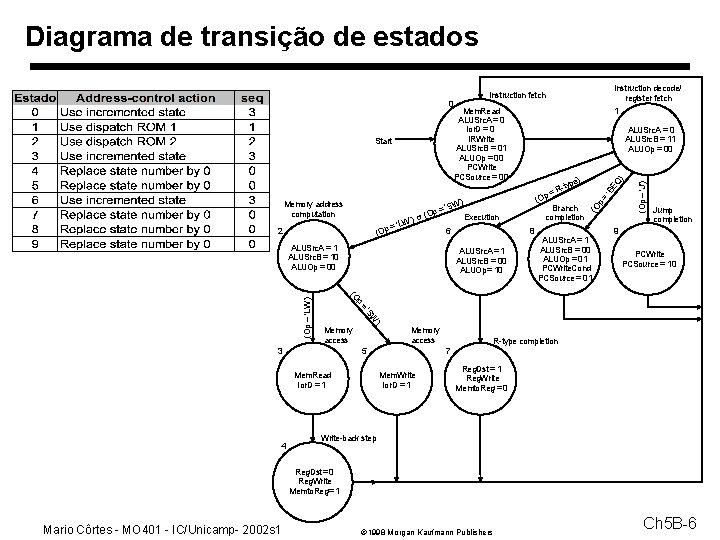

Diagrama de transição de estados 2 ALUSrc. A =1 ALUSrc. B = 00 ALUOp= 10 ') W 'S Memory access 3 Memory access 5 Mem. Read Ior. D = 1 4 (Op e) -typ R = Branch completion 8 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCWrite. Cond PCSource = 01 Jump completion 9 PCWrite PCSource = 10 p= (O (Op = 'LW') ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 (Op = 'J') ') 'SW p= O ( r Execution o W') = 'L 6 (Op Memory address computation 1 'BE Q' ) Start Mem. Read ALUSrc. A = 0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSource = 00 (O p= 0 Instruction decode/ register fetch Instruction fetch R-type completion 7 Mem. Write Ior. D = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 Write-back step Reg. Dst=0 Reg. Write Memto. Reg=1 Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-6

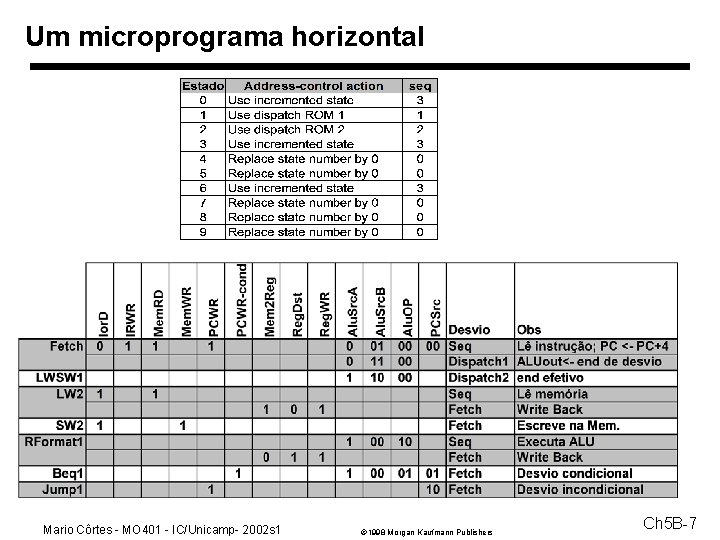

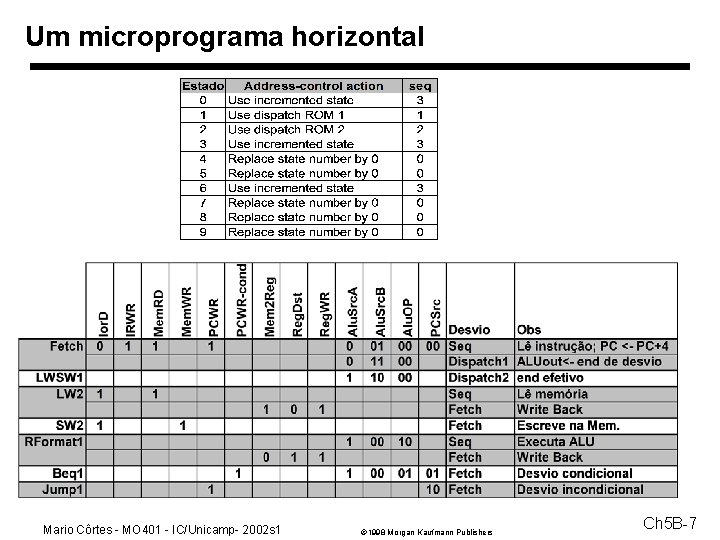

Um microprograma horizontal Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-7

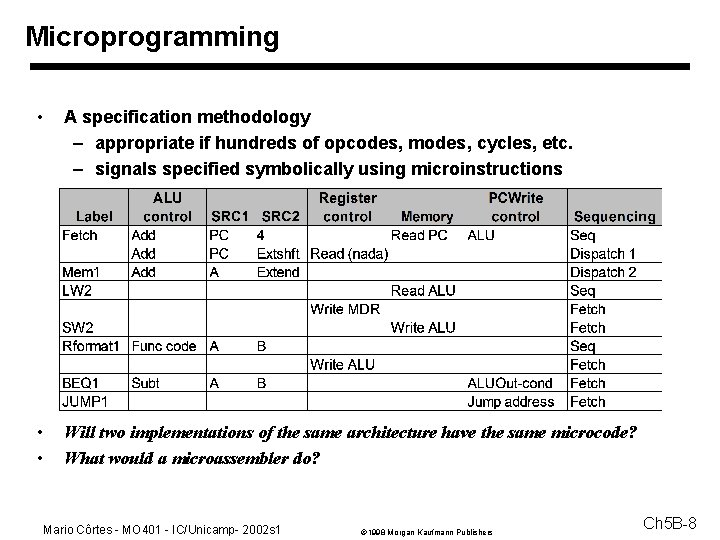

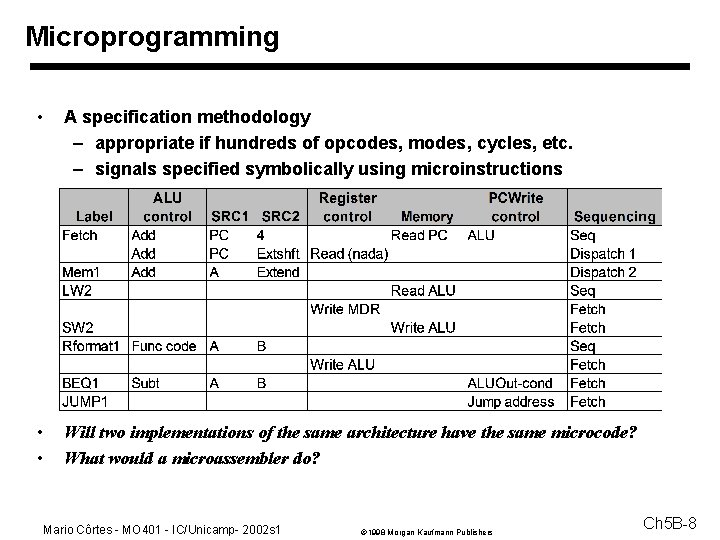

Microprogramming • A specification methodology – appropriate if hundreds of opcodes, modes, cycles, etc. – signals specified symbolically using microinstructions • • Will two implementations of the same architecture have the same microcode? What would a microassembler do? Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-8

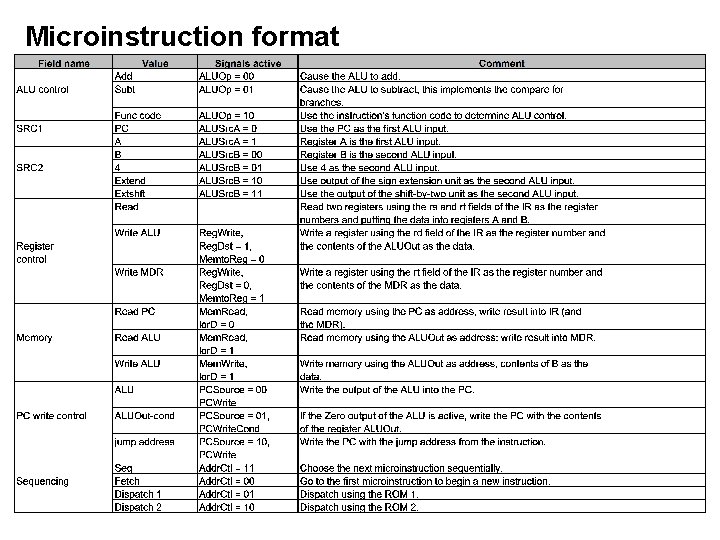

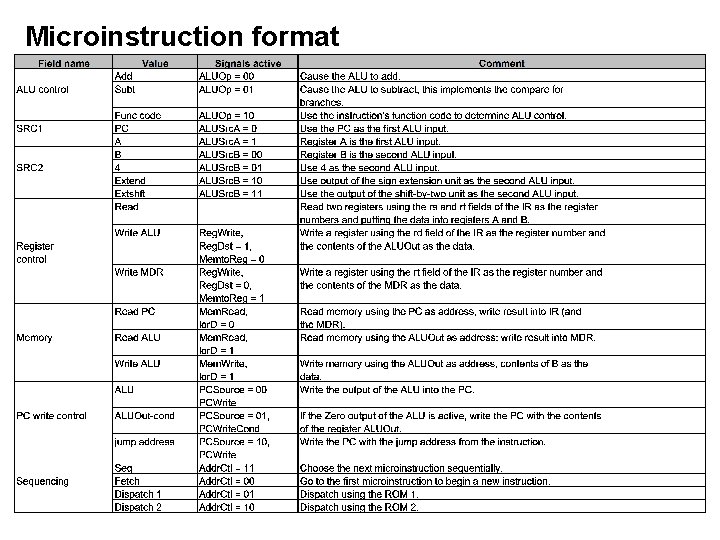

Microinstruction format

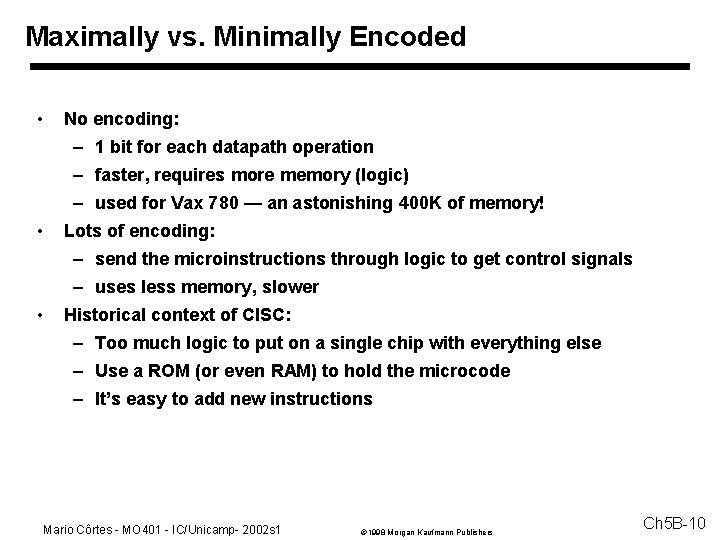

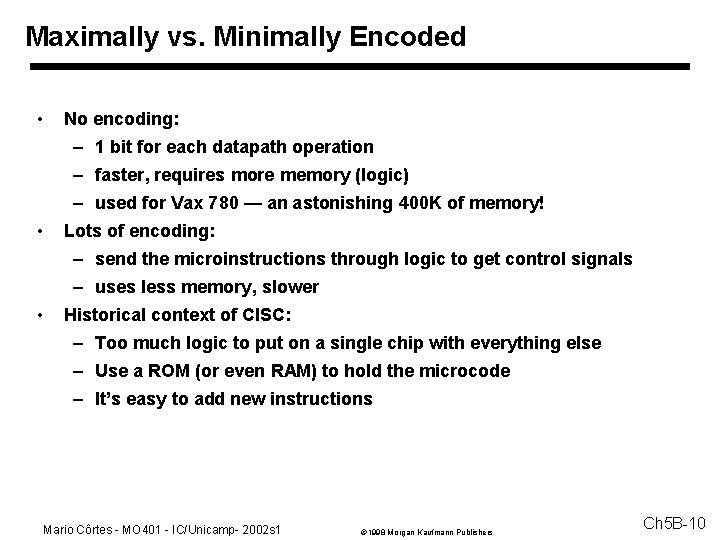

Maximally vs. Minimally Encoded • No encoding: – 1 bit for each datapath operation – faster, requires more memory (logic) – used for Vax 780 — an astonishing 400 K of memory! • Lots of encoding: – send the microinstructions through logic to get control signals – uses less memory, slower • Historical context of CISC: – Too much logic to put on a single chip with everything else – Use a ROM (or even RAM) to hold the microcode – It’s easy to add new instructions Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-10

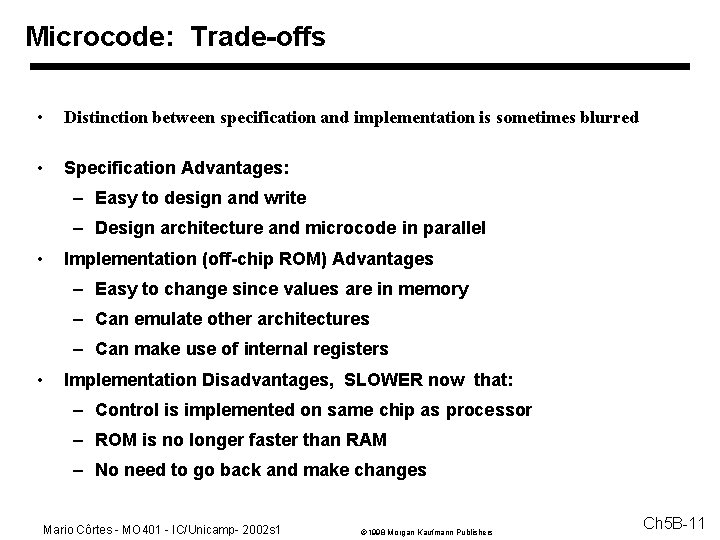

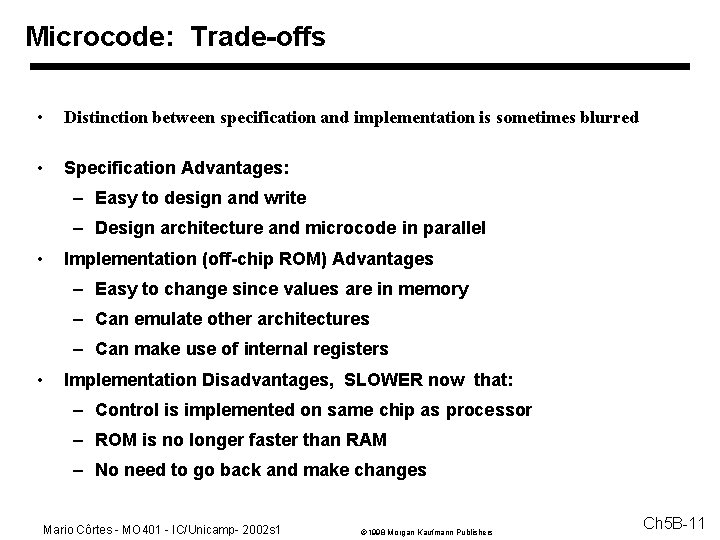

Microcode: Trade-offs • Distinction between specification and implementation is sometimes blurred • Specification Advantages: – Easy to design and write – Design architecture and microcode in parallel • Implementation (off-chip ROM) Advantages – Easy to change since values are in memory – Can emulate other architectures – Can make use of internal registers • Implementation Disadvantages, SLOWER now that: – Control is implemented on same chip as processor – ROM is no longer faster than RAM – No need to go back and make changes Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-11

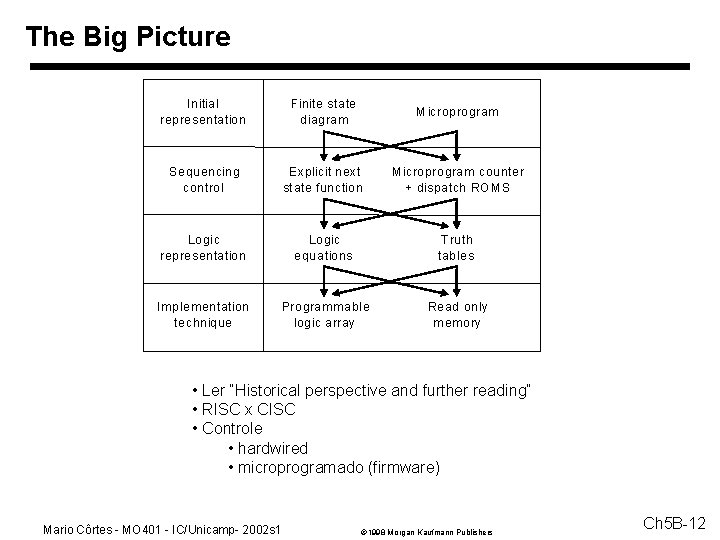

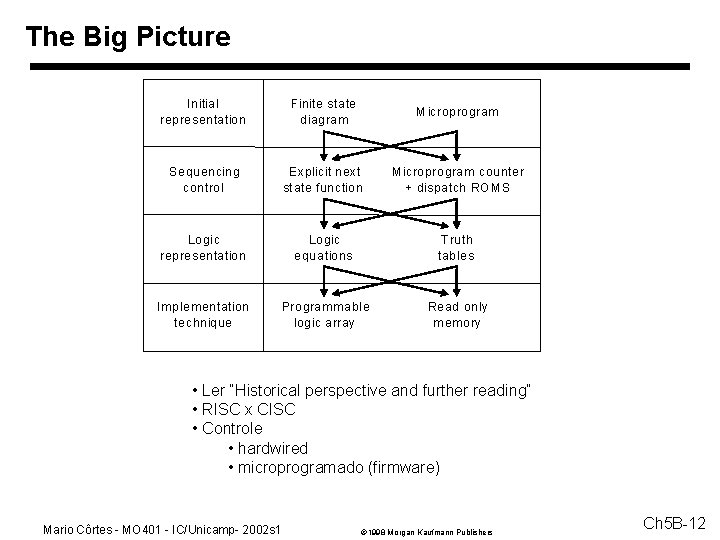

The Big Picture Initial representation Finite state diagram M icroprogram Sequencing control Explicit next state function M icroprogram counter + dispatch RO M S Logic representation Logic equations T ruth tables Im plementation technique Program mable logic array Read only m em ory • Ler “Historical perspective and further reading” • RISC x CISC • Controle • hardwired • microprogramado (firmware) Mario Côrtes - MO 401 - IC/Unicamp- 2002 s 1 1998 Morgan Kaufmann Publishers Ch 5 B-12