Chapter 8 SPI Protocol and DAC Interfacing 1

- Slides: 33

Chapter 8 SPI Protocol and DAC Interfacing 1

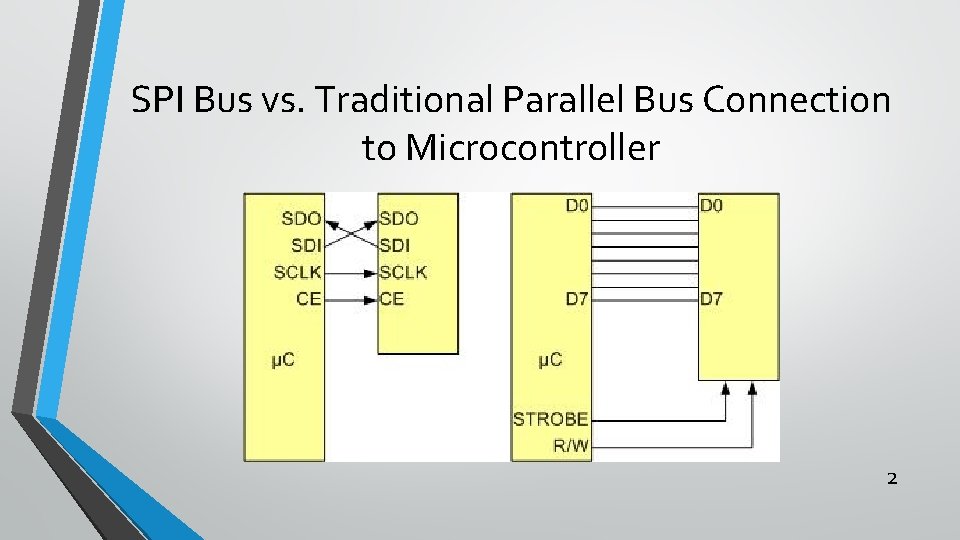

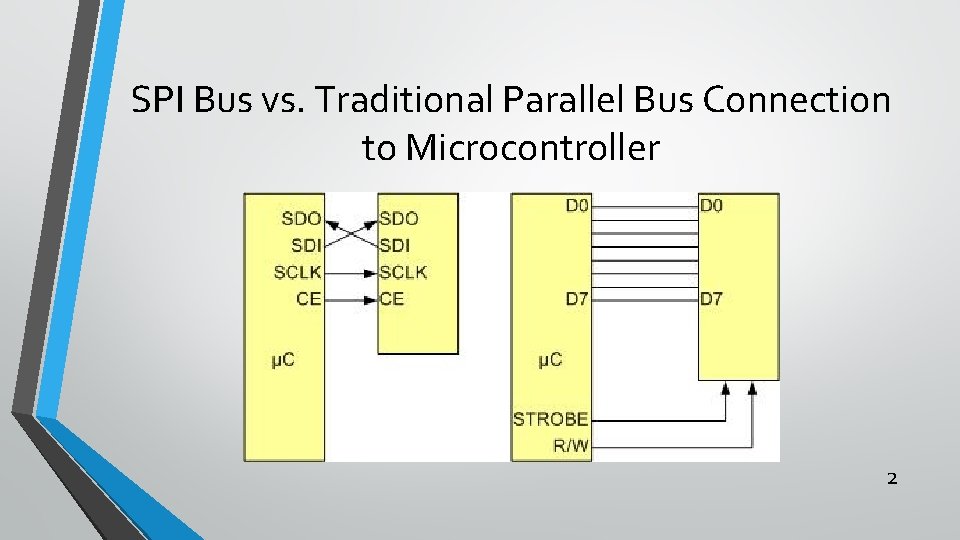

SPI Bus vs. Traditional Parallel Bus Connection to Microcontroller 2

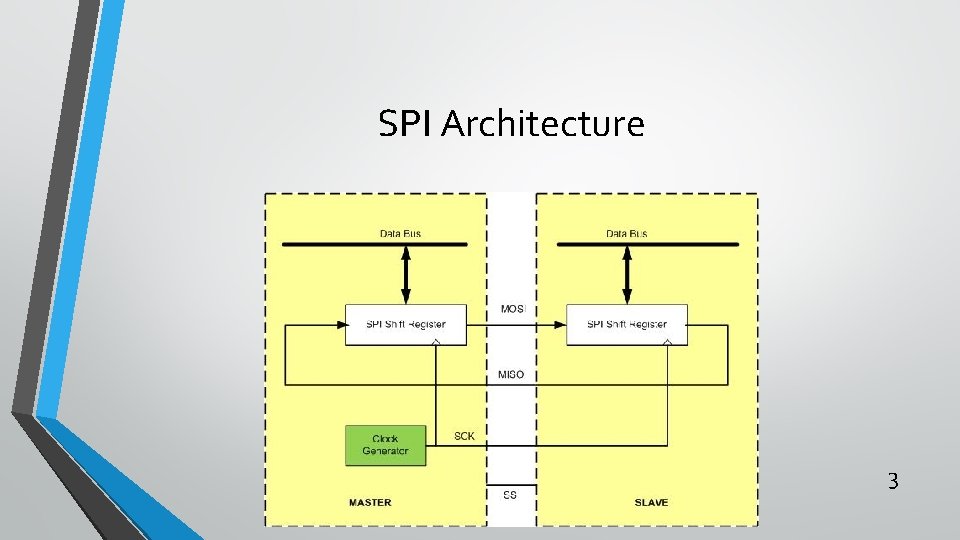

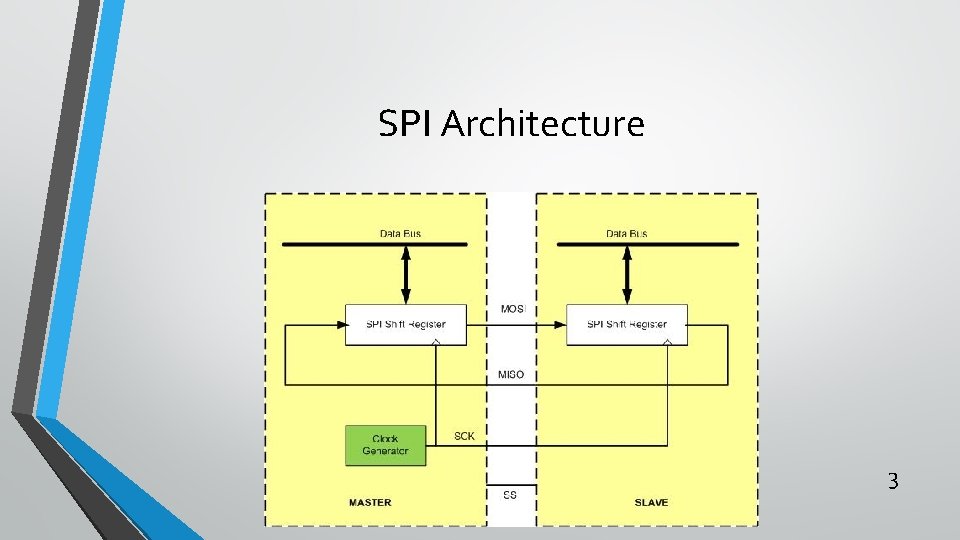

SPI Architecture 3

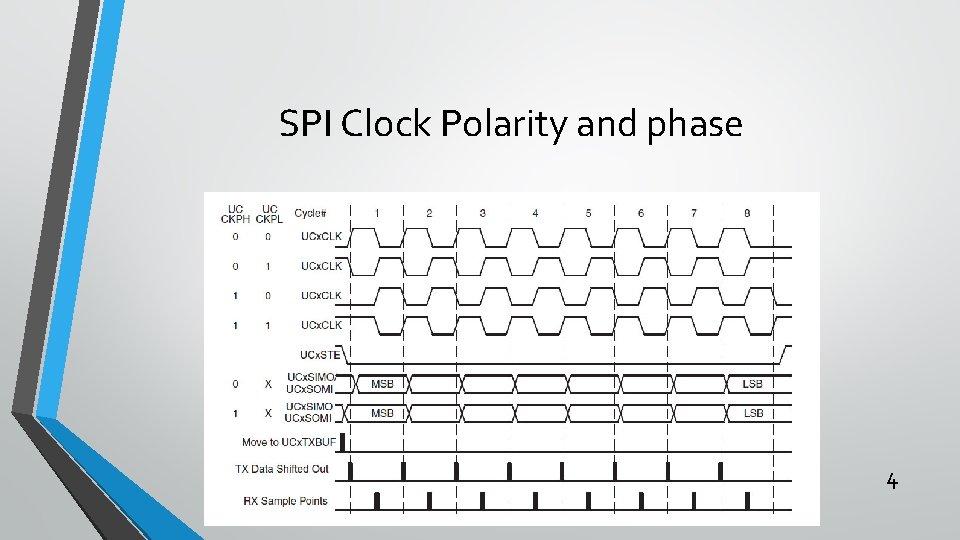

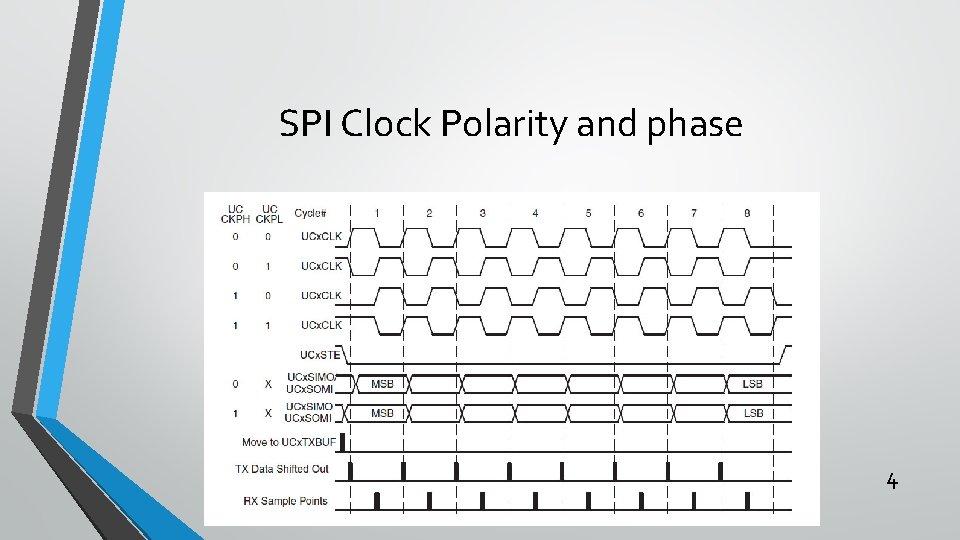

SPI Clock Polarity and phase 4

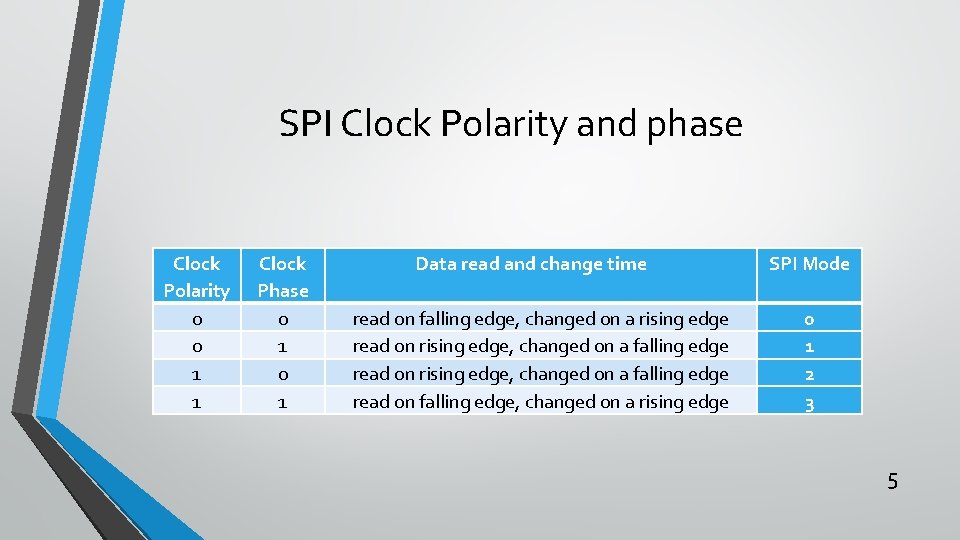

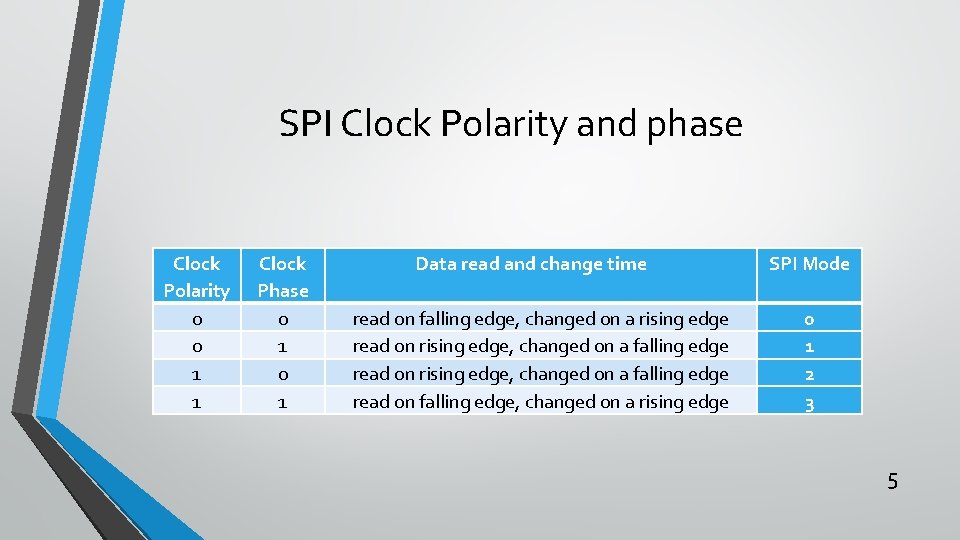

SPI Clock Polarity and phase Clock Polarity 0 0 1 1 Clock Phase 0 1 Data read and change time read on falling edge, changed on a rising edge read on rising edge, changed on a falling edge read on falling edge, changed on a rising edge SPI Mode 0 1 2 3 5

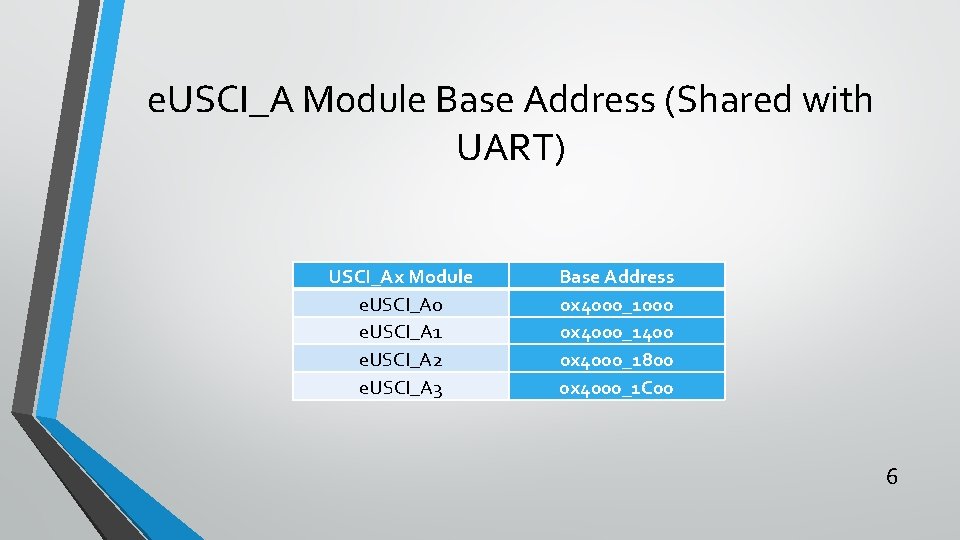

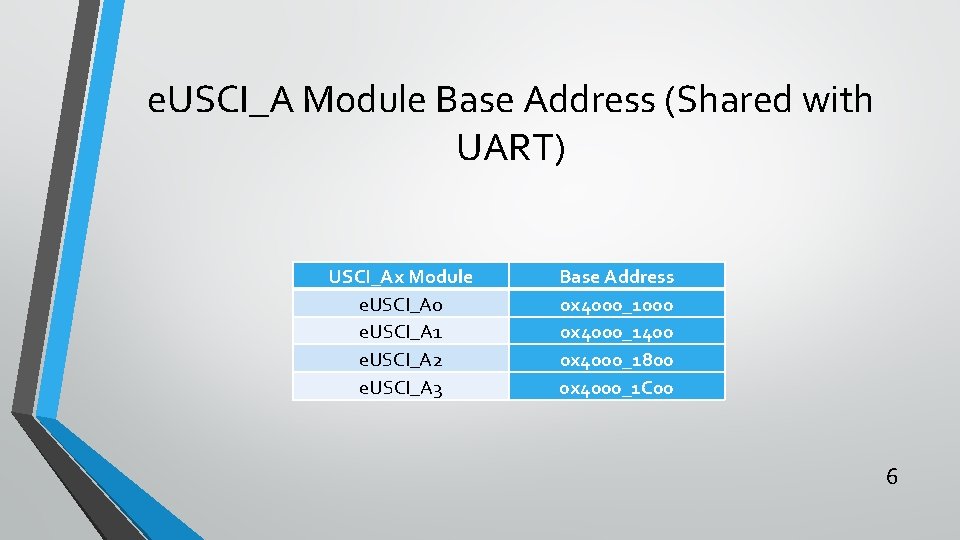

e. USCI_A Module Base Address (Shared with UART) USCI_Ax Module e. USCI_A 0 e. USCI_A 1 e. USCI_A 2 e. USCI_A 3 Base Address 0 x 4000_1000 0 x 4000_1400 0 x 4000_1800 0 x 4000_1 C 00 6

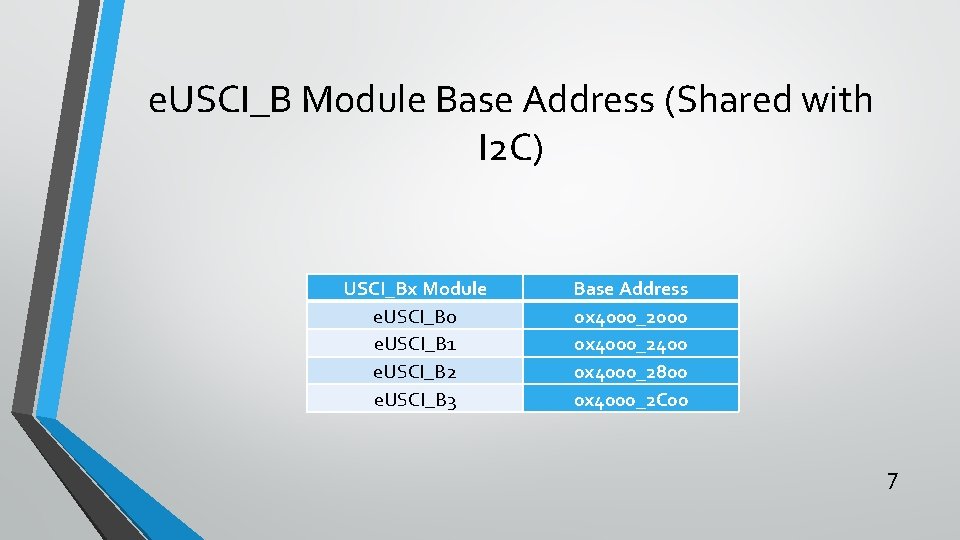

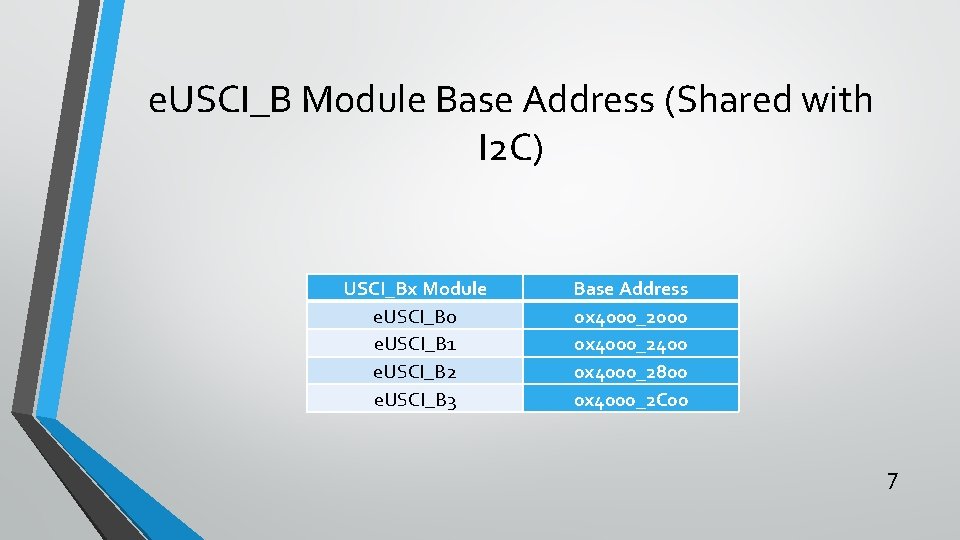

e. USCI_B Module Base Address (Shared with I 2 C) USCI_Bx Module e. USCI_B 0 e. USCI_B 1 e. USCI_B 2 e. USCI_B 3 Base Address 0 x 4000_2000 0 x 4000_2400 0 x 4000_2800 0 x 4000_2 C 00 7

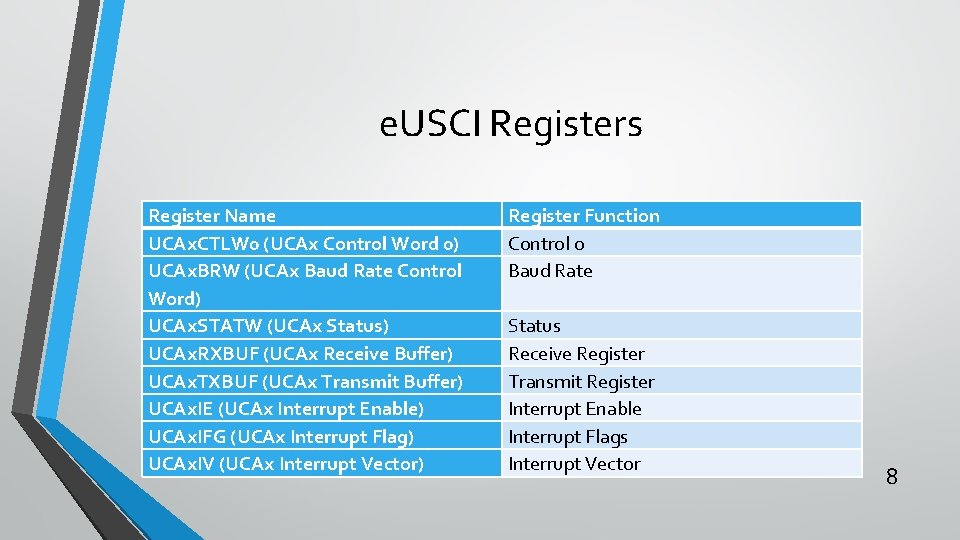

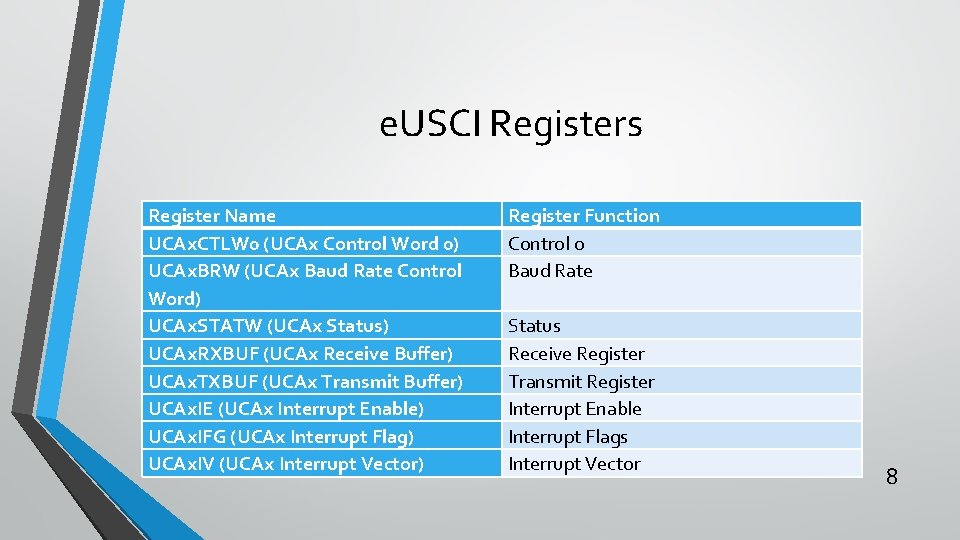

e. USCI Registers Register Name UCAx. CTLW 0 (UCAx Control Word 0) UCAx. BRW (UCAx Baud Rate Control Word) UCAx. STATW (UCAx Status) UCAx. RXBUF (UCAx Receive Buffer) UCAx. TXBUF (UCAx Transmit Buffer) UCAx. IE (UCAx Interrupt Enable) UCAx. IFG (UCAx Interrupt Flag) UCAx. IV (UCAx Interrupt Vector) Register Function Control 0 Baud Rate Status Receive Register Transmit Register Interrupt Enable Interrupt Flags Interrupt Vector 8

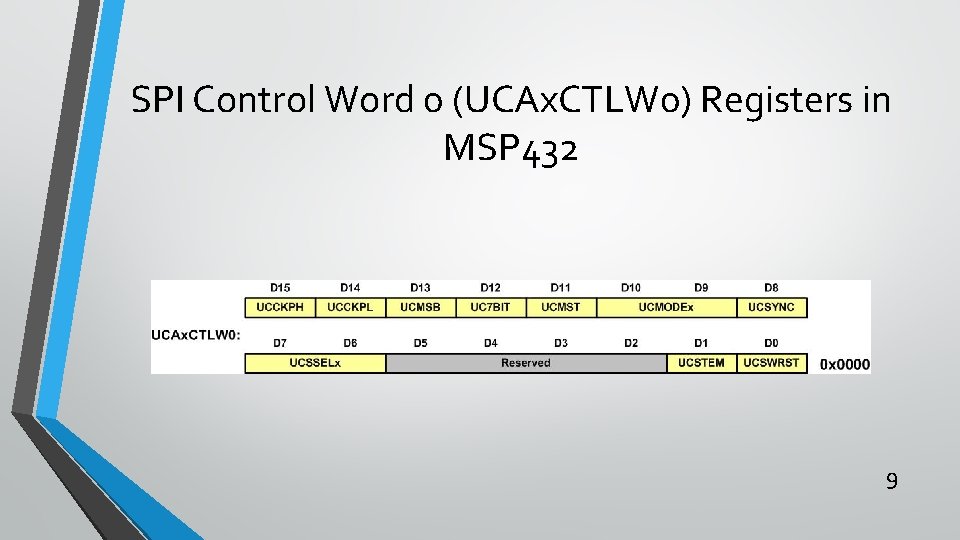

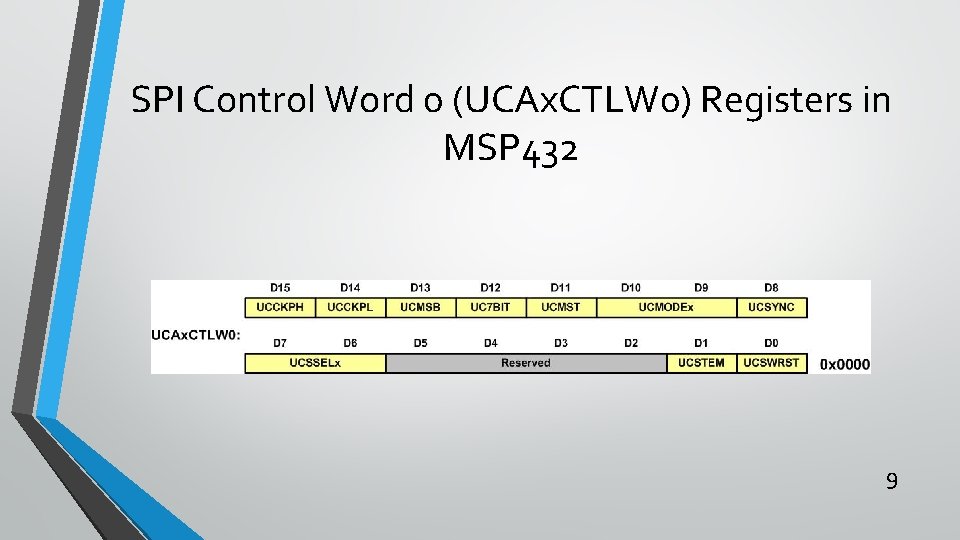

SPI Control Word 0 (UCAx. CTLW 0) Registers in MSP 432 9

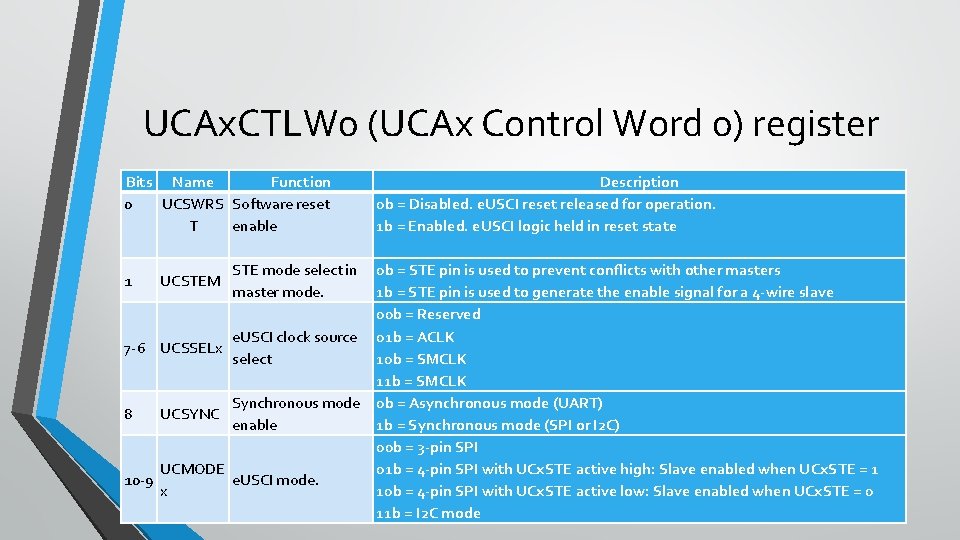

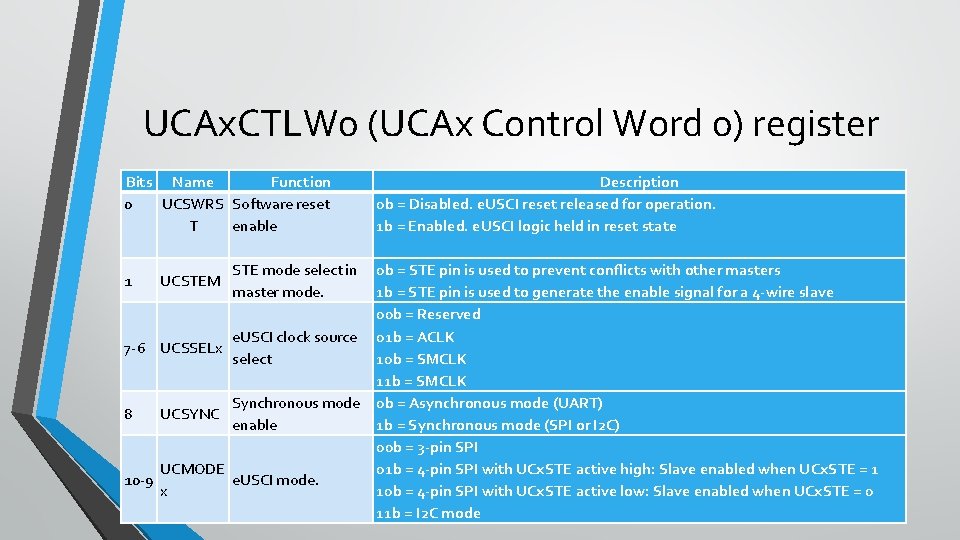

UCAx. CTLW 0 (UCAx Control Word 0) register Bits Name Function 0 UCSWRS Software reset T enable STE mode select in 1 UCSTEM master mode. Description 0 b = Disabled. e. USCI reset released for operation. 1 b = Enabled. e. USCI logic held in reset state 0 b = STE pin is used to prevent conflicts with other masters 1 b = STE pin is used to generate the enable signal for a 4 -wire slave 00 b = Reserved e. USCI clock source 01 b = ACLK 7 -6 UCSSELx select 10 b = SMCLK 11 b = SMCLK Synchronous mode 0 b = Asynchronous mode (UART) 8 UCSYNC enable 1 b = Synchronous mode (SPI or I 2 C) 00 b = 3 -pin SPI UCMODE 01 b = 4 -pin SPI with UCx. STE active high: Slave enabled when UCx. STE = 1 10 10 -9 e. USCI mode. x 10 b = 4 -pin SPI with UCx. STE active low: Slave enabled when UCx. STE = 0 11 b = I 2 C mode

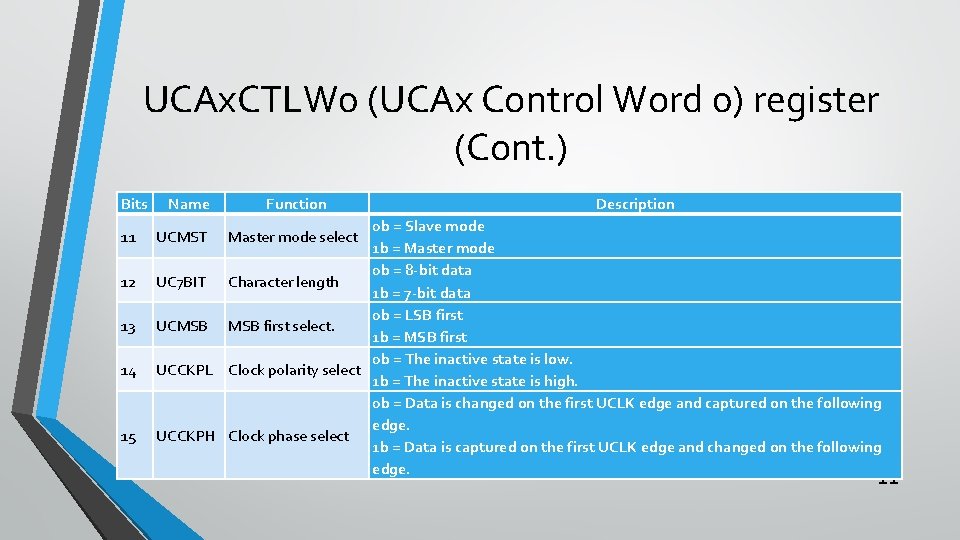

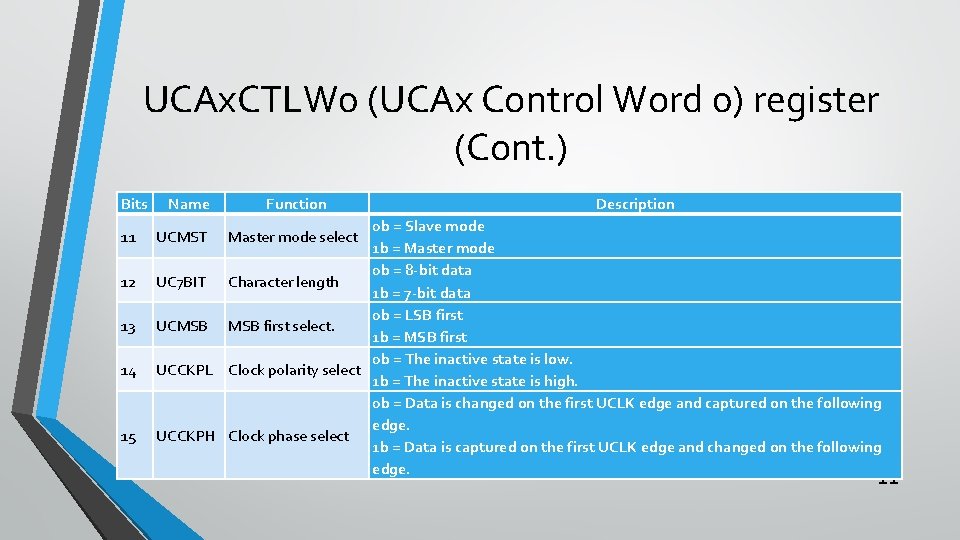

UCAx. CTLW 0 (UCAx Control Word 0) register (Cont. ) Bits 11 12 13 14 15 Name Function Description 0 b = Slave mode 1 b = Master mode 0 b = 8 -bit data UC 7 BIT Character length 1 b = 7 -bit data 0 b = LSB first UCMSB first select. 1 b = MSB first 0 b = The inactive state is low. UCCKPL Clock polarity select 1 b = The inactive state is high. 0 b = Data is changed on the first UCLK edge and captured on the following edge. UCCKPH Clock phase select 1 b = Data is captured on the first UCLK edge and changed on the following edge. UCMST Master mode select 11

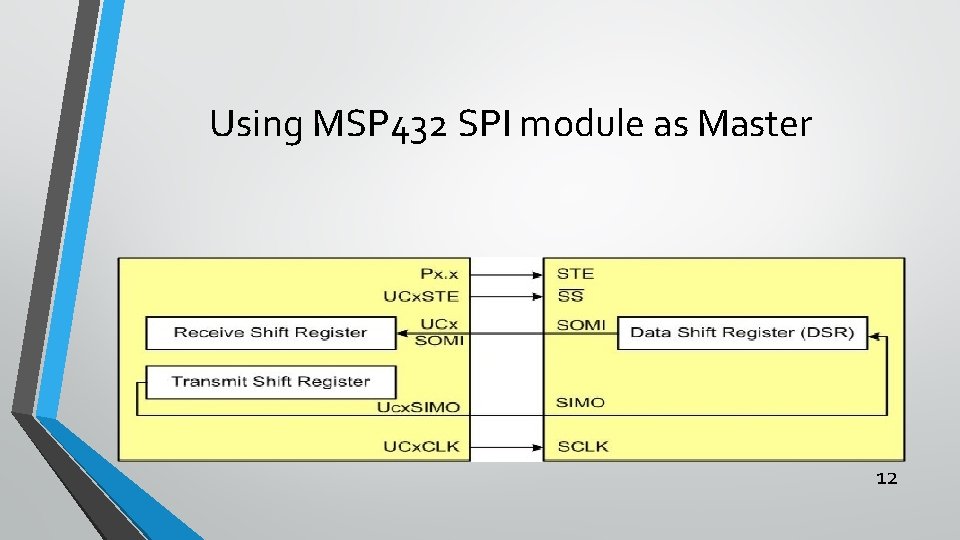

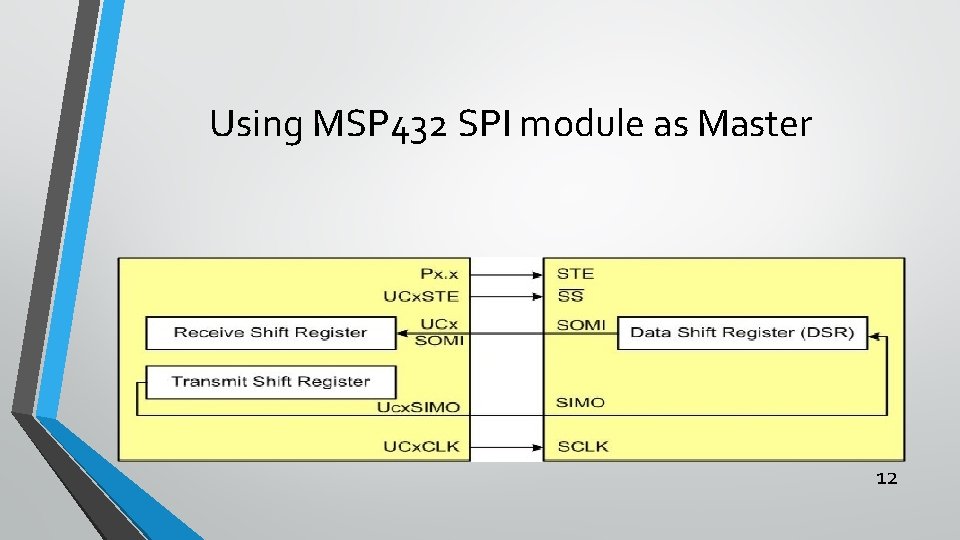

Using MSP 432 SPI module as Master 12

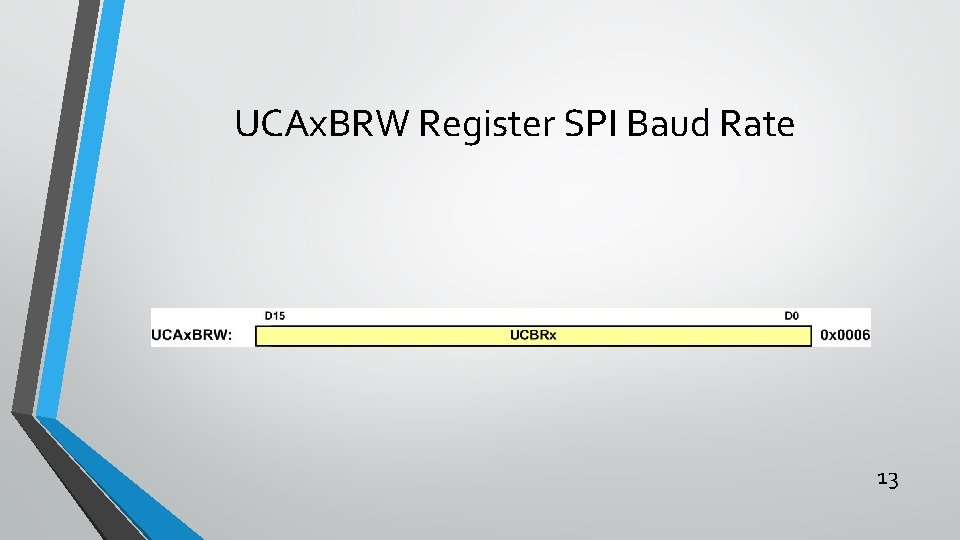

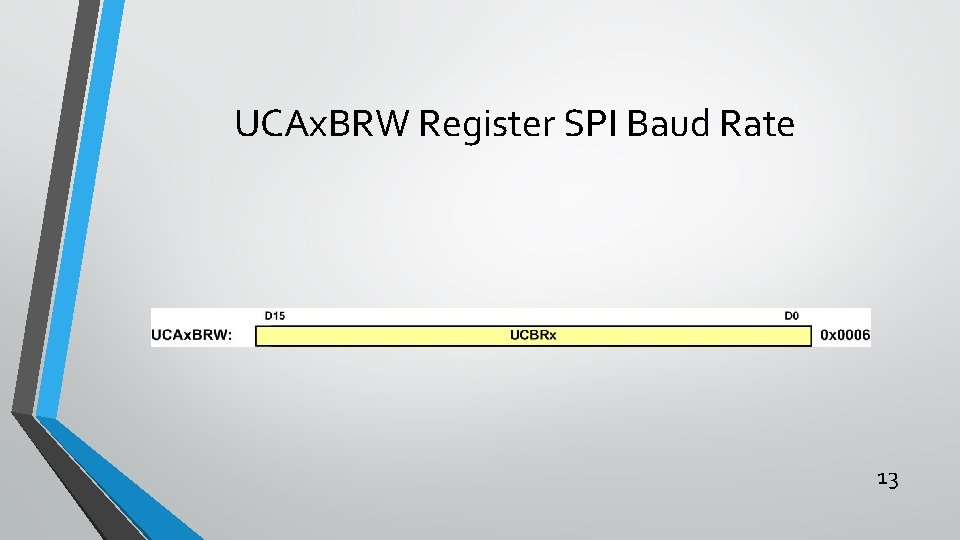

UCAx. BRW Register SPI Baud Rate 13

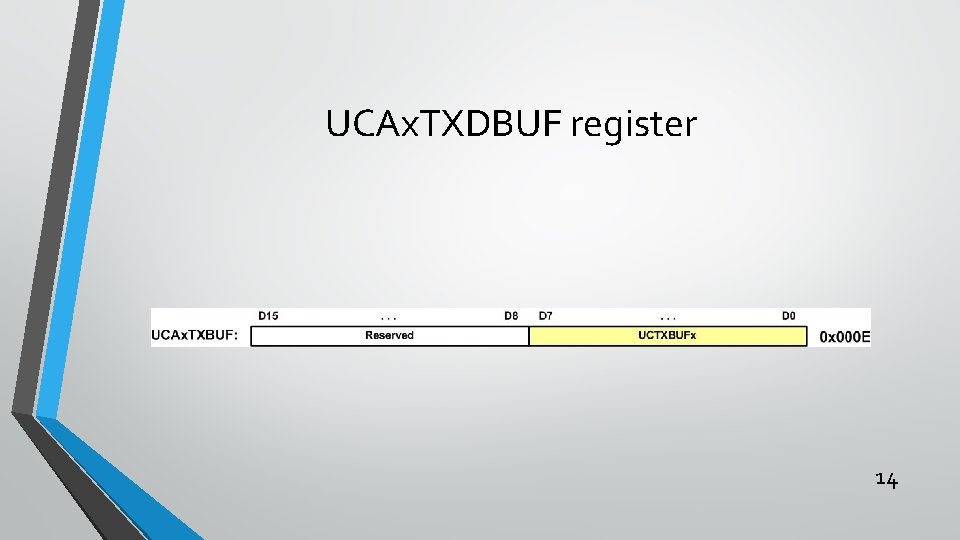

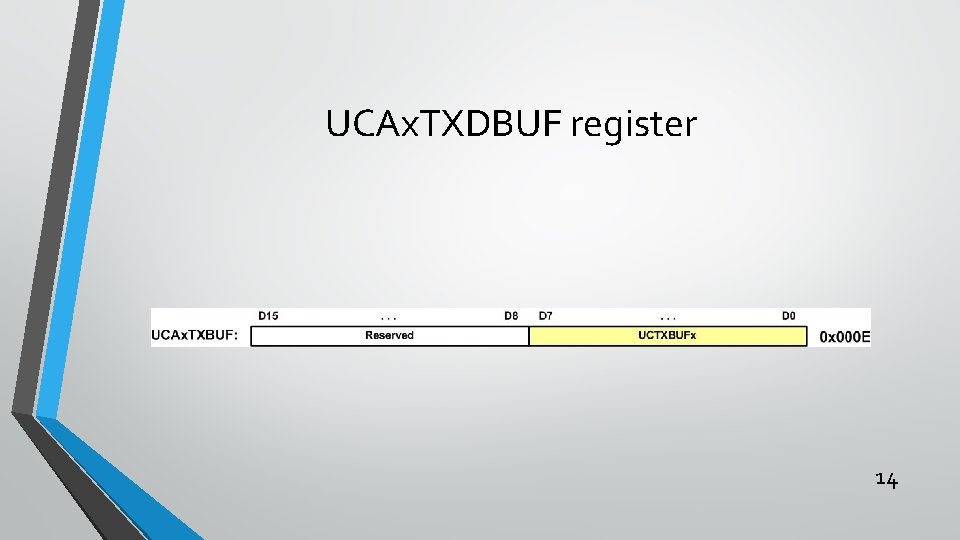

UCAx. TXDBUF register 14

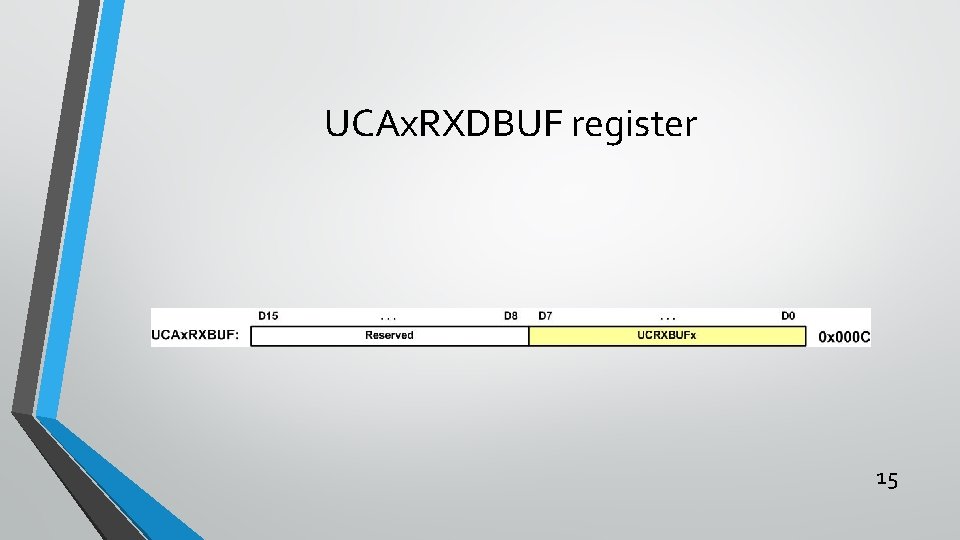

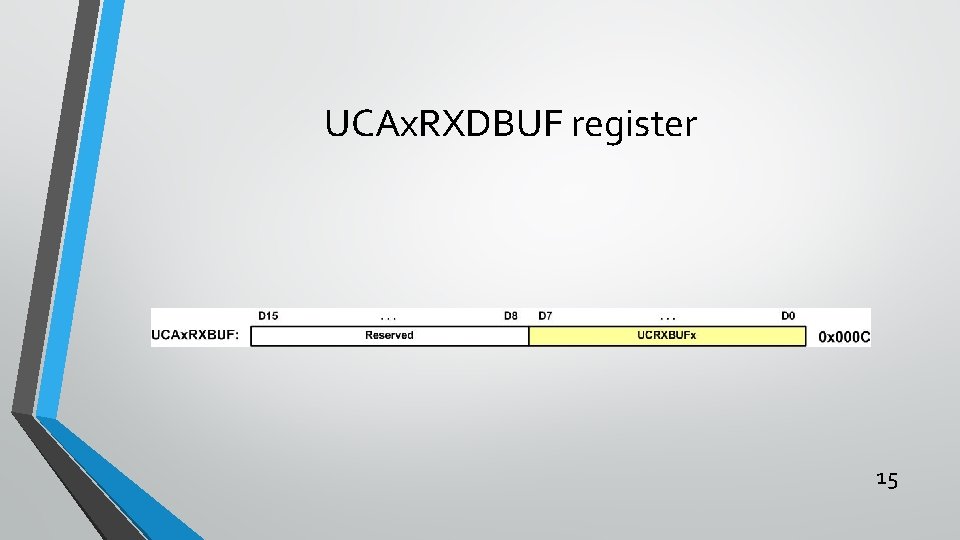

UCAx. RXDBUF register 15

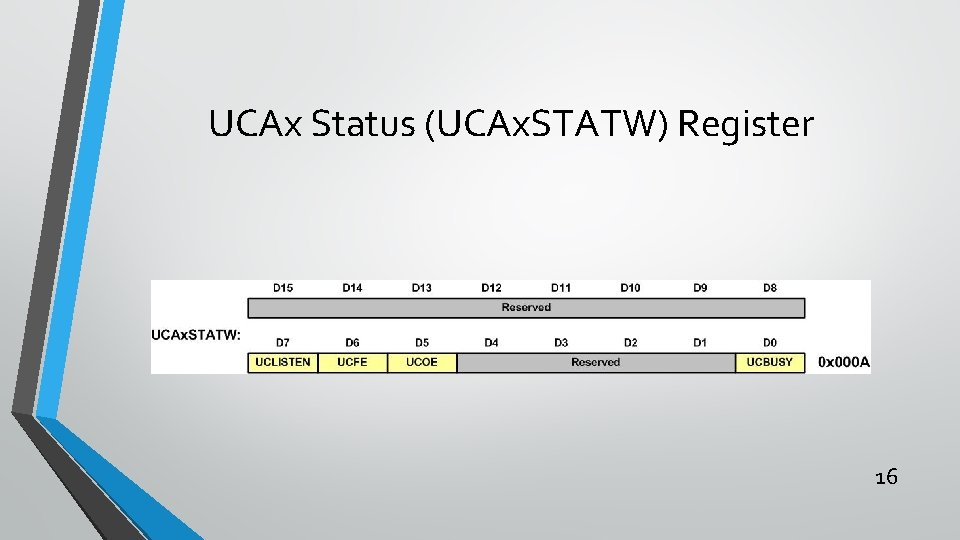

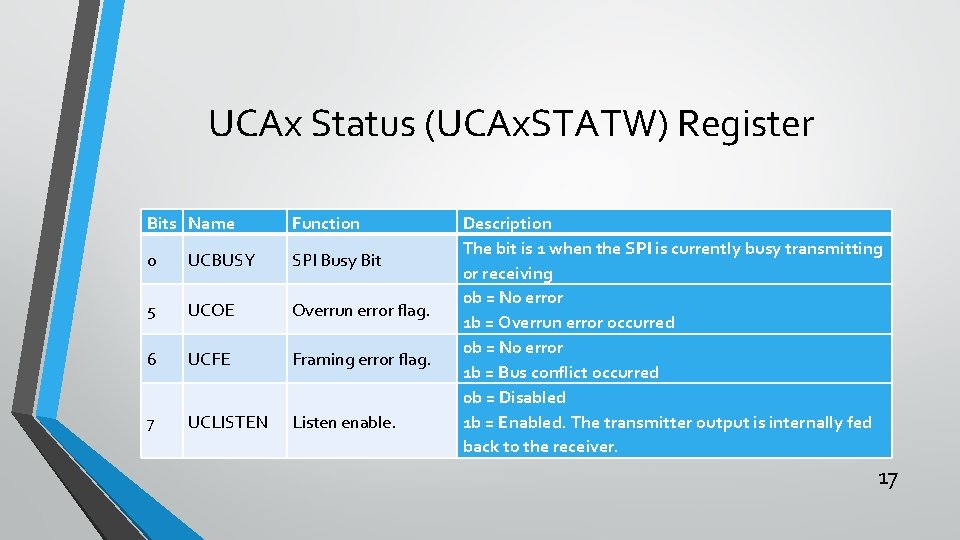

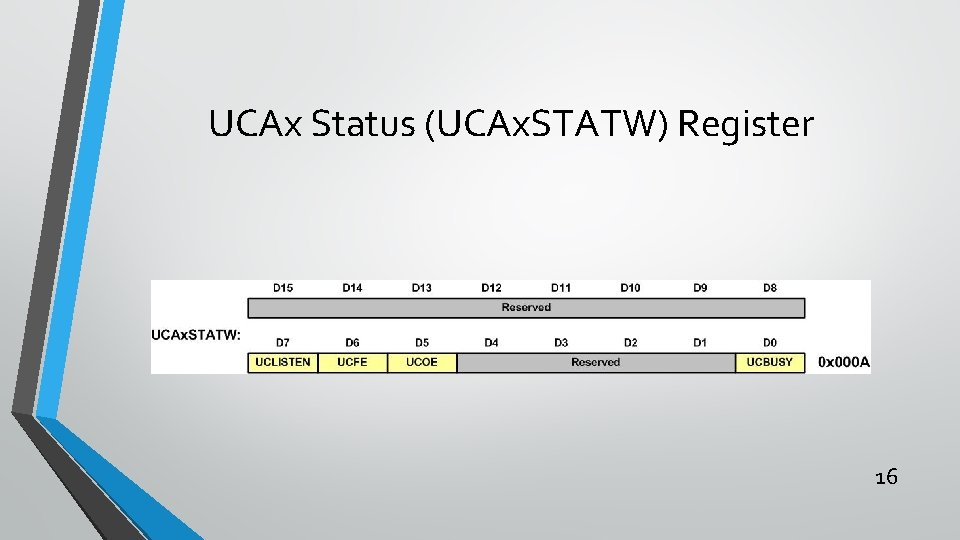

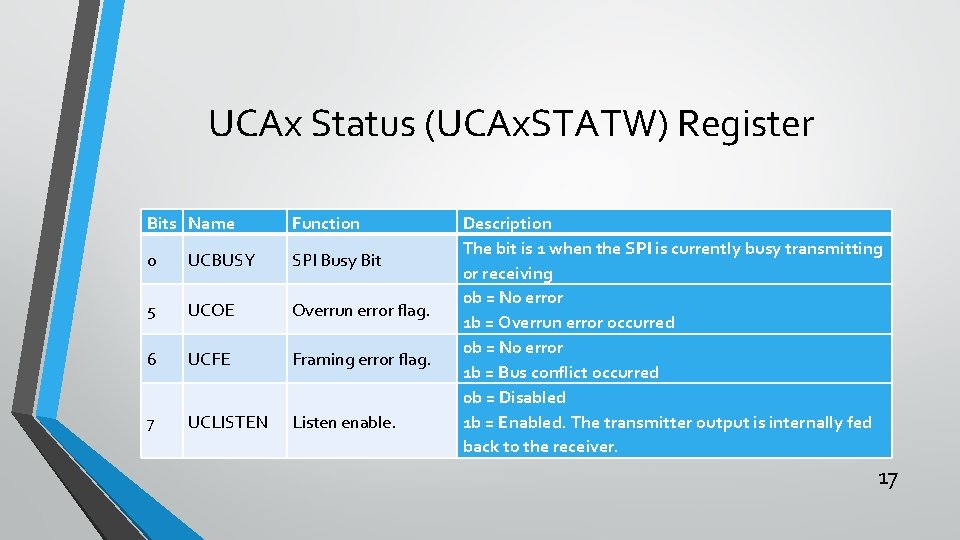

UCAx Status (UCAx. STATW) Register 16

UCAx Status (UCAx. STATW) Register Bits Name Function 0 UCBUSY SPI Busy Bit 5 UCOE Overrun error flag. 6 UCFE Framing error flag. 7 UCLISTEN Listen enable. Description The bit is 1 when the SPI is currently busy transmitting or receiving 0 b = No error 1 b = Overrun error occurred 0 b = No error 1 b = Bus conflict occurred 0 b = Disabled 1 b = Enabled. The transmitter output is internally fed back to the receiver. 17

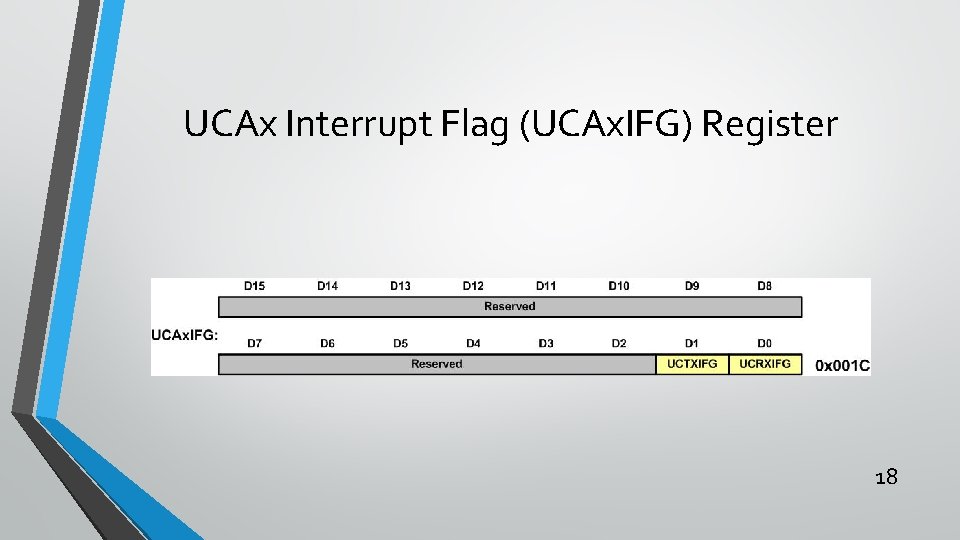

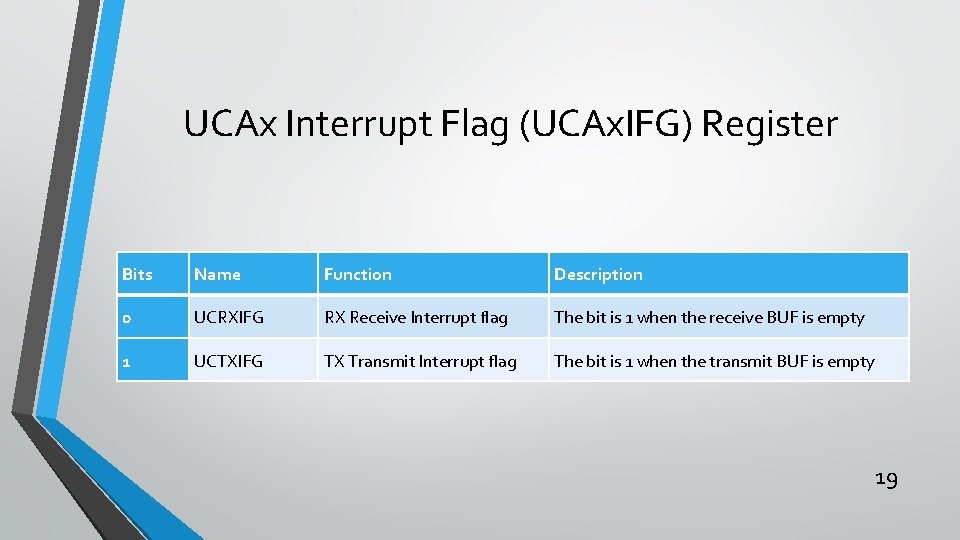

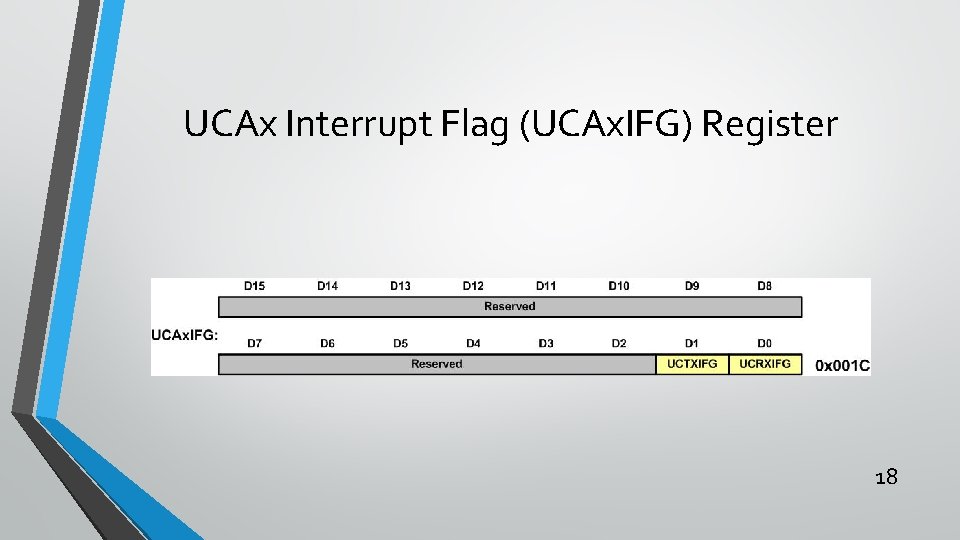

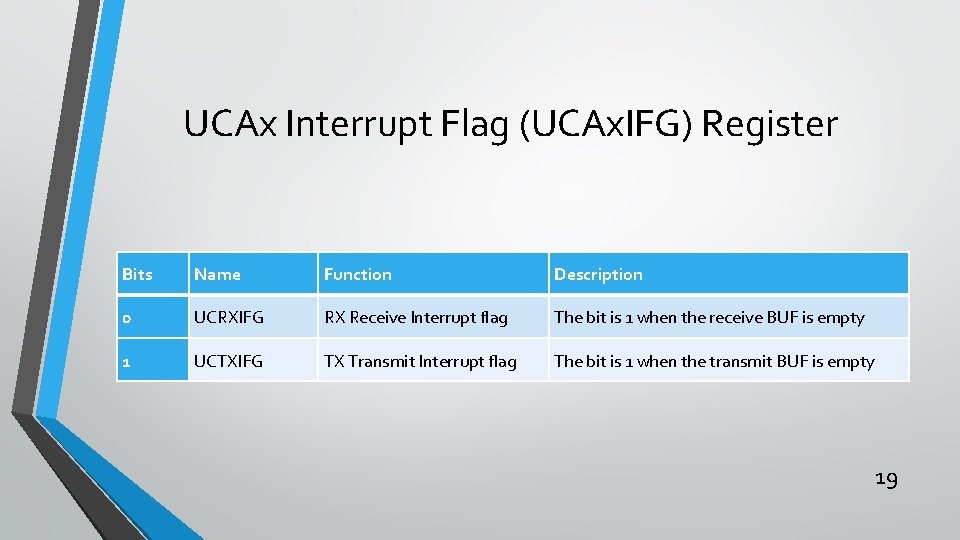

UCAx Interrupt Flag (UCAx. IFG) Register 18

UCAx Interrupt Flag (UCAx. IFG) Register Bits Name Function Description 0 UCRXIFG RX Receive Interrupt flag The bit is 1 when the receive BUF is empty 1 UCTXIFG TX Transmit Interrupt flag The bit is 1 when the transmit BUF is empty 19

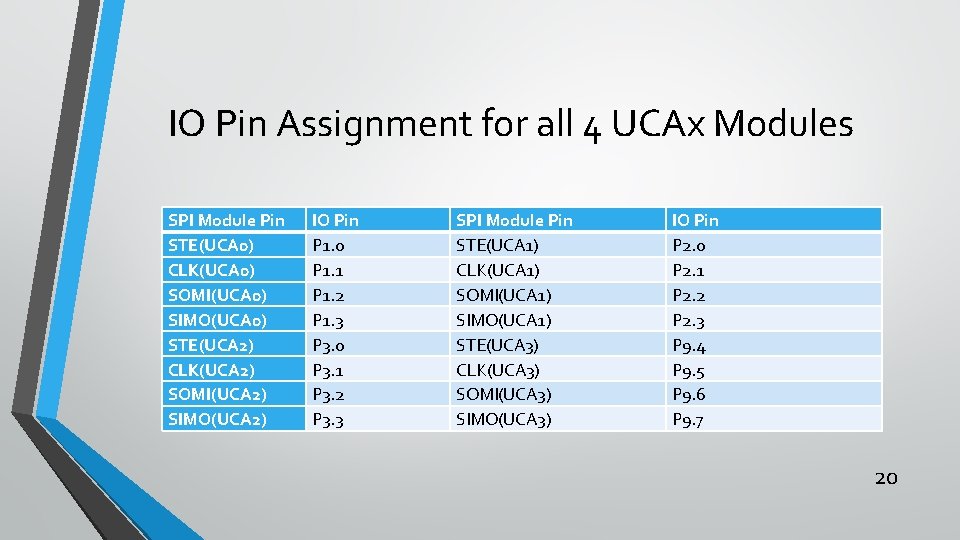

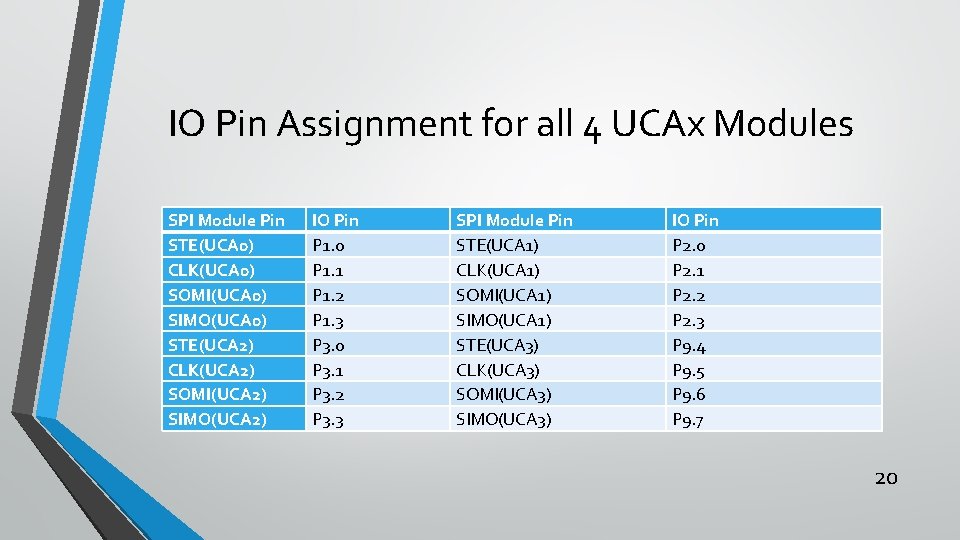

IO Pin Assignment for all 4 UCAx Modules SPI Module Pin STE(UCA 0) CLK(UCA 0) SOMI(UCA 0) SIMO(UCA 0) STE(UCA 2) CLK(UCA 2) SOMI(UCA 2) SIMO(UCA 2) IO Pin P 1. 0 P 1. 1 P 1. 2 P 1. 3 P 3. 0 P 3. 1 P 3. 2 P 3. 3 SPI Module Pin STE(UCA 1) CLK(UCA 1) SOMI(UCA 1) SIMO(UCA 1) STE(UCA 3) CLK(UCA 3) SOMI(UCA 3) SIMO(UCA 3) IO Pin P 2. 0 P 2. 1 P 2. 2 P 2. 3 P 9. 4 P 9. 5 P 9. 6 P 9. 7 20

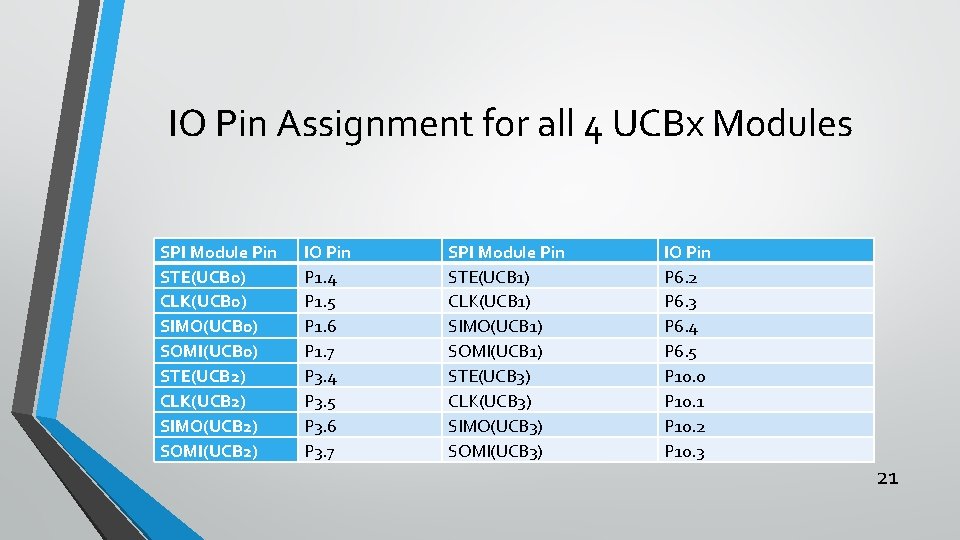

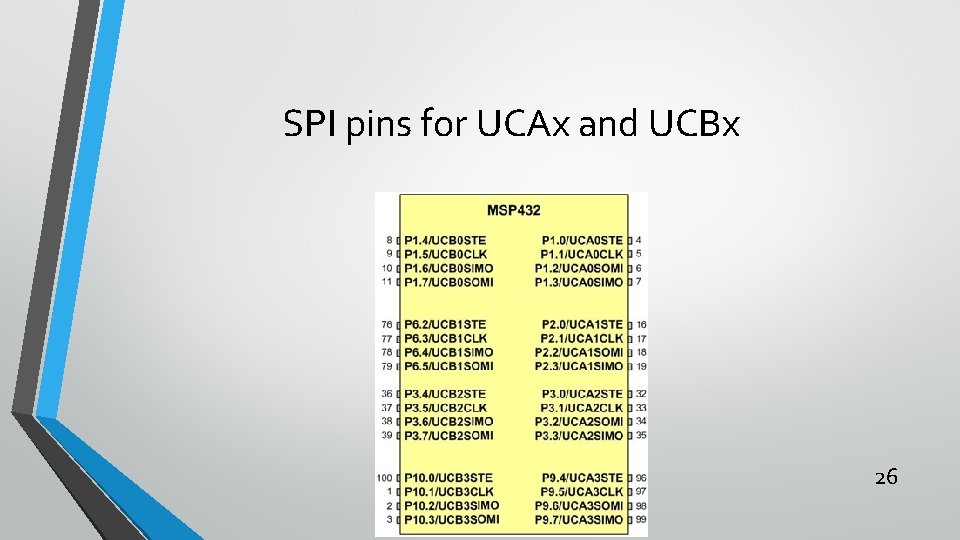

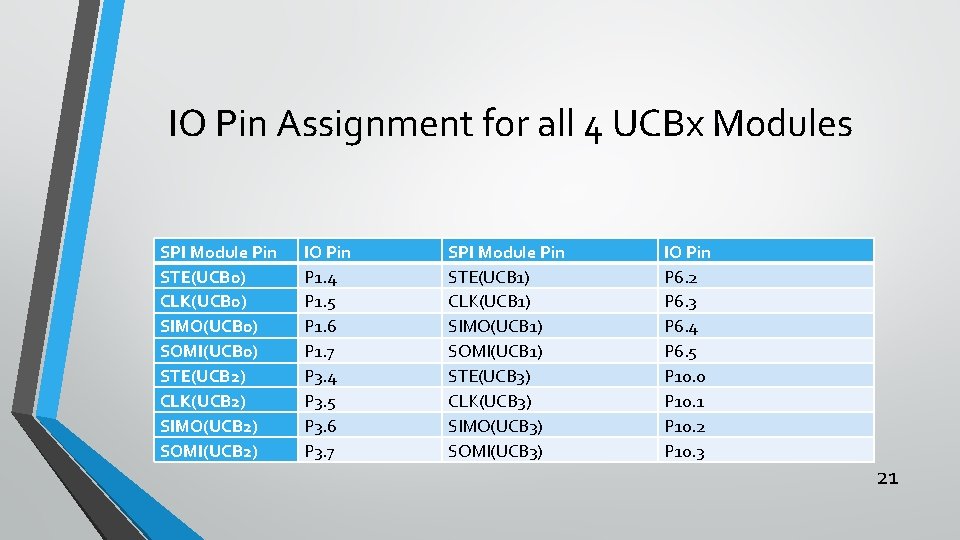

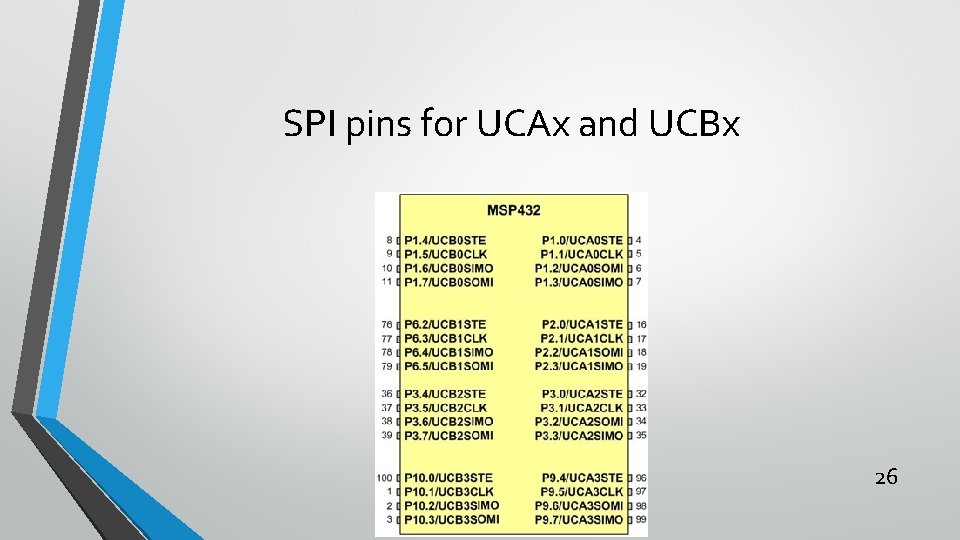

IO Pin Assignment for all 4 UCBx Modules SPI Module Pin STE(UCB 0) CLK(UCB 0) SIMO(UCB 0) SOMI(UCB 0) STE(UCB 2) CLK(UCB 2) SIMO(UCB 2) SOMI(UCB 2) IO Pin P 1. 4 P 1. 5 P 1. 6 P 1. 7 P 3. 4 P 3. 5 P 3. 6 P 3. 7 SPI Module Pin STE(UCB 1) CLK(UCB 1) SIMO(UCB 1) SOMI(UCB 1) STE(UCB 3) CLK(UCB 3) SIMO(UCB 3) SOMI(UCB 3) IO Pin P 6. 2 P 6. 3 P 6. 4 P 6. 5 P 10. 0 P 10. 1 P 10. 2 P 10. 3 21

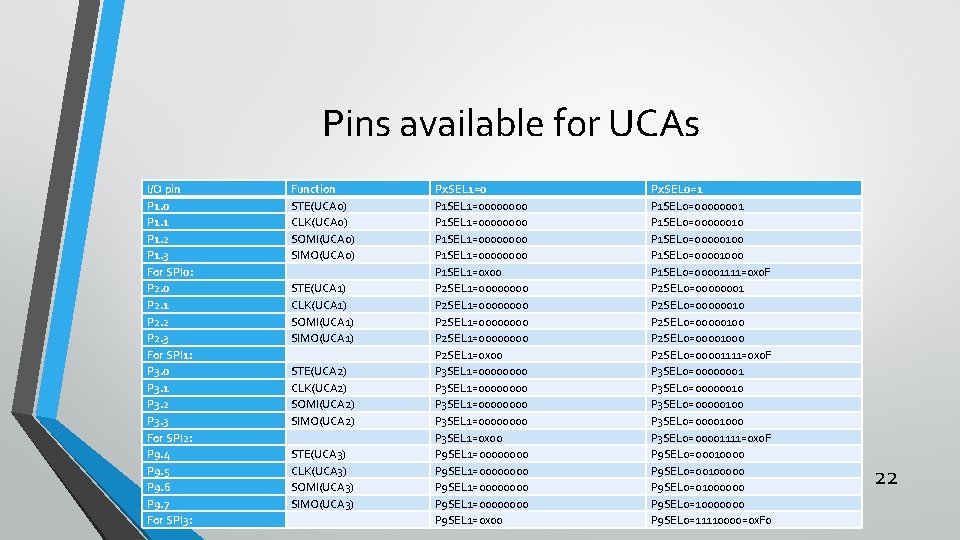

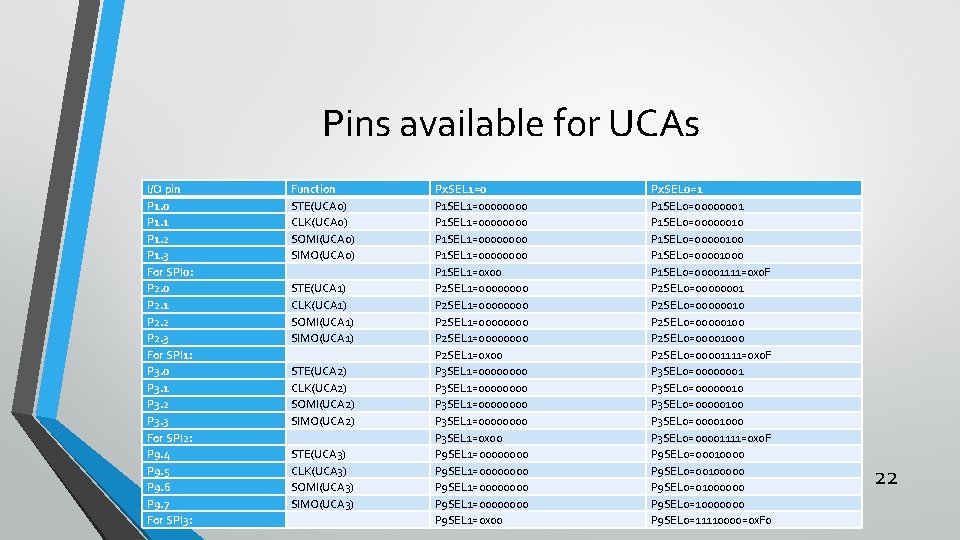

Pins available for UCAs I/O pin P 1. 0 P 1. 1 P 1. 2 P 1. 3 For SPI 0: P 2. 0 P 2. 1 P 2. 2 P 2. 3 For SPI 1: P 3. 0 P 3. 1 P 3. 2 P 3. 3 For SPI 2: P 9. 4 P 9. 5 P 9. 6 P 9. 7 For SPI 3: Function STE(UCA 0) CLK(UCA 0) SOMI(UCA 0) SIMO(UCA 0) STE(UCA 1) CLK(UCA 1) SOMI(UCA 1) SIMO(UCA 1) STE(UCA 2) CLK(UCA 2) SOMI(UCA 2) SIMO(UCA 2) STE(UCA 3) CLK(UCA 3) SOMI(UCA 3) SIMO(UCA 3) Px. SEL 1=0 P 1 SEL 1=00000000 P 1 SEL 1=0 x 00 P 2 SEL 1=00000000 P 2 SEL 1=0 x 00 P 3 SEL 1=00000000 P 3 SEL 1=0 x 00 P 9 SEL 1=00000000 P 9 SEL 1=0 x 00 Px. SEL 0=1 P 1 SEL 0=00000001 P 1 SEL 0=00000010 P 1 SEL 0=00000100 P 1 SEL 0=00001000 P 1 SEL 0=00001111=0 x 0 F P 2 SEL 0=00000001 P 2 SEL 0=00000010 P 2 SEL 0=00000100 P 2 SEL 0=00001000 P 2 SEL 0=00001111=0 x 0 F P 3 SEL 0=00000001 P 3 SEL 0=00000010 P 3 SEL 0=00000100 P 3 SEL 0=00001000 P 3 SEL 0=00001111=0 x 0 F P 9 SEL 0=00010000 P 9 SEL 0=00100000 P 9 SEL 0=01000000 P 9 SEL 0=10000000 P 9 SEL 0=11110000=0 x. F 0 22

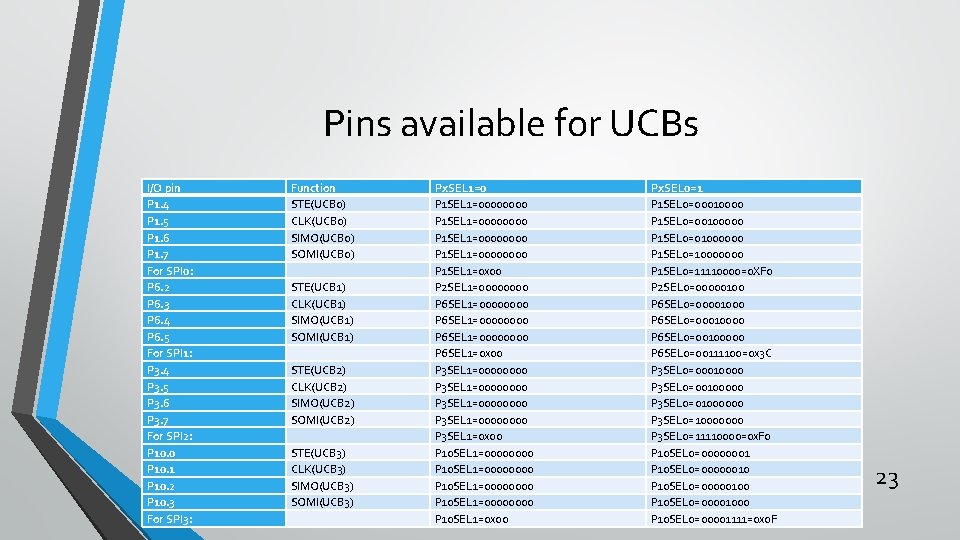

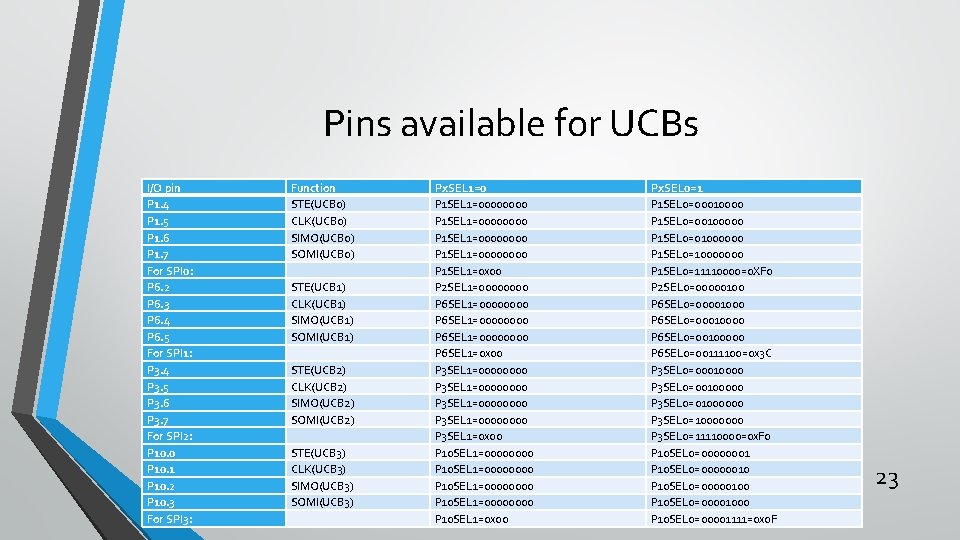

Pins available for UCBs I/O pin P 1. 4 P 1. 5 P 1. 6 P 1. 7 For SPI 0: P 6. 2 P 6. 3 P 6. 4 P 6. 5 For SPI 1: P 3. 4 P 3. 5 P 3. 6 P 3. 7 For SPI 2: P 10. 0 P 10. 1 P 10. 2 P 10. 3 For SPI 3: Function STE(UCB 0) CLK(UCB 0) SIMO(UCB 0) SOMI(UCB 0) STE(UCB 1) CLK(UCB 1) SIMO(UCB 1) SOMI(UCB 1) STE(UCB 2) CLK(UCB 2) SIMO(UCB 2) SOMI(UCB 2) STE(UCB 3) CLK(UCB 3) SIMO(UCB 3) SOMI(UCB 3) Px. SEL 1=0 P 1 SEL 1=00000000 P 1 SEL 1=0 x 00 P 2 SEL 1=00000000 P 6 SEL 1=0 x 00 P 3 SEL 1=00000000 P 3 SEL 1=0 x 00 P 10 SEL 1=00000000 P 10 SEL 1=0 x 00 Px. SEL 0=1 P 1 SEL 0=00010000 P 1 SEL 0=00100000 P 1 SEL 0=01000000 P 1 SEL 0=10000000 P 1 SEL 0=11110000=0 XF 0 P 2 SEL 0=00000100 P 6 SEL 0=00001000 P 6 SEL 0=00010000 P 6 SEL 0=00100000 P 6 SEL 0=00111100=0 x 3 C P 3 SEL 0=00010000 P 3 SEL 0=00100000 P 3 SEL 0=01000000 P 3 SEL 0=10000000 P 3 SEL 0=11110000=0 x. F 0 P 10 SEL 0=00000001 P 10 SEL 0=00000010 P 10 SEL 0=00000100 P 10 SEL 0=00001000 P 10 SEL 0=00001111=0 x 0 F 23

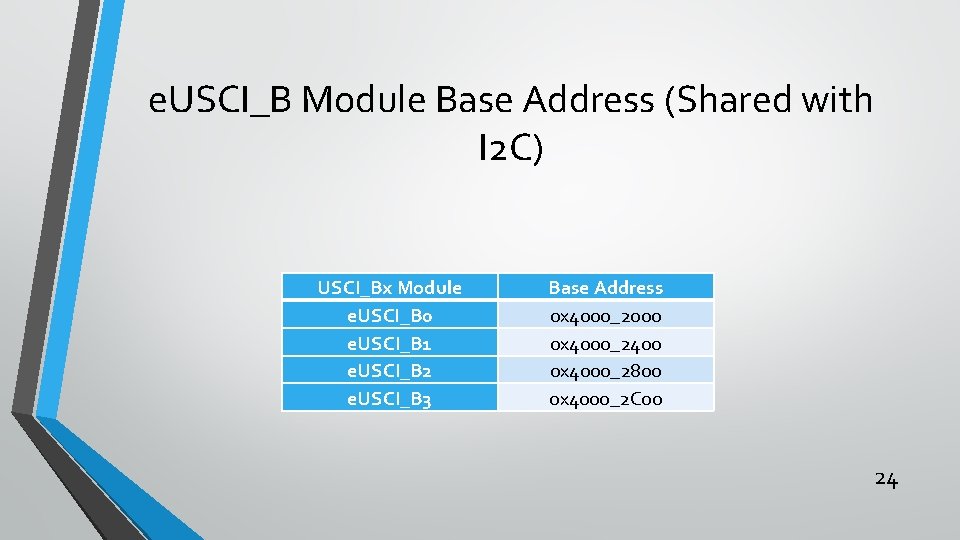

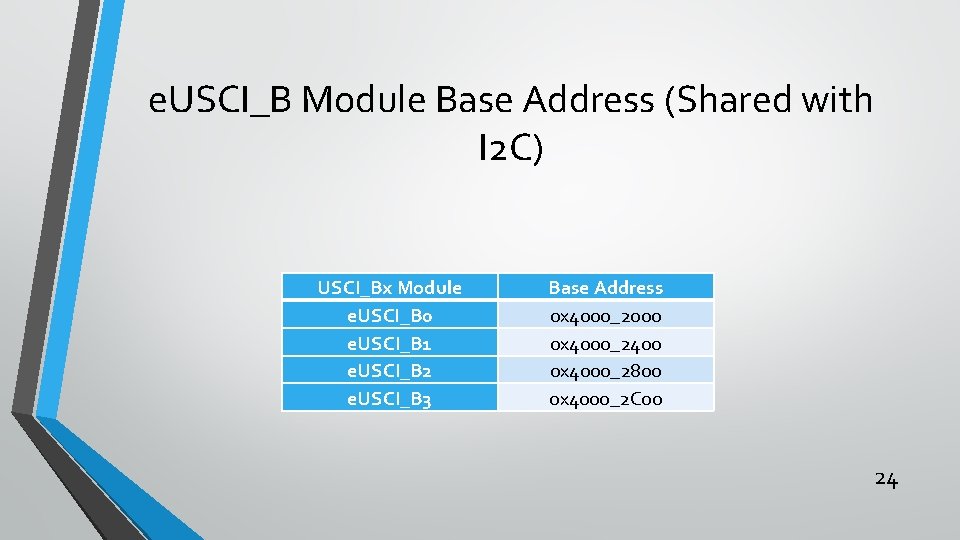

e. USCI_B Module Base Address (Shared with I 2 C) USCI_Bx Module e. USCI_B 0 e. USCI_B 1 e. USCI_B 2 e. USCI_B 3 Base Address 0 x 4000_2000 0 x 4000_2400 0 x 4000_2800 0 x 4000_2 C 00 24

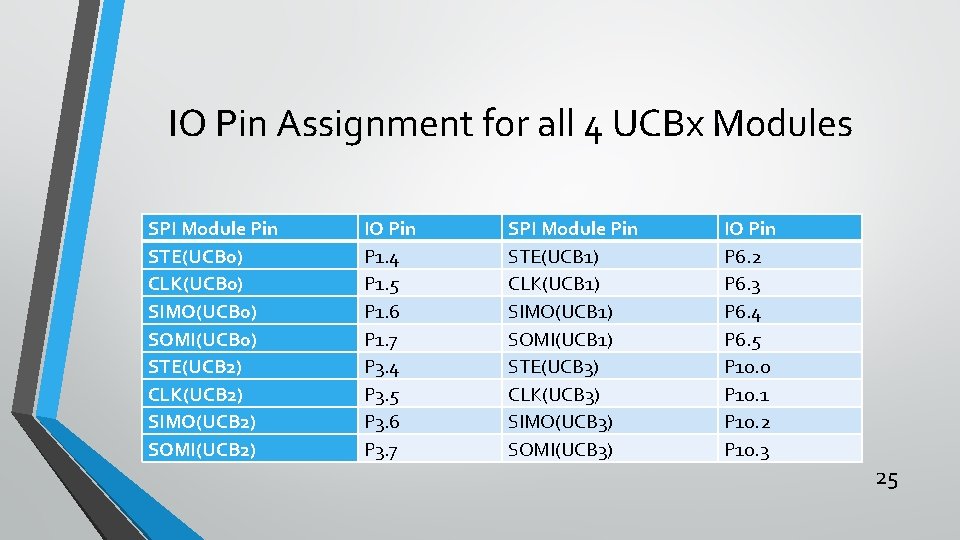

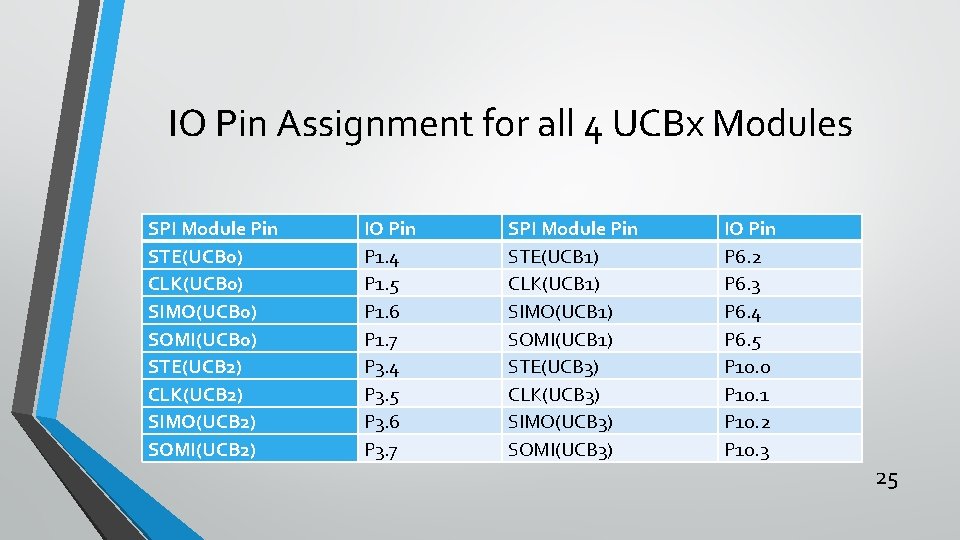

IO Pin Assignment for all 4 UCBx Modules SPI Module Pin STE(UCB 0) CLK(UCB 0) SIMO(UCB 0) SOMI(UCB 0) STE(UCB 2) CLK(UCB 2) SIMO(UCB 2) SOMI(UCB 2) IO Pin P 1. 4 P 1. 5 P 1. 6 P 1. 7 P 3. 4 P 3. 5 P 3. 6 P 3. 7 SPI Module Pin STE(UCB 1) CLK(UCB 1) SIMO(UCB 1) SOMI(UCB 1) STE(UCB 3) CLK(UCB 3) SIMO(UCB 3) SOMI(UCB 3) IO Pin P 6. 2 P 6. 3 P 6. 4 P 6. 5 P 10. 0 P 10. 1 P 10. 2 P 10. 3 25

SPI pins for UCAx and UCBx 26

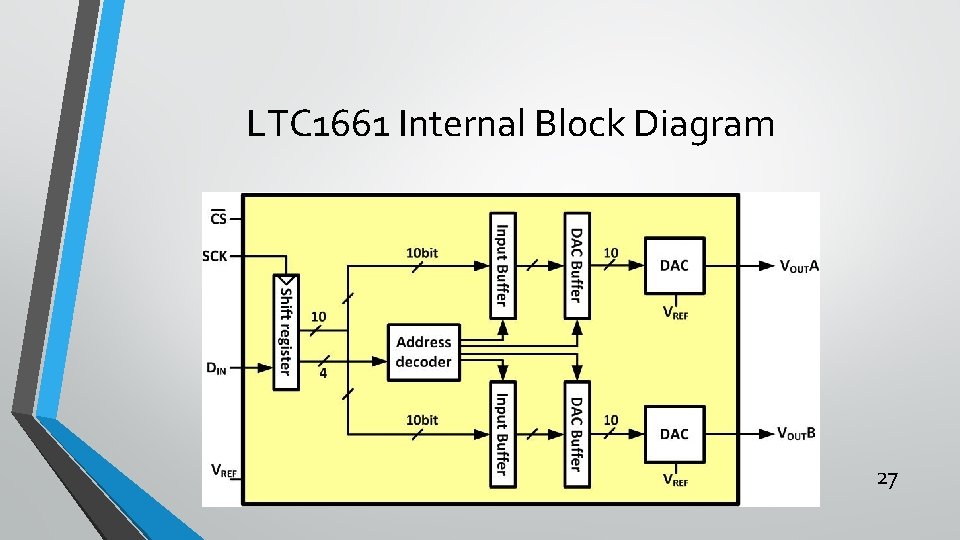

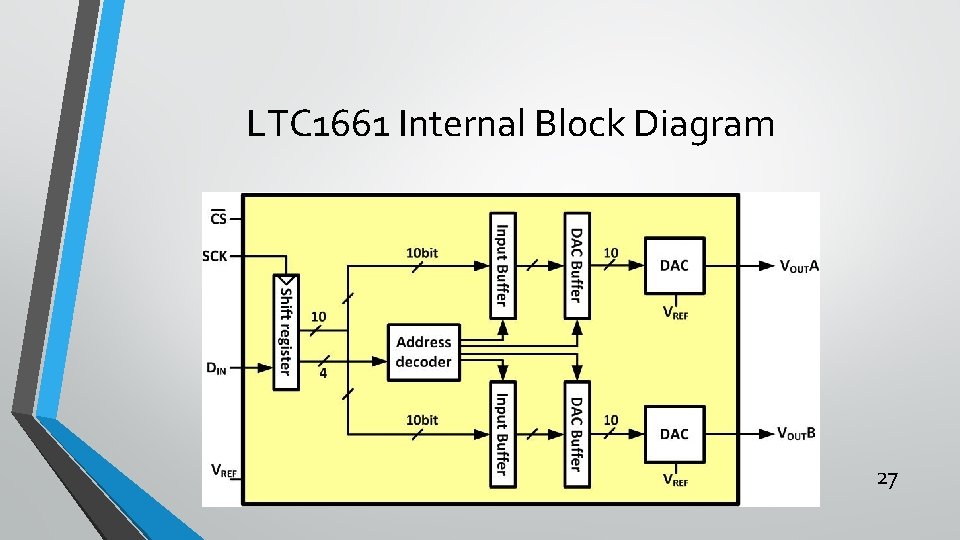

LTC 1661 Internal Block Diagram 27

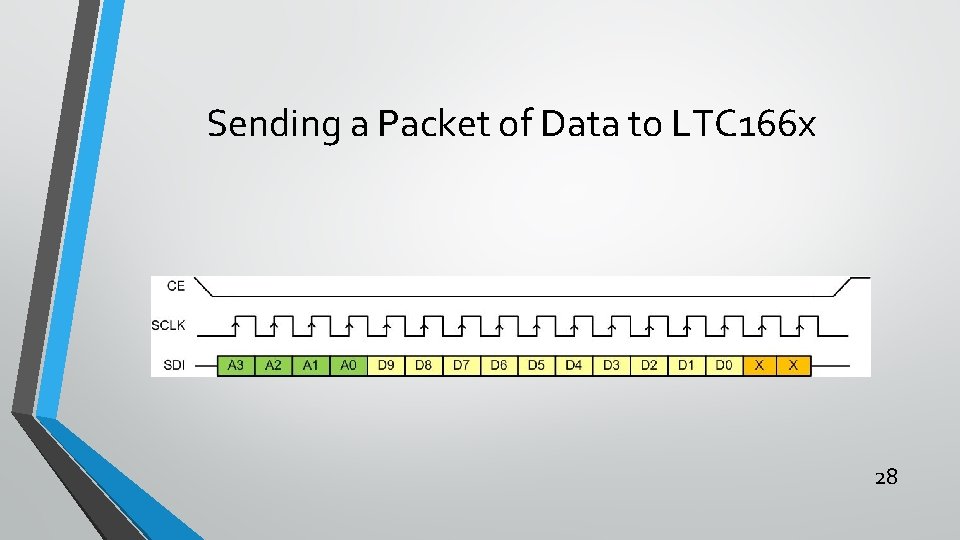

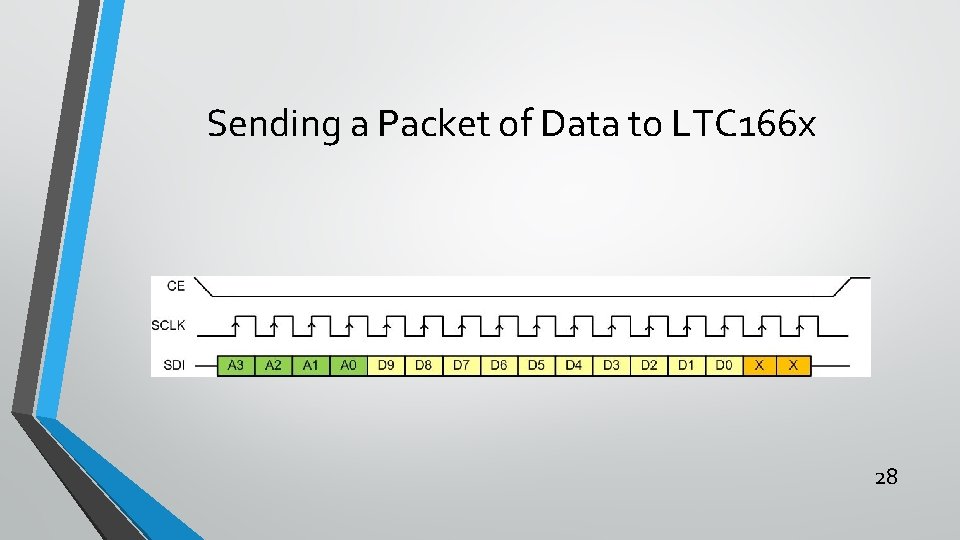

Sending a Packet of Data to LTC 166 x 28

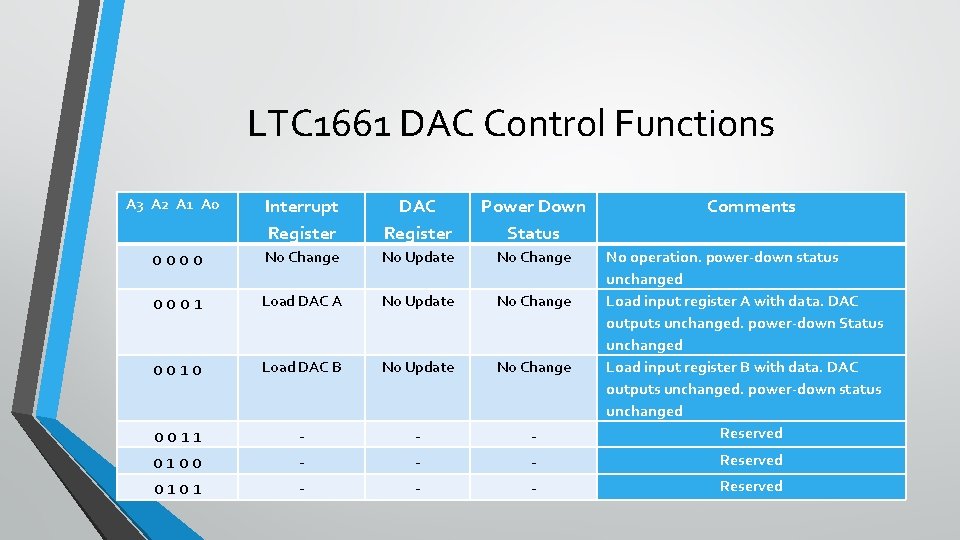

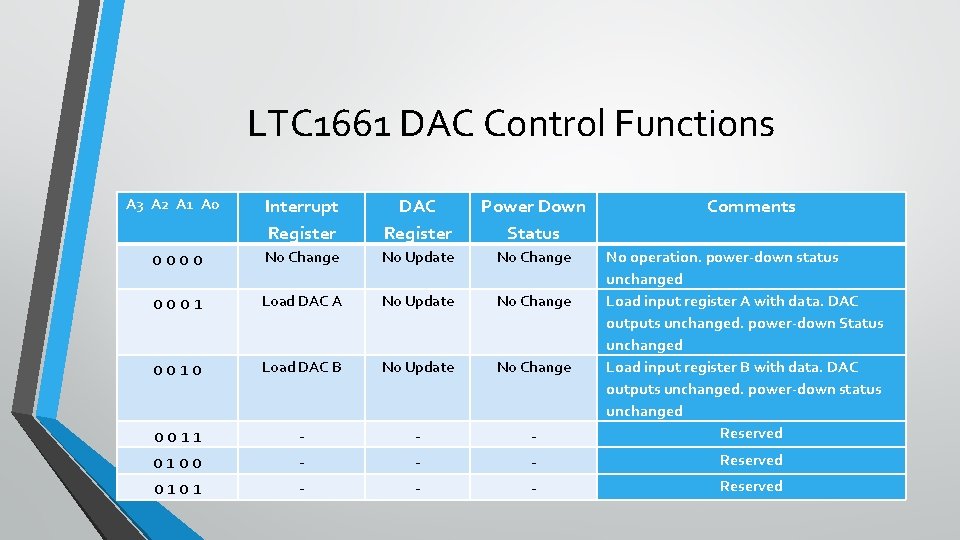

LTC 1661 DAC Control Functions A 3 A 2 A 1 A 0 Interrupt Register DAC Register Power Down Status 0 0 No Change No Update No Change 0 0 0 1 Load DAC A No Update No Change 0 0 1 0 Load DAC B No Update No Change 0 0 1 1 0 0 0 1 - - - Comments No operation. power-down status unchanged Load input register A with data. DAC outputs unchanged. power-down Status unchanged Load input register B with data. DAC outputs unchanged. power-down status unchanged Reserved 29

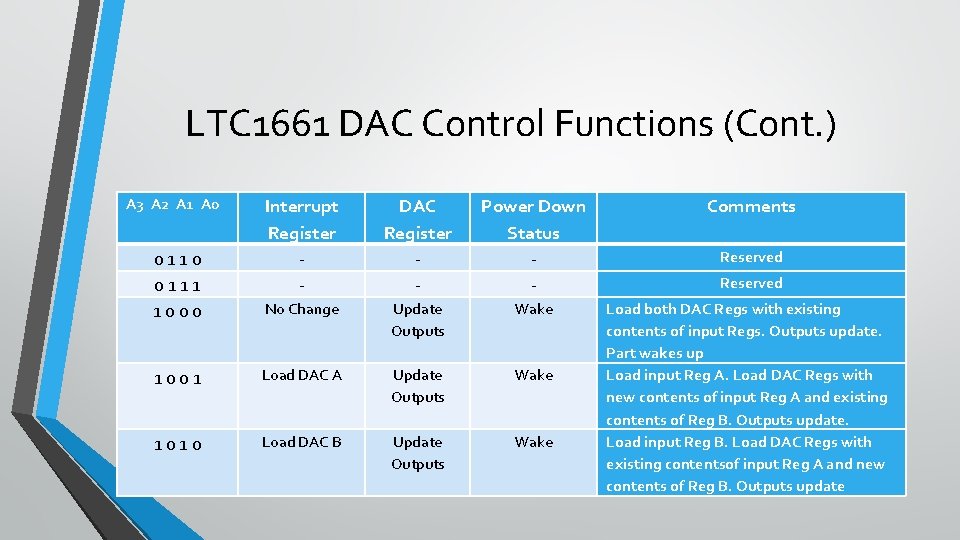

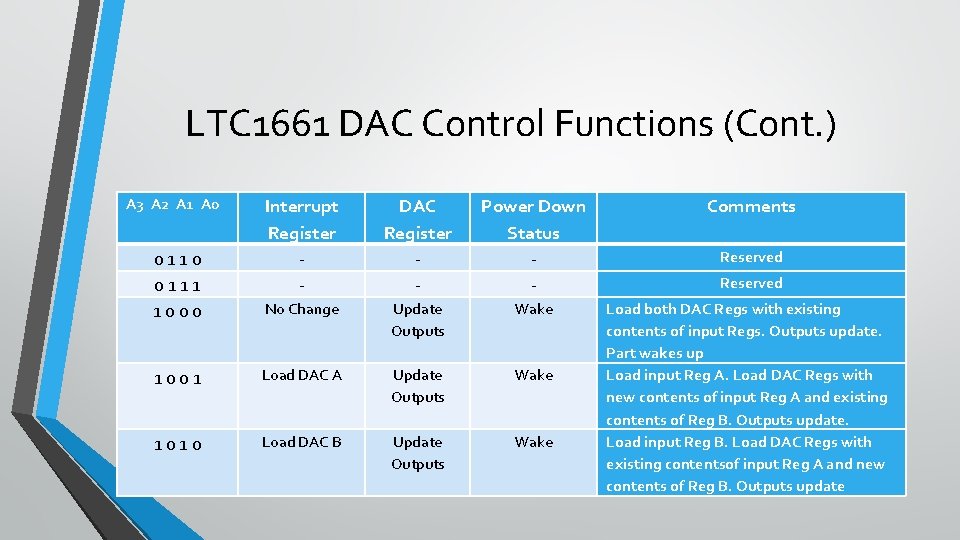

LTC 1661 DAC Control Functions (Cont. ) A 3 A 2 A 1 A 0 Interrupt Register - DAC Register - Power Down Status - Comments No Change Update Outputs Wake 1 0 0 1 Load DAC A Update Outputs Wake 1 0 Load DAC B Update Outputs Wake Load both DAC Regs with existing contents of input Regs. Outputs update. Part wakes up Load input Reg A. Load DAC Regs with new contents of input Reg A and existing contents of Reg B. Outputs update. Load input Reg B. Load DAC Regs with existing contentsof input Reg A and new 30 contents of Reg B. Outputs update 0 1 1 0 0 0 Reserved

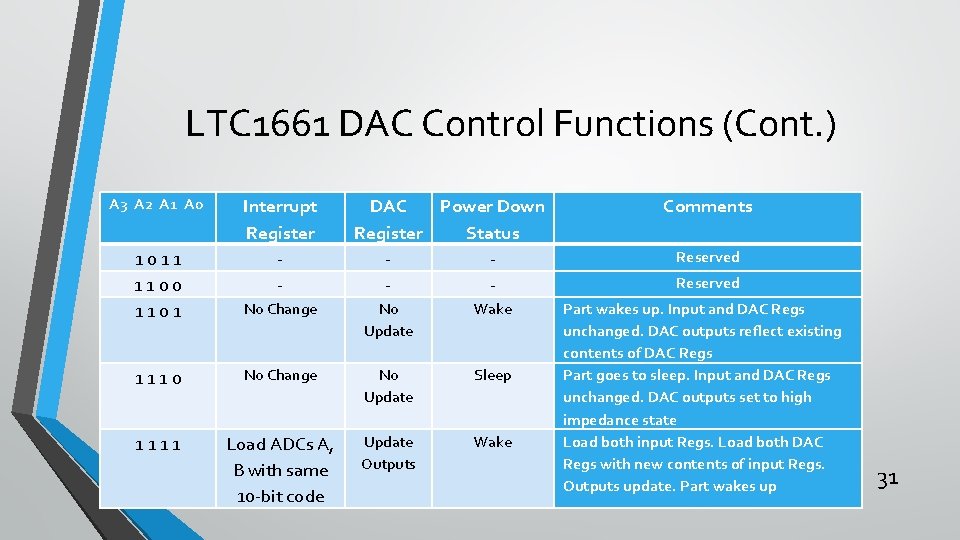

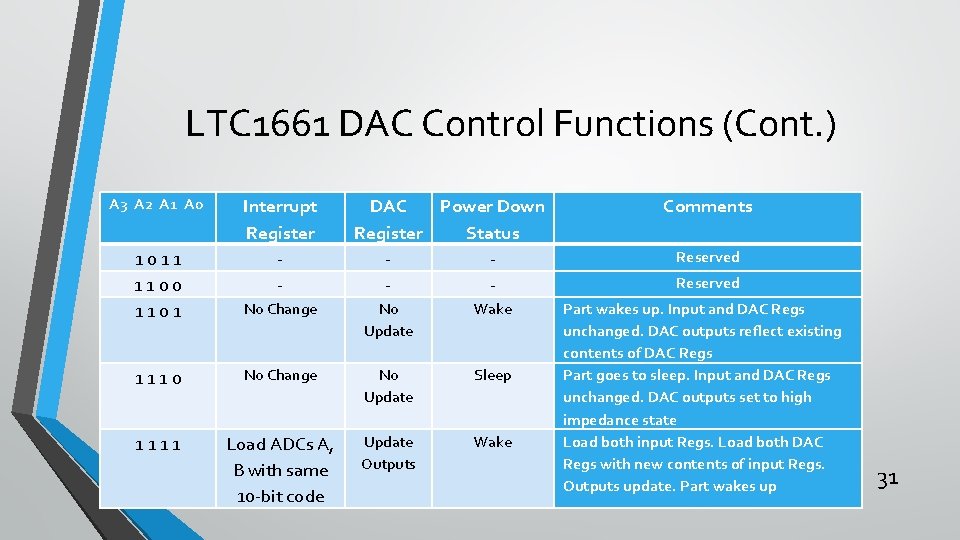

LTC 1661 DAC Control Functions (Cont. ) A 3 A 2 A 1 A 0 1 1 1 1 0 0 1 1 0 1 Interrupt Register - DAC Power Down Register Status - No Change No Update Wake 1 1 1 0 No Change No Update Sleep 1 1 Load ADCs A, B with same 10 -bit code Update Outputs Wake Comments Reserved Part wakes up. Input and DAC Regs unchanged. DAC outputs reflect existing contents of DAC Regs Part goes to sleep. Input and DAC Regs unchanged. DAC outputs set to high impedance state Load both input Regs. Load both DAC Regs with new contents of input Regs. Outputs update. Part wakes up 31

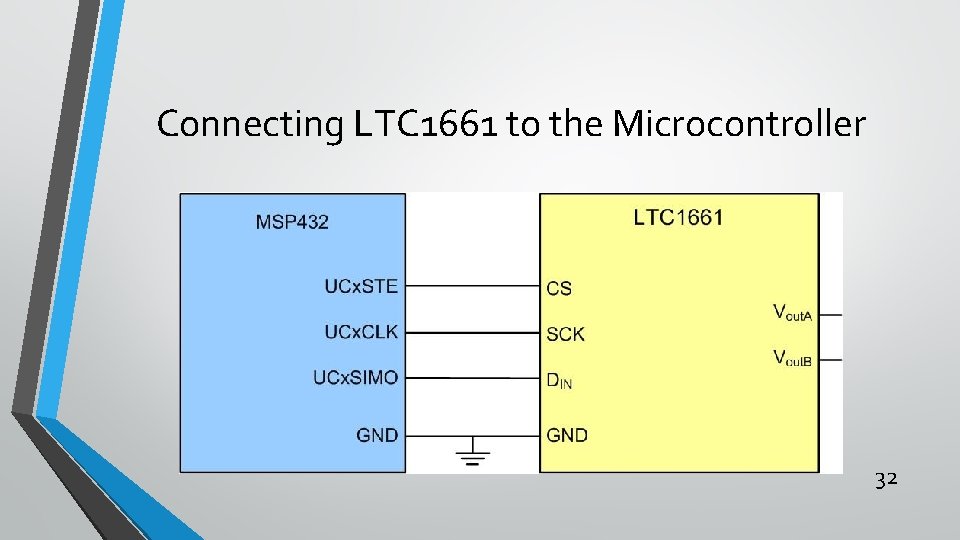

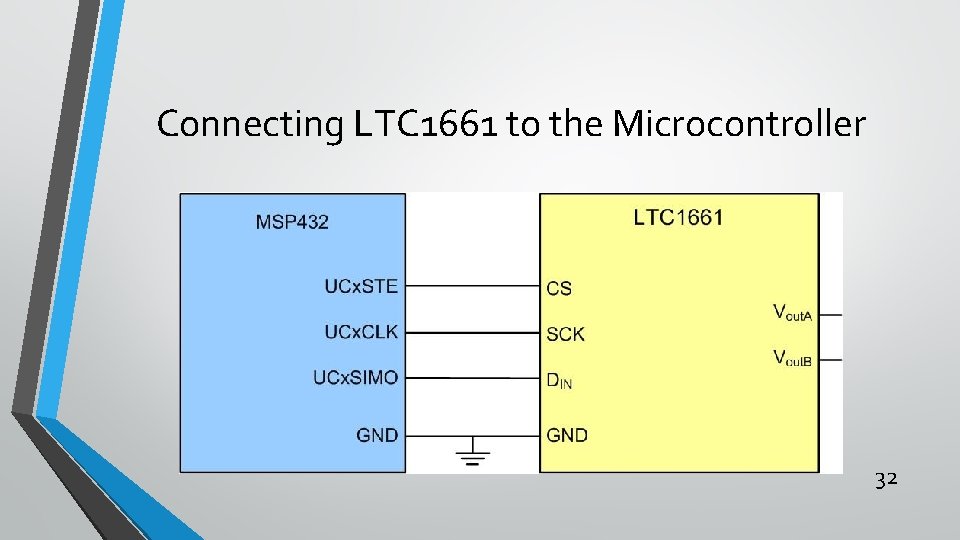

Connecting LTC 1661 to the Microcontroller 32

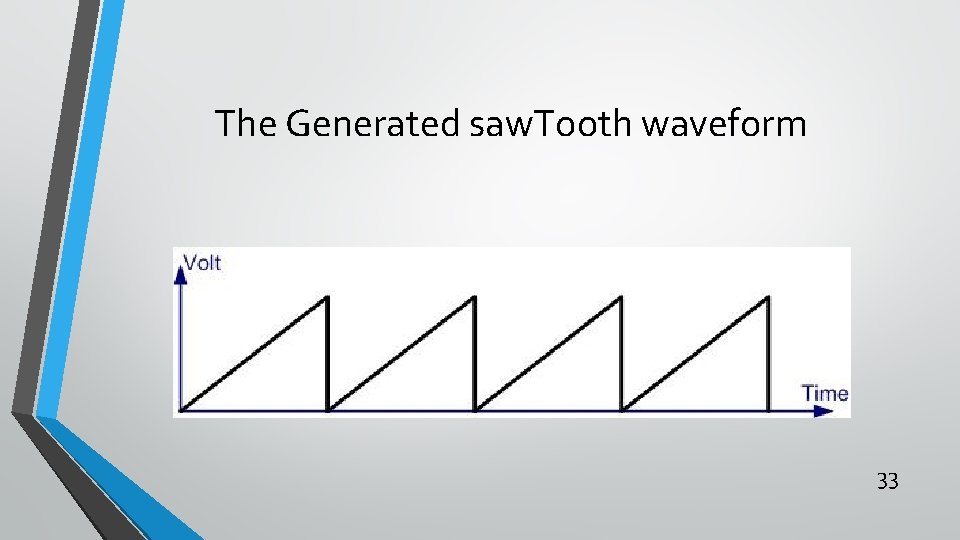

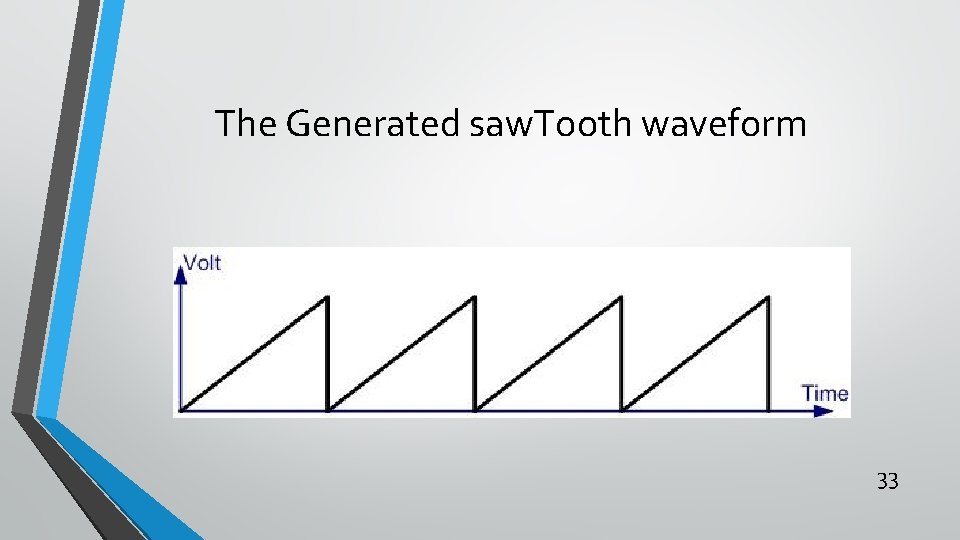

The Generated saw. Tooth waveform 33