Chapter 8 Main Memory CSS 503 Systems Programming

- Slides: 26

Chapter 8: Main Memory CSS 503 Systems Programming Prof. Munehiro Fukuda Computing & Software Systems University of Washington Bothell CSS 503 Chapter 8: Main Memory 0

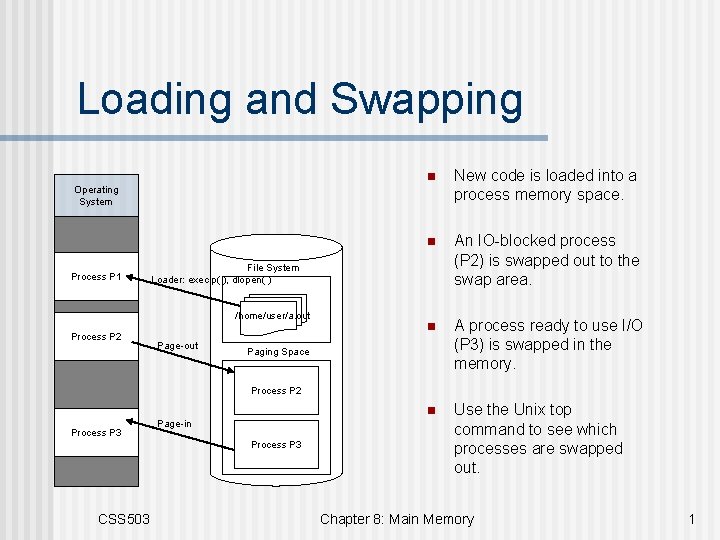

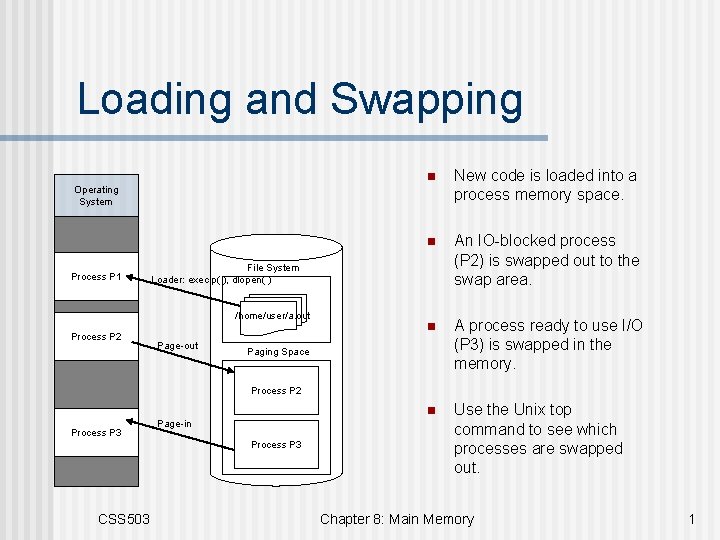

Loading and Swapping Operating System Process P 1 New code is loaded into a process memory space. n An IO-blocked process (P 2) is swapped out to the swap area. n A process ready to use I/O (P 3) is swapped in the memory. n Use the Unix top command to see which processes are swapped out. File System Loader: execlp( ), dlopen( ) /home/user/a. out Process P 2 n Page-out Paging Space Process P 2 Process P 3 Page-in Process P 3 CSS 503 Chapter 8: Main Memory 1

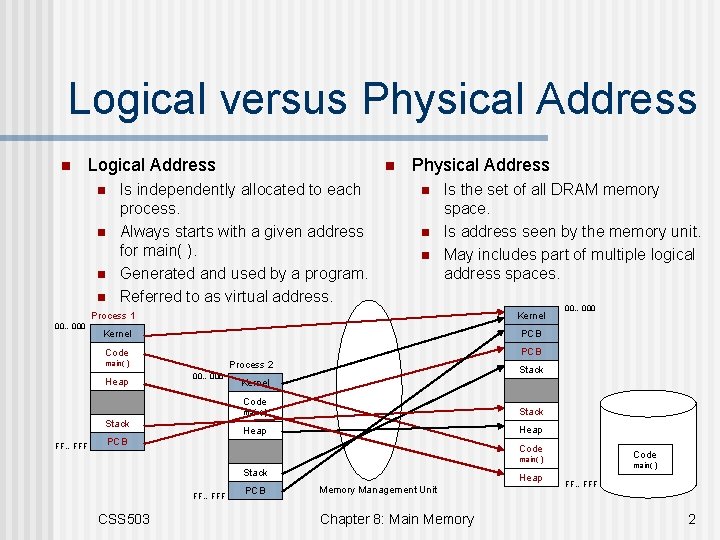

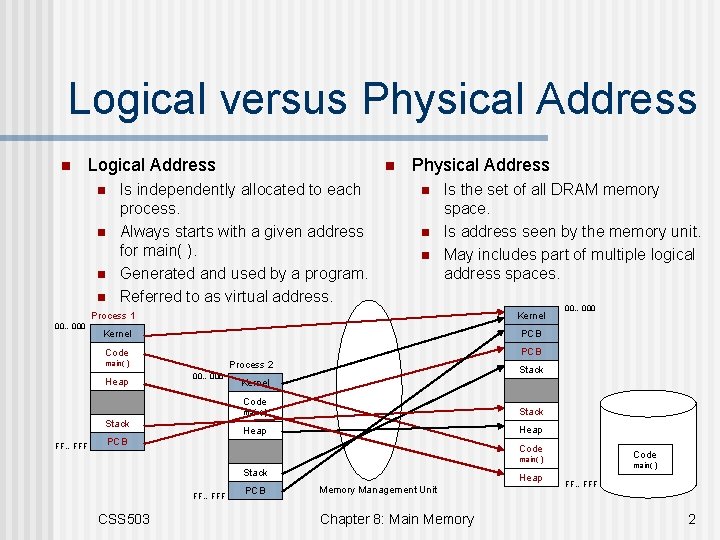

Logical versus Physical Address n Logical Address n n n Is independently allocated to each process. Always starts with a given address for main( ). Generated and used by a program. Referred to as virtual address. Physical Address n n n Is the set of all DRAM memory space. Is address seen by the memory unit. May includes part of multiple logical address spaces. Kernel Process 1 00… 000 Kernel PCB Code PCB main( ) Heap Process 2 00… 000 Stack Kernel Code Stack FF…FFF PCB 00… 000 main( ) Stack Heap Code main( ) Stack FF…FFF CSS 503 PCB Heap Memory Management Unit Chapter 8: Main Memory main( ) FF…FFF 2

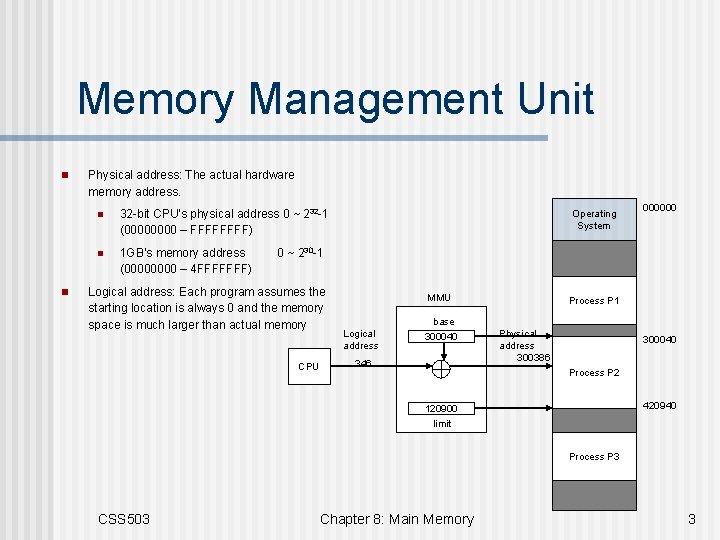

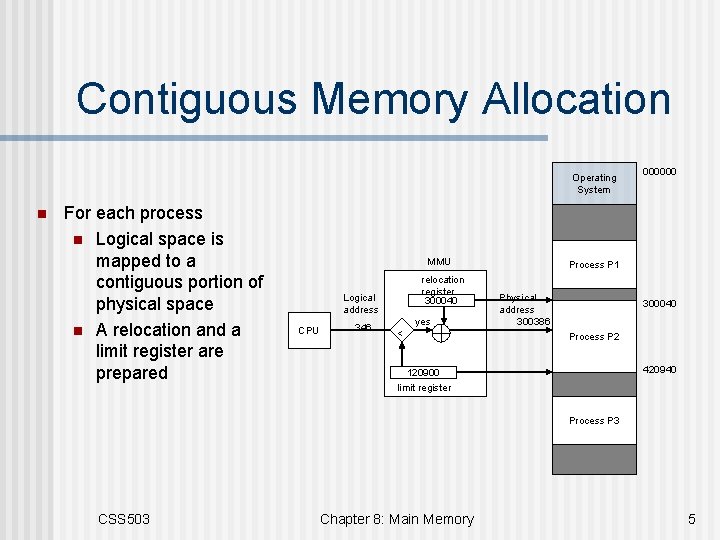

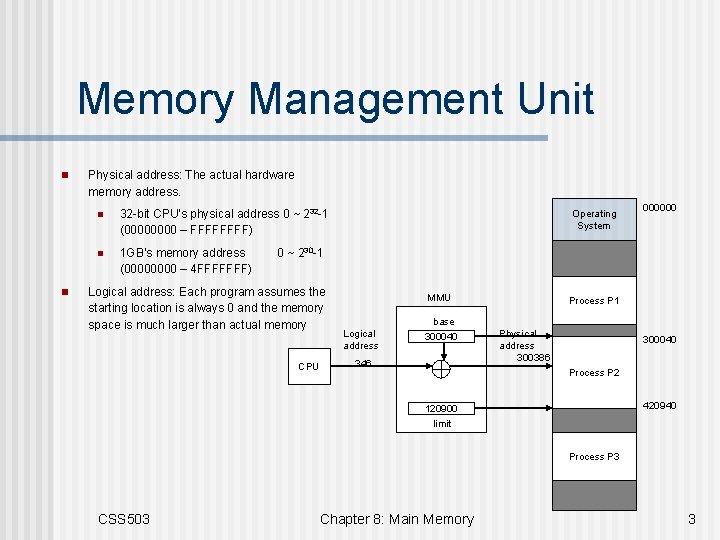

Memory Management Unit n n Physical address: The actual hardware memory address. n 32 -bit CPU’s physical address 0 ~ 232 -1 (0000 – FFFF) n 1 GB’s memory address (0000 – 4 FFFFFFF) Operating System 000000 0 ~ 230 -1 Logical address: Each program assumes the starting location is always 0 and the memory space is much larger than actual memory CPU MMU Logical address base 300040 346 Process P 1 Physical address 300386 300040 Process P 2 420940 120900 limit Process P 3 CSS 503 Chapter 8: Main Memory 3

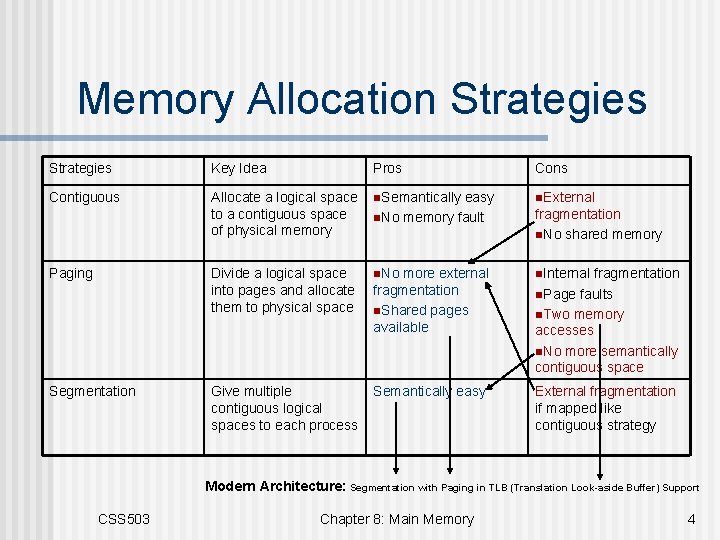

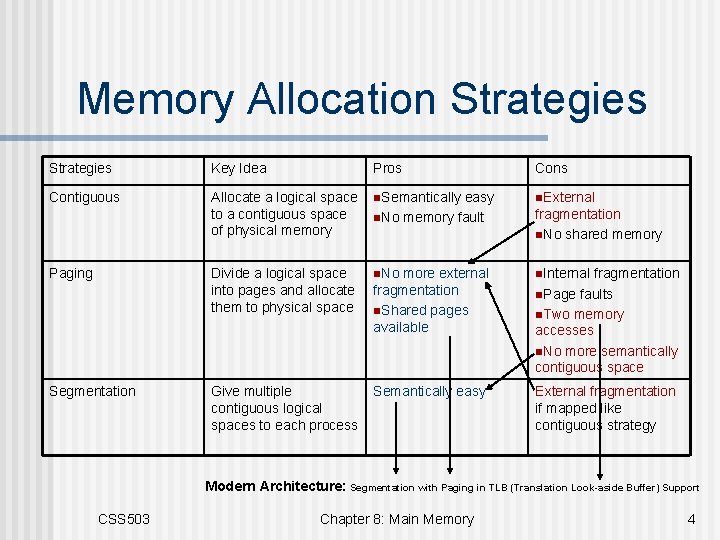

Memory Allocation Strategies Key Idea Pros Contiguous Allocate a logical space to a contiguous space of physical memory n. Semantically easy n. No memory fault n. External Paging Divide a logical space into pages and allocate them to physical space n. No more external fragmentation n. Shared pages available n. Internal Segmentation Give multiple contiguous logical spaces to each process Semantically easy External fragmentation if mapped like contiguous strategy fragmentation n. No shared memory fragmentation n. Page faults n. Two memory accesses n. No more semantically contiguous space Modern Architecture: Segmentation with Paging in TLB (Translation Look-aside Buffer) Support CSS 503 Chapter 8: Main Memory 4

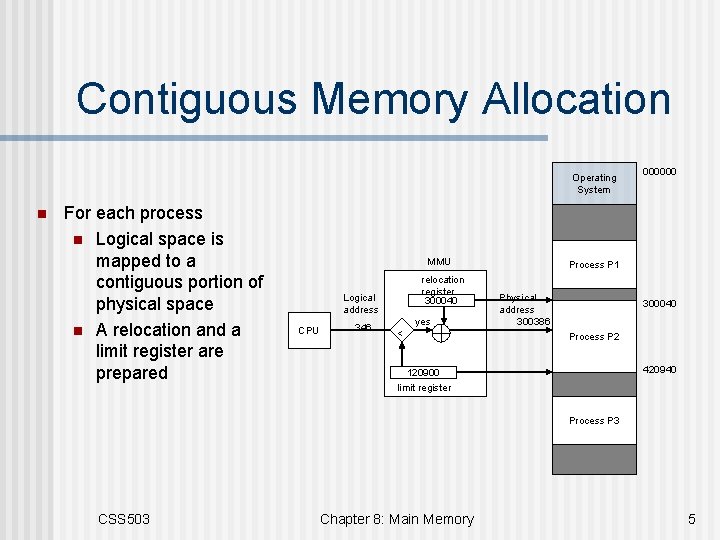

Contiguous Memory Allocation Operating System n For each process n Logical space is mapped to a contiguous portion of physical space n A relocation and a limit register are prepared MMU relocation register 300040 Logical address CPU 346 yes < 000000 Process P 1 Physical address 300386 300040 Process P 2 420940 120900 limit register Process P 3 CSS 503 Chapter 8: Main Memory 5

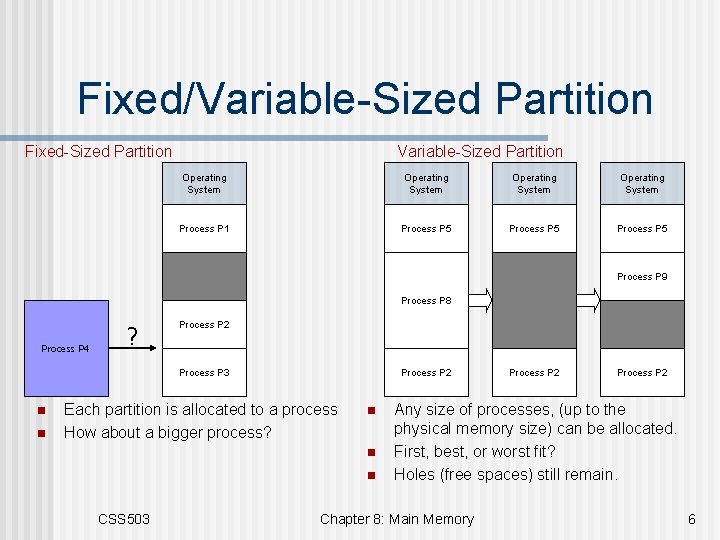

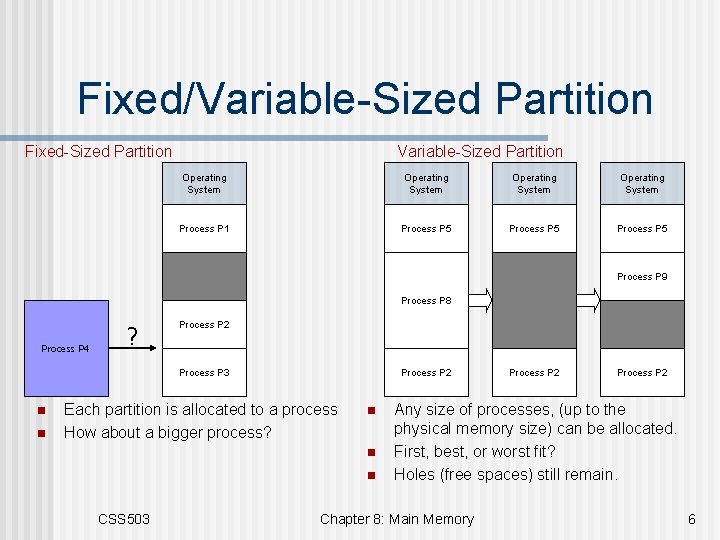

Fixed/Variable-Sized Partition Fixed-Sized Partition Variable-Sized Partition Operating System Process P 1 Process P 5 Process P 9 Process P 8 Process P 4 ? Process P 2 Process P 3 n n Process P 2 Each partition is allocated to a process How about a bigger process? n n n CSS 503 Process P 2 Any size of processes, (up to the physical memory size) can be allocated. First, best, or worst fit? Holes (free spaces) still remain. Chapter 8: Main Memory 6

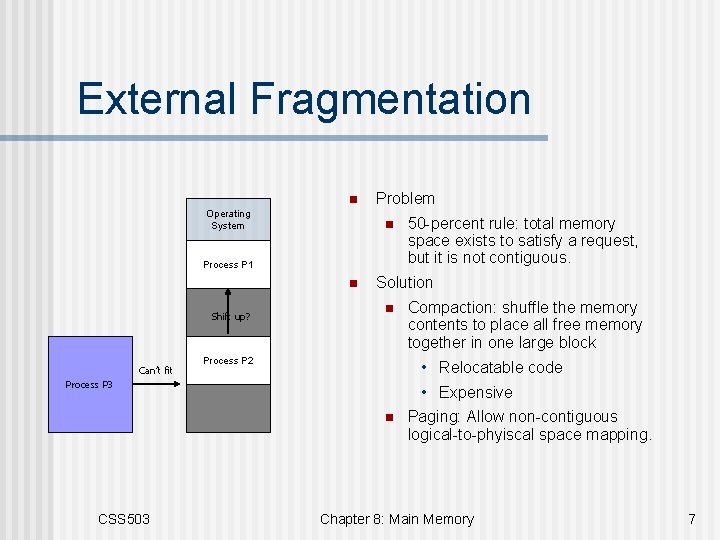

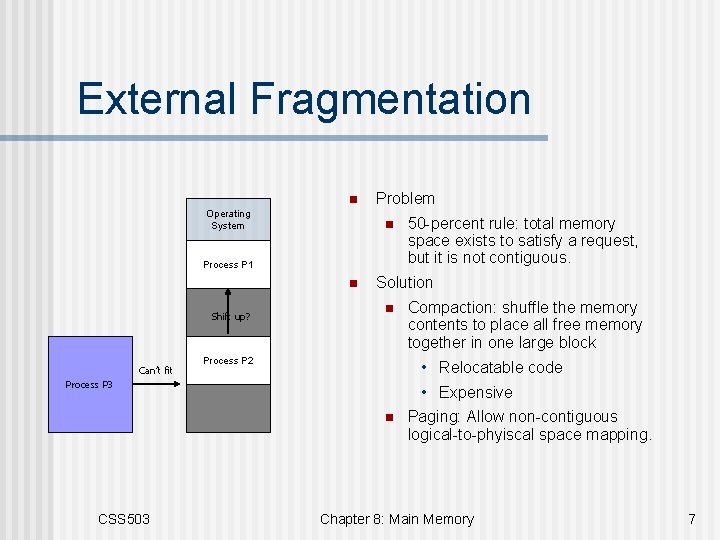

External Fragmentation n Operating System Problem n Process P 1 n Shift up? Can’t fit Solution n Process P 2 Compaction: shuffle the memory contents to place all free memory together in one large block • Relocatable code Process P 3 • Expensive n CSS 503 50 -percent rule: total memory space exists to satisfy a request, but it is not contiguous. Paging: Allow non-contiguous logical-to-phyiscal space mapping. Chapter 8: Main Memory 7

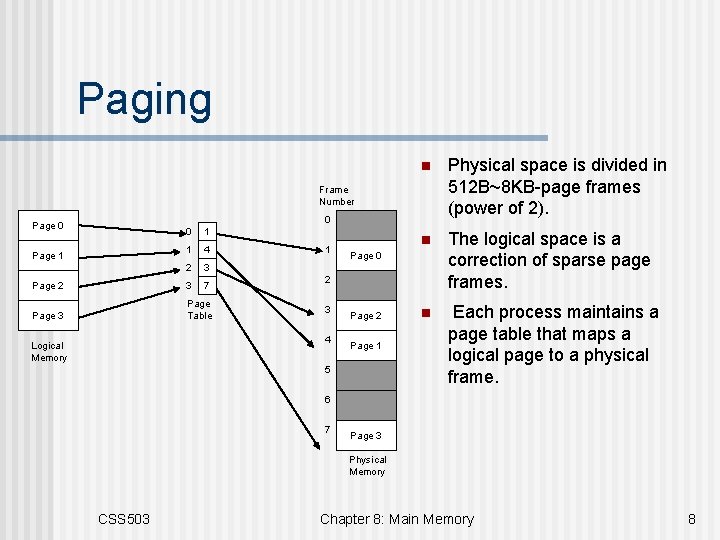

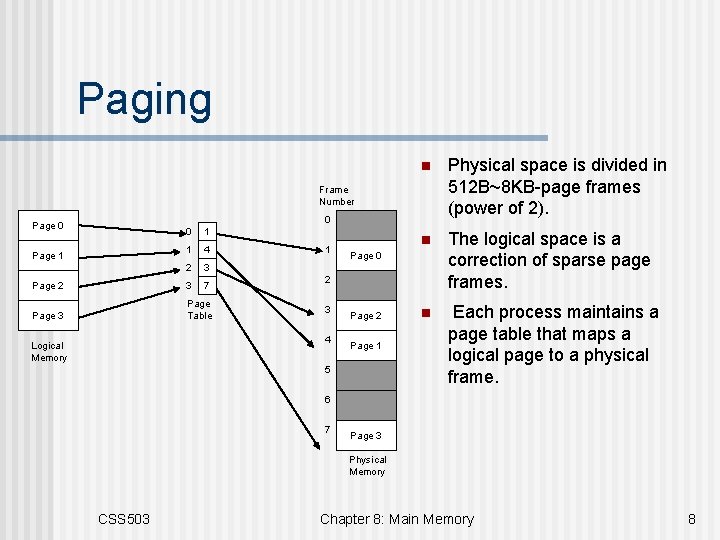

Paging n Physical space is divided in 512 B~8 KB-page frames (power of 2). n The logical space is a correction of sparse page frames. n Each process maintains a page table that maps a logical page to a physical frame. Frame Number 0 Page 0 0 1 1 4 2 3 Page 2 3 7 Page 3 Page Table Page 1 1 2 3 4 Logical Memory Page 0 Page 2 Page 1 5 6 7 Page 3 Physical Memory CSS 503 Chapter 8: Main Memory 8

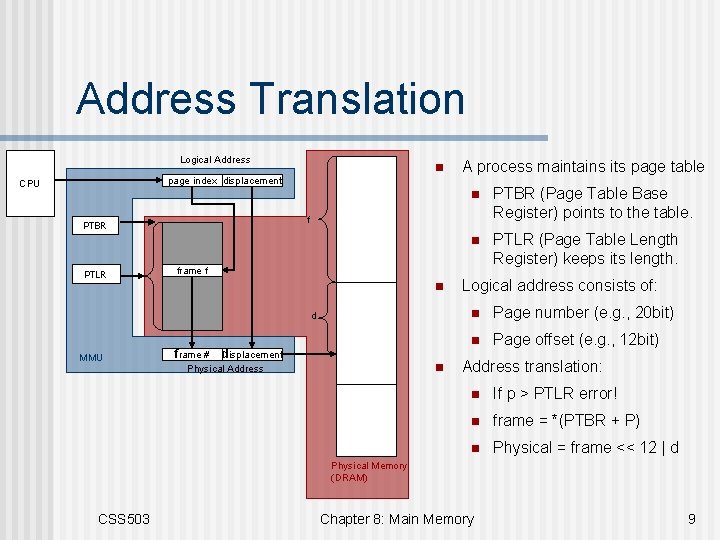

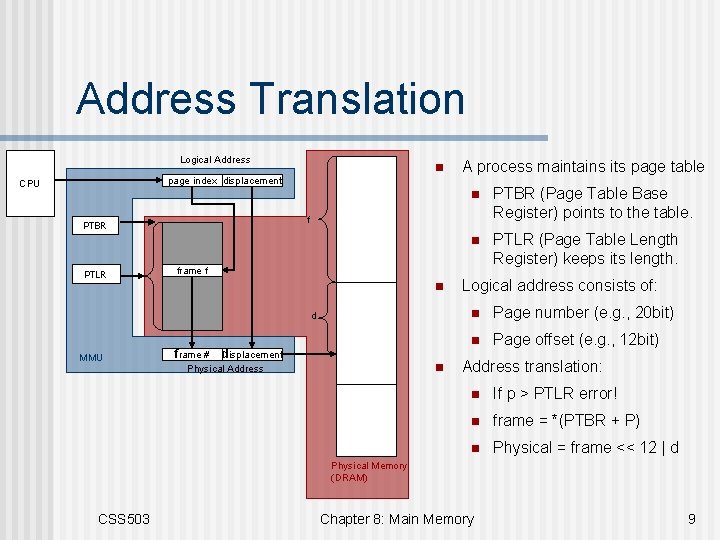

Address Translation Logical Address n page index displacement CPU PTBR (Page Table Base Register) points to the table. n PTLR (Page Table Length Register) keeps its length. frame f n d MMU n f PTBR PTLR A process maintains its page table frame # displacement n Physical Address Logical address consists of: n Page number (e. g. , 20 bit) n Page offset (e. g. , 12 bit) Address translation: n If p > PTLR error! n frame = *(PTBR + P) n Physical = frame << 12 | d Physical Memory (DRAM) CSS 503 Chapter 8: Main Memory 9

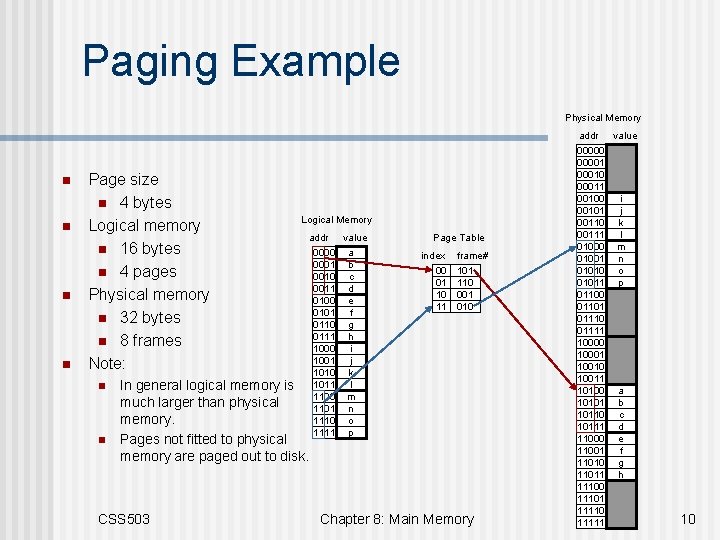

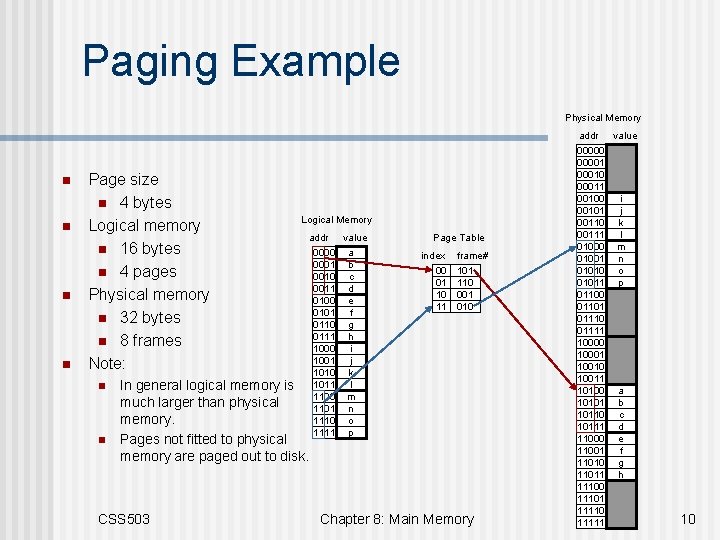

Paging Example Physical Memory n n Page size n 4 bytes Logical memory n 16 bytes n 4 pages Physical memory n 32 bytes n 8 frames Note: n n Logical Memory addr value 0000 a 0001 b 0010 c 0011 d 0100 e 0101 f 0110 g 0111 h 1000 i 1001 j 1010 k 1011 l 1100 m 1101 n 1110 o 1111 p Page Table index 00 01 10 11 frame# 101 110 001 010 In general logical memory is much larger than physical memory. Pages not fitted to physical memory are paged out to disk. CSS 503 Chapter 8: Main Memory addr value 000001 00010 00011 00100 i 00101 j 00110 k 00111 l 01000 m 01001 n 01010 o 01011 p 01100 01101 01110 01111 10000 10001 10010 10011 10100 a 10101 b 10110 c 10111 d 11000 e 11001 f 11010 g 11011 h 11100 11101 11110 11111 10

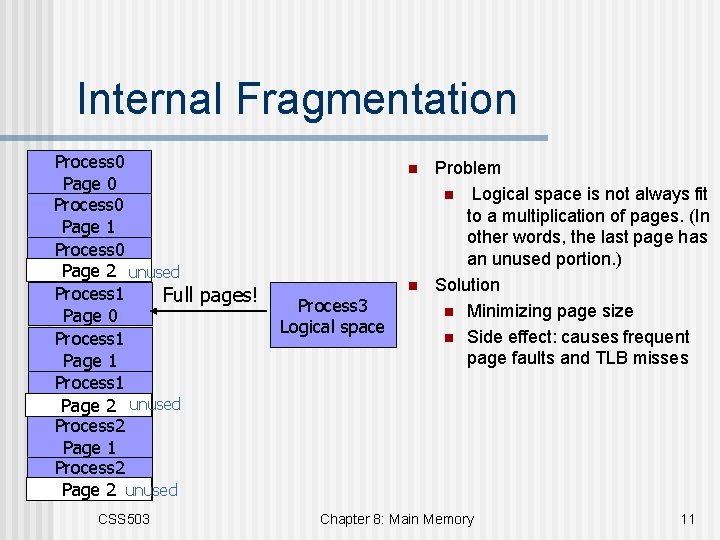

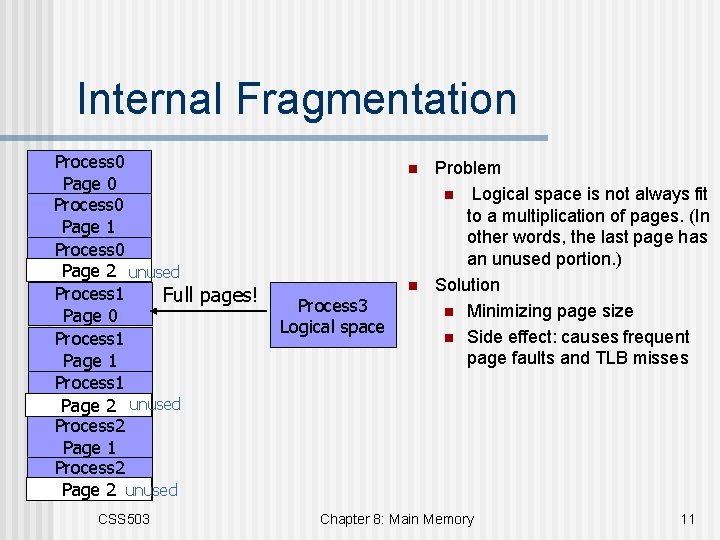

Internal Fragmentation Process 0 Page 0 Process 0 Page 1 Process 0 Page 2 0 unused Process 1 Full pages! Page 0 Process 1 Page 1 Process 1 Page 20 unused Page Process 2 Page 1 Process 2 Page 20 unused CSS 503 n Process 3 Logical space n Problem n Logical space is not always fit to a multiplication of pages. (In other words, the last page has an unused portion. ) Solution n Minimizing page size n Side effect: causes frequent page faults and TLB misses Chapter 8: Main Memory 11

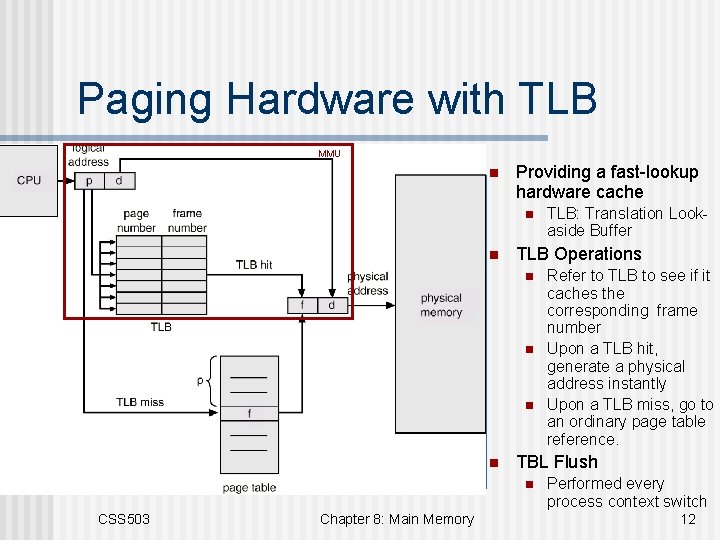

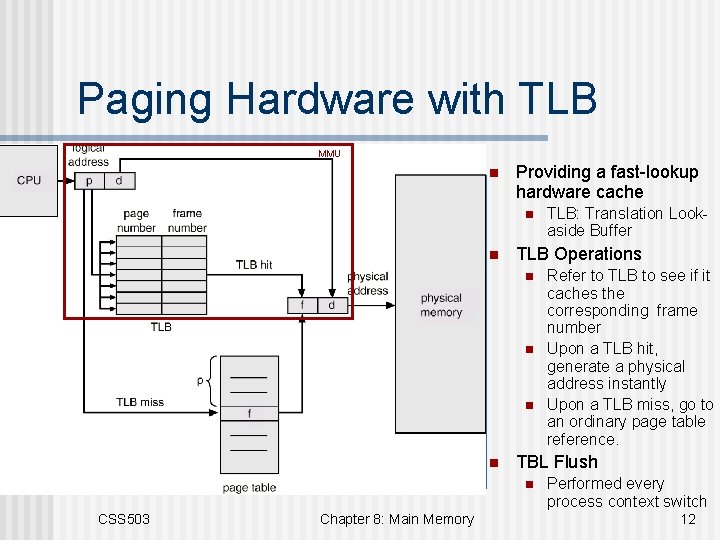

Paging Hardware with TLB MMU n Providing a fast-lookup hardware cache n n TLB Operations n Two memory accesses! n n DRAM Memory CSS 503 Chapter 8: Main Memory n TLB: Translation Lookaside Buffer Refer to TLB to see if it caches the corresponding frame number Upon a TLB hit, generate a physical address instantly Upon a TLB miss, go to an ordinary page table reference. TBL Flush n Performed every process context switch 12

Discussions 1 1. 2. 3. Discuss about the pros and cons of large and small page size. How does TLB contribute to making thread context switch cheaper than process context switch? Consider cases when TLB is not so useful. CSS 503 Chapter 8: Main Memory 13

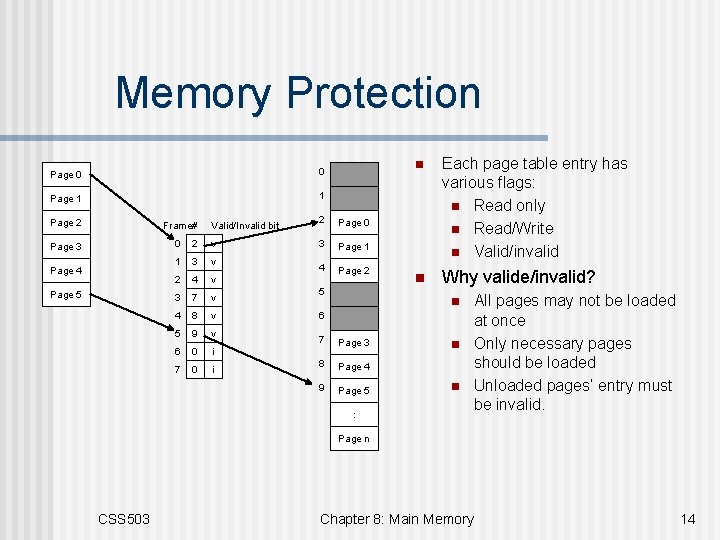

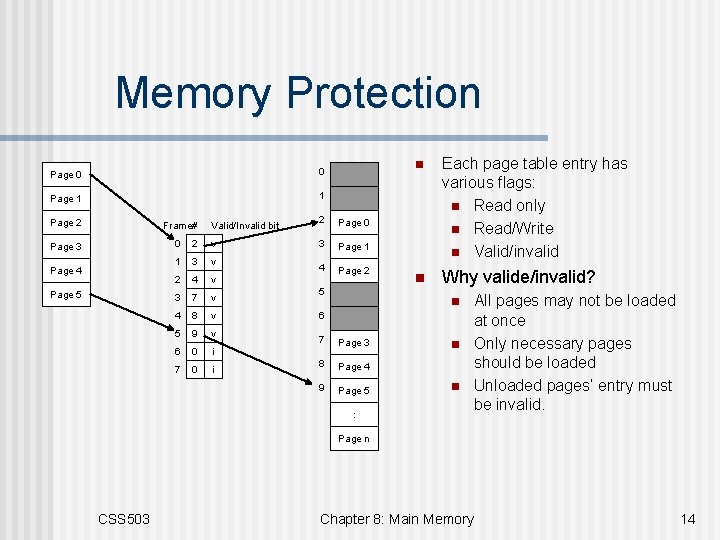

Memory Protection Page 0 0 Page 1 1 Page 2 Frame# Page 3 0 2 v 1 3 v 2 4 v Page 4 Page 5 Valid/Invalid bit 3 7 v 4 8 v 5 9 v 6 0 i 7 0 i 2 Page 0 3 Page 1 4 Page 2 5 n Each page table entry has various flags: n Read only n Read/Write n Valid/invalid n Why valide/invalid? n 6 7 Page 3 8 Page 4 9 Page 5 n n : All pages may not be loaded at once Only necessary pages should be loaded Unloaded pages’ entry must be invalid. Page n CSS 503 Chapter 8: Main Memory 14

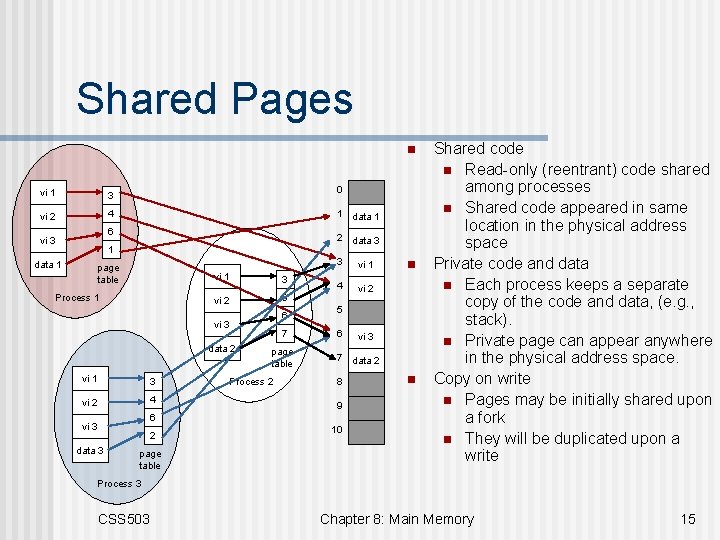

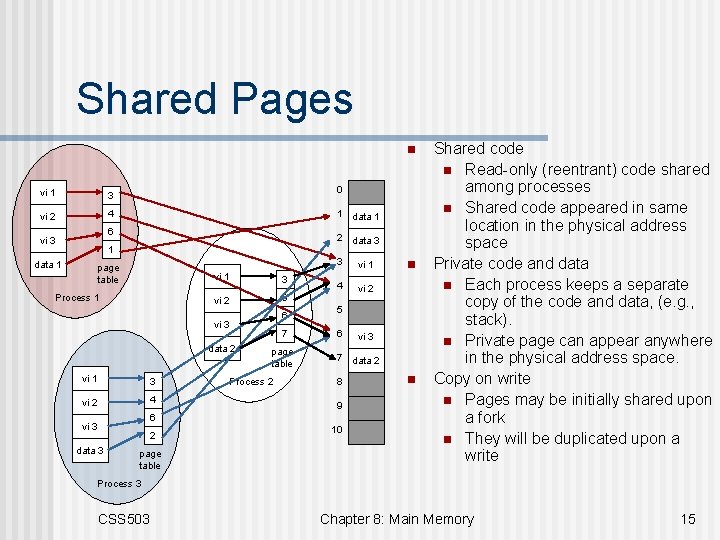

Shared Pages n vi 1 3 vi 2 4 1 data 1 6 vi 3 data 1 0 2 data 3 1 page table Process 1 vi 1 3 vi 2 6 6 vi 3 data 2 vi 1 3 vi 2 4 7 page table Process 2 3 vi 1 4 vi 2 5 6 2 data 3 page table vi 3 7 data 2 8 9 6 vi 3 n 10 n Shared code n Read-only (reentrant) code shared among processes n Shared code appeared in same location in the physical address space Private code and data n Each process keeps a separate copy of the code and data, (e. g. , stack). n Private page can appear anywhere in the physical address space. Copy on write n Pages may be initially shared upon a fork n They will be duplicated upon a write Process 3 CSS 503 Chapter 8: Main Memory 15

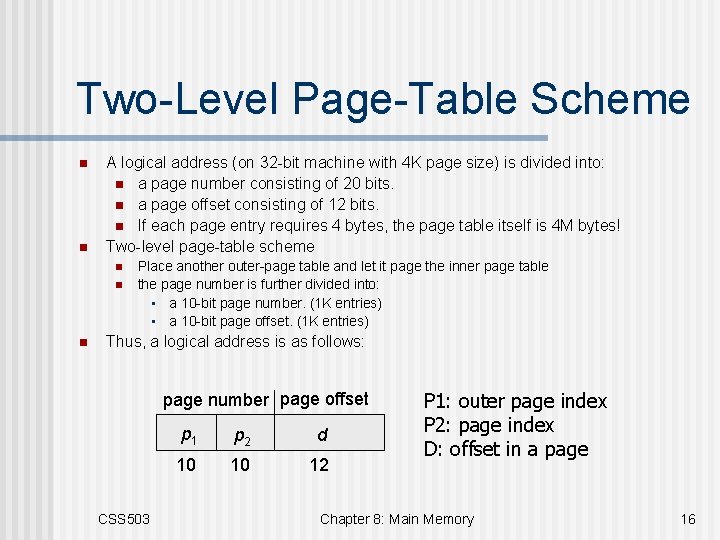

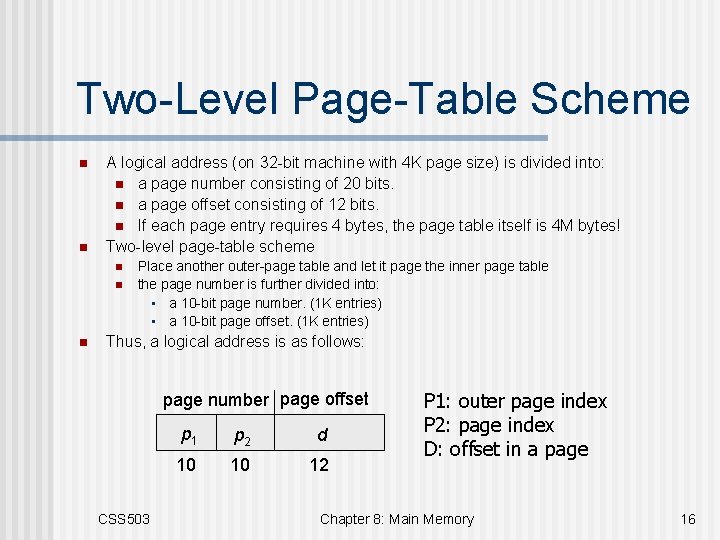

Two-Level Page-Table Scheme n n A logical address (on 32 -bit machine with 4 K page size) is divided into: n a page number consisting of 20 bits. n a page offset consisting of 12 bits. n If each page entry requires 4 bytes, the page table itself is 4 M bytes! Two-level page-table scheme n n n Place another outer-page table and let it page the inner page table the page number is further divided into: • a 10 -bit page number. (1 K entries) • a 10 -bit page offset. (1 K entries) Thus, a logical address is as follows: page number page offset CSS 503 p 1 p 2 d 10 10 12 P 1: outer page index P 2: page index D: offset in a page Chapter 8: Main Memory 16

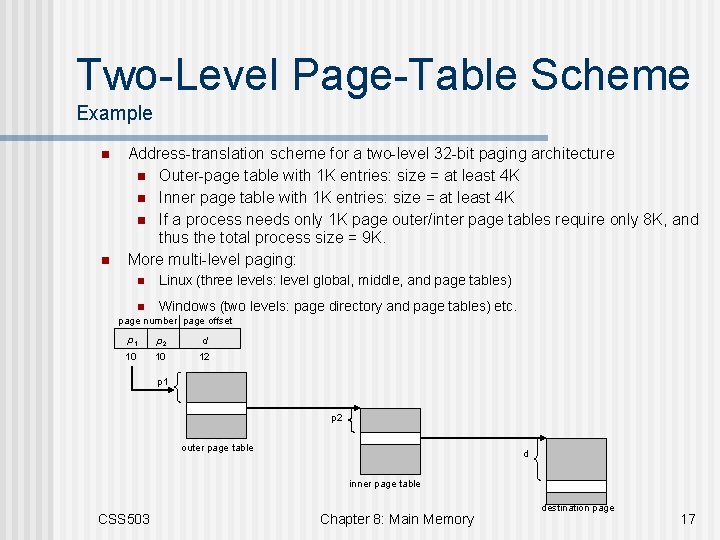

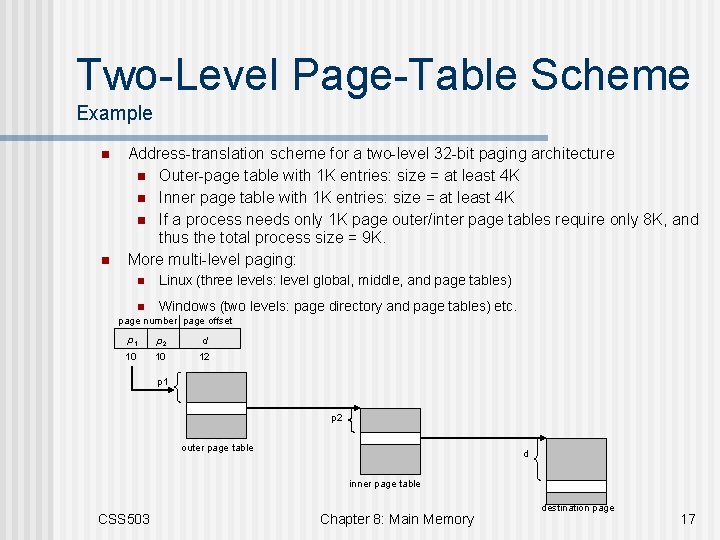

Two-Level Page-Table Scheme Example n n Address-translation scheme for a two-level 32 -bit paging architecture n Outer-page table with 1 K entries: size = at least 4 K n Inner page table with 1 K entries: size = at least 4 K n If a process needs only 1 K page outer/inter page tables require only 8 K, and thus the total process size = 9 K. More multi-level paging: n Linux (three levels: level global, middle, and page tables) n Windows (two page number page offset p 1 p 2 d 10 10 12 levels: page directory and page tables) etc. p 1 p 2 outer page table d inner page table CSS 503 Chapter 8: Main Memory destination page 17

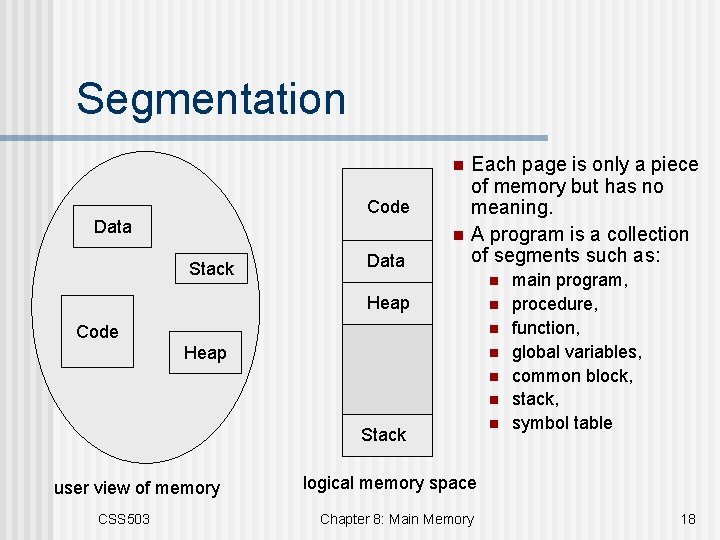

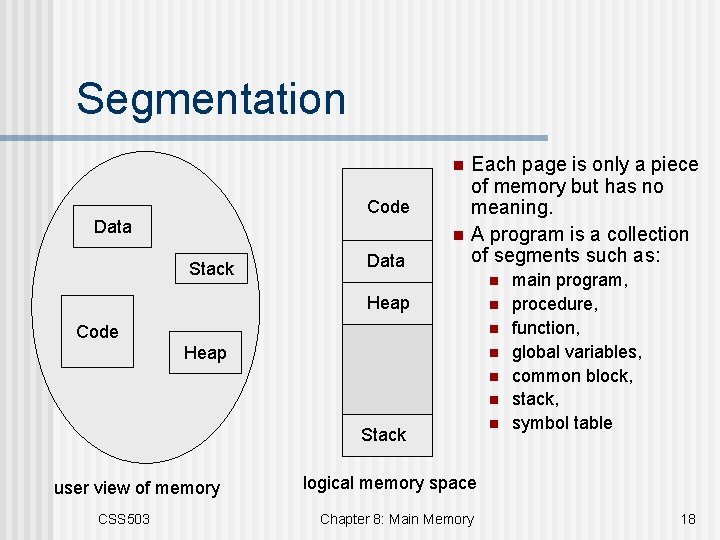

Segmentation n Code Data n Stack Data Each page is only a piece of memory but has no meaning. A program is a collection of segments such as: n Heap Code n n Heap n n n Stack user view of memory CSS 503 n main program, procedure, function, global variables, common block, stack, symbol table logical memory space Chapter 8: Main Memory 18

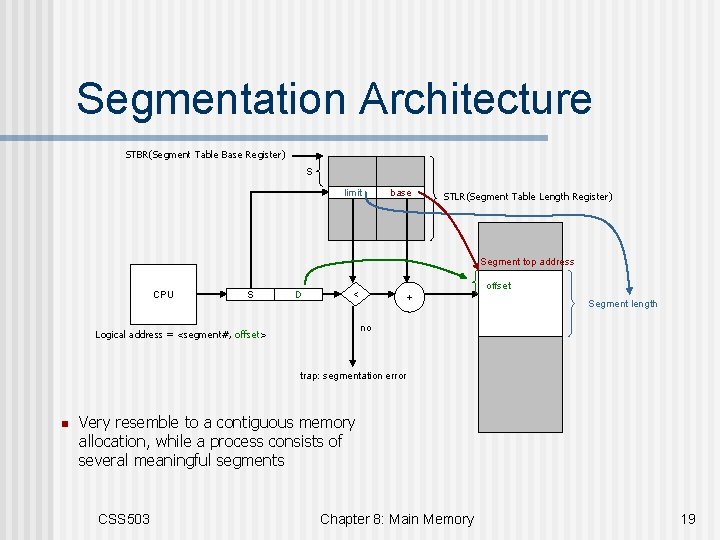

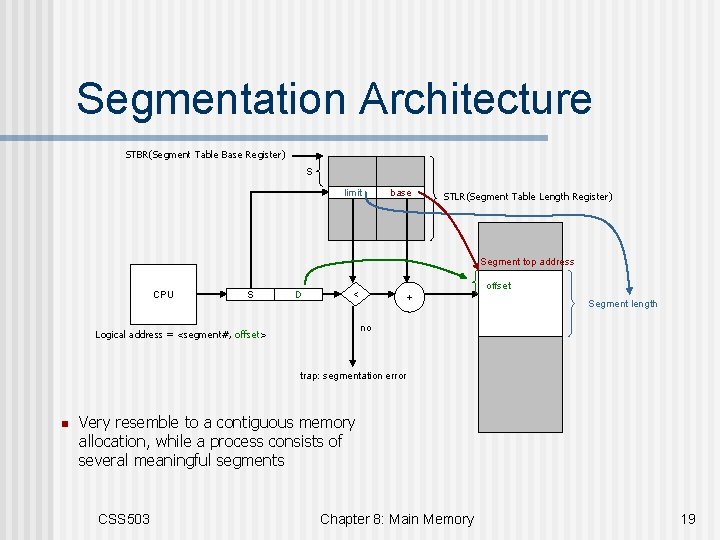

Segmentation Architecture STBR(Segment Table Base Register) S limit base STLR(Segment Table Length Register) Segment top address CPU S D offset < + Segment length no Logical address = <segment#, offset> trap: segmentation error n Very resemble to a contiguous memory allocation, while a process consists of several meaningful segments CSS 503 Chapter 8: Main Memory 19

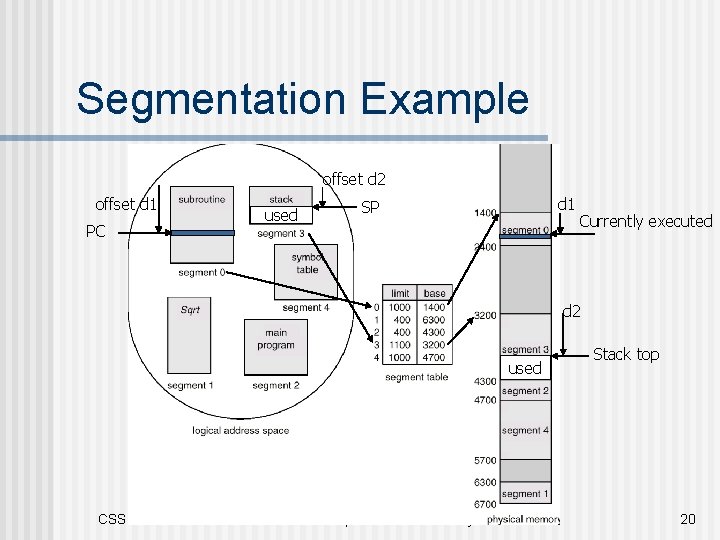

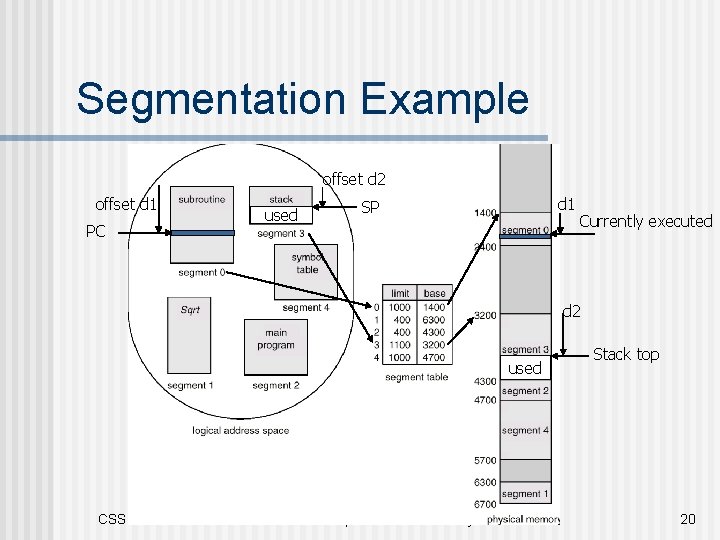

Segmentation Example offset d 2 offset d 1 PC used d 1 SP Currently executed d 2 used CSS 503 Chapter 8: Main Memory Stack top 20

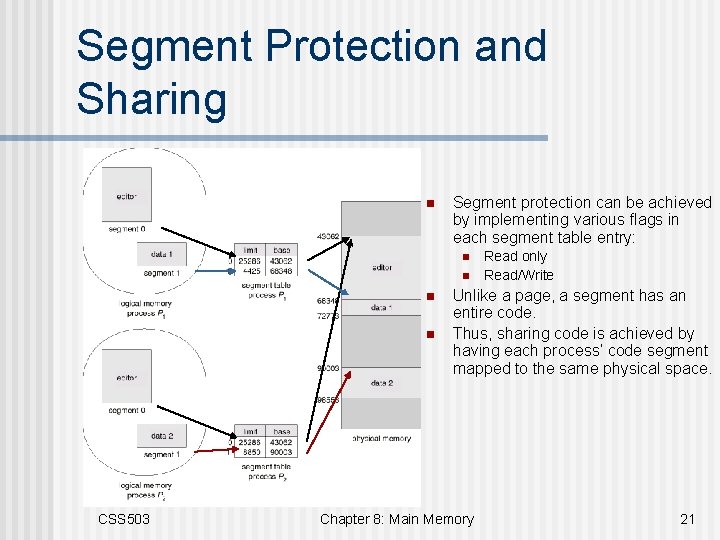

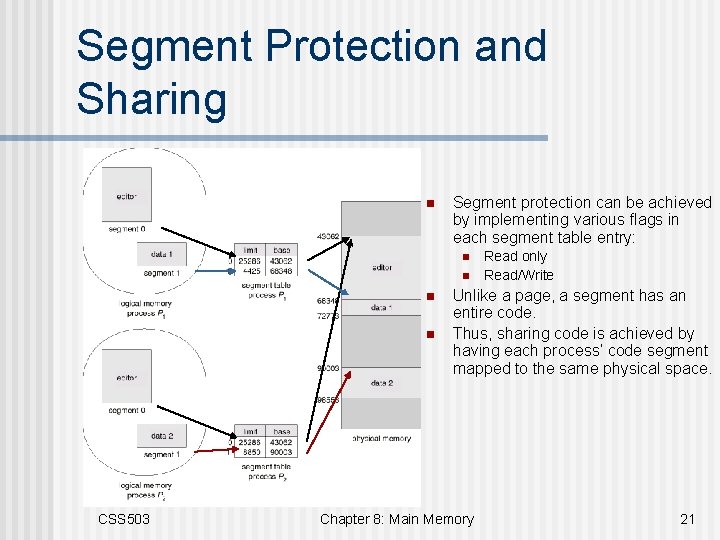

Segment Protection and Sharing n Segment protection can be achieved by implementing various flags in each segment table entry: n n CSS 503 Read only Read/Write Unlike a page, a segment has an entire code. Thus, sharing code is achieved by having each process’ code segment mapped to the same physical space. Chapter 8: Main Memory 21

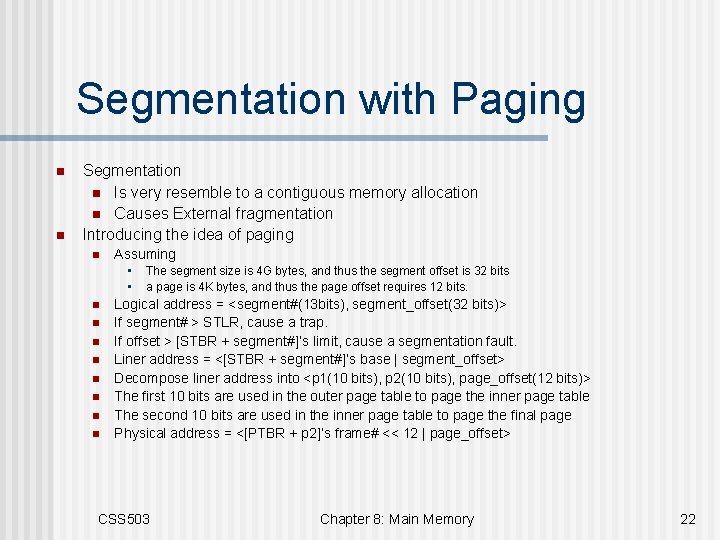

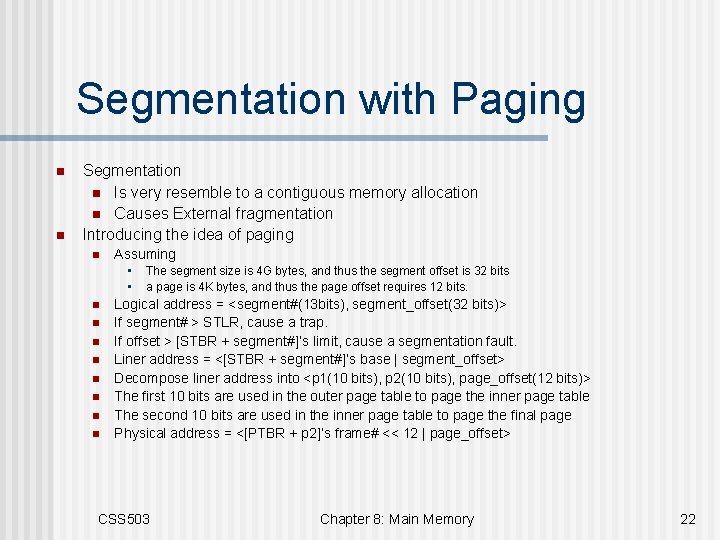

Segmentation with Paging n n Segmentation n Is very resemble to a contiguous memory allocation n Causes External fragmentation Introducing the idea of paging n Assuming • • n n n n The segment size is 4 G bytes, and thus the segment offset is 32 bits a page is 4 K bytes, and thus the page offset requires 12 bits. Logical address = <segment#(13 bits), segment_offset(32 bits)> If segment# > STLR, cause a trap. If offset > [STBR + segment#]’s limit, cause a segmentation fault. Liner address = <[STBR + segment#]’s base | segment_offset> Decompose liner address into <p 1(10 bits), p 2(10 bits), page_offset(12 bits)> The first 10 bits are used in the outer page table to page the inner page table The second 10 bits are used in the inner page table to page the final page Physical address = <[PTBR + p 2]’s frame# << 12 | page_offset> CSS 503 Chapter 8: Main Memory 22

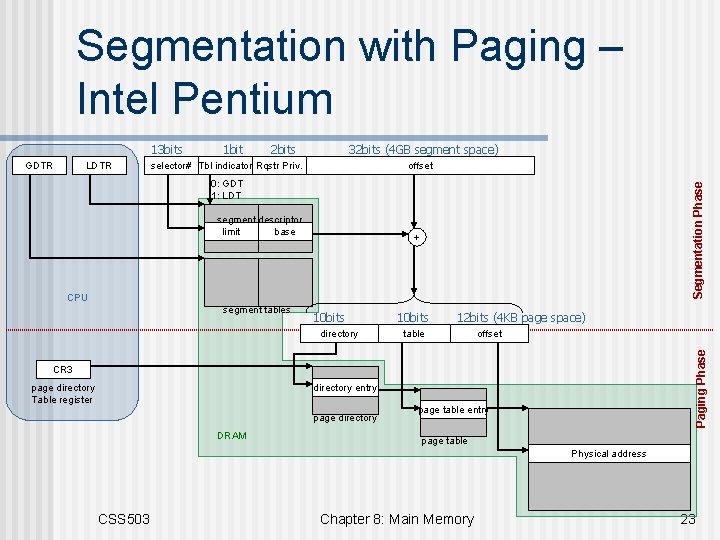

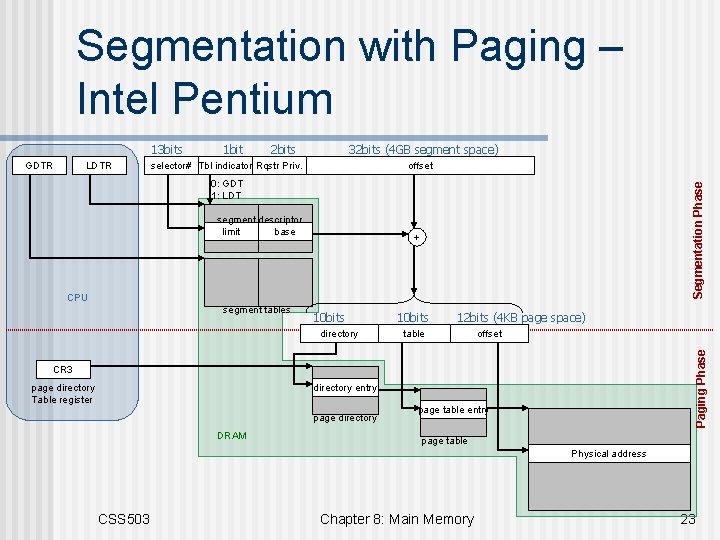

Segmentation with Paging – Intel Pentium 13 bits GDTR LDTR 1 bit 2 bits 32 bits (4 GB segment space) selector# Tbl indicator Rqstr Priv. offset segment descriptor limit base Segmentation Phase 0: GDT 1: LDT + CPU 10 bits directory 10 bits 12 bits (4 KB page space) table offset Paging Phase segment tables CR 3 directory entry page directory Table register page directory DRAM page table entry page table Physical address CSS 503 Chapter 8: Main Memory 23

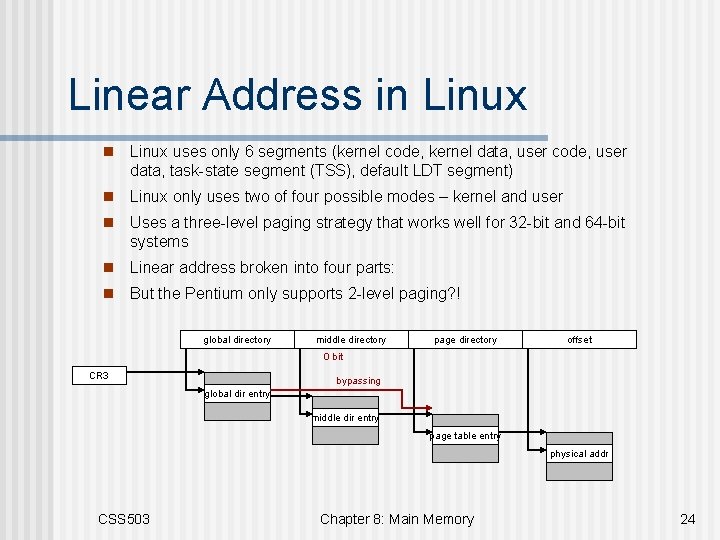

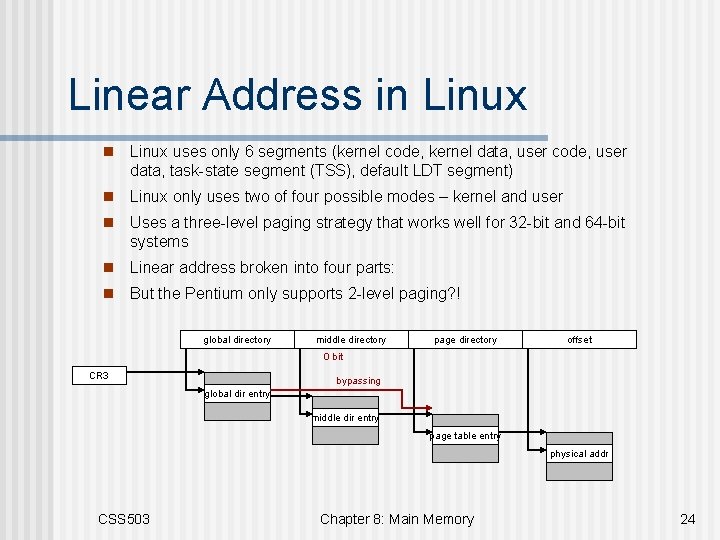

Linear Address in Linux uses only 6 segments (kernel code, kernel data, user code, user data, task-state segment (TSS), default LDT segment) n Linux only uses two of four possible modes – kernel and user n Uses a three-level paging strategy that works well for 32 -bit and 64 -bit systems n Linear address broken into four parts: n But the Pentium only supports 2 -level paging? ! global directory middle directory page directory offset 0 bit CR 3 bypassing global dir entry middle dir entry page table entry physical addr CSS 503 Chapter 8: Main Memory 24

Discussion 2 n Discuss about the textbook exercises: 8. 8 n 8. 12 n 8. 19 n 8. 23 n 8. 25 n 8. 28 n CSS 503 Chapter 8: Main Memory 25