Chapter 7 Timers 1 TIMER 0 MODULE The

- Slides: 13

Chapter 7 Timers 1

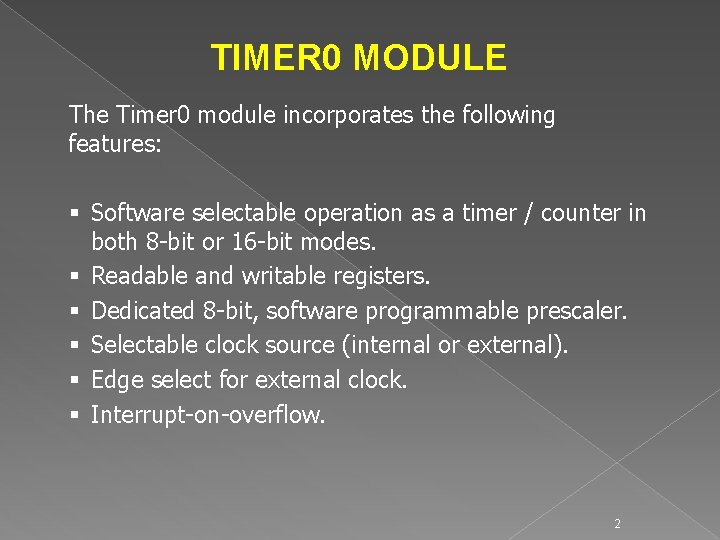

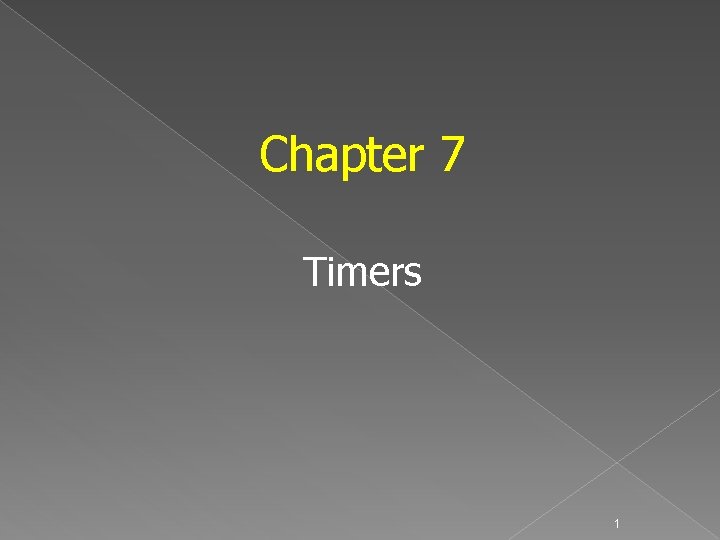

TIMER 0 MODULE The Timer 0 module incorporates the following features: § Software selectable operation as a timer / counter in both 8 -bit or 16 -bit modes. § Readable and writable registers. § Dedicated 8 -bit, software programmable prescaler. § Selectable clock source (internal or external). § Edge select for external clock. § Interrupt-on-overflow. 2

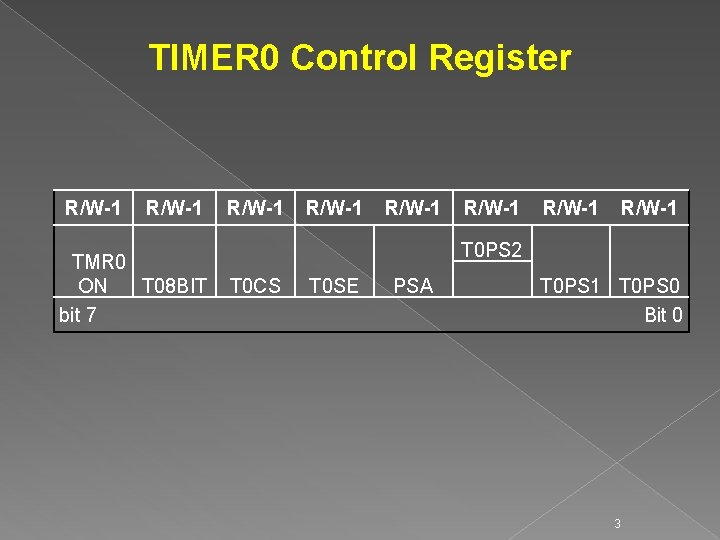

TIMER 0 Control Register R/W-1 TMR 0 ON T 08 BIT bit 7 R/W-1 R/W-1 T 0 PS 2 T 0 CS T 0 SE PSA T 0 PS 1 T 0 PS 0 Bit 0 3

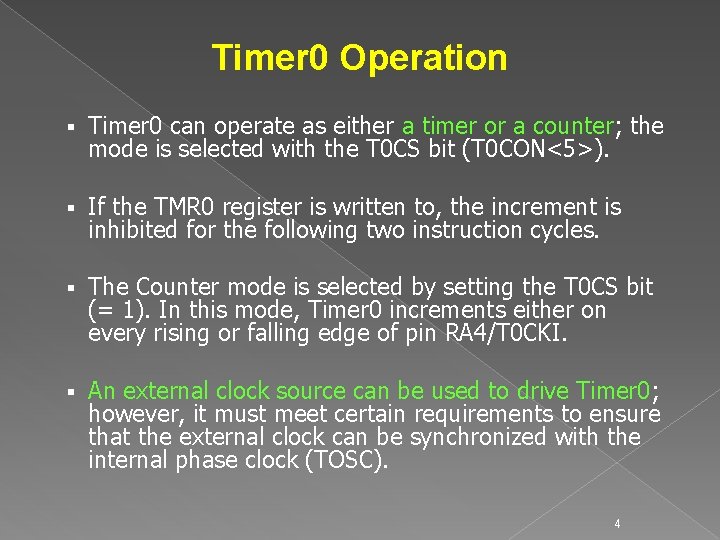

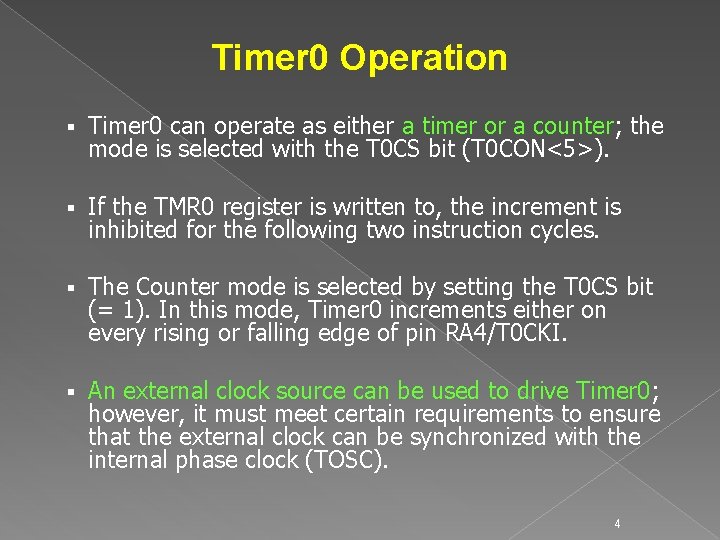

Timer 0 Operation § Timer 0 can operate as either a timer or a counter; the mode is selected with the T 0 CS bit (T 0 CON<5>). § If the TMR 0 register is written to, the increment is inhibited for the following two instruction cycles. § The Counter mode is selected by setting the T 0 CS bit (= 1). In this mode, Timer 0 increments either on every rising or falling edge of pin RA 4/T 0 CKI. § An external clock source can be used to drive Timer 0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (TOSC). 4

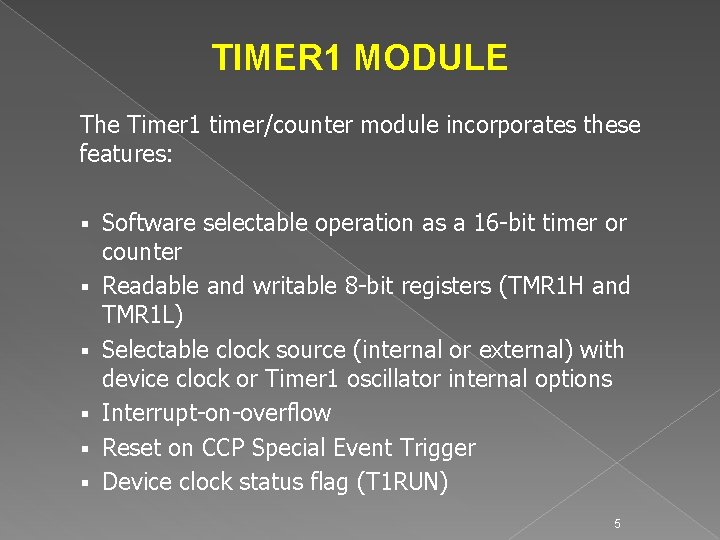

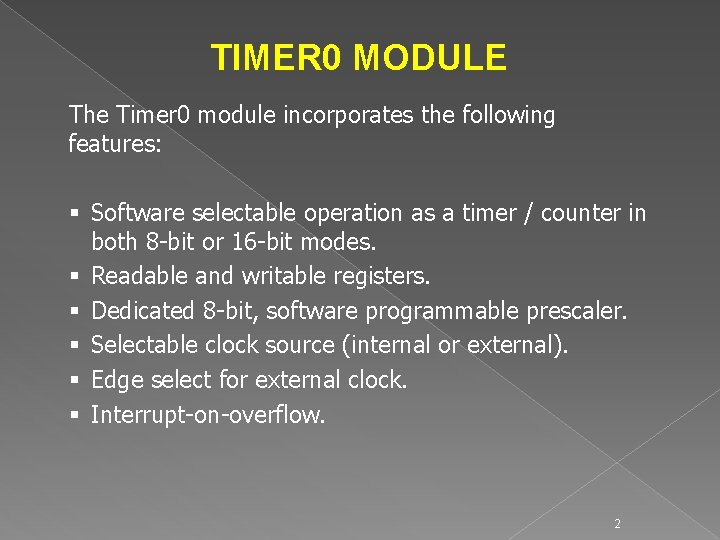

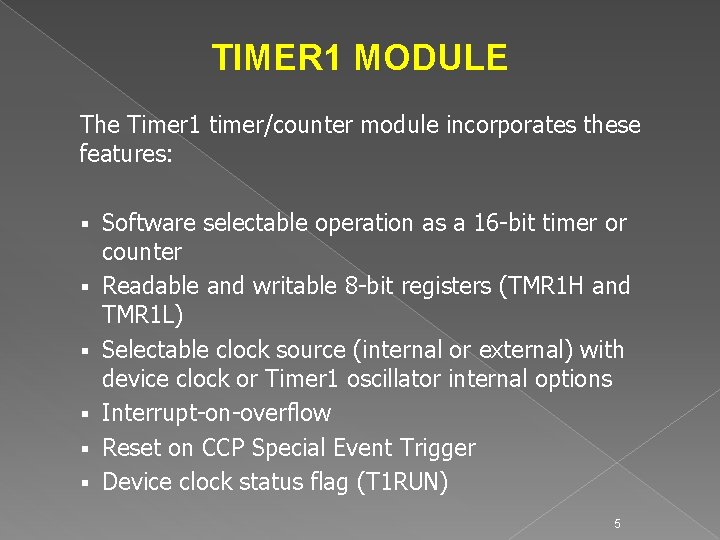

TIMER 1 MODULE The Timer 1 timer/counter module incorporates these features: § § § Software selectable operation as a 16 -bit timer or counter Readable and writable 8 -bit registers (TMR 1 H and TMR 1 L) Selectable clock source (internal or external) with device clock or Timer 1 oscillator internal options Interrupt-on-overflow Reset on CCP Special Event Trigger Device clock status flag (T 1 RUN) 5

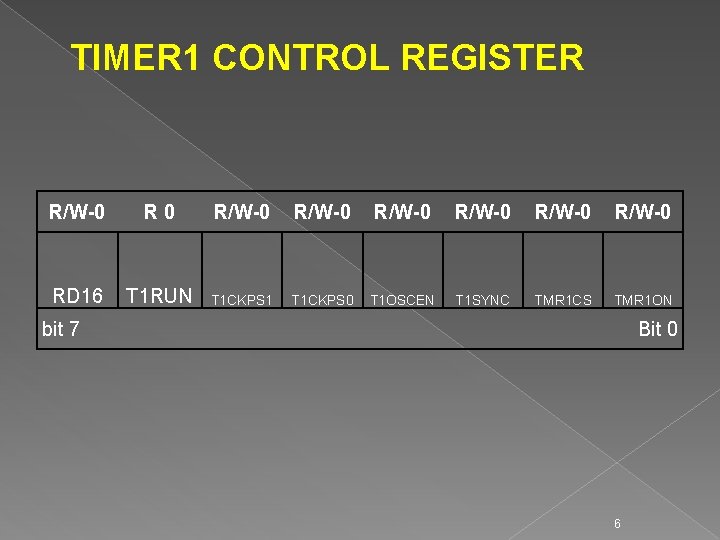

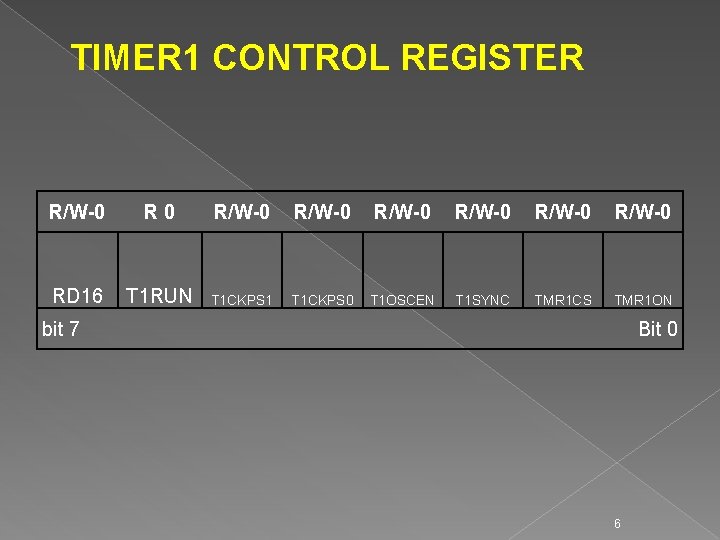

TIMER 1 CONTROL REGISTER R/W-0 R 0 R/W-0 R/W-0 RD 16 T 1 RUN T 1 CKPS 1 T 1 CKPS 0 T 1 OSCEN T 1 SYNC TMR 1 CS TMR 1 ON bit 7 Bit 0 6

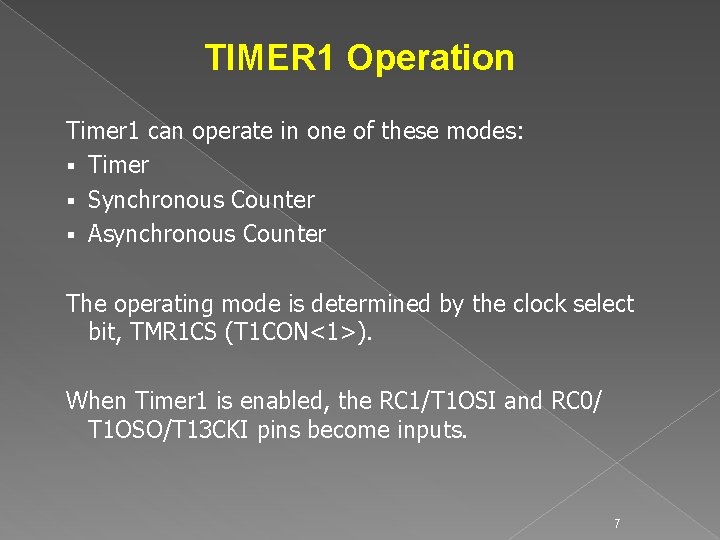

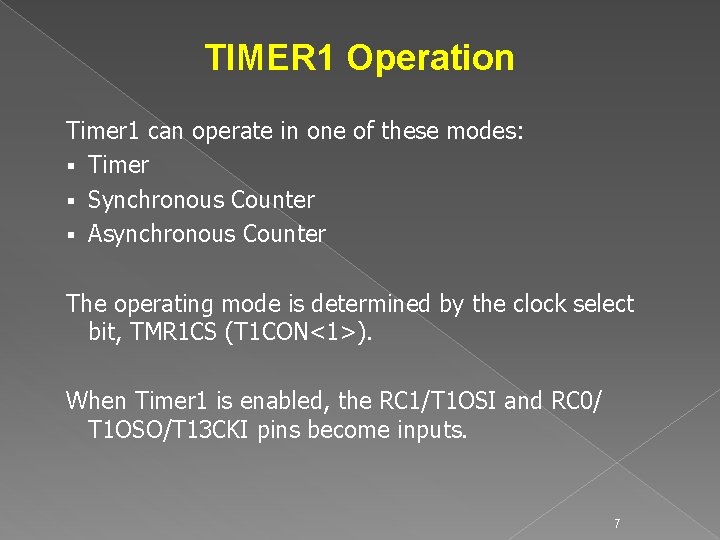

TIMER 1 Operation Timer 1 can operate in one of these modes: § Timer § Synchronous Counter § Asynchronous Counter The operating mode is determined by the clock select bit, TMR 1 CS (T 1 CON<1>). When Timer 1 is enabled, the RC 1/T 1 OSI and RC 0/ T 1 OSO/T 13 CKI pins become inputs. 7

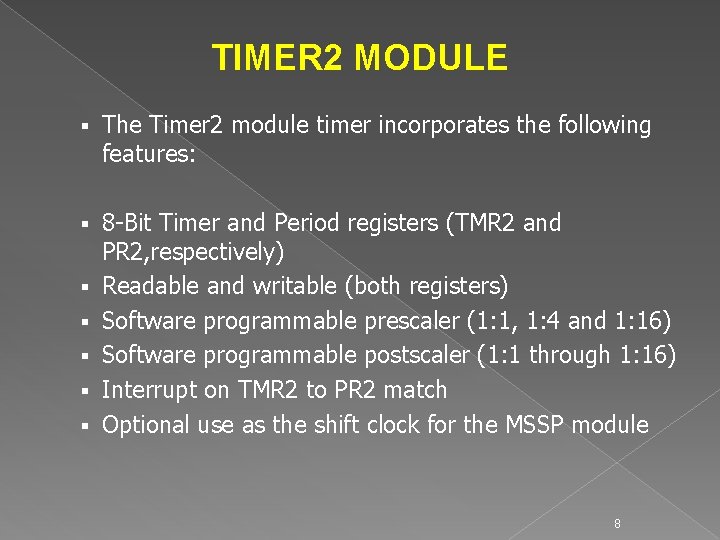

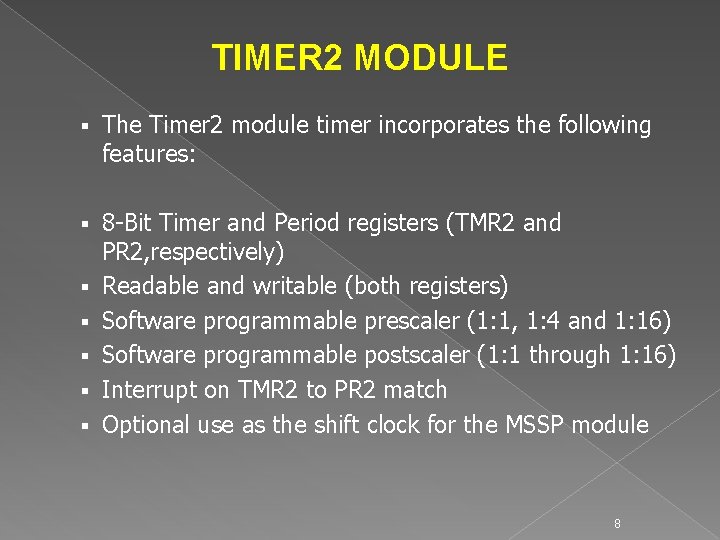

TIMER 2 MODULE § The Timer 2 module timer incorporates the following features: § 8 -Bit Timer and Period registers (TMR 2 and PR 2, respectively) Readable and writable (both registers) Software programmable prescaler (1: 1, 1: 4 and 1: 16) Software programmable postscaler (1: 1 through 1: 16) Interrupt on TMR 2 to PR 2 match Optional use as the shift clock for the MSSP module § § § 8

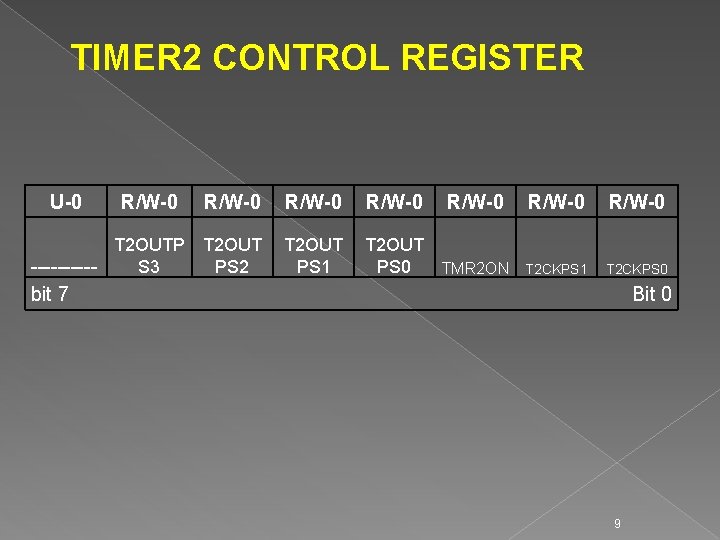

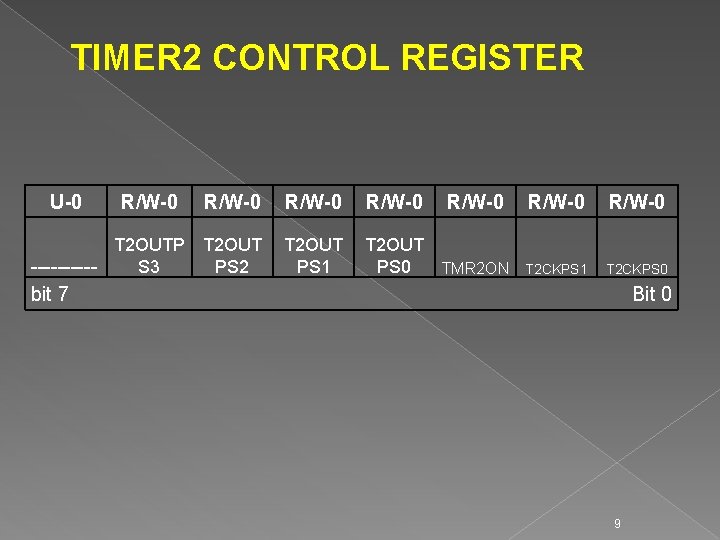

TIMER 2 CONTROL REGISTER U-0 R/W-0 T 2 OUTP -----S 3 R/W-0 T 2 OUT PS 2 T 2 OUT PS 1 T 2 OUT PS 0 TMR 2 ON R/W-0 T 2 CKPS 1 T 2 CKPS 0 bit 7 Bit 0 9

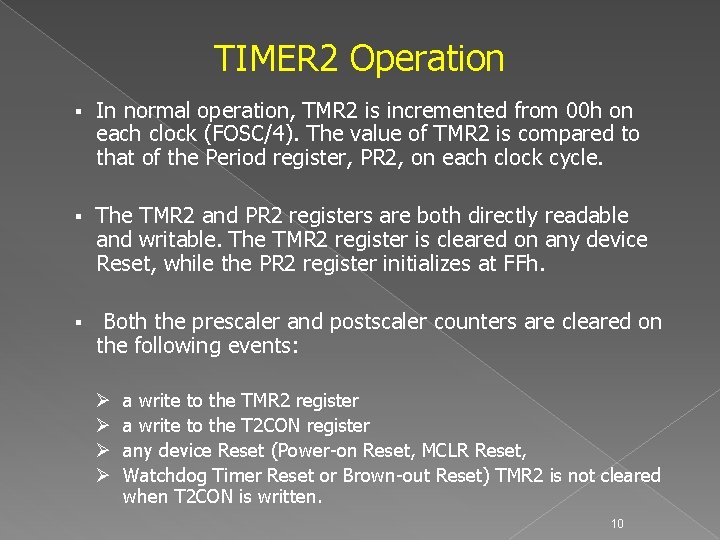

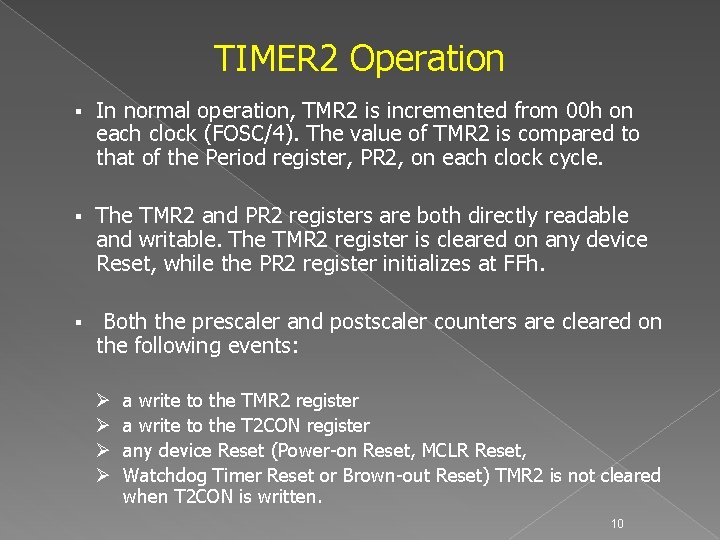

TIMER 2 Operation § In normal operation, TMR 2 is incremented from 00 h on each clock (FOSC/4). The value of TMR 2 is compared to that of the Period register, PR 2, on each clock cycle. § The TMR 2 and PR 2 registers are both directly readable and writable. The TMR 2 register is cleared on any device Reset, while the PR 2 register initializes at FFh. § Both the prescaler and postscaler counters are cleared on the following events: Ø Ø a write to the TMR 2 register a write to the T 2 CON register any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset) TMR 2 is not cleared when T 2 CON is written. 10

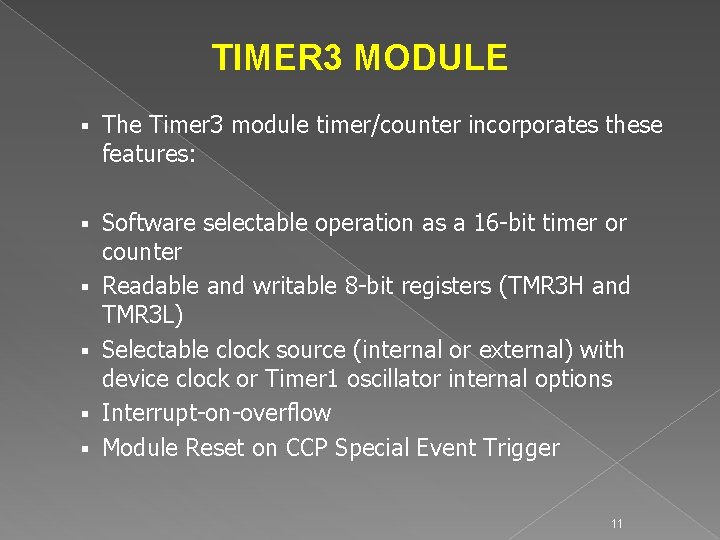

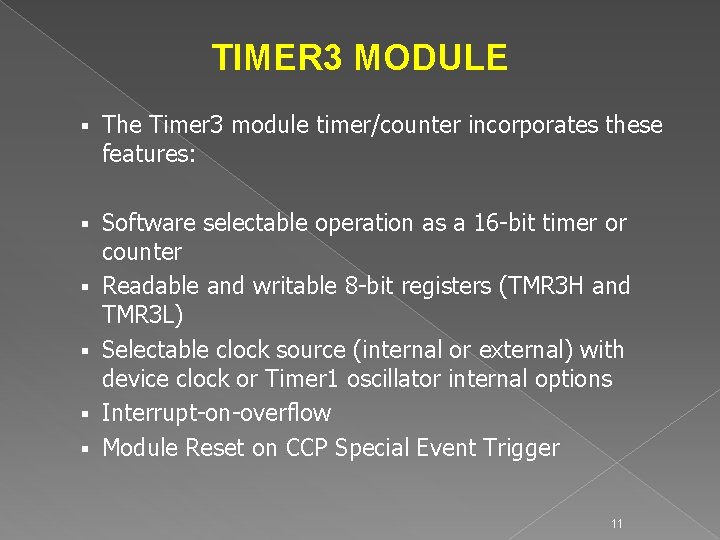

TIMER 3 MODULE § The Timer 3 module timer/counter incorporates these features: § Software selectable operation as a 16 -bit timer or counter Readable and writable 8 -bit registers (TMR 3 H and TMR 3 L) Selectable clock source (internal or external) with device clock or Timer 1 oscillator internal options Interrupt-on-overflow Module Reset on CCP Special Event Trigger § § 11

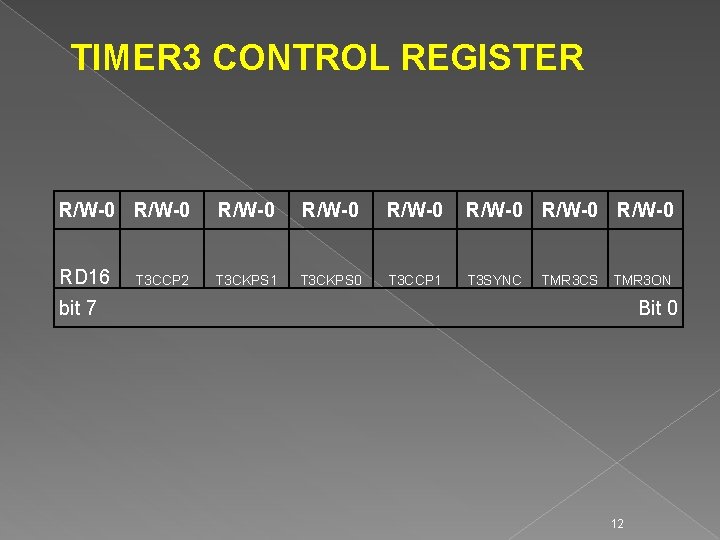

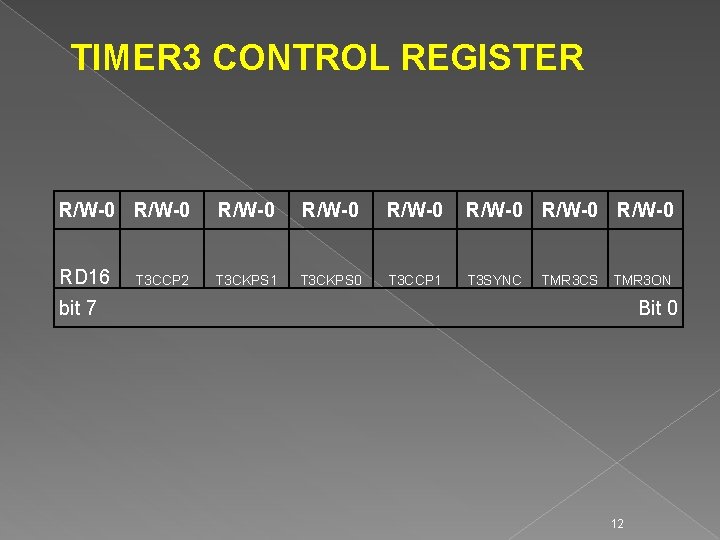

TIMER 3 CONTROL REGISTER R/W-0 R/W-0 RD 16 T 3 CKPS 1 T 3 CKPS 0 T 3 CCP 1 T 3 SYNC T 3 CCP 2 TMR 3 CS TMR 3 ON bit 7 Bit 0 12

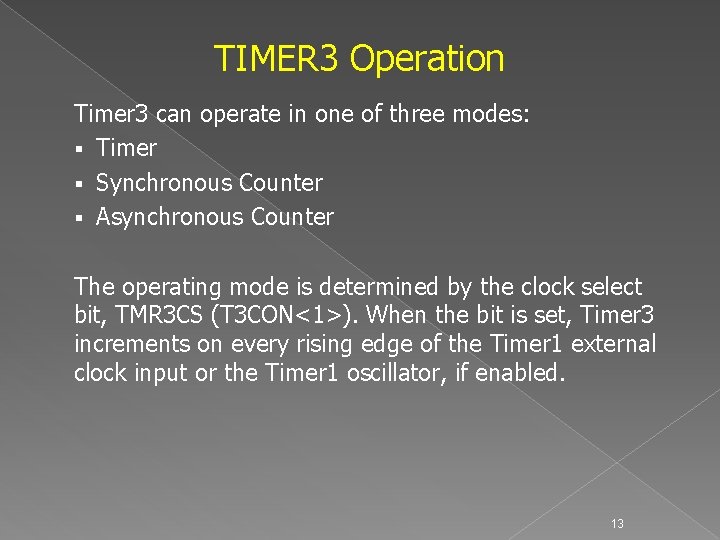

TIMER 3 Operation Timer 3 can operate in one of three modes: § Timer § Synchronous Counter § Asynchronous Counter The operating mode is determined by the clock select bit, TMR 3 CS (T 3 CON<1>). When the bit is set, Timer 3 increments on every rising edge of the Timer 1 external clock input or the Timer 1 oscillator, if enabled. 13