Chapter 7 Sequential logic design principles u Memory

- Slides: 16

Chapter 7 Sequential logic design principles u. Memory devices : Latch and Flip-flop u. Sequential logic : Pipeline and FSM u. Analysis and Synthesis for FSM

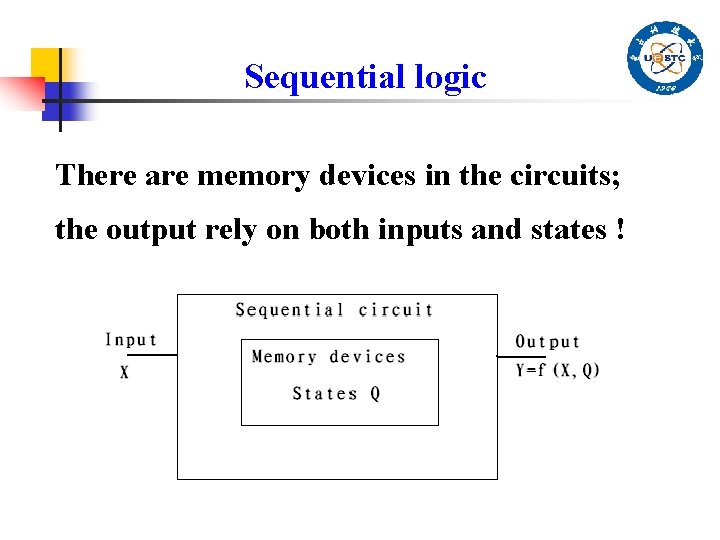

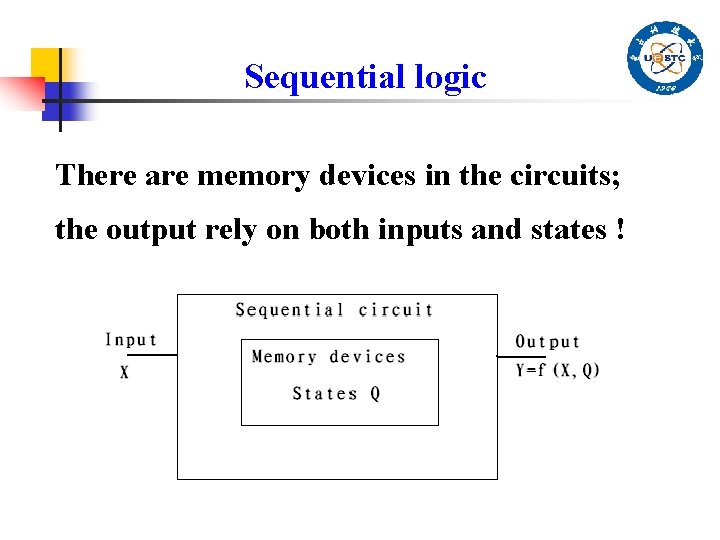

Sequential logic There are memory devices in the circuits; the output rely on both inputs and states !

Memory devices Latch: the inputs be watched continuously and output may be changed at any time; Flip-flop: the input be sampled and output may be changed only at the times determined by the clock !

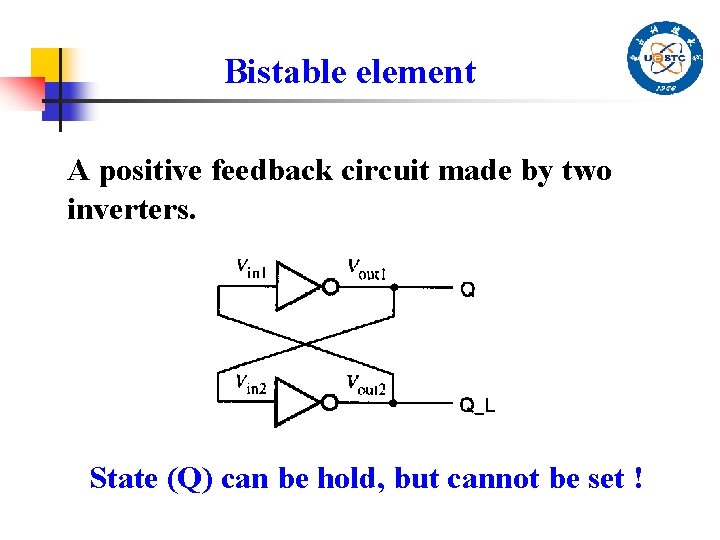

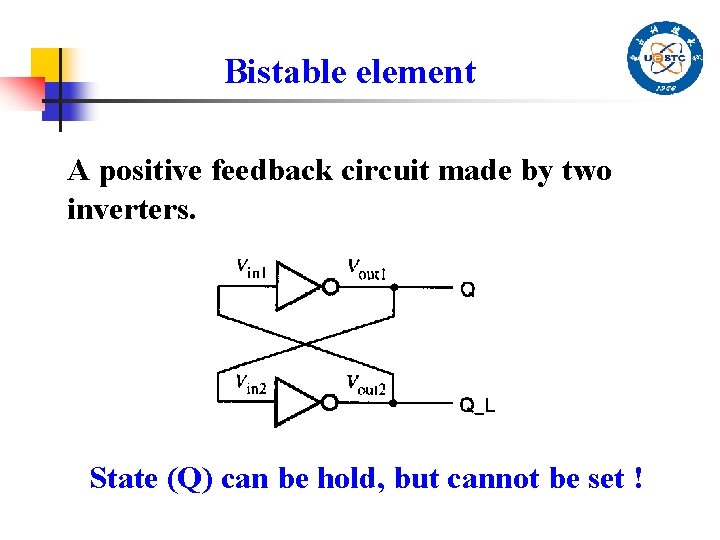

Bistable element A positive feedback circuit made by two inverters. State (Q) can be hold, but cannot be set !

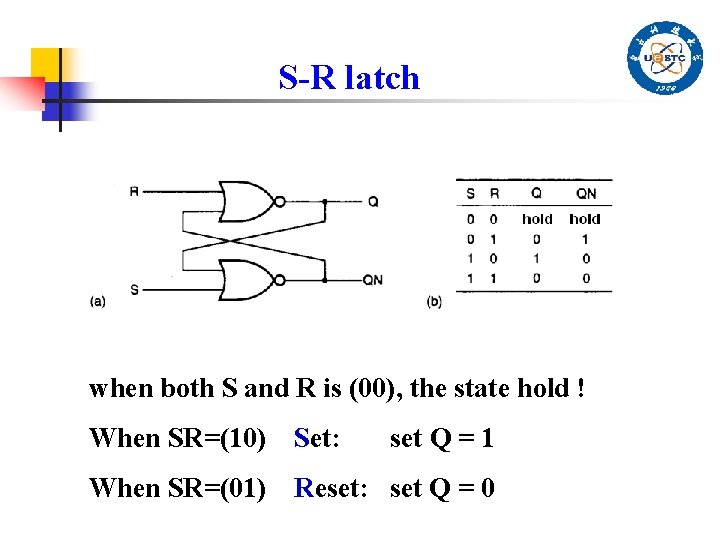

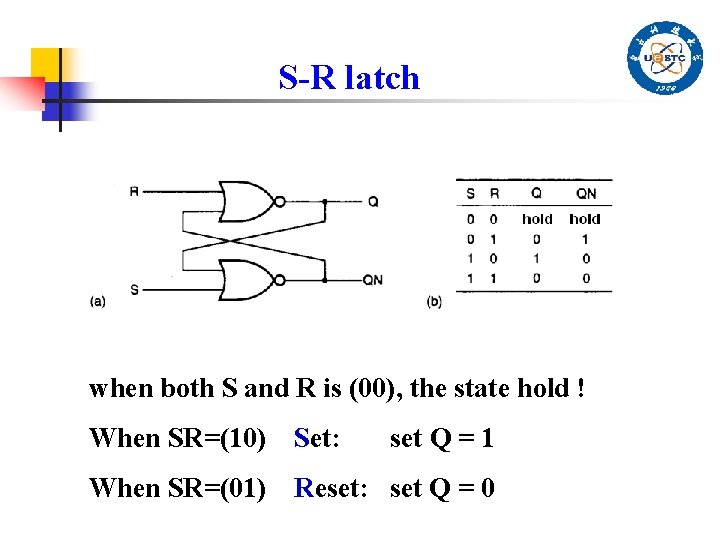

S-R latch when both S and R is (00), the state hold ! When SR=(10) Set: set Q = 1 When SR=(01) Reset: set Q = 0

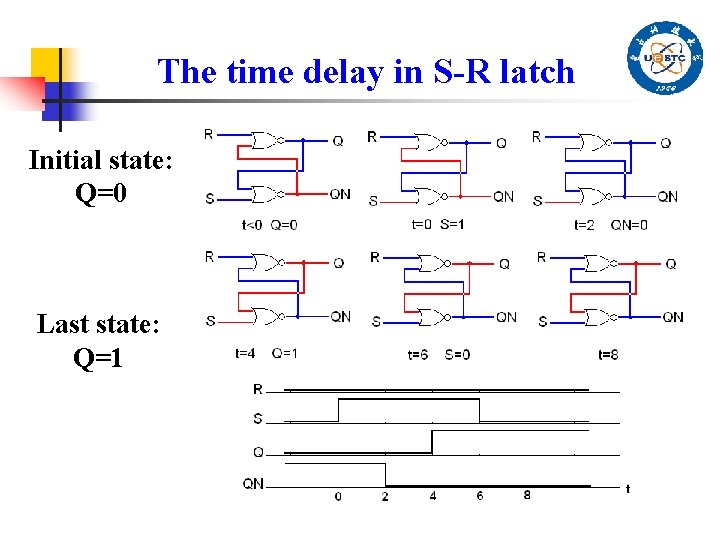

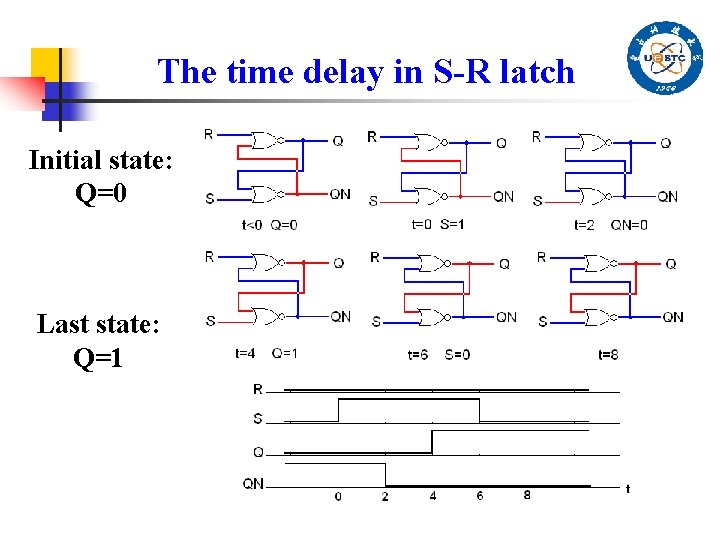

The time delay in S-R latch Initial state: Q=0 Last state: Q=1

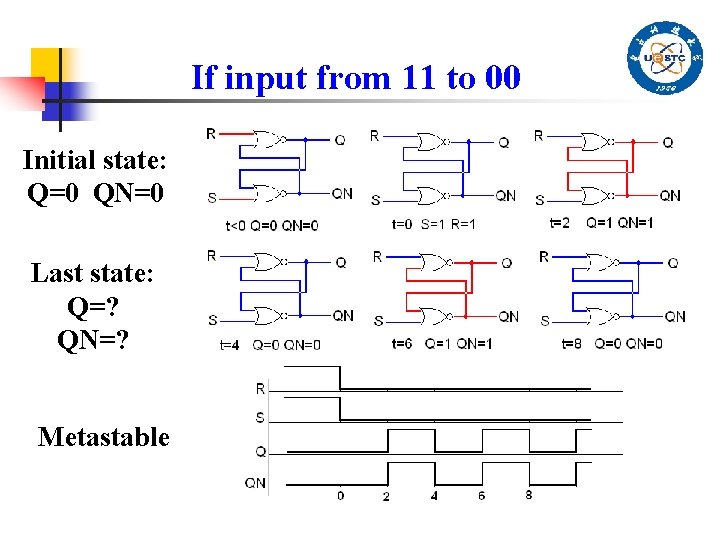

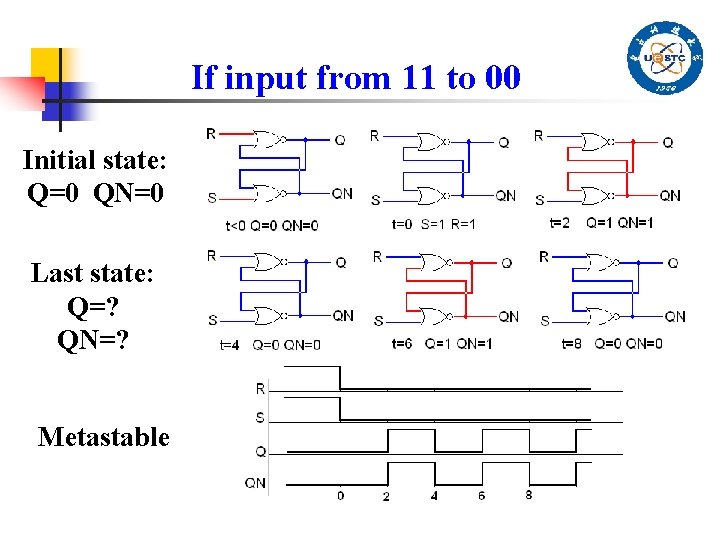

If input from 11 to 00 Initial state: Q=0 QN=0 Last state: Q=? QN=? Metastable

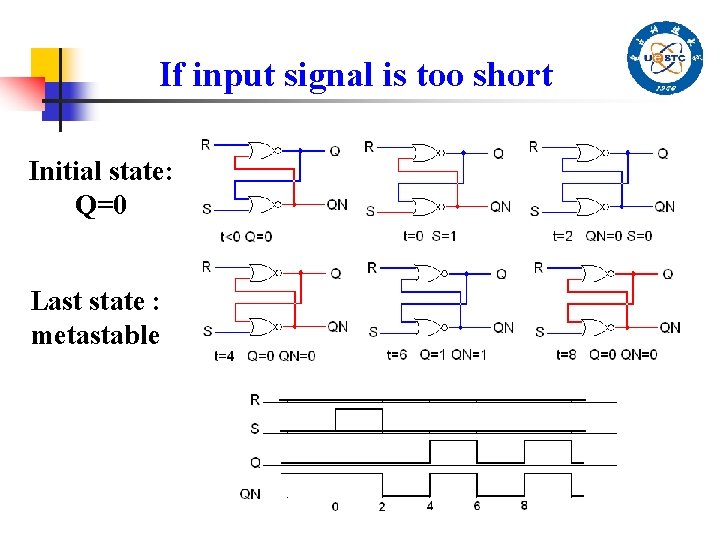

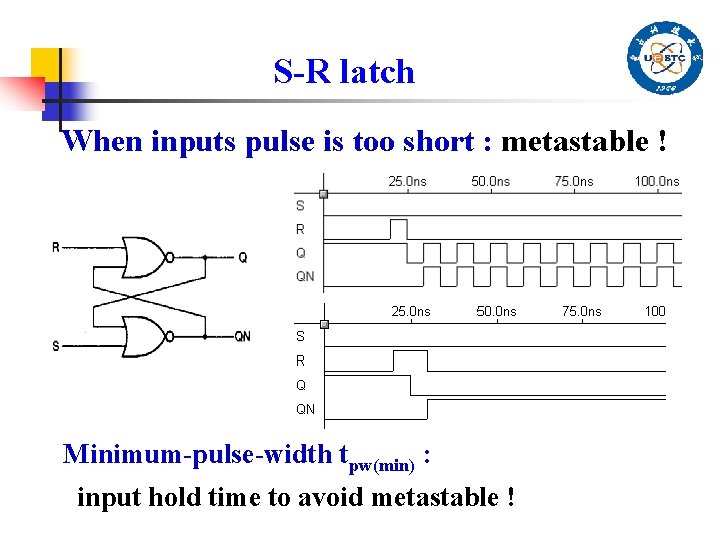

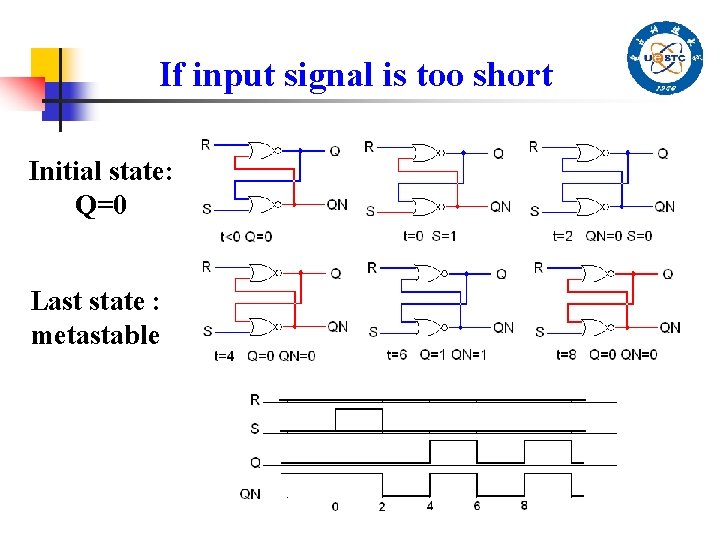

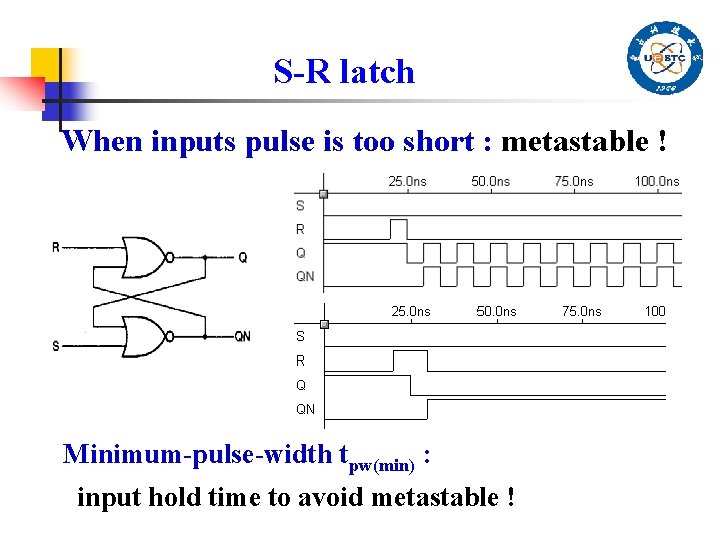

If input signal is too short Initial state: Q=0 Last state : metastable

S-R latch When inputs pulse is too short : metastable ! Minimum-pulse-width tpw(min) : input hold time to avoid metastable !

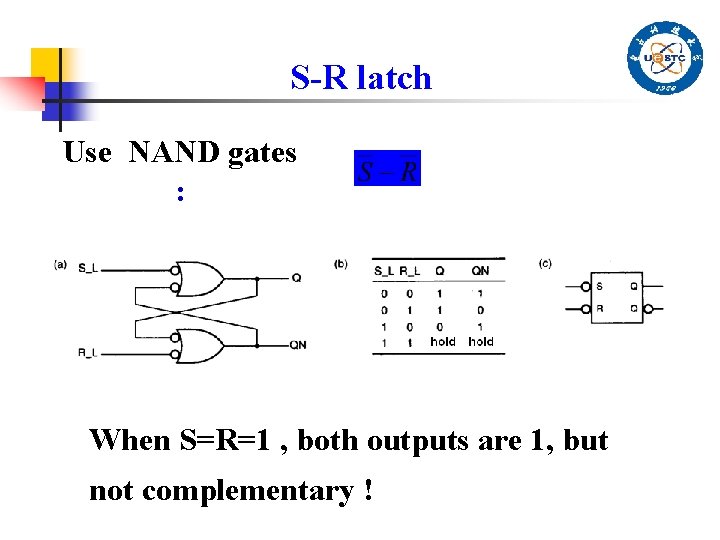

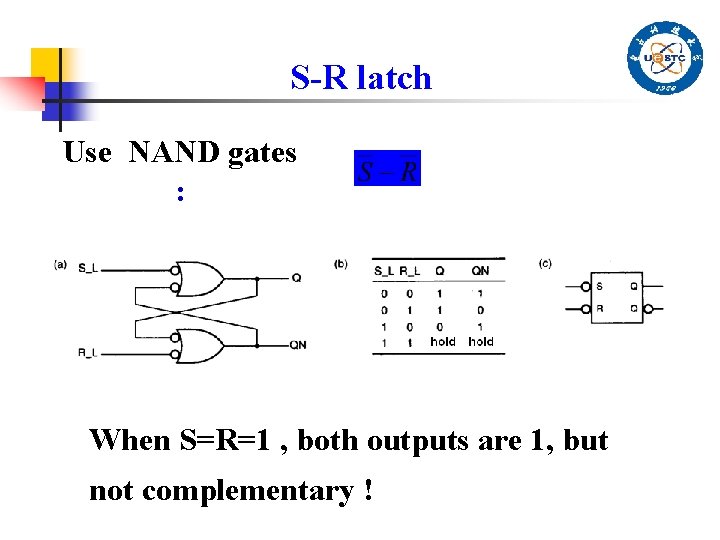

S-R latch Use NAND gates : When S=R=1 , both outputs are 1, but not complementary !

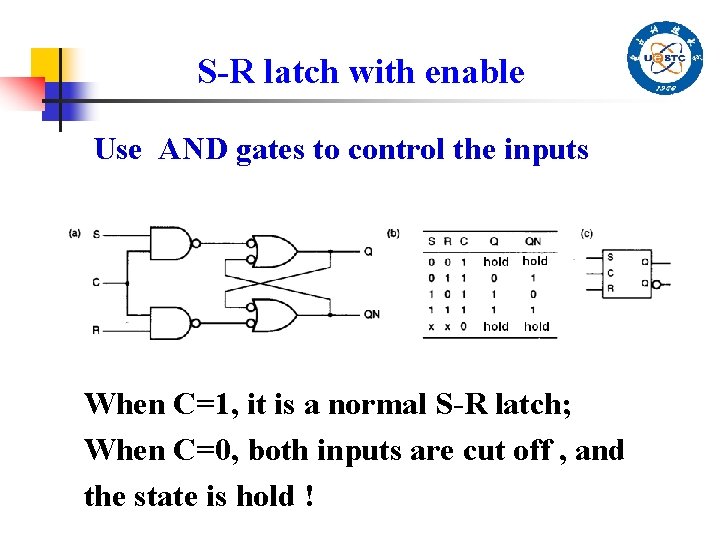

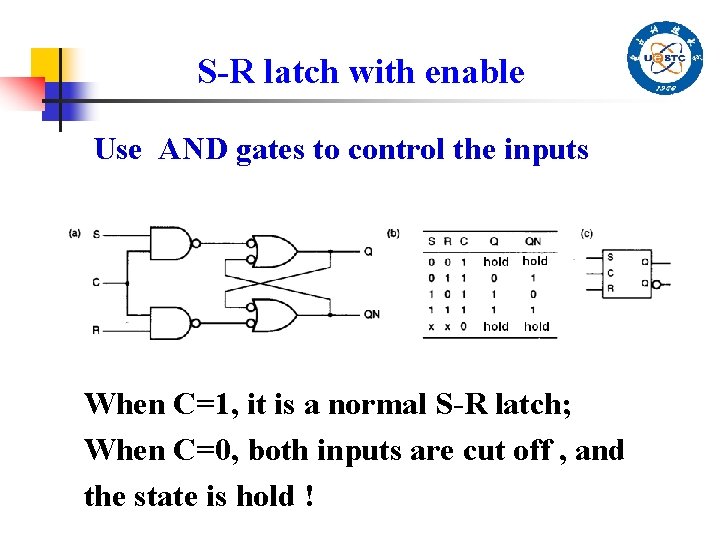

S-R latch with enable Use AND gates to control the inputs When C=1, it is a normal S-R latch; When C=0, both inputs are cut off , and the state is hold !

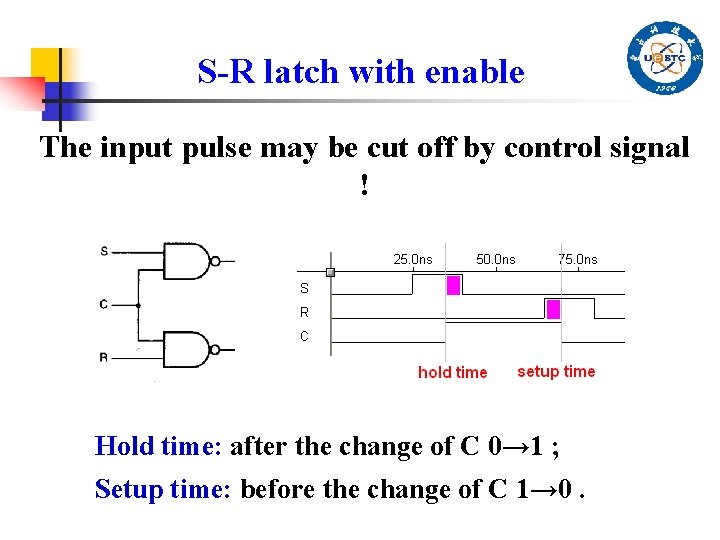

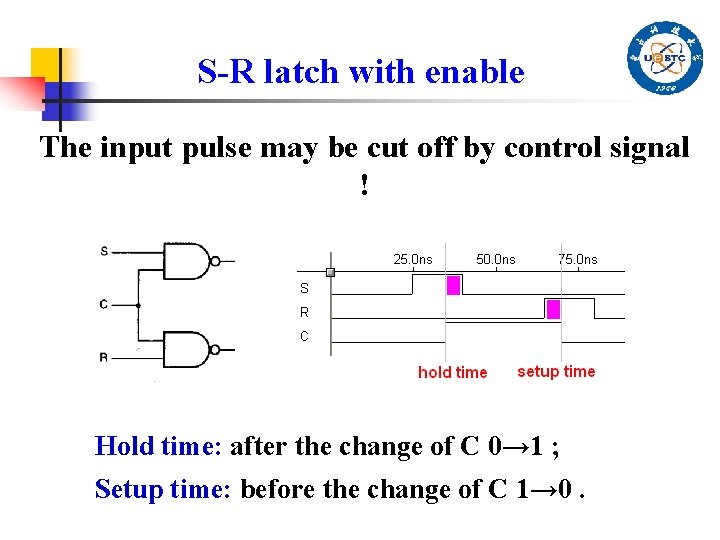

S-R latch with enable The input pulse may be cut off by control signal ! Hold time: after the change of C 0→ 1 ; Setup time: before the change of C 1→ 0.

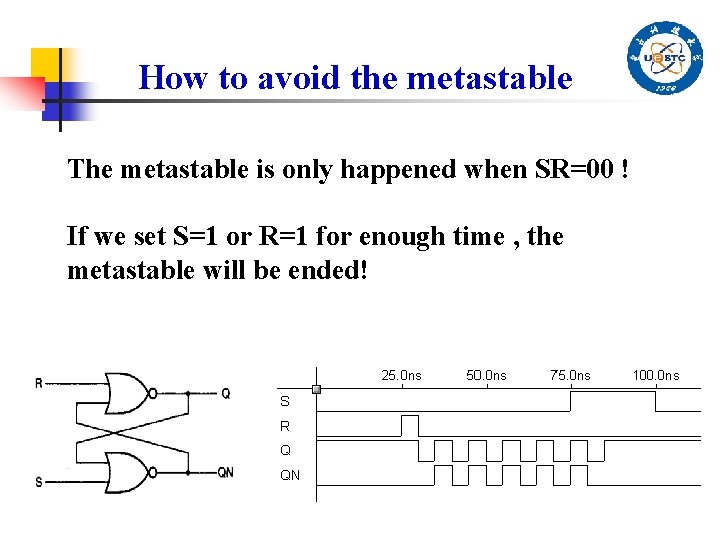

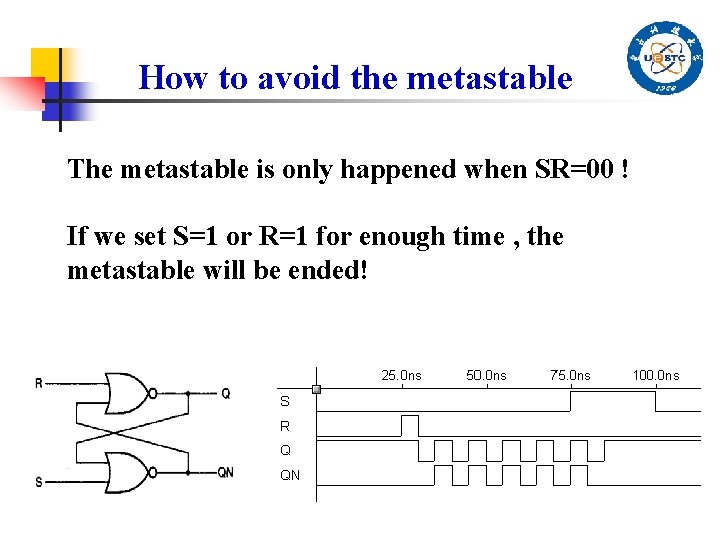

How to avoid the metastable The metastable is only happened when SR=00 ! If we set S=1 or R=1 for enough time , the metastable will be ended!

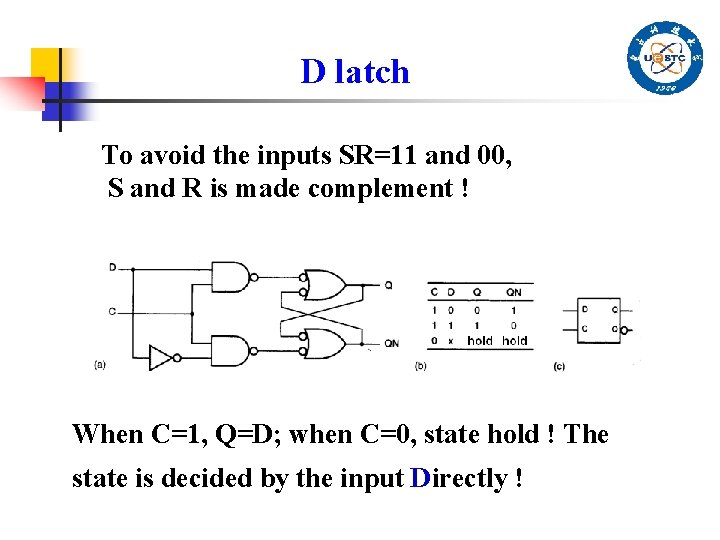

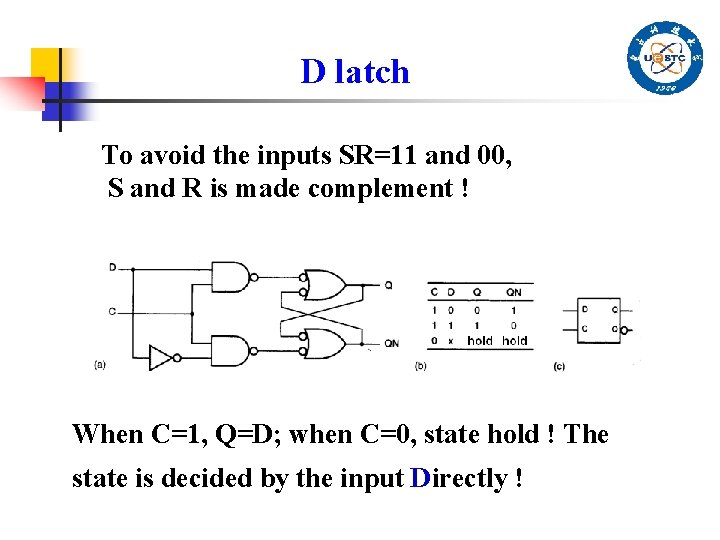

D latch To avoid the inputs SR=11 and 00, S and R is made complement ! When C=1, Q=D; when C=0, state hold ! The state is decided by the input Directly !

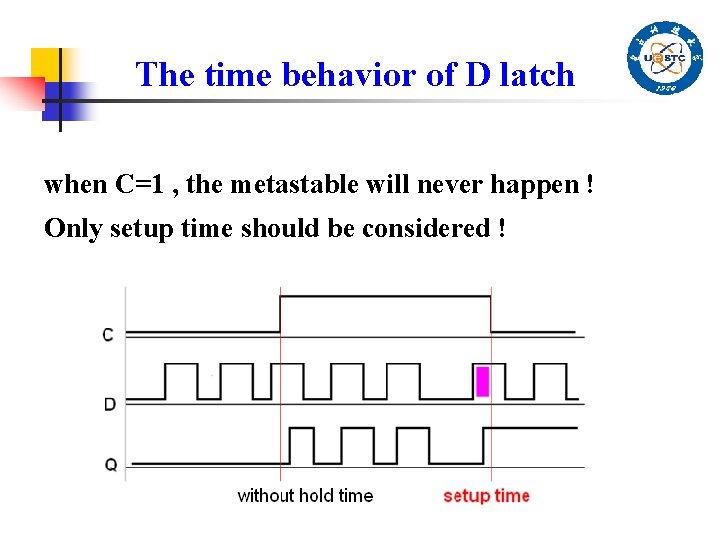

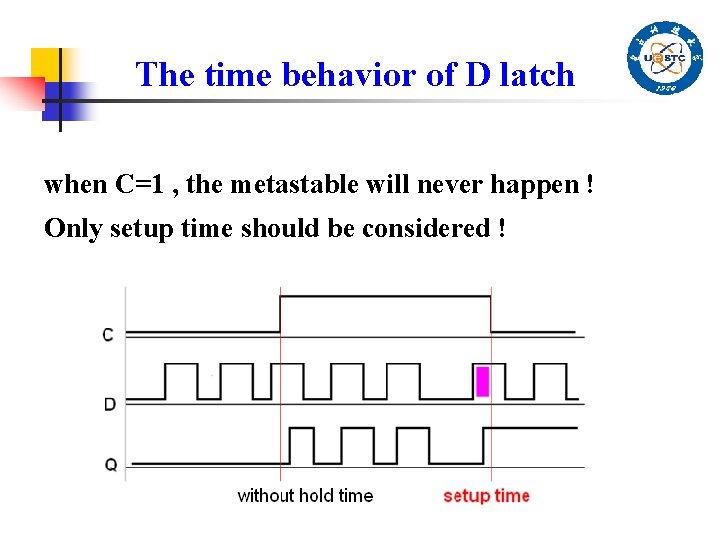

The time behavior of D latch when C=1 , the metastable will never happen ! Only setup time should be considered !

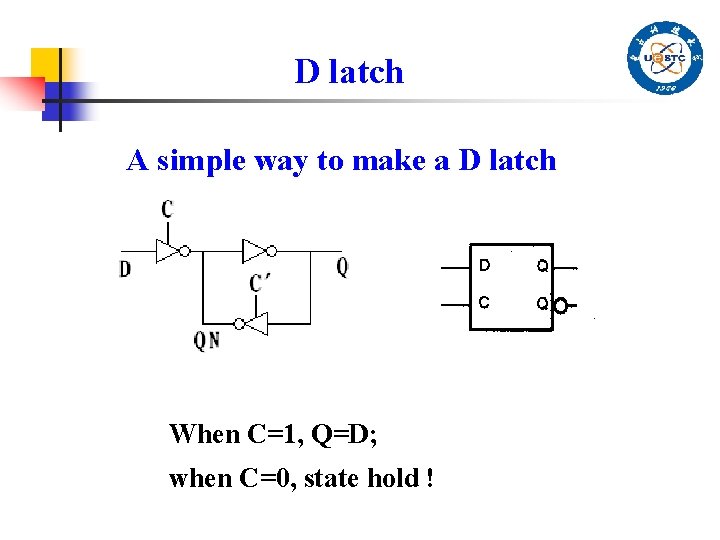

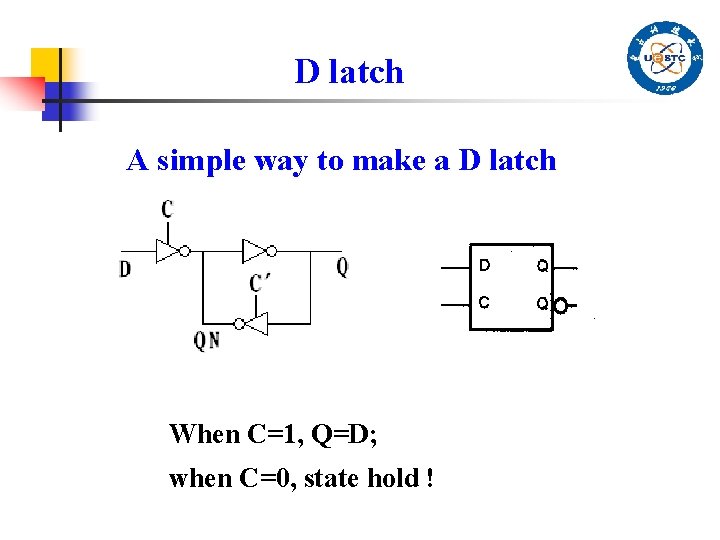

D latch A simple way to make a D latch When C=1, Q=D; when C=0, state hold !