Chapter 7 Microsequencer Control Unit Design Images courtesy

![Micro-operations Mnemonic ARPC ARDR PCIN Micro-Operation AR PC AR DR[5. . 0] PC PC Micro-operations Mnemonic ARPC ARDR PCIN Micro-Operation AR PC AR DR[5. . 0] PC PC](https://slidetodoc.com/presentation_image/5dfc1e1fd574d2696e8bd5ca1589a1e7/image-12.jpg)

- Slides: 58

Chapter 7 Microsequencer Control Unit Design Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Chapter Outline • • Basic Microsequencer Design Very Simple Microsequencer Relatively Simple Microsequencer Reducing the Number of Microinstructions • Microcoded vs. Hardwired Control • Pentium Microprocessor Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Micro-stuff • • • Micro-operations Microinstructions Microprograms Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

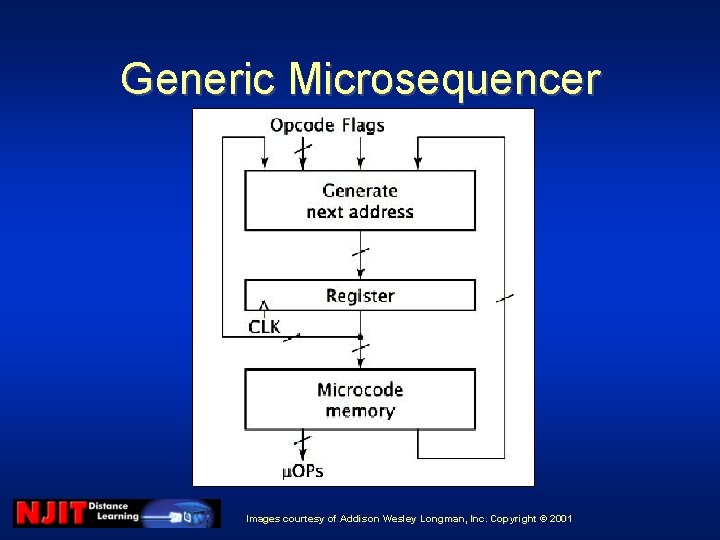

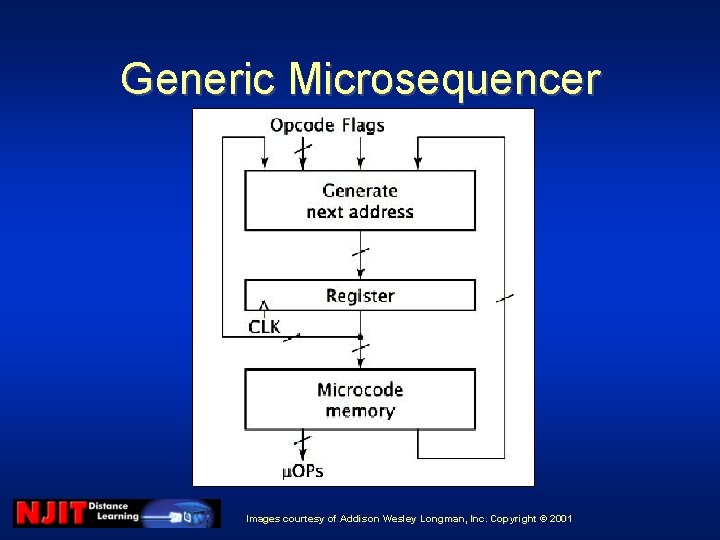

Generic Microsequencer Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

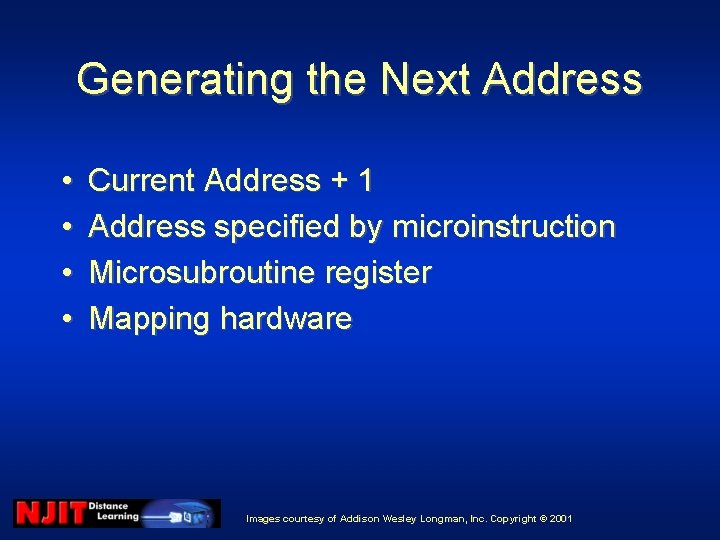

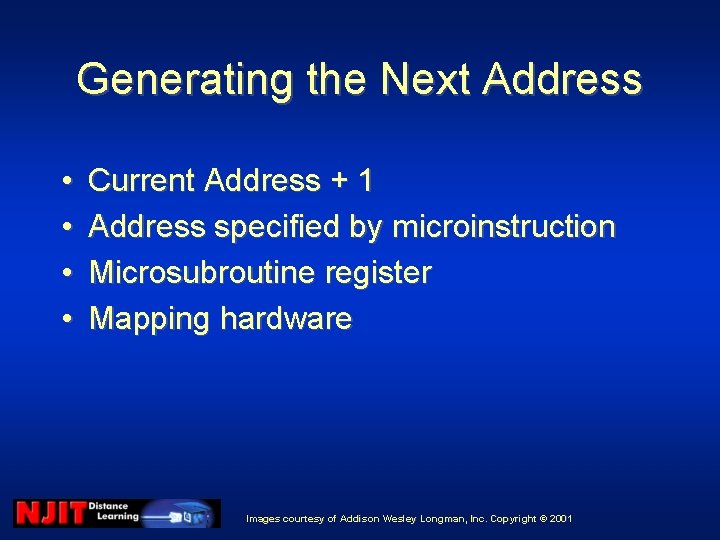

Generating the Next Address • • Current Address + 1 Address specified by microinstruction Microsubroutine register Mapping hardware Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

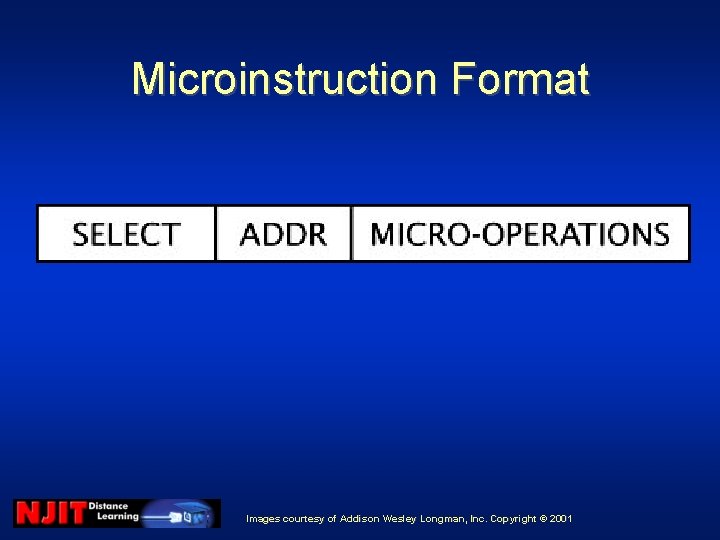

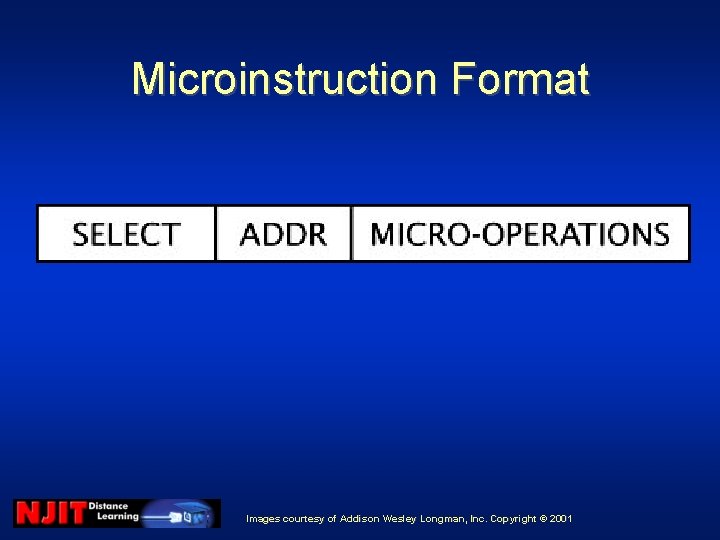

Microinstruction Format Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Types of Microcode • • • Horizontal Vertical Direct Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

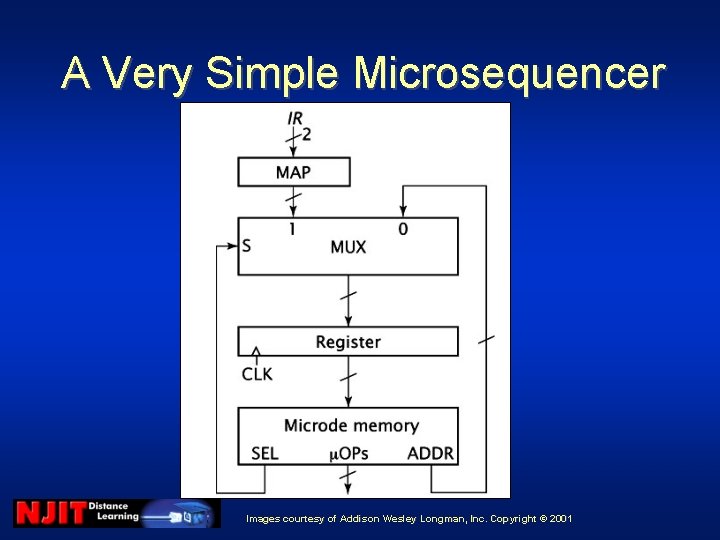

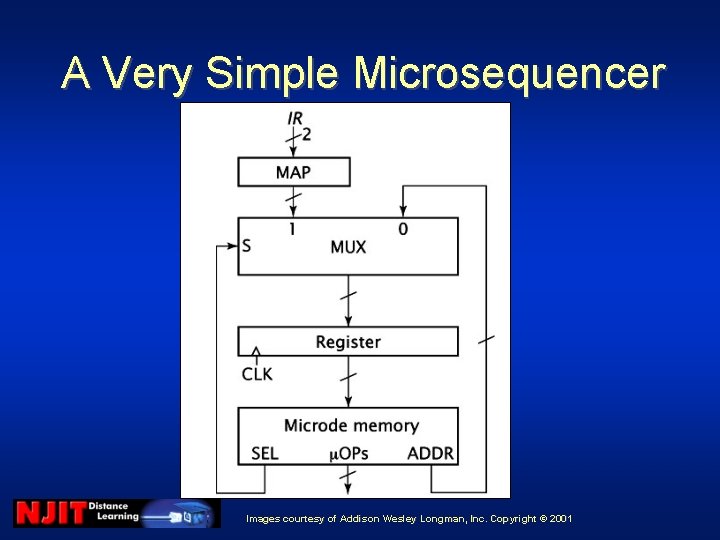

A Very Simple Microsequencer Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

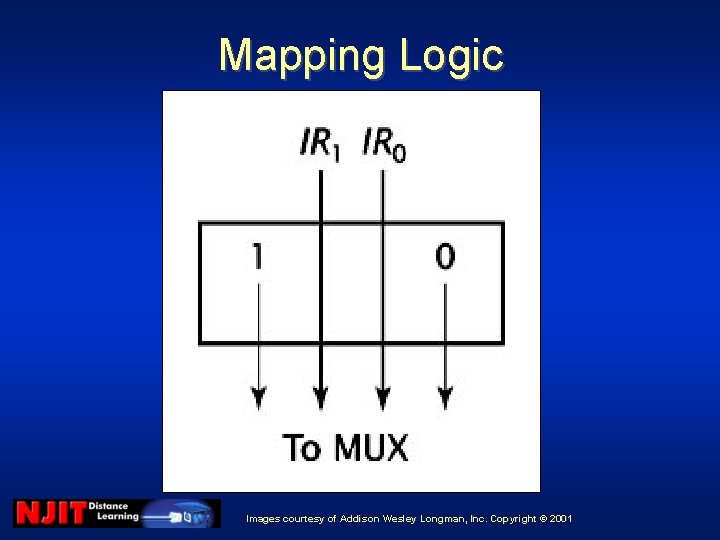

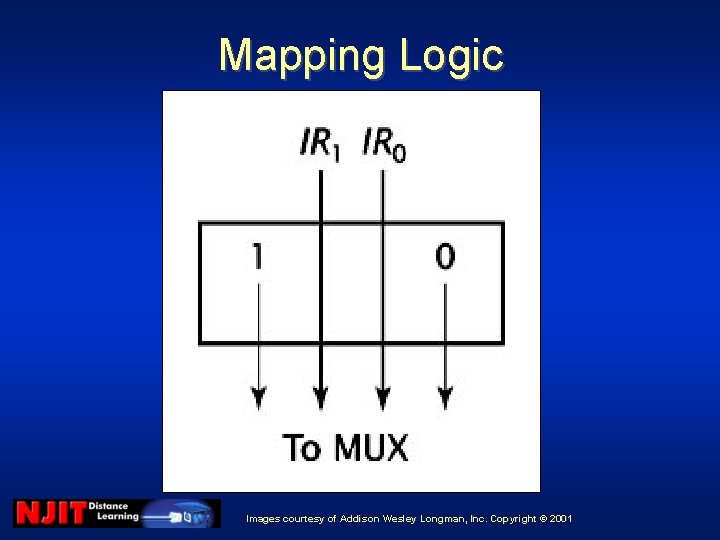

Mapping Logic Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

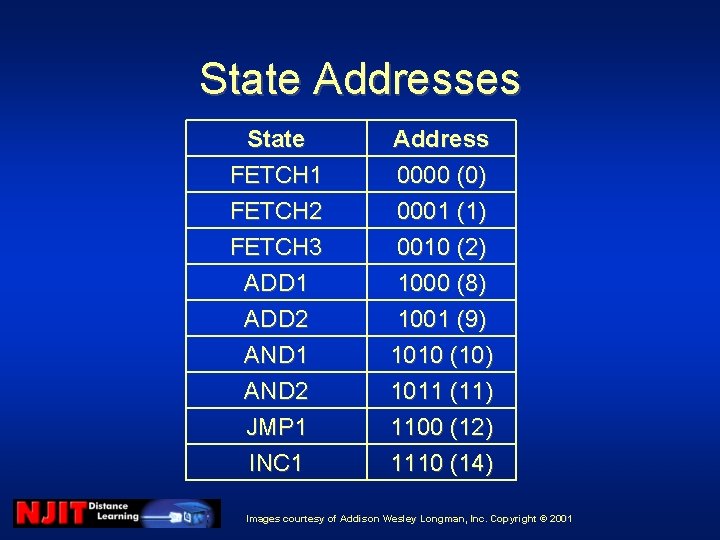

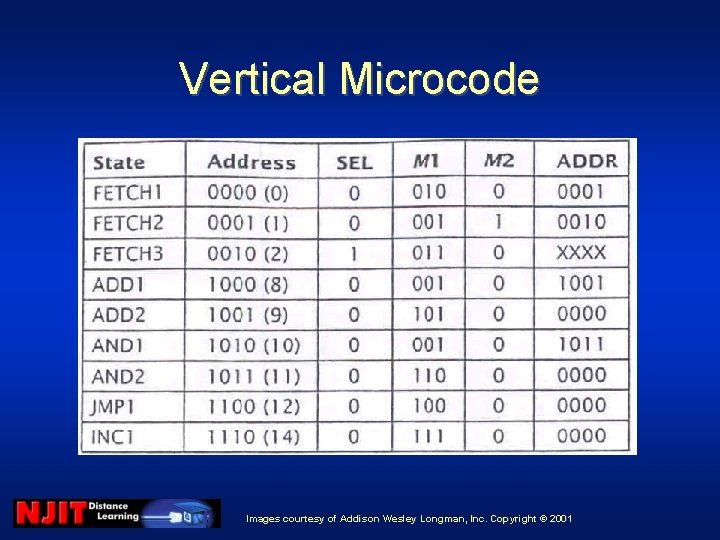

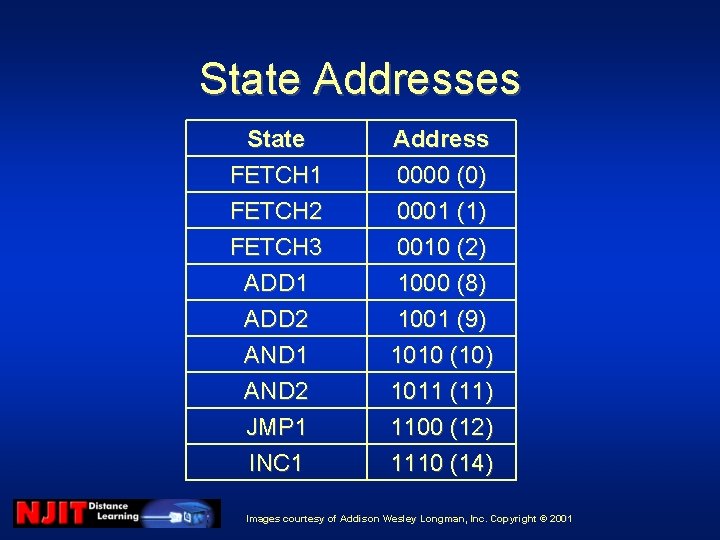

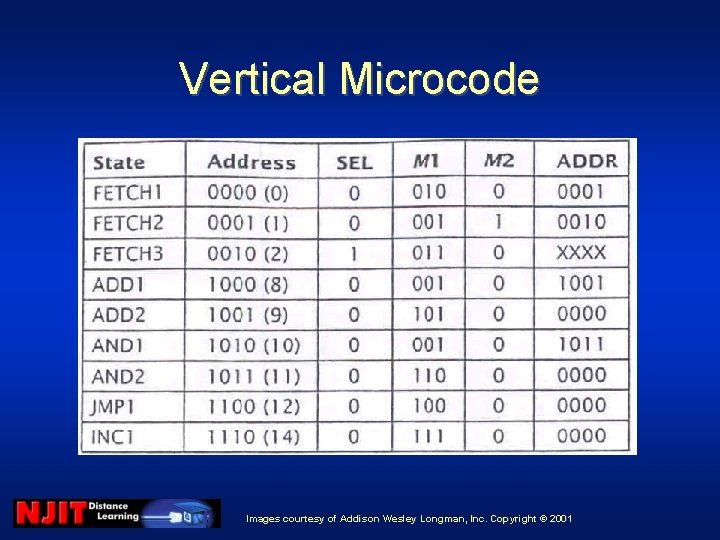

State Addresses State FETCH 1 FETCH 2 FETCH 3 Address 0000 (0) 0001 (1) 0010 (2) ADD 1 ADD 2 AND 1 AND 2 JMP 1 INC 1 1000 (8) 1001 (9) 1010 (10) 1011 (11) 1100 (12) 1110 (14) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

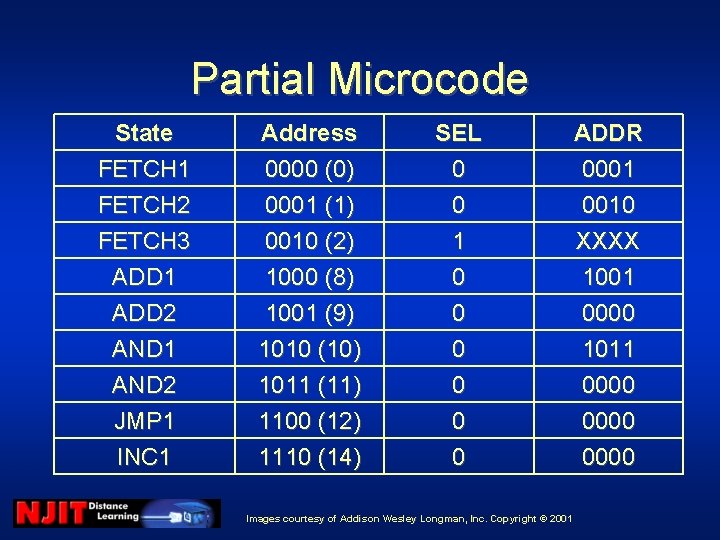

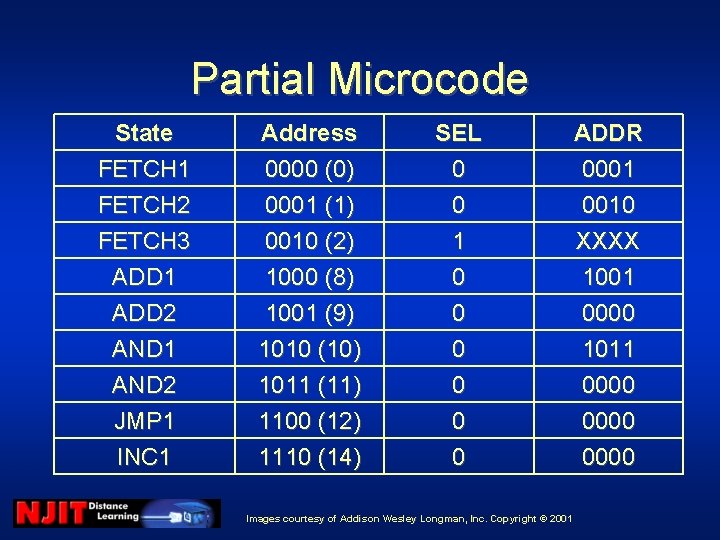

Partial Microcode State FETCH 1 FETCH 2 FETCH 3 Address 0000 (0) 0001 (1) 0010 (2) SEL 0 0 1 ADDR 0001 0010 XXXX ADD 1 ADD 2 AND 1 AND 2 JMP 1 INC 1 1000 (8) 1001 (9) 1010 (10) 1011 (11) 1100 (12) 1110 (14) 0 0 0 1001 0000 1011 0000 Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

![Microoperations Mnemonic ARPC ARDR PCIN MicroOperation AR PC AR DR5 0 PC PC Micro-operations Mnemonic ARPC ARDR PCIN Micro-Operation AR PC AR DR[5. . 0] PC PC](https://slidetodoc.com/presentation_image/5dfc1e1fd574d2696e8bd5ca1589a1e7/image-12.jpg)

Micro-operations Mnemonic ARPC ARDR PCIN Micro-Operation AR PC AR DR[5. . 0] PC PC + 1 PCDR DRM IRDR PLUS AND ACIN PC DR[5. . 0] DR M IR DR[7. . 6] AC AC + DR AC AC^DR AC AC + 1 Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

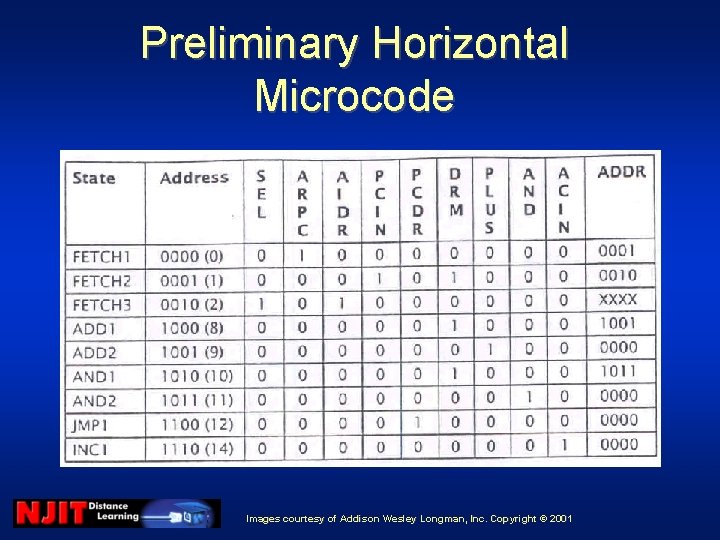

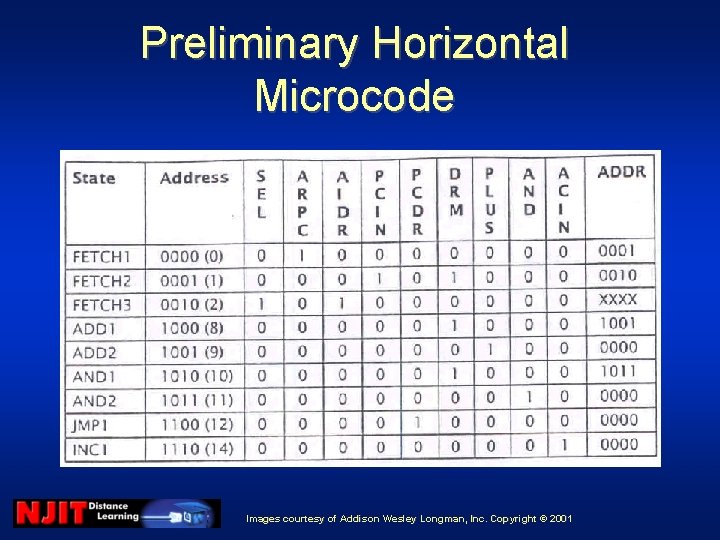

Preliminary Horizontal Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

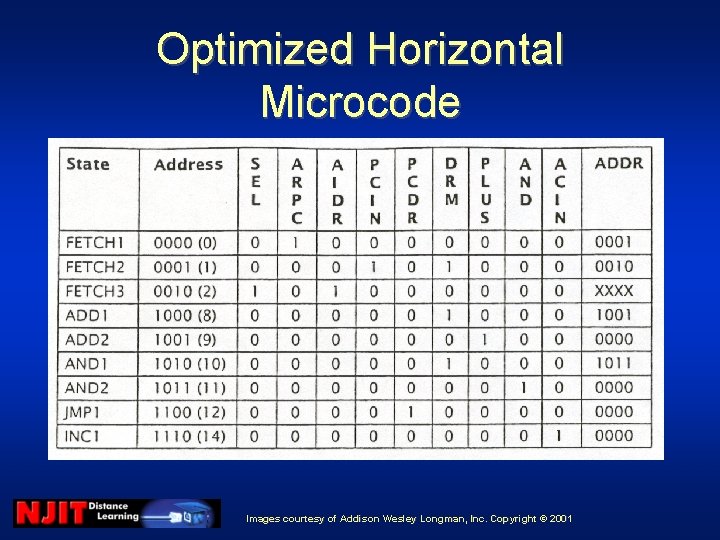

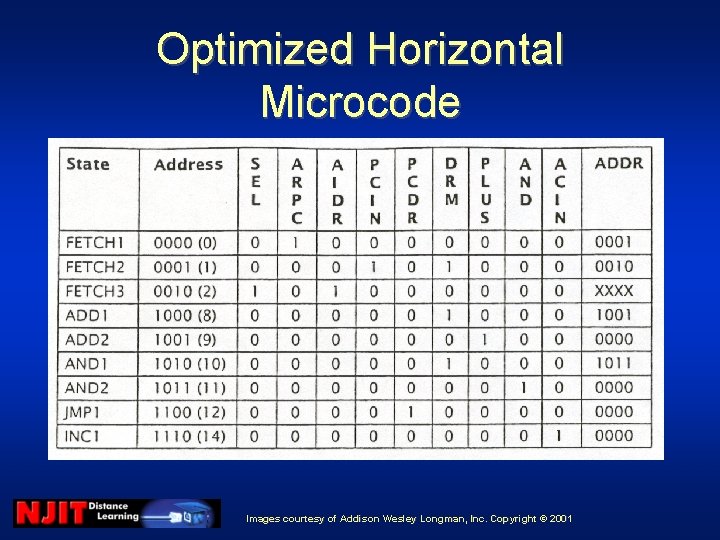

Optimized Horizontal Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

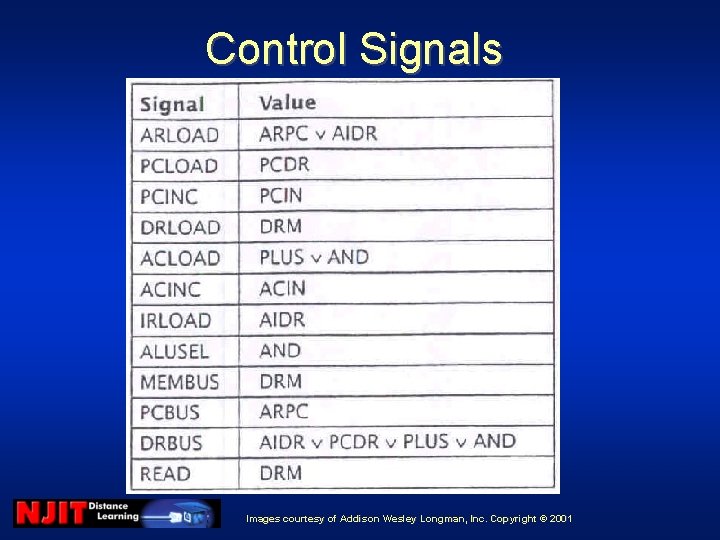

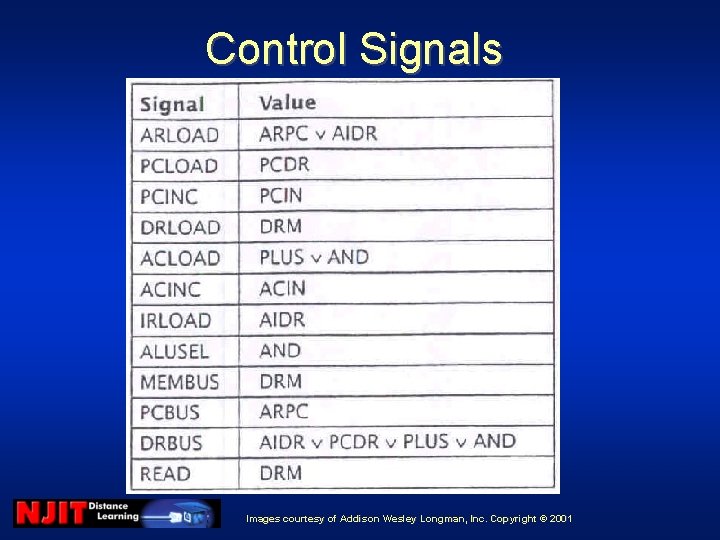

Control Signals Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

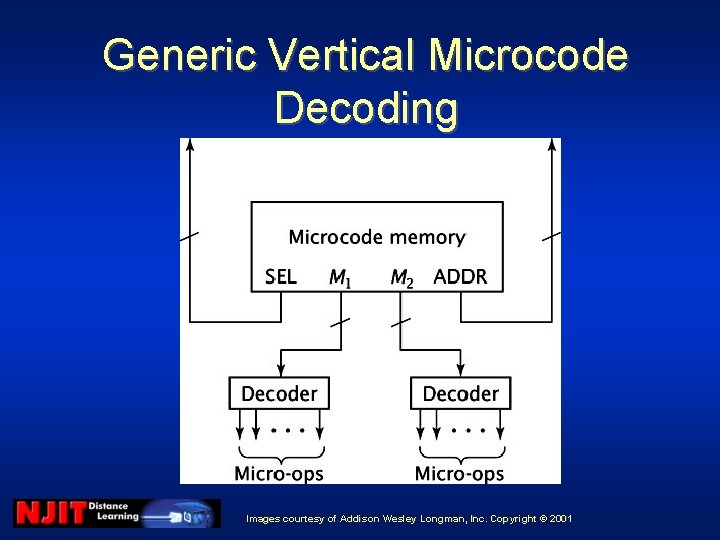

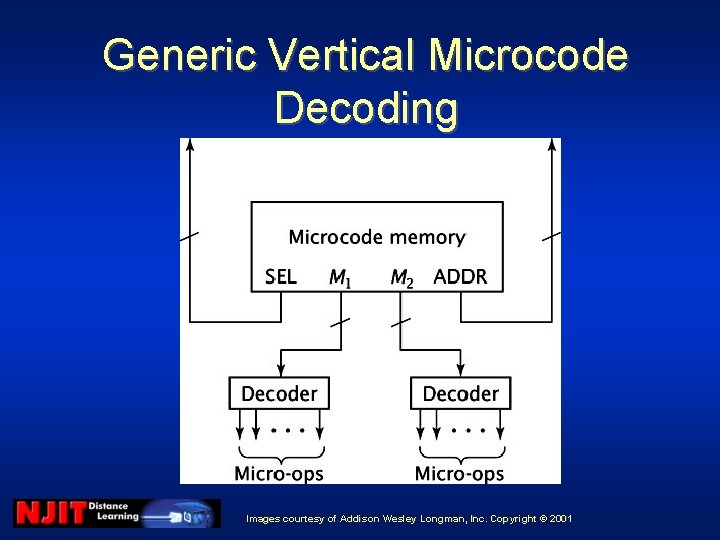

Generic Vertical Microcode Decoding Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

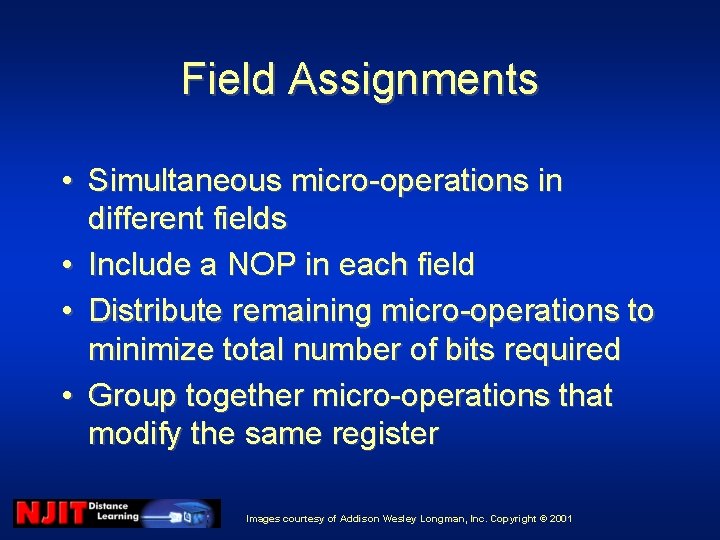

Field Assignments • Simultaneous micro-operations in different fields Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Field Assignments • Simultaneous micro-operations in different fields • Include a NOP in each field Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Field Assignments • Simultaneous micro-operations in different fields • Include a NOP in each field • Distribute remaining micro-operations to minimize total number of bits required Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Field Assignments • Simultaneous micro-operations in different fields • Include a NOP in each field • Distribute remaining micro-operations to minimize total number of bits required • Group together micro-operations that modify the same register Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

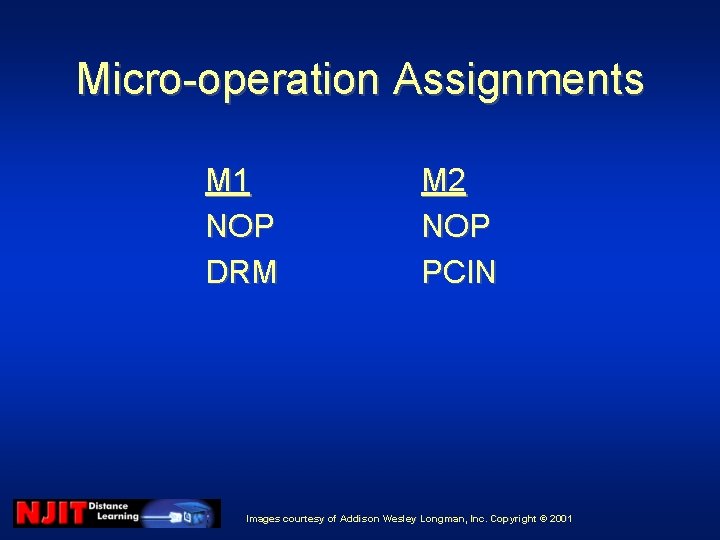

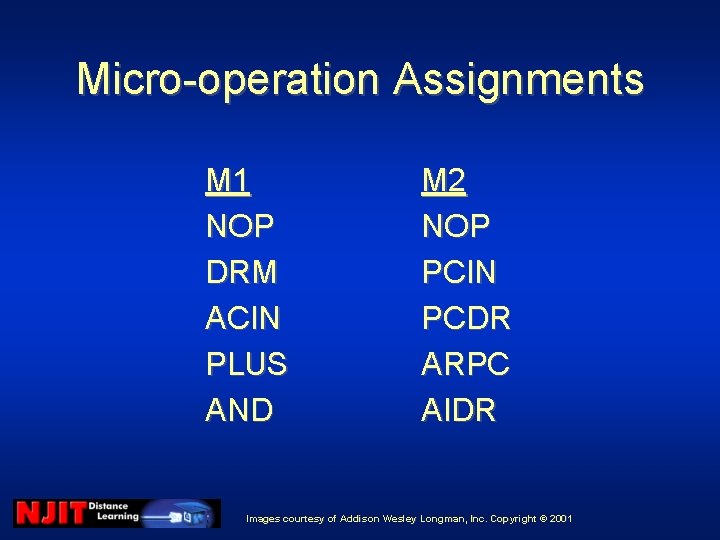

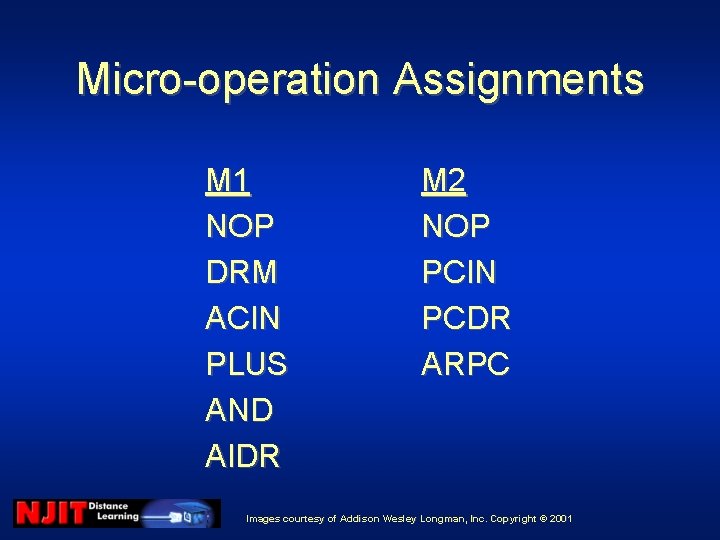

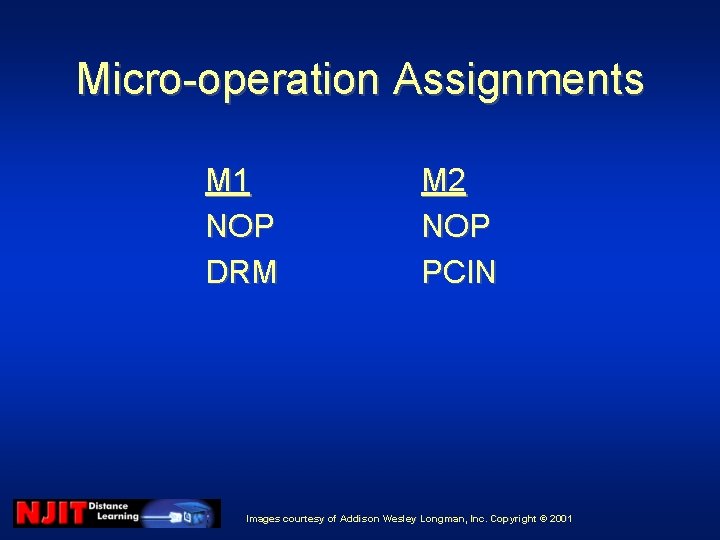

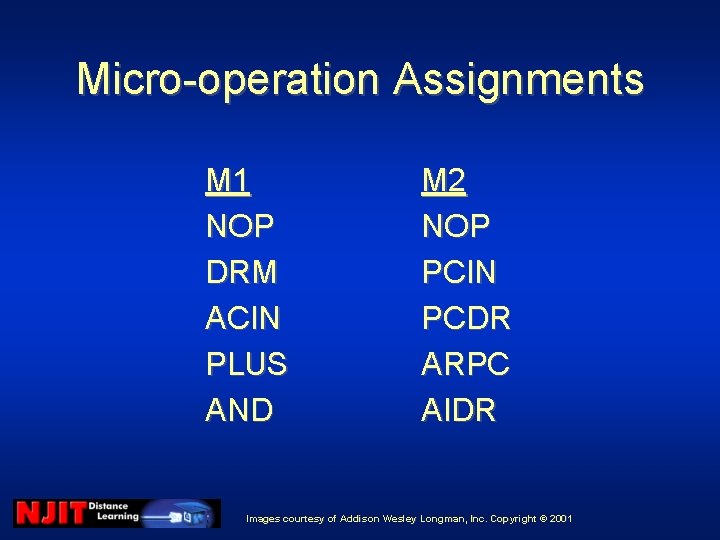

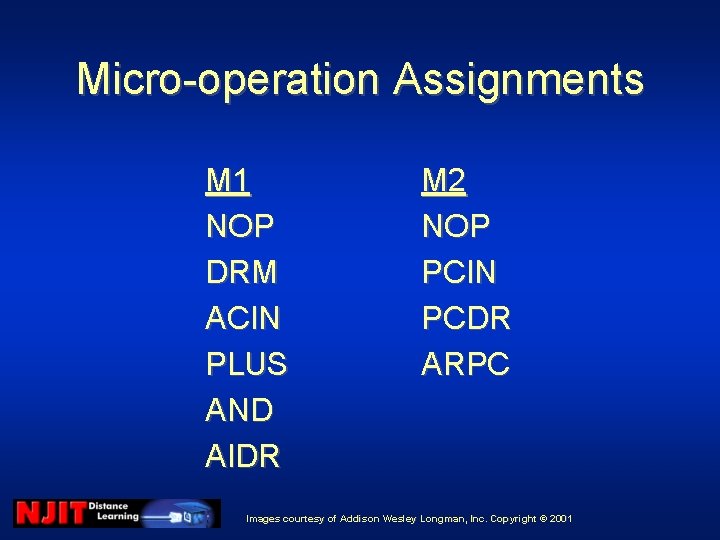

Micro-operation Assignments M 1 NOP DRM M 2 NOP PCIN Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Micro-operation Assignments M 1 NOP DRM ACIN PLUS AND M 2 NOP PCIN PCDR ARPC AIDR Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Micro-operation Assignments M 1 NOP DRM ACIN PLUS AND AIDR M 2 NOP PCIN PCDR ARPC Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

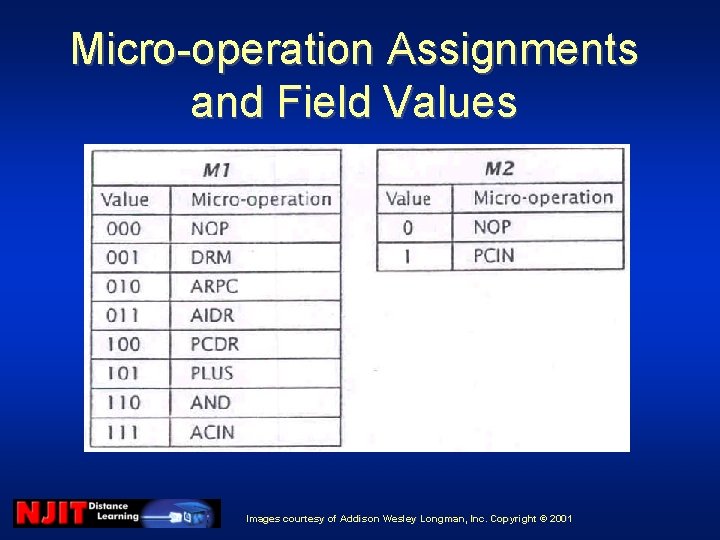

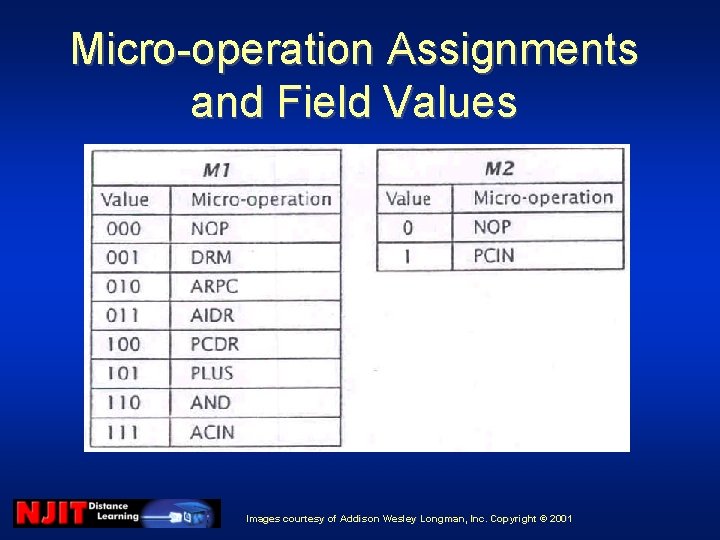

Micro-operation Assignments and Field Values Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Vertical Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

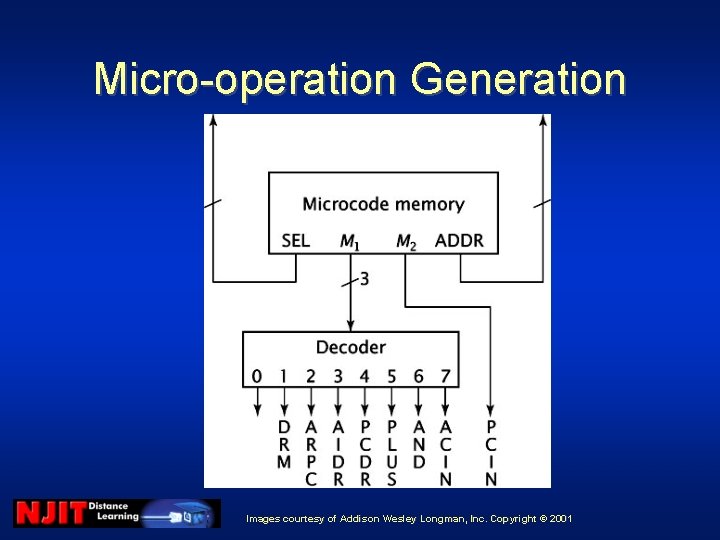

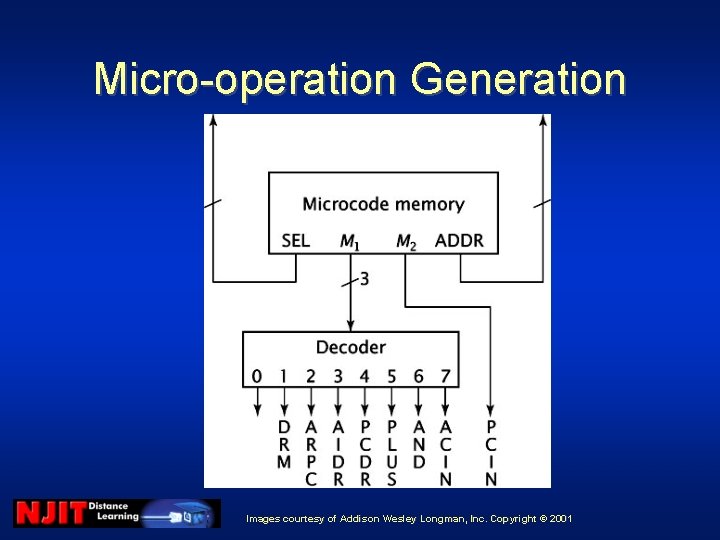

Micro-operation Generation Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

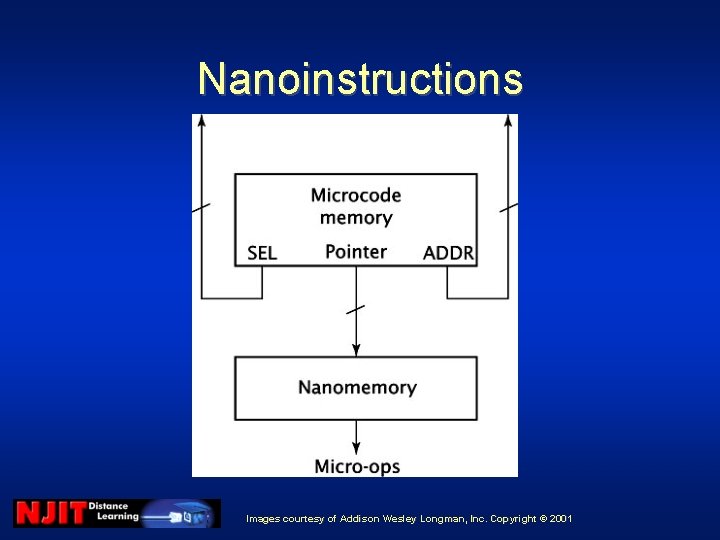

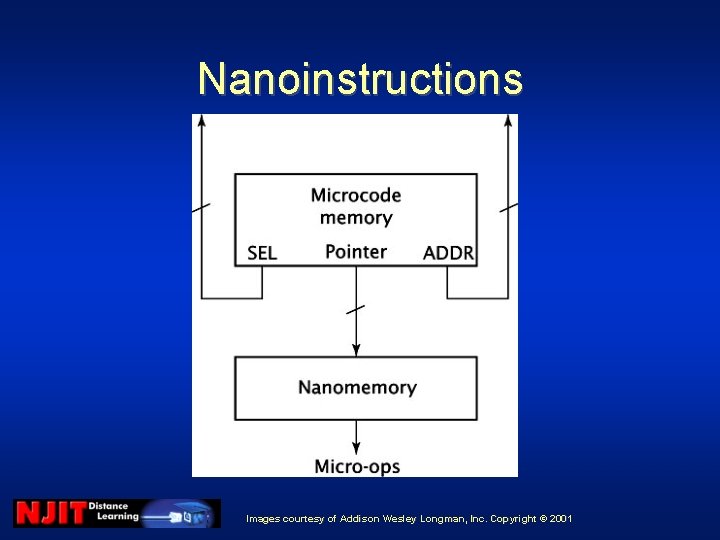

Nanoinstructions Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Directly Generating Control Signals • Output control signals instead of microoperations • No external decoding required • No external hardware required to generate control signals • More difficult to code Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

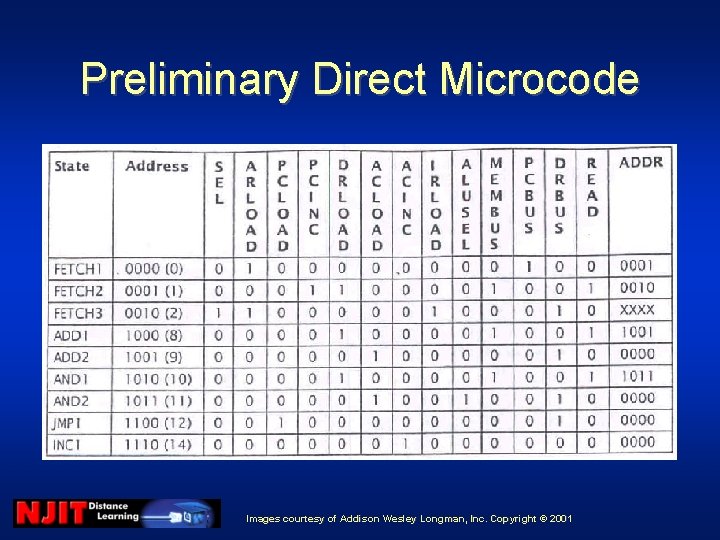

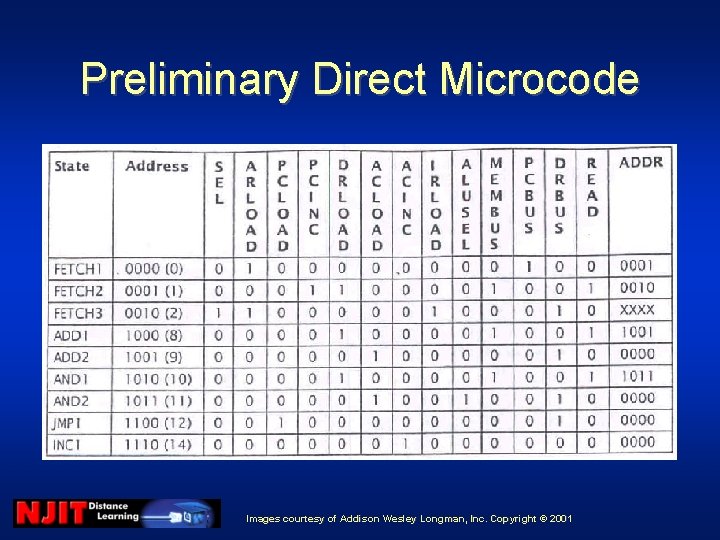

Preliminary Direct Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

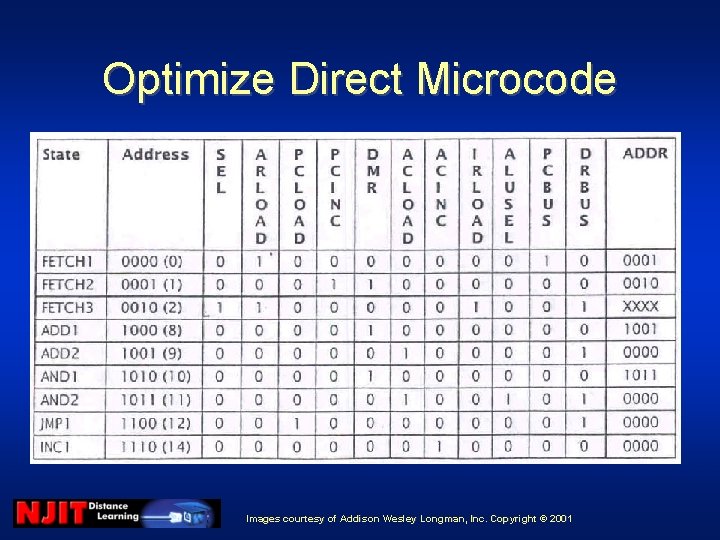

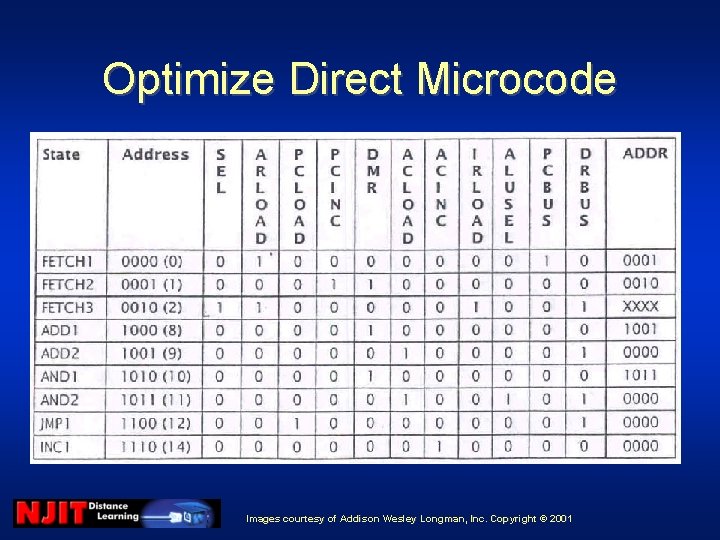

Optimize Direct Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Relatively Simple Microsequencer • No changes to – Instruction set – Data paths – ALU Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

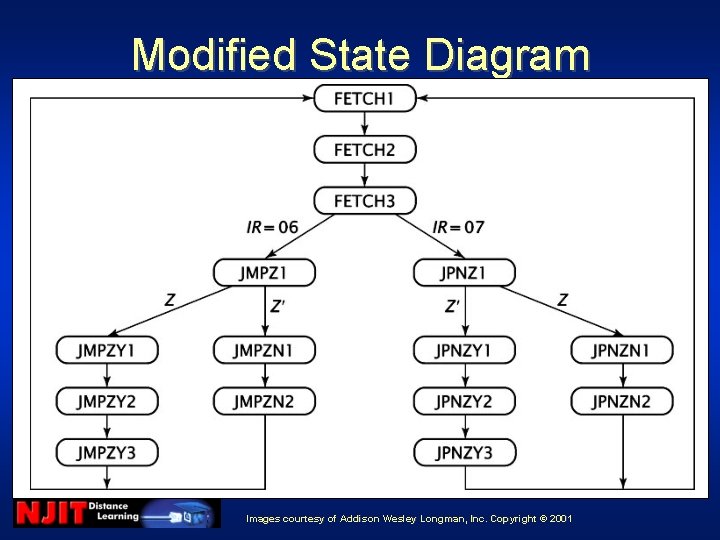

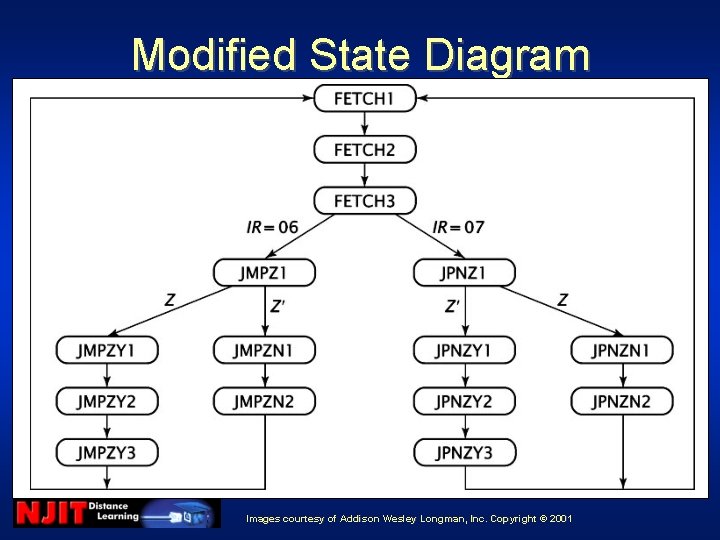

Modified State Diagram Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

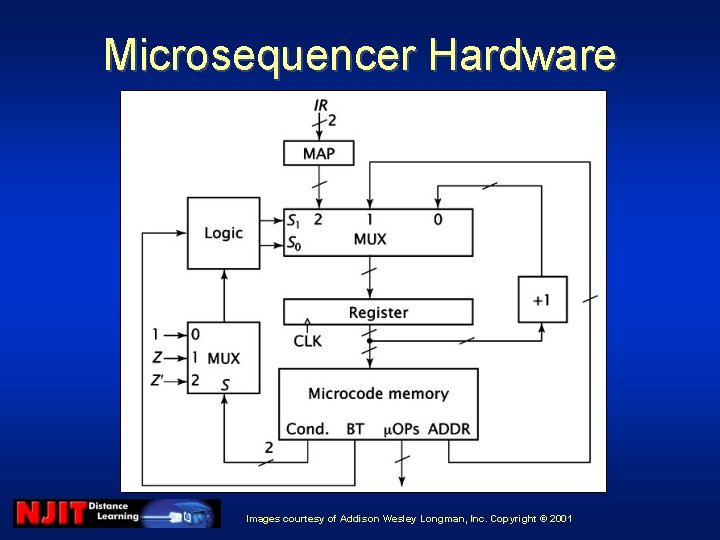

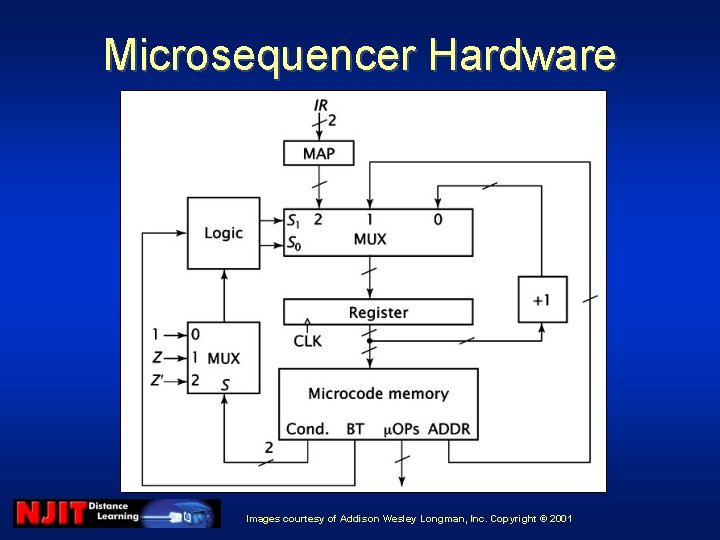

Microsequencer Hardware Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

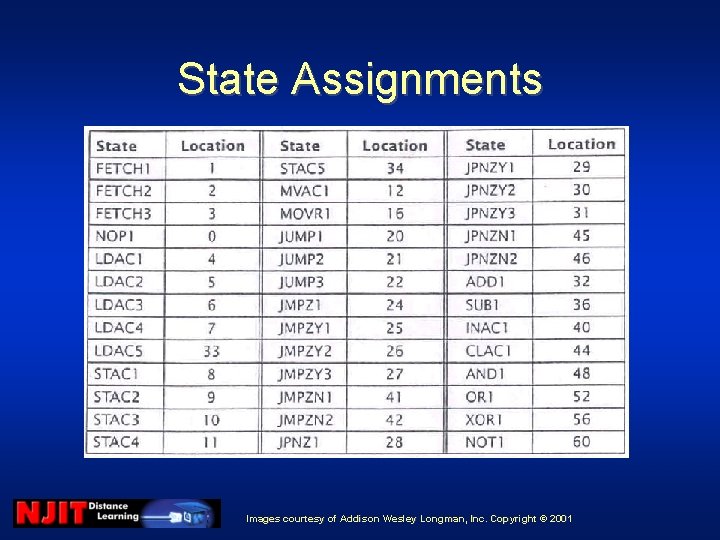

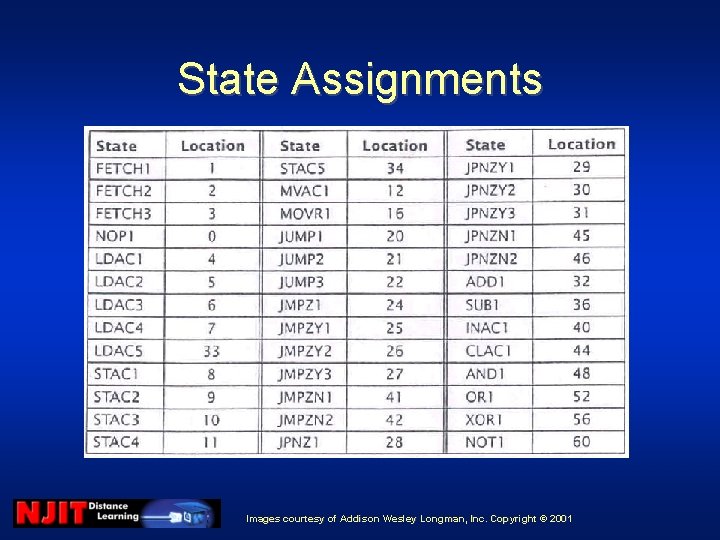

State Assignments Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

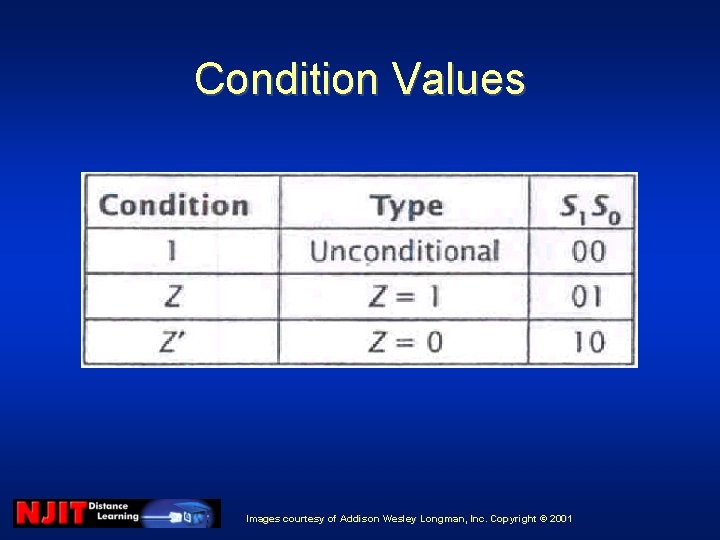

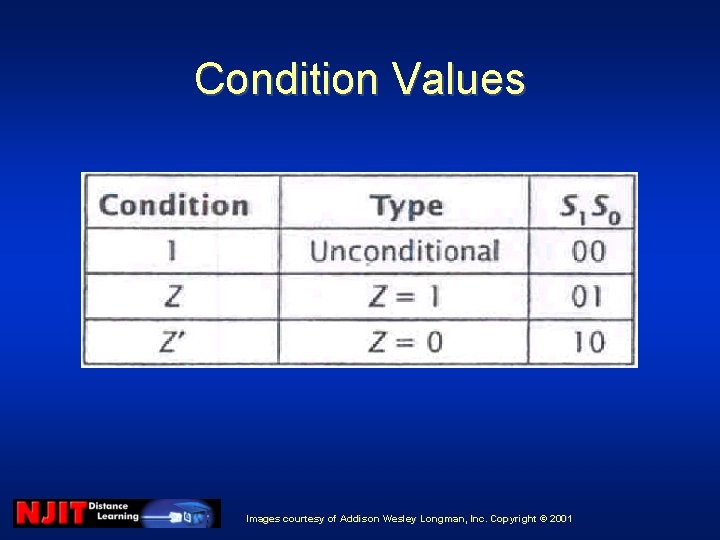

Condition Values Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

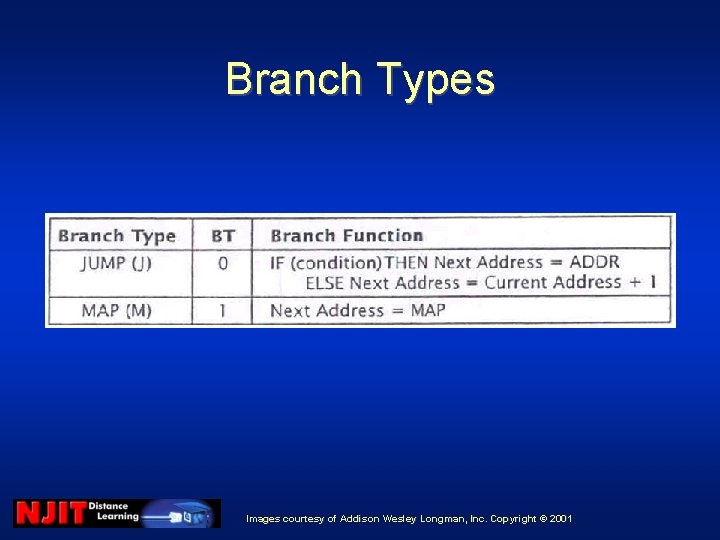

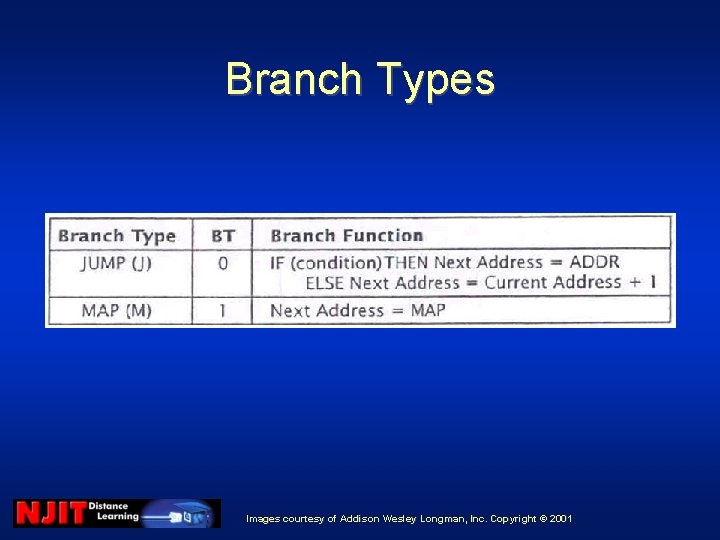

Branch Types Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

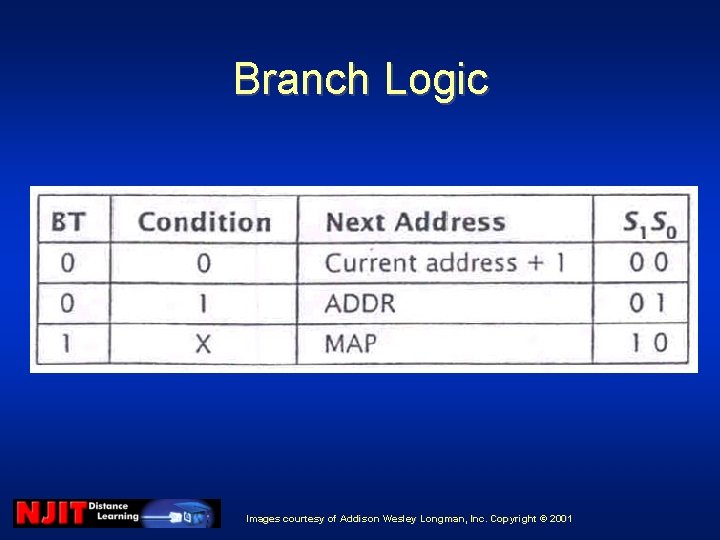

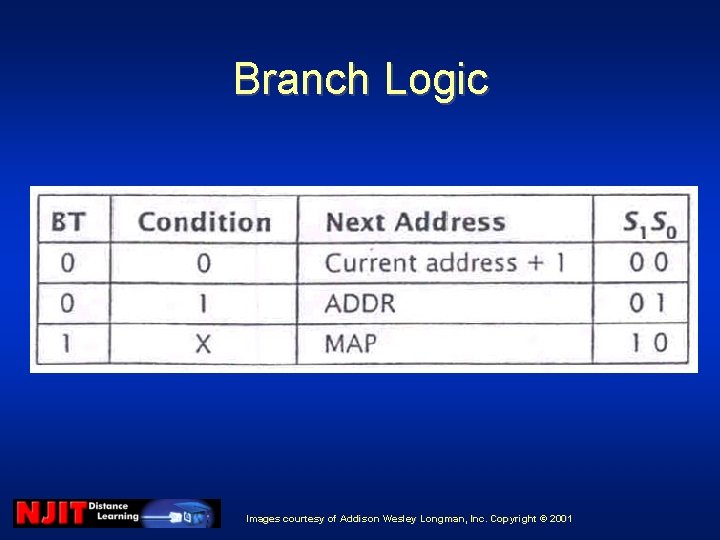

Branch Logic Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

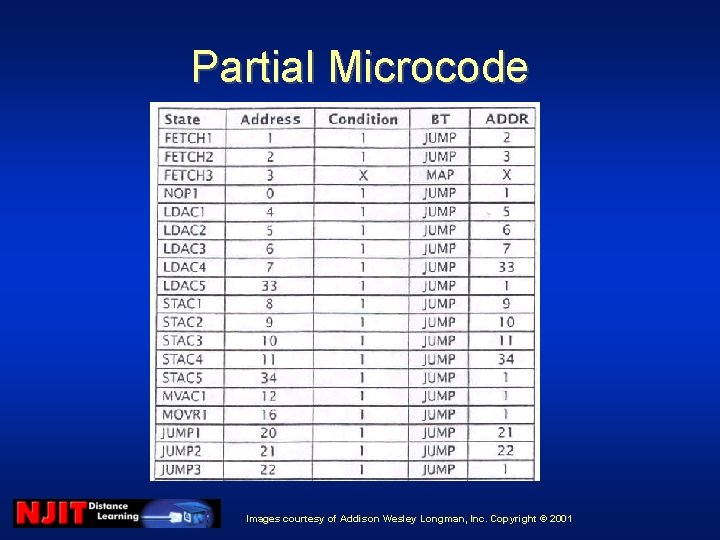

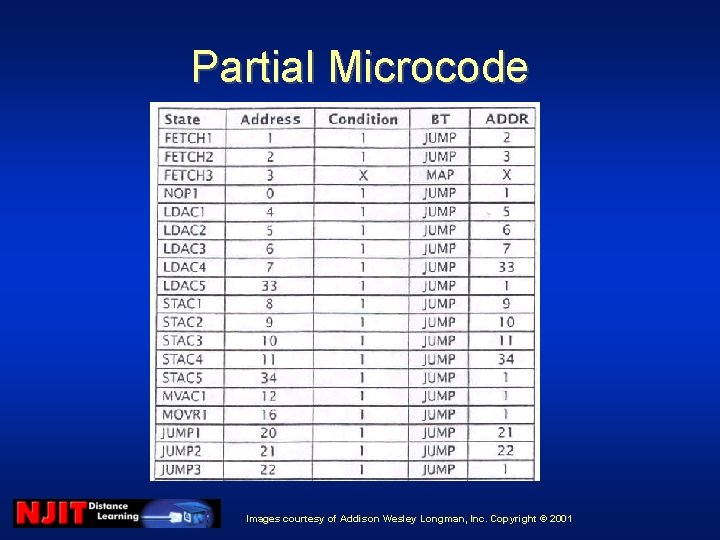

Partial Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

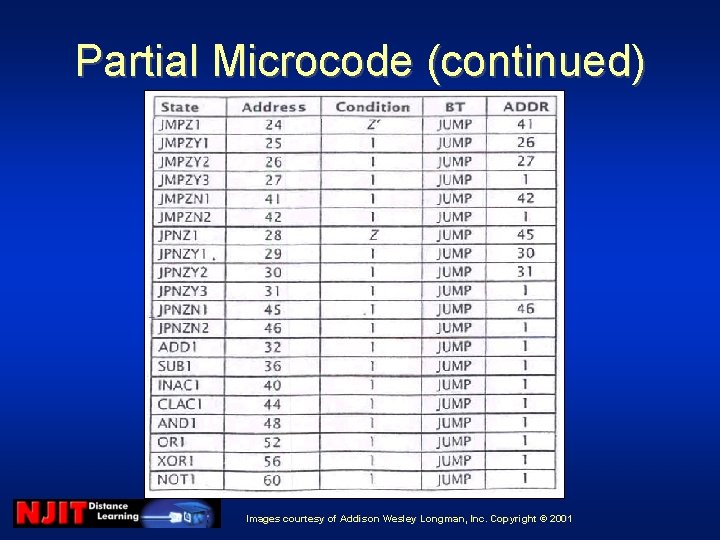

Partial Microcode (continued) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

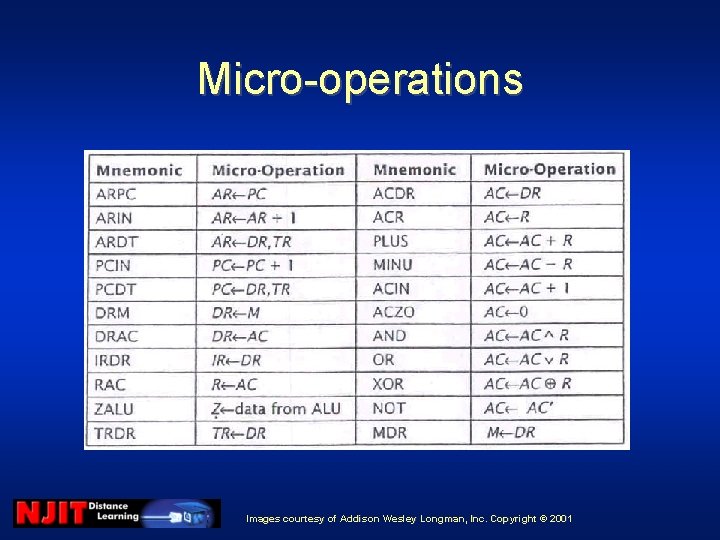

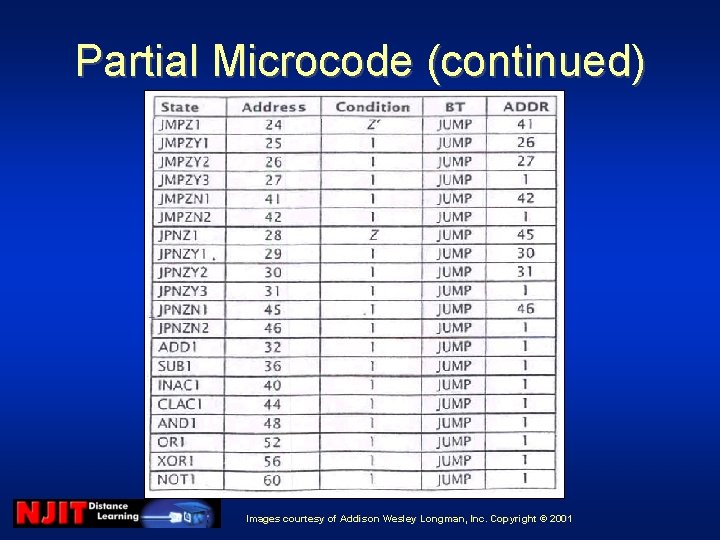

Micro-operations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

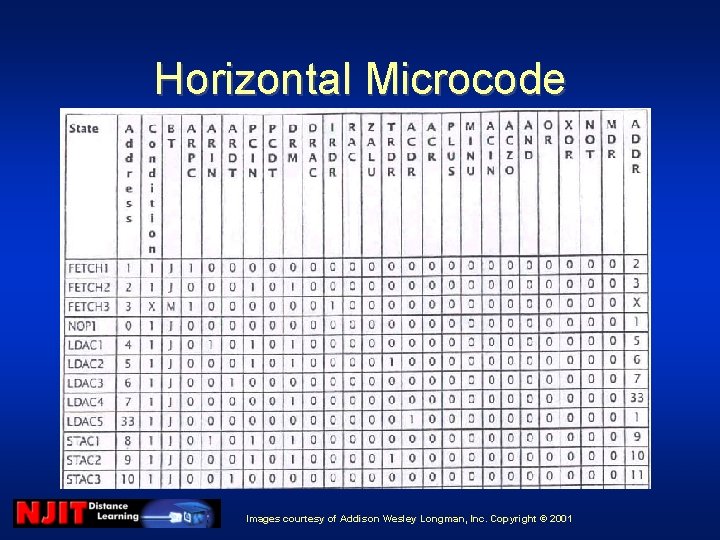

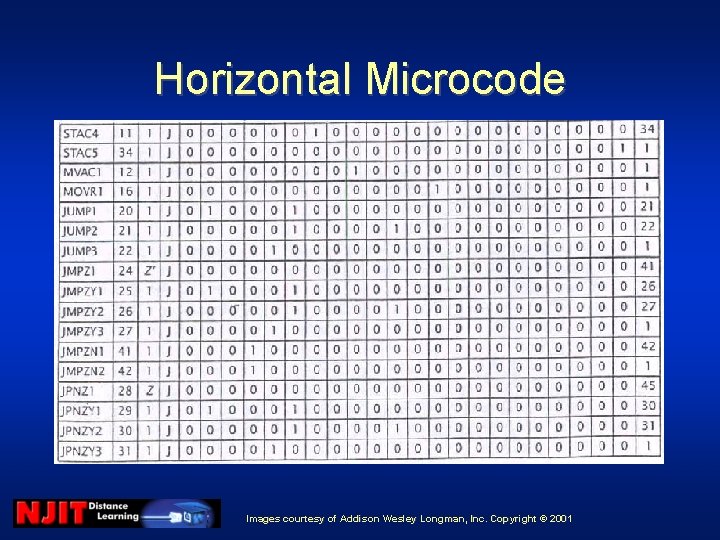

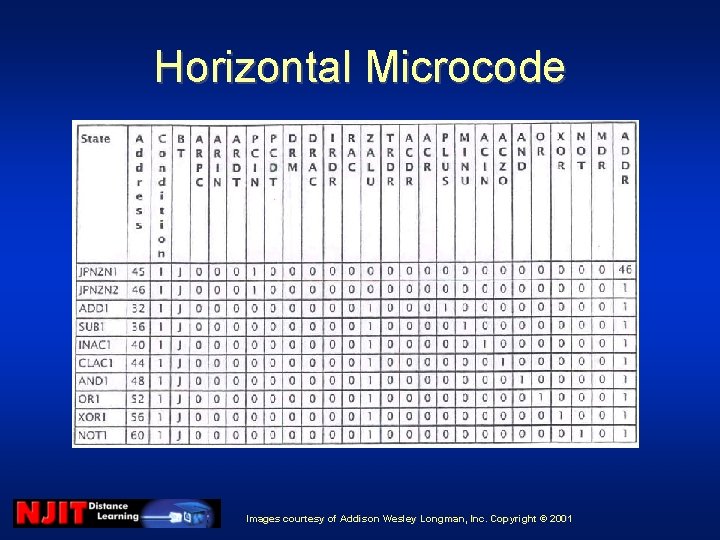

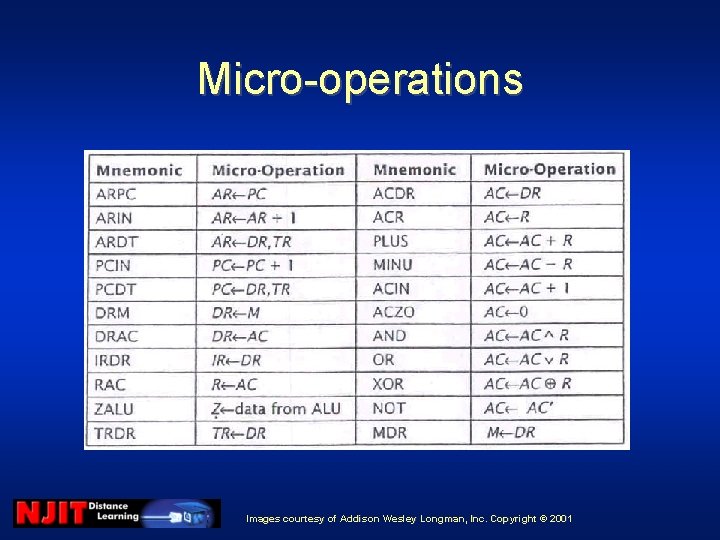

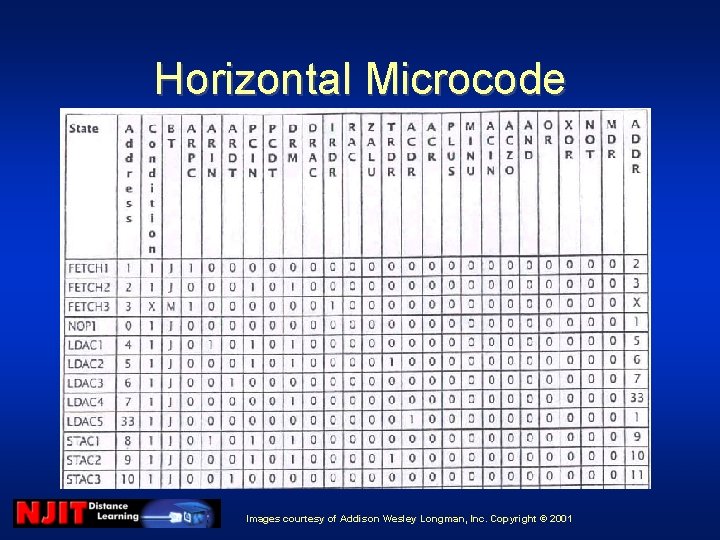

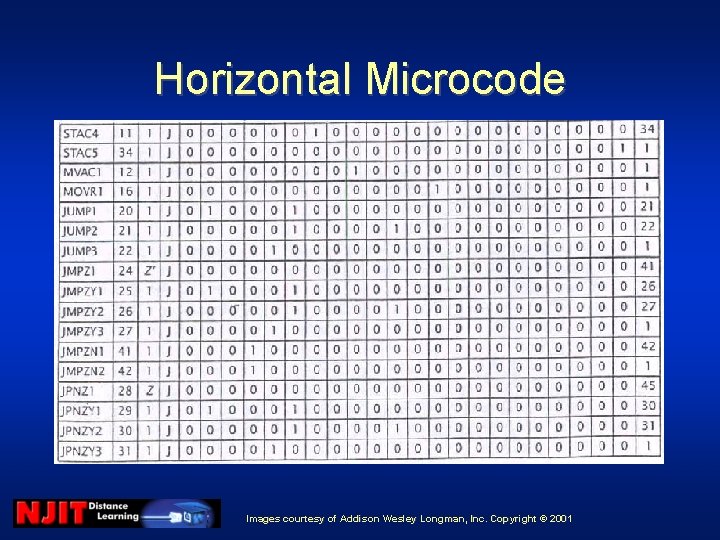

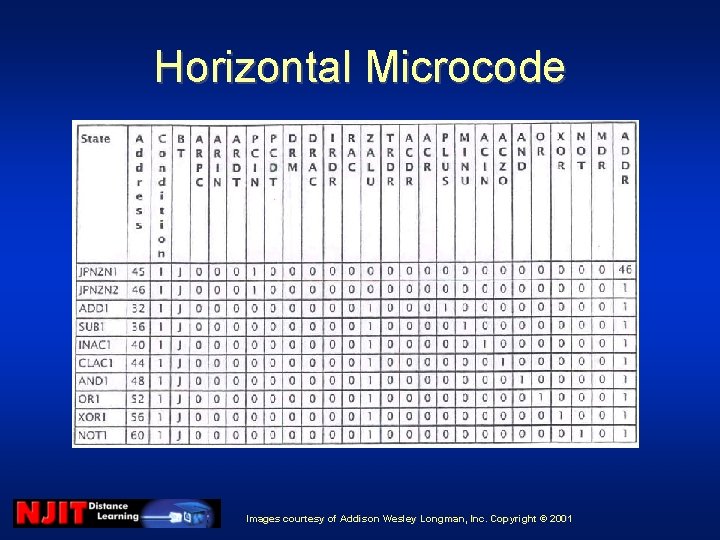

Horizontal Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Horizontal Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Horizontal Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

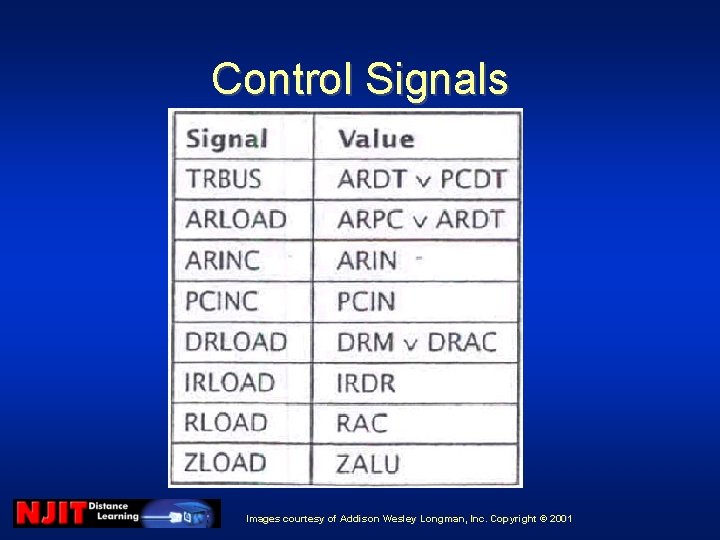

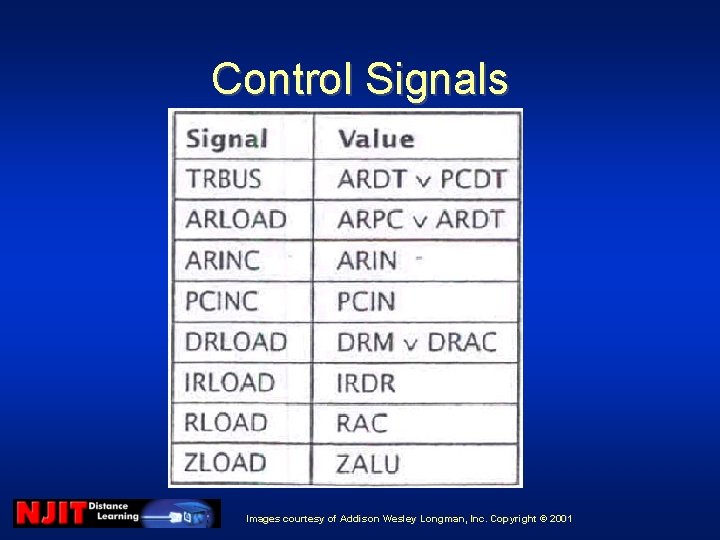

Control Signals Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Reducing the Number of Microinstructions • Microsubroutines • Microcode Jumps Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

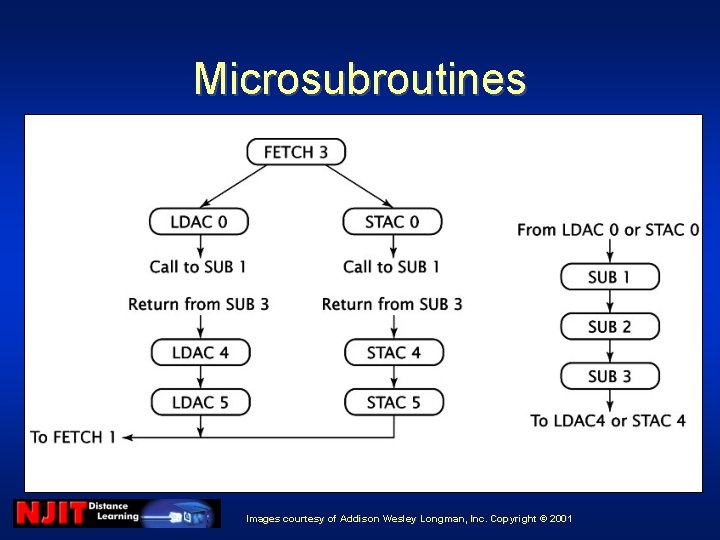

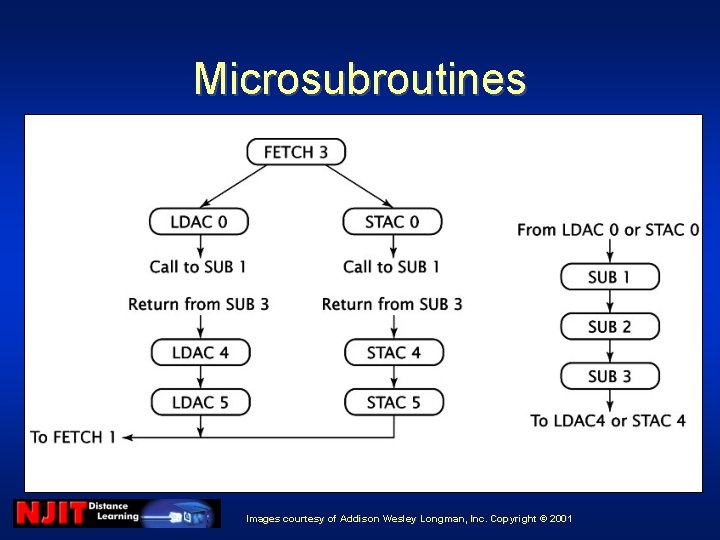

Microsubroutines Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

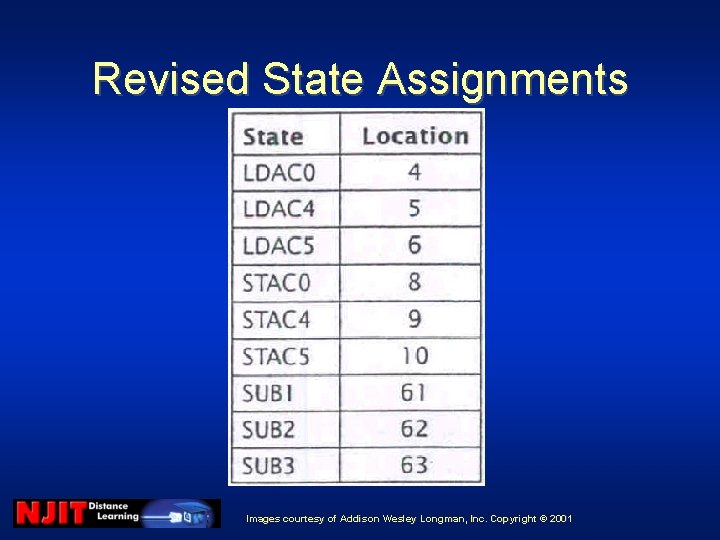

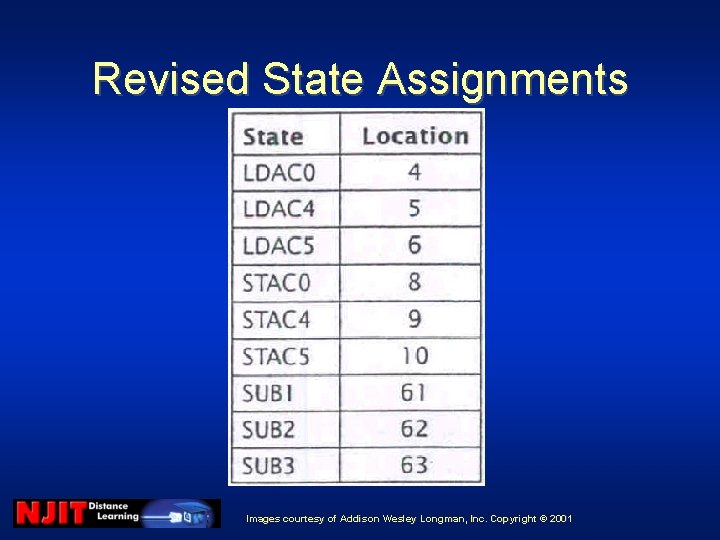

Revised State Assignments Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

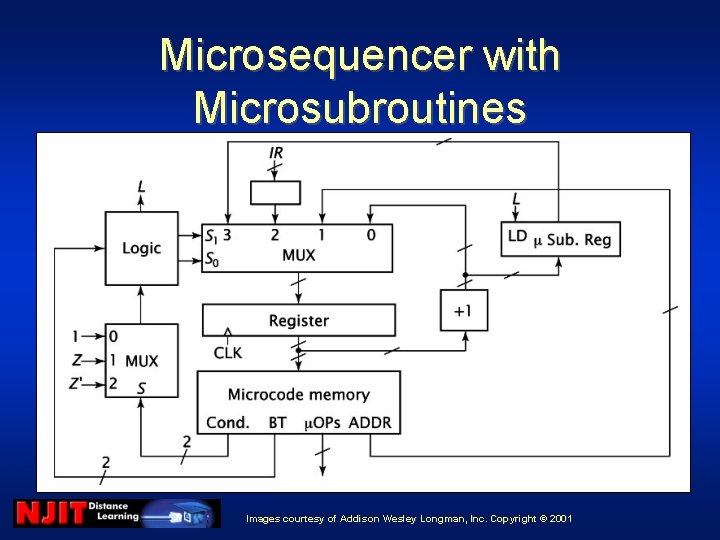

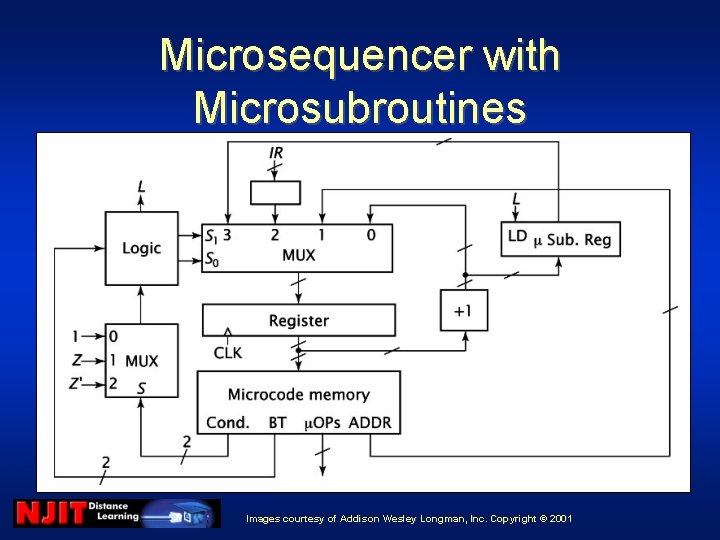

Microsequencer with Microsubroutines Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

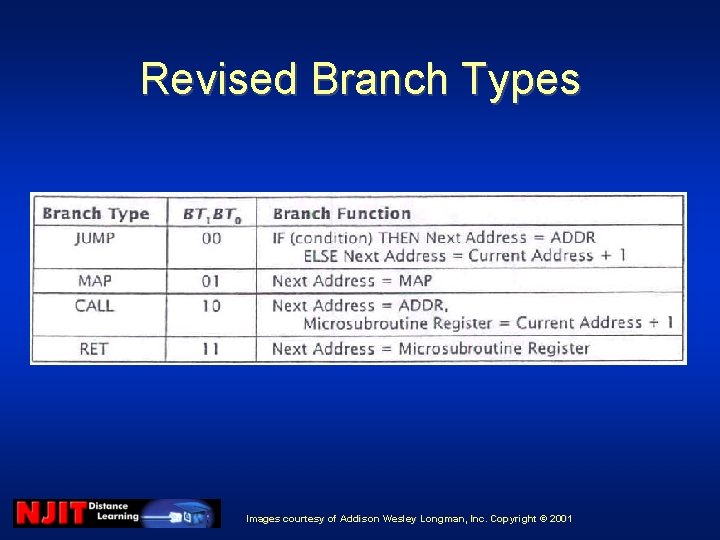

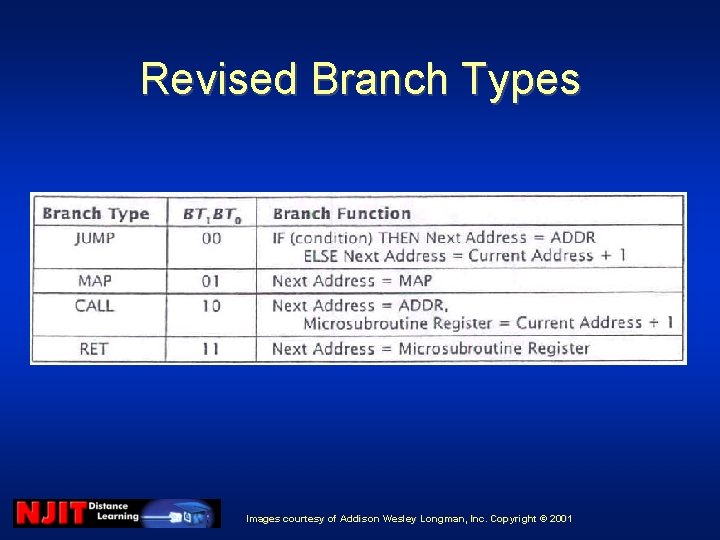

Revised Branch Types Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

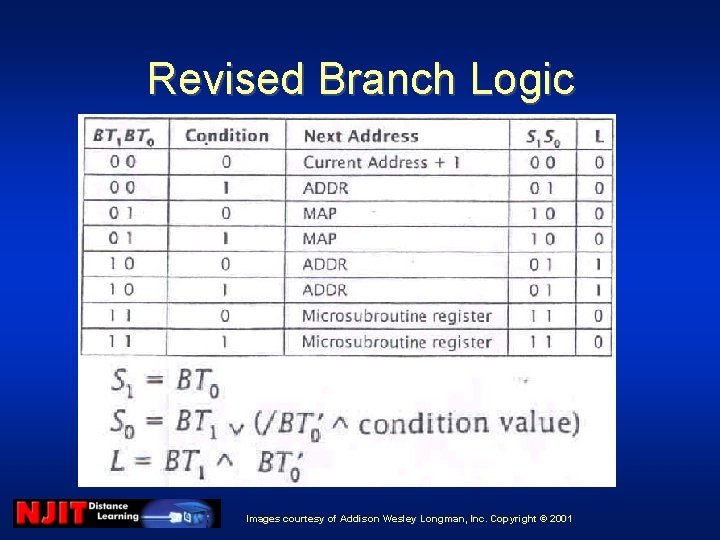

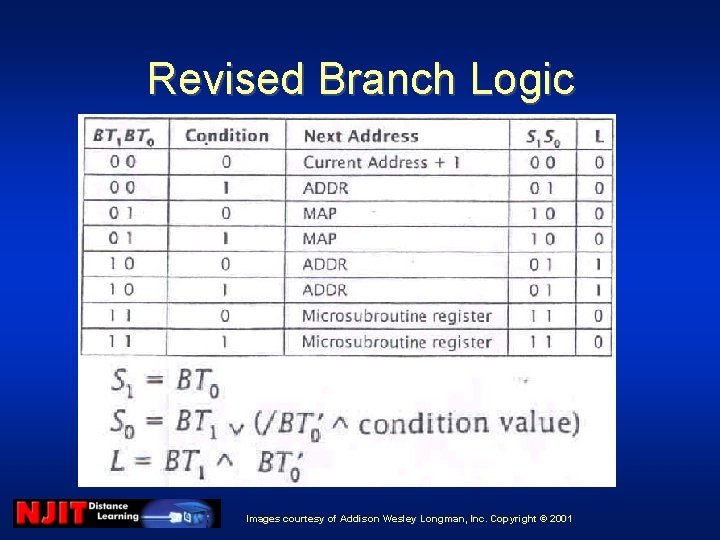

Revised Branch Logic Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

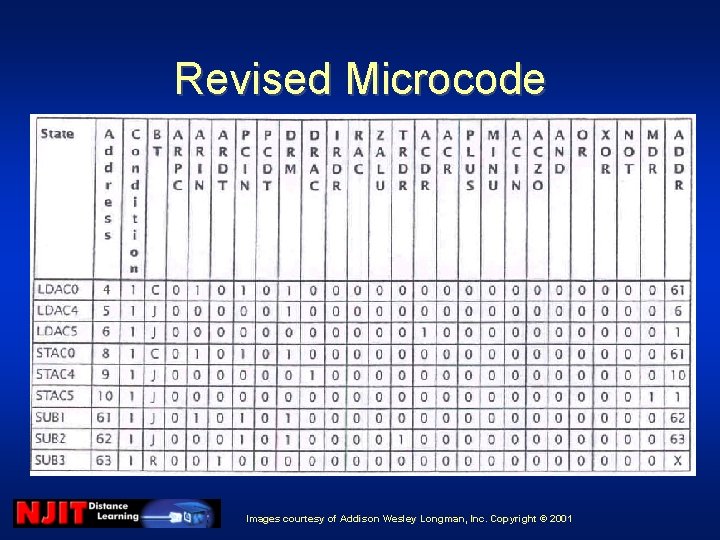

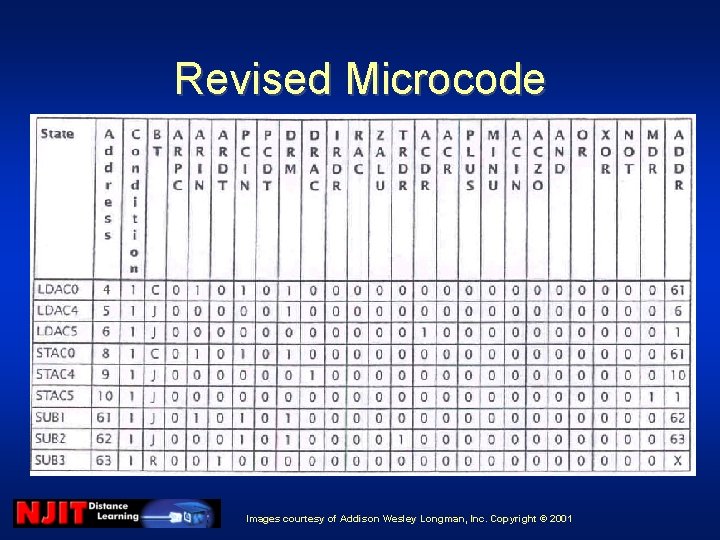

Revised Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

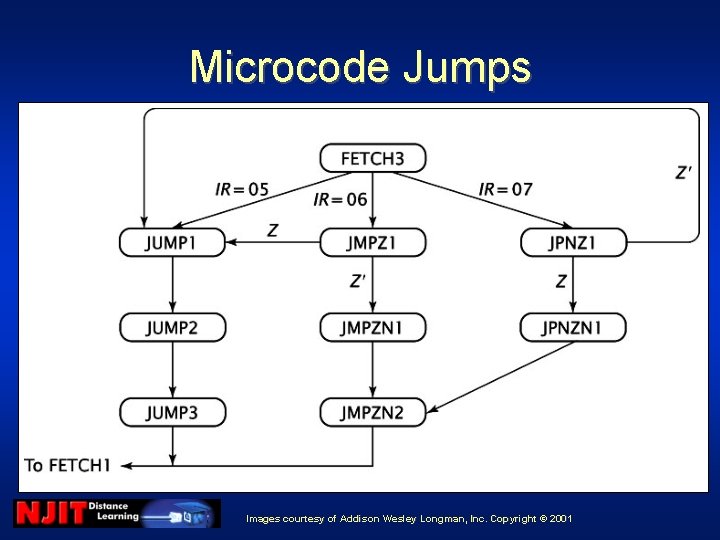

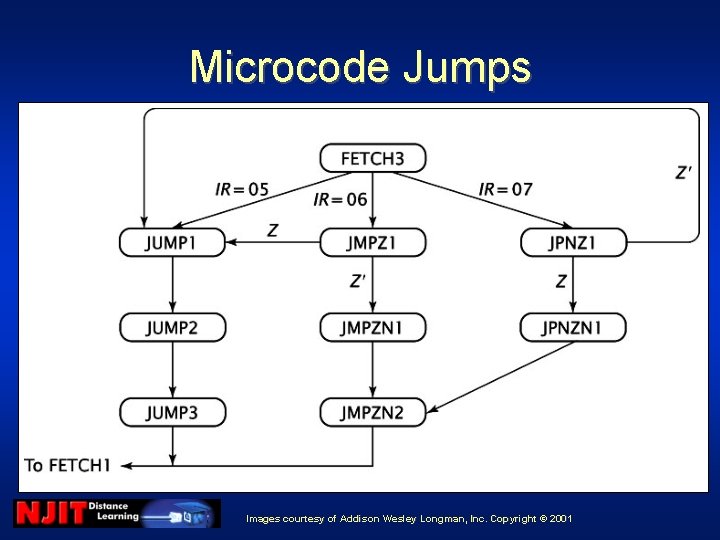

Microcode Jumps Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

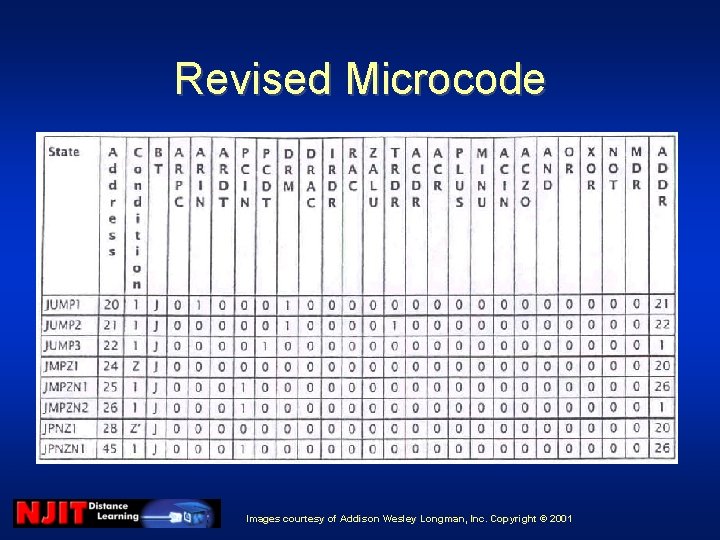

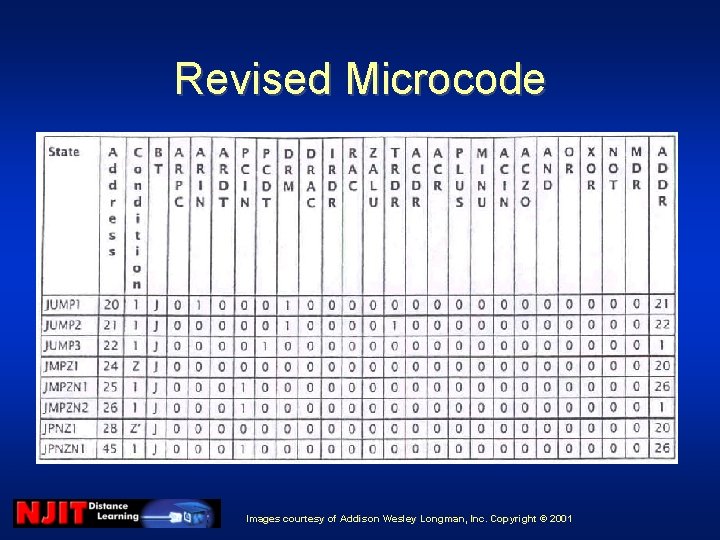

Revised Microcode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Microprogrammed Control vs. Hardwired Control • Complexity of the instruction set Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Microprogrammed Control vs. Hardwired Control • Complexity of the instruction set • Ease of modification Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Microprogrammed Control vs. Hardwired Control • • • Complexity of the instruction set Ease of modification Clock speed Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

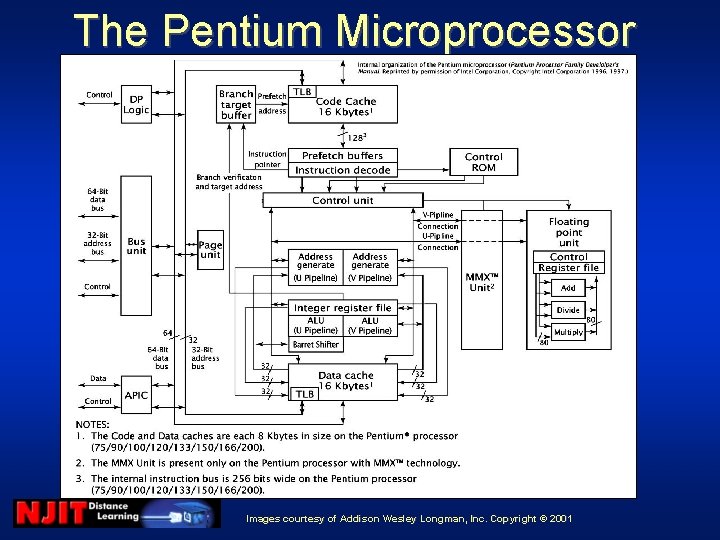

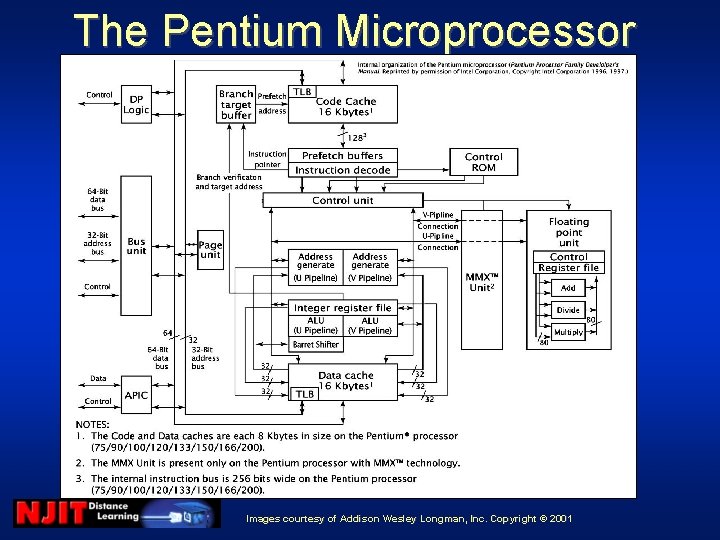

The Pentium Microprocessor Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Summary • • Basic Microsequencer Design Very Simple Microsequencer Relatively Simple Microsequencer Reducing the Number of Microinstructions • Microcoded vs. Hardwired Control • Pentium Microprocessor Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001