CHAPTER 7 LATCHED FLIPFLOPS AND TIMER INTRODUCTION Latches

- Slides: 22

CHAPTER 7 LATCHED, FLIP-FLOPS, AND TIMER

INTRODUCTION • Latches and flip-flops are the basic single-bit memory elements used to build sequential circuit with one or two inputs/outputs, designed using individual logic gates and feedback loops. • Latches: – The output of a latch depends on its current inputs and on its previous output and its change of state can happen at any time when its inputs change. • Flip-Flops: – The output of a flip-flop also depends on current inputs and its previous output but the change of state occurs at specific times determined by a clock input.

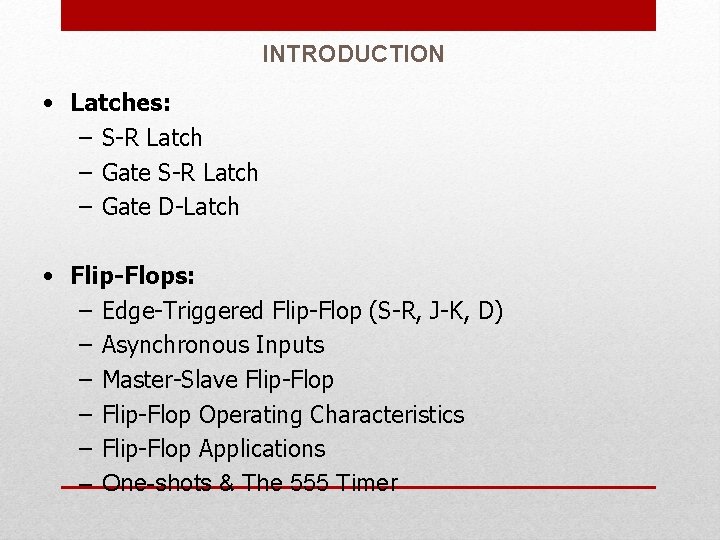

INTRODUCTION • Latches: – S-R Latch – Gate D-Latch • Flip-Flops: – Edge-Triggered Flip-Flop (S-R, J-K, D) – Asynchronous Inputs – Master-Slave Flip-Flop – Flip-Flop Operating Characteristics – Flip-Flop Applications – One-shots & The 555 Timer

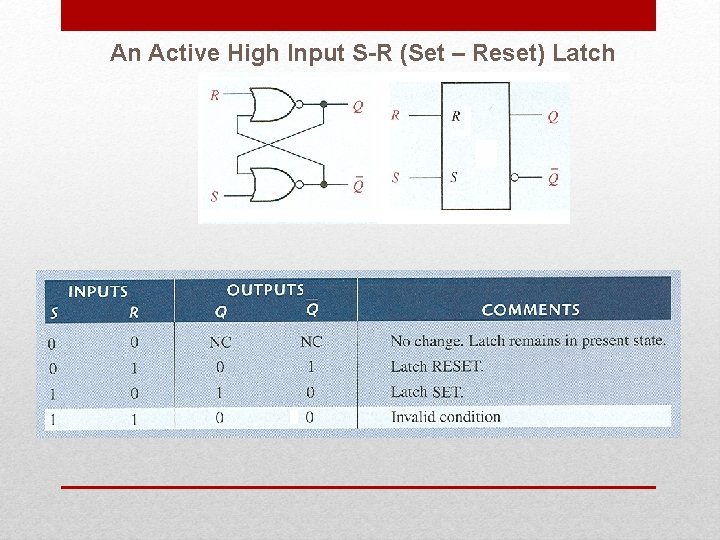

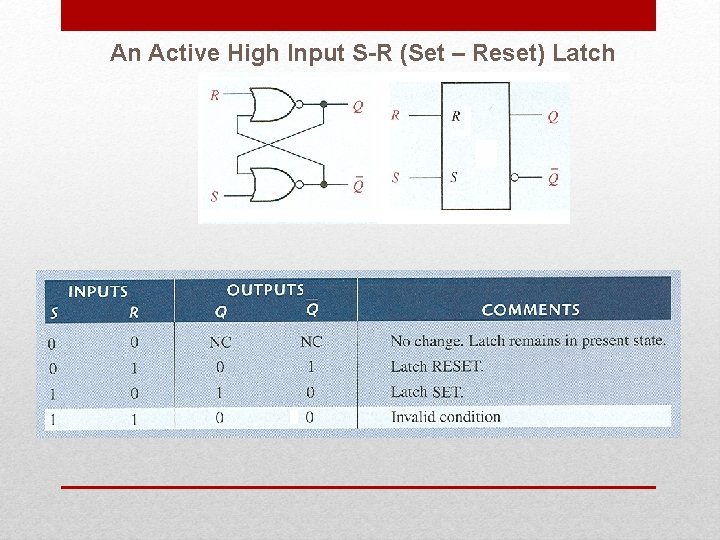

An Active High Input S-R (Set – Reset) Latch

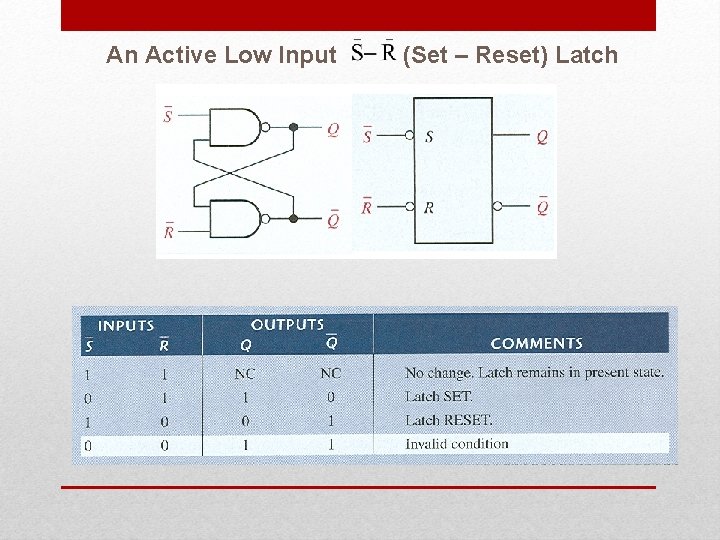

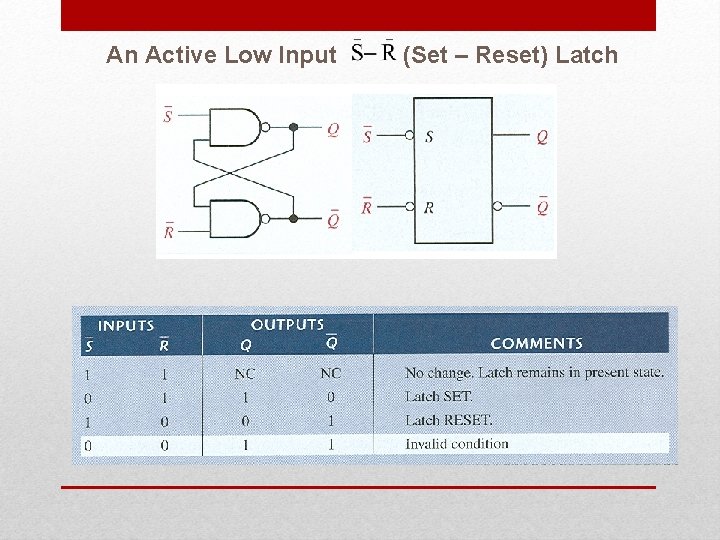

An Active Low Input (Set – Reset) Latch

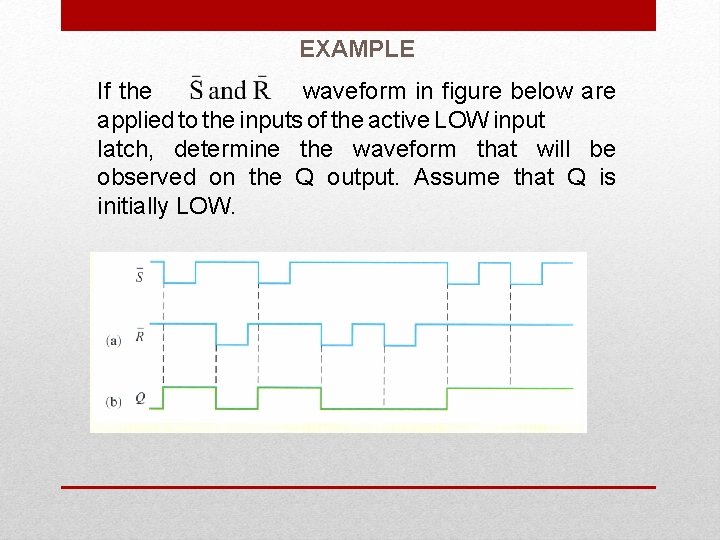

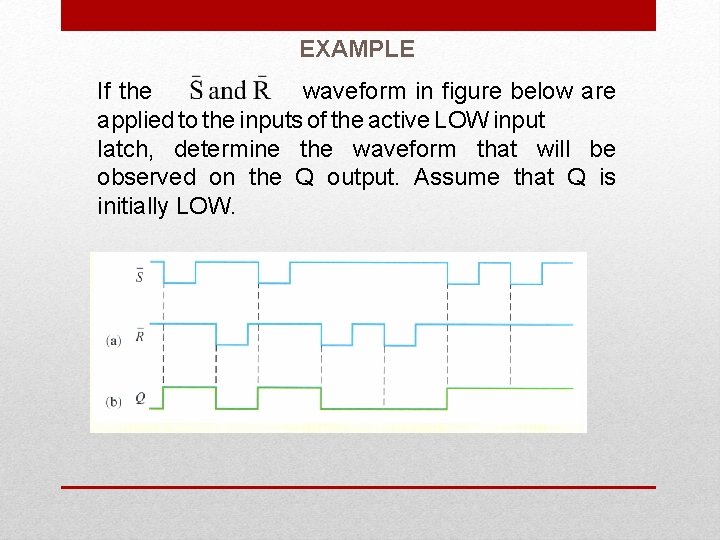

EXAMPLE If the waveform in figure below are applied to the inputs of the active LOW input latch, determine the waveform that will be observed on the Q output. Assume that Q is initially LOW.

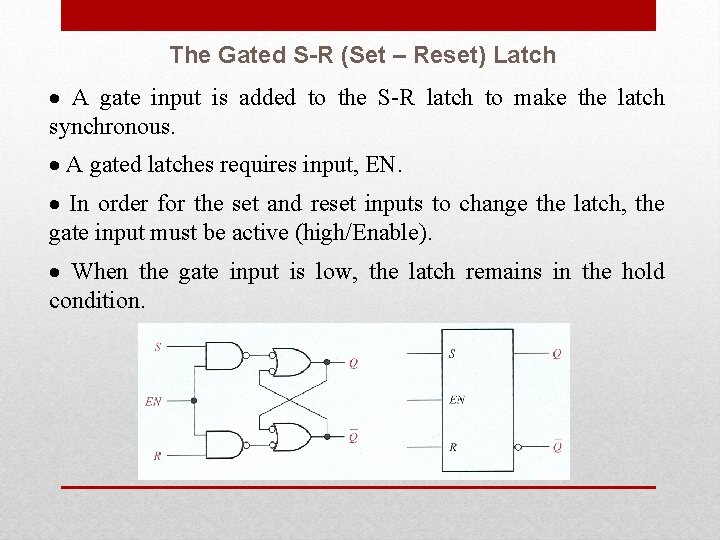

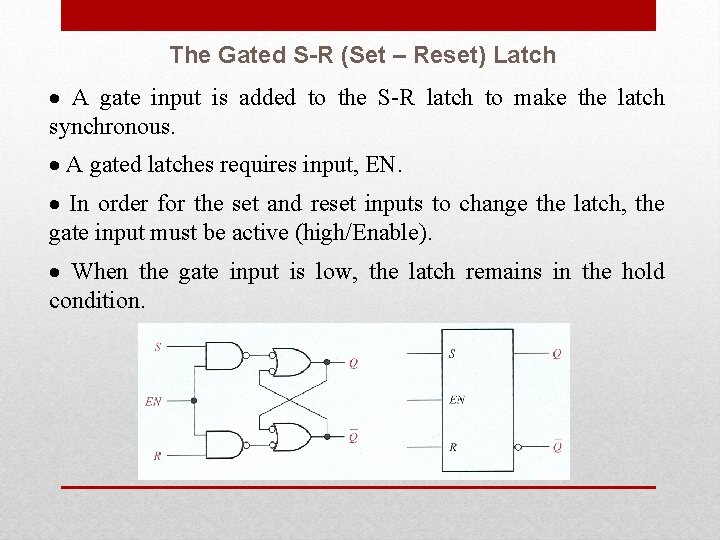

The Gated S-R (Set – Reset) Latch · A gate input is added to the S-R latch to make the latch synchronous. · A gated latches requires input, EN. · In order for the set and reset inputs to change the latch, the gate input must be active (high/Enable). · When the gate input is low, the latch remains in the hold condition.

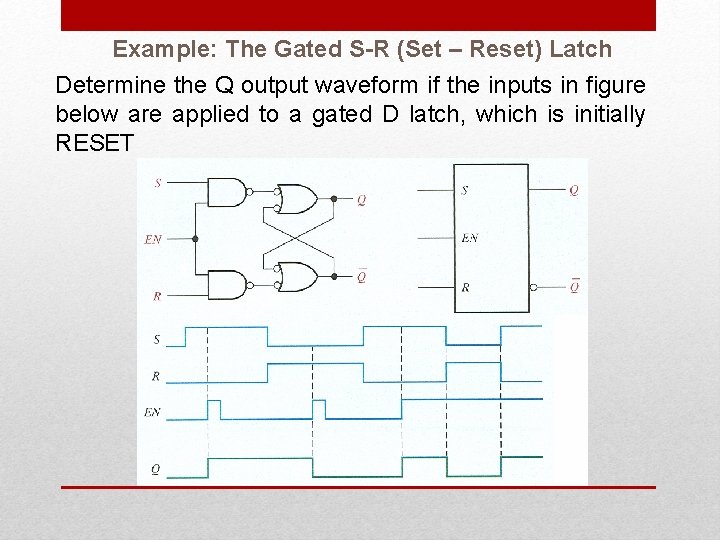

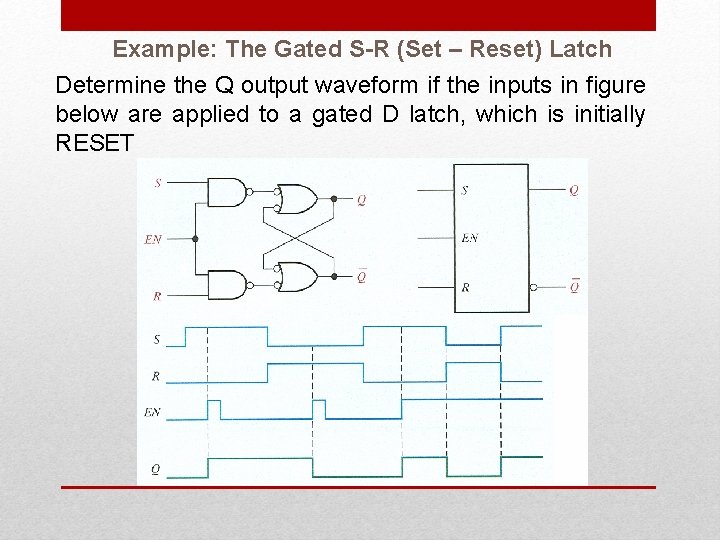

Example: The Gated S-R (Set – Reset) Latch Determine the Q output waveform if the inputs in figure below are applied to a gated D latch, which is initially RESET

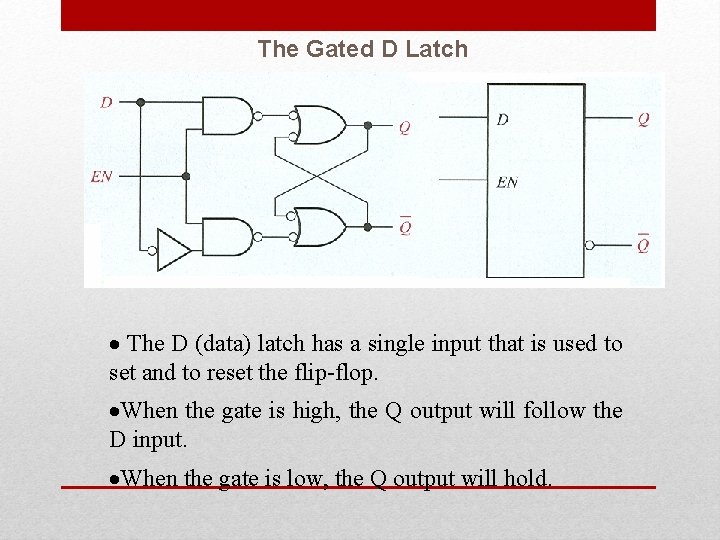

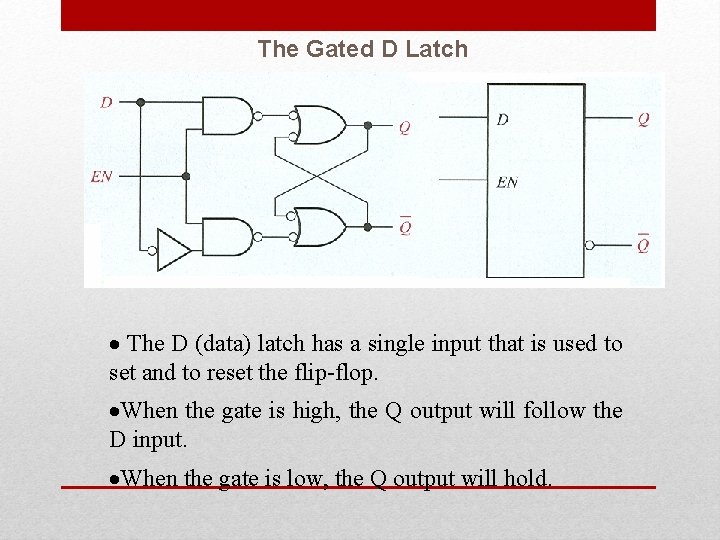

The Gated D Latch · The D (data) latch has a single input that is used to set and to reset the flip-flop. ·When the gate is high, the Q output will follow the D input. ·When the gate is low, the Q output will hold.

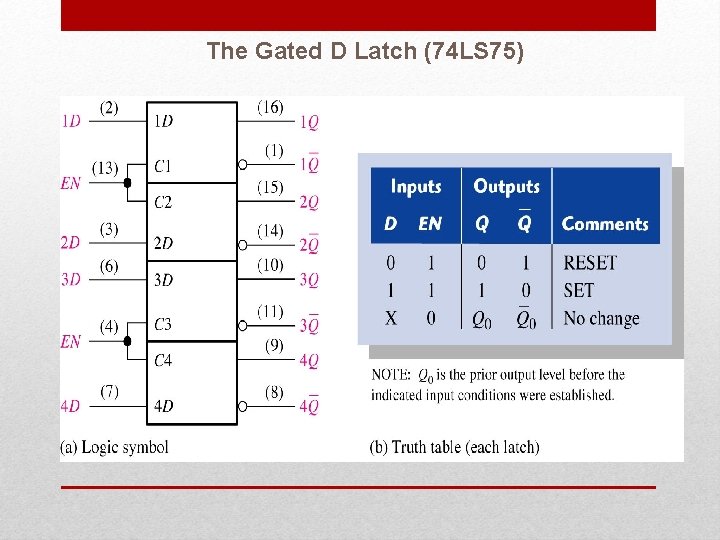

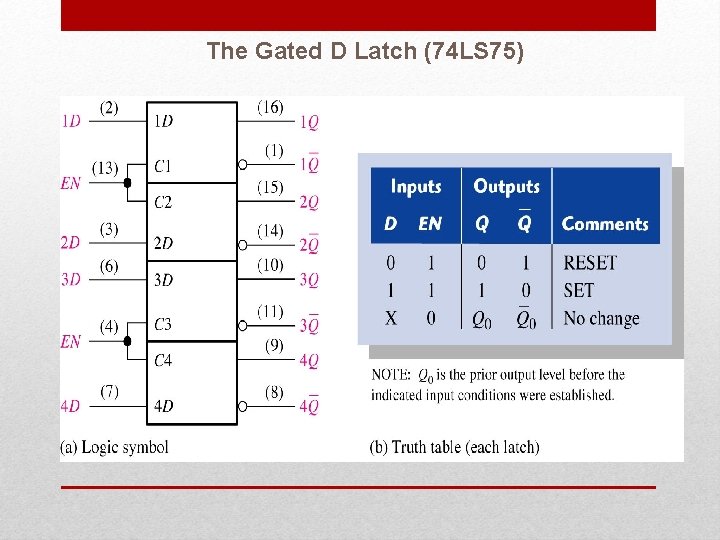

The Gated D Latch (74 LS 75)

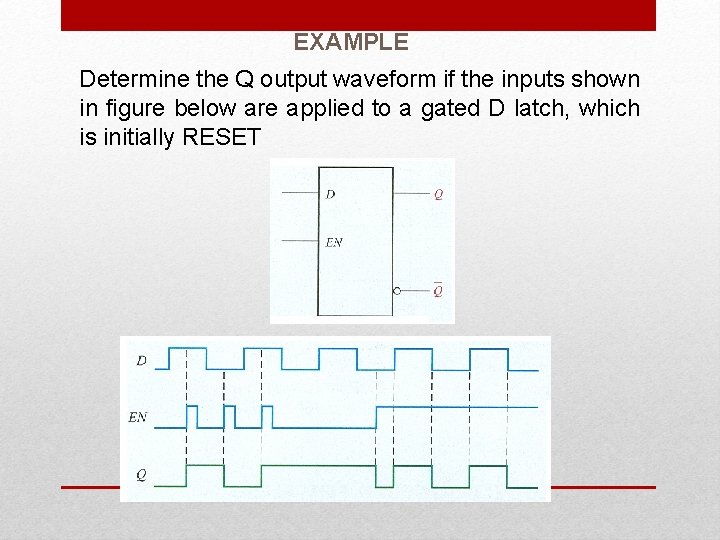

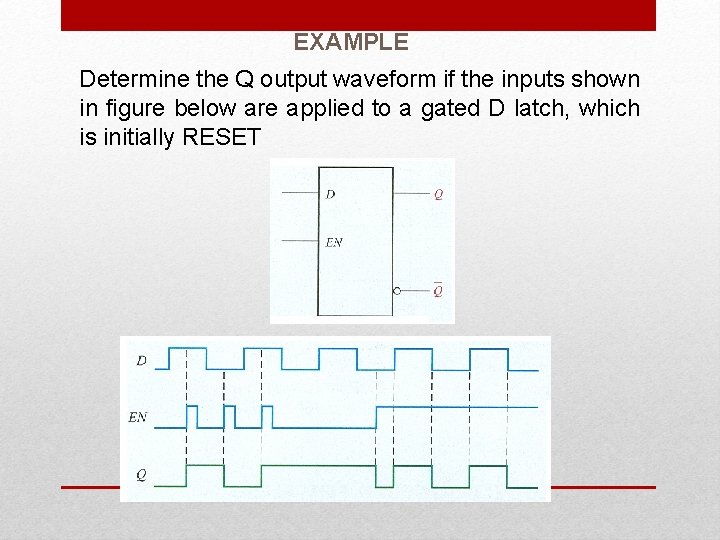

EXAMPLE Determine the Q output waveform if the inputs shown in figure below are applied to a gated D latch, which is initially RESET

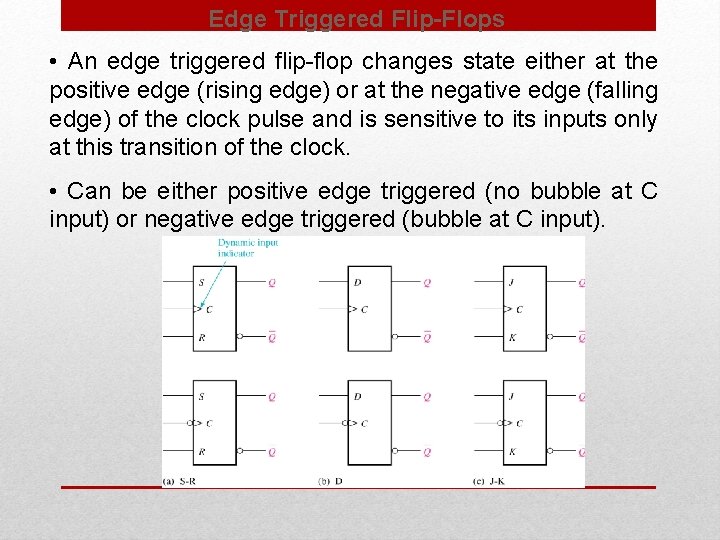

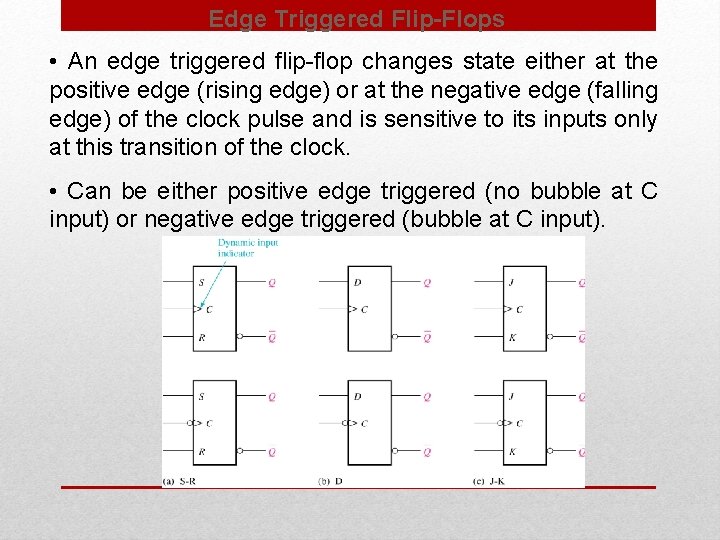

Edge Triggered Flip-Flops • An edge triggered flip-flop changes state either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock pulse and is sensitive to its inputs only at this transition of the clock. • Can be either positive edge triggered (no bubble at C input) or negative edge triggered (bubble at C input).

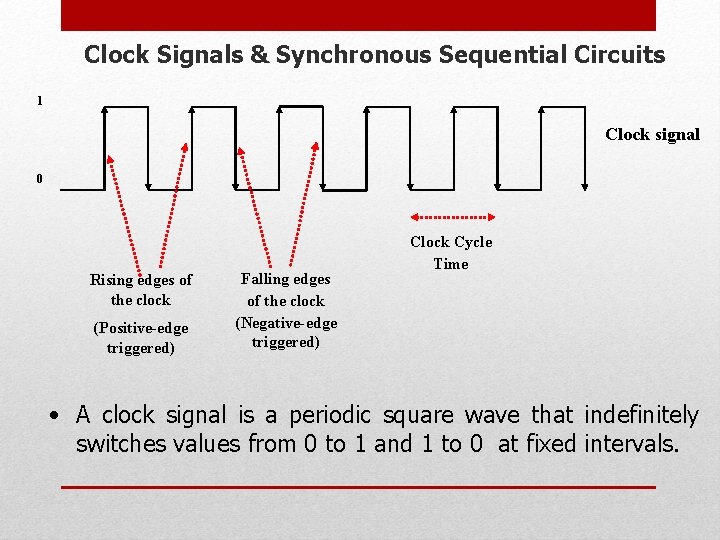

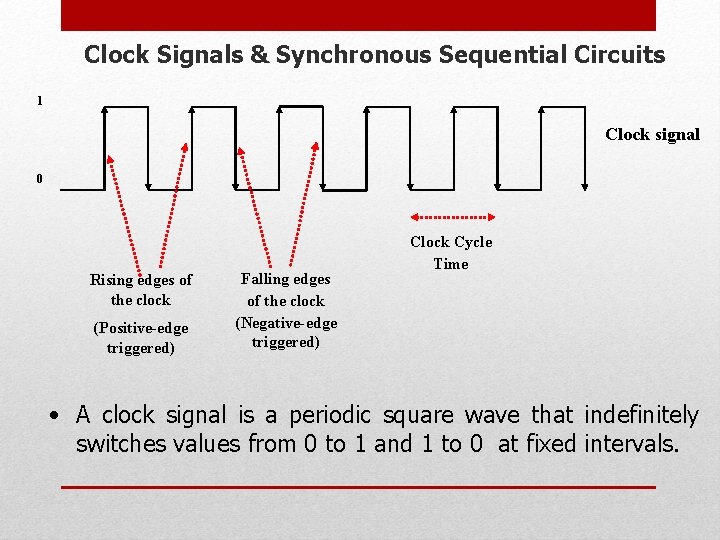

Clock Signals & Synchronous Sequential Circuits 1 Clock signal 0 Rising edges of the clock (Positive-edge triggered) Falling edges of the clock (Negative-edge triggered) Clock Cycle Time • A clock signal is a periodic square wave that indefinitely switches values from 0 to 1 and 1 to 0 at fixed intervals.

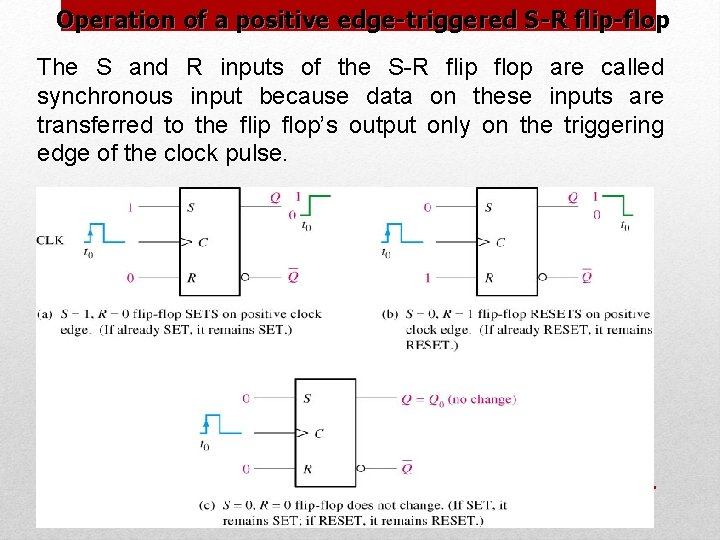

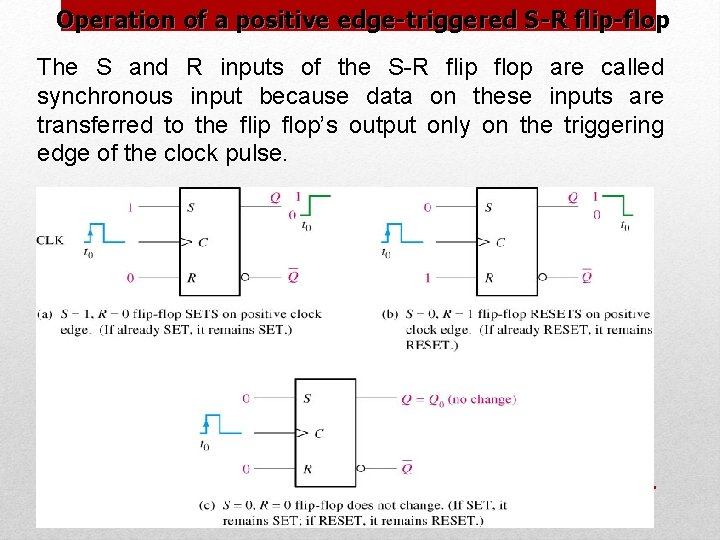

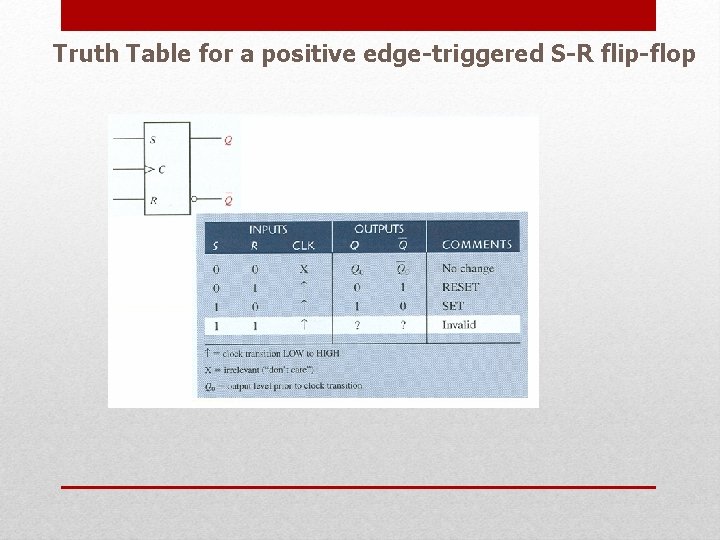

Operation of a positive edge-triggered S-R flip-flop The S and R inputs of the S-R flip flop are called synchronous input because data on these inputs are transferred to the flip flop’s output only on the triggering edge of the clock pulse.

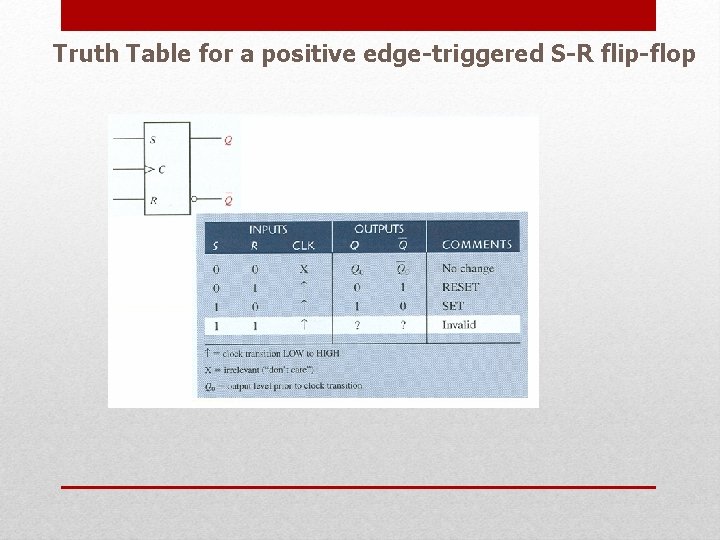

Truth Table for a positive edge-triggered S-R flip-flop

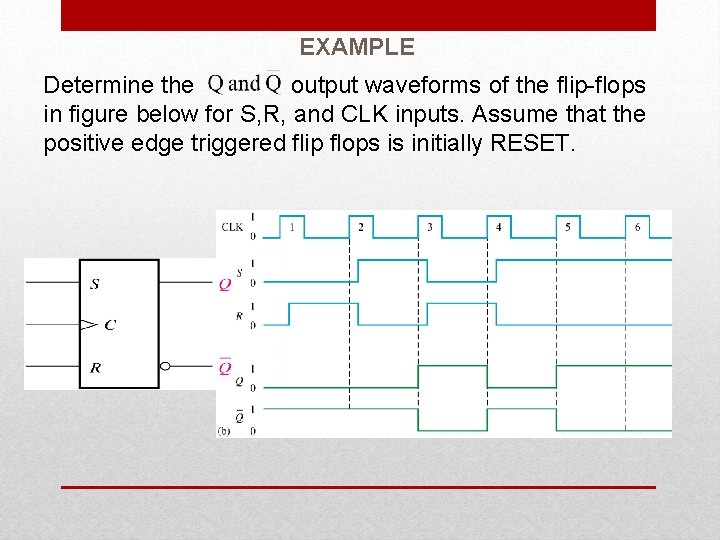

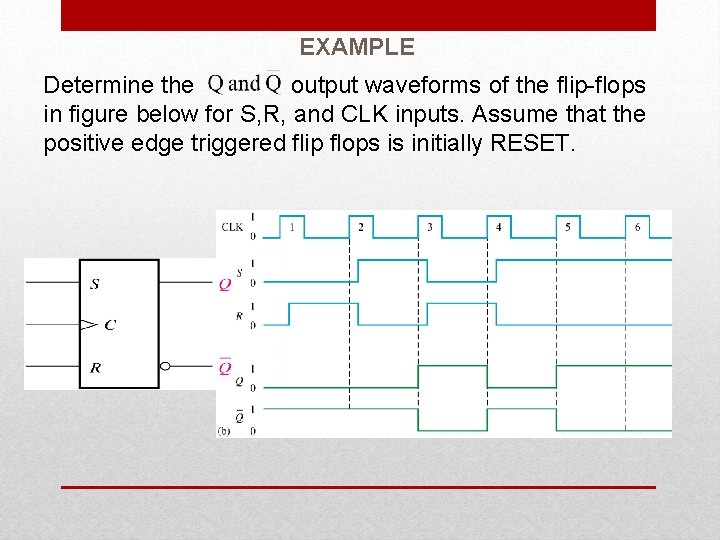

EXAMPLE Determine the output waveforms of the flip-flops in figure below for S, R, and CLK inputs. Assume that the positive edge triggered flip flops is initially RESET.

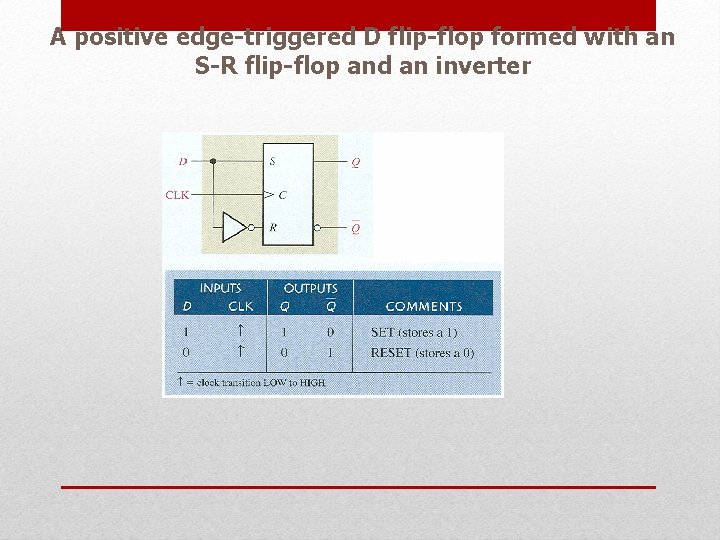

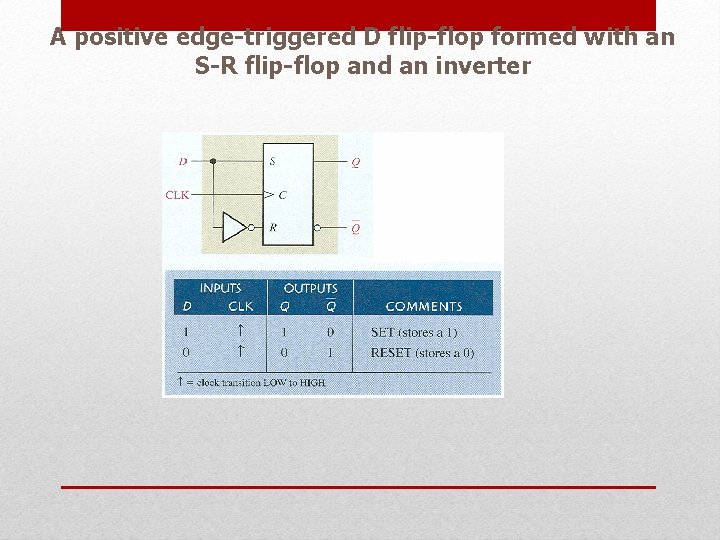

A positive edge-triggered D flip-flop formed with an S-R flip-flop and an inverter

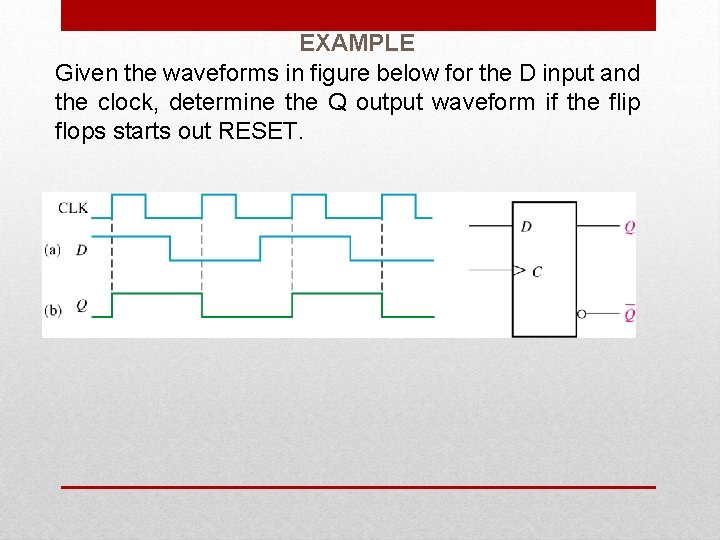

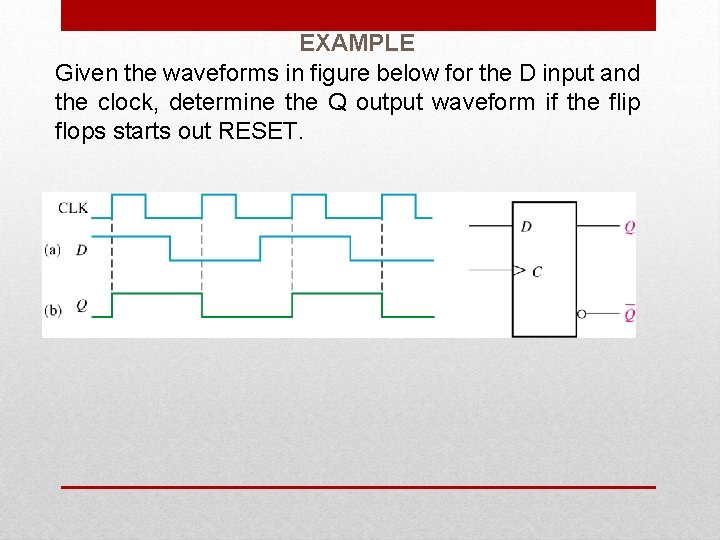

EXAMPLE Given the waveforms in figure below for the D input and the clock, determine the Q output waveform if the flip flops starts out RESET.

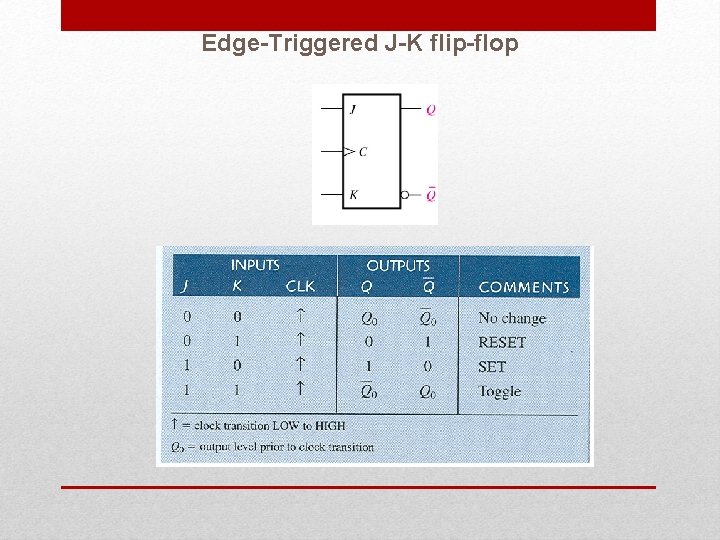

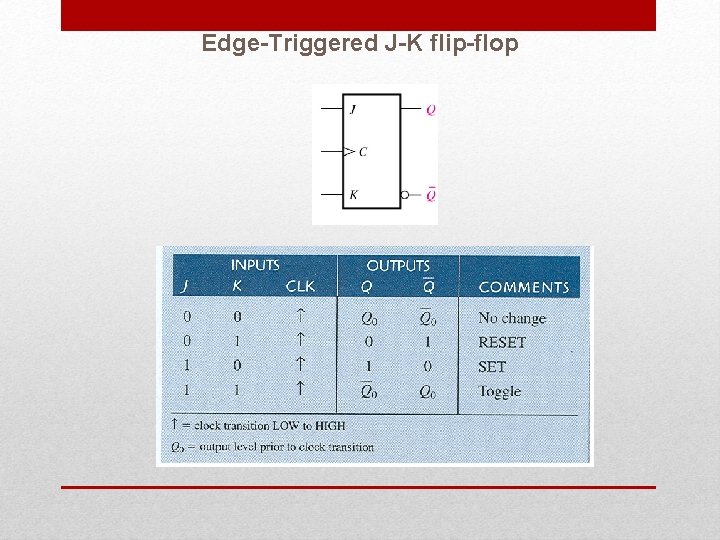

Edge-Triggered J-K flip-flop

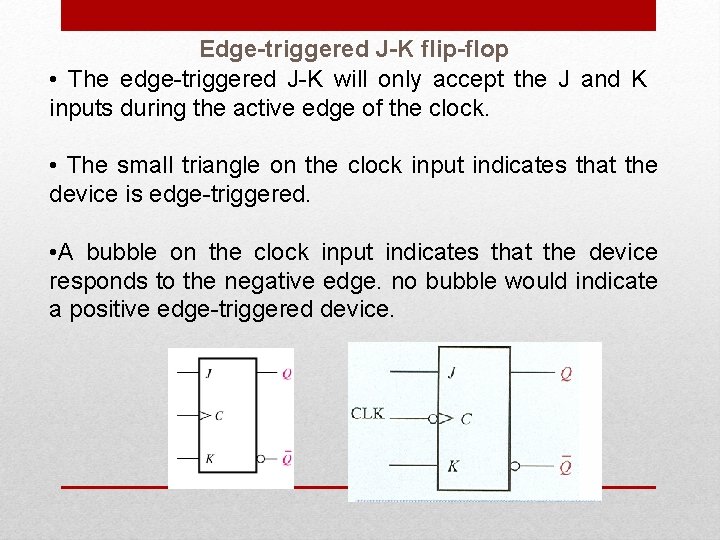

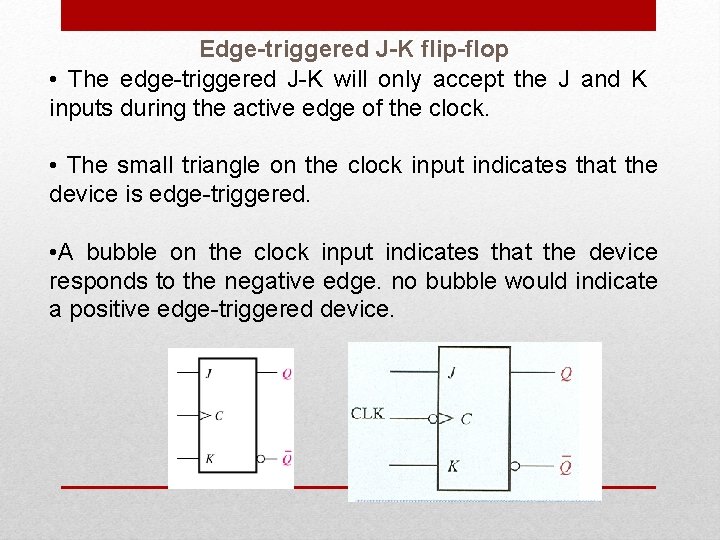

Edge-triggered J-K flip-flop • The edge-triggered J-K will only accept the J and K inputs during the active edge of the clock. • The small triangle on the clock input indicates that the device is edge-triggered. • A bubble on the clock input indicates that the device responds to the negative edge. no bubble would indicate a positive edge-triggered device.

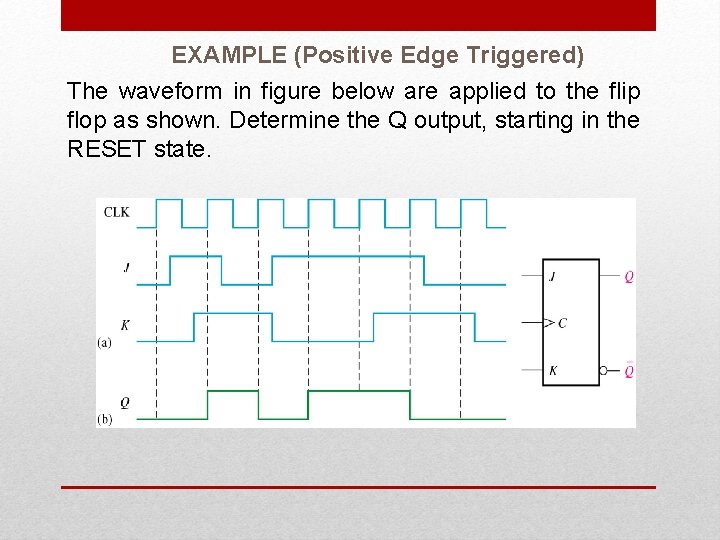

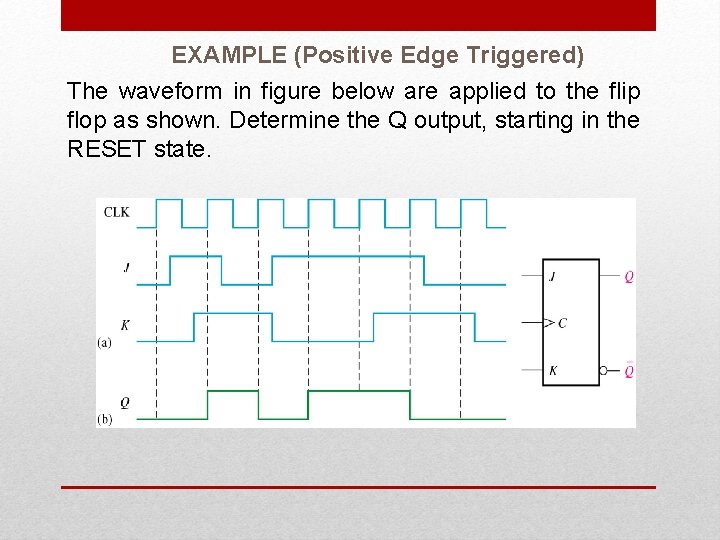

EXAMPLE (Positive Edge Triggered) The waveform in figure below are applied to the flip flop as shown. Determine the Q output, starting in the RESET state.

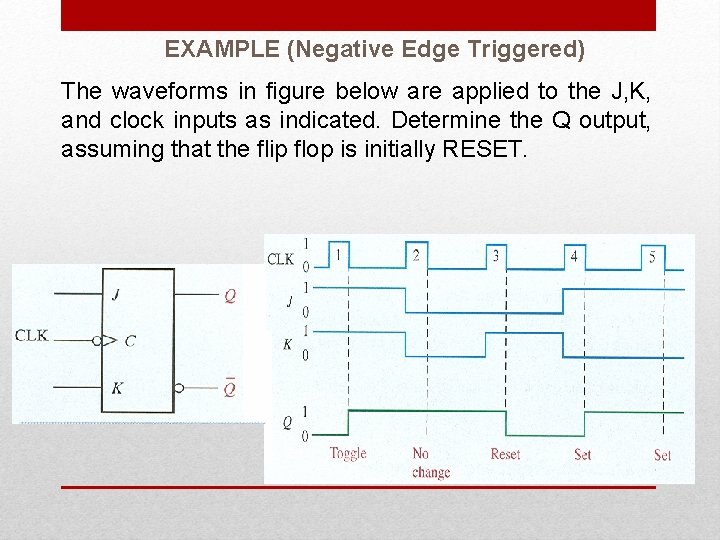

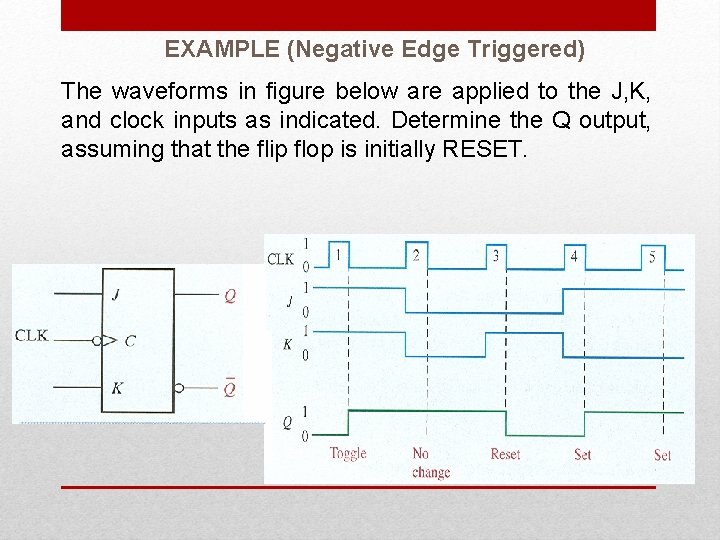

EXAMPLE (Negative Edge Triggered) The waveforms in figure below are applied to the J, K, and clock inputs as indicated. Determine the Q output, assuming that the flip flop is initially RESET.