Chapter 6 Test Compression EE 141 VLSI Test

![Taxonomy of various response compaction schemes Compaction Schemes I Space Zero-aliasing Compactor [Chakrabarty 1998] Taxonomy of various response compaction schemes Compaction Schemes I Space Zero-aliasing Compactor [Chakrabarty 1998]](https://slidetodoc.com/presentation_image/597daaa39d0e21500565e171353e3e54/image-36.jpg)

- Slides: 70

Chapter 6 Test Compression EE 141 VLSI Test Principles and Architectures 1 Ch. 6 - Test Compression –

What is this chapter about? Introduce the basic concepts of test data compression q Focus on stimulus compression and response compaction techniques q Present and discuss commercial tools on test compression q EE 141 VLSI Test Principles and Architectures 2 Ch. 6 - Test Compression –

Test Compression q Introduction q Test Stimulus Compression q Test Response Compaction q Industry Practices q Concluding Remarks EE 141 VLSI Test Principles and Architectures 3 Ch. 6 - Test Compression –

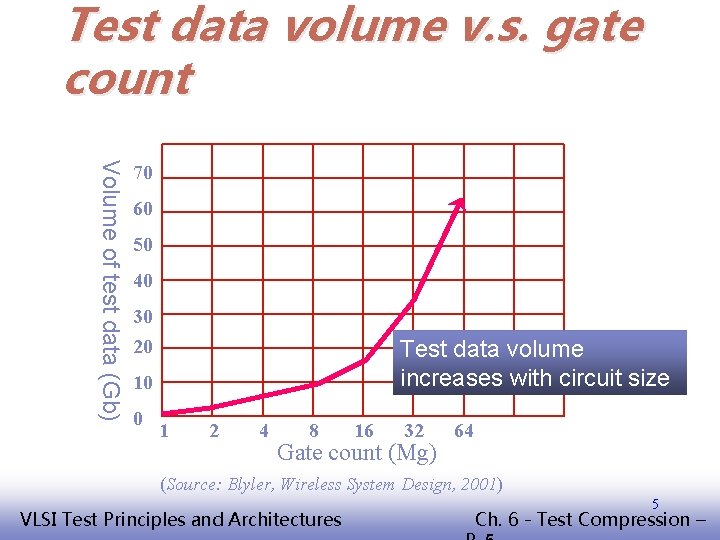

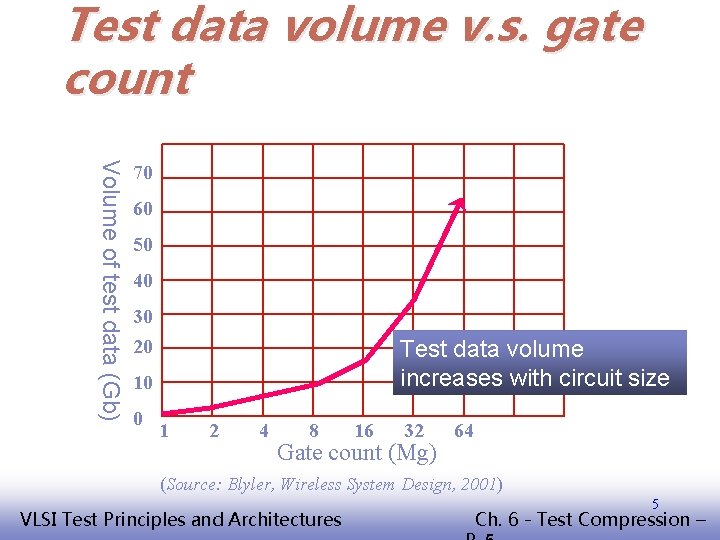

Introduction q Why do we need test compression? § Test data volume § Test time § Test pins q Why can we compress test data? § Deterministic test vector has “don’t care” (X’s) EE 141 VLSI Test Principles and Architectures 4 Ch. 6 - Test Compression –

Test data volume v. s. gate count Volume of test data (Gb) 70 60 50 40 30 20 Test data volume increases with circuit size 10 0 1 2 4 8 16 32 Gate count (Mg) 64 (Source: Blyler, Wireless System Design, 2001) EE 141 VLSI Test Principles and Architectures 5 Ch. 6 - Test Compression –

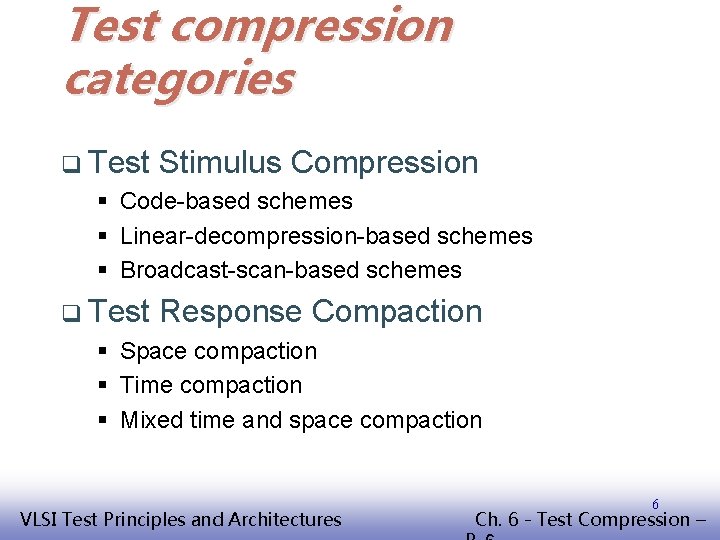

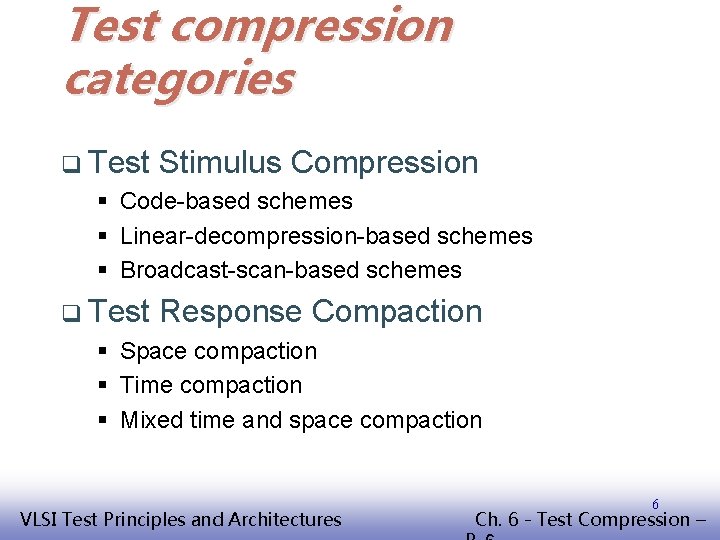

Test compression categories q Test Stimulus Compression § Code-based schemes § Linear-decompression-based schemes § Broadcast-scan-based schemes q Test Response Compaction § Space compaction § Time compaction § Mixed time and space compaction EE 141 VLSI Test Principles and Architectures 6 Ch. 6 - Test Compression –

Architecture for test compression Response Stimulus EE 141 VLSI Test Principles and Architectures Core Compactor Low-Cost ATE Decompressor Compressed Stimulus Compacted Response 7 Ch. 6 - Test Compression –

Test stimulus compression Code-based schemes q Linear-decompression-based schemes q Broadcast-scan-based schemes q EE 141 VLSI Test Principles and Architectures 8 Ch. 6 - Test Compression –

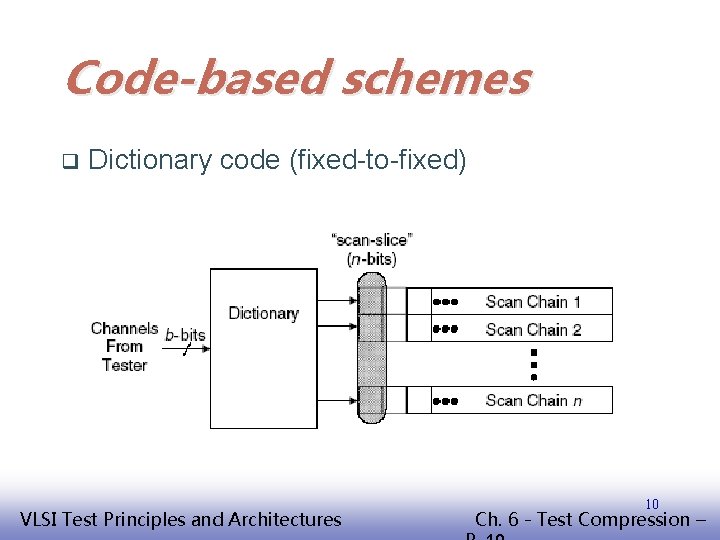

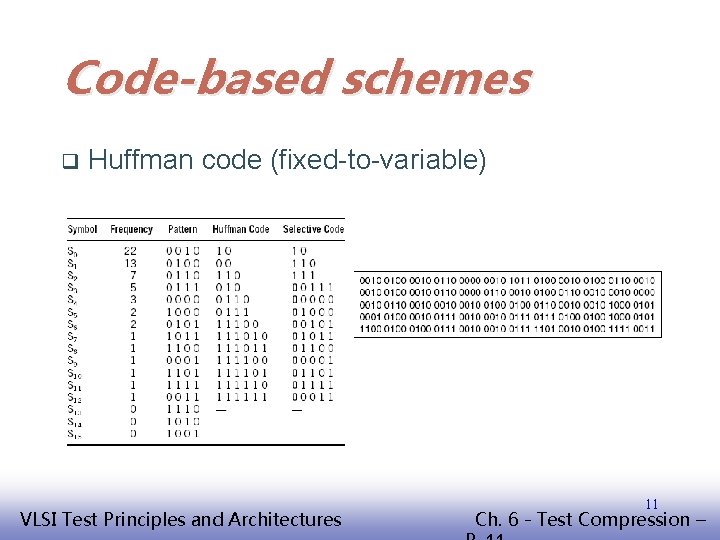

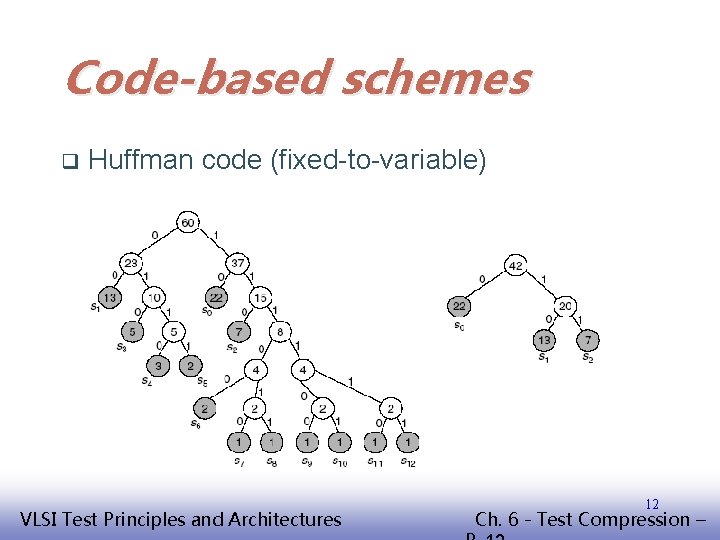

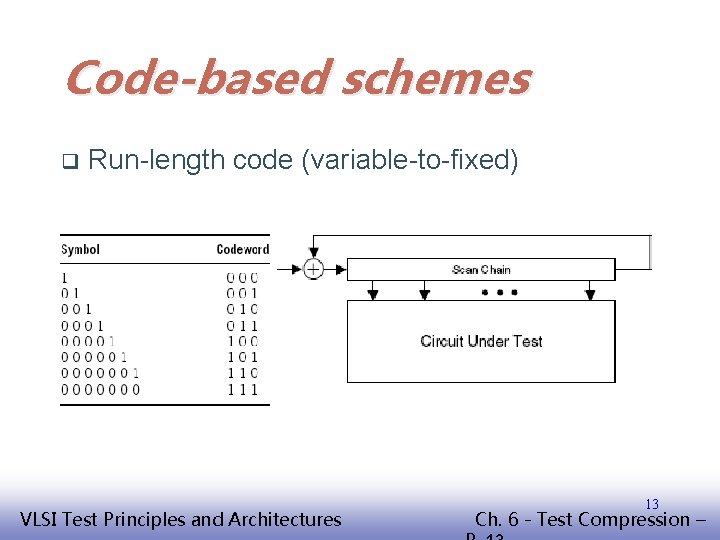

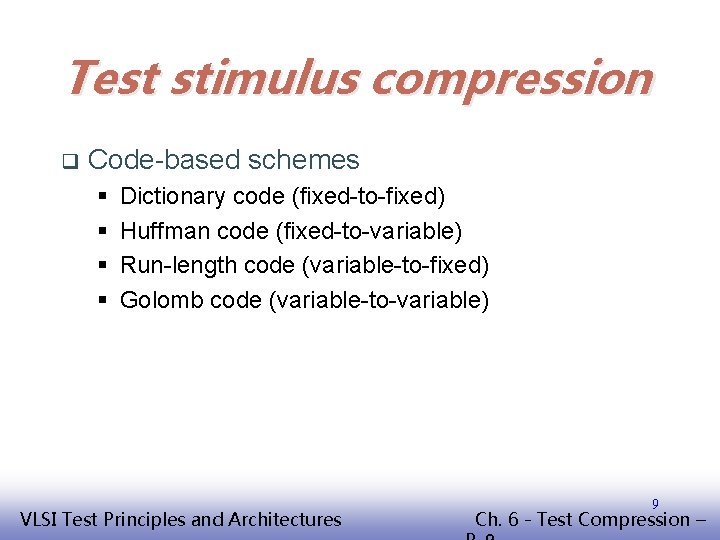

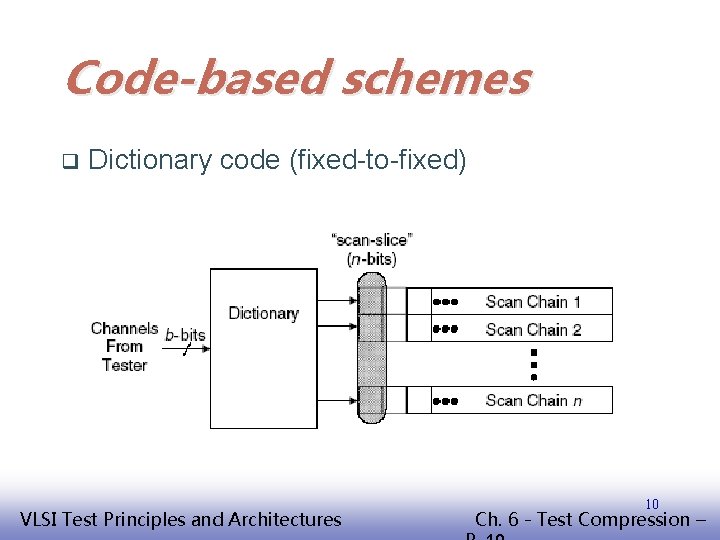

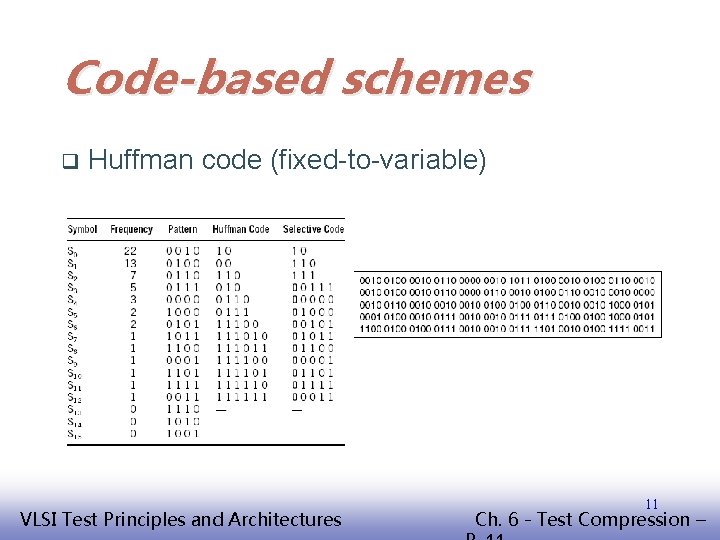

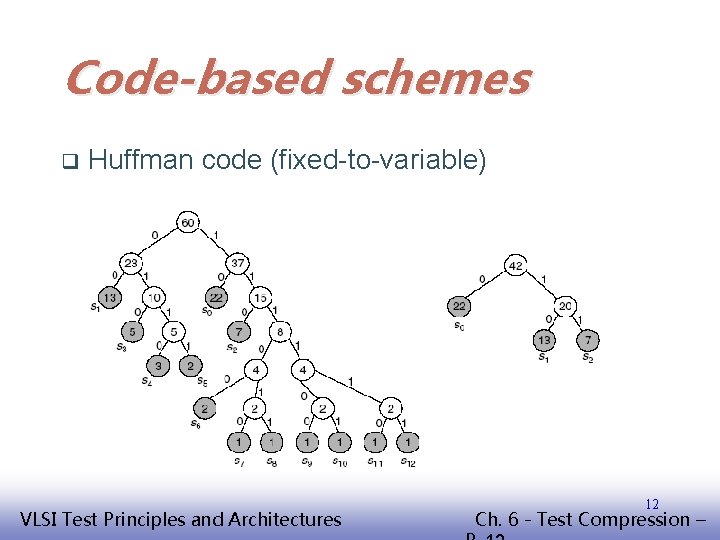

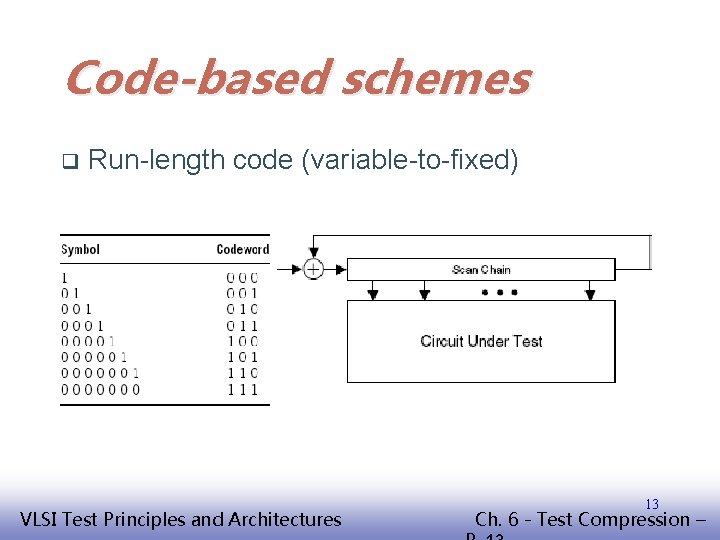

Test stimulus compression q Code-based schemes § § Dictionary code (fixed-to-fixed) Huffman code (fixed-to-variable) Run-length code (variable-to-fixed) Golomb code (variable-to-variable) EE 141 VLSI Test Principles and Architectures 9 Ch. 6 - Test Compression –

Code-based schemes q Dictionary code (fixed-to-fixed) EE 141 VLSI Test Principles and Architectures 10 Ch. 6 - Test Compression –

Code-based schemes q Huffman code (fixed-to-variable) EE 141 VLSI Test Principles and Architectures 11 Ch. 6 - Test Compression –

Code-based schemes q Huffman code (fixed-to-variable) EE 141 VLSI Test Principles and Architectures 12 Ch. 6 - Test Compression –

Code-based schemes q Run-length code (variable-to-fixed) EE 141 VLSI Test Principles and Architectures 13 Ch. 6 - Test Compression –

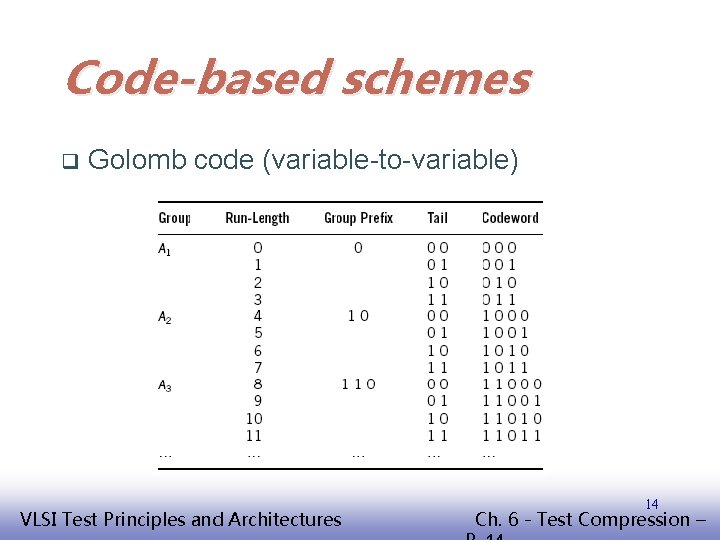

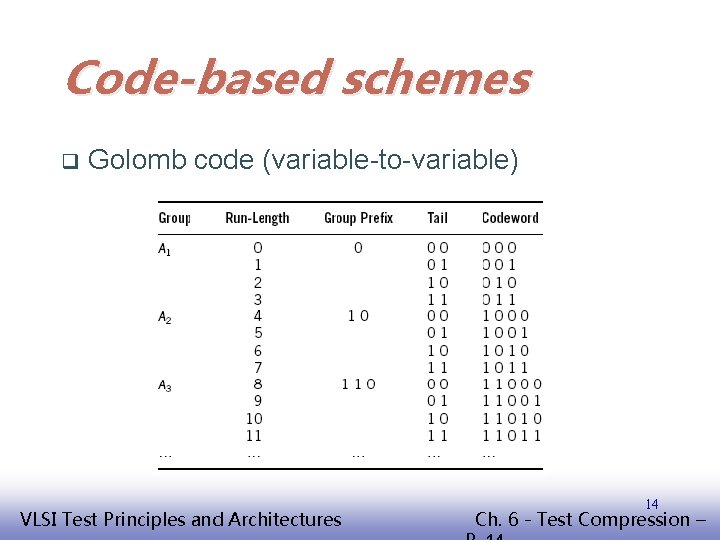

Code-based schemes q Golomb code (variable-to-variable) EE 141 VLSI Test Principles and Architectures 14 Ch. 6 - Test Compression –

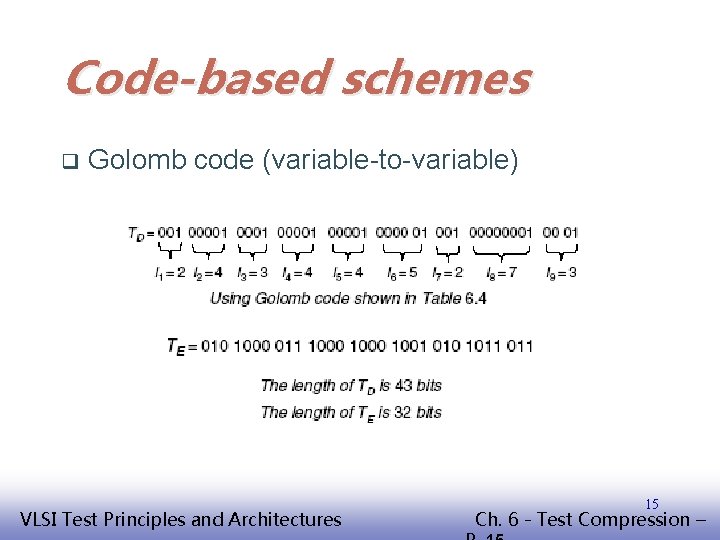

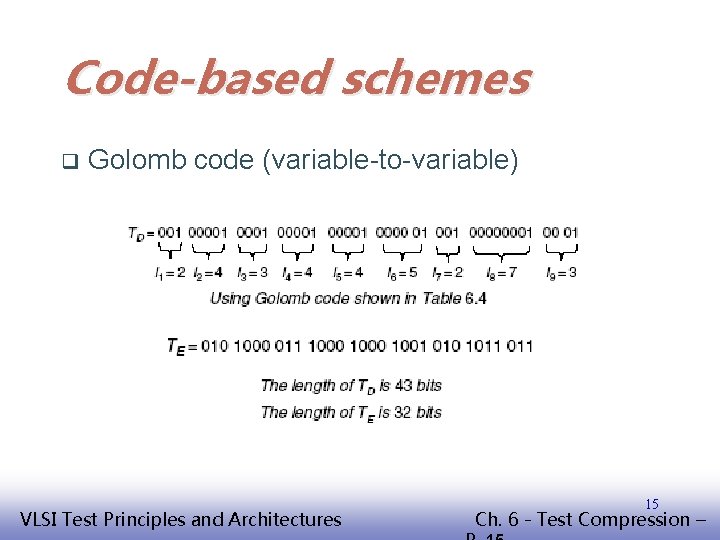

Code-based schemes q Golomb code (variable-to-variable) EE 141 VLSI Test Principles and Architectures 15 Ch. 6 - Test Compression –

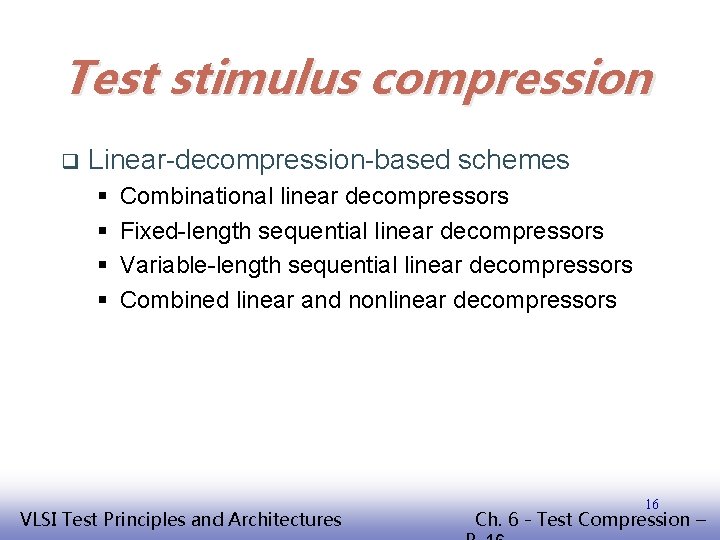

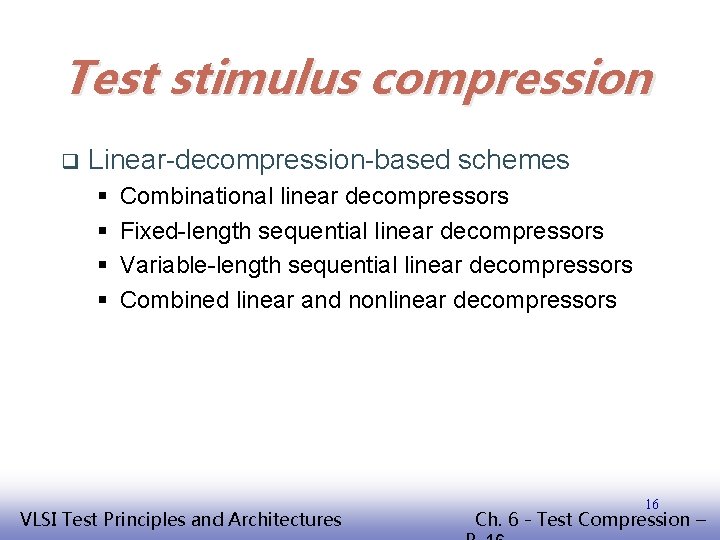

Test stimulus compression q Linear-decompression-based schemes § § Combinational linear decompressors Fixed-length sequential linear decompressors Variable-length sequential linear decompressors Combined linear and nonlinear decompressors EE 141 VLSI Test Principles and Architectures 16 Ch. 6 - Test Compression –

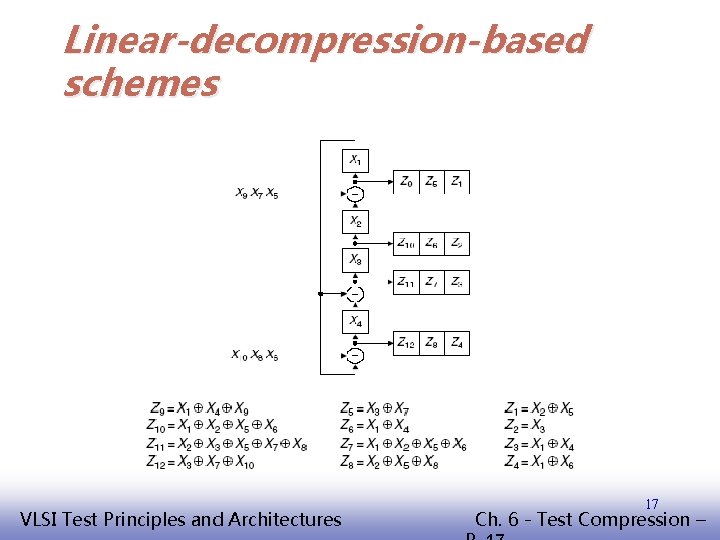

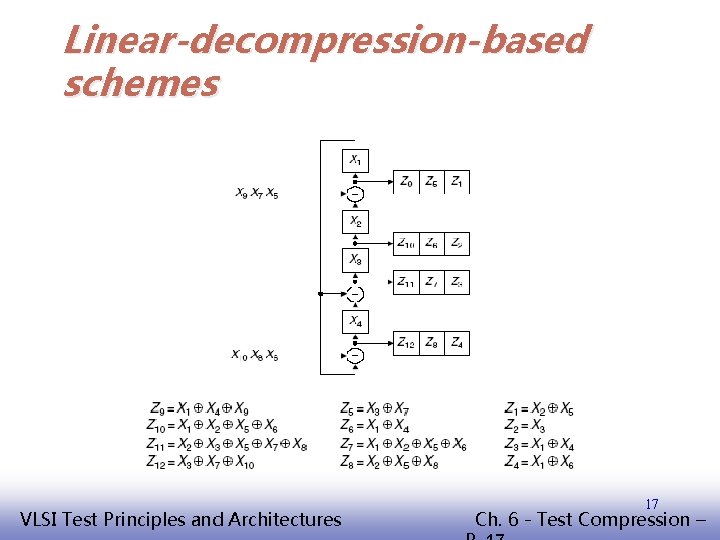

Linear-decompression-based schemes EE 141 VLSI Test Principles and Architectures 17 Ch. 6 - Test Compression –

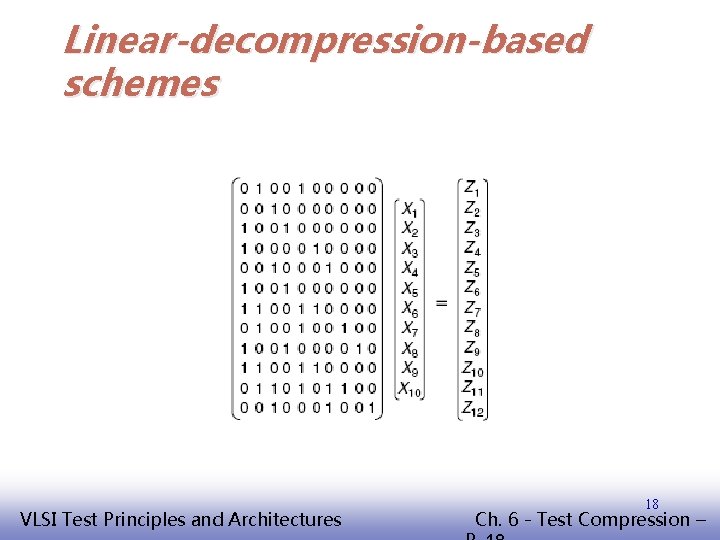

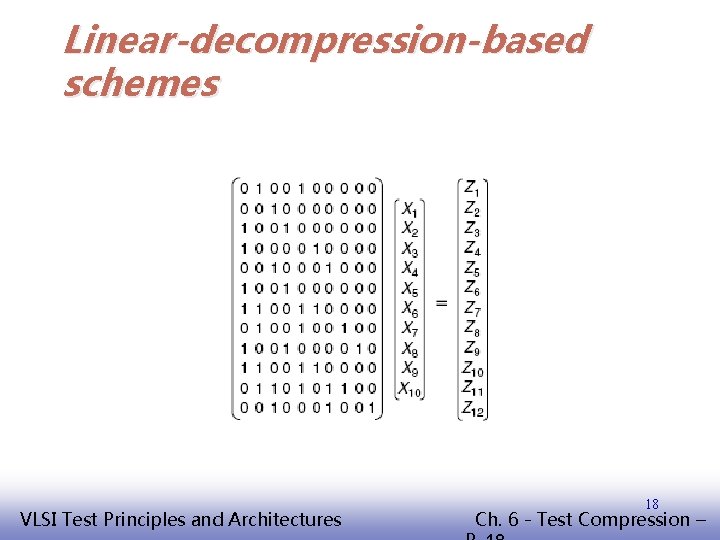

Linear-decompression-based schemes EE 141 VLSI Test Principles and Architectures 18 Ch. 6 - Test Compression –

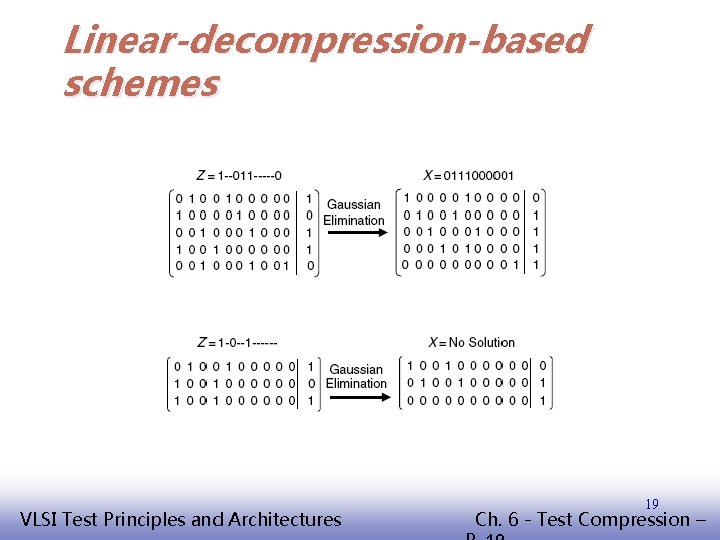

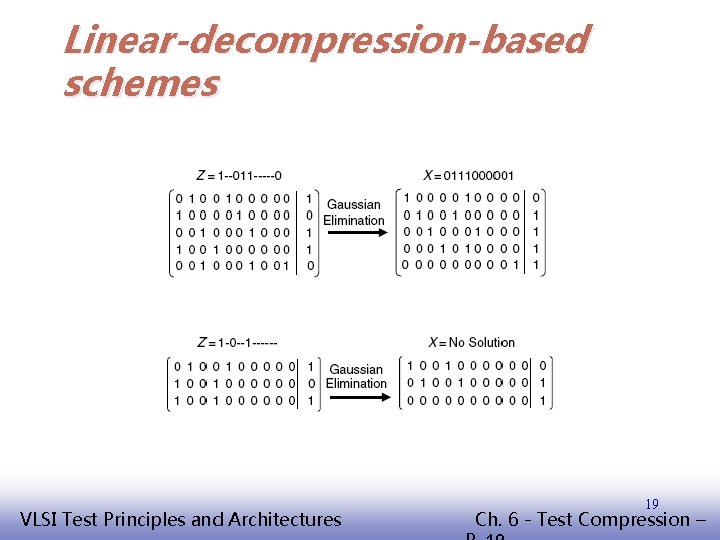

Linear-decompression-based schemes EE 141 VLSI Test Principles and Architectures 19 Ch. 6 - Test Compression –

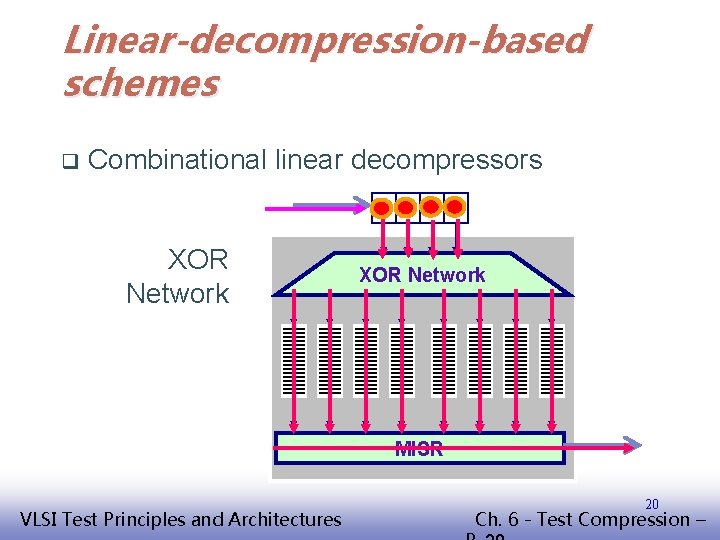

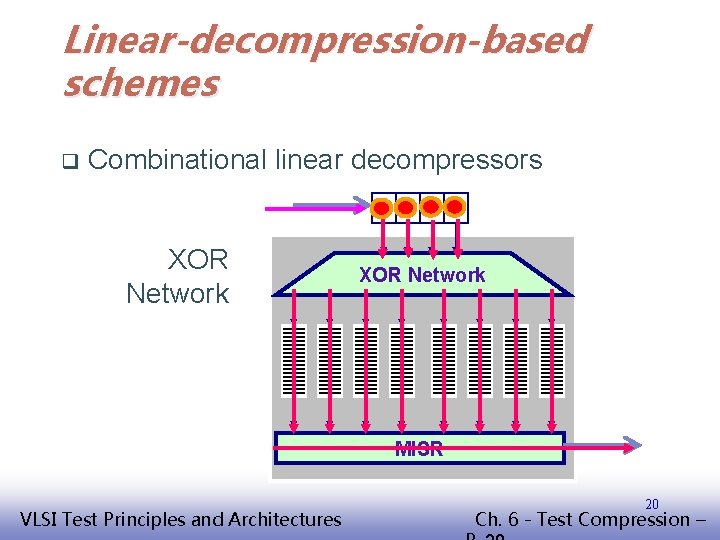

Linear-decompression-based schemes q Combinational linear decompressors XOR Network MISR EE 141 VLSI Test Principles and Architectures 20 Ch. 6 - Test Compression –

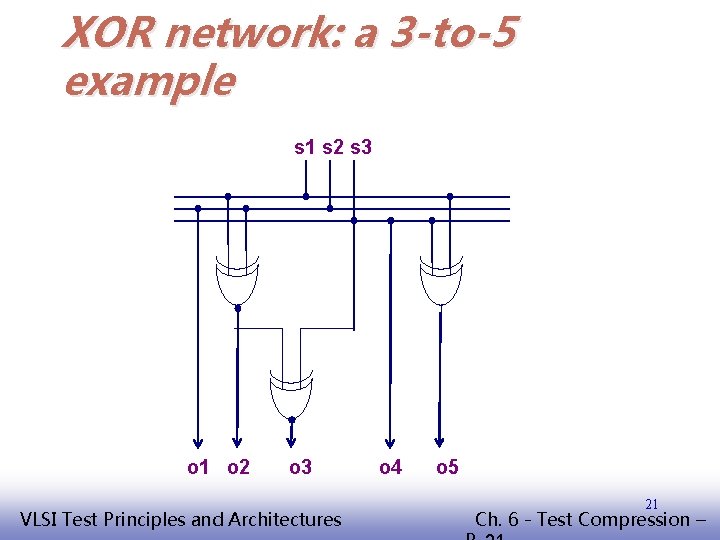

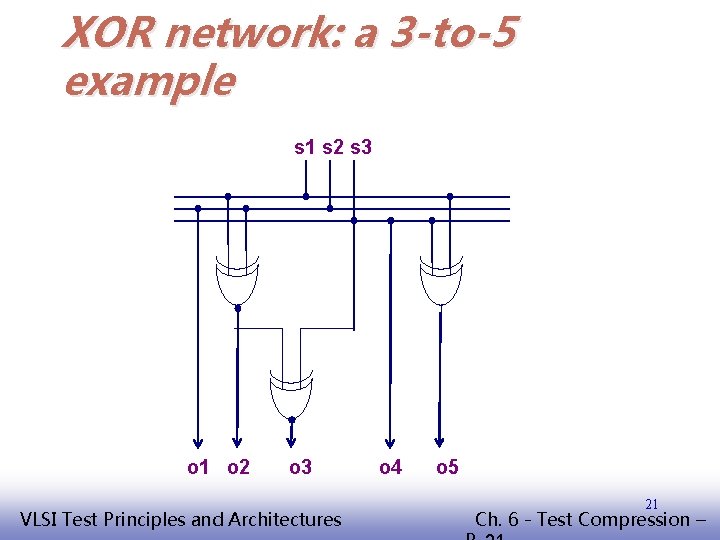

XOR network: a 3 -to-5 example s 1 s 2 s 3 o 1 o 2 o 3 EE 141 VLSI Test Principles and Architectures o 4 o 5 21 Ch. 6 - Test Compression –

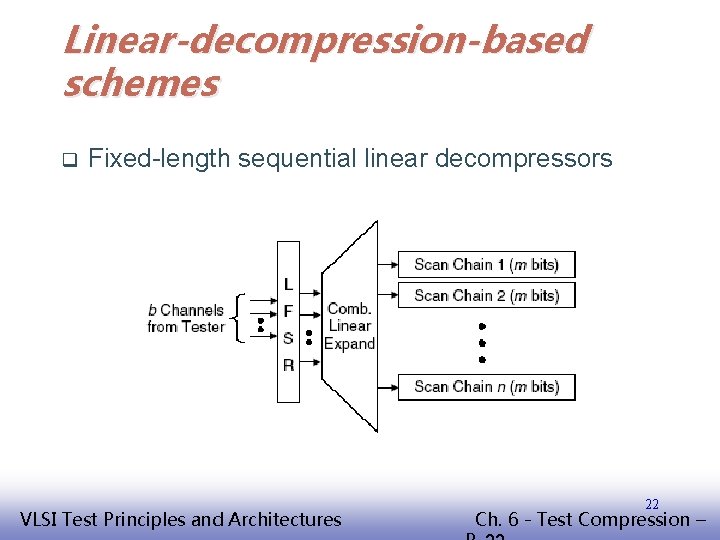

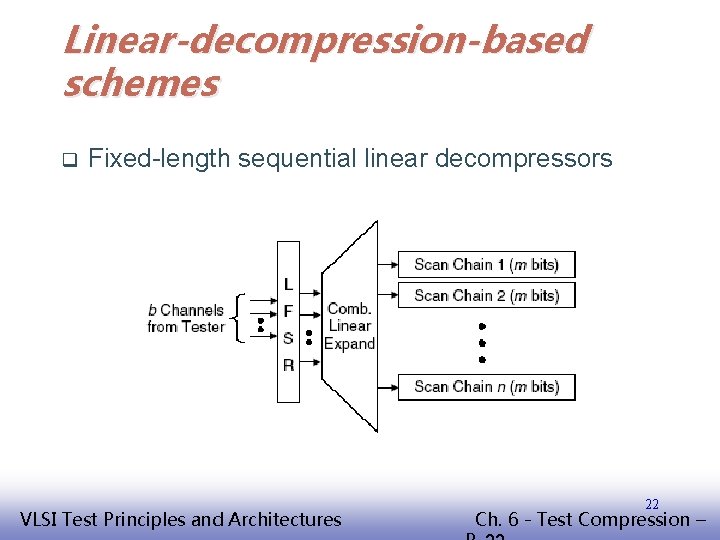

Linear-decompression-based schemes q Fixed-length sequential linear decompressors EE 141 VLSI Test Principles and Architectures 22 Ch. 6 - Test Compression –

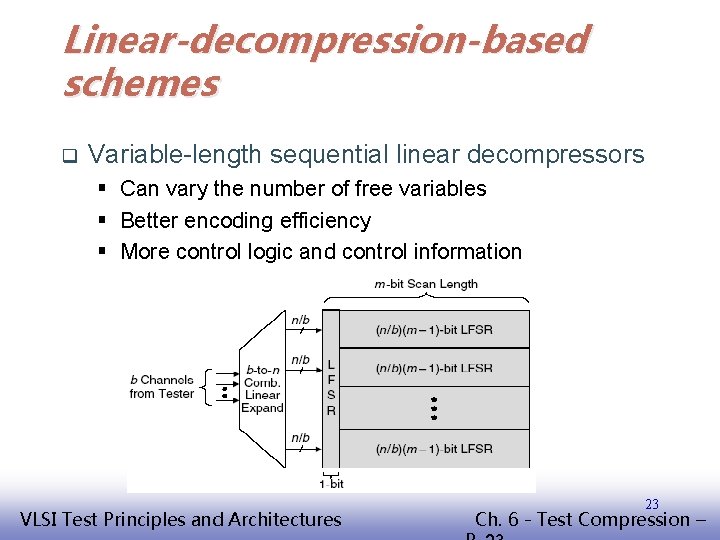

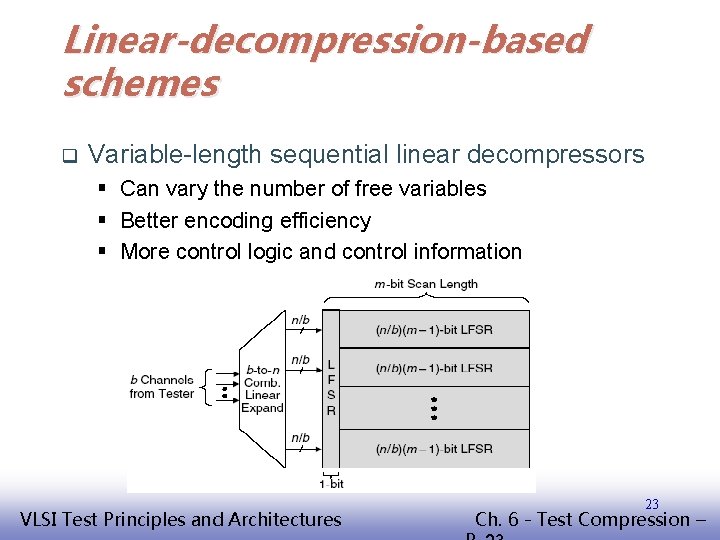

Linear-decompression-based schemes q Variable-length sequential linear decompressors § Can vary the number of free variables § Better encoding efficiency § More control logic and control information EE 141 VLSI Test Principles and Architectures 23 Ch. 6 - Test Compression –

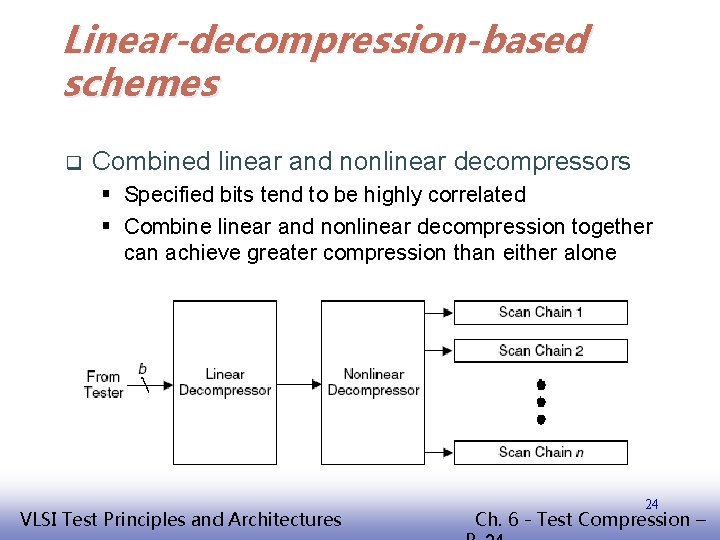

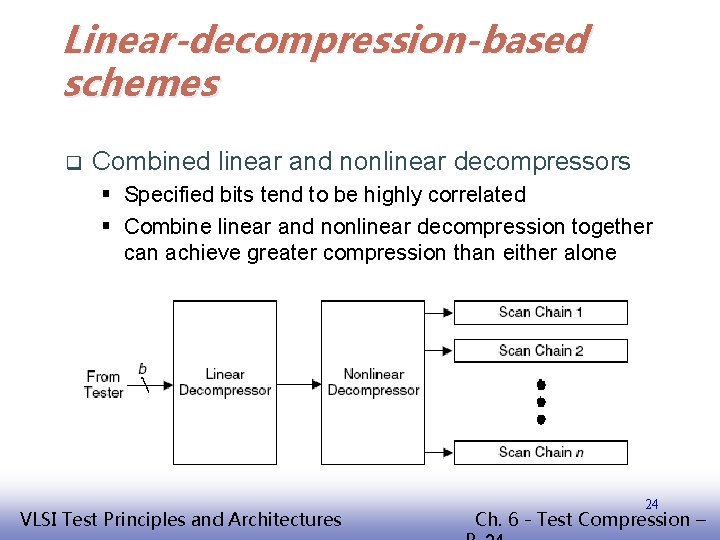

Linear-decompression-based schemes q Combined linear and nonlinear decompressors § Specified bits tend to be highly correlated § Combine linear and nonlinear decompression together can achieve greater compression than either alone EE 141 VLSI Test Principles and Architectures 24 Ch. 6 - Test Compression –

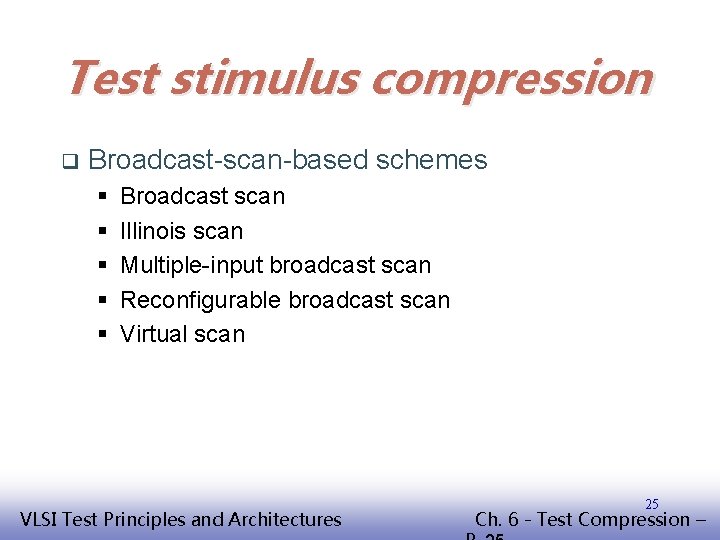

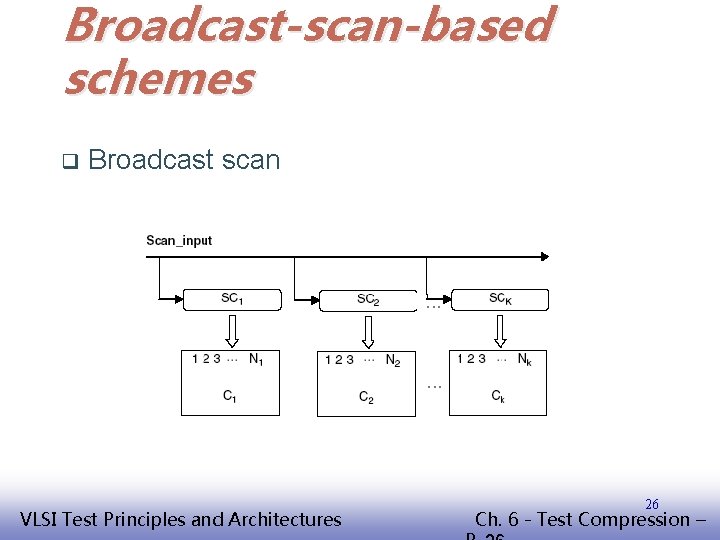

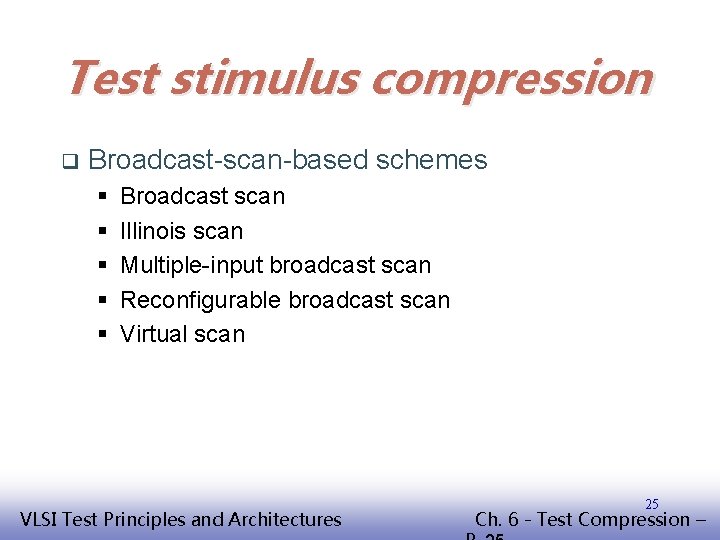

Test stimulus compression q Broadcast-scan-based schemes § § § Broadcast scan Illinois scan Multiple-input broadcast scan Reconfigurable broadcast scan Virtual scan EE 141 VLSI Test Principles and Architectures 25 Ch. 6 - Test Compression –

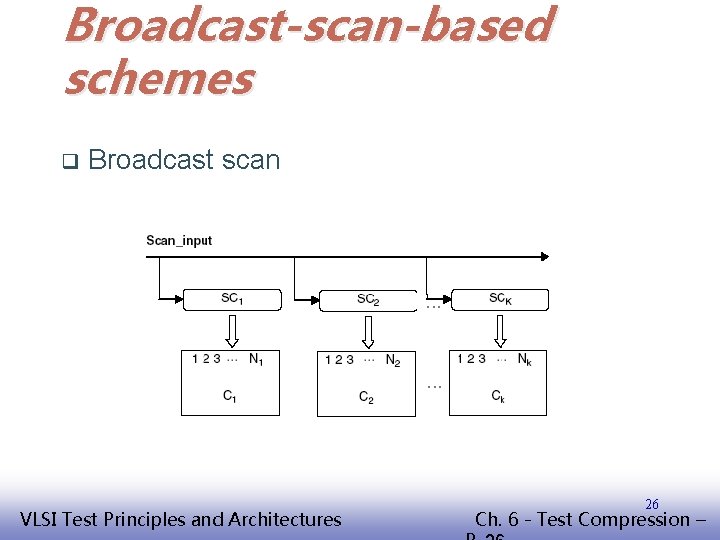

Broadcast-scan-based schemes q Broadcast scan EE 141 VLSI Test Principles and Architectures 26 Ch. 6 - Test Compression –

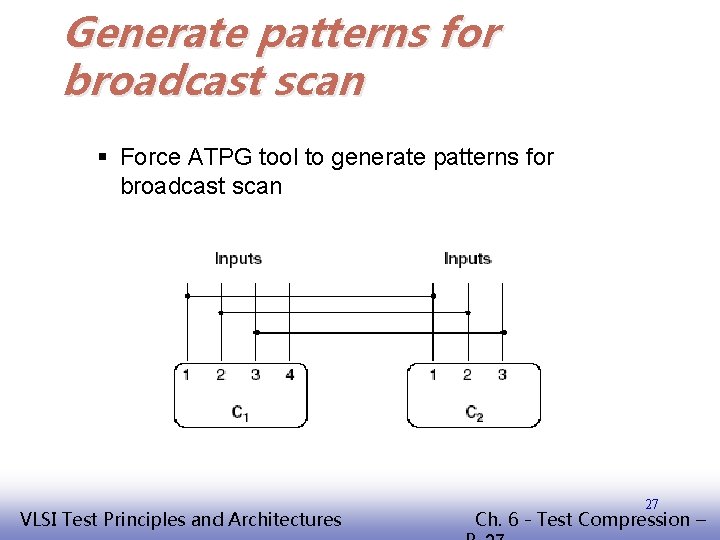

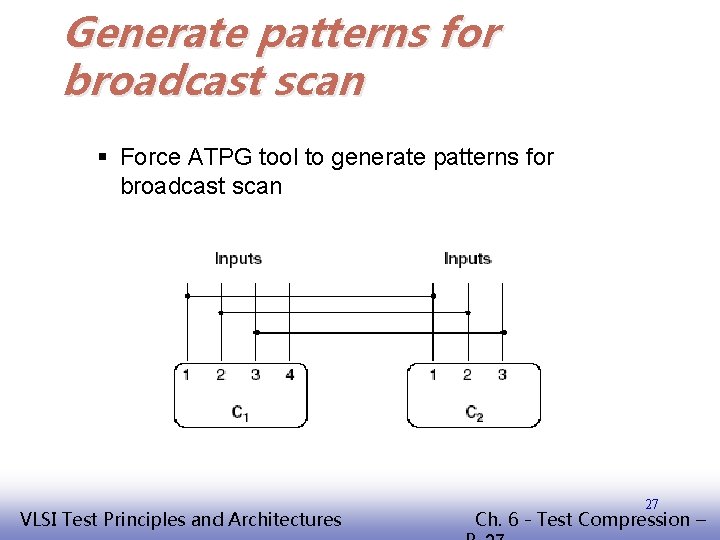

Generate patterns for broadcast scan § Force ATPG tool to generate patterns for broadcast scan EE 141 VLSI Test Principles and Architectures 27 Ch. 6 - Test Compression –

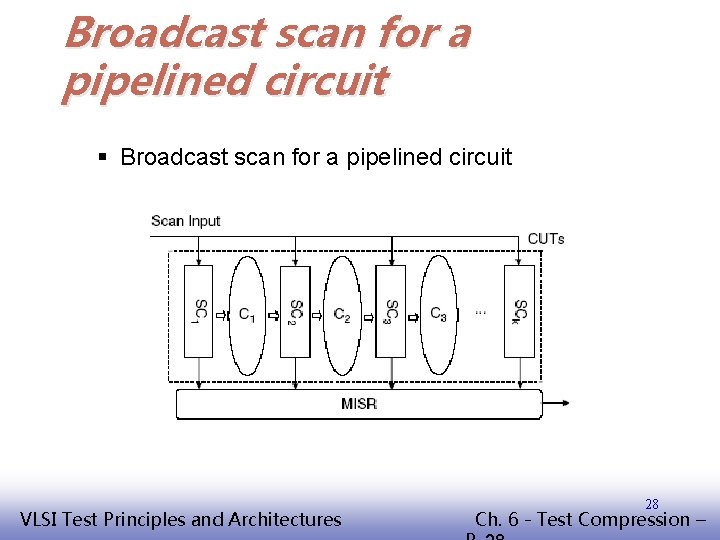

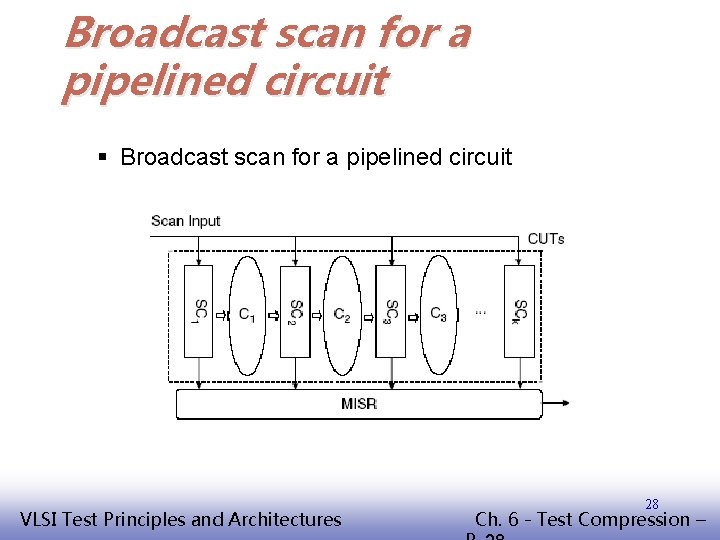

Broadcast scan for a pipelined circuit § Broadcast scan for a pipelined circuit EE 141 VLSI Test Principles and Architectures 28 Ch. 6 - Test Compression –

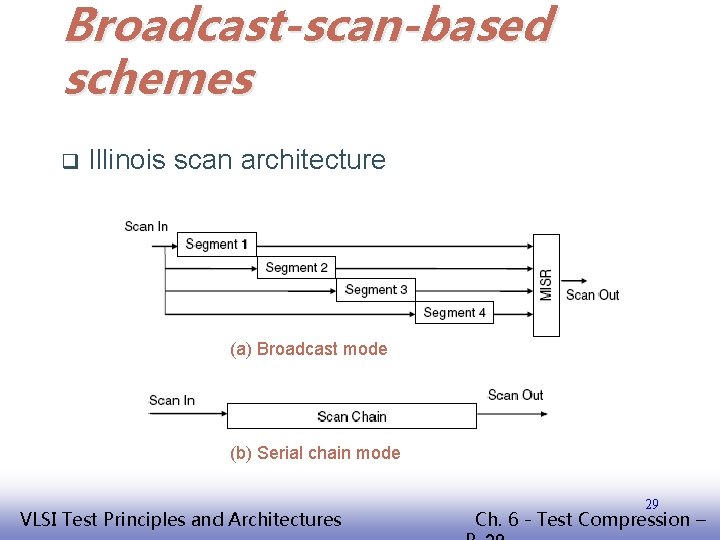

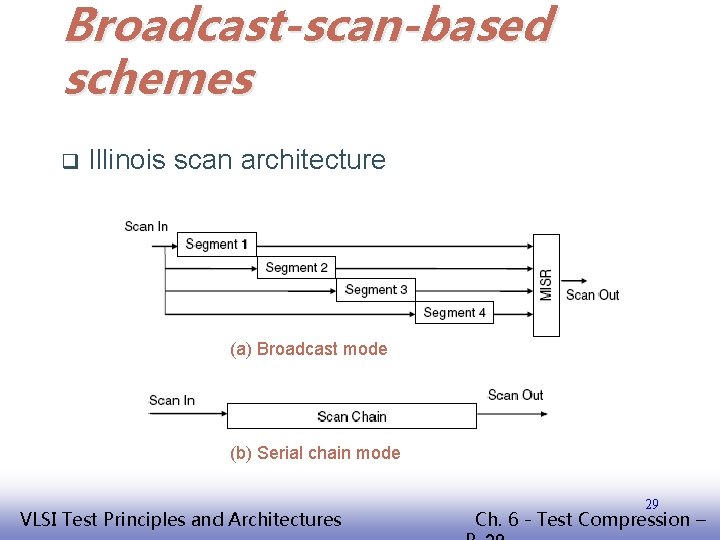

Broadcast-scan-based schemes q Illinois scan architecture (a) Broadcast mode (b) Serial chain mode EE 141 VLSI Test Principles and Architectures 29 Ch. 6 - Test Compression –

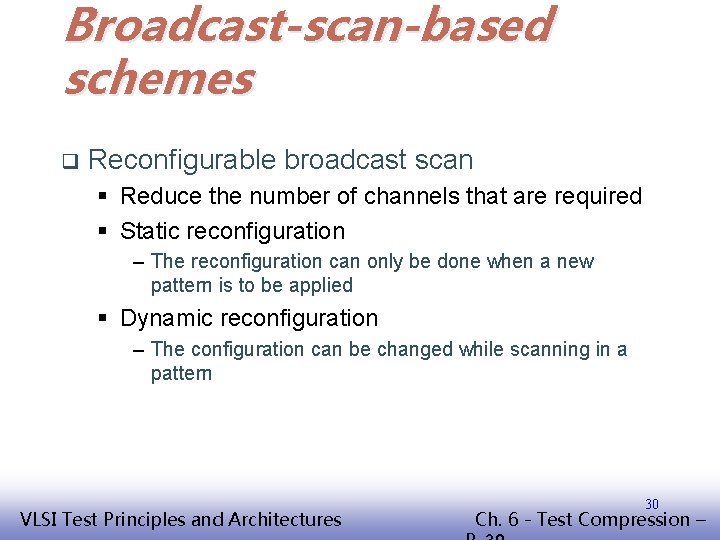

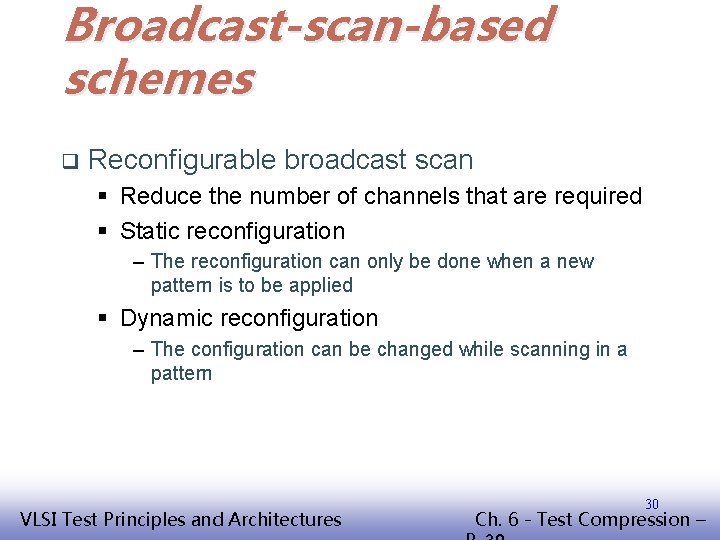

Broadcast-scan-based schemes q Reconfigurable broadcast scan § Reduce the number of channels that are required § Static reconfiguration – The reconfiguration can only be done when a new pattern is to be applied § Dynamic reconfiguration – The configuration can be changed while scanning in a pattern EE 141 VLSI Test Principles and Architectures 30 Ch. 6 - Test Compression –

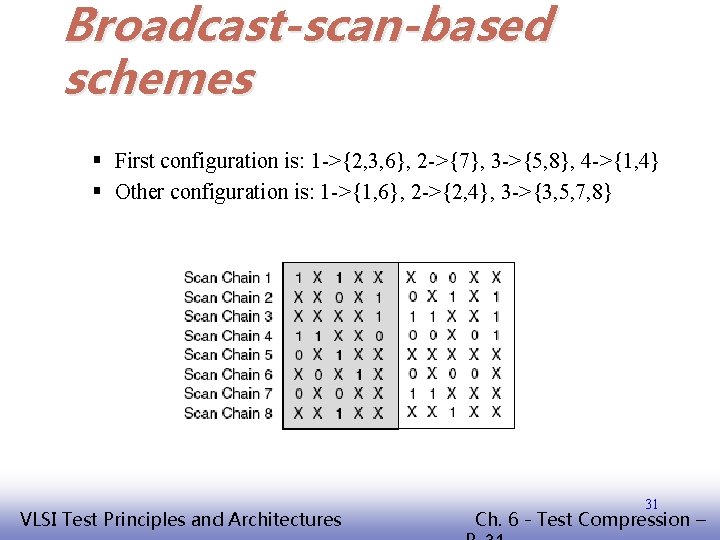

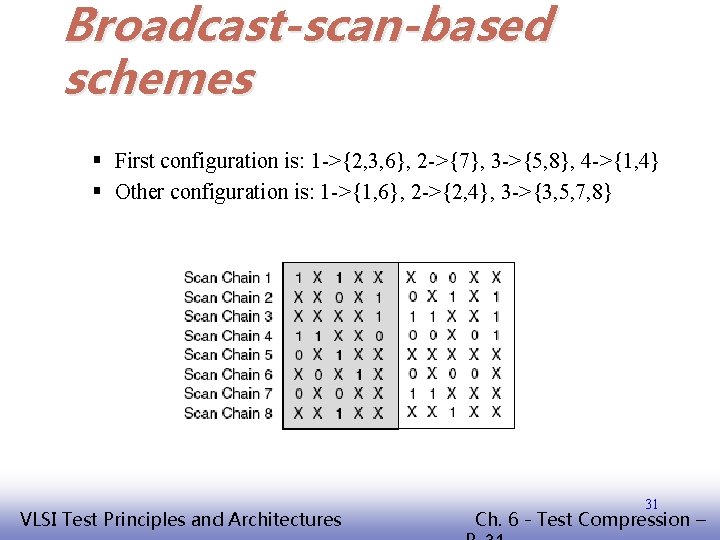

Broadcast-scan-based schemes § First configuration is: 1 ->{2, 3, 6}, 2 ->{7}, 3 ->{5, 8}, 4 ->{1, 4} § Other configuration is: 1 ->{1, 6}, 2 ->{2, 4}, 3 ->{3, 5, 7, 8} EE 141 VLSI Test Principles and Architectures 31 Ch. 6 - Test Compression –

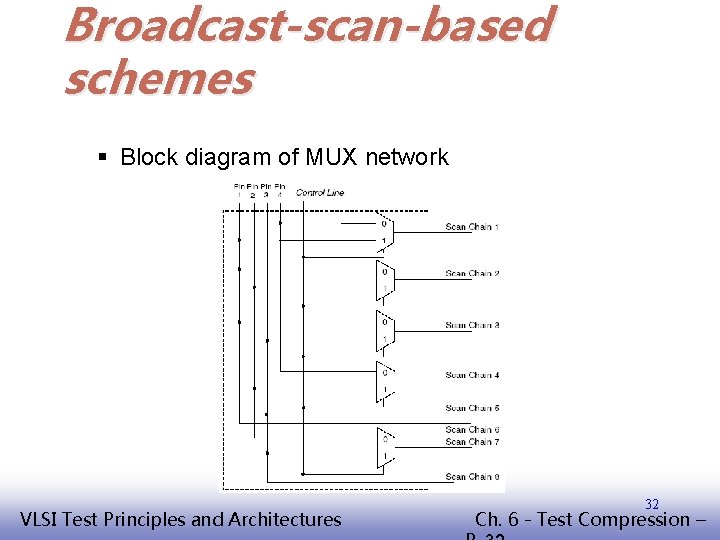

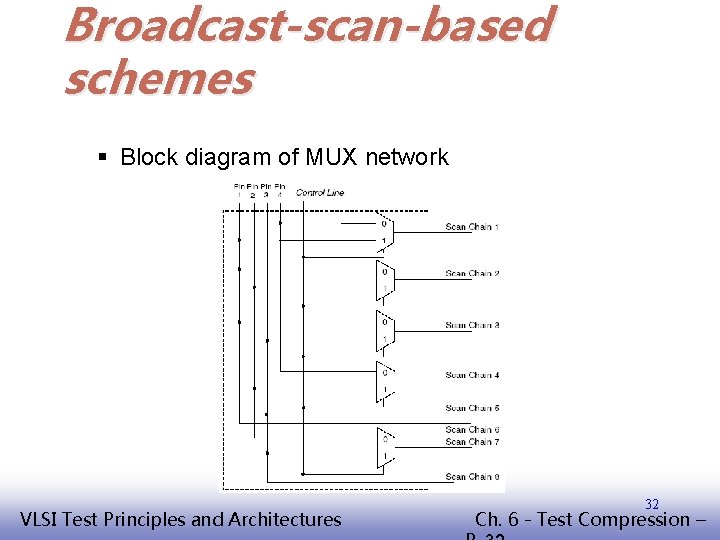

Broadcast-scan-based schemes § Block diagram of MUX network EE 141 VLSI Test Principles and Architectures 32 Ch. 6 - Test Compression –

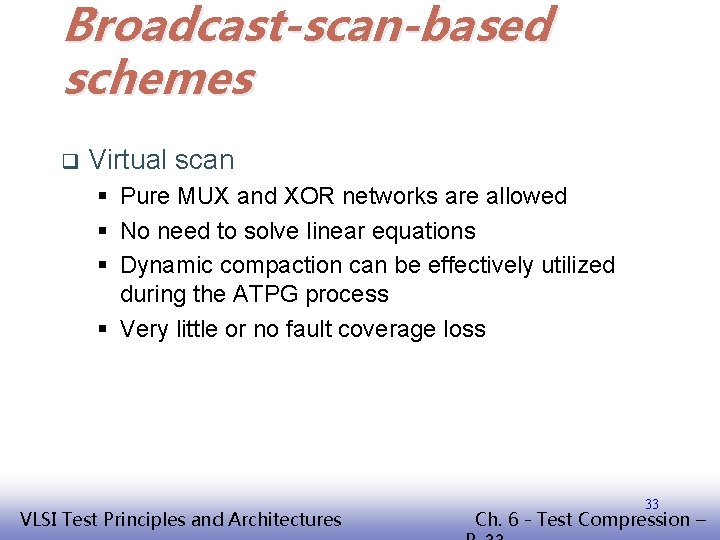

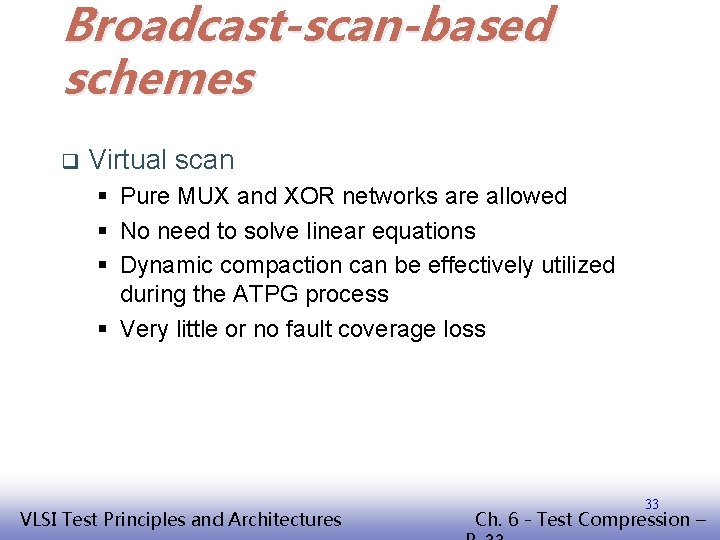

Broadcast-scan-based schemes q Virtual scan § Pure MUX and XOR networks are allowed § No need to solve linear equations § Dynamic compaction can be effectively utilized during the ATPG process § Very little or no fault coverage loss EE 141 VLSI Test Principles and Architectures 33 Ch. 6 - Test Compression –

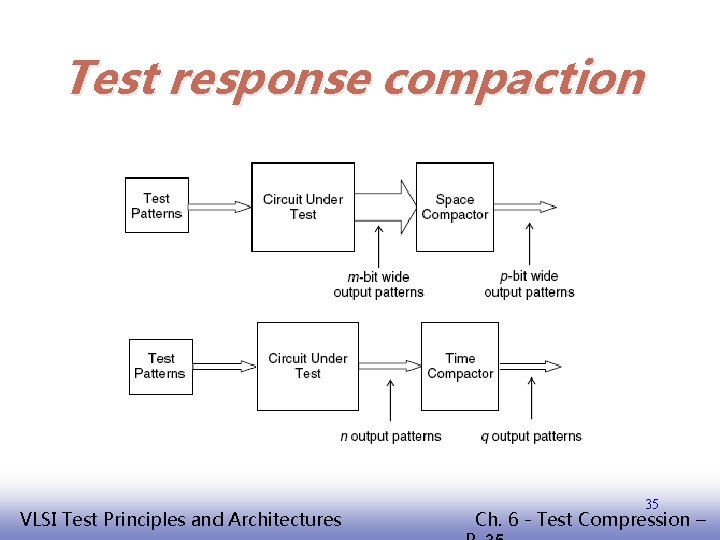

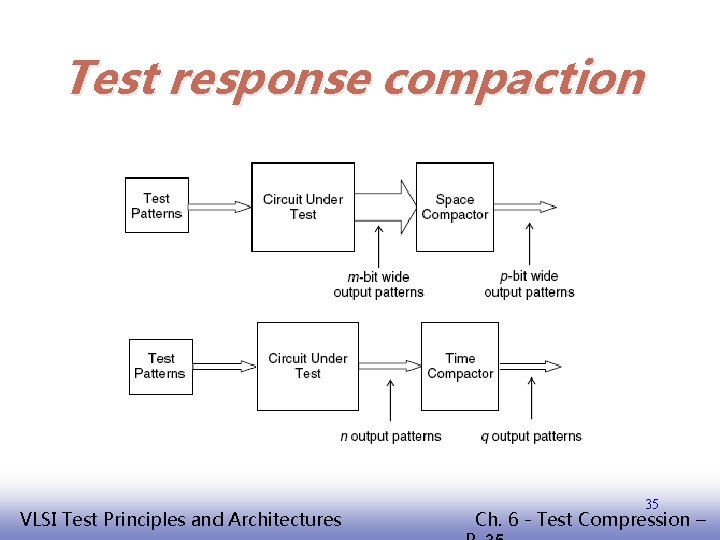

Test response compaction Space compaction q Time compaction q Mixed time and space compaction q EE 141 VLSI Test Principles and Architectures 34 Ch. 6 - Test Compression –

Test response compaction EE 141 VLSI Test Principles and Architectures 35 Ch. 6 - Test Compression –

![Taxonomy of various response compaction schemes Compaction Schemes I Space Zeroaliasing Compactor Chakrabarty 1998 Taxonomy of various response compaction schemes Compaction Schemes I Space Zero-aliasing Compactor [Chakrabarty 1998]](https://slidetodoc.com/presentation_image/597daaa39d0e21500565e171353e3e54/image-36.jpg)

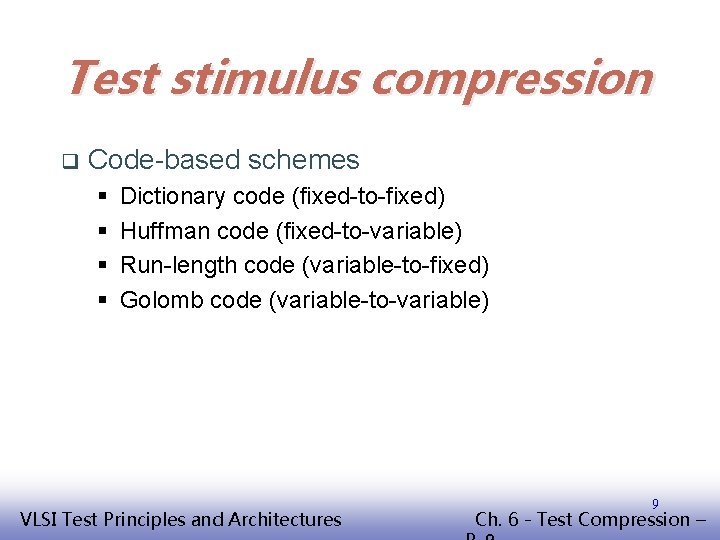

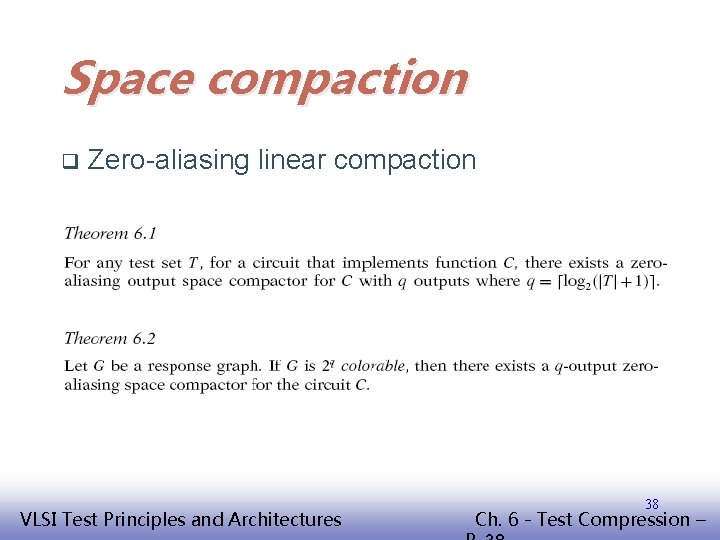

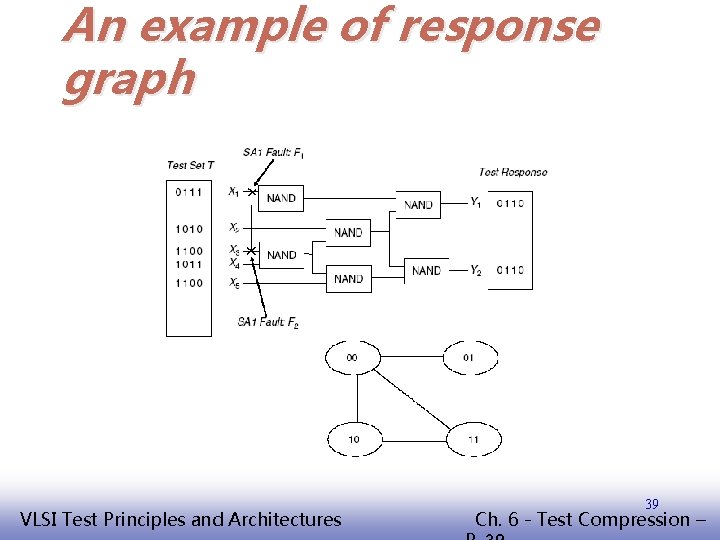

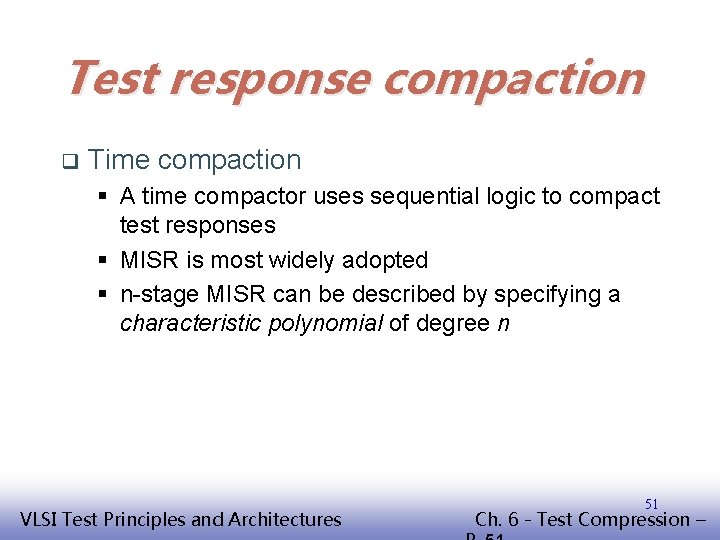

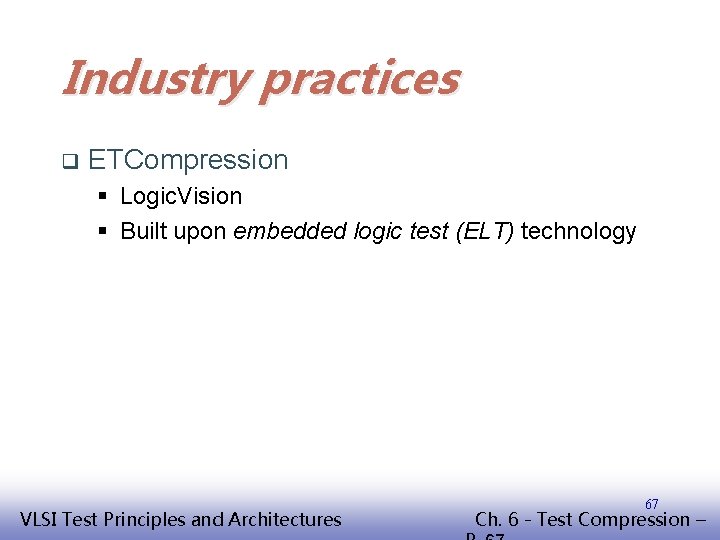

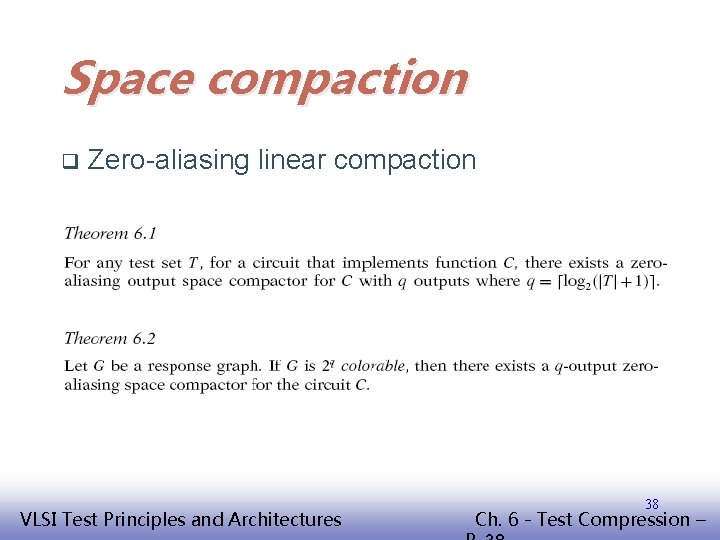

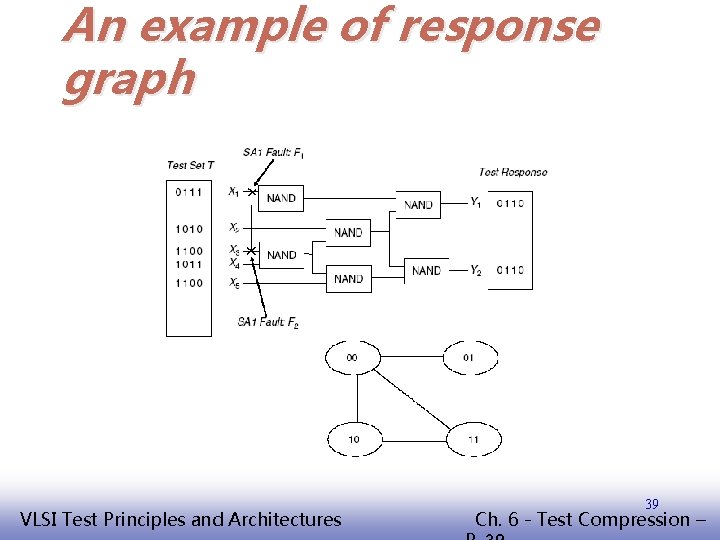

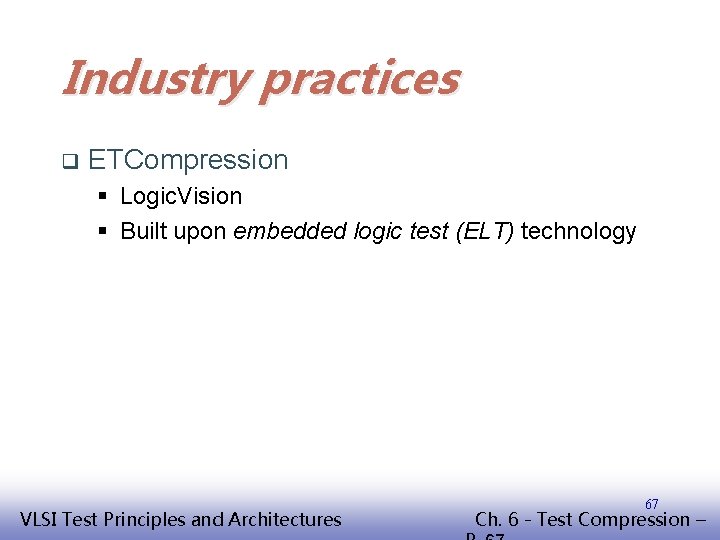

Taxonomy of various response compaction schemes Compaction Schemes I Space Zero-aliasing Compactor [Chakrabarty 1998] [Pouya 1998] Parity Tree [Karpovsky 1987] Enhanced Parity Tree [Sinanoglu 2003] X-Compact [Mitra 2004] q-Compactor [Han 2003] Convolutional Compactor [Rajski 2005] II Time CFS III CFI Linearity OPMISR [Barnhart 2002] Block Compactor [Wang 2003] i-Compact [Patel 2003] Compactor for SA [Wohl 2001] Scalable Selector [Wohl 2004] EE 141 VLSI Test Principles and Architectures Nonlinearity 36 Ch. 6 - Test Compression –

Test response compaction q Space compaction § § § Zero-aliasing linear compaction X-compact X-blocking X-masking X-impact EE 141 VLSI Test Principles and Architectures 37 Ch. 6 - Test Compression –

Space compaction q Zero-aliasing linear compaction EE 141 VLSI Test Principles and Architectures 38 Ch. 6 - Test Compression –

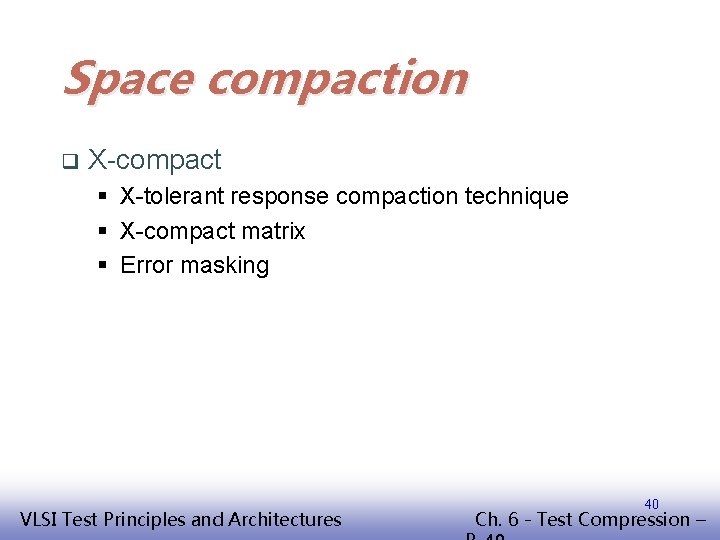

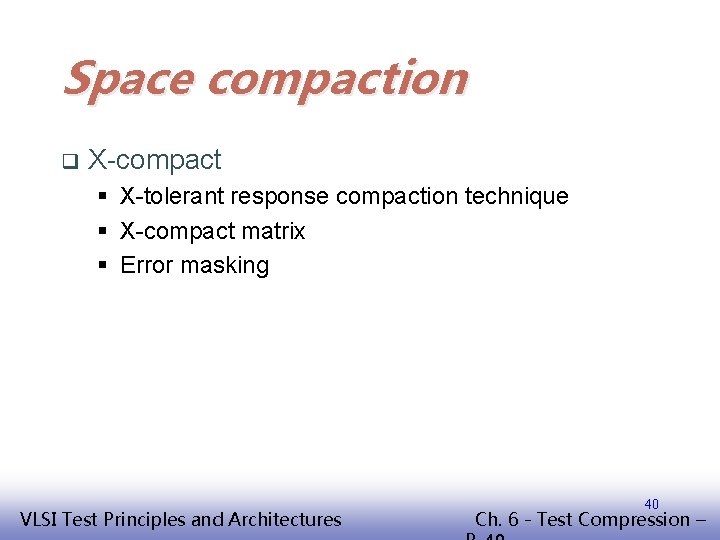

An example of response graph EE 141 VLSI Test Principles and Architectures 39 Ch. 6 - Test Compression –

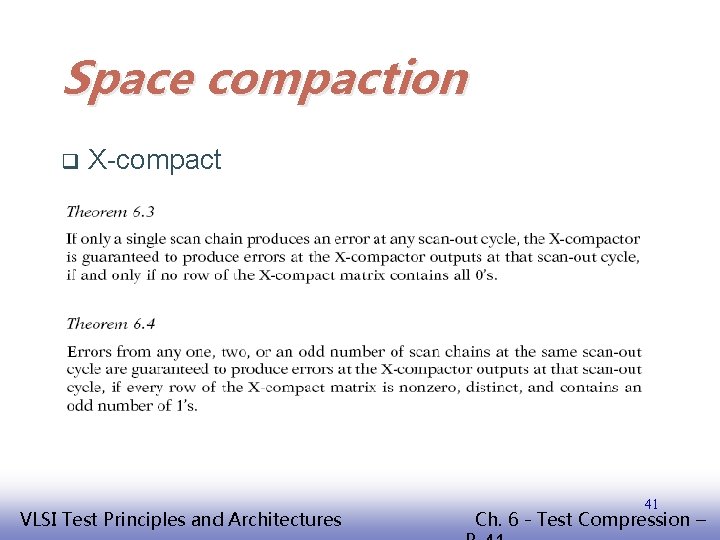

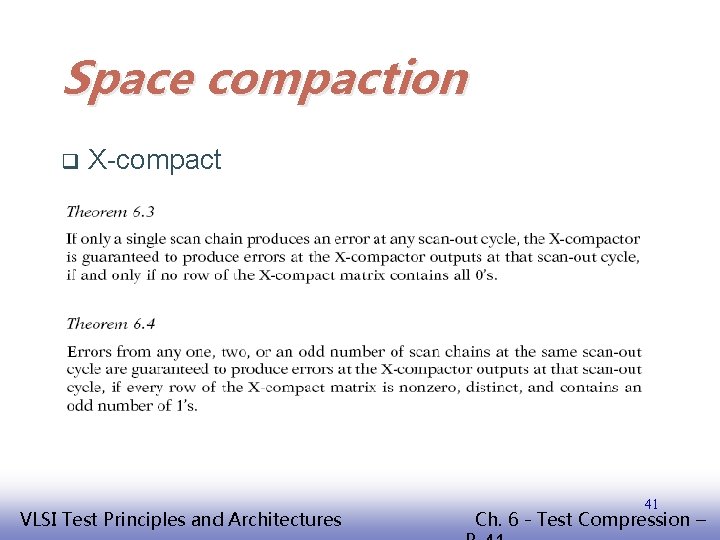

Space compaction q X-compact § X-tolerant response compaction technique § X-compact matrix § Error masking EE 141 VLSI Test Principles and Architectures 40 Ch. 6 - Test Compression –

Space compaction q X-compact EE 141 VLSI Test Principles and Architectures 41 Ch. 6 - Test Compression –

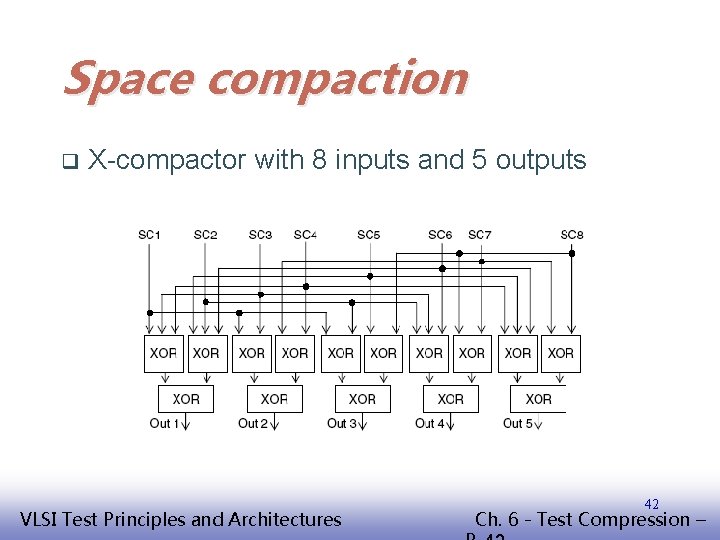

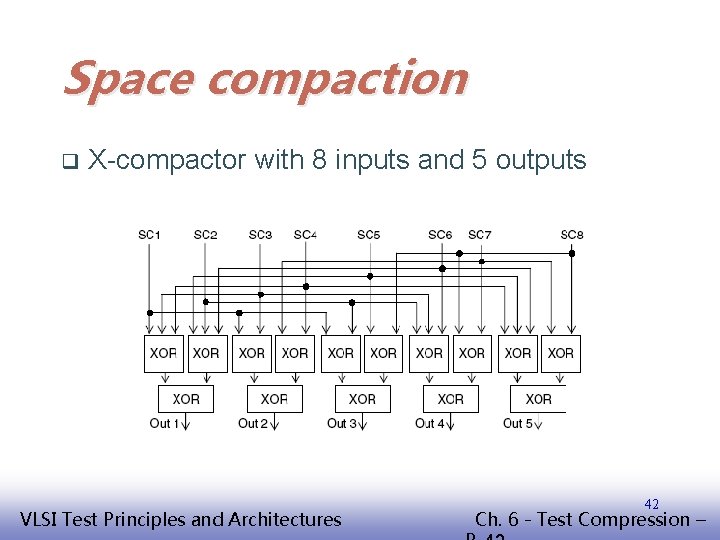

Space compaction q X-compactor with 8 inputs and 5 outputs EE 141 VLSI Test Principles and Architectures 42 Ch. 6 - Test Compression –

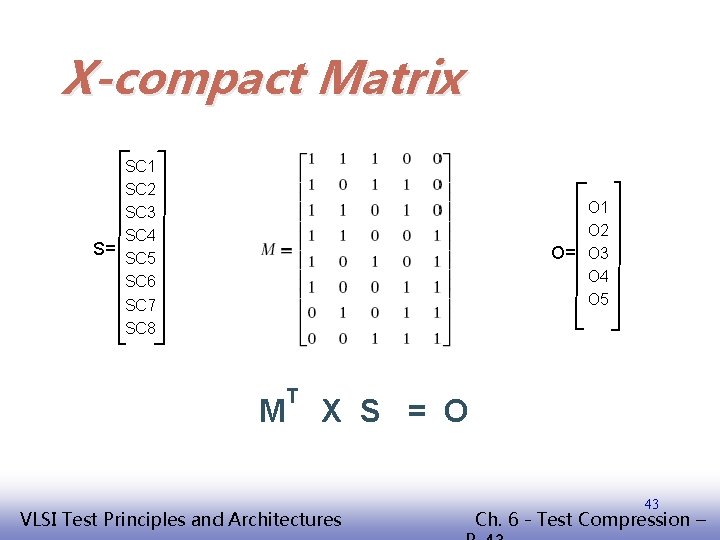

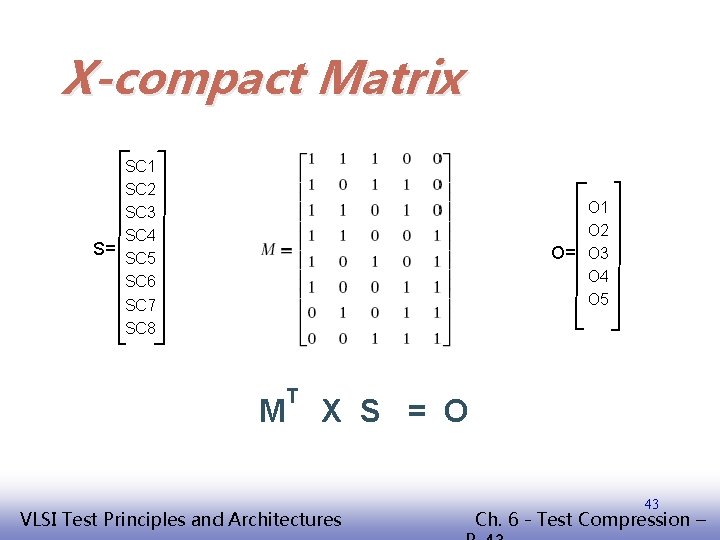

X-compact Matrix SC 1 SC 2 SC 3 SC 4 S= SC 5 SC 6 SC 7 SC 8 O 1 O 2 O= O 3 O 4 O 5 M T X S = O EE 141 VLSI Test Principles and Architectures 43 Ch. 6 - Test Compression –

Space compaction q X-blocking (or X-bounding) § X’s can be blocked before reaching the response compactor § Can ensure that no X’s will be observed § May result in fault coverage loss § Add area overhead and may impact delay EE 141 VLSI Test Principles and Architectures 44 Ch. 6 - Test Compression –

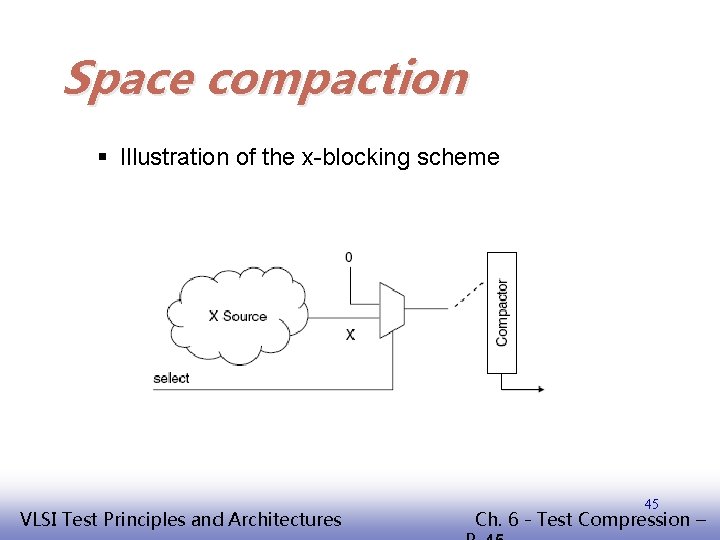

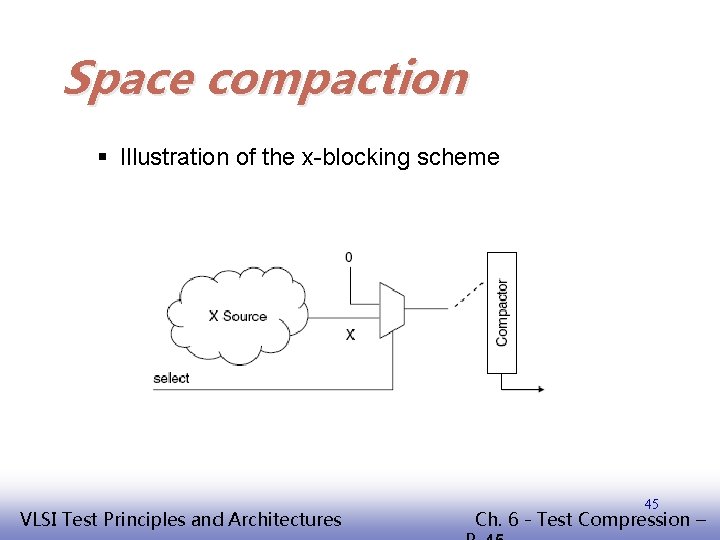

Space compaction § Illustration of the x-blocking scheme EE 141 VLSI Test Principles and Architectures 45 Ch. 6 - Test Compression –

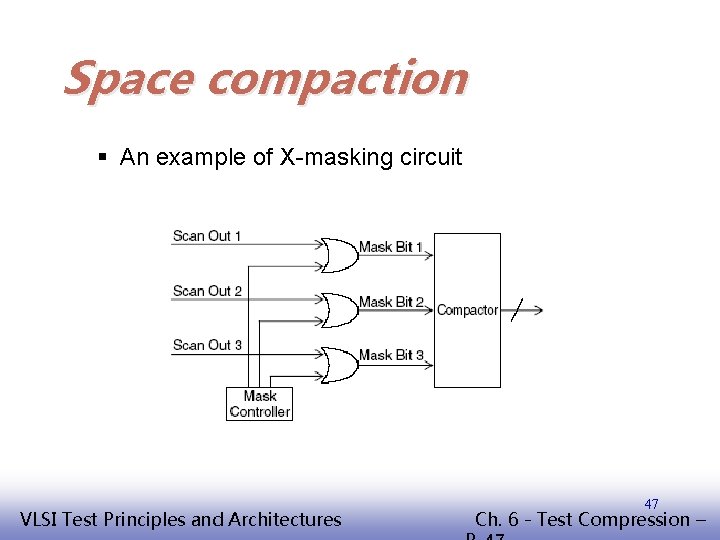

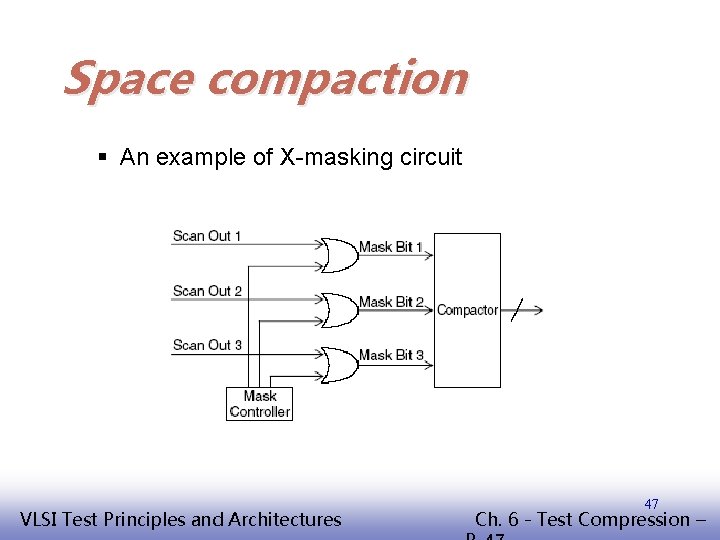

Space compaction q X-masking § X’s can be masked off right before the response compactor § Mask data is required to indicate when the masking should take place § Mask date can be compressed – Possible compression techniques are weighted pseudorandom LFSR reseeding or run-length encoding EE 141 VLSI Test Principles and Architectures 46 Ch. 6 - Test Compression –

Space compaction § An example of X-masking circuit EE 141 VLSI Test Principles and Architectures 47 Ch. 6 - Test Compression –

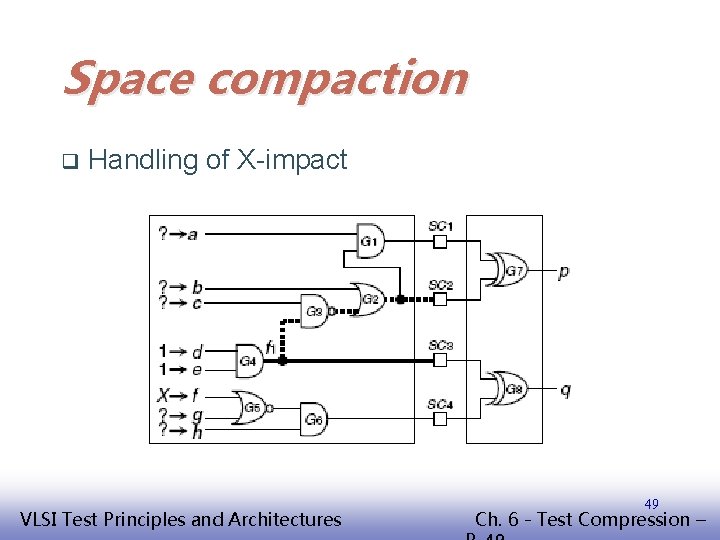

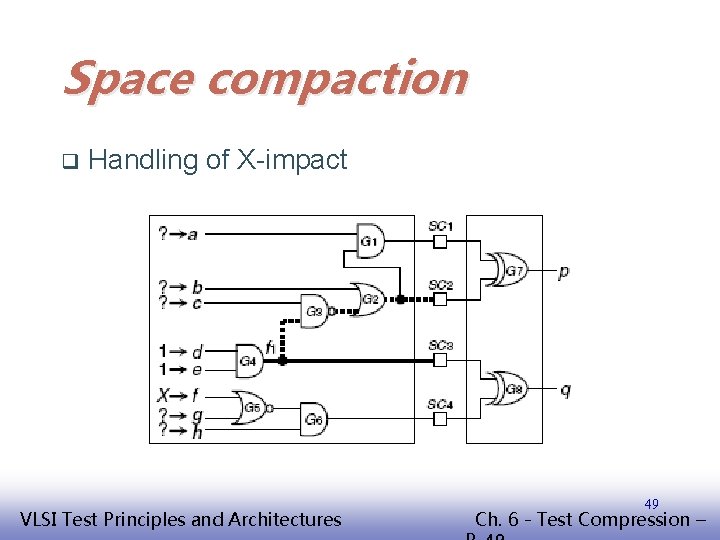

Space compaction q X-impact § Simply use ATPG to algorithmically handle the impact of residual x’s on the space compactor § Without adding any extra circuitry EE 141 VLSI Test Principles and Architectures 48 Ch. 6 - Test Compression –

Space compaction q Handling of X-impact EE 141 VLSI Test Principles and Architectures 49 Ch. 6 - Test Compression –

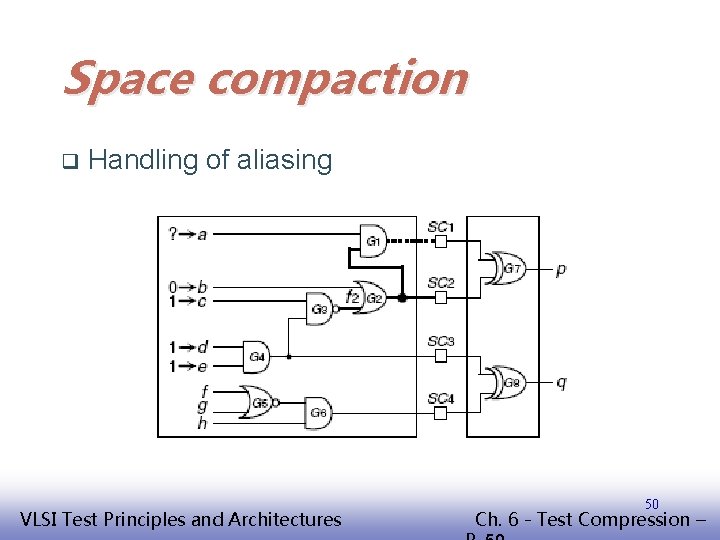

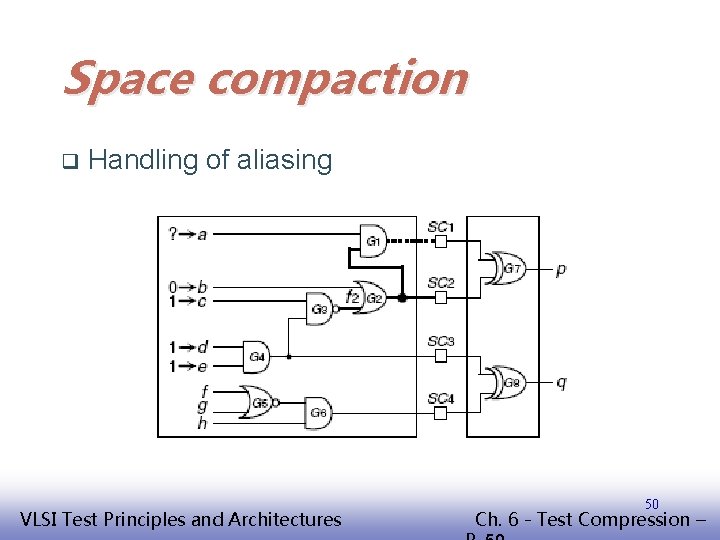

Space compaction q Handling of aliasing EE 141 VLSI Test Principles and Architectures 50 Ch. 6 - Test Compression –

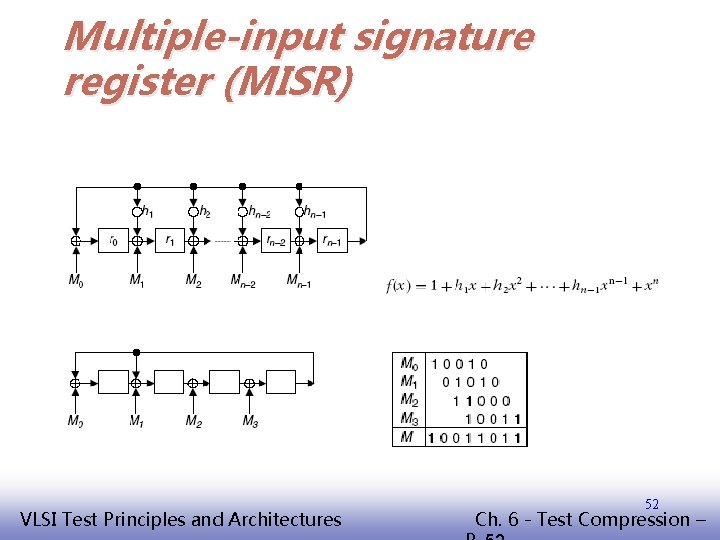

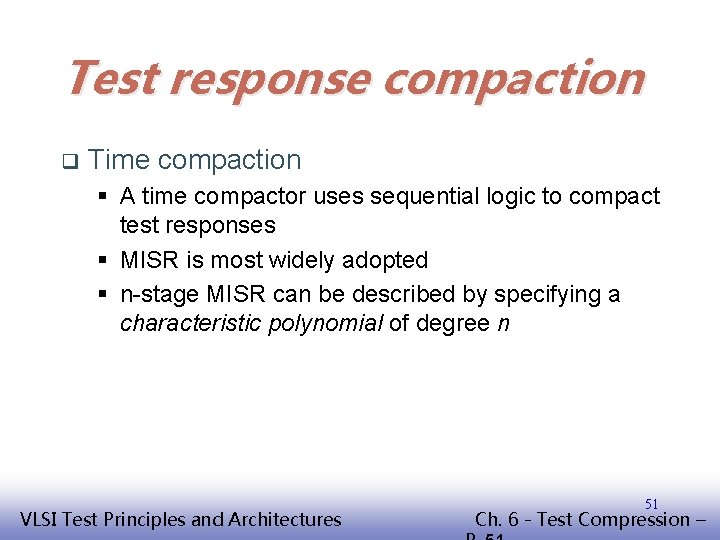

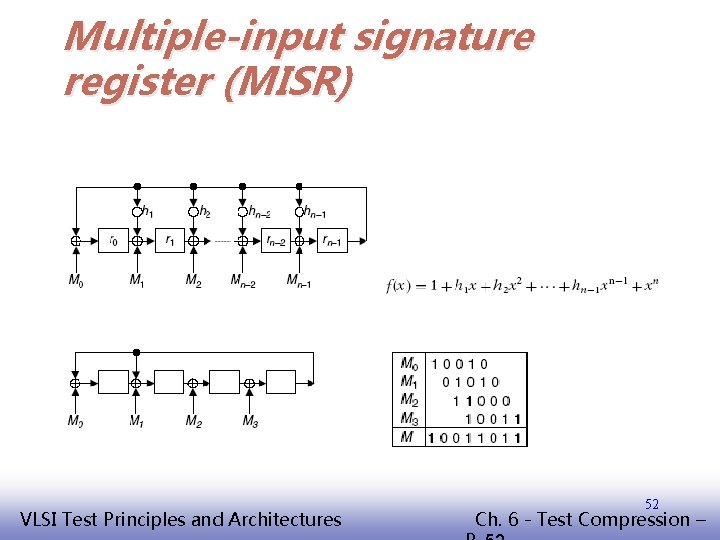

Test response compaction q Time compaction § A time compactor uses sequential logic to compact test responses § MISR is most widely adopted § n-stage MISR can be described by specifying a characteristic polynomial of degree n EE 141 VLSI Test Principles and Architectures 51 Ch. 6 - Test Compression –

Multiple-input signature register (MISR) EE 141 VLSI Test Principles and Architectures 52 Ch. 6 - Test Compression –

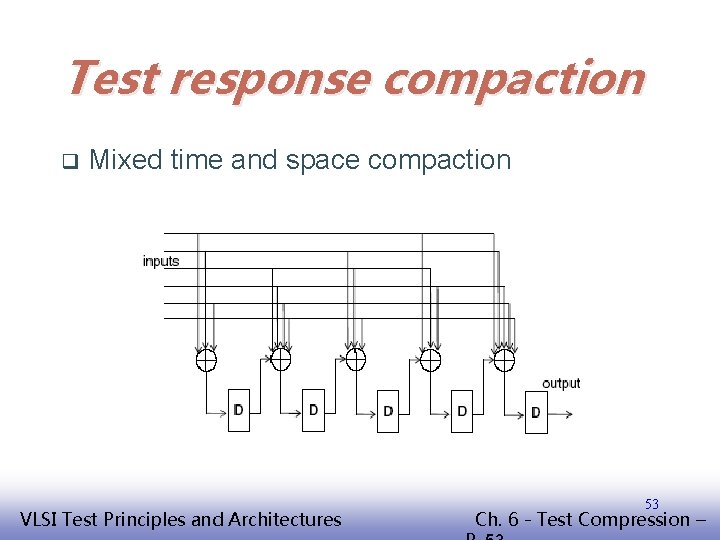

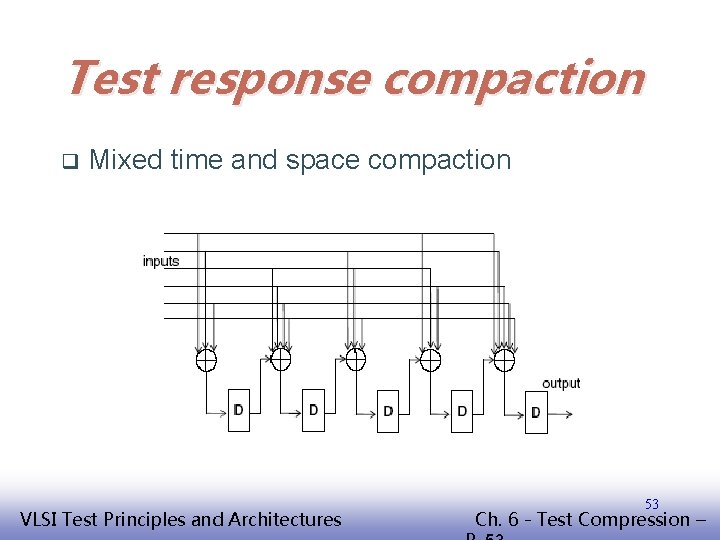

Test response compaction q Mixed time and space compaction EE 141 VLSI Test Principles and Architectures 53 Ch. 6 - Test Compression –

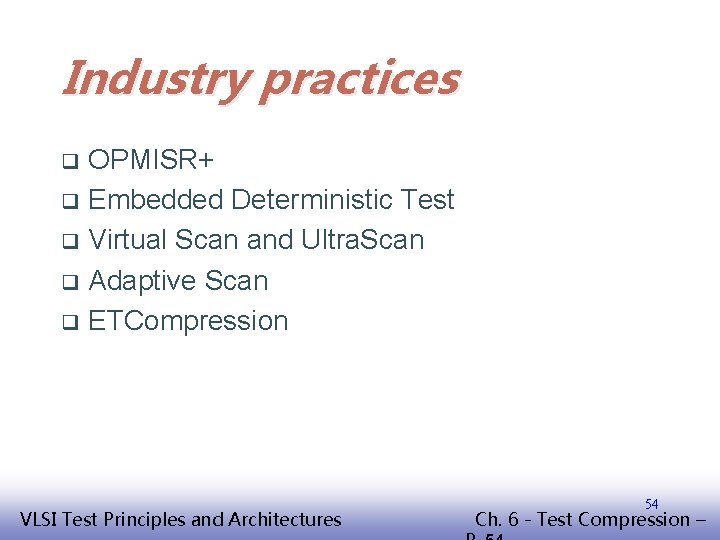

Industry practices OPMISR+ q Embedded Deterministic Test q Virtual Scan and Ultra. Scan q Adaptive Scan q ETCompression q EE 141 VLSI Test Principles and Architectures 54 Ch. 6 - Test Compression –

Industry solutions categories q Linear-decompression-based schemes § Two steps – ETCompression, Logic. Vision – Test. Kompress, Mentor Graphics – SOCBIST, Synopsys q Broadcast-scan-based schemes § Single step – SPMISR+, Cadence – Virtual. Scan and Ultra. Scan, Syn. Test – DFT MAX, Synopsys EE 141 VLSI Test Principles and Architectures 55 Ch. 6 - Test Compression –

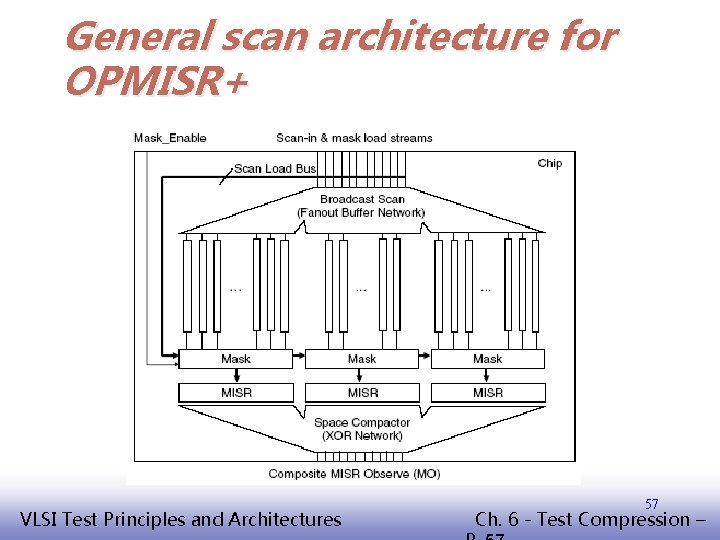

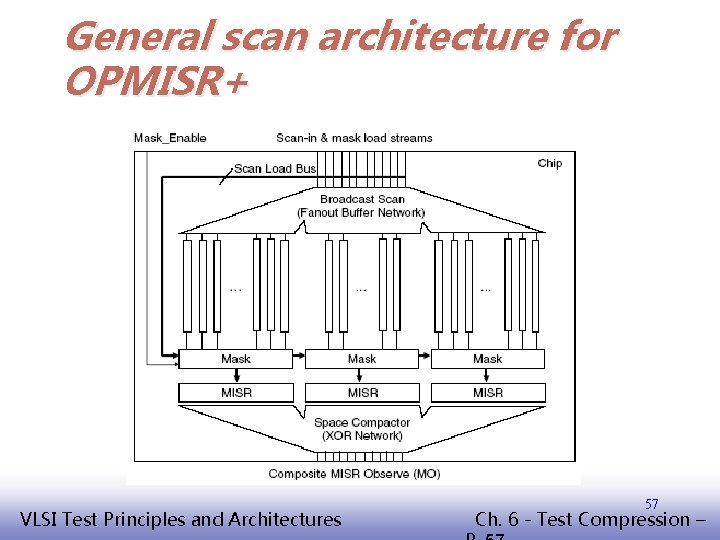

Industry practices q OPMISR+ § Cadence § Roots in IBM ‘s logic BIST and ATPG technology EE 141 VLSI Test Principles and Architectures 56 Ch. 6 - Test Compression –

General scan architecture for OPMISR+ EE 141 VLSI Test Principles and Architectures 57 Ch. 6 - Test Compression –

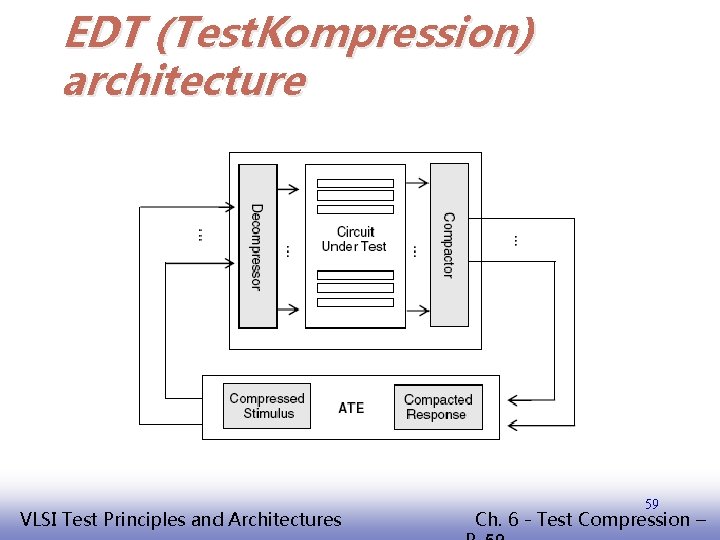

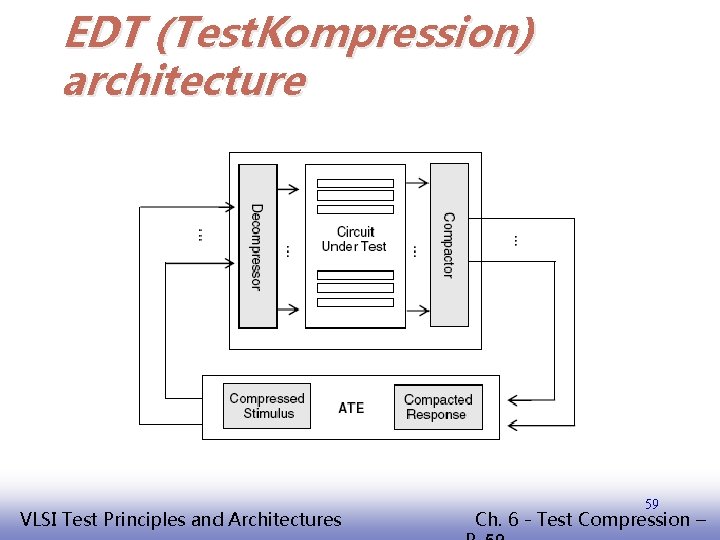

Industry practices q Embedded Deterministic Test (Test. Kompress) § Mentor Graphics § First commercially available on-chip test compression product EE 141 VLSI Test Principles and Architectures 58 Ch. 6 - Test Compression –

EDT (Test. Kompression) architecture EE 141 VLSI Test Principles and Architectures 59 Ch. 6 - Test Compression –

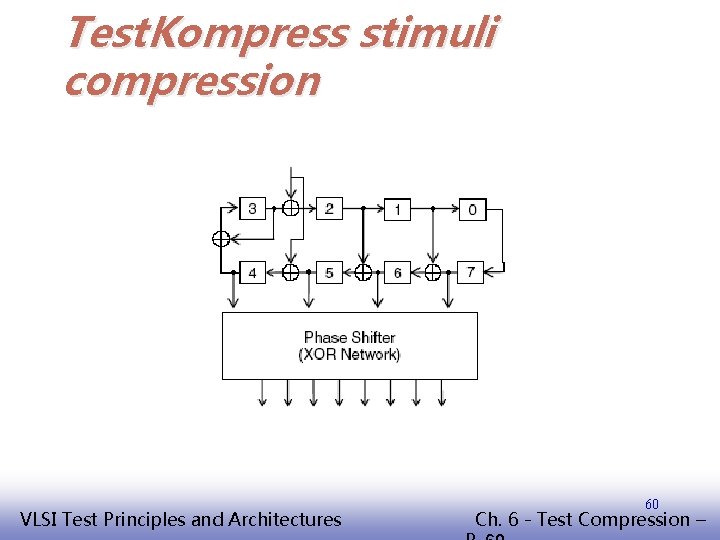

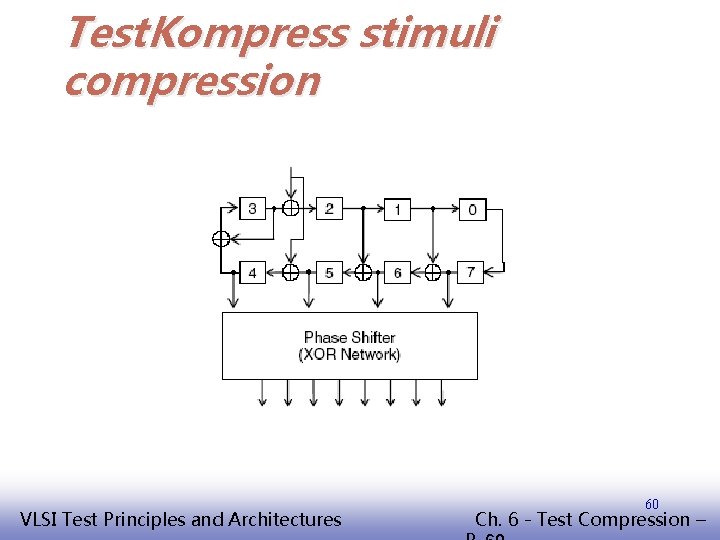

Test. Kompress stimuli compression EE 141 VLSI Test Principles and Architectures 60 Ch. 6 - Test Compression –

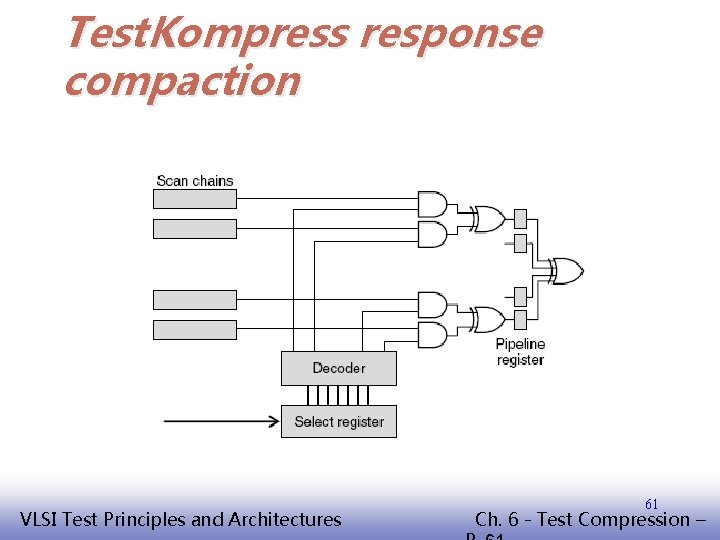

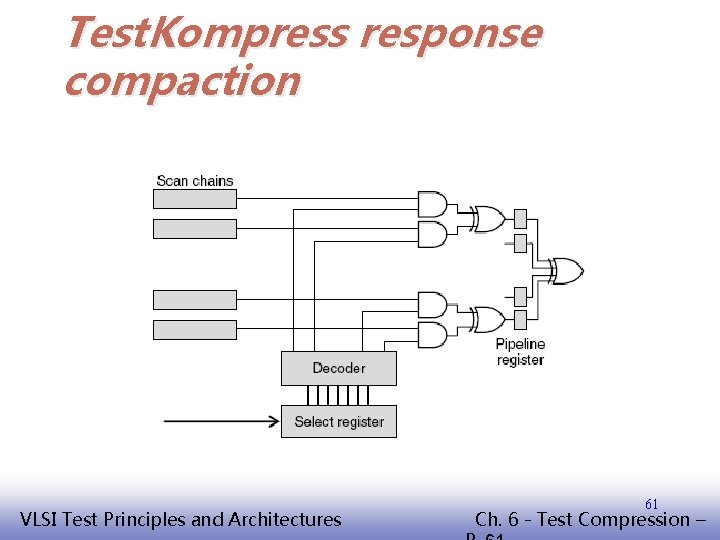

Test. Kompress response compaction EE 141 VLSI Test Principles and Architectures 61 Ch. 6 - Test Compression –

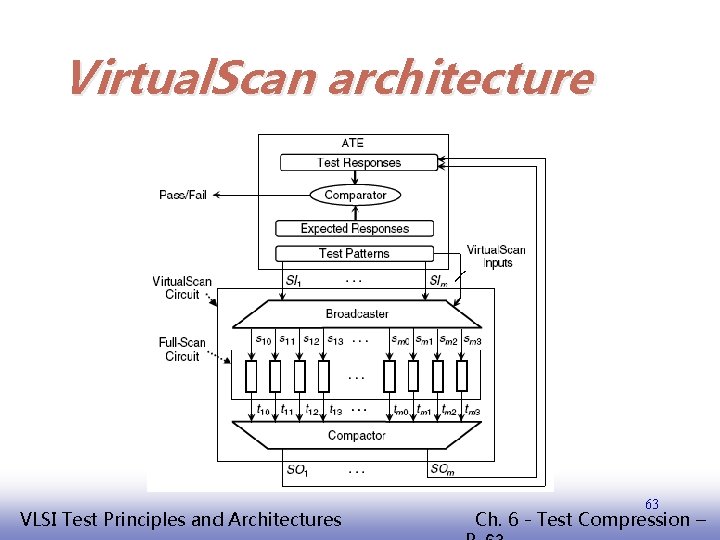

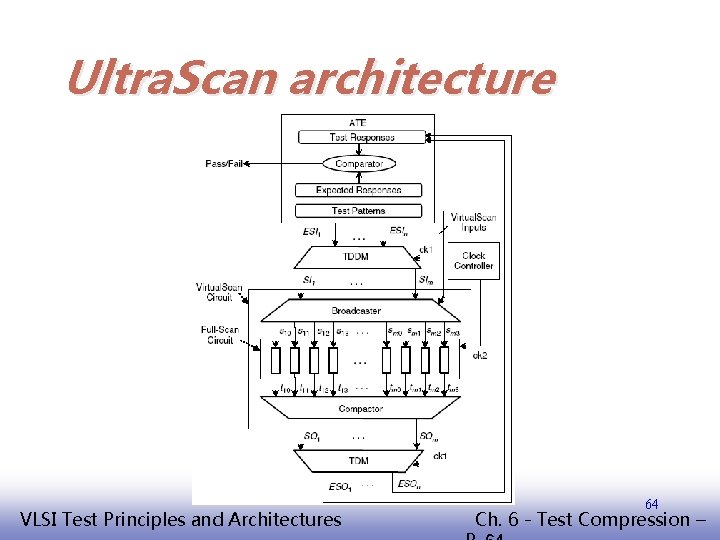

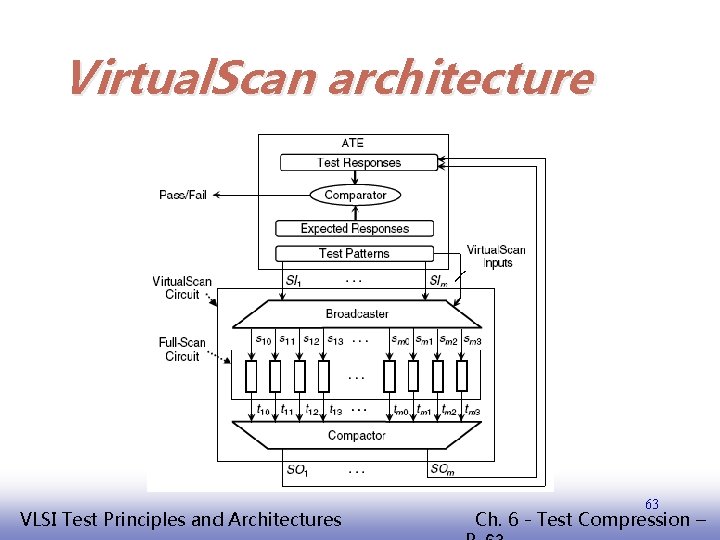

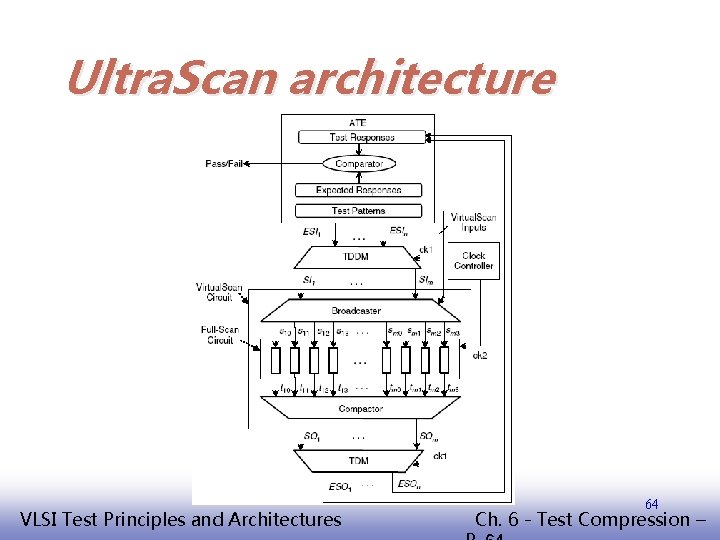

Industry practices q Virtual Scan and Ultra. Scan § Syn. Test § First commercial product based on the broadcast scan scheme using combinational logic for pattern decompression EE 141 VLSI Test Principles and Architectures 62 Ch. 6 - Test Compression –

Virtual. Scan architecture EE 141 VLSI Test Principles and Architectures 63 Ch. 6 - Test Compression –

Ultra. Scan architecture EE 141 VLSI Test Principles and Architectures 64 Ch. 6 - Test Compression –

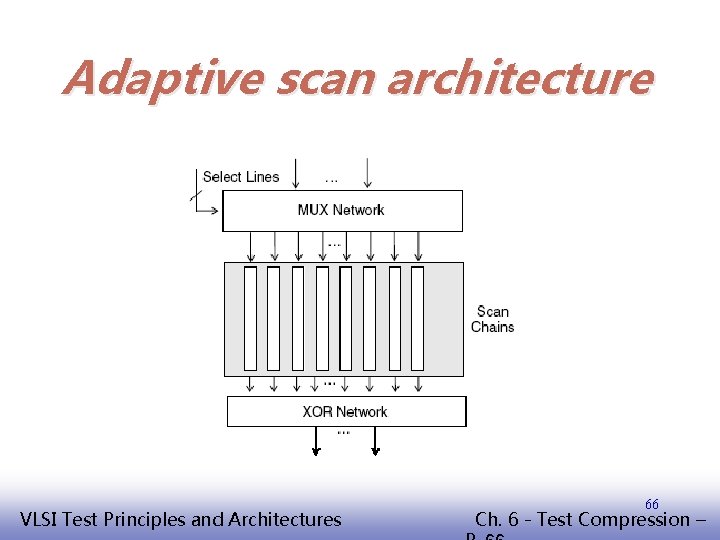

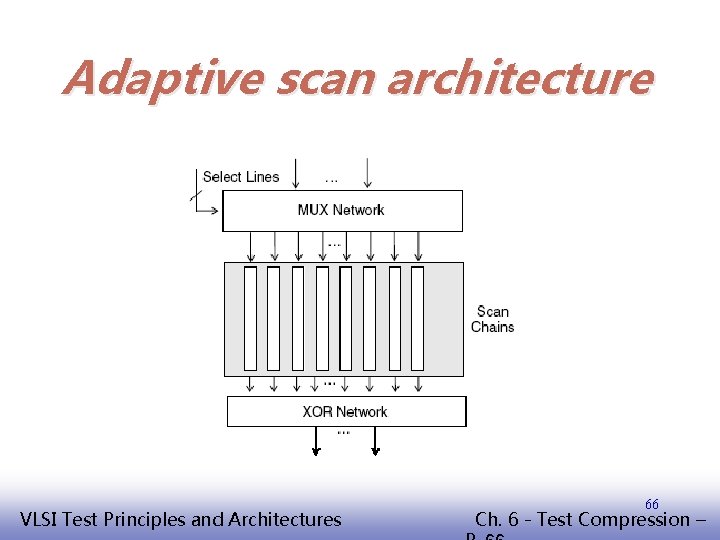

Industry practices q Adaptive Scan § Synopsys § Designed to be the next generation scan architecture EE 141 VLSI Test Principles and Architectures 65 Ch. 6 - Test Compression –

Adaptive scan architecture EE 141 VLSI Test Principles and Architectures 66 Ch. 6 - Test Compression –

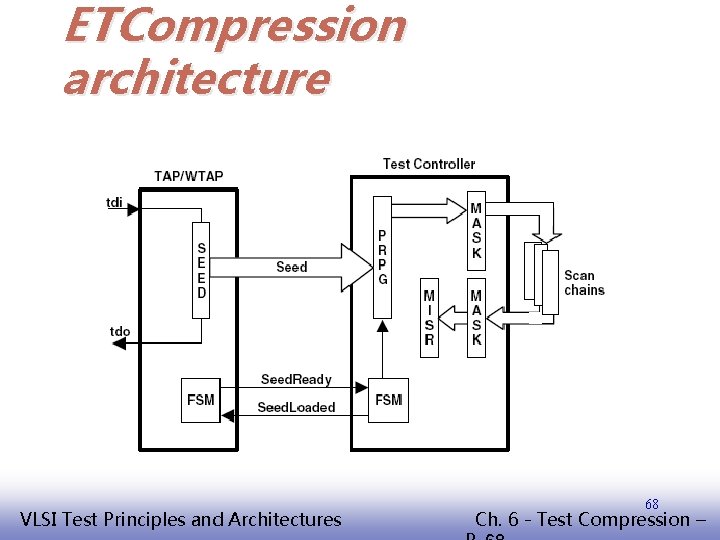

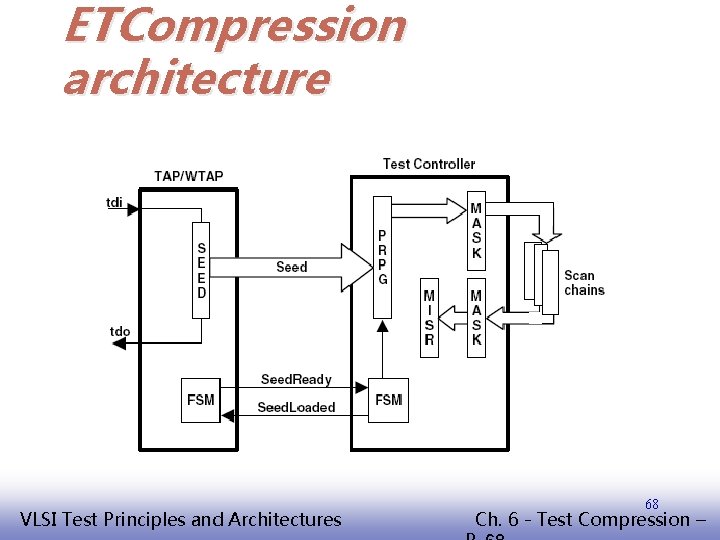

Industry practices q ETCompression § Logic. Vision § Built upon embedded logic test (ELT) technology EE 141 VLSI Test Principles and Architectures 67 Ch. 6 - Test Compression –

ETCompression architecture EE 141 VLSI Test Principles and Architectures 68 Ch. 6 - Test Compression –

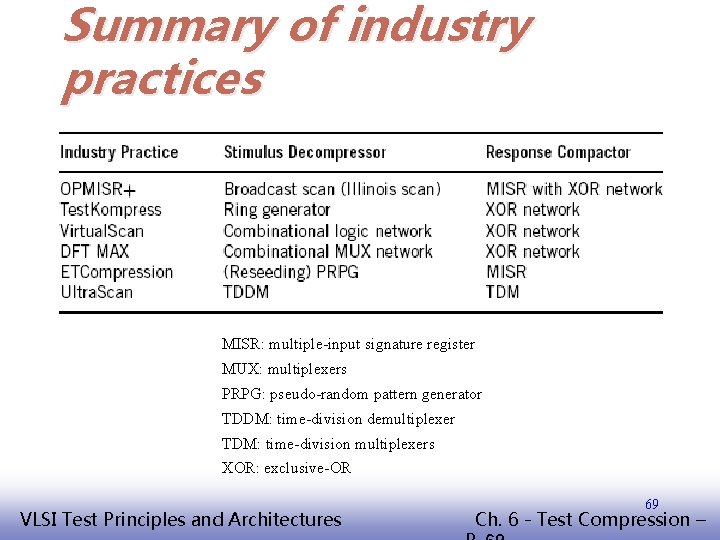

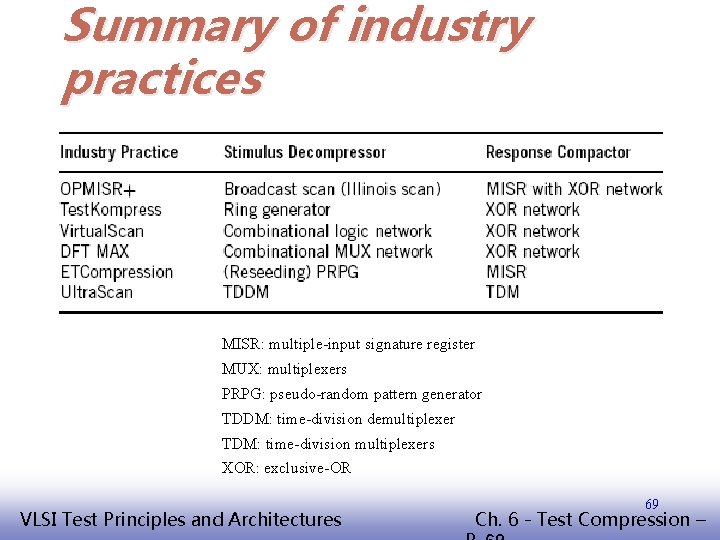

Summary of industry practices MISR: multiple-input signature register MUX: multiplexers PRPG: pseudo-random pattern generator TDDM: time-division demultiplexer TDM: time-division multiplexers XOR: exclusive-OR EE 141 VLSI Test Principles and Architectures 69 Ch. 6 - Test Compression –

Concluding remarks q Test compression is § An effective method for reducing test data volume and test application time with relatively small cost § An effective test structure for embedded hard cores § Easy to implement and capable of producing highquality tests § Successfully as part of design flow q Need to unify different compression architectures EE 141 VLSI Test Principles and Architectures 70 Ch. 6 - Test Compression –