Chapter 6 System Integration and Performance Chapter goals

- Slides: 63

Chapter 6 System Integration and Performance

Chapter goals n n n Describe the implementation of the system bus and bus protocol. Describe how the CPU and bus interact with peripheral devices. Describe the purpose and function of device controllers.

Chapter goals cont. n n Describe how interrupts coordinate actions of the CPU with secondary storage and I/O devices Describe how buffers, caches, and data compression improve computer system performance

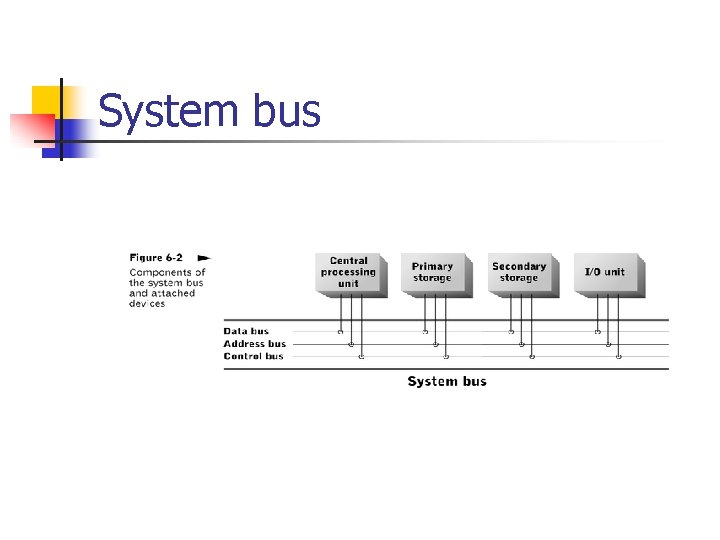

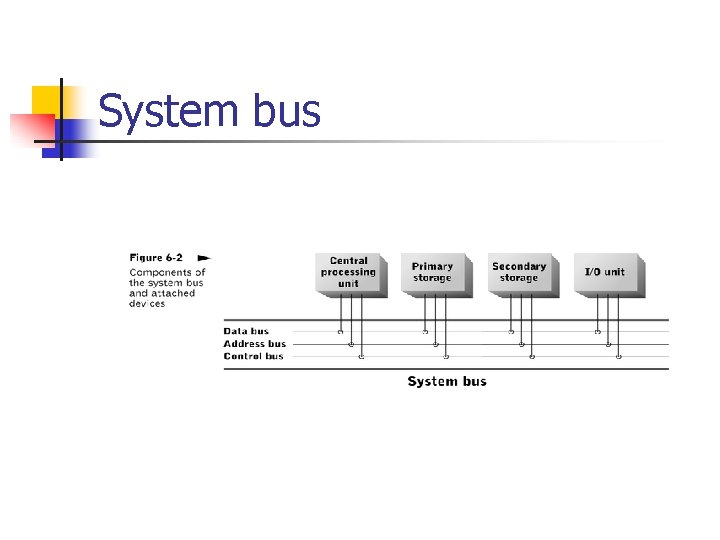

Role of the system bus n n Bus is mechanism that allows computer components to work together Is made up of parallel communication lines connecting computer components n n n CPU, hard drive, parallel port, modem, etc. Can connect two or more devices Information can travel in both directions

System bus (cont. ) n n Can connect both internal (hard drive) and external (printer) devices System bus has three parts n n Data bus – carries data Address bus – used if RAM is involved Control bus – commands and status information Each bus line carries 1 bit of information

System bus

Bus Clock n n n Like the CPU, the bus has a clock that acts as a timing device For CPU, each tick is trigger to execute an instruction For system bus, each tick is an opportunity to transmit data or a control message

Bus clock cont. n n Bus clock is MUCH slower than CPU clock Think of CPU as the highway and the system bus as the local streets

Why slower? n Data on bus must travel a longer physical distance than data in CPU n n n Even though data is traveling at the speed of light it still needs more time to travel over a greater distance Need to allows time to factor out noise, interference Also allows time to operate controller logic in peripheral devices

Bus data transfer rate n n n Called the bus data capacity Expresses how much data can travel across bus over time Is a combination of n n n Bus clock speed Data transfer unit (usually a word) Is used to calculate things like n Time required to load large files (i. e. video)

Bus protocol n n n Data transportation rules that ensure the smooth transfer of information without error Dictates the format, content, and timing of data, memory addresses, and messages Every peripheral device (no matter the manufacturer) must follow the bus protocol rules

Bus protocol cont. n n n Protocol can impact (reduce) data transfer rates Protocols often require exchanges of control signals Control signals consume bus cycles that could otherwise send data

Sample protocol n Example: if a disk drive transfers data to RAM as the result of an explicit CPU instruction, the following steps are followed: n n CPU sends command to the drive Drive send acknowledgement to CPU Drive carries out transfer Drive sends confirmation to CPU that transfer is complete

Why use protocols? n n Protocol regulates bus access Stops devices from interfering with each other I/O data transfer is the largest cause of errors in computers I/O commands need to be acknowledged and confirmed

What if two devices need the bus? n n When two (or more) peripheral devices need access to the bus at the same time that is called a collision Three solutions are in place to deal with this n n n Master-slave Multiple master Peer to peer

Master-slave n n n CPU is bus master Traditional computer architecture No device can access the bus unless in response to explicit command from CPU Allows a very simple protocol No collision is possible as long as CPU waits for response from device before proceeding to the next bus request

Master-slave cont. n Overall system performance is severely degraded n n n If devices can only communicate through the CPU, then transfers between devices, i. e. memory to disk, must pass through the CPU Every transfer takes at least 2 bus cycles CPU cannot execute software while it is managing the bus

A better solution n n System performance is improved if storage and I/O devices can transmit data among themselves without explicit CPU involvement Direct Memory Access (DMA) controller is attached to the bus and main memory DMA assumes the role of bus master for all transfers between memory and other storage or I/O devices CPU is free to do whatever

Multiple master bus n n Any device can assume control of the bus, or act as bus master for transfer to any other device (not just memory) Still only a single device can be master at one time Bus arbitration unit is a simple processor attached to a multiple master bus It decides which devices must wait when multiple devices want to become a bus master

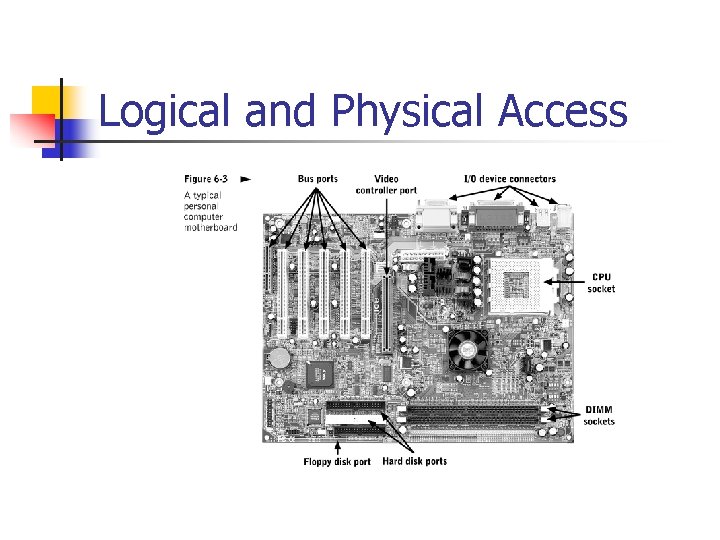

Logical vs. Physical Access n n I/O port is a communication pathway from the CPU to a peripheral device I/O port is often implemented as a memory address that can be accessed (read or written to) by n n The CPU Or a single peripheral device

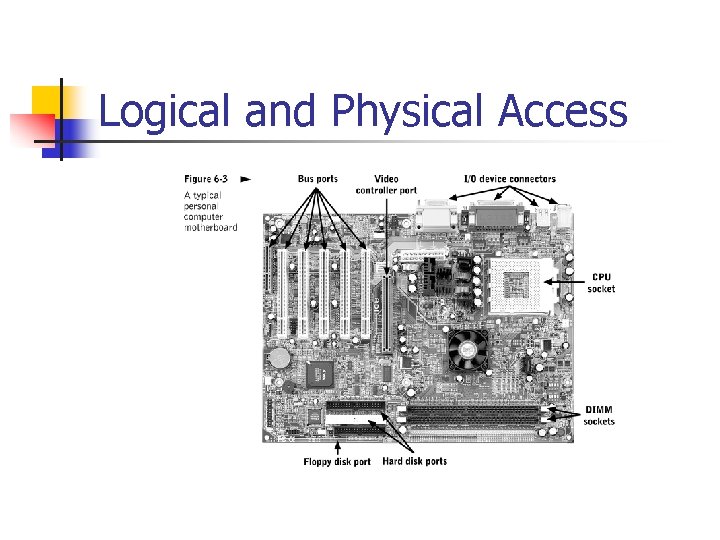

Logical and Physical Access

I/O Ports n n n Each peripheral device may have several I/O ports and use them for different purposes Dedicated bus hardware controls data movement between I/O ports and peripheral devices CPU reads and writes to I/O ports using ordinary data movement instructions or dedicated I/O instructions

The CPU and I/O Ports n n I/O port is more than a memory address, it is a data conduit It is a logical abstraction used by the CPU and the bus to interact with each peripheral device in a similar way

Logical access n n CPU and the bus both interact with each peripheral device as if it was a storage device containing one or more bytes of contiguous memory CPU and the bus deals with each device the same way, but devices are different n n n Storage capacity Internal data coding methods If storage or I/O device

Linear address space n n A read/write operation to/from this hypothetical device is called a logical access The set of sequentially numbered storage locations is called a linear address space

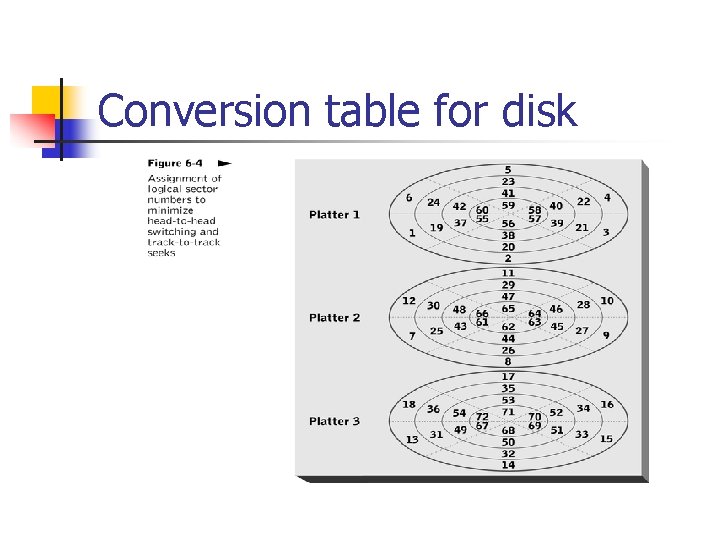

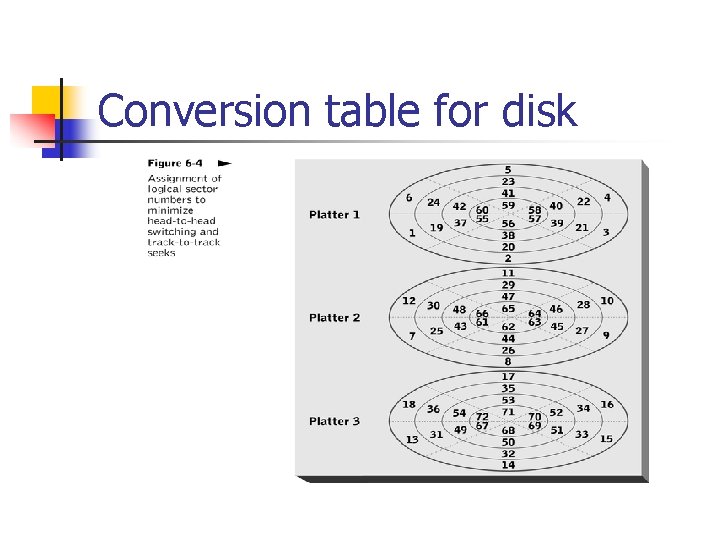

How logical becomes physical n n n Logical access assumes device is similar to memory (RAM) Bus address lines carry the position within the linear address space being read or written Device controller makes the conversion via a conversion table or a simple algorithm

Conversion table for disk

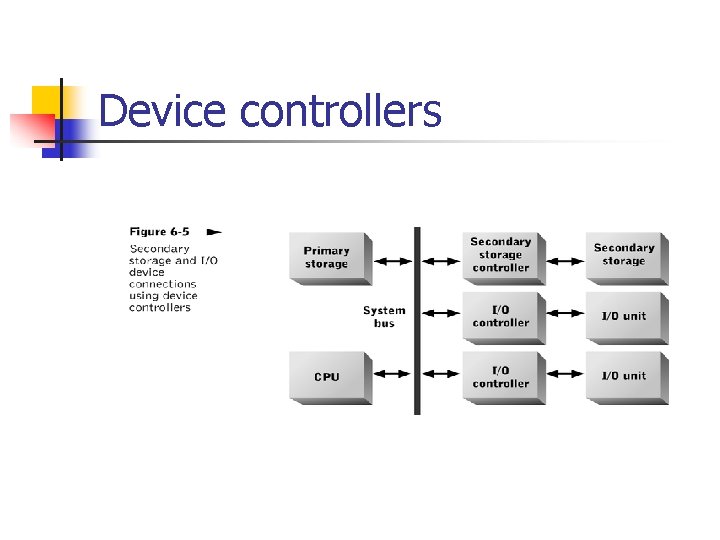

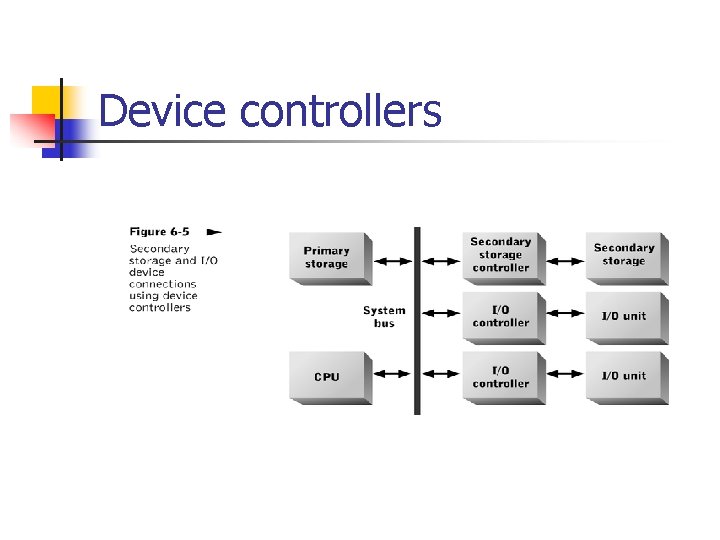

Device controllers n n Storage devices have intermediaries that connect them to the system bus Translate logical access to physical access Handles bus protocol (receiving and acknowledging commands) Permits several devices to share a bus connection

Device controllers

Device controllers cont. n n Device controllers monitor the bus control lines for signals to peripheral devices Translates those signals into appropriate commands for its device

Interrupts n n Secondary storage and I/O device transfer rates are much slower than the CPU Why? n n Slower bus clock Peripheral devices have mechanical elements (access arm, spin mechanism) that are slower than speed of electricity

Interrupts cont. n n n When the CPU issues a read/write instruction it ALWAYS has to wait This waiting time can translate into thousands, millions, or even billions of CPU cycles To allow CPU to be used more efficiently, interrupts are used

How interrupts work n n n When a program (task, process, thread) needs I/O, CPU makes I/O request over the system bus Then puts your task aside (asleep) Does something else for the time being

Interrupts cont. n n When I/O is complete, interrupt signal is sent to the CPU can now restart your task with I/O task being complete

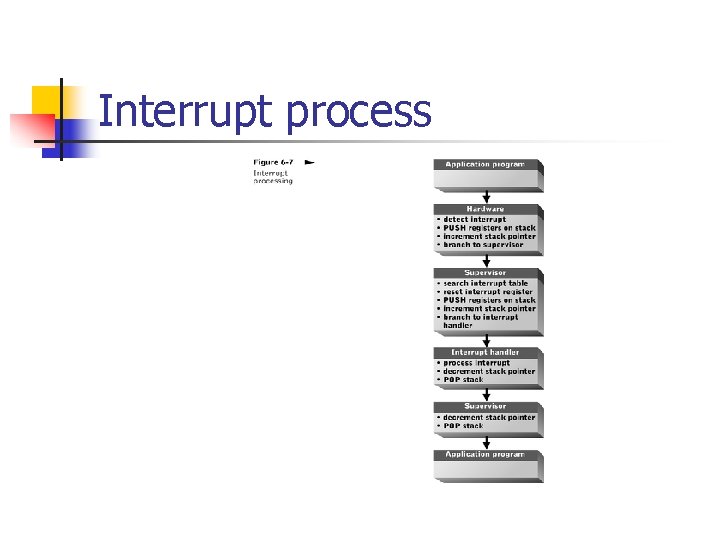

CPU and Interrupts n n n Portion of the CPU (separate from the fetch execute cycle) continuously monitors the bus for interrupt signals The signal is an interrupt code that indicates the bus port number of the device sending the interrupt CPU copies any interrupt signals it encounters into an interrupt register

The CPU and Interrupts cont. n n As an extra step in the fetch execute cycle, the CPU checks the interrupt register after completing an instruction but before fetching another one If interrupt register has a non-zero value CPU must respond to the interrupt

CPU and Interrupts n If CPU is to process an interrupt it does the following: n n Puts aside (suspends) current task Resets interrupt register to 0 (zero) Processes interrupt by calling interrupt handler After interrupt processing is complete, resumes suspended program

Interrupt handlers n n Interrupts are a mechanism for calling (invoking) system software processes and programs Operating system (OS) provides lowlevel processing routines (service calls) n n Examples: reading data in from the keyboard Writing to a file

Interrupt handlers cont. n n There is a unique individual interrupt handler (i. e. program) to process each possible interrupt Each handler is a separate program stored in a separate part of main memory

Interrupt table n n n A conversion table in main memory that has a list of all interrupt codes Interrupt code is used as an index into interrupt table For each interrupt code, interrupt table has the memory address of each interrupt handler

Interrupt handlers n n Supervisor (OS) examines the interrupt code, uses it as an index into the interrupt table Looks up memory location of needed interrupt handler Loads that memory location into the PC (program counter) Interrupt handler begins executing

Multiple interrupts n n n It is possible (even likely) that interrupts will interrupt each other OS has an algorithm to determine what goes first Assigns priorities to different interrupts based on n n Error conditions Critical hardware failures

Suspending a process n n Whenever a process is suspended or interrupted the system must save whatever information is necessary to allow the process to restart again Typically that involved saving n n PC and IR Any other specialized or general purpose registers that were in use

Saving a process n n The collection of information needed to restart a process is called the “machine state” It is saved in a special storage location called the stack

The Stack n n n The stack is a specialize storage location in RAM It is a data structure where you add and delete information from the same end Therefore the last process saved by the CPU is the first one it will pick up

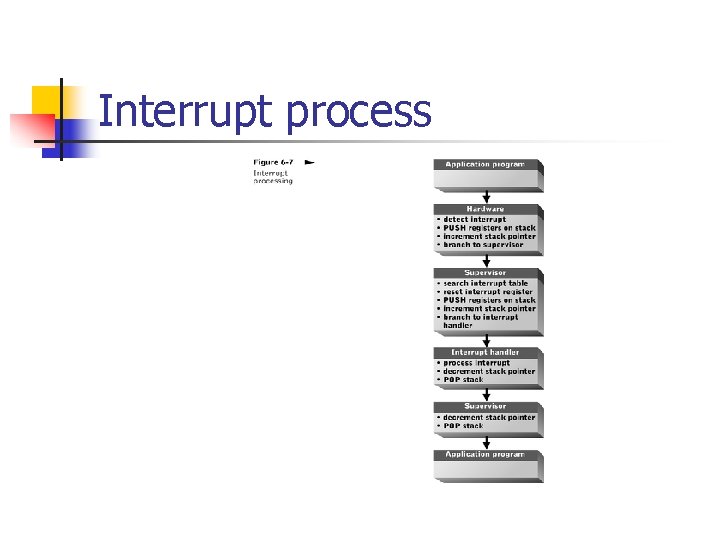

Interrupt process

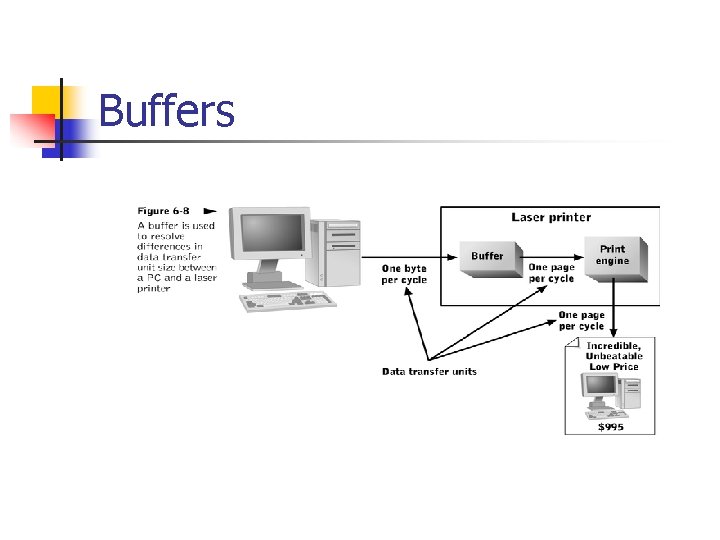

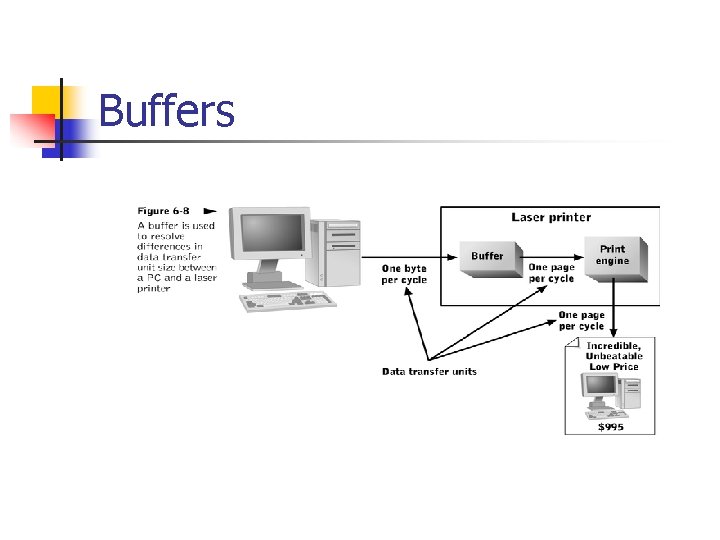

Buffers n n Buffers are a mechanism that uses RAM to overcome slow data transfer rate to peripheral devices Small storage area (in RAM) used to hold data in transit from one device to another

Buffers and printing n n Printed version of document with formatting information is copied to RAM When full page is ready it is released from the buffer Document is written from RAM to printer Also have input buffers – keyboard, modem, etc.

Buffers

Cache n n Pronounced “cash” Separate high speed storage area specifically managed to improve overall system performance Idea is most often needed data is kept in the cache Must be managed intelligently

Cache cont. n n Data content is not automatically removed (unlike buffer) Used for bi-directional data transfer Used only for storage device access Larger than buffer

Cache cont. n n n Basic idea is that access to high speed cache is faster than hard drive During a write operation cache acts as a buffer Data written to cache then to drive

Cache controller n n Manages the content of the cache It must “guess” which files should be in the cache, i. e. what data the CPU will ask for n n n Cache hit – when data is found in the cache Cache miss – when data is not found Cache swap – old data removed and new data inserted

Cache cont. n n Even a small cache can significantly improve performance Ratio of primary storage to cache of 10, 000 to 1 can result in cache hit rate of 90%

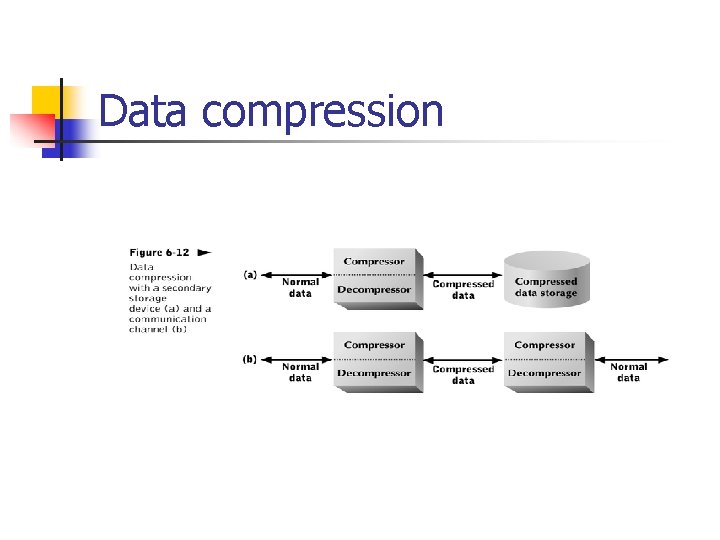

Compression n n Technique to reduce the number of bits used to encode a set of related data items, i. e. a file or stream of video Some formats (MP 3, GIF) are intentionally compressed data formats

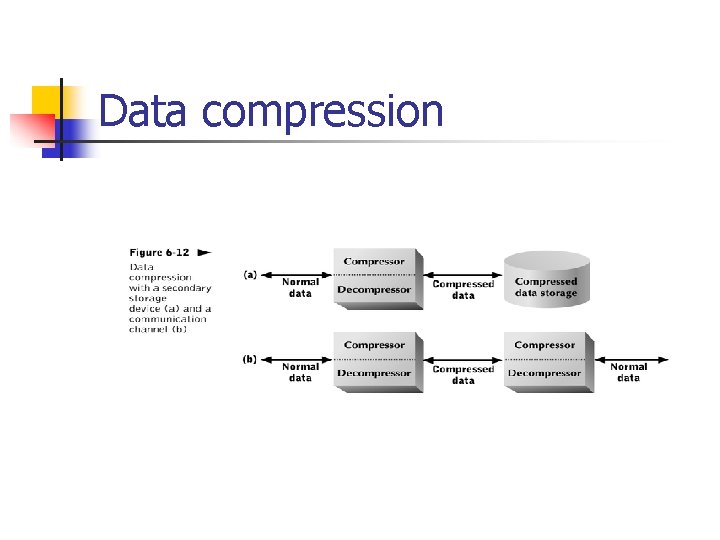

Compression cont. n n Compression is accomplished by the application of a compression algorithm (specific mathematical technique) Also need corresponding decompression algorithms to restore data to its original state

Compression cont. n n n Compression algorithms vary What types of data are appropriate Whether any data is lost Amount by which data is compressed Lossless compression (zip) – no loss of data Lossy – some loss of data (audio or video)

Compression cont. n n Compression rate – size before and after compression Used to reduce secondary storage requirements Transmit over Internet Package files together

Data compression

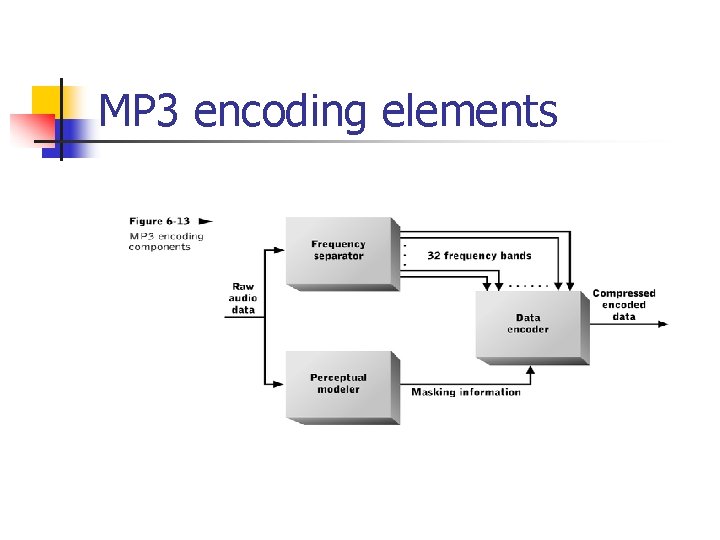

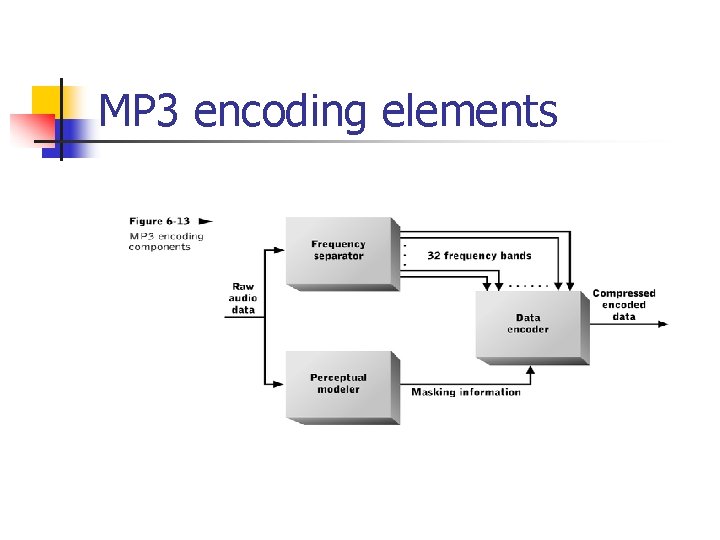

MP 3 encoding elements

MP 3 n How MP 3 works http: //www. howstuffworks. com/mp 31. h tm

Summary n n The system bus is the communication pathway that connects the CPU with memory and other devices The CPU communicates with peripheral devices through I/O ports

Summary cont. n n n Application programs use interrupt processing to coordinate data transfers to or from peripheral devices, notify the CPU of errors, and call operating system service programs A buffer is a region of memory that holds a single unit of data for transfer to or from a device Compression reduces the number of bits required to encode a data set or stream, effectively increasing the capacity of a communication channel or storage device