Chapter 6 Multichannel Buffered Serial Port Mc BSP

Chapter 6 Multi-channel Buffered Serial Port (Mc. BSP)

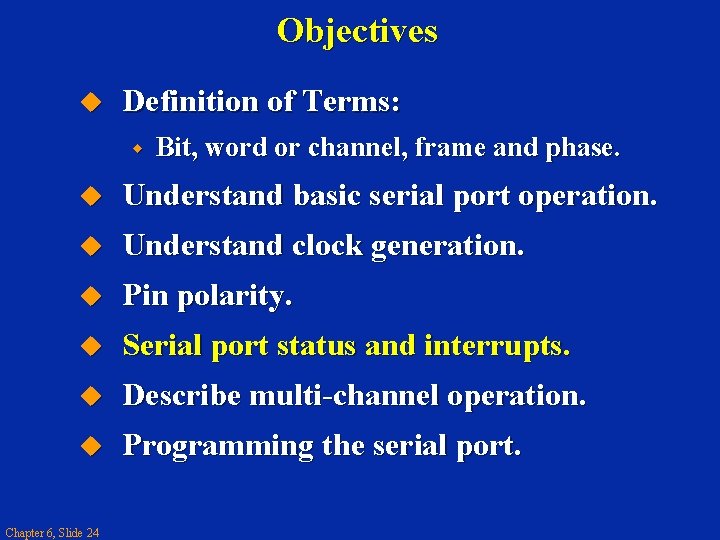

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 2

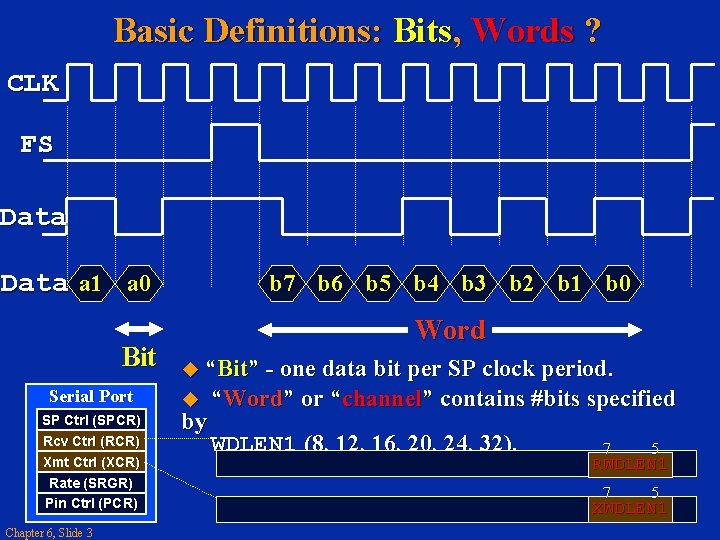

Basic Definitions: Bits, Words ? CLK FS Data a 1 a 0 Bit Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 3 b 7 b 6 b 5 b 4 b 3 b 2 b 1 b 0 Word “Bit” - one data bit per SP clock period. by “Word” or “channel” contains #bits specified WDLEN 1 (8, 12, 16, 20, 24, 32). 7 5 RWDLEN 1 XWDLEN 1

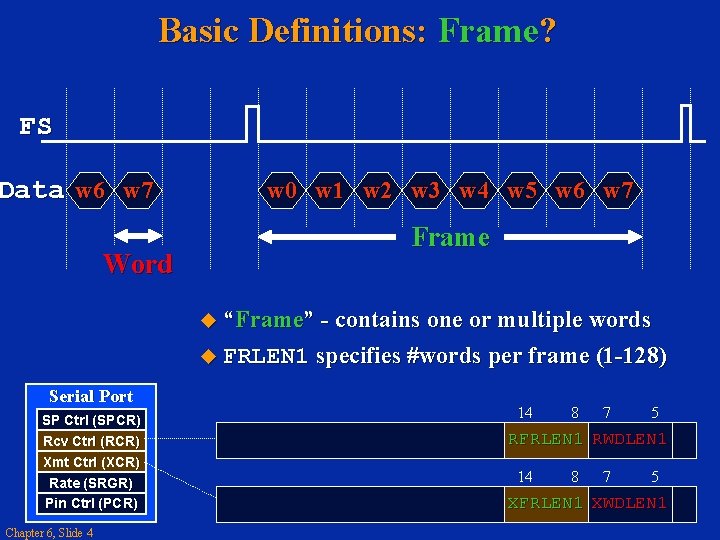

Basic Definitions: Frame? FS Data w 6 w 7 Word w 0 w 1 w 2 w 3 w 4 w 5 w 6 w 7 Frame “Frame” - contains one or multiple words FRLEN 1 specifies #words per frame (1 -128) Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 4 14 8 7 5 RFRLEN 1 RWDLEN 1 14 8 7 5 XFRLEN 1 XWDLEN 1

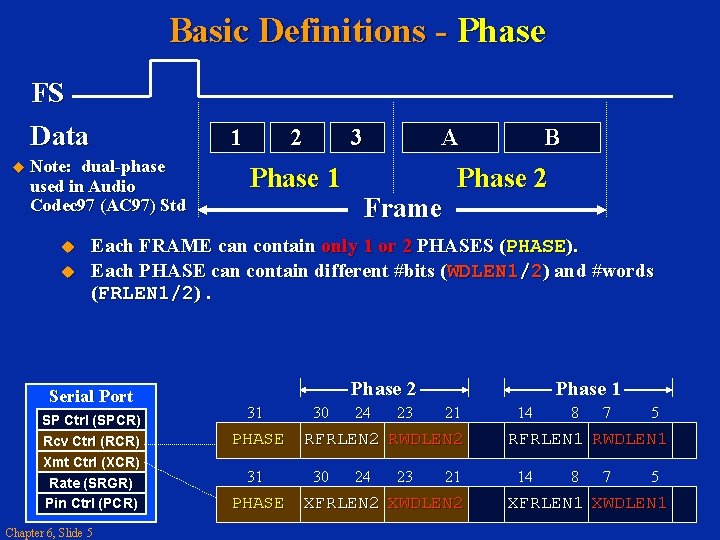

Basic Definitions - Phase FS Data 1 Note: dual-phase used in Audio Codec 97 (AC 97) Std 2 3 Phase 1 A Frame B Phase 2 Each FRAME can contain only 1 or 2 PHASES (PHASE). Each PHASE can contain different #bits (WDLEN 1/2) and #words (FRLEN 1/2). Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 5 Phase 2 31 PHASE 30 24 23 Phase 1 21 RFRLEN 2 RWDLEN 2 30 24 23 21 XFRLEN 2 XWDLEN 2 14 8 7 5 RFRLEN 1 RWDLEN 1 14 8 7 5 XFRLEN 1 XWDLEN 1

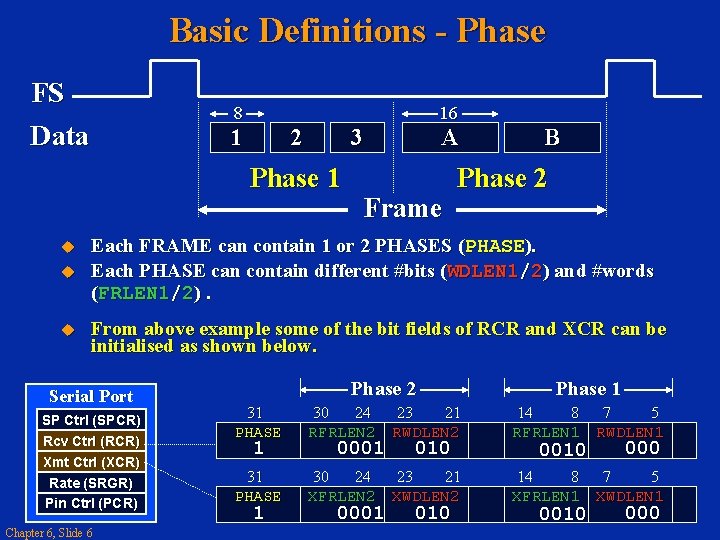

Basic Definitions - Phase FS Data 8 1 2 16 3 Phase 1 A Frame B Phase 2 Each FRAME can contain 1 or 2 PHASES (PHASE). Each PHASE can contain different #bits (WDLEN 1/2) and #words (FRLEN 1/2). From above example some of the bit fields of RCR and XCR can be initialised as shown below. Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 6 Phase 2 Phase 1 31 PHASE 30 24 RFRLEN 2 23 21 RWDLEN 2 8 14 RFRLEN 1 7 5 RWDLEN 1 31 PHASE 30 24 XFRLEN 2 23 21 XWDLEN 2 8 14 XFRLEN 1 7 5 XWDLEN 1 1 1 0001 010 0010 000

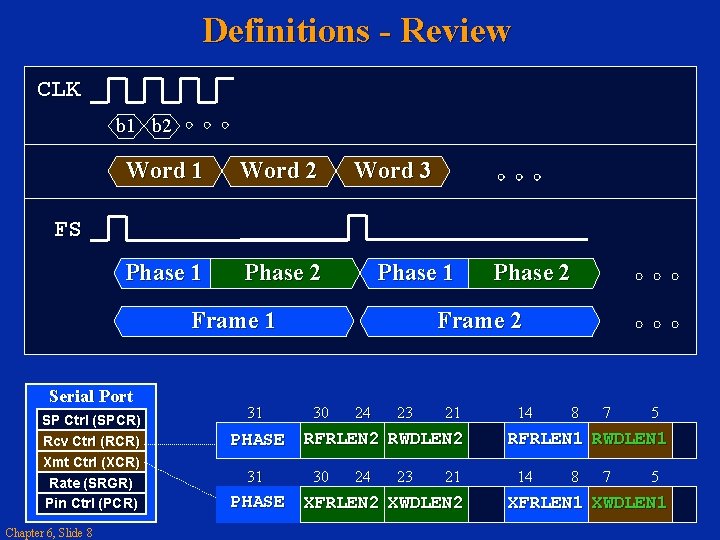

Definitions - Review CLK b 1 b 2 Word 1 Word 2 Phase 1 Phase 2 Word 3 FS Phase 1 Frame 1 Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 8 31 PHASE Phase 2 Frame 2 30 24 23 21 RFRLEN 2 RWDLEN 2 30 24 23 21 XFRLEN 2 XWDLEN 2 14 8 7 5 RFRLEN 1 RWDLEN 1 14 8 7 5 XFRLEN 1 XWDLEN 1

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 9

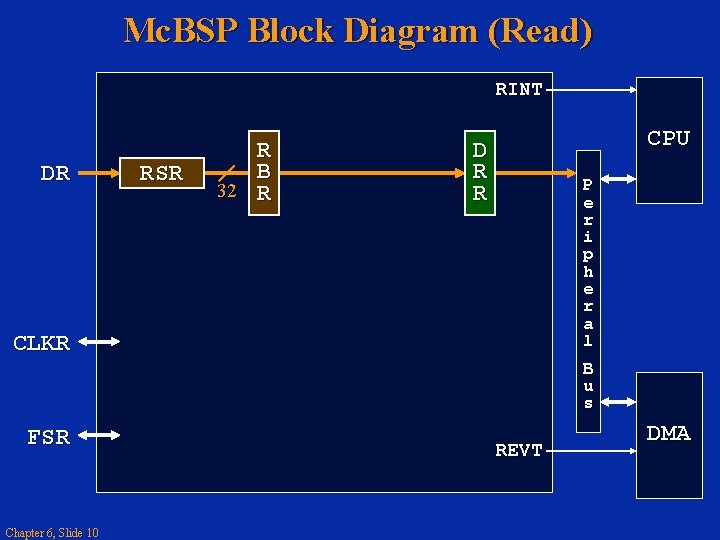

Mc. BSP Block Diagram (Read) RINT DR RSR R B 32 R CPU D R R P e r i p h e r a l CLKR B u s FSR Chapter 6, Slide 10 REVT DMA

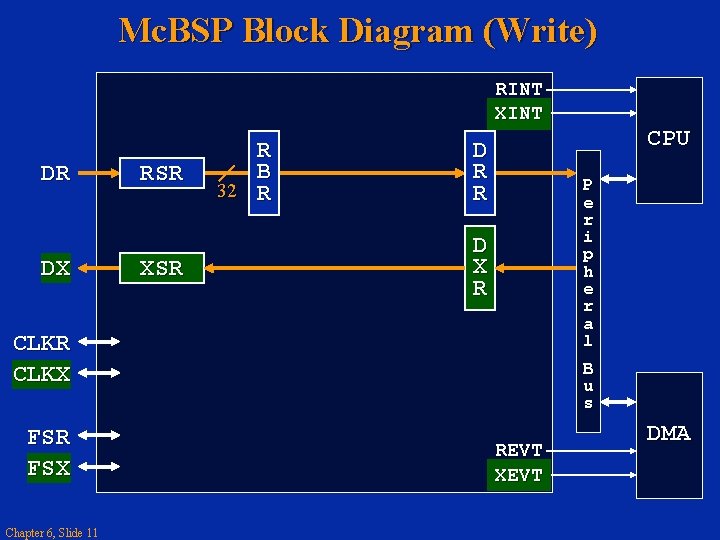

Mc. BSP Block Diagram (Write) RINT XINT DR DX RSR XSR R B 32 R D R R P e r i p h e r a l D X R CLKX FSR FSX Chapter 6, Slide 11 CPU B u s REVT XEVT DMA

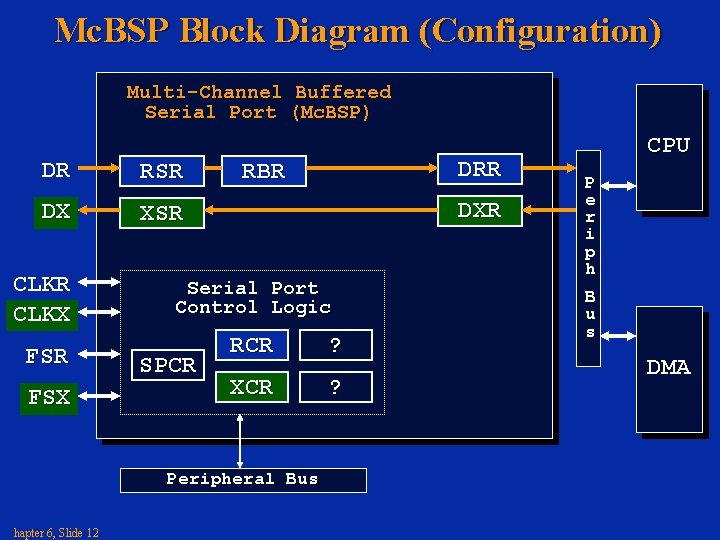

Mc. BSP Block Diagram (Configuration) Multi-Channel Buffered Serial Port (Mc. BSP) DR RSR DX XSR CLKX FSR FSX DXR Serial Port Control Logic SPCR RCR ? XCR ? Peripheral Bus Chapter 6, Slide 12 DRR RBR CPU P e r i p h B u s DMA

Serial Port - Basic Operation Multi-Channel Buffered Serial Port (Mc. BSP) DR RSR DX XSR CLKX FSR FSX DRR RBR DXR Serial Port Control Logic SPCR RCR SRGR XCR Peripheral Bus Chapter 6, Slide 13 CPU P e r i p h B u s DMA “TRANSMIT” “RECEIVE”

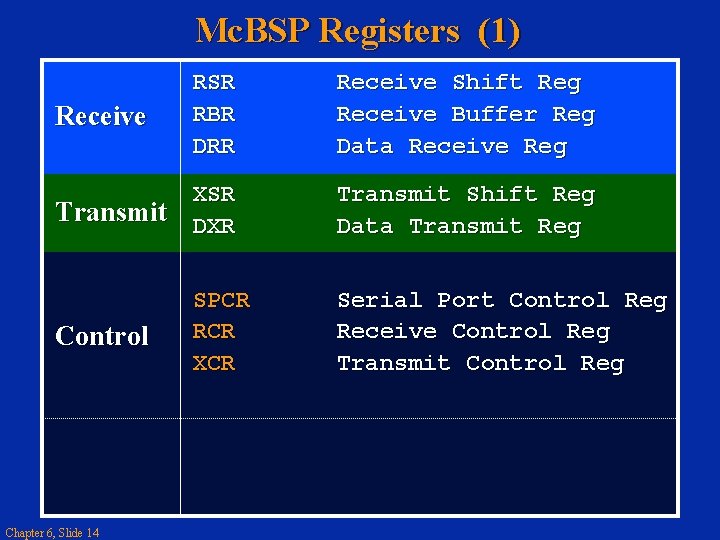

Mc. BSP Registers (1) Receive RSR RBR DRR Receive Shift Reg Receive Buffer Reg Data Receive Reg Transmit XSR DXR Transmit Shift Reg Data Transmit Reg Control SPCR RCR XCR Serial Port Control Reg Receive Control Reg Transmit Control Reg Chapter 6, Slide 14

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 15

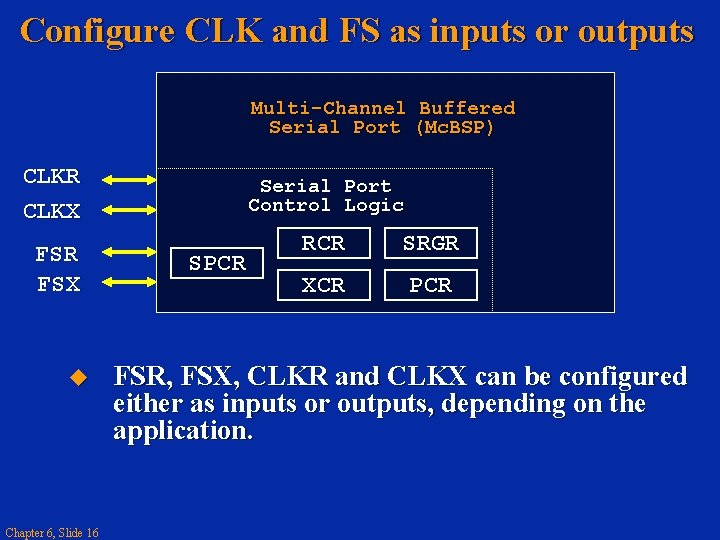

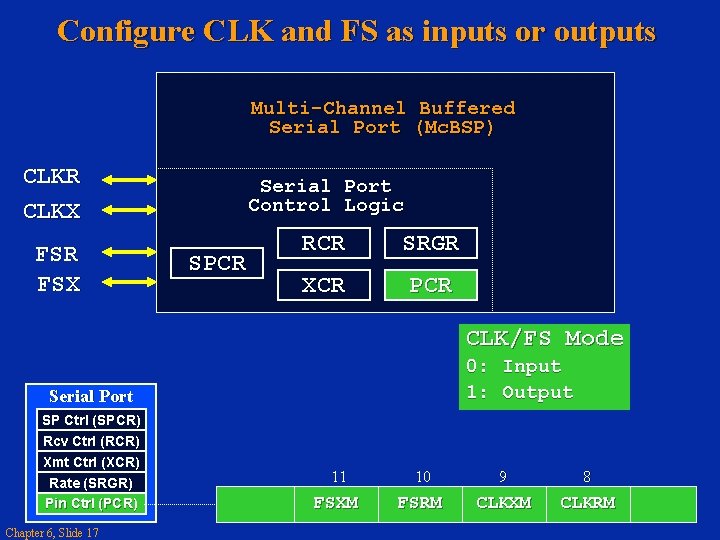

Configure CLK and FS as inputs or outputs Multi-Channel Buffered Serial Port (Mc. BSP) CLKR CLKX FSR FSX Chapter 6, Slide 16 Serial Port Control Logic SPCR RCR SRGR XCR PCR FSR, FSX, CLKR and CLKX can be configured either as inputs or outputs, depending on the application.

Configure CLK and FS as inputs or outputs Multi-Channel Buffered Serial Port (Mc. BSP) CLKR CLKX FSR FSX Serial Port Control Logic SPCR RCR SRGR XCR PCR CLK/FS Mode 0: Input 1: Output Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 17 11 10 9 8 FSXM FSRM CLKXM CLKRM

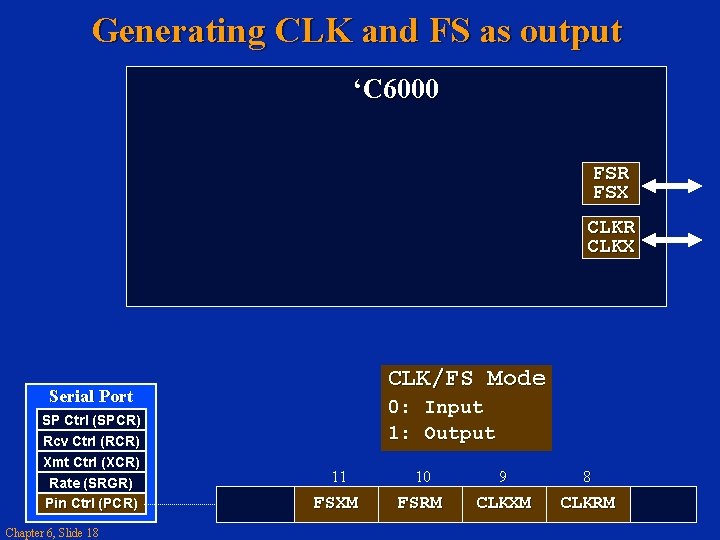

Generating CLK and FS as output ‘C 6000 FSR FSX CLKR CLKX CLK/FS Mode Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 18 0: Input 1: Output 11 10 9 8 FSXM FSRM CLKXM CLKRM

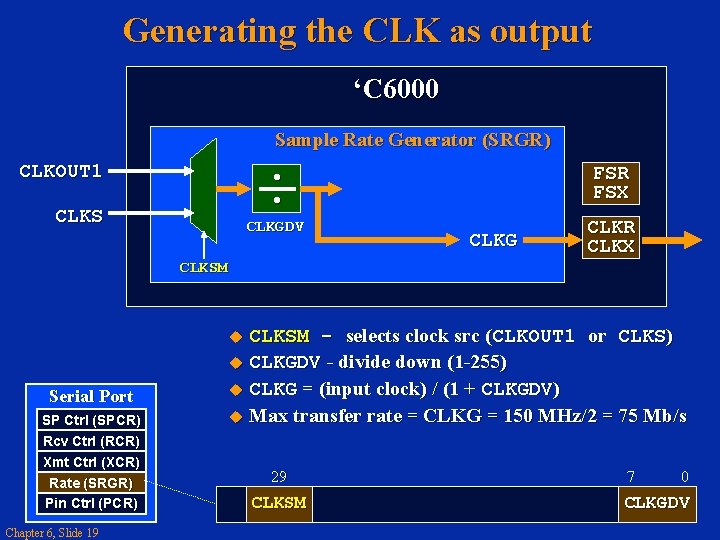

Generating the CLK as output ‘C 6000 Sample Rate Generator (SRGR) CLKOUT 1 FSR FSX CLKS CLKGDV CLKSM CLKG CLKR CLKX - selects clock src (CLKOUT 1 or CLKS) CLKGDV - divide down (1 -255) CLKG = (input clock) / (1 + CLKGDV) Max transfer rate = CLKG = 150 MHz/2 = 75 Mb/s CLKSM Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 19 29 CLKSM 7 0 CLKGDV

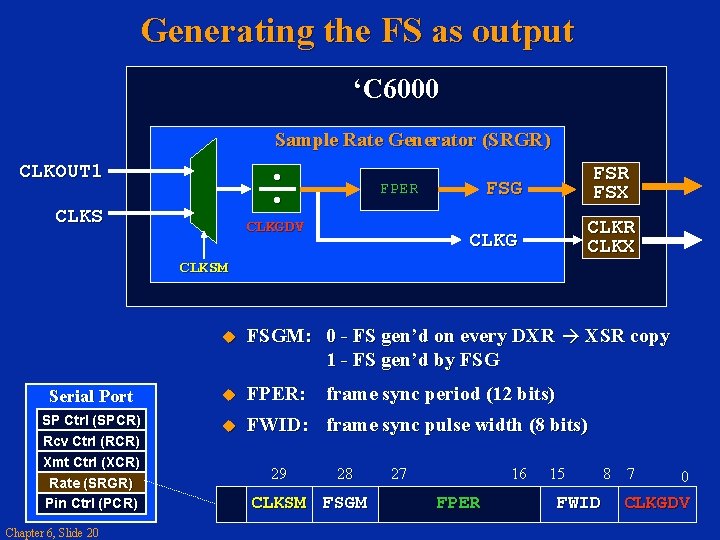

Generating the FS as output ‘C 6000 Sample Rate Generator (SRGR) CLKOUT 1 CLKS FSG FSR FSX CLKG CLKR CLKX FPER CLKGDV CLKSM FSGM: 0 - FS gen’d on every DXR à XSR copy 1 - FS gen’d by FSG Serial Port FPER: frame sync period (12 bits) SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) FWID: frame sync pulse width (8 bits) Chapter 6, Slide 20 29 28 CLKSM FSGM 27 16 FPER 15 FWID 8 7 0 CLKGDV

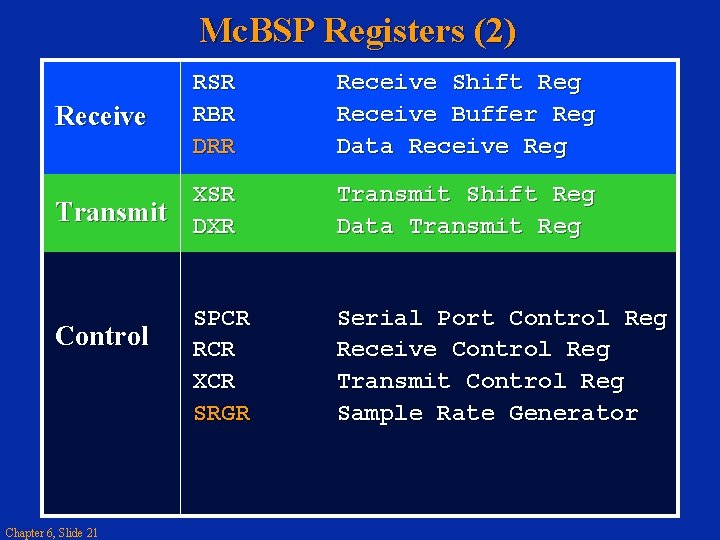

Mc. BSP Registers (2) Receive RSR RBR DRR Receive Shift Reg Receive Buffer Reg Data Receive Reg Transmit XSR DXR Transmit Shift Reg Data Transmit Reg SPCR RCR XCR SRGR Serial Port Control Reg Receive Control Reg Transmit Control Reg Sample Rate Generator Control Chapter 6, Slide 21

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 22

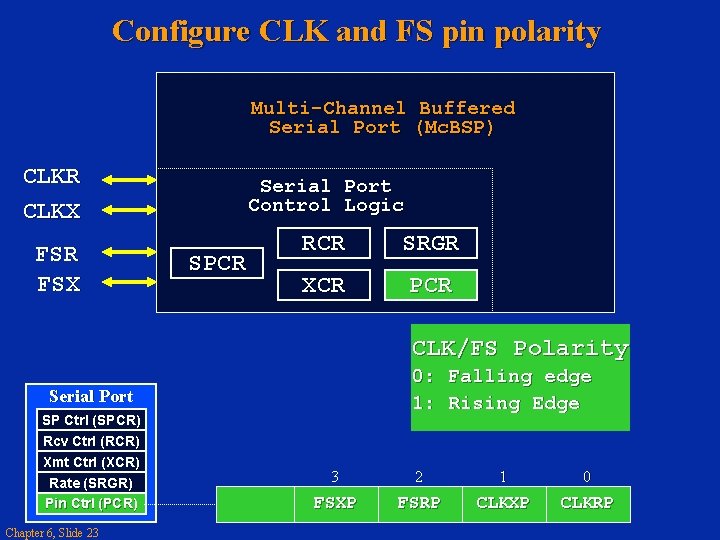

Configure CLK and FS pin polarity Multi-Channel Buffered Serial Port (Mc. BSP) CLKR CLKX FSR FSX Serial Port Control Logic SPCR RCR SRGR XCR PCR CLK/FS Polarity 0: Falling edge 1: Rising Edge Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 23 3 2 1 0 FSXP FSRP CLKXP CLKRP

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port status and interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 24

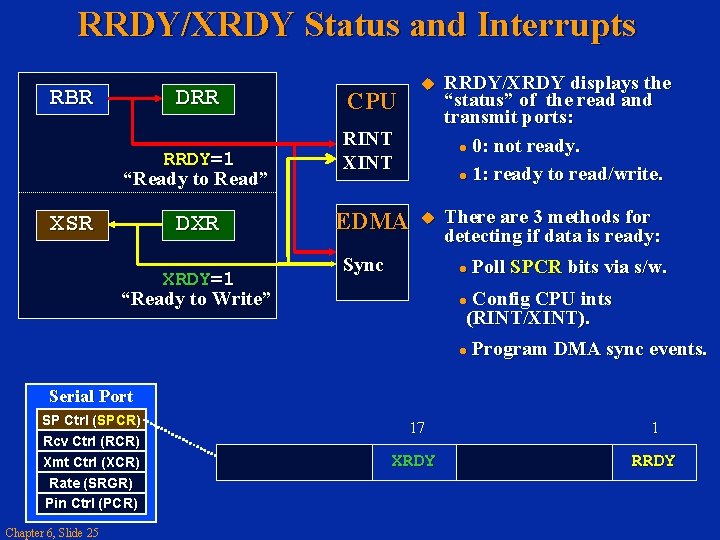

RRDY/XRDY Status and Interrupts RBR DRR RRDY=1 “Ready to Read” XSR DXR XRDY=1 “Ready to Write” CPU RRDY/XRDY displays the “status” of the read and transmit ports: l 0: not ready. l 1: ready to read/write. There are 3 methods for detecting if data is ready: RINT XINT EDMA Sync l Poll SPCR bits via s/w. Config CPU ints (RINT/XINT). l l Program DMA sync events. Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 25 17 1 XRDY RRDY

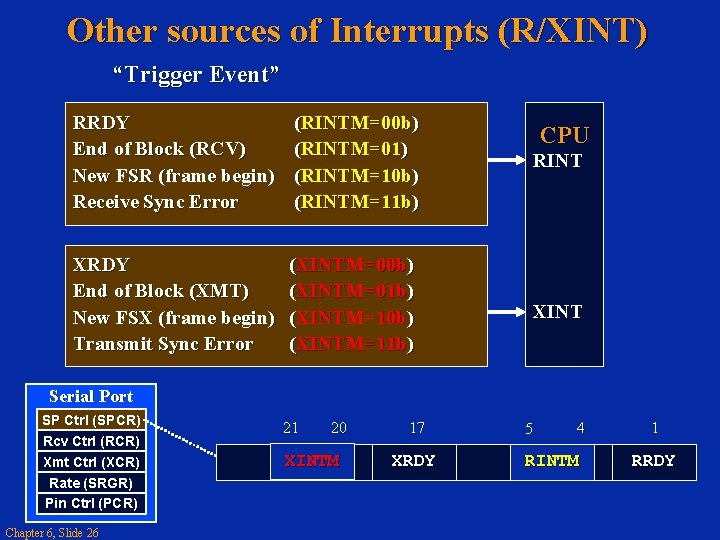

Other sources of Interrupts (R/XINT) “Trigger Event” RRDY End of Block (RCV) New FSR (frame begin) Receive Sync Error (RINTM=00 b) (RINTM=01) (RINTM=10 b) (RINTM=11 b) RINT XRDY End of Block (XMT) New FSX (frame begin) Transmit Sync Error (XINTM=00 b) (XINTM=01 b) (XINTM=10 b) (XINTM=11 b) XINT CPU Serial Port SP Ctrl (SPCR) Rcv Ctrl (RCR) Xmt Ctrl (XCR) Rate (SRGR) Pin Ctrl (PCR) Chapter 6, Slide 26 21 20 XINTM 17 XRDY 5 4 RINTM 1 RRDY

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port status and interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 27

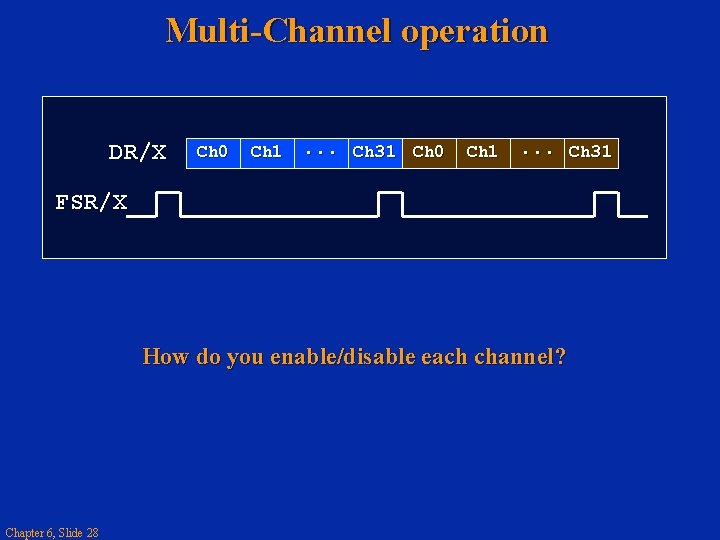

Multi-Channel operation DR/X Ch 0 Ch 1 . . . Ch 31 Ch 0 Ch 1 . . . FSR/X How do you enable/disable each channel? Chapter 6, Slide 28 Ch 31

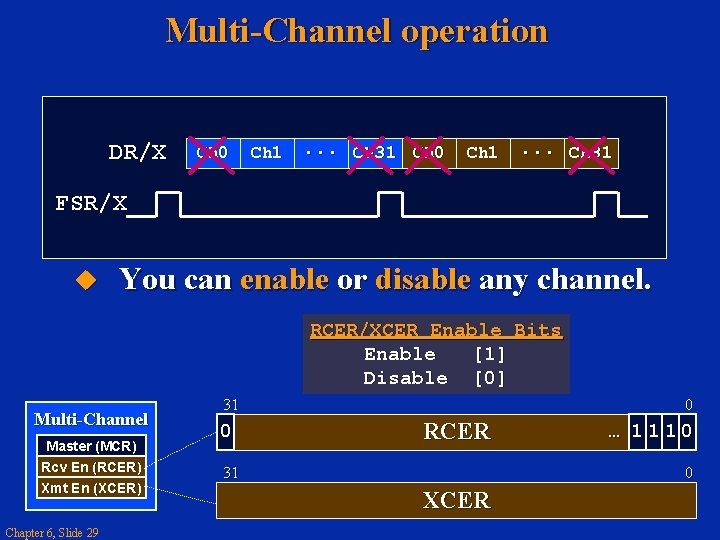

Multi-Channel operation DR/X Ch 0 Ch 1 . . . Ch 31 FSR/X You can enable or disable any channel. RCER/XCER Enable Bits Enable [1] Disable [0] Multi-Channel Master (MCR) Rcv En (RCER) Xmt En (XCER) Chapter 6, Slide 29 31 0 0 RCER 31 … 1110 0 XCER

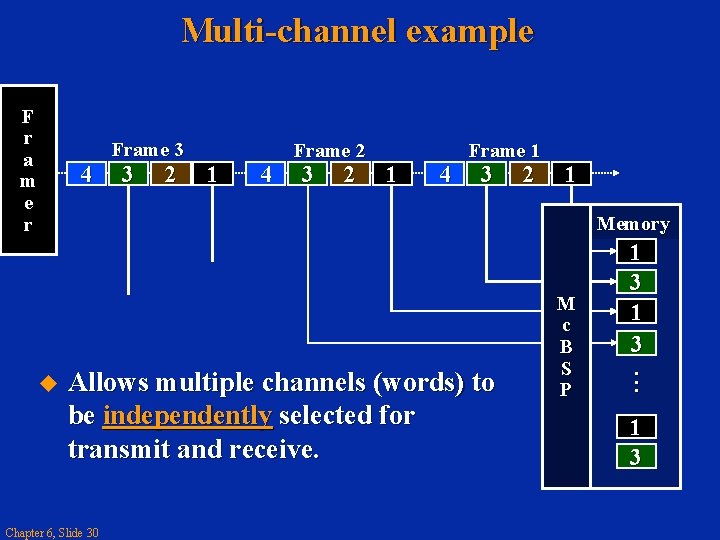

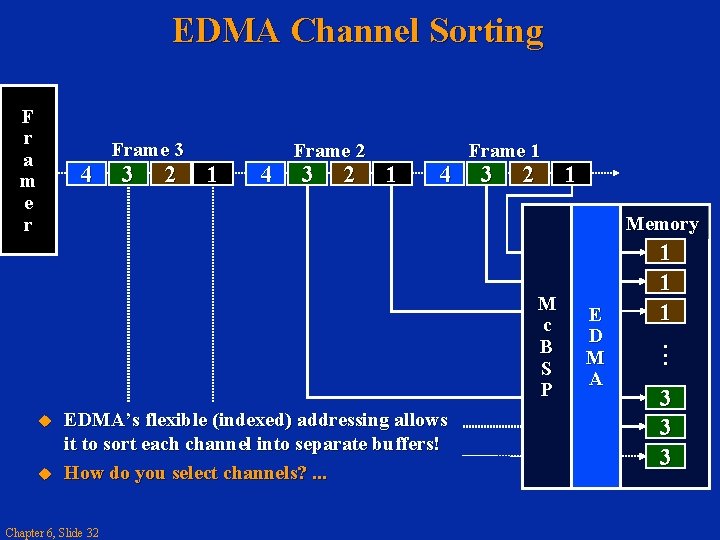

Multi-channel example F r a m e r 4 Frame 3 3 2 1 4 Frame 2 3 2 1 4 Frame 1 3 2 1 Memory Allows multiple channels (words) to be independently selected for transmit and receive. Chapter 6, Slide 30 M c B S P 1 3. . . 1 3

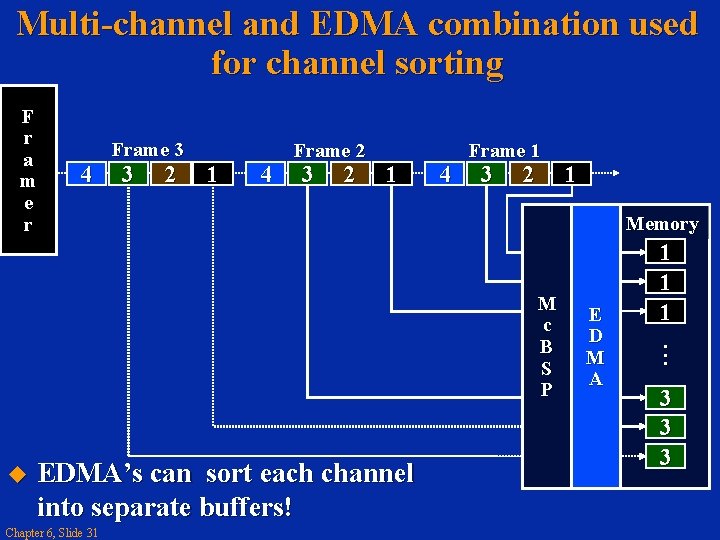

Multi-channel and EDMA combination used for channel sorting F r a m e r 4 Frame 3 3 2 1 4 Frame 2 3 2 1 4 Frame 1 3 2 Memory M c B S P EDMA’s can sort each channel into separate buffers! Chapter 6, Slide 31 1 E D M A 1 1 1. . . 3 3 3

EDMA Channel Sorting F r a m e r 4 Frame 3 3 2 1 4 Frame 2 3 2 1 4 Frame 1 3 2 1 Memory M c B S P EDMA’s flexible (indexed) addressing allows it to sort each channel into separate buffers! How do you select channels? . . . Chapter 6, Slide 32 E D M A 1 1 1. . . 3 3 3

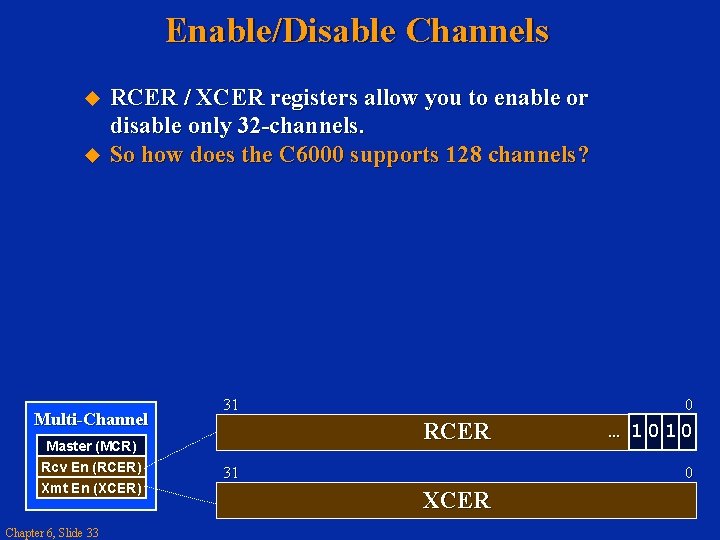

Enable/Disable Channels RCER / XCER registers allow you to enable or disable only 32 -channels. So how does the C 6000 supports 128 channels? Multi-Channel Master (MCR) Rcv En (RCER) Xmt En (XCER) Chapter 6, Slide 33 31 0 RCER 31 … 1010 0 XCER

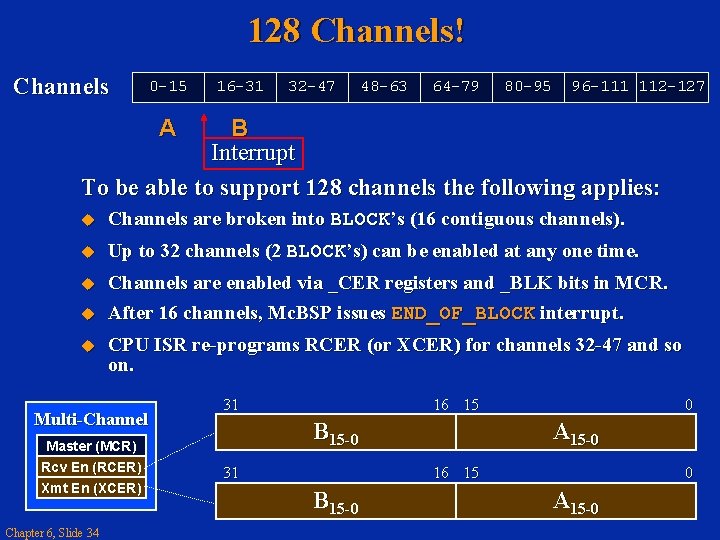

128 Channels! Channels 0 -15 16 -31 32 -47 48 -63 64 -79 80 -95 96 -111 112 -127 A B Interrupt To be able to support 128 channels the following applies: Channels are broken into BLOCK’s (16 contiguous channels). Up to 32 channels (2 BLOCK’s) can be enabled at any one time. Channels are enabled via _CER registers and _BLK bits in MCR. After 16 channels, Mc. BSP issues END_OF_BLOCK interrupt. CPU ISR re-programs RCER (or XCER) for channels 32 -47 and so on. Multi-Channel Master (MCR) Rcv En (RCER) Xmt En (XCER) Chapter 6, Slide 34 16 15 31 B 15 -0 RCER 0 A 15 -0 16 15 31 B 15 -0 XCER 0 A 15 -0

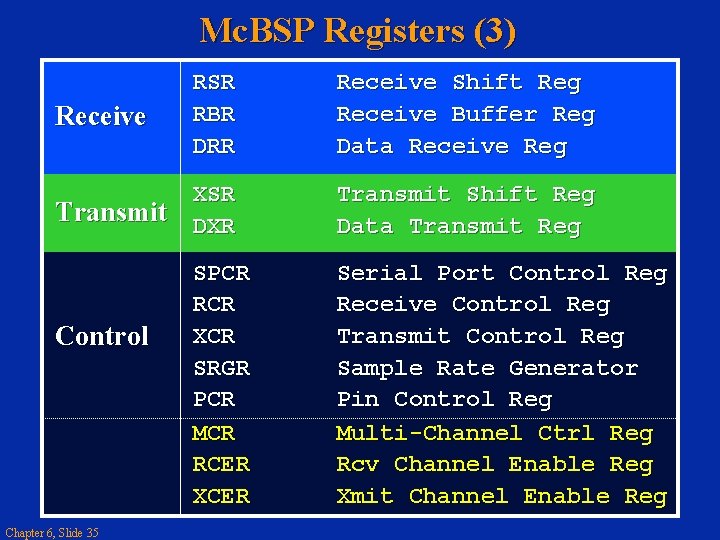

Mc. BSP Registers (3) Receive RSR RBR DRR Receive Shift Reg Receive Buffer Reg Data Receive Reg Transmit XSR DXR Transmit Shift Reg Data Transmit Reg SPCR RCR XCR SRGR PCR MCR RCER XCER Serial Port Control Reg Receive Control Reg Transmit Control Reg Sample Rate Generator Pin Control Reg Multi-Channel Ctrl Reg Rcv Channel Enable Reg Xmit Channel Enable Reg Control Chapter 6, Slide 35

Objectives Definition of Terms: w Bit, word or channel, frame and phase. Understand basic serial port operation. Understand clock generation. Pin polarity. Serial port status and interrupts. Describe multi-channel operation. Programming the serial port. Chapter 6, Slide 36

Programming the Serial Port There are three methods available for programming the serial port: 1. Writing directly to the serial port registers. 2. Using the Chip Support Library (CSL). 3. Graphically using the DSP/BIOS GUI configuration tool. Chapter 6, Slide 37

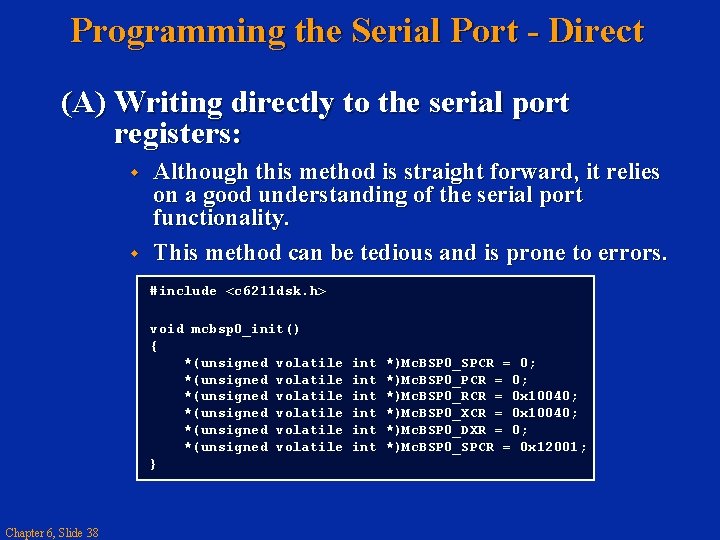

Programming the Serial Port - Direct (A) Writing directly to the serial port registers: w w Although this method is straight forward, it relies on a good understanding of the serial port functionality. This method can be tedious and is prone to errors. #include <c 6211 dsk. h> void mcbsp 0_init() { *(unsigned volatile *(unsigned volatile } Chapter 6, Slide 38 int int int *)Mc. BSP 0_SPCR = 0; *)Mc. BSP 0_RCR = 0 x 10040; *)Mc. BSP 0_XCR = 0 x 10040; *)Mc. BSP 0_DXR = 0; *)Mc. BSP 0_SPCR = 0 x 12001;

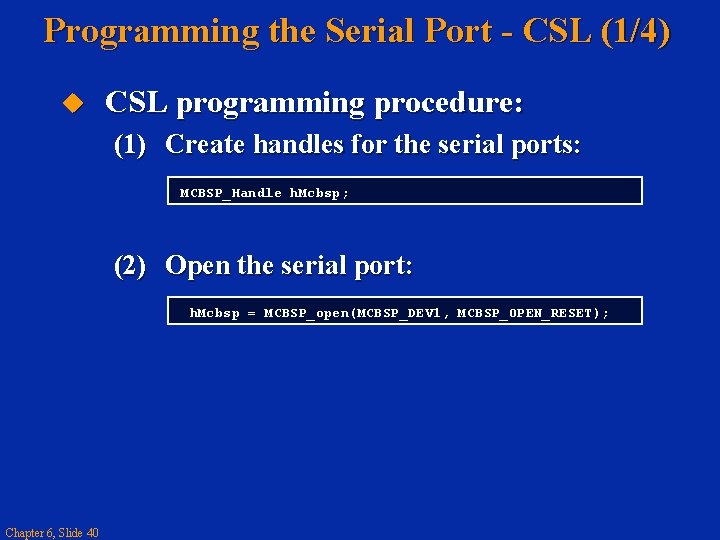

Programming the Serial Port - CSL (1/4) (B) Using the Chip Support Library: w w w Chapter 6, Slide 39 The CSL provides a C language interface for configuring and controlling the on-chip peripherals, in this case the Serial Ports. The library is modular with each module corresponding to a specific peripheral. This has the advantage of reducing the code size. Some modules rely on other modules also being included, for example the IRQ module is required when using the EDMA module.

Programming the Serial Port - CSL (1/4) CSL programming procedure: (1) Create handles for the serial ports: MCBSP_Handle h. Mcbsp; (2) Open the serial port: h. Mcbsp = MCBSP_open(MCBSP_DEV 1, MCBSP_OPEN_RESET); Chapter 6, Slide 40

Programming the Serial Port - CSL (2/4) CSL programming procedure: (3) Create a configuration structure for serial port: w Chapter 6, Slide 41 LinksMc. BSP_Config_Struct. pdf

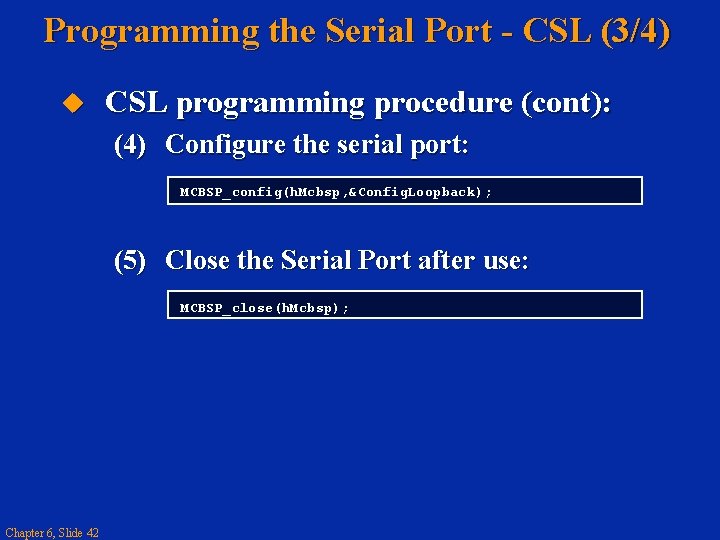

Programming the Serial Port - CSL (3/4) CSL programming procedure (cont): (4) Configure the serial port: MCBSP_config(h. Mcbsp, &Config. Loopback); (5) Close the Serial Port after use: MCBSP_close(h. Mcbsp); Chapter 6, Slide 42

Programming the Serial Port - CSL (4/4) Practical example on DSP Code 6711 Project name: mcbsp_dynamiccfg. pjt Location: CodeChapter 06 - Mc. BSPDynamic_CSL_Config Chapter 6, Slide 43

Programming the Serial Port using the DSP/BIOS GUI (C) DSP/BIOS GUI Interface: w Chapter 6, Slide 44 With this method the configuration structure is created graphically and the setup code is generated automatically.

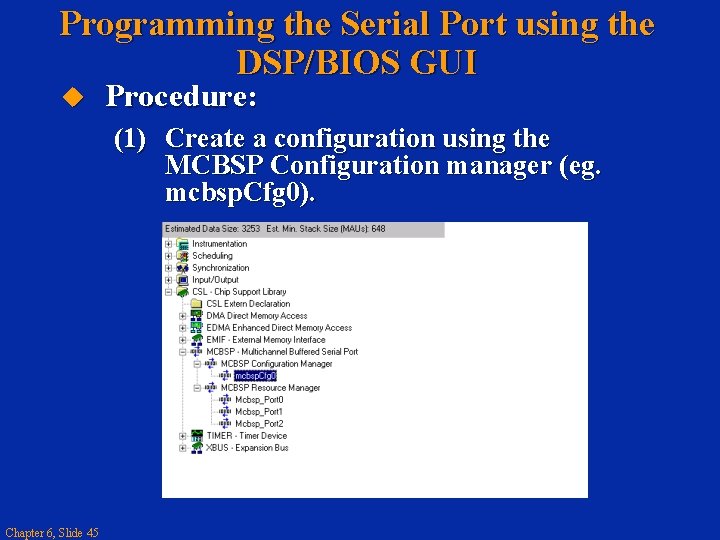

Programming the Serial Port using the DSP/BIOS GUI Procedure: (1) Create a configuration using the MCBSP Configuration manager (eg. mcbsp. Cfg 0). Chapter 6, Slide 45

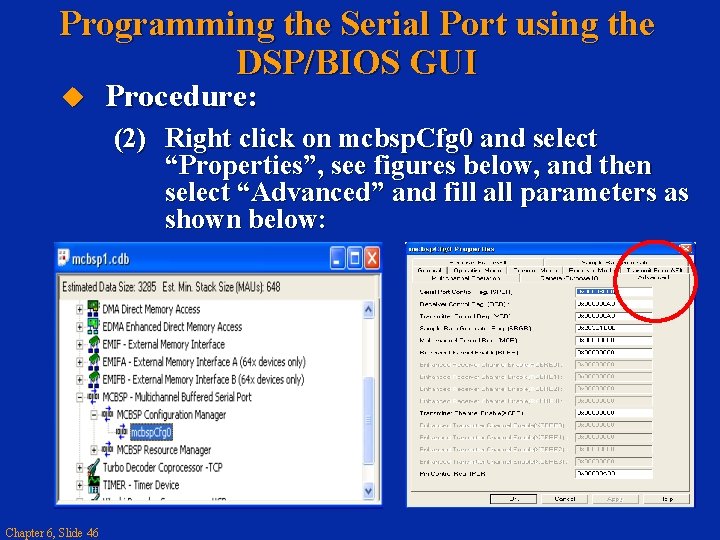

Programming the Serial Port using the DSP/BIOS GUI Procedure: (2) Right click on mcbsp. Cfg 0 and select “Properties”, see figures below, and then select “Advanced” and fill all parameters as shown below: Chapter 6, Slide 46

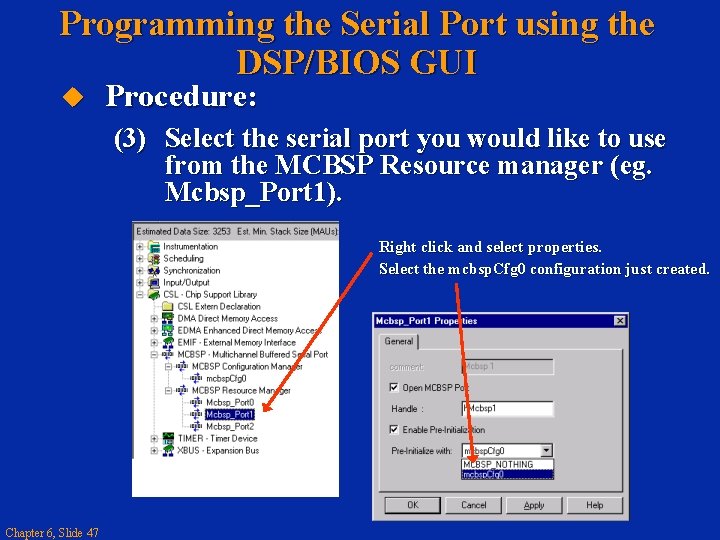

Programming the Serial Port using the DSP/BIOS GUI Procedure: (3) Select the serial port you would like to use from the MCBSP Resource manager (eg. Mcbsp_Port 1). Right click and select properties. Select the mcbsp. Cfg 0 configuration just created. Chapter 6, Slide 47

Programming the Serial Port using the DSP/BIOS GUI Procedure: (4) A file is then generated that contains the configuration code. The file generated for this example is shown on the next slide. Chapter 6, Slide 48

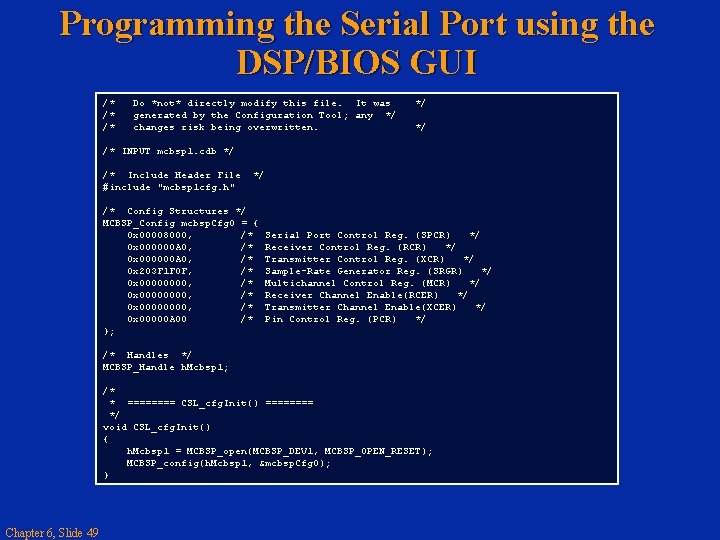

Programming the Serial Port using the DSP/BIOS GUI /* /* /* Do *not* directly modify this file. It was generated by the Configuration Tool; any */ changes risk being overwritten. */ */ /* INPUT mcbsp 1. cdb */ /* Include Header File #include "mcbsp 1 cfg. h" */ /* Config Structures */ MCBSP_Config mcbsp. Cfg 0 = { 0 x 00008000, /* 0 x 000000 A 0, /* 0 x 203 F 1 F 0 F, /* 0 x 00000000, /* 0 x 00000 A 00 /* }; Serial Port Control Reg. (SPCR) */ Receiver Control Reg. (RCR) */ Transmitter Control Reg. (XCR) */ Sample-Rate Generator Reg. (SRGR) */ Multichannel Control Reg. (MCR) */ Receiver Channel Enable(RCER) */ Transmitter Channel Enable(XCER) */ Pin Control Reg. (PCR) */ /* Handles */ MCBSP_Handle h. Mcbsp 1; /* * ==== CSL_cfg. Init() ==== */ void CSL_cfg. Init() { h. Mcbsp 1 = MCBSP_open(MCBSP_DEV 1, MCBSP_OPEN_RESET); MCBSP_config(h. Mcbsp 1, &mcbsp. Cfg 0); } Chapter 6, Slide 49

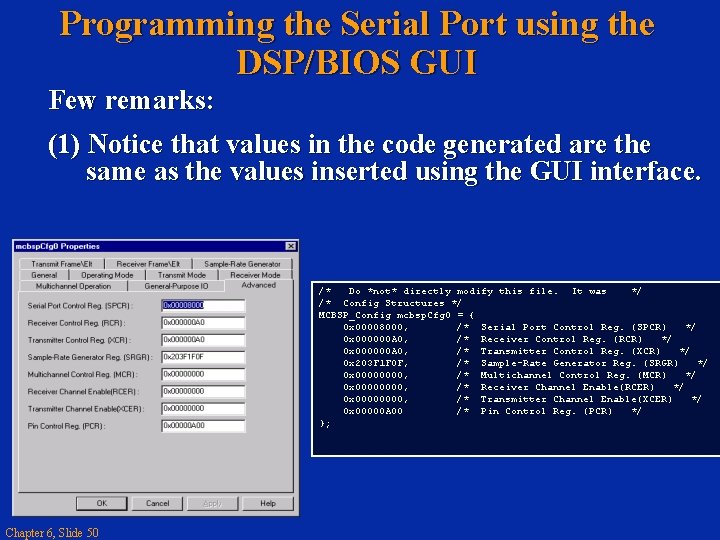

Programming the Serial Port using the DSP/BIOS GUI Few remarks: (1) Notice that values in the code generated are the same as the values inserted using the GUI interface. /* Do *not* directly modify this file. It was */ /* Config Structures */ MCBSP_Config mcbsp. Cfg 0 = { 0 x 00008000, /* Serial Port Control Reg. (SPCR) */ 0 x 000000 A 0, /* Receiver Control Reg. (RCR) */ 0 x 000000 A 0, /* Transmitter Control Reg. (XCR) */ 0 x 203 F 1 F 0 F, /* Sample-Rate Generator Reg. (SRGR) */ 0 x 0000, /* Multichannel Control Reg. (MCR) */ 0 x 0000, /* Receiver Channel Enable(RCER) */ 0 x 0000, /* Transmitter Channel Enable(XCER) */ 0 x 00000 A 00 /* Pin Control Reg. (PCR) */ }; Chapter 6, Slide 50

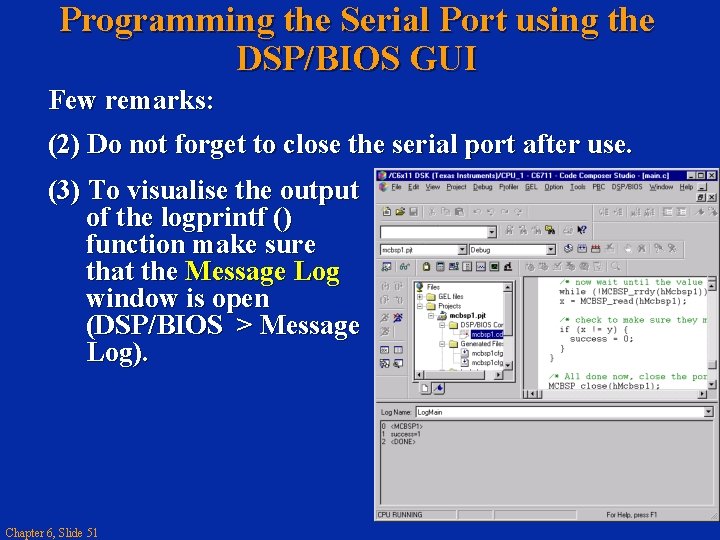

Programming the Serial Port using the DSP/BIOS GUI Few remarks: (2) Do not forget to close the serial port after use. (3) To visualise the output of the logprintf () function make sure that the Message Log window is open (DSP/BIOS > Message Log). Chapter 6, Slide 51

Programming the Serial Port - CSL (4/4) Practical example Chapter 6, Slide 52 Project name: mcbsp_staticcfg. pjt Location: CodeChapter 06 - Mc. BSPStatic_CSL_Config Extra Topic: Digital Loopback

Chapter 6 Multi-channel Buffered Serial Port (Mc. BSP) - End -

- Slides: 52