Chapter 6 II Designing Combinational Logic Circuits II

Chapter 6 (II) Designing Combinational Logic Circuits (II) • Dynamic CMOS Logic V 1. 0 5/4/2003 V 1. 1 5/11/2003 V 1. 2 5/15/2003 1 EE 141 Combinational Circu

Revision Chronicle q 5/4: § Split Chapter 6 into two parts: Part I focuses on Static and Pass Transistor Logic. Part II focuses on Dynamic Logic q 5/11: § Make minor revision in figures and adding the summary. q 5/11: § Make minor revision in figures and equations 2 EE 141 Combinational Circu

Dynamic CMOS q In Static CMOS circuits, at every point in time (except when switching), the output is connected to either GND or VDD via a low resistance path. § Fan-in of n requires 2 n (n NMOS plus n PMOS) devices q Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes. § Requires on n + 2 (n+1 NMOS plus 1 PMOS) transistors 3 EE 141 Combinational Circu

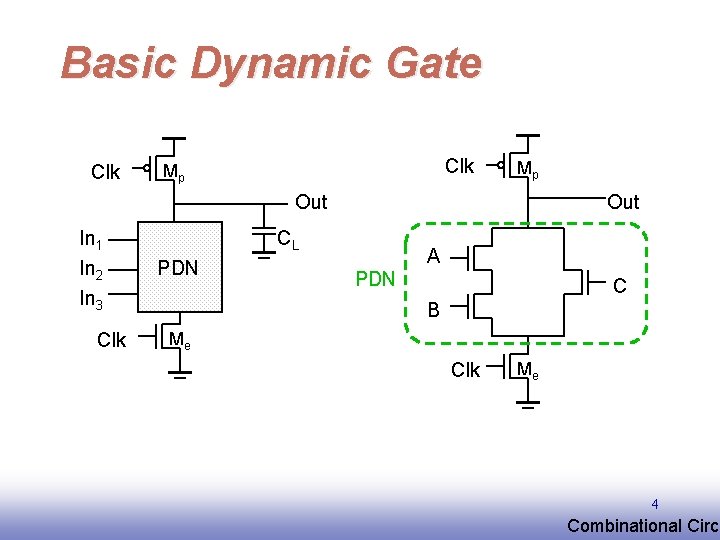

Basic Dynamic Gate Clk Mp Mp Out In 1 In 2 In 3 Clk Out CL PDN A PDN C B Me Clk Me 4 EE 141 Combinational Circu

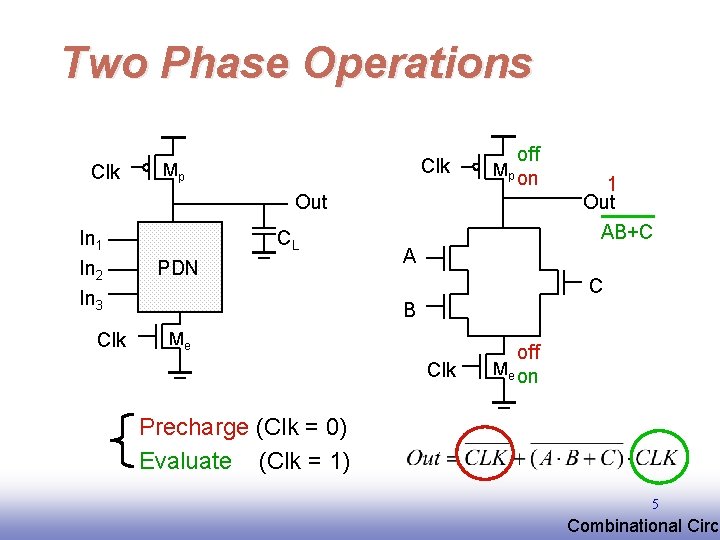

Two Phase Operations Clk Mp Mp off on Out In 1 In 2 In 3 Clk CL PDN 1 Out AB+C A C B Me Clk off Me on Precharge (Clk = 0) Evaluate (Clk = 1) 5 EE 141 Combinational Circu

Conditions on Output q Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation (one chance only). q Inputs to the gate can make at most one transition during evaluation. q Output can be in the high impedance state during the evaluation phase (PDN off), state is stored on CL Different from Static CMOS Output is connected to Either Vdd or GND through low-resistance path. 6 EE 141 Combinational Circu

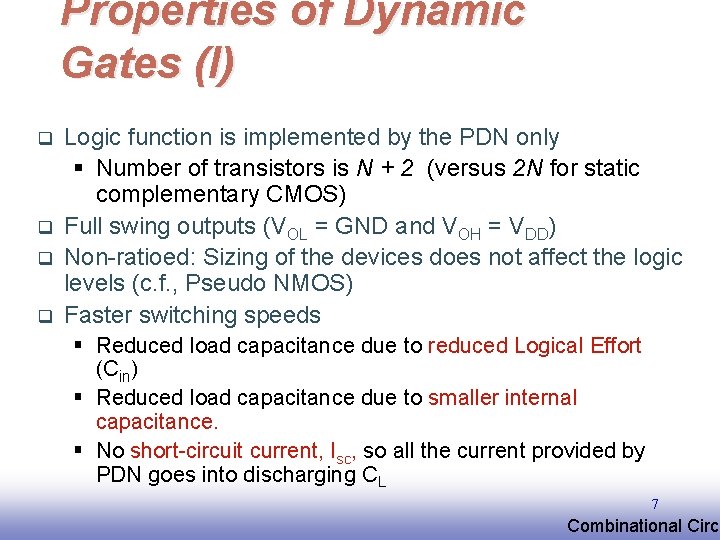

Properties of Dynamic Gates (I) q q Logic function is implemented by the PDN only § Number of transistors is N + 2 (versus 2 N for static complementary CMOS) Full swing outputs (VOL = GND and VOH = VDD) Non-ratioed: Sizing of the devices does not affect the logic levels (c. f. , Pseudo NMOS) Faster switching speeds § Reduced load capacitance due to reduced Logical Effort (Cin) § Reduced load capacitance due to smaller internal capacitance. § No short-circuit current, Isc, so all the current provided by PDN goes into discharging CL 7 EE 141 Combinational Circu

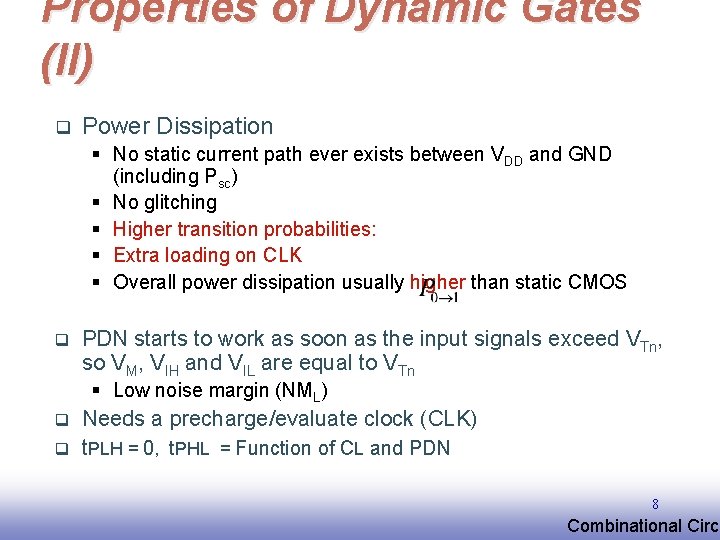

Properties of Dynamic Gates (II) q Power Dissipation § No static current path ever exists between VDD and GND (including Psc) § No glitching § Higher transition probabilities: § Extra loading on CLK § Overall power dissipation usually higher than static CMOS q PDN starts to work as soon as the input signals exceed VTn, so VM, VIH and VIL are equal to VTn § Low noise margin (NML) q q Needs a precharge/evaluate clock (CLK) t. PLH = 0, t. PHL = Function of CL and PDN 8 EE 141 Combinational Circu

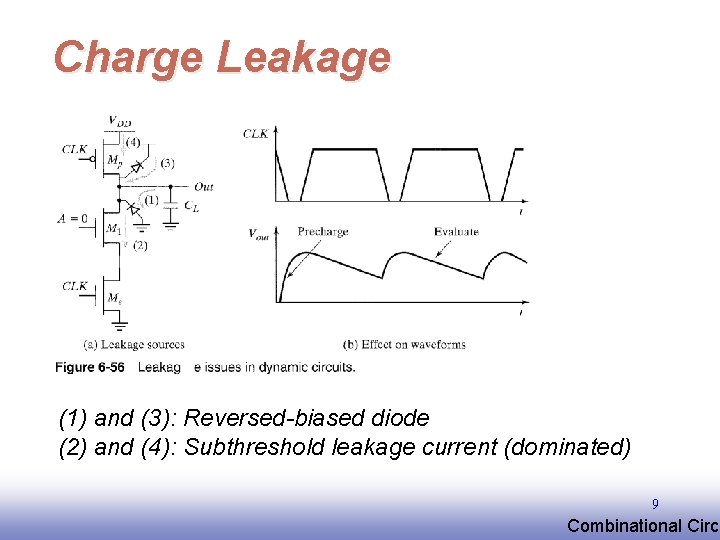

Charge Leakage (1) and (3): Reversed-biased diode (2) and (4): Subthreshold leakage current (dominated) 9 EE 141 Combinational Circu

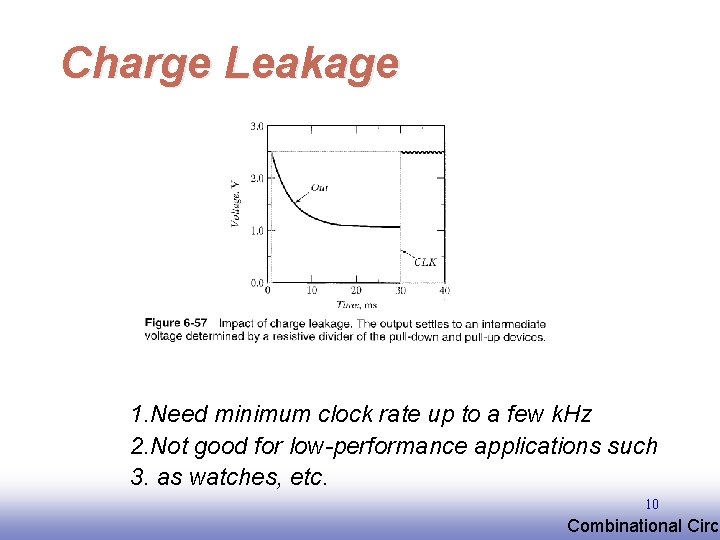

Charge Leakage 1. Need minimum clock rate up to a few k. Hz 2. Not good for low-performance applications such 3. as watches, etc. 10 EE 141 Combinational Circu

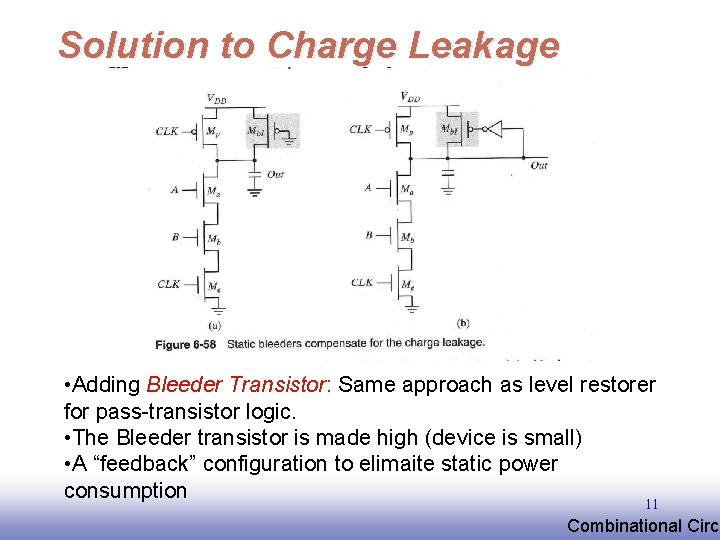

Solution to Charge Leakage • Adding Bleeder Transistor: Same approach as level restorer for pass-transistor logic. • The Bleeder transistor is made high (device is small) • A “feedback” configuration to elimaite static power consumption 11 EE 141 Combinational Circu

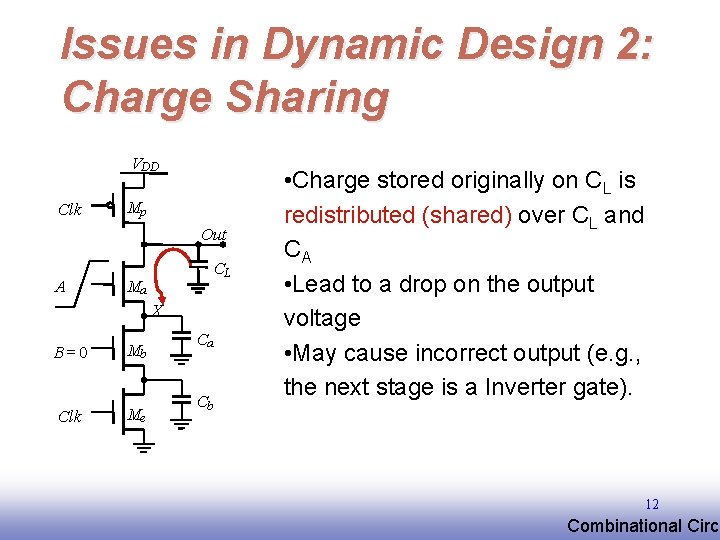

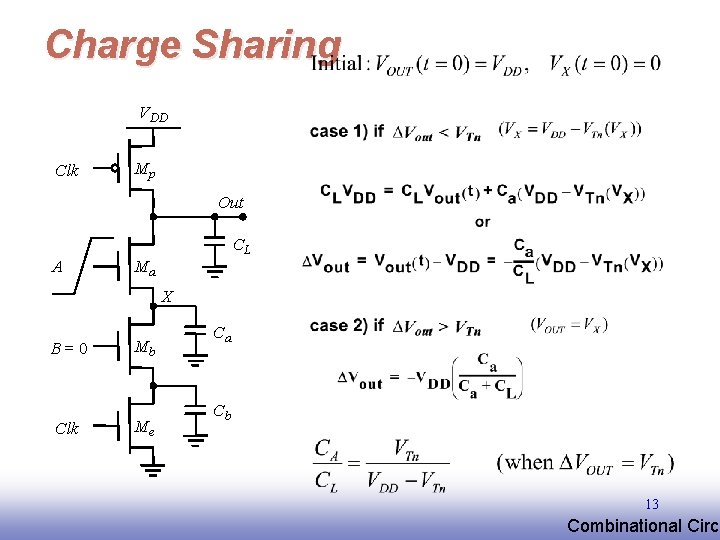

Issues in Dynamic Design 2: Charge Sharing VDD Clk Mp Out A CL Ma X B=0 Mb Clk Me Ca Cb • Charge stored originally on CL is redistributed (shared) over CL and CA • Lead to a drop on the output voltage • May cause incorrect output (e. g. , the next stage is a Inverter gate). 12 EE 141 Combinational Circu

Charge Sharing VDD Clk Mp Out CL A Ma X B=0 Clk Mb Me Ca Cb 13 EE 141 Combinational Circu

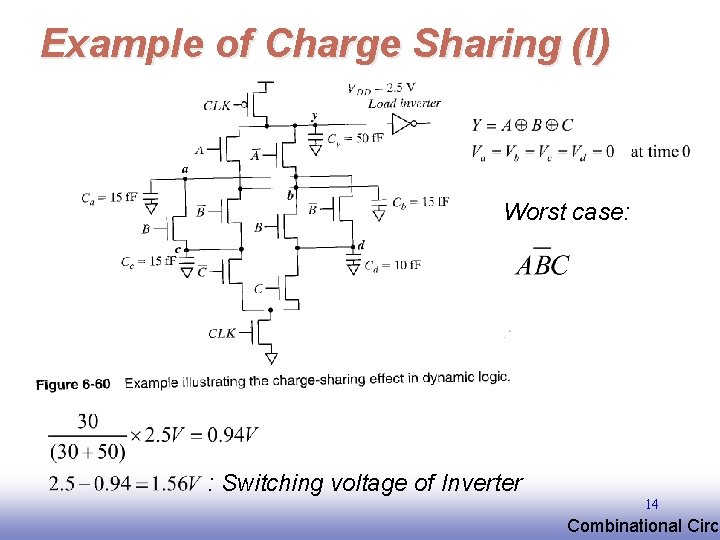

Example of Charge Sharing (I) Worst case: : Switching voltage of Inverter 14 EE 141 Combinational Circu

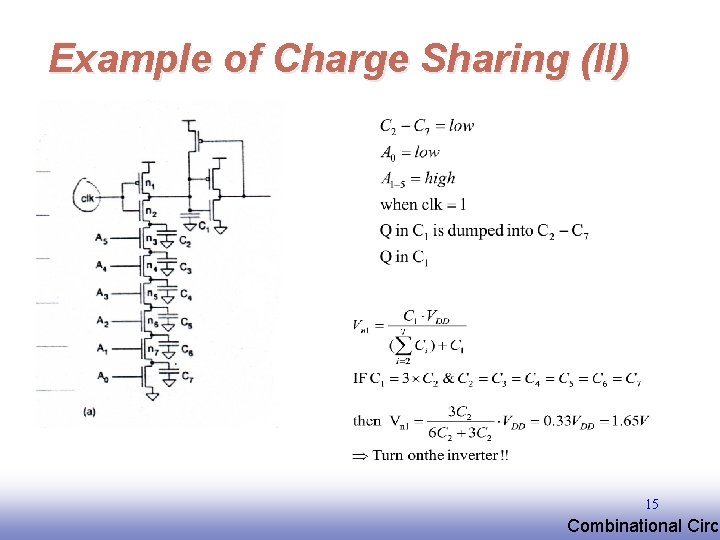

Example of Charge Sharing (II) 15 EE 141 Combinational Circu

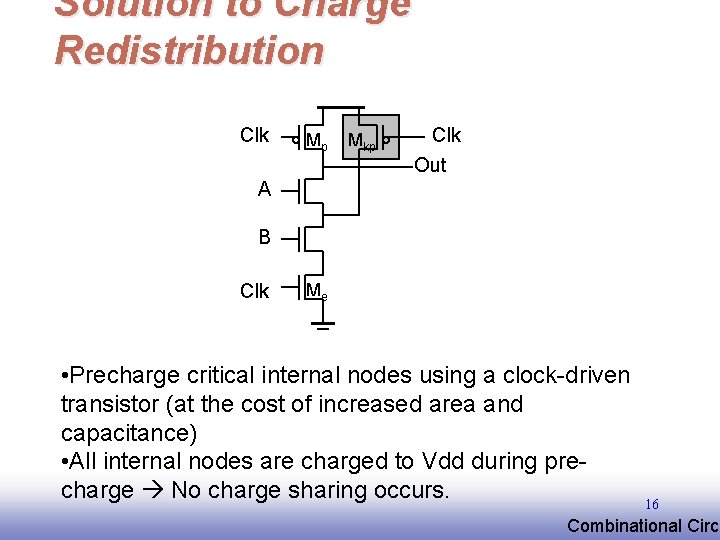

Solution to Charge Redistribution Clk Mp Mkp Clk Out A B Clk Me • Precharge critical internal nodes using a clock-driven transistor (at the cost of increased area and capacitance) • All internal nodes are charged to Vdd during precharge No charge sharing occurs. EE 141 16 Combinational Circu

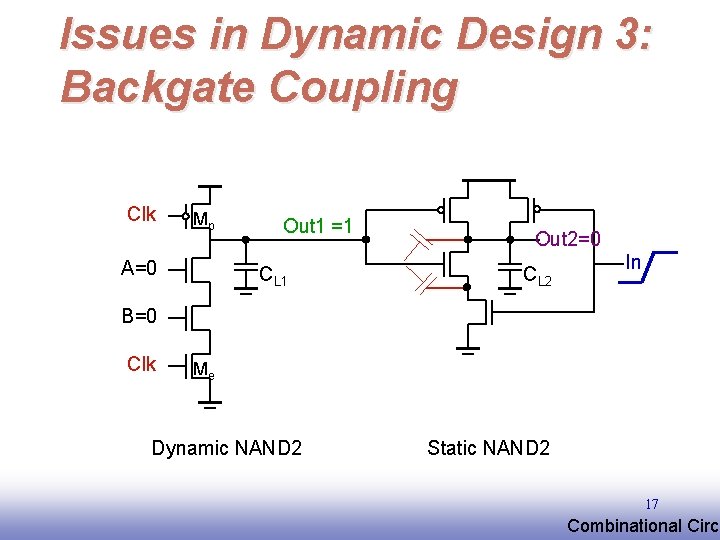

Issues in Dynamic Design 3: Backgate Coupling Clk Mp A=0 Out 1 =1 CL 1 Out 2=0 CL 2 In B=0 Clk Me Dynamic NAND 2 Static NAND 2 17 EE 141 Combinational Circu

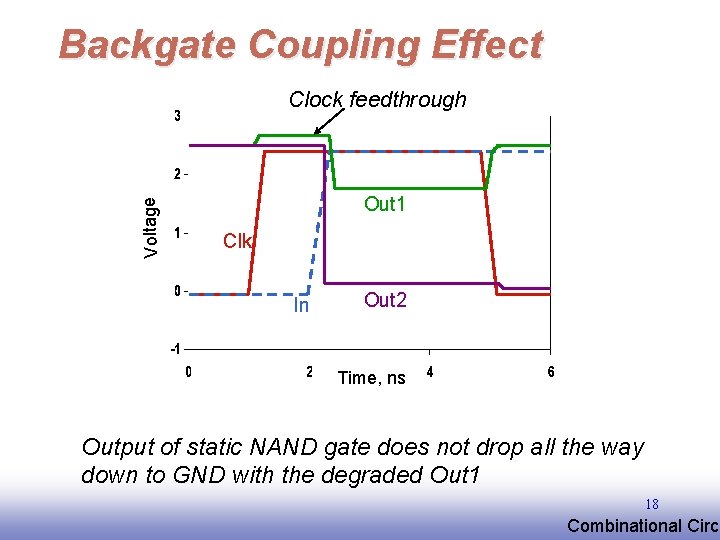

Backgate Coupling Effect Voltage Clock feedthrough Out 1 Clk In Out 2 Time, ns Output of static NAND gate does not drop all the way down to GND with the degraded Out 1 18 EE 141 Combinational Circu

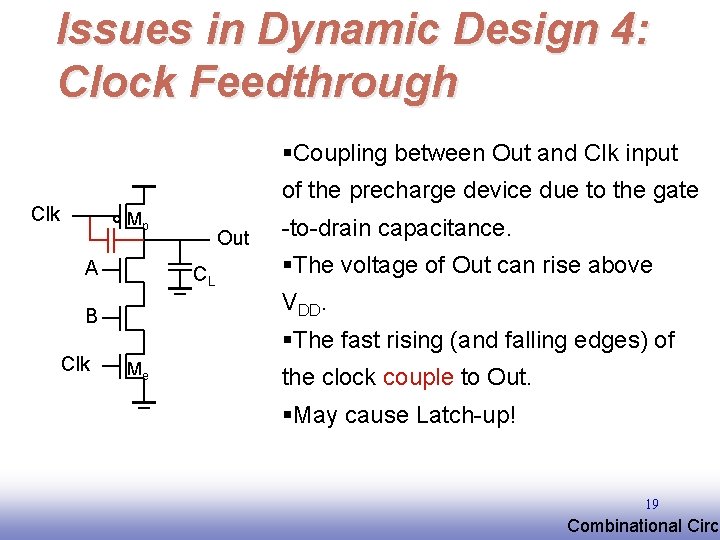

Issues in Dynamic Design 4: Clock Feedthrough §Coupling between Out and Clk input of the precharge device due to the gate Clk Mp A CL B Clk Out -to-drain capacitance. §The voltage of Out can rise above VDD. §The fast rising (and falling edges) of Me the clock couple to Out. §May cause Latch-up! 19 EE 141 Combinational Circu

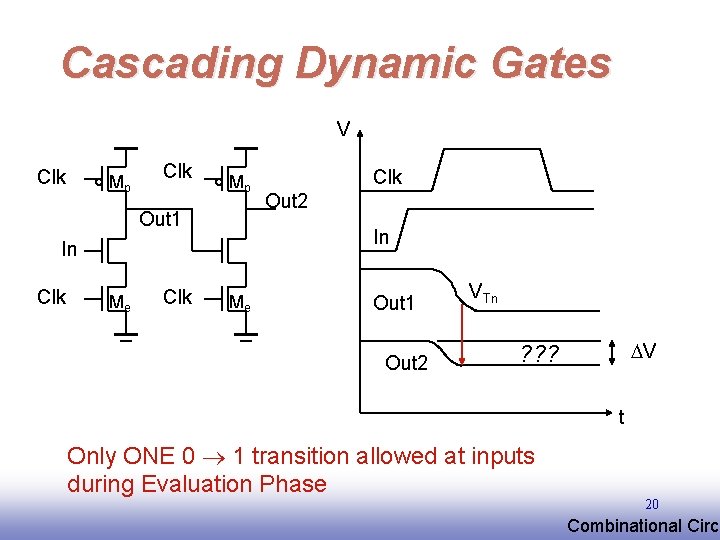

Cascading Dynamic Gates V Clk Mp Out 1 Me Clk Out 2 In In Clk Me Out 1 Out 2 VTn V ? ? ? t Only ONE 0 1 transition allowed at inputs during Evaluation Phase EE 141 20 Combinational Circu

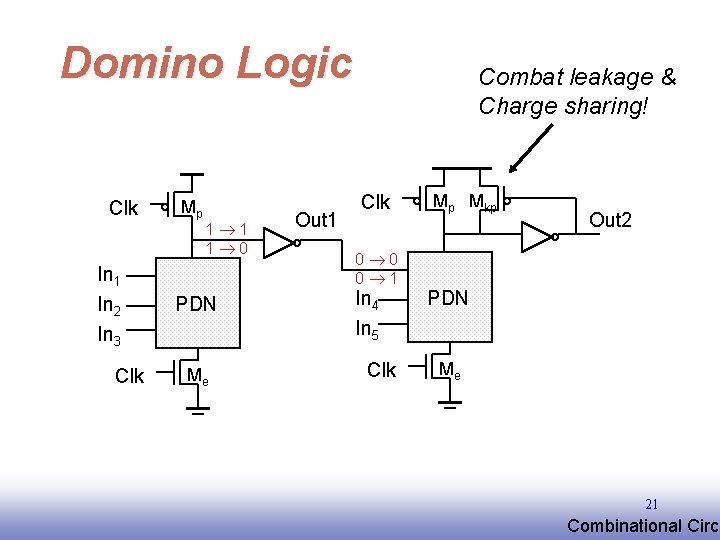

Domino Logic Clk In 1 In 2 In 3 Clk Mp 1 1 1 0 PDN Me Out 1 Combat leakage & Charge sharing! Clk 0 0 0 1 In 4 In 5 Clk Mp Mkp Out 2 PDN Me 21 EE 141 Combinational Circu

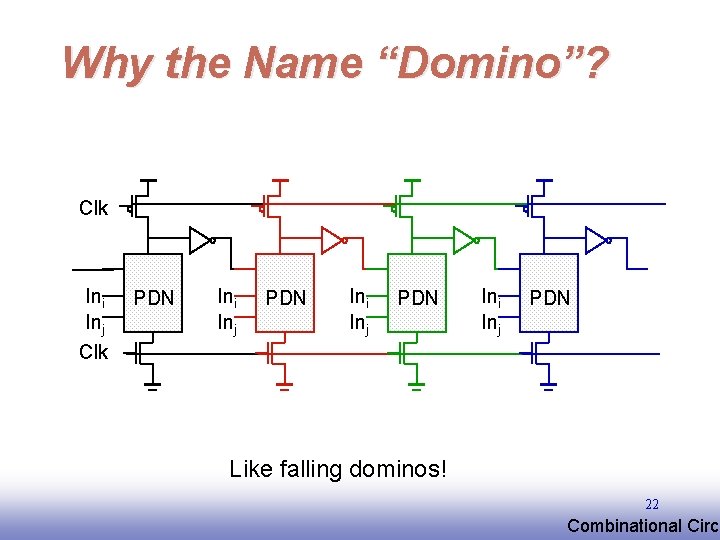

Why the Name “Domino”? Clk Ini Inj Clk PDN Ini Inj PDN Like falling dominos! 22 EE 141 Combinational Circu

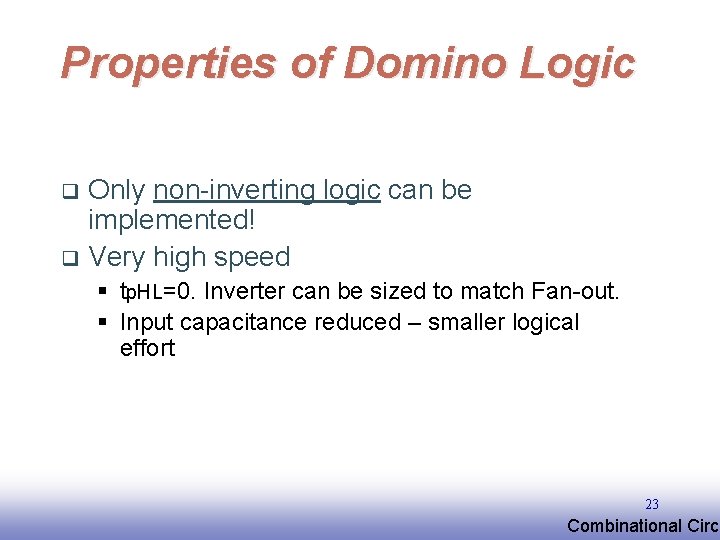

Properties of Domino Logic Only non-inverting logic can be implemented! q Very high speed q § tp. HL=0. Inverter can be sized to match Fan-out. § Input capacitance reduced – smaller logical effort 23 EE 141 Combinational Circu

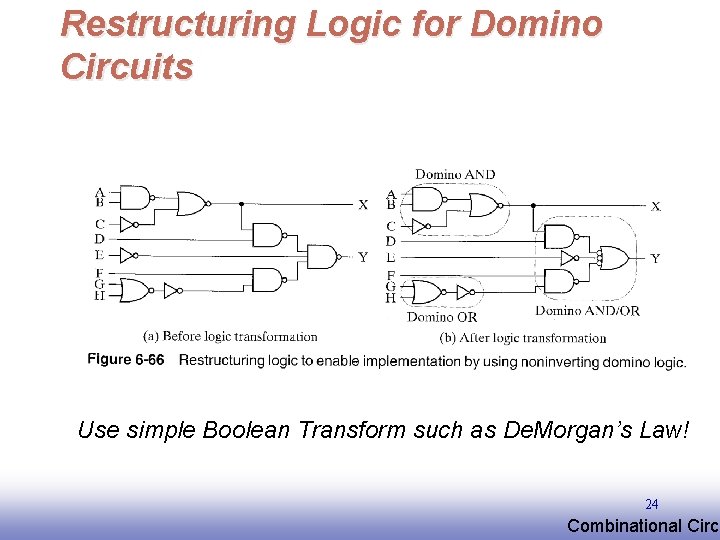

Restructuring Logic for Domino Circuits Use simple Boolean Transform such as De. Morgan’s Law! 24 EE 141 Combinational Circu

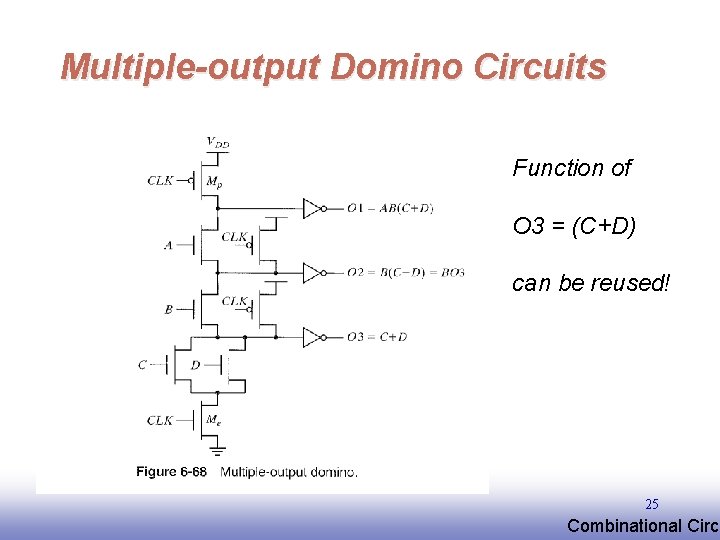

Multiple-output Domino Circuits Function of O 3 = (C+D) can be reused! 25 EE 141 Combinational Circu

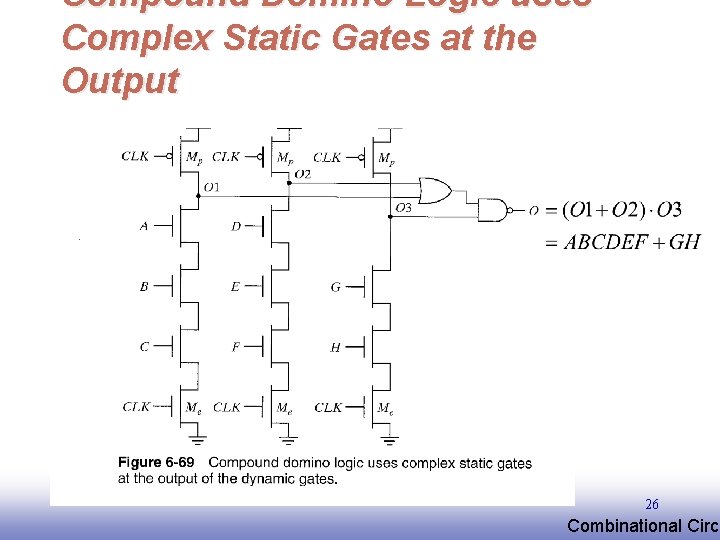

Compound Domino Logic uses Complex Static Gates at the Output 26 EE 141 Combinational Circu

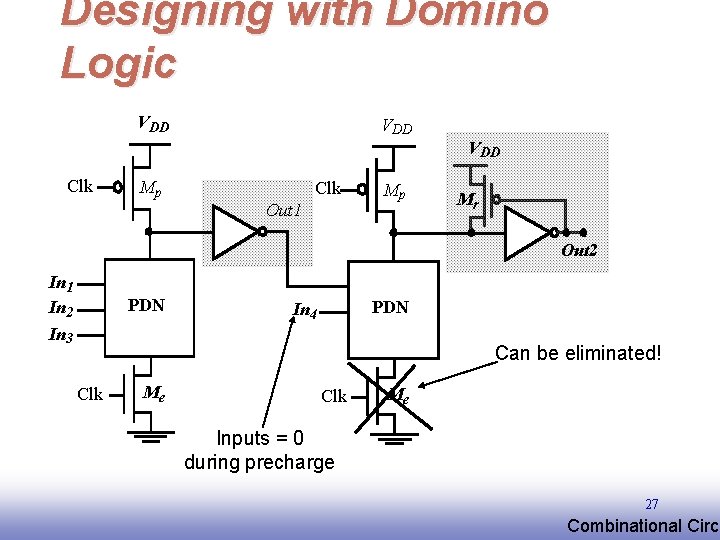

Designing with Domino Logic VDD VDD Clk Mp Clk Out 1 Mp Mr Out 2 In 1 In 2 In 3 PDN In 4 Can be eliminated! Clk Me Inputs = 0 during precharge 27 EE 141 Combinational Circu

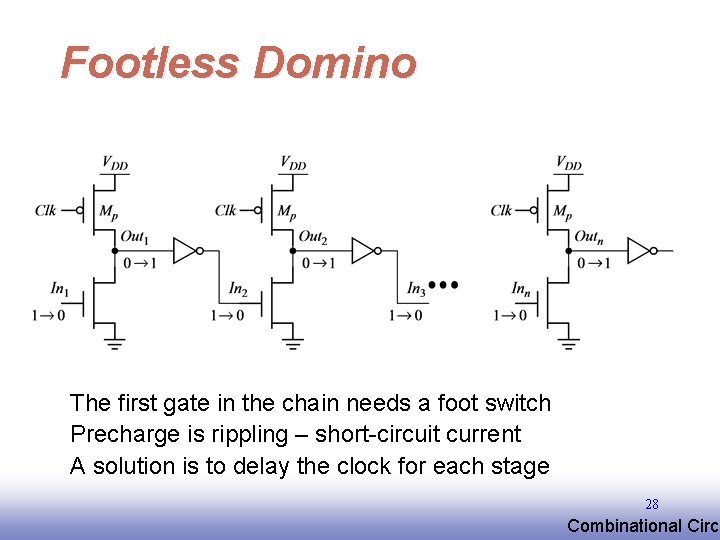

Footless Domino The first gate in the chain needs a foot switch Precharge is rippling – short-circuit current A solution is to delay the clock for each stage 28 EE 141 Combinational Circu

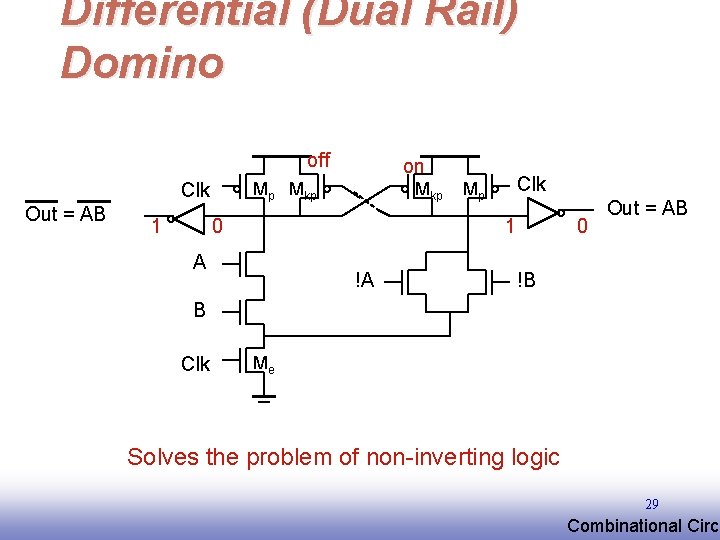

Differential (Dual Rail) Domino off Mp Mkp Clk Out = AB 1 on Mkp 0 Clk Mp 1 A !A 0 Out = AB !B B Clk Me Solves the problem of non-inverting logic 29 EE 141 Combinational Circu

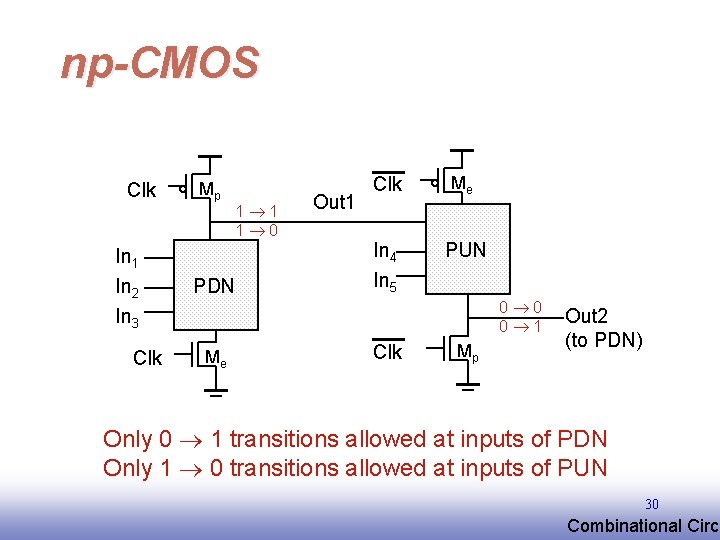

np-CMOS Clk In 1 In 2 In 3 Clk Mp 1 1 1 0 PDN Me Out 1 Clk Me In 4 In 5 PUN 0 0 0 1 Clk Mp Out 2 (to PDN) Only 0 1 transitions allowed at inputs of PDN Only 1 0 transitions allowed at inputs of PUN 30 EE 141 Combinational Circu

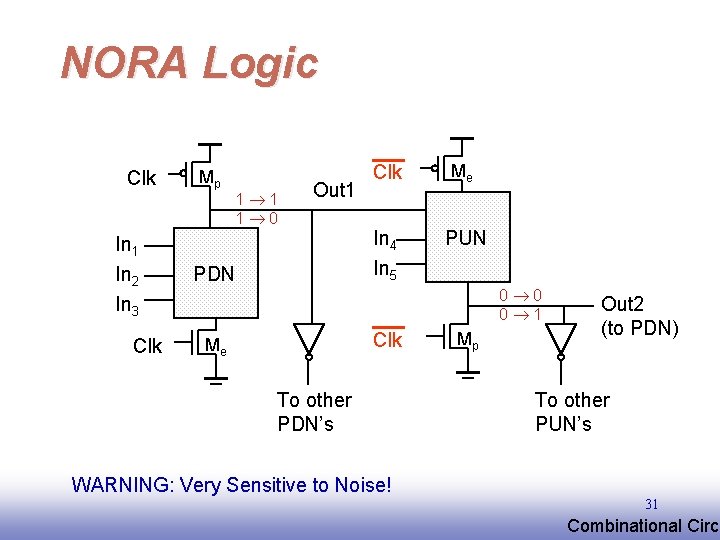

NORA Logic Clk In 1 In 2 In 3 Clk Mp 1 1 1 0 Out 1 PDN Clk Me In 4 In 5 PUN 0 0 0 1 Clk Me To other PDN’s Mp Out 2 (to PDN) To other PUN’s WARNING: Very Sensitive to Noise! 31 EE 141 Combinational Circu

Summary of Dynamic CMOS Dynamic circuits should be designed with care (watch out charge sharing, etc. ) q It has smaller footprint and higher speed, but may not be best for low-power designs. q The current trend is towards an increased use of complementary static CMOS q Design Automation Tools: Optimization at the logic level, rather at the circuit level. q 32 EE 141 Combinational Circu

- Slides: 32