CHAPTER 5 THE LC3 Adapted from slides provided

![Solution �Instruction at x 3002 is [R 2 = NOT(R 2)]. If R 2 Solution �Instruction at x 3002 is [R 2 = NOT(R 2)]. If R 2](https://slidetodoc.com/presentation_image_h/37c0e060a9b8721f0ad3421a3e4e7a89/image-73.jpg)

- Slides: 73

CHAPTER 5 THE LC-3 Adapted from slides provided by Mc. Graw-Hill Companies Inc. , modified by professors at University of Wisconsin-Madison

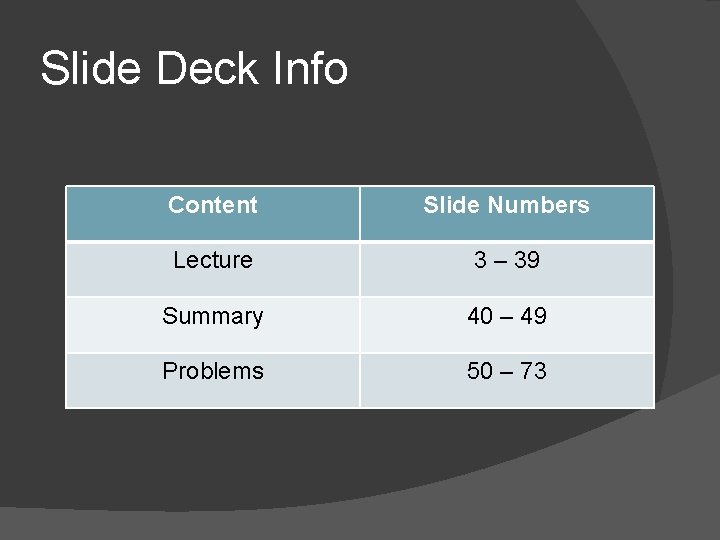

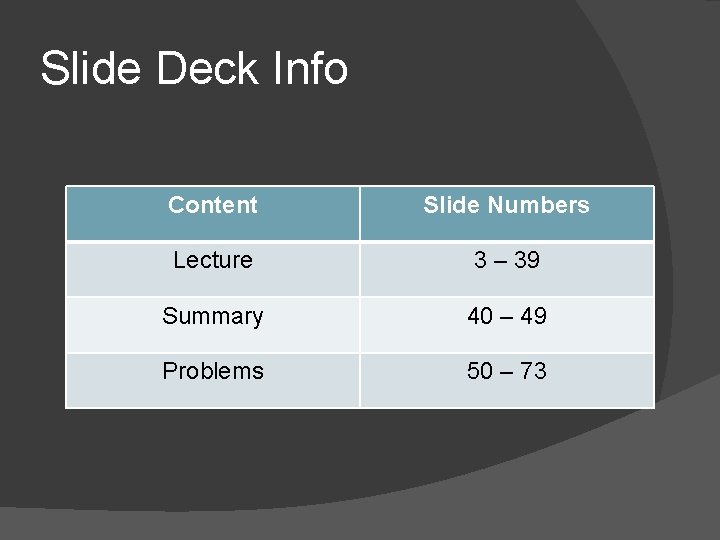

Slide Deck Info Content Slide Numbers Lecture 3 – 39 Summary 40 – 49 Problems 50 – 73

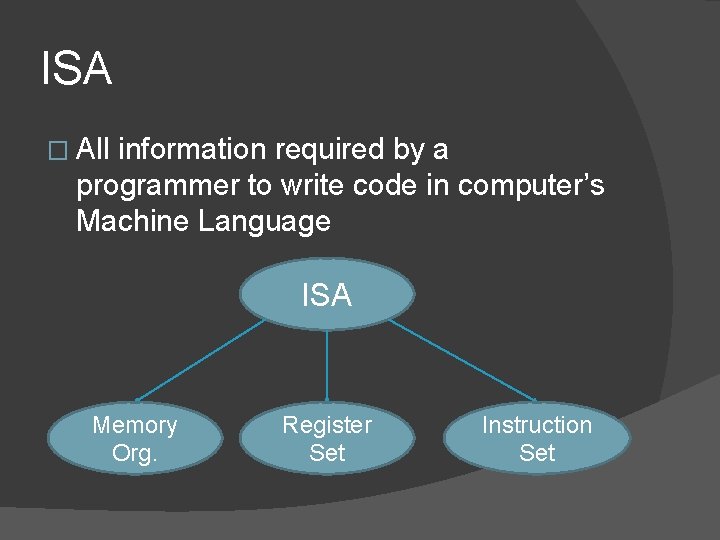

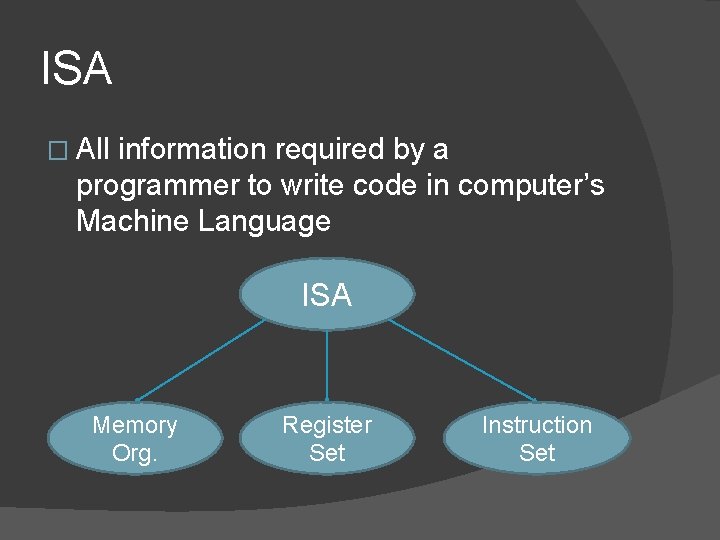

ISA � All information required by a programmer to write code in computer’s Machine Language ISA Memory Org. Register Set Instruction Set

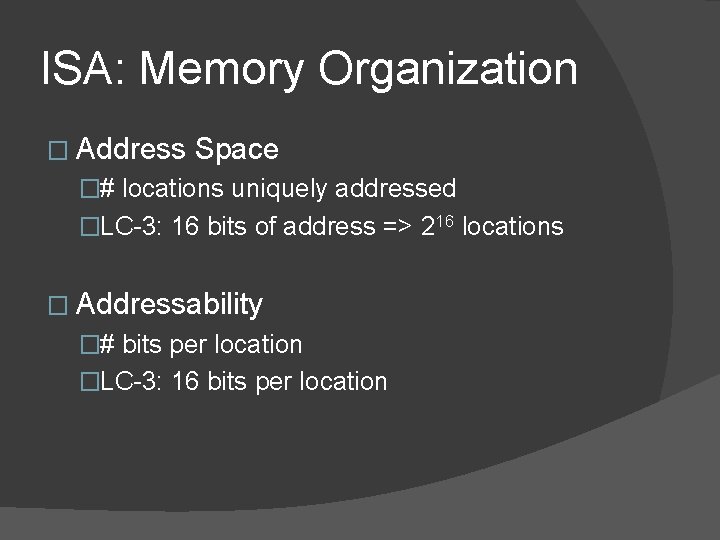

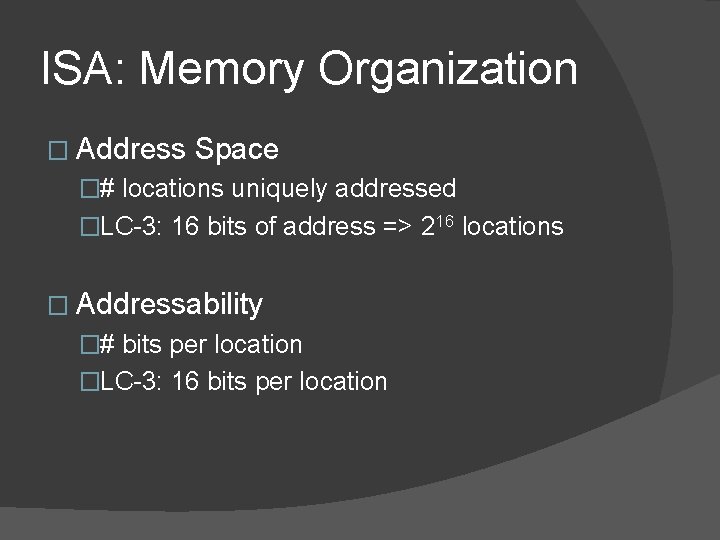

ISA: Memory Organization � Address Space �# locations uniquely addressed �LC-3: 16 bits of address => 216 locations � Addressability �# bits per location �LC-3: 16 bits per location

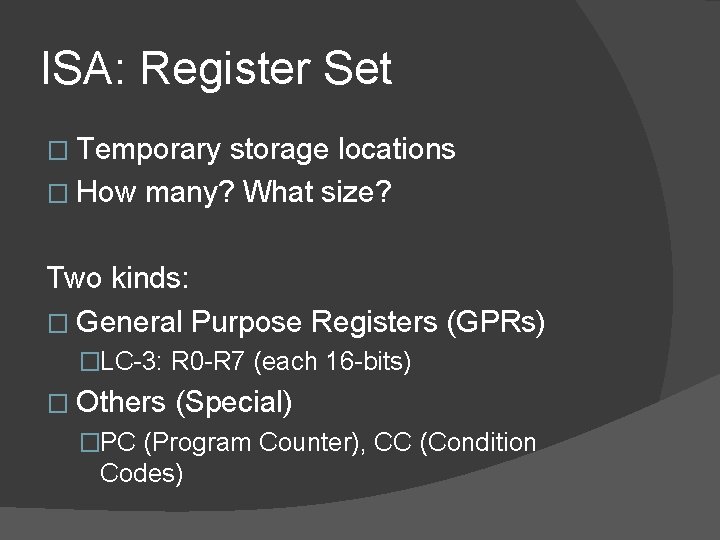

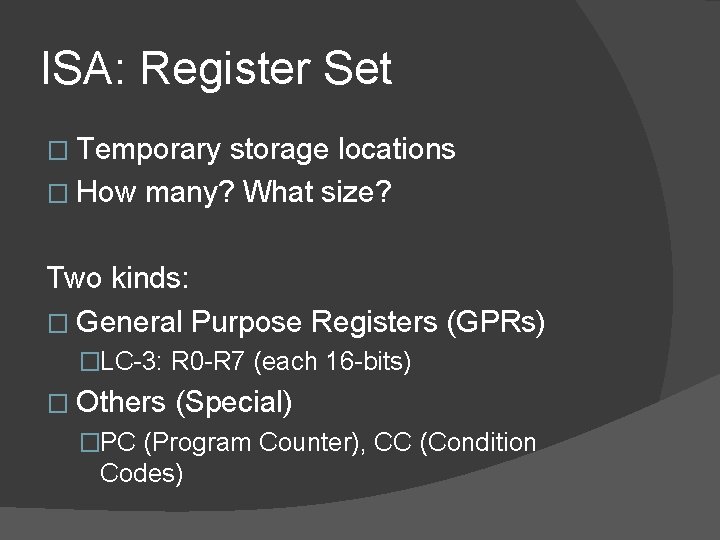

ISA: Register Set � Temporary storage locations � How many? What size? Two kinds: � General Purpose Registers (GPRs) �LC-3: R 0 -R 7 (each 16 -bits) � Others (Special) �PC (Program Counter), CC (Condition Codes)

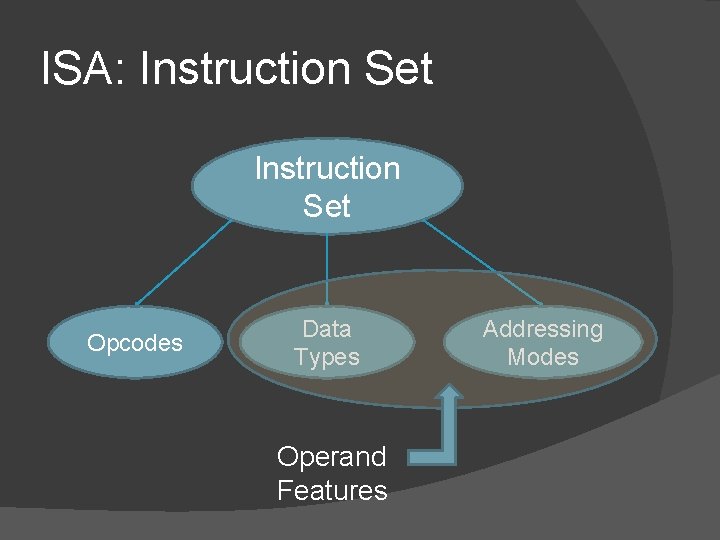

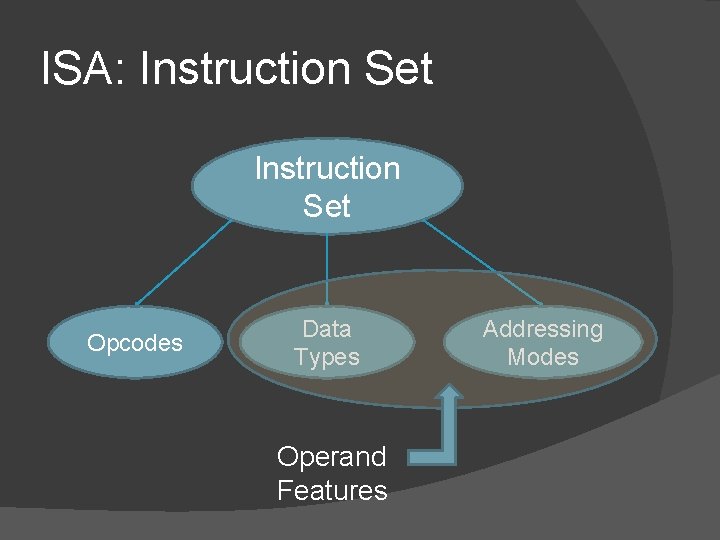

ISA: Instruction Set Opcodes Data Types Operand Features Addressing Modes

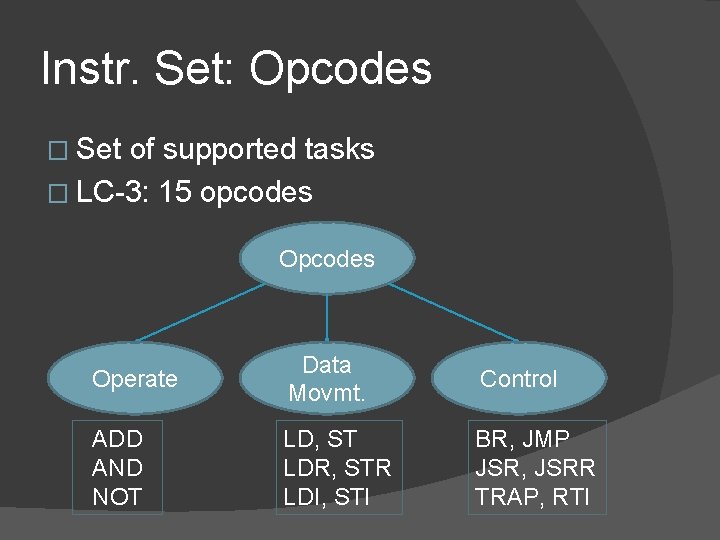

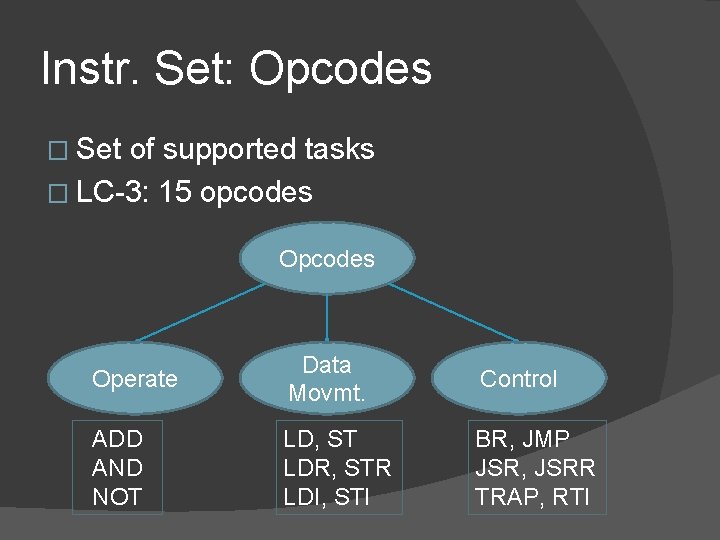

Instr. Set: Opcodes � Set of supported tasks � LC-3: 15 opcodes Operate ADD AND NOT Data Movmt. Control LD, ST LDR, STR LDI, STI BR, JMP JSR, JSRR TRAP, RTI

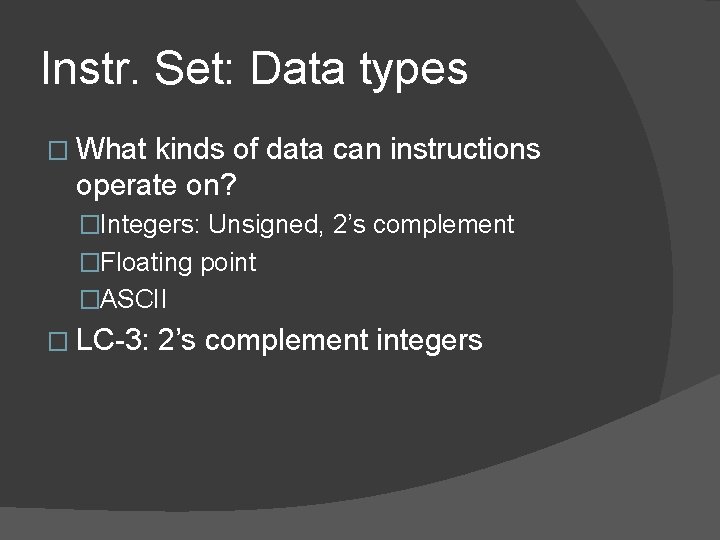

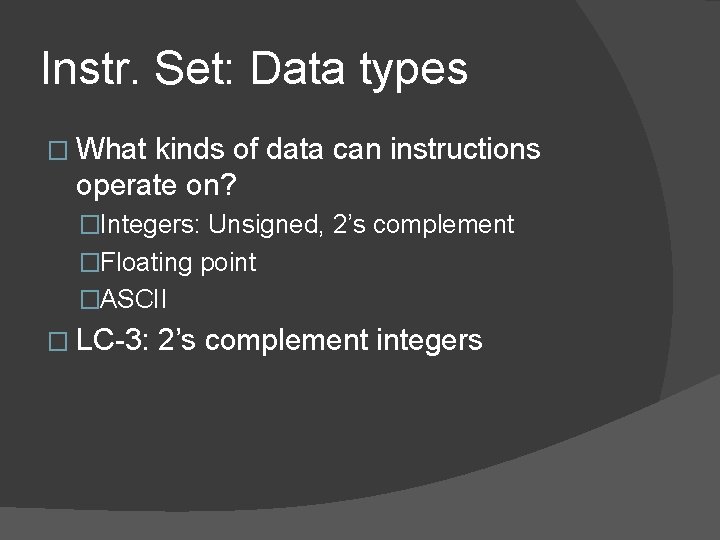

Instr. Set: Data types � What kinds of data can instructions operate on? �Integers: Unsigned, 2’s complement �Floating point �ASCII � LC-3: 2’s complement integers

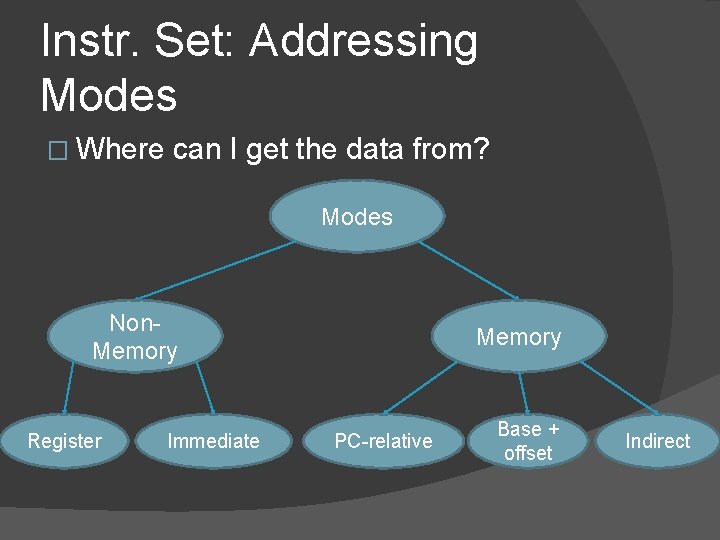

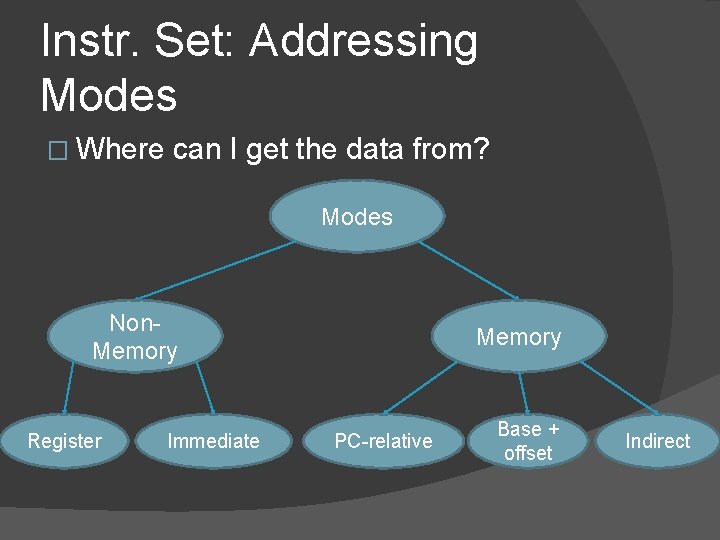

Instr. Set: Addressing Modes � Where can I get the data from? Modes Non. Memory Register Immediate Memory PC-relative Base + offset Indirect

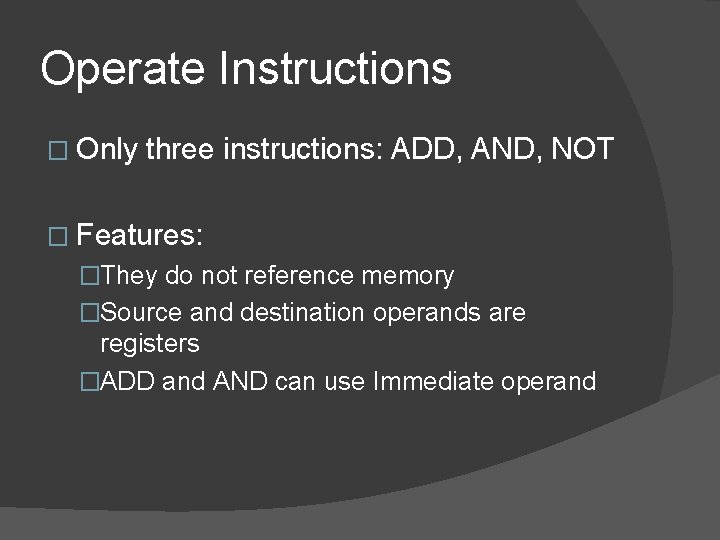

Operate Instructions � Only three instructions: ADD, AND, NOT � Features: �They do not reference memory �Source and destination operands are registers �ADD and AND can use Immediate operand

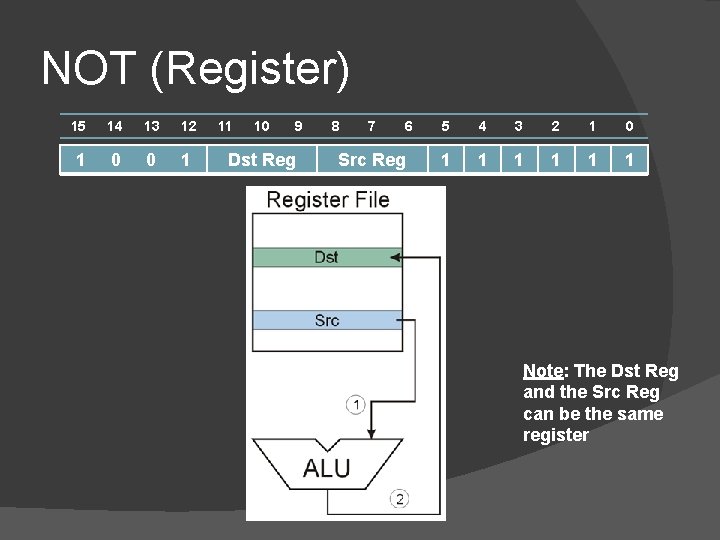

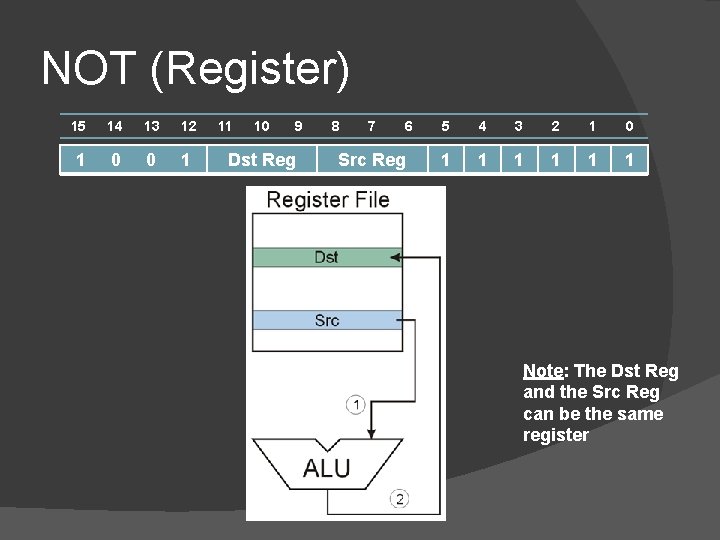

NOT (Register) 15 14 13 12 1 0 0 1 11 10 9 Dst Reg 8 7 6 Src Reg 5 4 3 2 1 0 1 1 1 Note: The Dst Reg and the Src Reg can be the same register

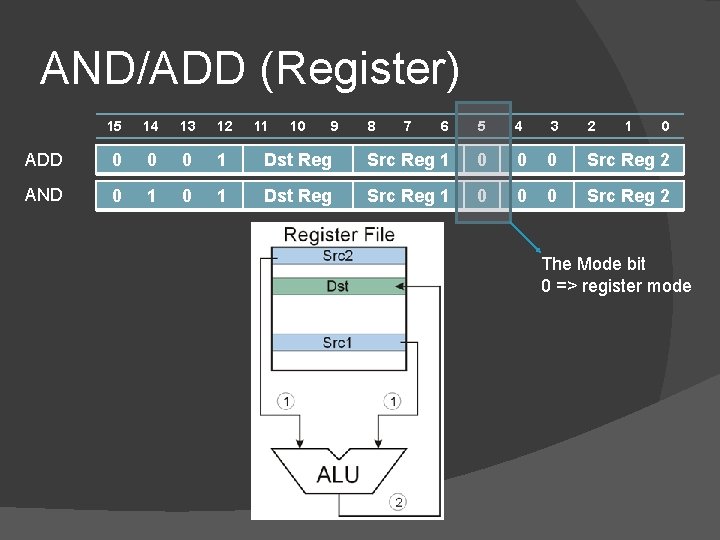

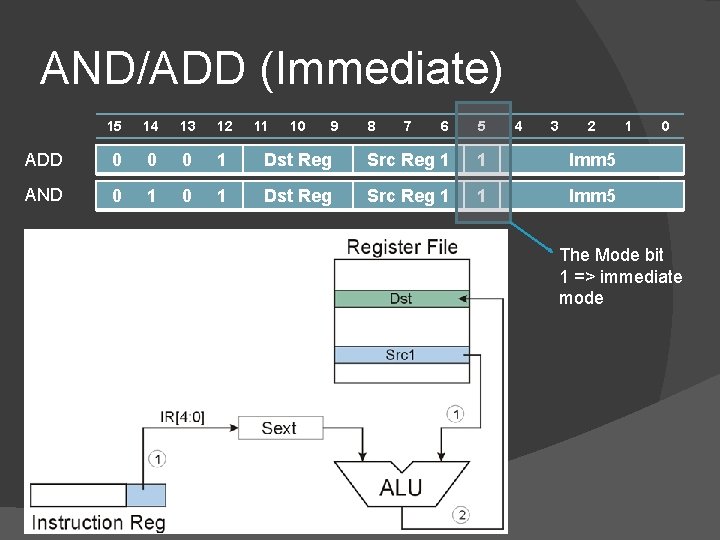

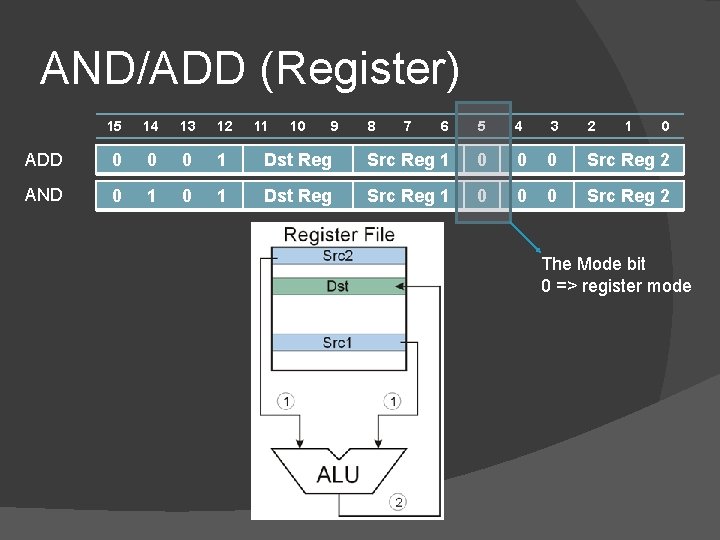

AND/ADD (Register) 15 14 13 12 ADD 0 0 0 1 AND 0 1 11 10 9 8 7 6 5 4 3 2 1 0 Dst Reg Src Reg 1 0 0 0 Src Reg 2 The Mode bit 0 => register mode

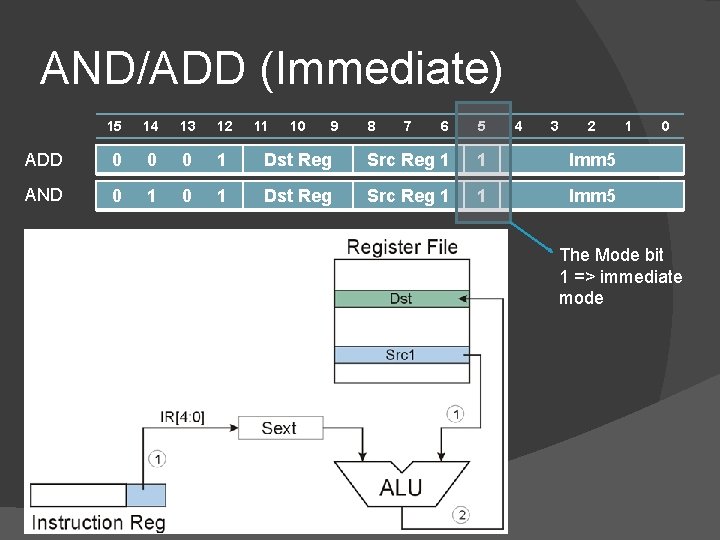

AND/ADD (Immediate) 15 14 13 12 ADD 0 0 0 1 AND 0 1 11 10 9 8 7 6 5 4 3 2 Dst Reg Src Reg 1 1 Imm 5 1 0 The Mode bit 1 => immediate mode

What about other operations? � How to subtract? � How to do OR? � Copy a register? � Initialize a register to 0?

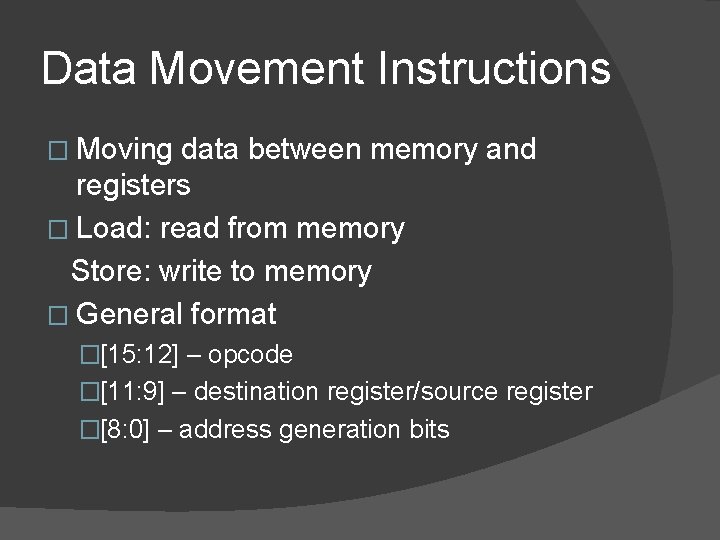

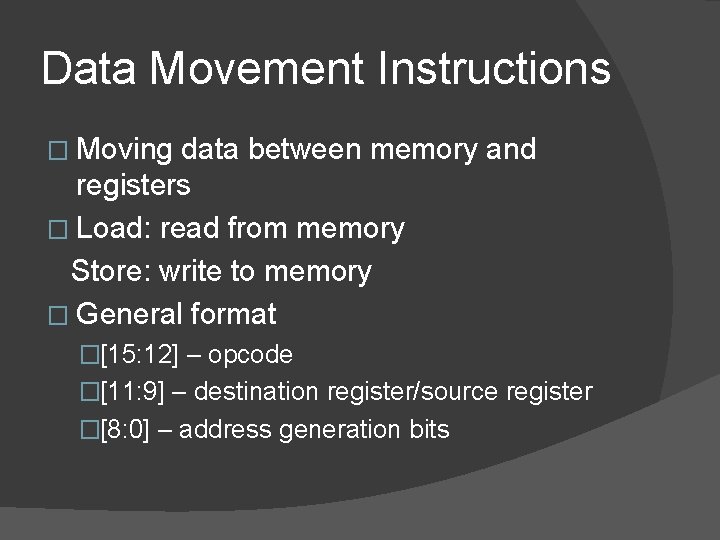

Data Movement Instructions � Moving data between memory and registers � Load: read from memory Store: write to memory � General format �[15: 12] – opcode �[11: 9] – destination register/source register �[8: 0] – address generation bits

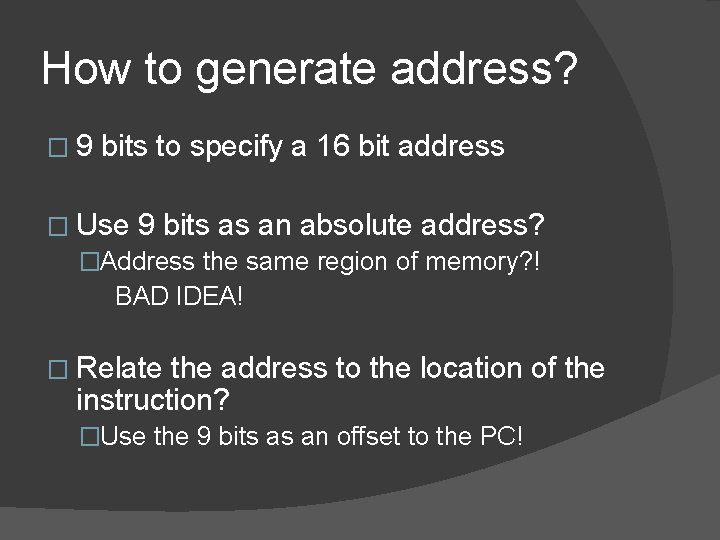

How to generate address? � 9 bits to specify a 16 bit address � Use 9 bits as an absolute address? �Address the same region of memory? ! BAD IDEA! � Relate the address to the location of the instruction? �Use the 9 bits as an offset to the PC!

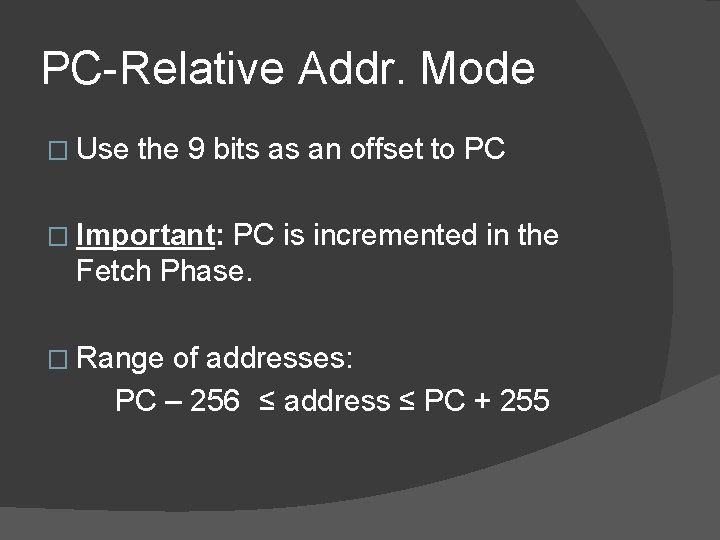

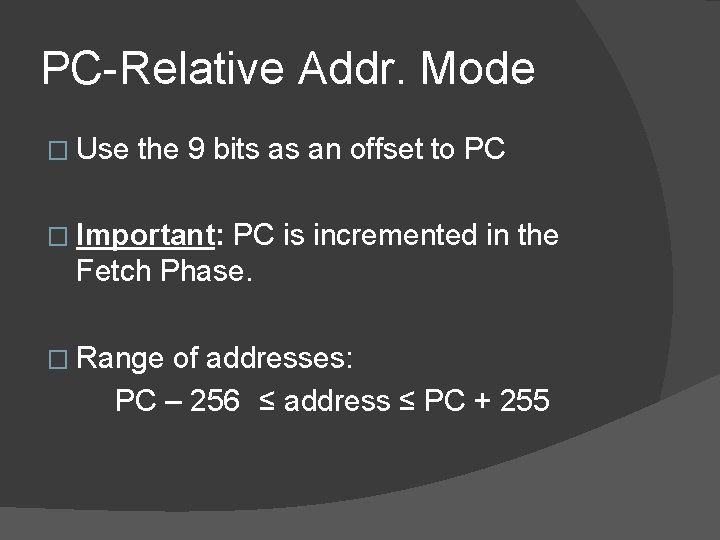

PC-Relative Addr. Mode � Use the 9 bits as an offset to PC � Important: PC is incremented in the Fetch Phase. � Range of addresses: PC – 256 ≤ address ≤ PC + 255

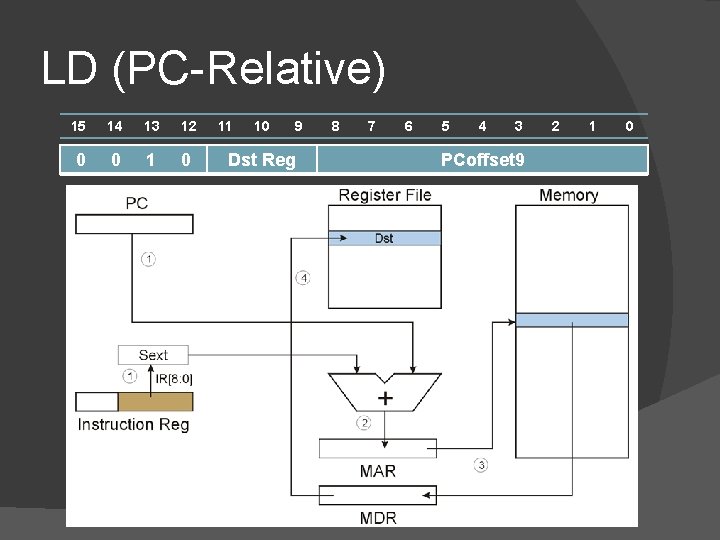

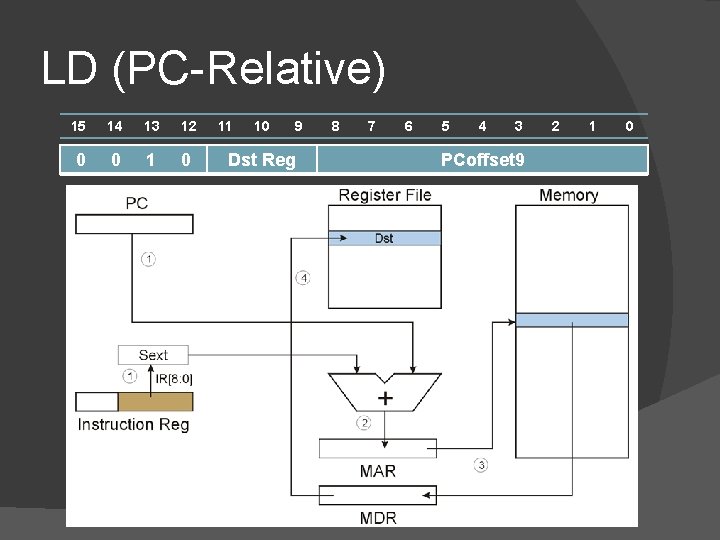

LD (PC-Relative) 15 14 13 12 0 0 11 10 9 Dst Reg 8 7 6 5 4 3 PCoffset 9 2 1 0

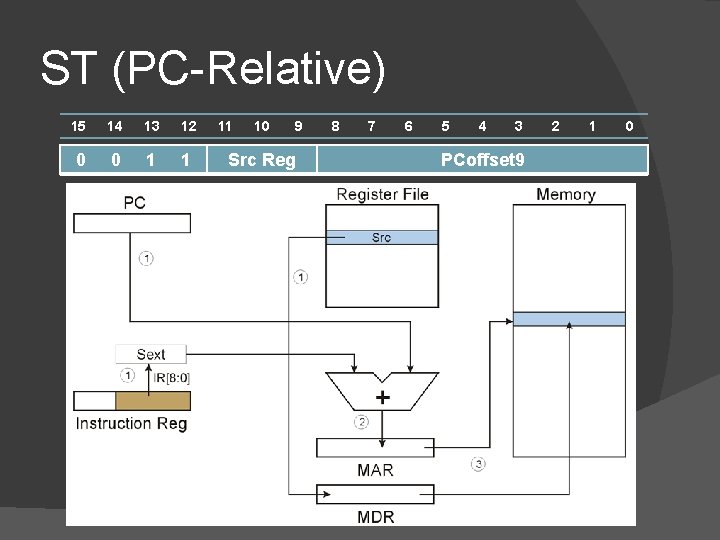

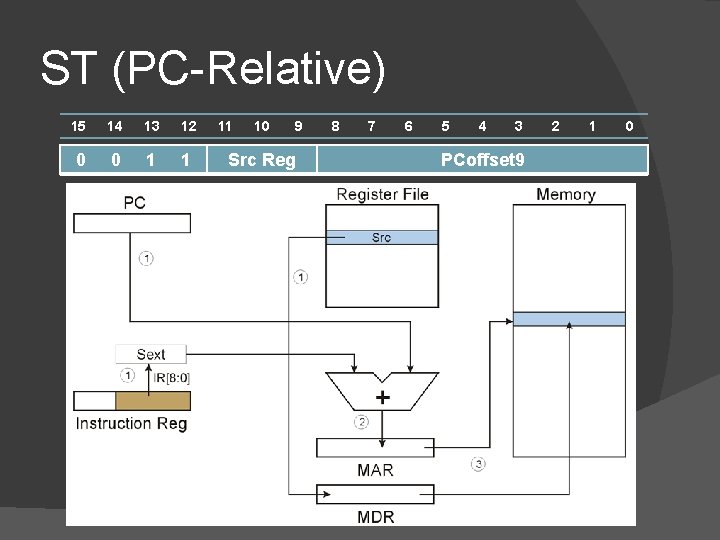

ST (PC-Relative) 15 14 13 12 0 0 1 1 11 10 9 Src Reg 8 7 6 5 4 3 PCoffset 9 2 1 0

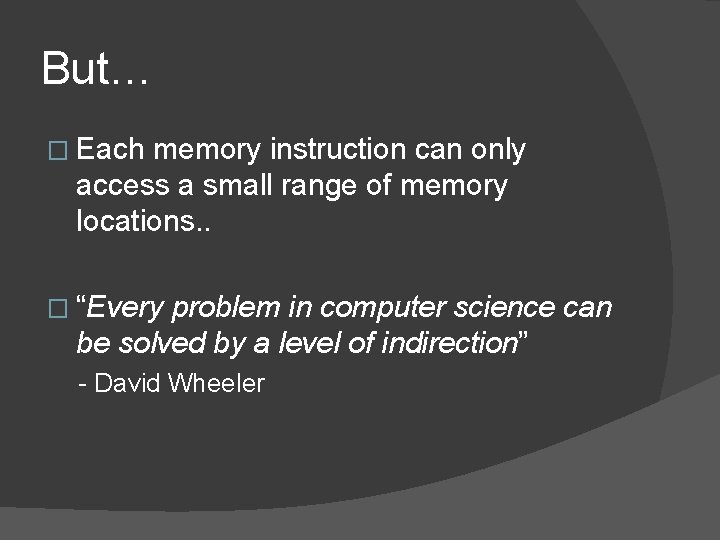

But… � Each memory instruction can only access a small range of memory locations. . � “Every problem in computer science can be solved by a level of indirection” - David Wheeler

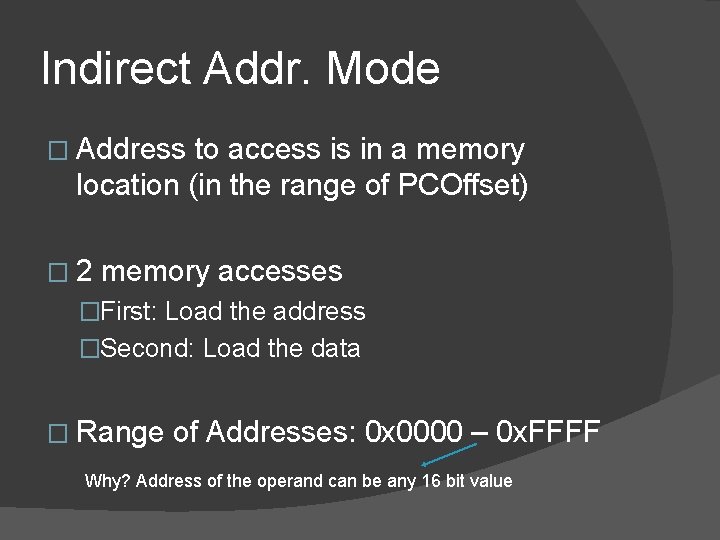

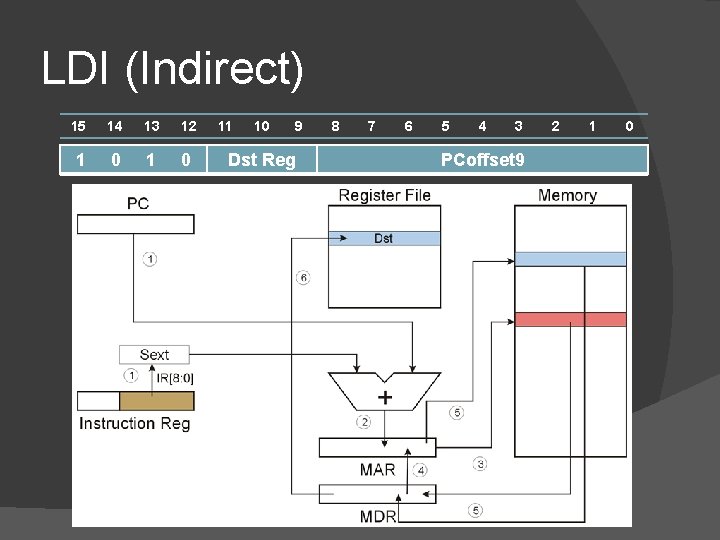

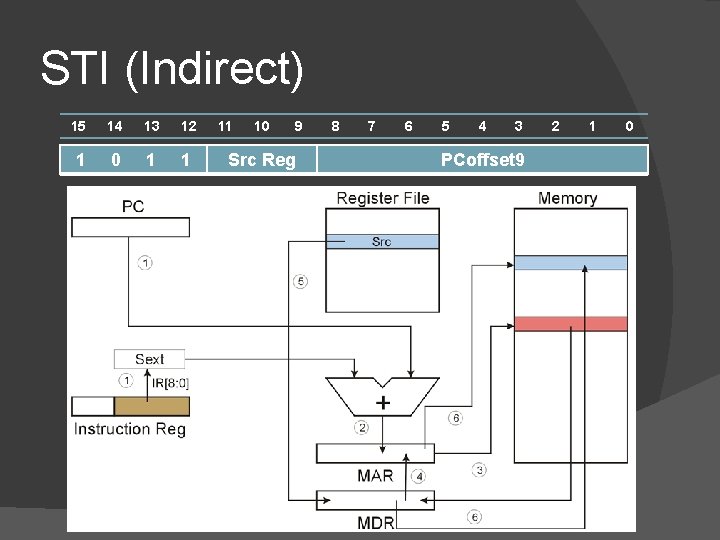

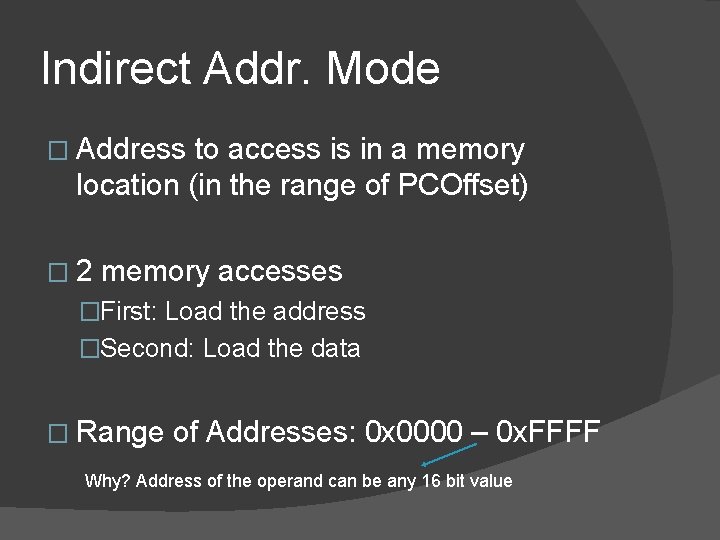

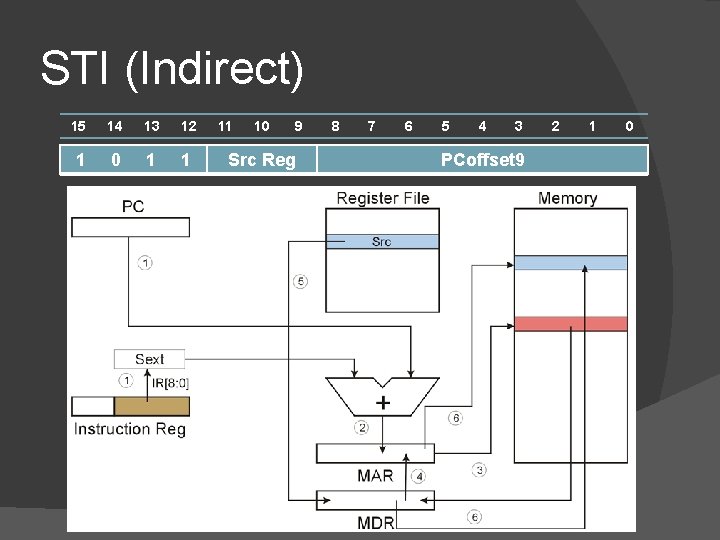

Indirect Addr. Mode � Address to access is in a memory location (in the range of PCOffset) � 2 memory accesses �First: Load the address �Second: Load the data � Range of Addresses: 0 x 0000 – 0 x. FFFF Why? Address of the operand can be any 16 bit value

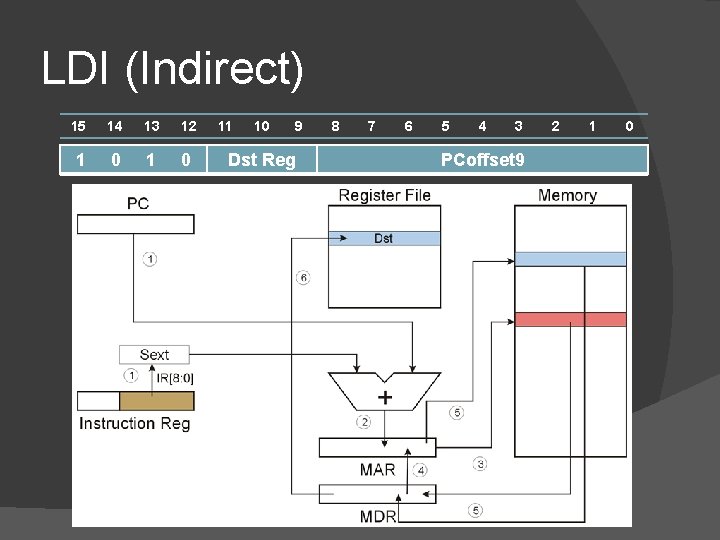

LDI (Indirect) 15 14 13 12 1 0 11 10 9 Dst Reg 8 7 6 5 4 3 PCoffset 9 2 1 0

STI (Indirect) 15 14 13 12 1 0 1 1 11 10 9 Src Reg 8 7 6 5 4 3 PCoffset 9 2 1 0

Any other way? � We need a 16 bit value to use as memory address � Why not use the GPRs (R 0 -R 7)?

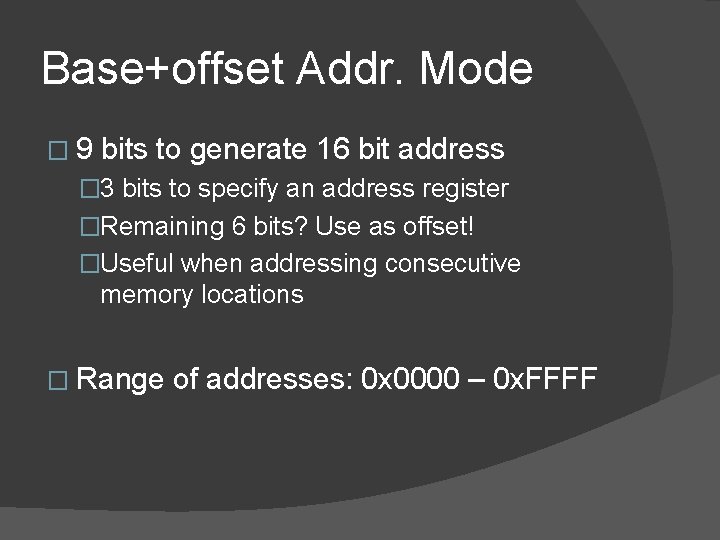

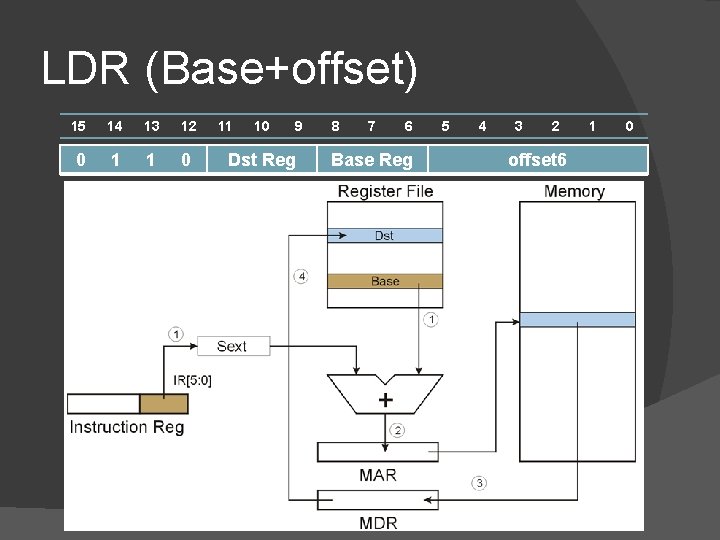

Base+offset Addr. Mode � 9 bits to generate 16 bit address � 3 bits to specify an address register �Remaining 6 bits? Use as offset! �Useful when addressing consecutive memory locations � Range of addresses: 0 x 0000 – 0 x. FFFF

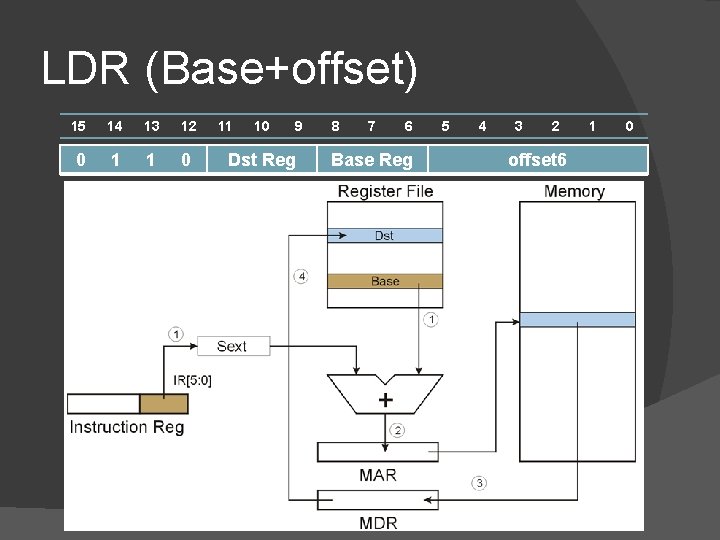

LDR (Base+offset) 15 14 13 12 0 1 1 0 11 10 9 Dst Reg 8 7 6 Base Reg 5 4 3 2 offset 6 1 0

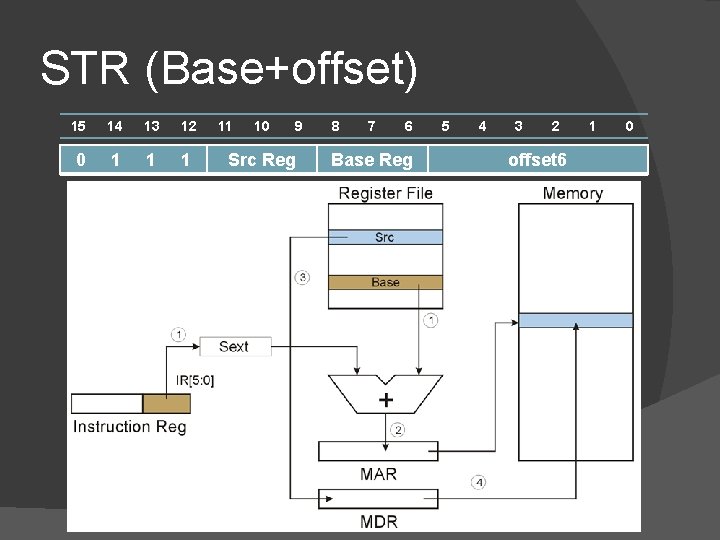

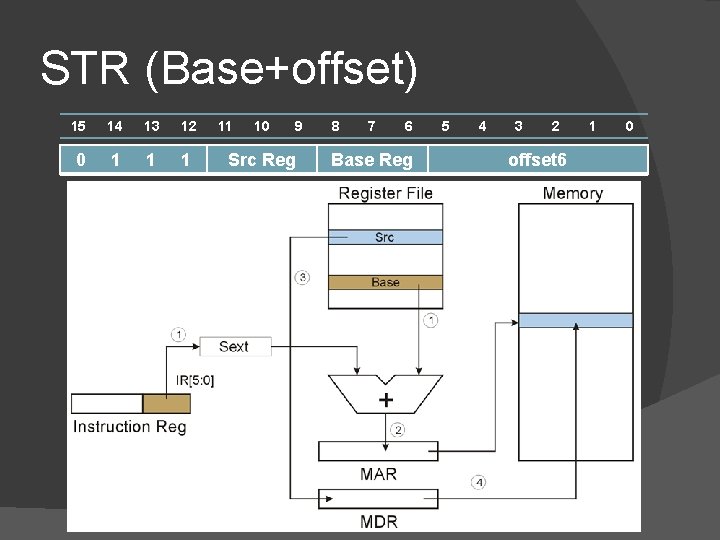

STR (Base+offset) 15 14 13 12 0 1 11 10 9 Src Reg 8 7 6 Base Reg 5 4 3 2 offset 6 1 0

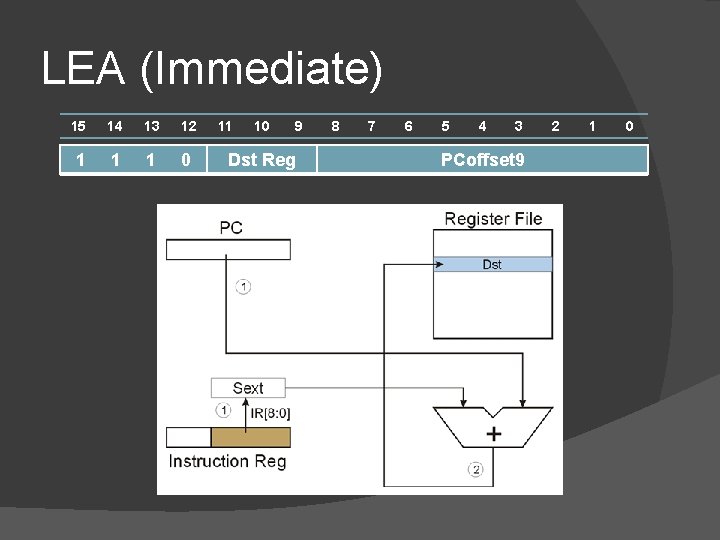

Load Effective Address � Computes an address like PC-Relative and stores result in a register � DOES NOT ACCESS MEMORY

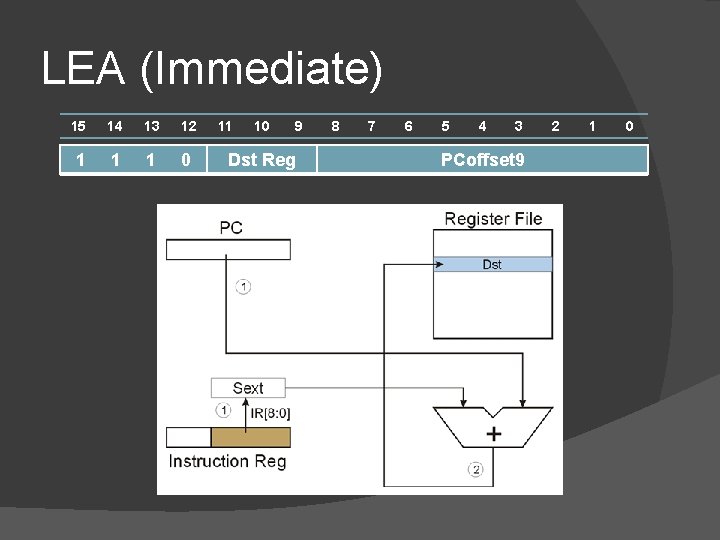

LEA (Immediate) 15 14 13 12 1 1 1 0 11 10 9 Dst Reg 8 7 6 5 4 3 PCoffset 9 2 1 0

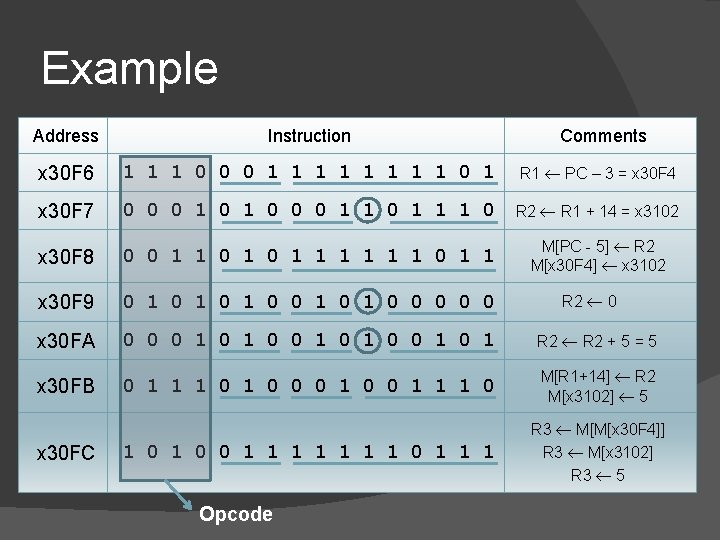

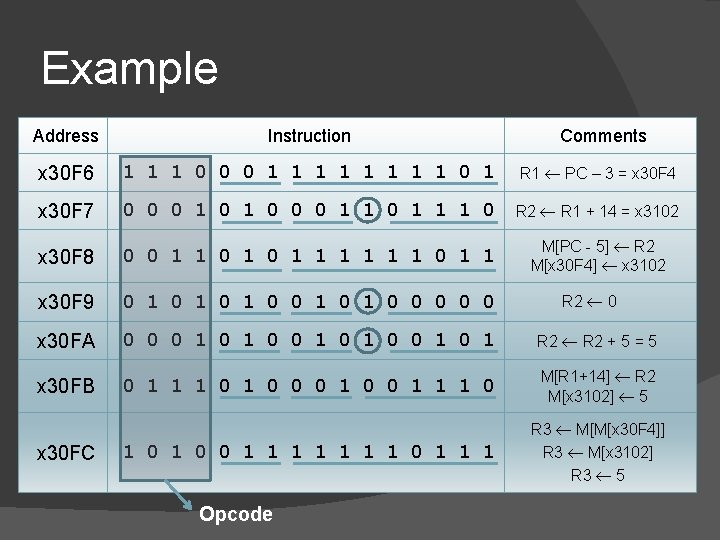

Example Address Instruction x 30 F 6 1 1 1 0 0 0 1 1 1 1 0 1 R 1 PC – 3 = x 30 F 4 x 30 F 7 0 0 0 1 1 1 0 R 2 R 1 + 14 = x 3102 x 30 F 8 0 0 1 1 1 0 1 1 M[PC - 5] R 2 M[x 30 F 4] x 3102 x 30 F 9 0 1 0 1 0 1 0 0 0 x 30 FA 0 0 0 1 0 1 0 0 1 R 2 + 5 = 5 x 30 FB 0 1 1 1 0 0 0 1 1 1 0 M[R 1+14] R 2 M[x 3102] 5 1 0 0 1 1 1 1 0 1 1 1 R 3 M[M[x 30 F 4]] R 3 M[x 3102] R 3 5 x 30 FC Opcode Comments R 2 0

Control Instructions � Change the sequence of instructions by modifying PC � 3 main types �Conditional Branch �Unconditional Branch �TRAP

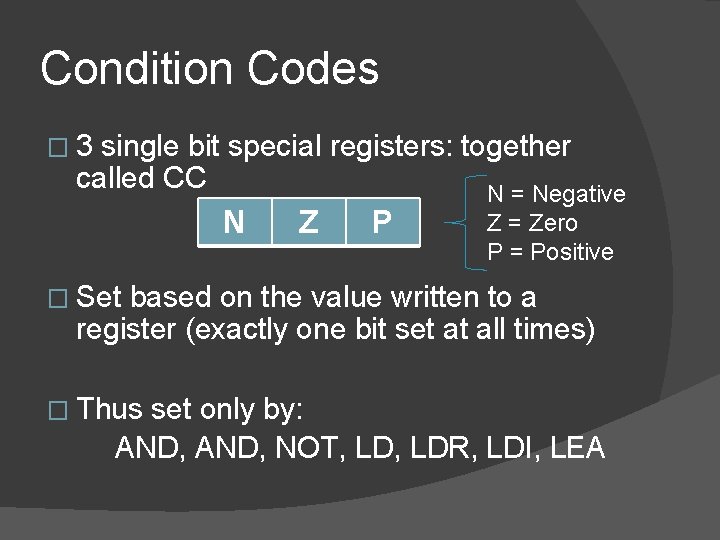

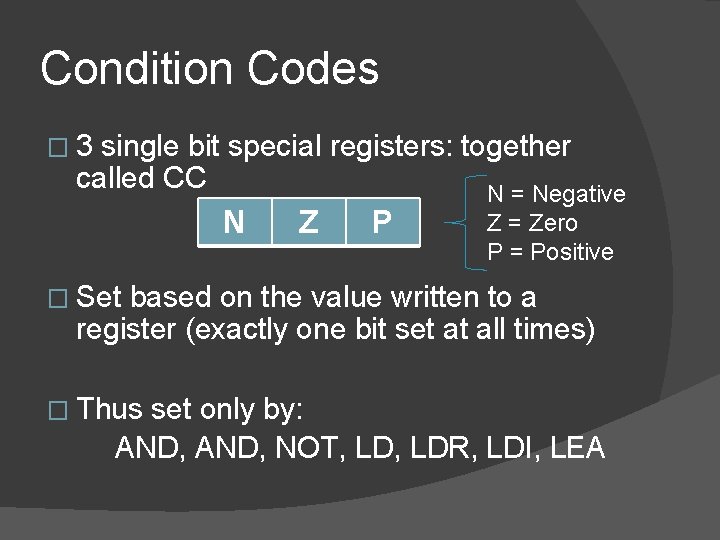

Condition Codes � 3 single bit special registers: together called CC N Z P N = Negative Z = Zero P = Positive � Set based on the value written to a register (exactly one bit set at all times) � Thus set only by: AND, NOT, LDR, LDI, LEA

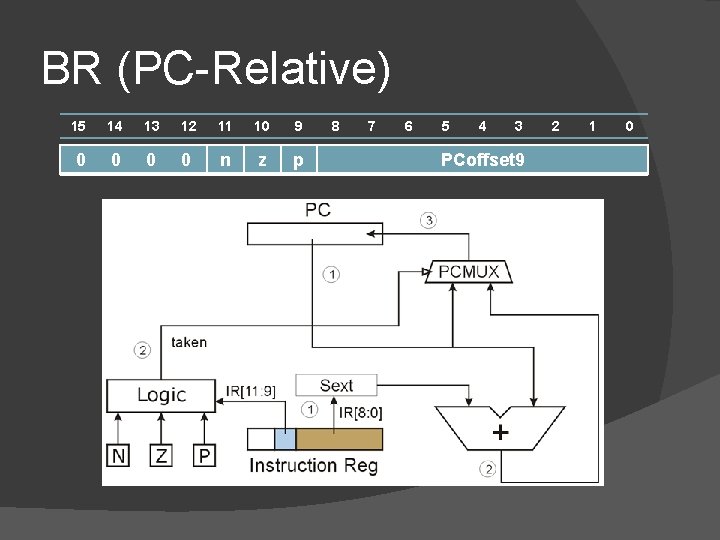

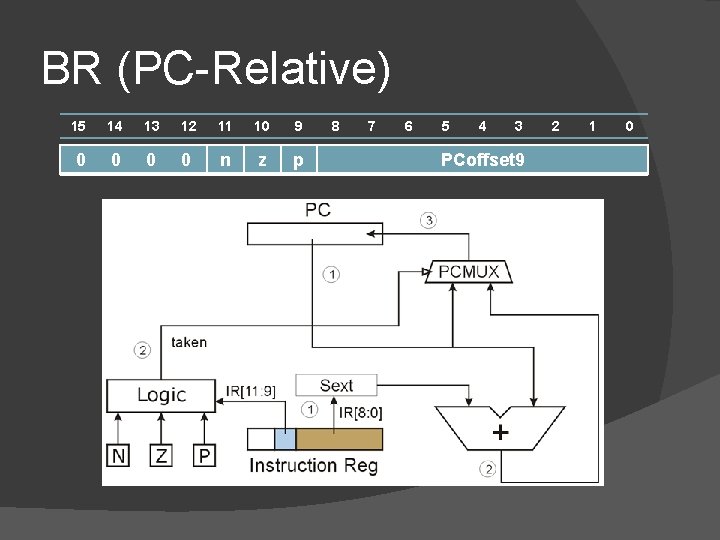

Branch (Conditional) � Changes PC based on “one or more Condition Codes” � Branch can be “Taken” or “Not Taken” � NOTE: PC has been incremented in the Fetch phase

BR (PC-Relative) 15 14 13 12 11 10 9 0 0 n z p 8 7 6 5 4 3 PCoffset 9 2 1 0

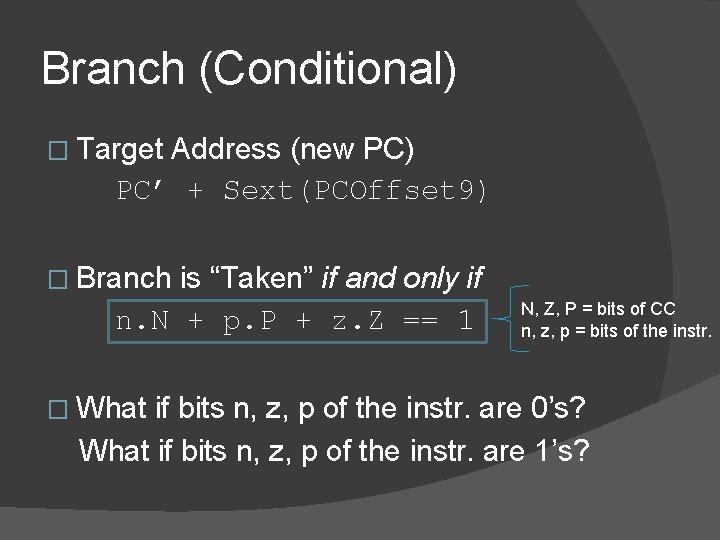

Branch (Conditional) � Target Address (new PC) PC’ + Sext(PCOffset 9) � Branch is “Taken” if and only if n. N + p. P + z. Z == 1 N, Z, P = bits of CC n, z, p = bits of the instr. � What if bits n, z, p of the instr. are 0’s? What if bits n, z, p of the instr. are 1’s?

Jump (Unconditional) � Always “Taken” � Target address is the contents of a register

JMP (Register) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1 1 0 0 0 Base Reg 0 0 0 What is the advantage of JMP over using BR with n, z, p set to 1’s?

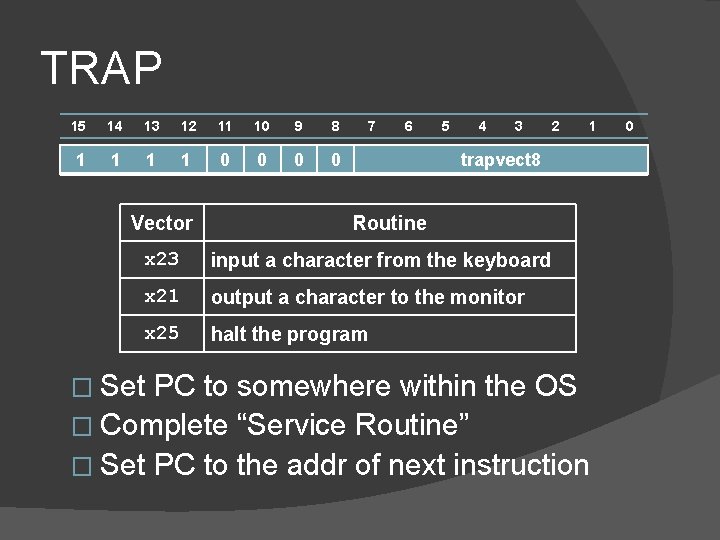

TRAP calls � Operating System (OS): Usually a program on top of which all other programs execute � Implements commonly used functions like reading from keyboard, printing on the display, etc.

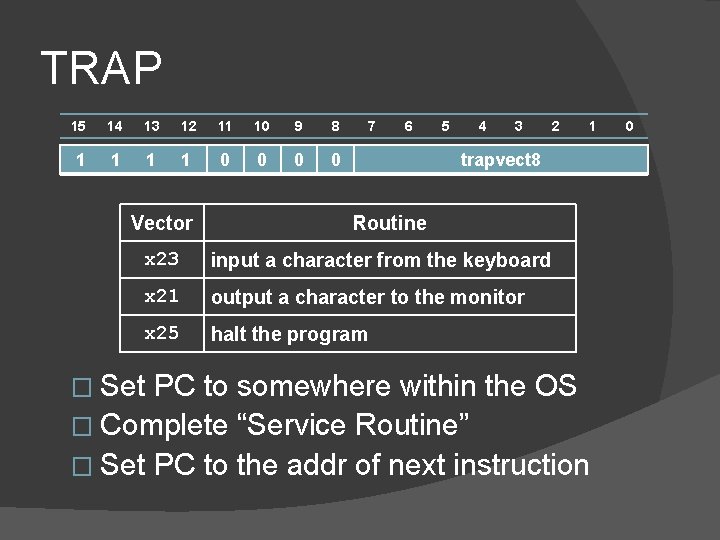

TRAP 15 14 13 12 11 10 9 8 1 1 0 0 Vector 7 6 5 4 3 2 1 trapvect 8 Routine x 23 input a character from the keyboard x 21 output a character to the monitor x 25 halt the program � Set PC to somewhere within the OS � Complete “Service Routine” � Set PC to the addr of next instruction 0

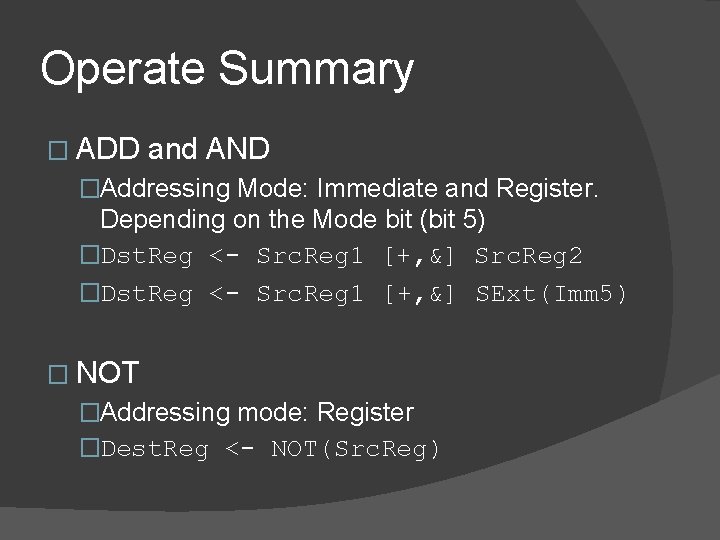

LC-3 ISA Summary

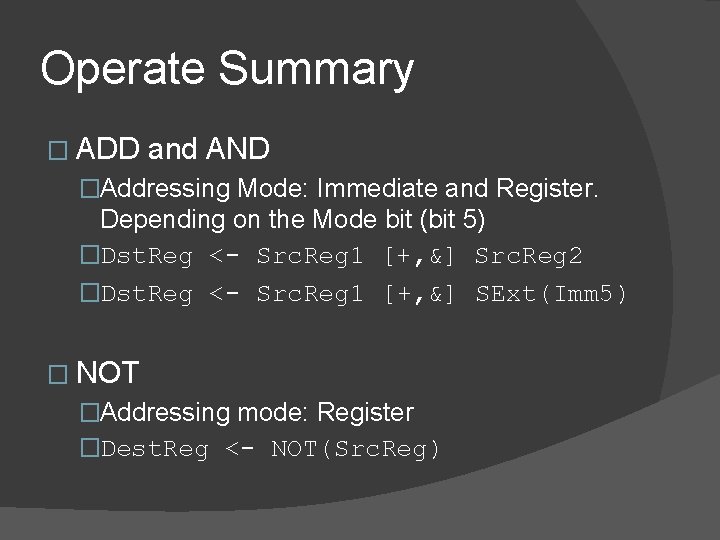

Operate Summary � ADD and AND �Addressing Mode: Immediate and Register. Depending on the Mode bit (bit 5) �Dst. Reg <- Src. Reg 1 [+, &] Src. Reg 2 �Dst. Reg <- Src. Reg 1 [+, &] SExt(Imm 5) � NOT �Addressing mode: Register �Dest. Reg <- NOT(Src. Reg)

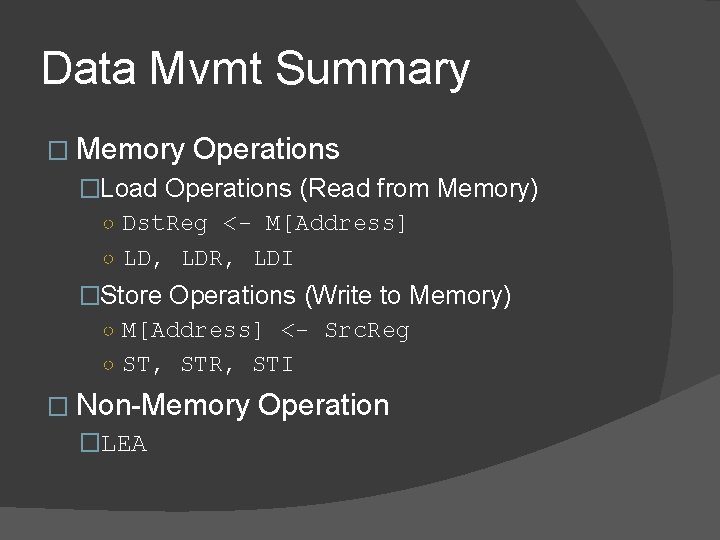

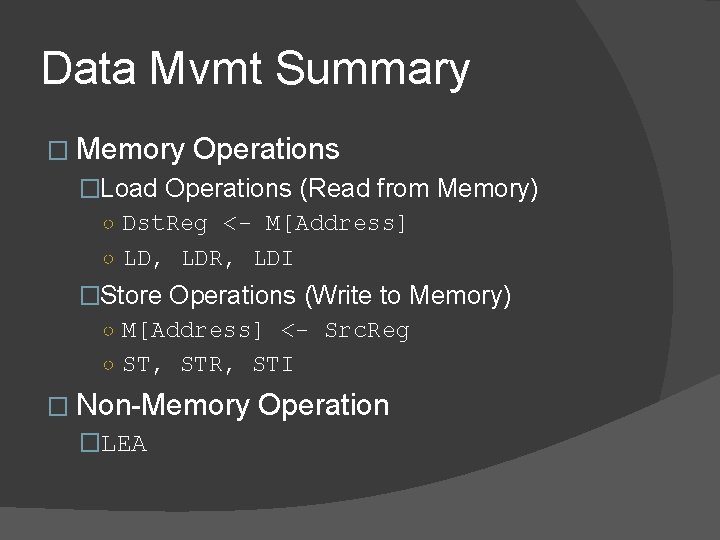

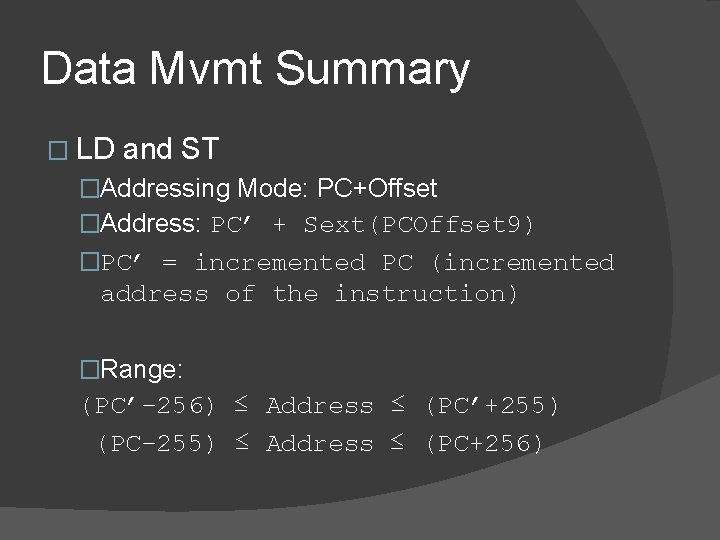

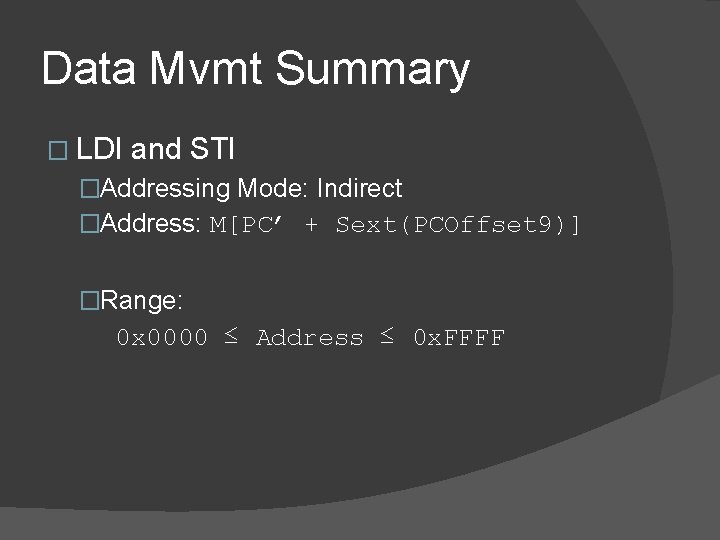

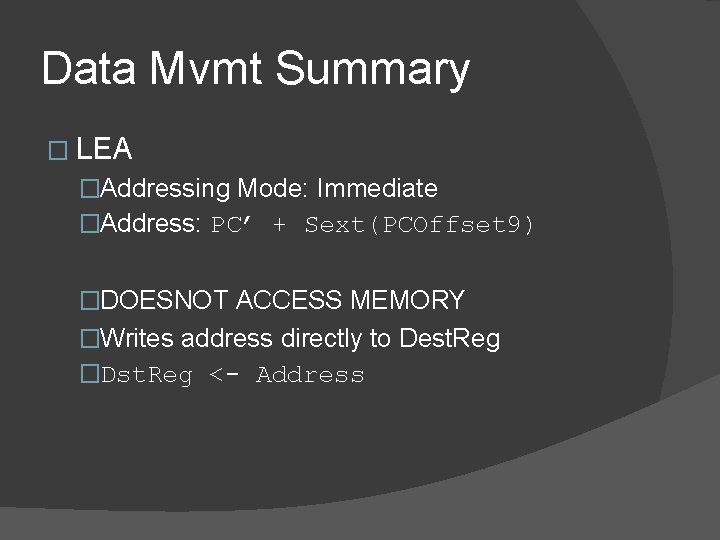

Data Mvmt Summary � Memory Operations �Load Operations (Read from Memory) ○ Dst. Reg <- M[Address] ○ LD, LDR, LDI �Store Operations (Write to Memory) ○ M[Address] <- Src. Reg ○ ST, STR, STI � Non-Memory Operation �LEA

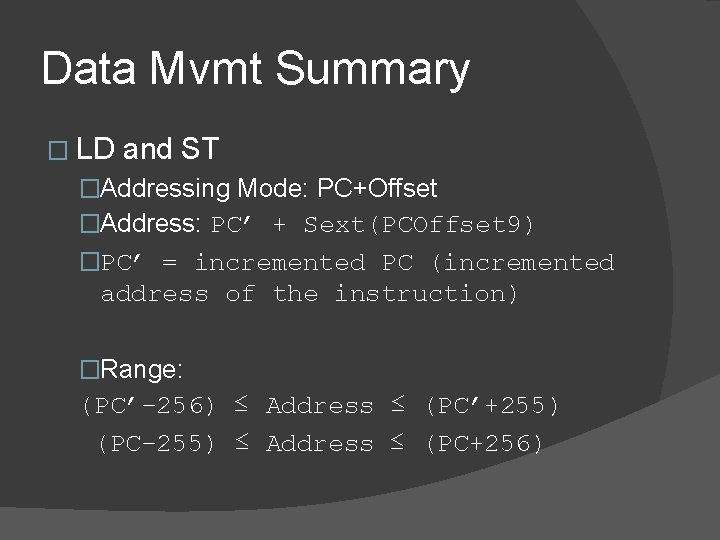

Data Mvmt Summary � LD and ST �Addressing Mode: PC+Offset �Address: PC’ + Sext(PCOffset 9) �PC’ = incremented PC (incremented address of the instruction) �Range: (PC’– 256) ≤ Address ≤ (PC’+255) (PC– 255) ≤ Address ≤ (PC+256)

Data Mvmt Summary � LDR and STR �Addressing Mode: Base+Offset �Address: Base. Reg + SExt(offset 6) �Range: 0 x 0000 ≤ Address ≤ 0 x. FFFF

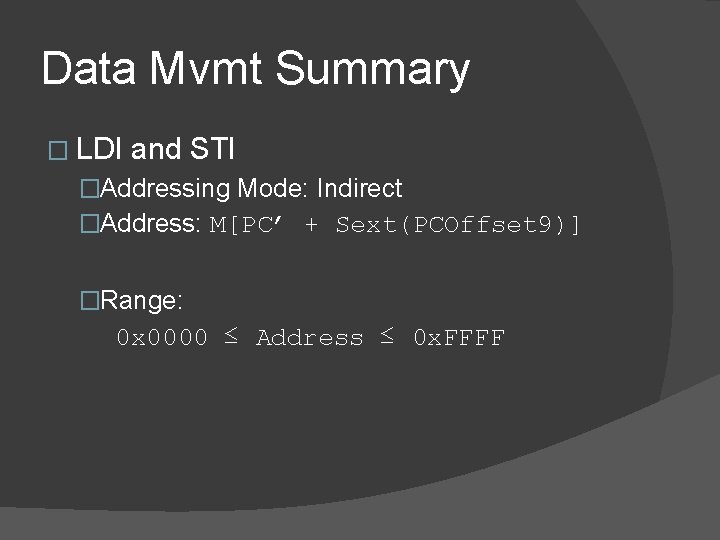

Data Mvmt Summary � LDI and STI �Addressing Mode: Indirect �Address: M[PC’ + Sext(PCOffset 9)] �Range: 0 x 0000 ≤ Address ≤ 0 x. FFFF

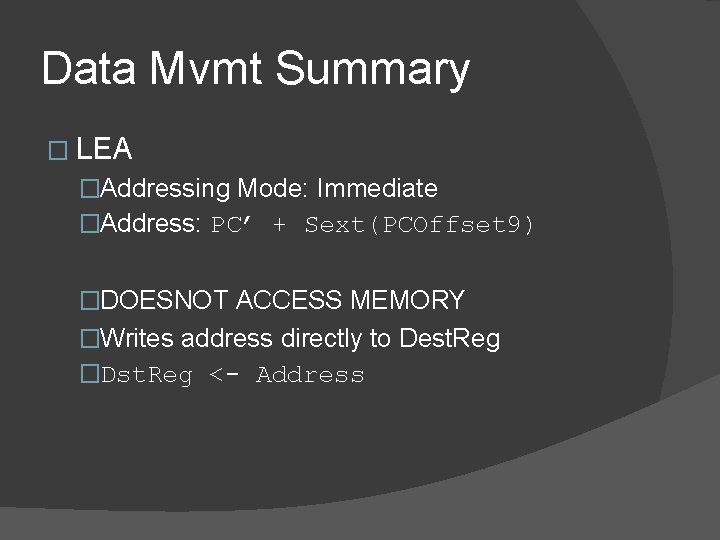

Data Mvmt Summary � LEA �Addressing Mode: Immediate �Address: PC’ + Sext(PCOffset 9) �DOESNOT ACCESS MEMORY �Writes address directly to Dest. Reg �Dst. Reg <- Address

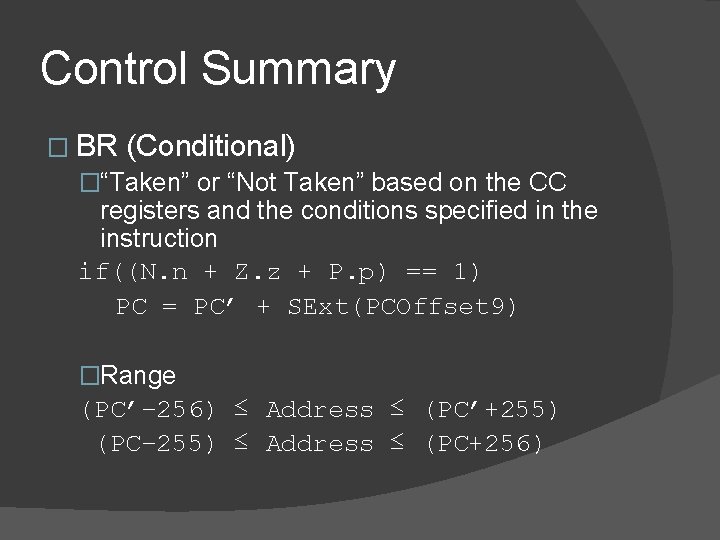

Control Summary � BR (Conditional) �“Taken” or “Not Taken” based on the CC registers and the conditions specified in the instruction if((N. n + Z. z + P. p) == 1) PC = PC’ + SExt(PCOffset 9) �Range (PC’– 256) ≤ Address ≤ (PC’+255) (PC– 255) ≤ Address ≤ (PC+256)

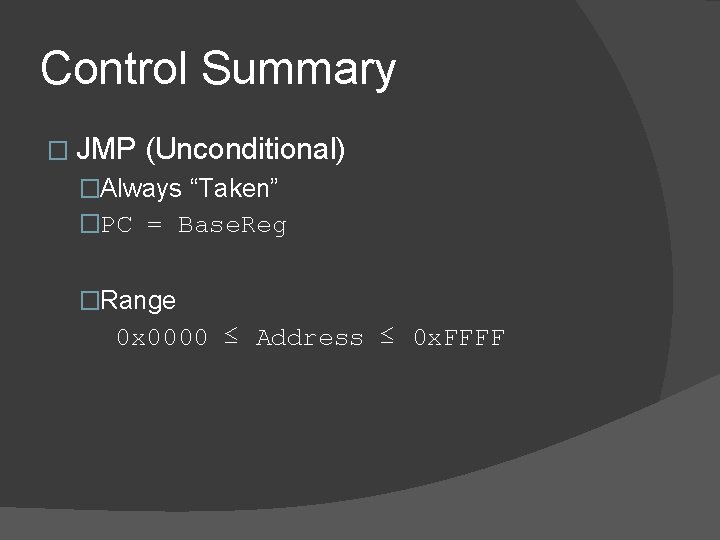

Control Summary � JMP (Unconditional) �Always “Taken” �PC = Base. Reg �Range 0 x 0000 ≤ Address ≤ 0 x. FFFF

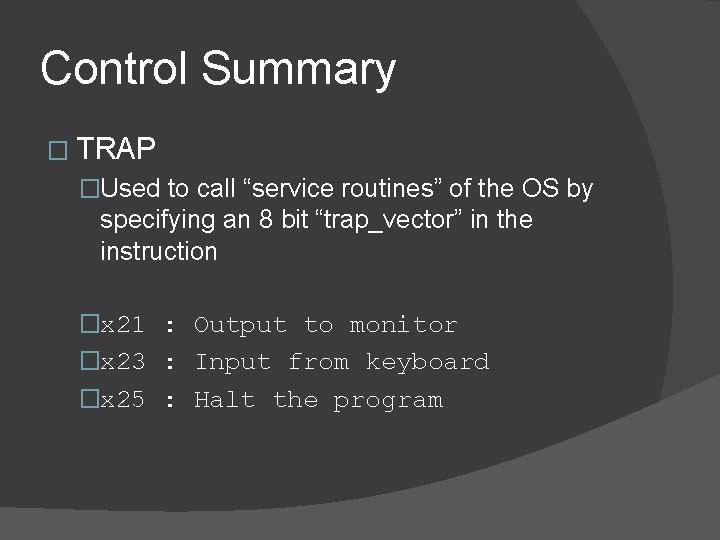

Control Summary � TRAP �Used to call “service routines” of the OS by specifying an 8 bit “trap_vector” in the instruction �x 21 : Output to monitor �x 23 : Input from keyboard �x 25 : Halt the program

Problem Time!

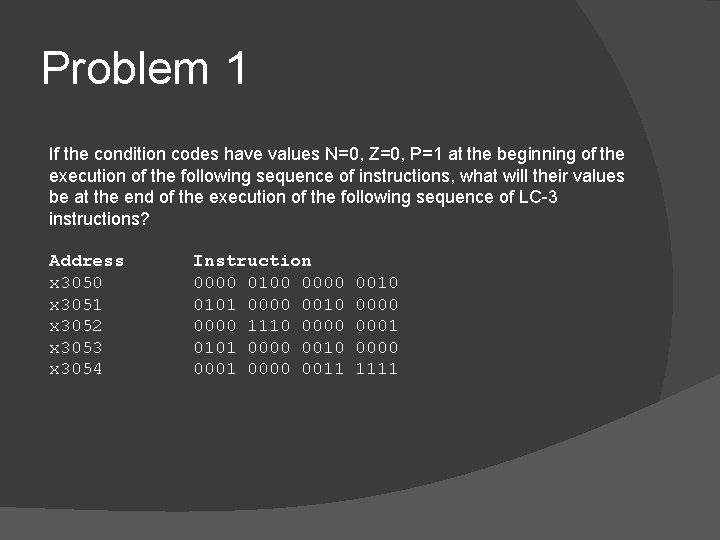

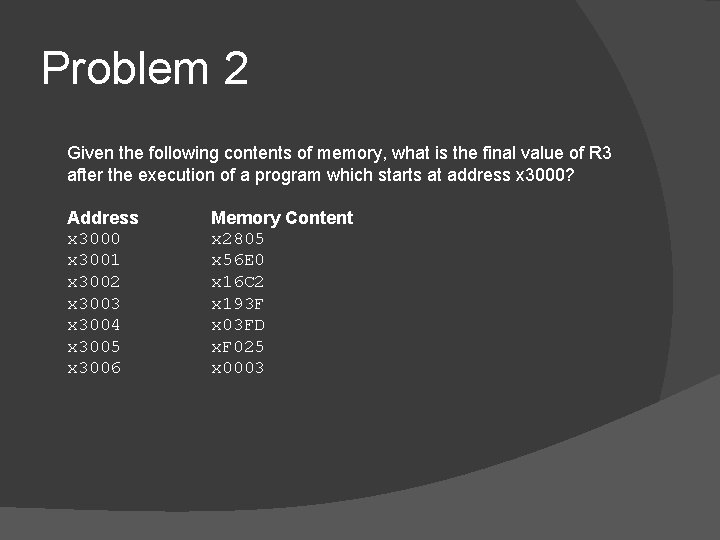

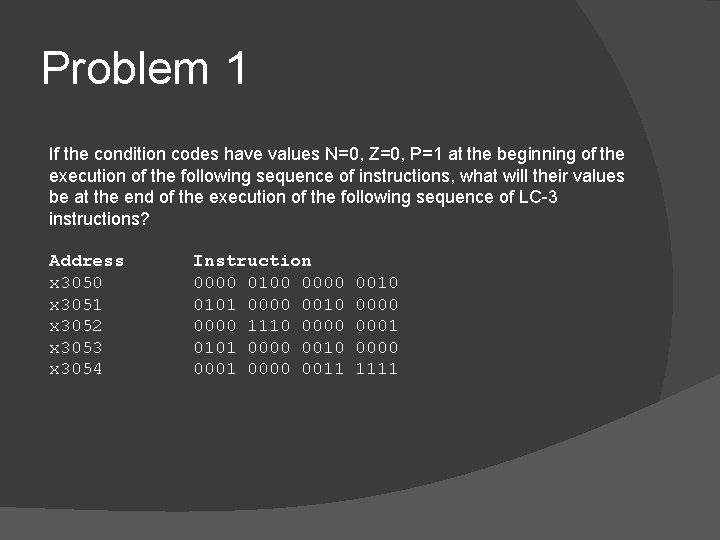

Problem 1 If the condition codes have values N=0, Z=0, P=1 at the beginning of the execution of the following sequence of instructions, what will their values be at the end of the execution of the following sequence of LC-3 instructions? Address x 3050 x 3051 x 3052 x 3053 x 3054 Instruction 0000 0100 0010 0101 0000 0010 0000 1110 0001 0101 0000 0010 0001 0000 0011 1111

Solution Address x 3050 x 3051 x 3052 x 3053 x 3054 Instruction 0000 0100 0010 ; BR if Z to PC’+2 0101 0000 0010 0000 ; R 0 = 0 0000 1110 0001 ; BR always to PC’+1 0101 0000 0010 0000 ; does not execute 0001 0000 0011 1111 ; R 0 = R 0 -1 N=1, Z=0, P=0

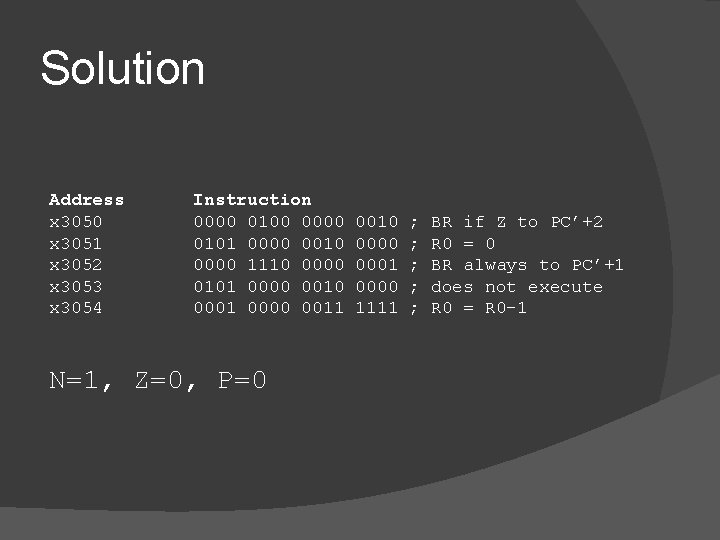

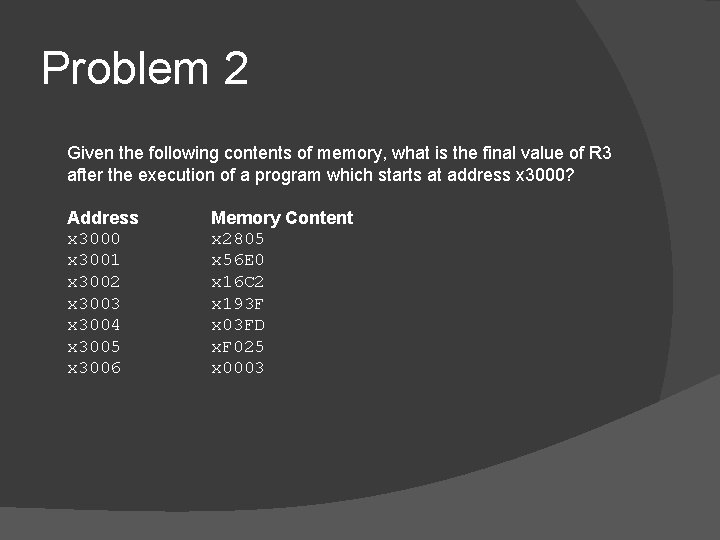

Problem 2 Given the following contents of memory, what is the final value of R 3 after the execution of a program which starts at address x 3000? Address x 3000 x 3001 x 3002 x 3003 x 3004 x 3005 x 3006 Memory Content x 2805 x 56 E 0 x 16 C 2 x 193 F x 03 FD x. F 025 x 0003

Solution Address x 3000 x 3001 x 3002 x 3003 x 3004 x 3005 x 3006 Memory Content x 2805 ; R 4 <- M[PC’+5] (LD R 4, #5) x 56 E 0 ; R 3 <- 0 (AND R 3, #0) x 16 C 2 ; R 3 <- R 3 + R 2 (ADD R 3, R 2) x 193 F ; R 4 <- R 4 – 1 (ADD R 4, -1) x 03 FD ; BR if P to PC’-3(BRp #-3) x. F 025 ; HALT x 0003 R 3 = 3 * R 2

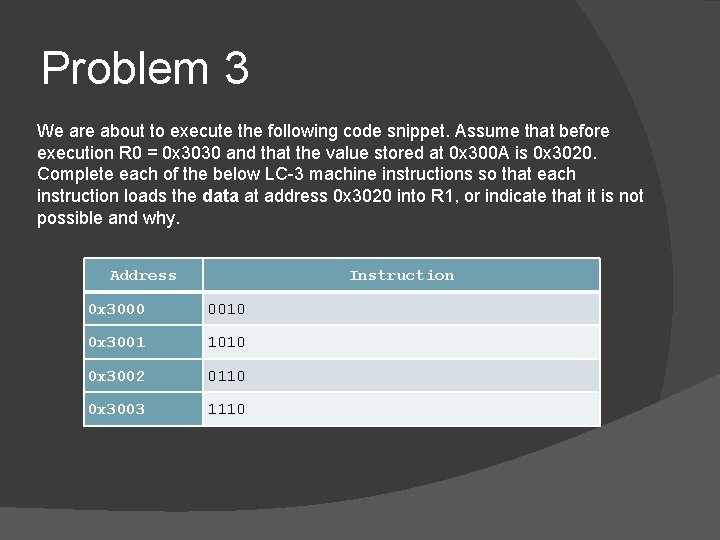

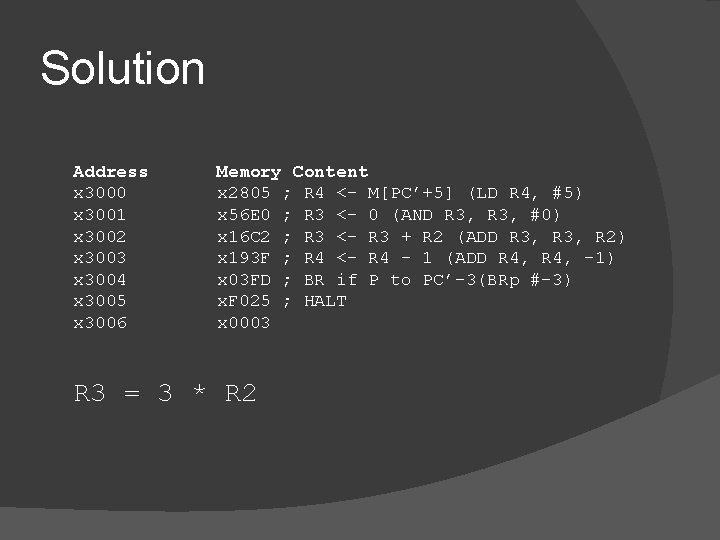

Problem 3 We are about to execute the following code snippet. Assume that before execution R 0 = 0 x 3030 and that the value stored at 0 x 300 A is 0 x 3020. Complete each of the below LC-3 machine instructions so that each instruction loads the data at address 0 x 3020 into R 1, or indicate that it is not possible and why. Address Instruction 0 x 3000 0010 0 x 3001 1010 0 x 3002 0110 0 x 3003 1110

Solution Address Instruction 0 x 3000 001 000011111 = 0 x 221 F 0 x 3001 1010 001 000001000 = 0 x. A 208 0 x 3002 0110 001 000 110000 = 0 x 6230 0 x 3003 Cannot be done (LEA)

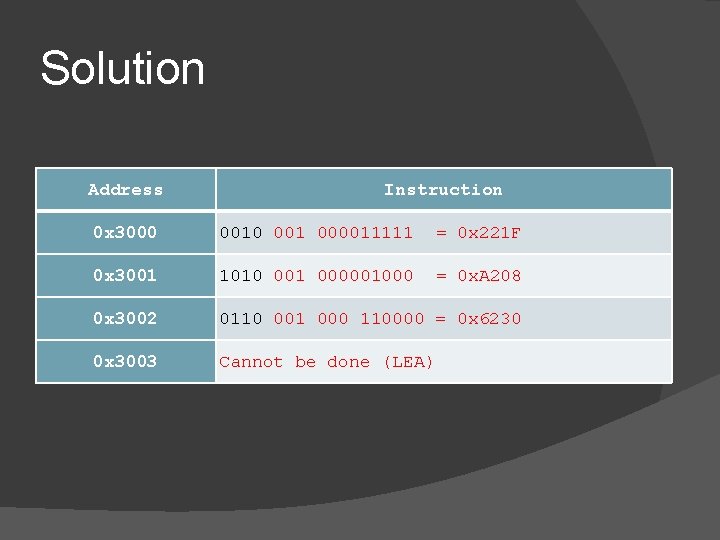

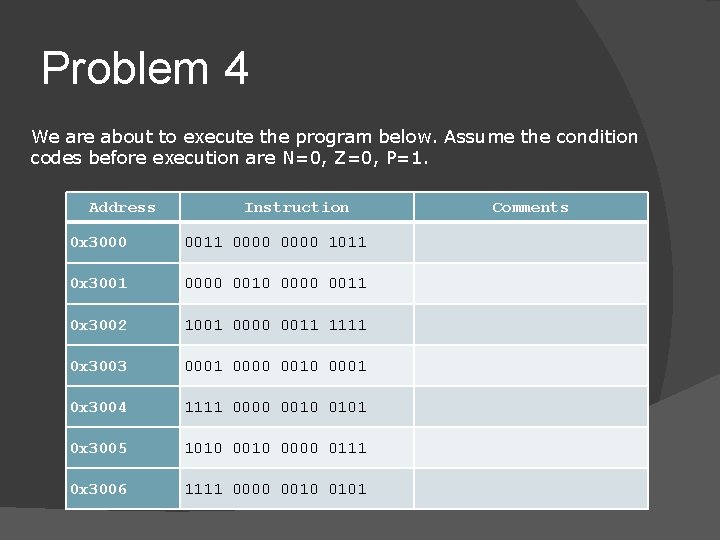

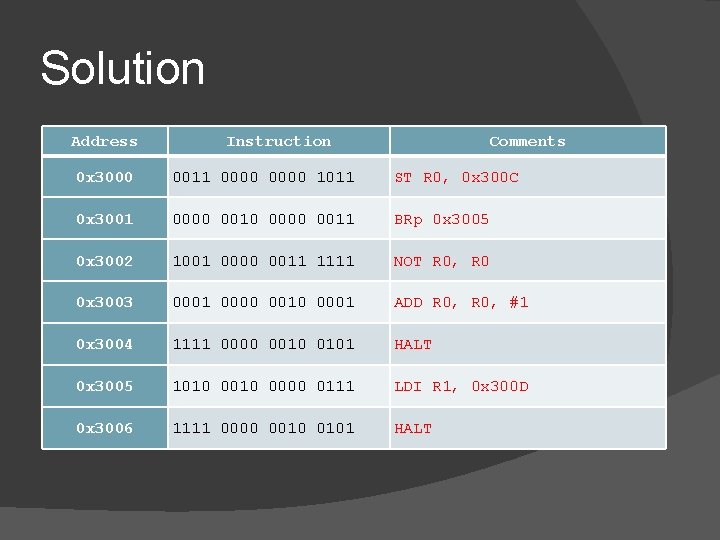

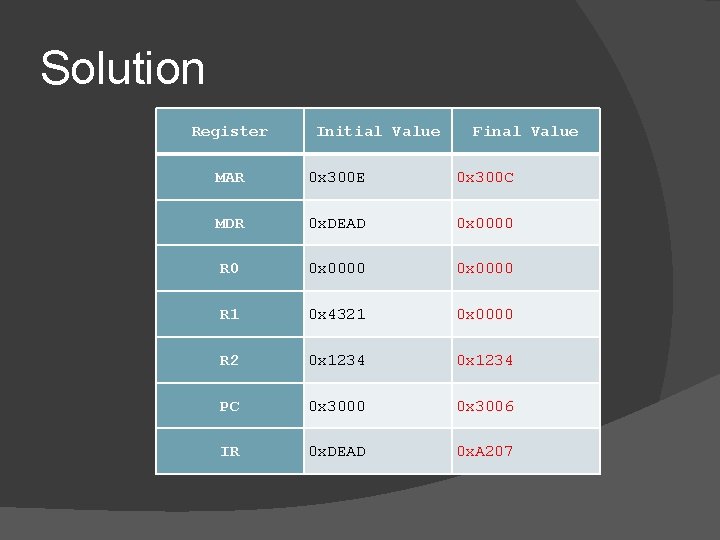

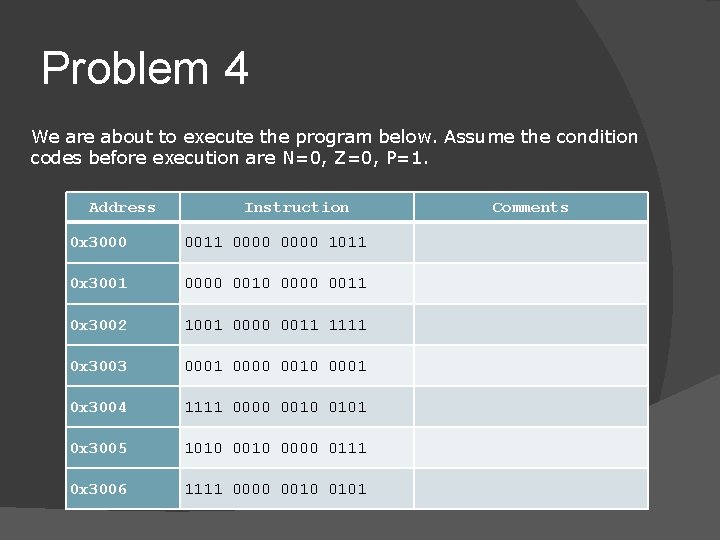

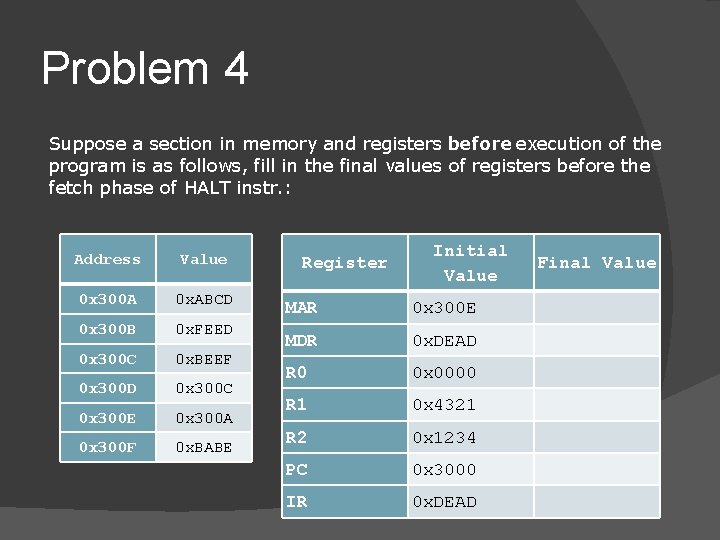

Problem 4 We are about to execute the program below. Assume the condition codes before execution are N=0, Z=0, P=1. Address Instruction 0 x 3000 0011 0000 1011 0 x 3001 0000 0010 0000 0011 0 x 3002 1001 0000 0011 1111 0 x 3003 0001 0000 0010 0001 0 x 3004 1111 0000 0010 0101 0 x 3005 1010 0000 0111 0 x 3006 1111 0000 0010 0101 Comments

Problem 4 Suppose a section in memory and registers before execution of the program is as follows, fill in the final values of registers before the fetch phase of HALT instr. : Address Value 0 x 300 A 0 x. ABCD 0 x 300 B 0 x. FEED 0 x 300 C 0 x. BEEF 0 x 300 D 0 x 300 C 0 x 300 E 0 x 300 A 0 x 300 F 0 x. BABE Register Initial Value Final Value MAR 0 x 300 E MDR 0 x. DEAD R 0 0 x 0000 R 1 0 x 4321 R 2 0 x 1234 PC 0 x 3000 IR 0 x. DEAD

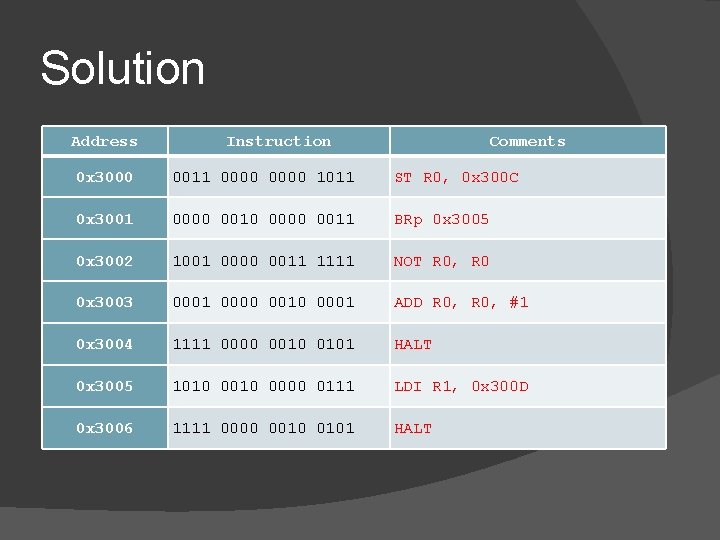

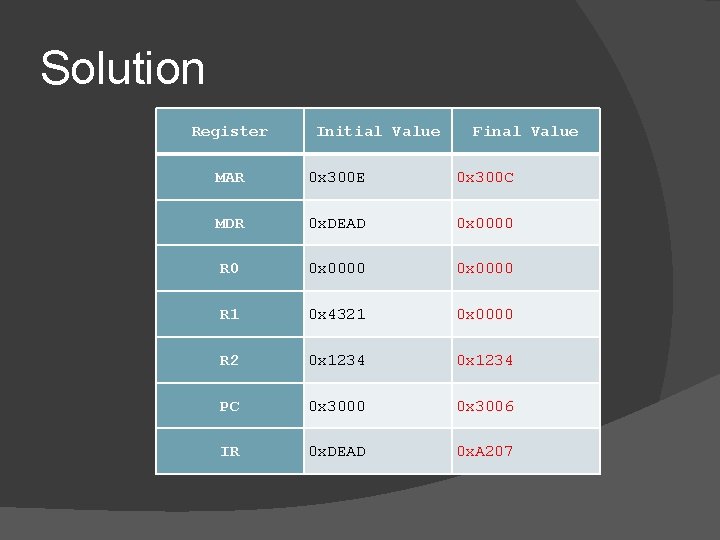

Solution Address Instruction Comments 0 x 3000 0011 0000 1011 ST R 0, 0 x 300 C 0 x 3001 0000 0010 0000 0011 BRp 0 x 3005 0 x 3002 1001 0000 0011 1111 NOT R 0, R 0 0 x 3003 0001 0000 0010 0001 ADD R 0, #1 0 x 3004 1111 0000 0010 0101 HALT 0 x 3005 1010 0000 0111 LDI R 1, 0 x 300 D 0 x 3006 1111 0000 0010 0101 HALT

Solution Register Initial Value Final Value MAR 0 x 300 E 0 x 300 C MDR 0 x. DEAD 0 x 0000 R 0 0 x 0000 R 1 0 x 4321 0 x 0000 R 2 0 x 1234 PC 0 x 3000 0 x 3006 IR 0 x. DEAD 0 x. A 207

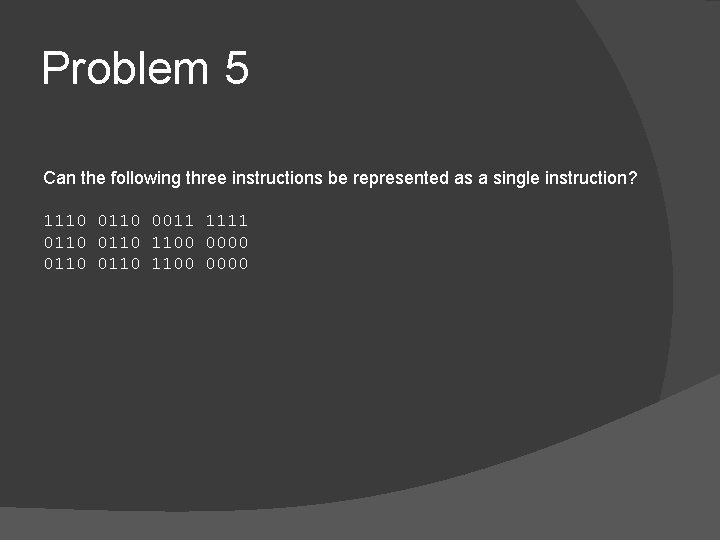

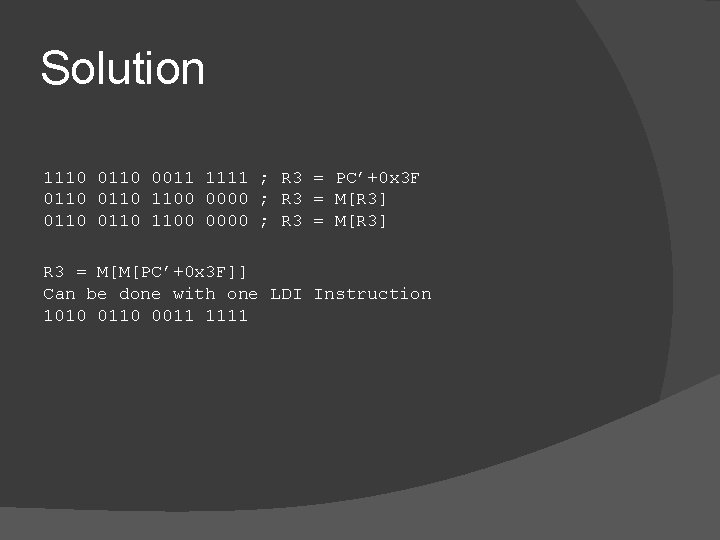

Problem 5 Can the following three instructions be represented as a single instruction? 1110 0011 1111 0110 1100 0000

Solution 1110 0011 1111 ; R 3 = PC’+0 x 3 F 0110 1100 0000 ; R 3 = M[R 3] R 3 = M[M[PC’+0 x 3 F]] Can be done with one LDI Instruction 1010 0110 0011 1111

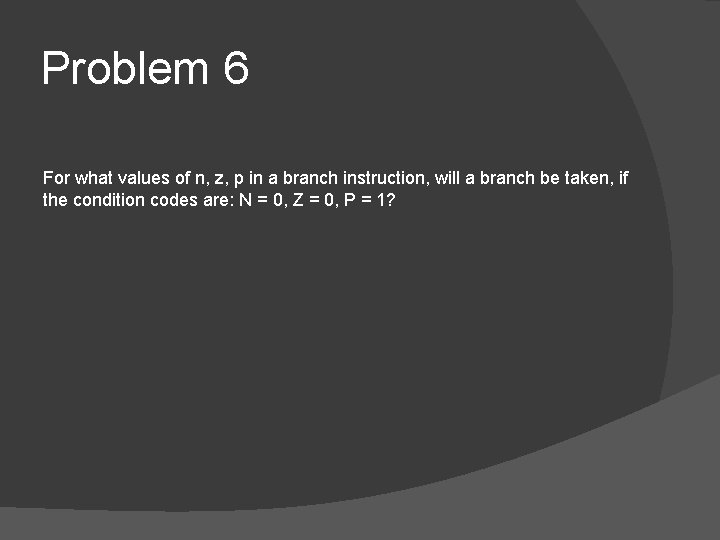

Problem 6 For what values of n, z, p in a branch instruction, will a branch be taken, if the condition codes are: N = 0, Z = 0, P = 1?

Solution P Condition Code is set So branch will be take for any combination of n, p, z where p = 1 n=0, p=1, z=0 n=1, p=1, z=0 n=0, p=1, z=1 n=1, p=1, z=1

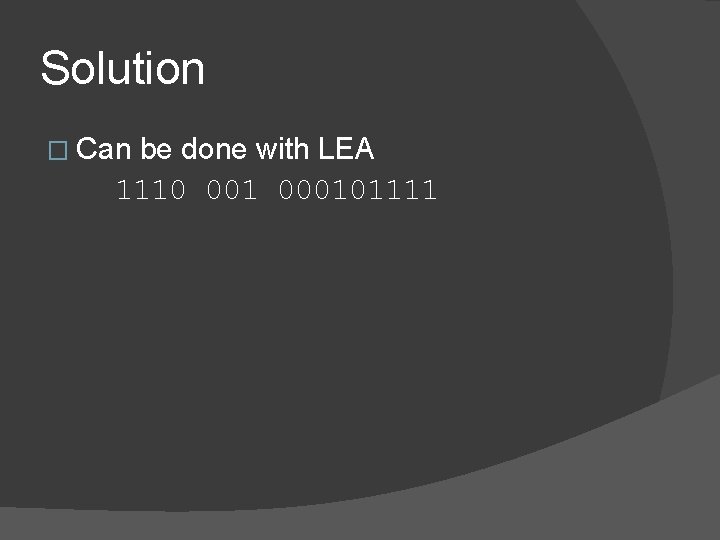

Problem 7 Assume that you need to store one of your favorite numbers, 0 x 3030, into R 1 using an instruction placed at 0 x 3000. However, your friend Phoebe tells you that it is impossible to put 0 x 3030 into R 1 using a single instruction. Do you agree with her? If you agree, give a reason why it is not possible to do this. If you do not agree, then write the instruction (in hex) which stores the value 0 x 3030 into R 1 using just one instruction placed at 0 x 3000. Note: You cannot assume the values of any of the registers or memory locations.

Solution � Can be done with LEA 1110 001 000101111

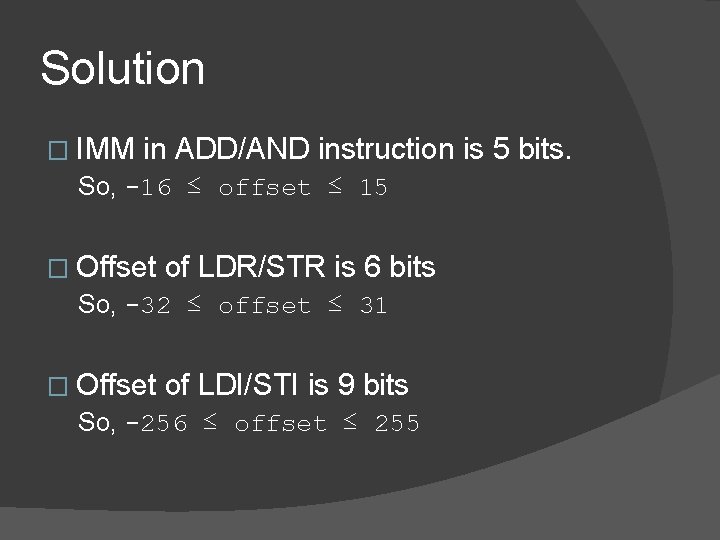

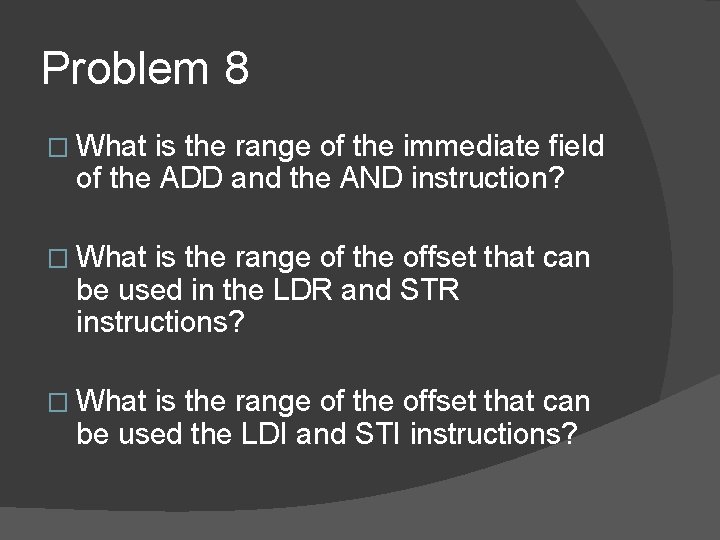

Problem 8 � What is the range of the immediate field of the ADD and the AND instruction? � What is the range of the offset that can be used in the LDR and STR instructions? � What is the range of the offset that can be used the LDI and STI instructions?

Solution � IMM in ADD/AND instruction is 5 bits. So, -16 ≤ offset ≤ 15 � Offset of LDR/STR is 6 bits So, -32 ≤ offset ≤ 31 � Offset of LDI/STI is 9 bits So, -256 ≤ offset ≤ 255

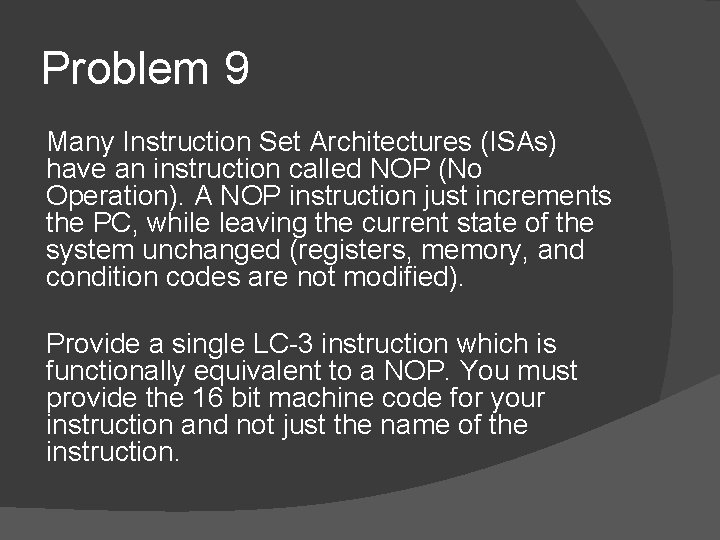

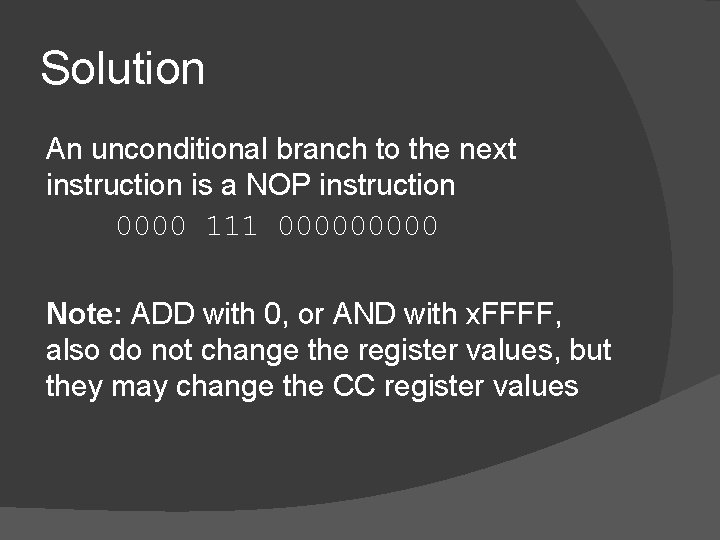

Problem 9 Many Instruction Set Architectures (ISAs) have an instruction called NOP (No Operation). A NOP instruction just increments the PC, while leaving the current state of the system unchanged (registers, memory, and condition codes are not modified). Provide a single LC-3 instruction which is functionally equivalent to a NOP. You must provide the 16 bit machine code for your instruction and not just the name of the instruction.

Solution An unconditional branch to the next instruction is a NOP instruction 0000 111 00000 Note: ADD with 0, or AND with x. FFFF, also do not change the register values, but they may change the CC register values

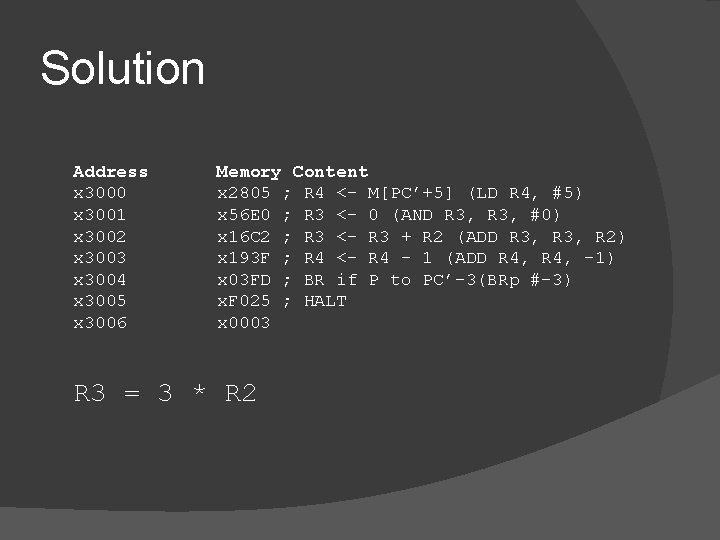

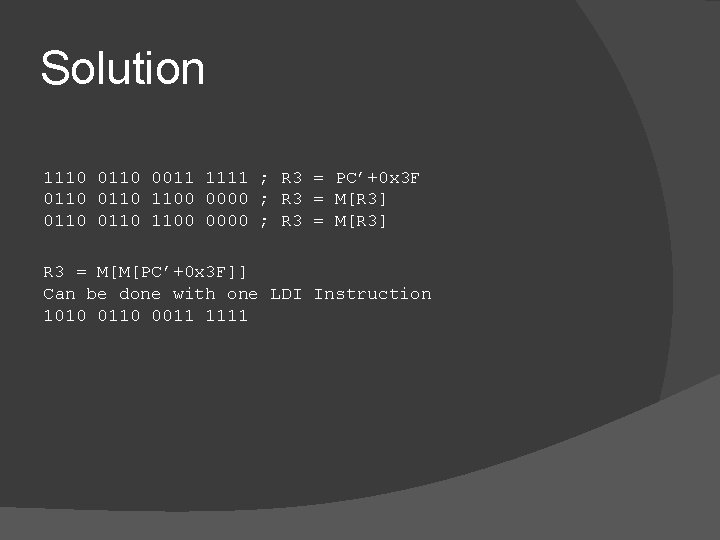

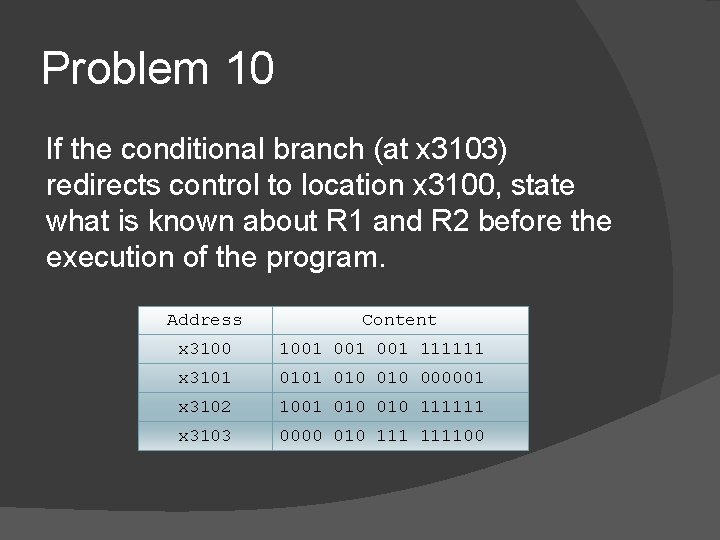

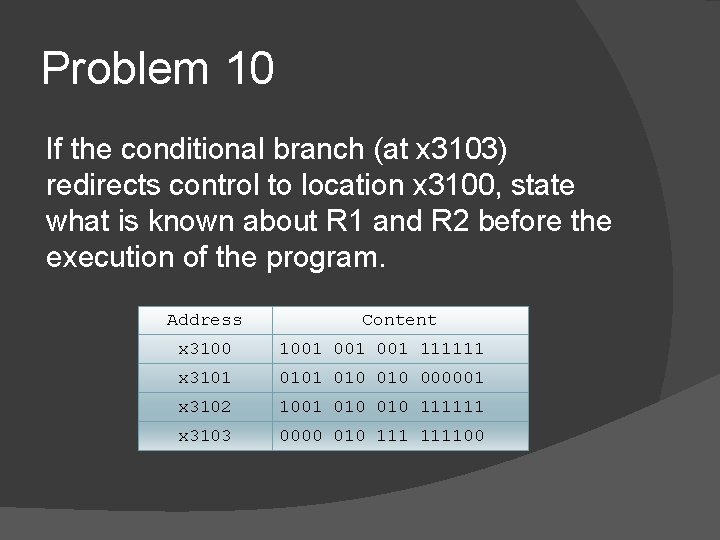

Problem 10 If the conditional branch (at x 3103) redirects control to location x 3100, state what is known about R 1 and R 2 before the execution of the program. Address Content x 3100 1001 001 111111 x 3101 010 000001 x 3102 1001 010 111111 x 3103 0000 010 111100

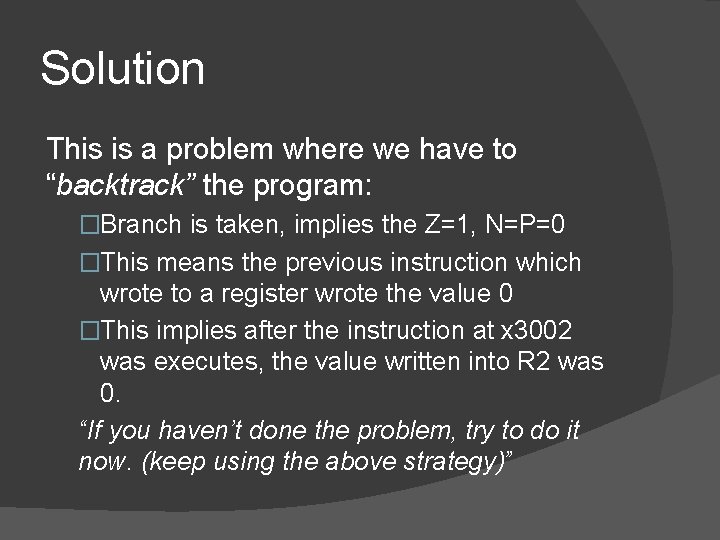

Solution This is a problem where we have to “backtrack” the program: �Branch is taken, implies the Z=1, N=P=0 �This means the previous instruction which wrote to a register wrote the value 0 �This implies after the instruction at x 3002 was executes, the value written into R 2 was 0. “If you haven’t done the problem, try to do it now. (keep using the above strategy)”

![Solution Instruction at x 3002 is R 2 NOTR 2 If R 2 Solution �Instruction at x 3002 is [R 2 = NOT(R 2)]. If R 2](https://slidetodoc.com/presentation_image_h/37c0e060a9b8721f0ad3421a3e4e7a89/image-73.jpg)

Solution �Instruction at x 3002 is [R 2 = NOT(R 2)]. If R 2 was 0 after the execution of the instruction, R 2 was 0 x. FFFF (or -1) before its execution. �Instruction at x 3001 is [R 2 = R 2 AND R 1]. If R 2 = 0 x. FFFF after execution of this instruction, then R 1 and R 2 should be 0 x. FFFF before its execution. �Instruction at x 3000 is [R 1 = NOT(R 1)]. If R 1 is 0 x. FFFF after the execution of the instruction, R 1 = 0 before its execution. So, R 1 = 0, R 2 = 0 x. FFFF