Chapter 5 Interconnect RLC Model n Efficient capacitance

![Extension to Random Nets [Xu-HE, GLSVLSI’ 01] n Nets with arbitrary locations, lengths, thickness, Extension to Random Nets [Xu-HE, GLSVLSI’ 01] n Nets with arbitrary locations, lengths, thickness,](https://slidetodoc.com/presentation_image_h/a1b82c4c245c7e3a109ce67434c323c4/image-18.jpg)

- Slides: 26

Chapter 5 Interconnect RLC Model n Efficient capacitance model üEfficient inductance model üRC and RLC circuit model generation n Numeric based interconnect modeling

Is RC Model still Sufficient? n Interconnect impedance is more than resistance u Z R +j L u n 1/tr On-chip inductance should be considered u When L becomes comparable to R as we move towards Ghz+ designs

Candidates for On-Chip Inductance n Wide clock trees u Skews are different under RLC and RC models u Neighboring signals are disturbed due to large clock di/dt noise n Fast edge rate (~100 ps) buses u RC model under-estimates crosstalk n P/G grids (and C 4 bumps) u di/dt noise might overweight IR drop

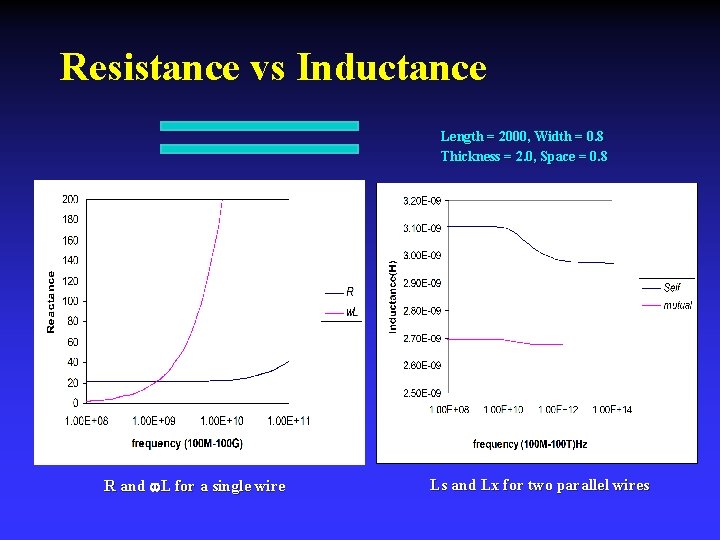

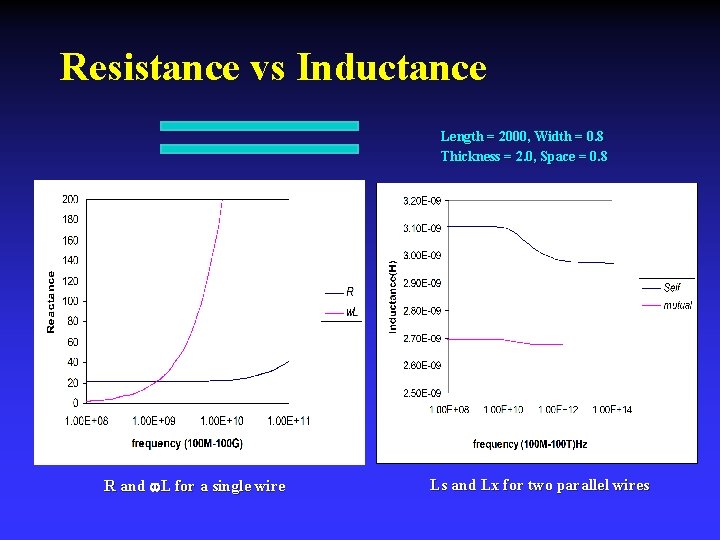

Resistance vs Inductance Length = 2000, Width = 0. 8 Thickness = 2. 0, Space = 0. 8 R and L for a single wire Ls and Lx for two parallel wires

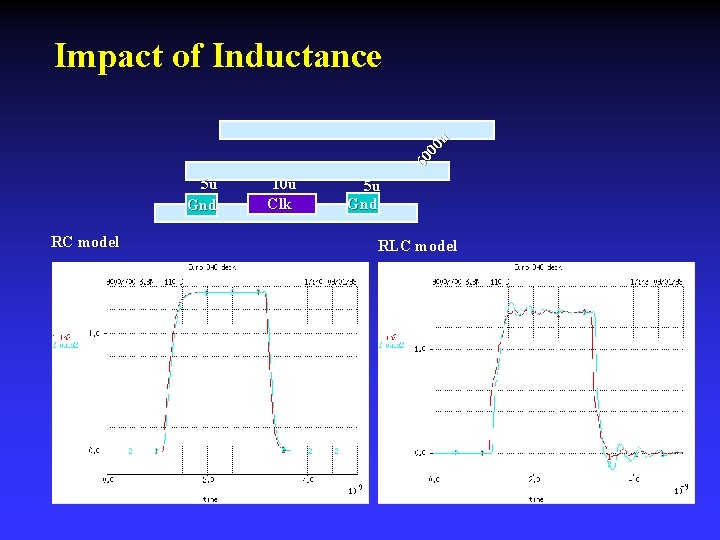

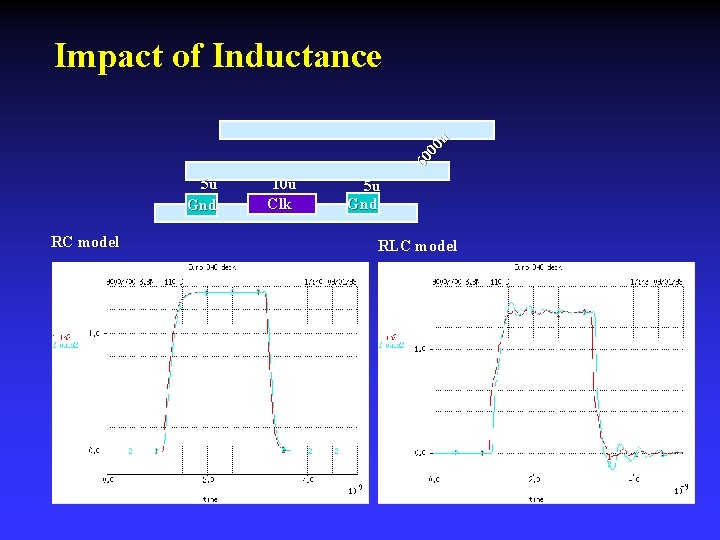

60 00 u Impact of Inductance 5 u Gnd RC model 10 u Clk 5 u Gnd RLC model

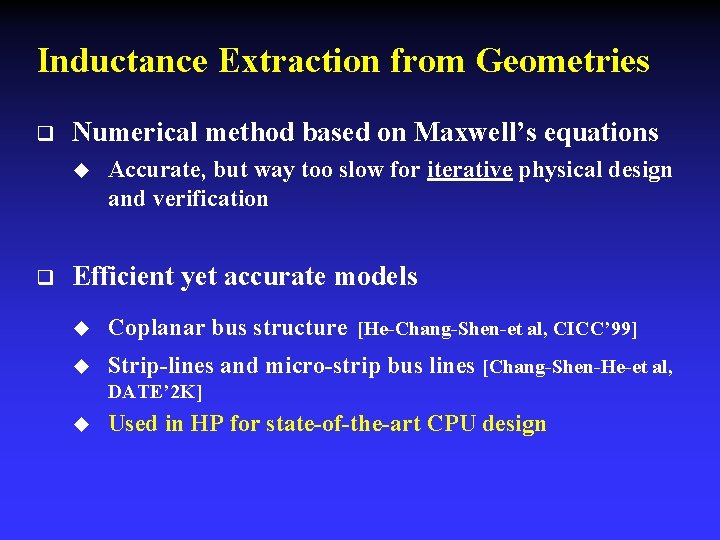

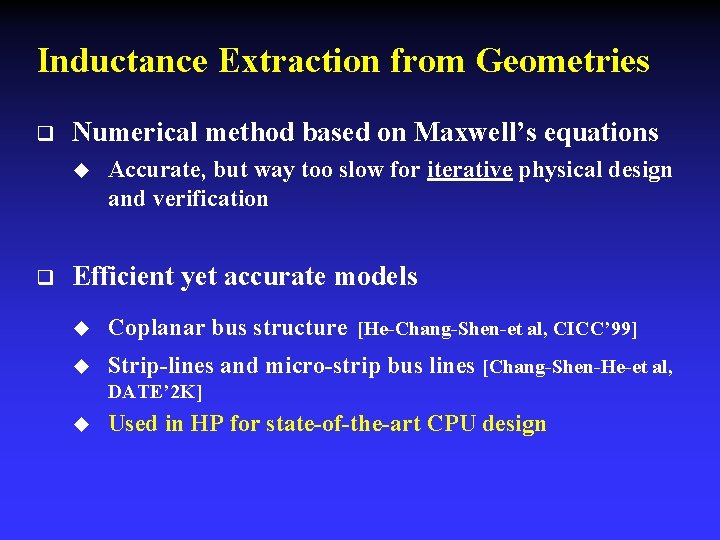

Inductance Extraction from Geometries q Numerical method based on Maxwell’s equations u q Accurate, but way too slow for iterative physical design and verification Efficient yet accurate models u Coplanar bus structure [He-Chang-Shen-et al, CICC’ 99] u Strip-lines and micro-strip bus lines [Chang-Shen-He-et al, DATE’ 2 K] u Used in HP for state-of-the-art CPU design

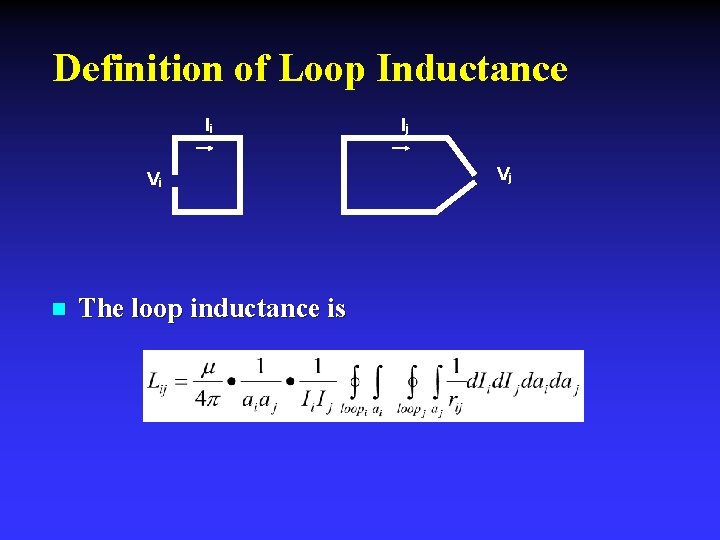

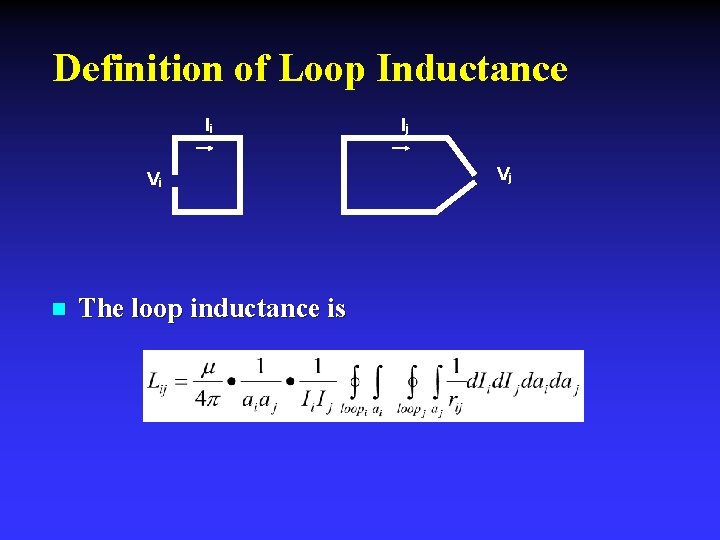

Definition of Loop Inductance Ii Vi n The loop inductance is Ij Vj

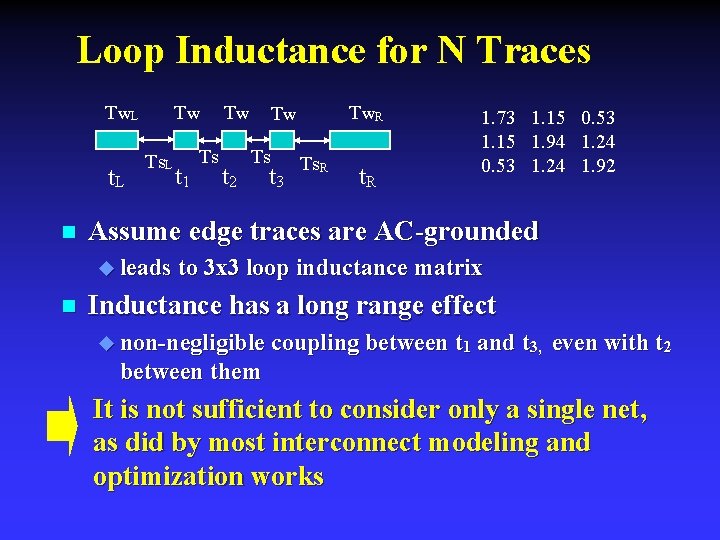

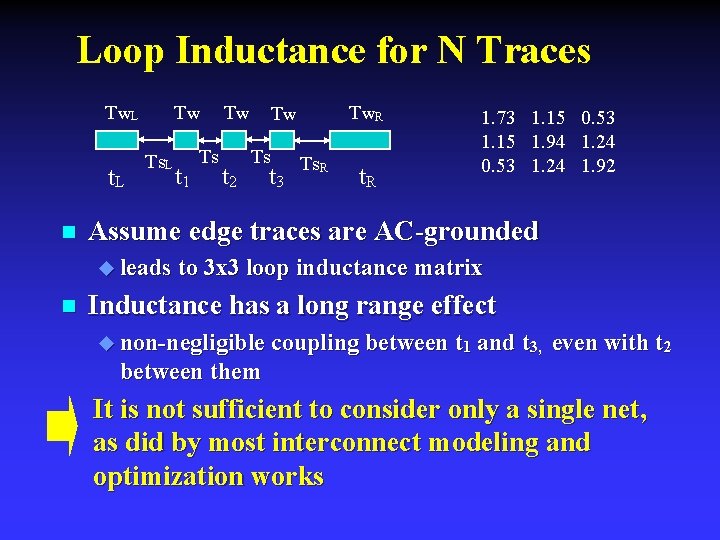

Loop Inductance for N Traces Tw T w. L t. L n Ts. L t 1 Ts Tw t 2 T w. R Tw Ts t 3 Ts. R t. R 1. 73 1. 15 0. 53 1. 15 1. 94 1. 24 0. 53 1. 24 1. 92 Assume edge traces are AC-grounded u leads to 3 x 3 loop inductance matrix n Inductance has a long range effect u non-negligible coupling between t 1 and t 3, even with t 2 between them It is not sufficient to consider only a single net, as did by most interconnect modeling and optimization works

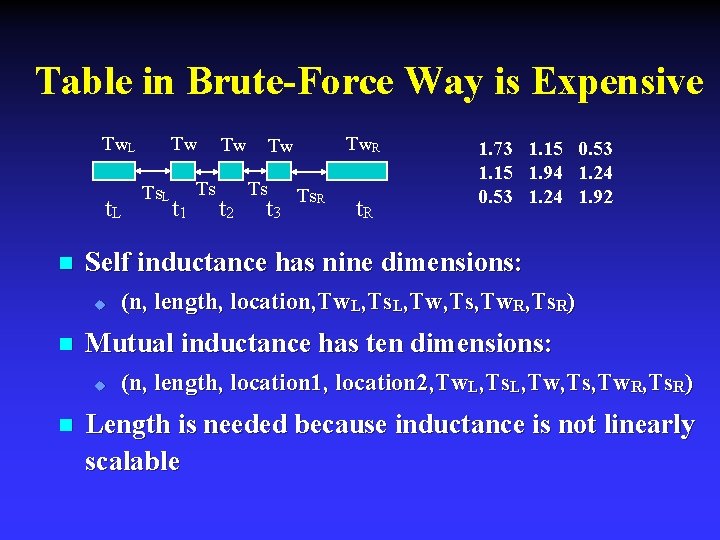

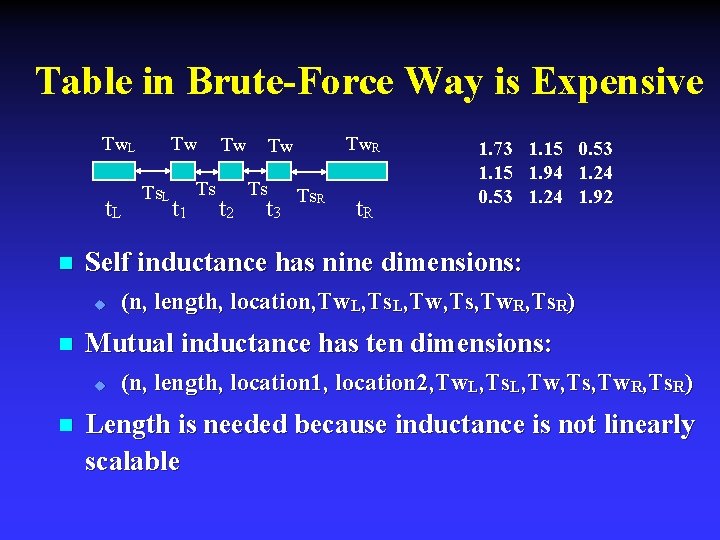

Table in Brute-Force Way is Expensive Tw T w. L t. L n t 2 Ts t 3 Ts. R t. R 1. 73 1. 15 0. 53 1. 15 1. 94 1. 24 0. 53 1. 24 1. 92 (n, length, location, Tw. L, Ts. L, Tw, Ts, Tw. R, Ts. R) Mutual inductance has ten dimensions: u n t 1 Ts T w. R Tw Self inductance has nine dimensions: u n Ts. L Tw (n, length, location 1, location 2, Tw. L, Ts. L, Tw, Ts, Tw. R, Ts. R) Length is needed because inductance is not linearly scalable

Definition of Partial Inductance Vi n Vj Partial inductance is the portion of loop inductance for a segment when its current returns via the infinity u called partial element equivalent circuit (PEEC) model n If current is uniform (no skin effect), the partial inductance is

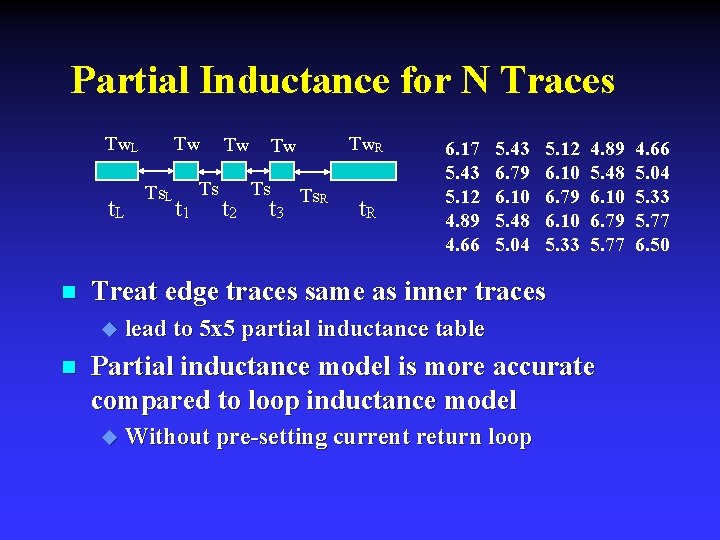

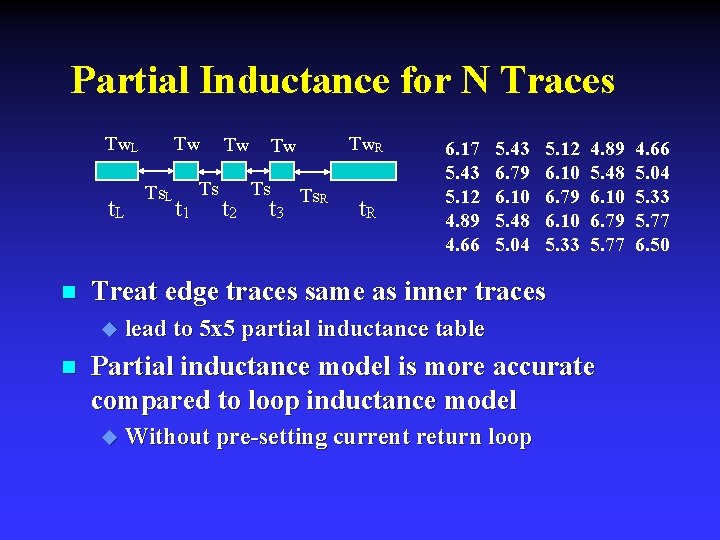

Partial Inductance for N Traces Tw T w. L t. L n t 1 Ts t 2 T w. R Tw Ts t 3 Ts. R t. R 6. 17 5. 43 5. 12 4. 89 4. 66 5. 43 6. 79 6. 10 5. 48 5. 04 5. 12 6. 10 6. 79 6. 10 5. 33 4. 89 5. 48 6. 10 6. 79 5. 77 Treat edge traces same as inner traces u n Ts. L Tw lead to 5 x 5 partial inductance table Partial inductance model is more accurate compared to loop inductance model u Without pre-setting current return loop 4. 66 5. 04 5. 33 5. 77 6. 50

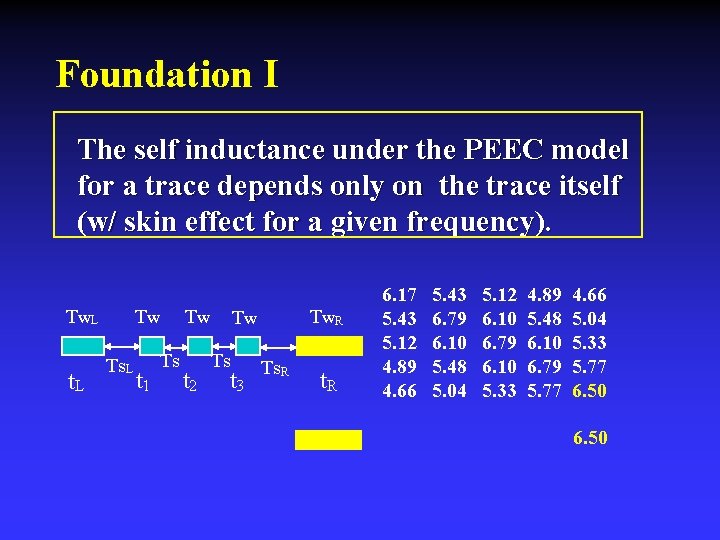

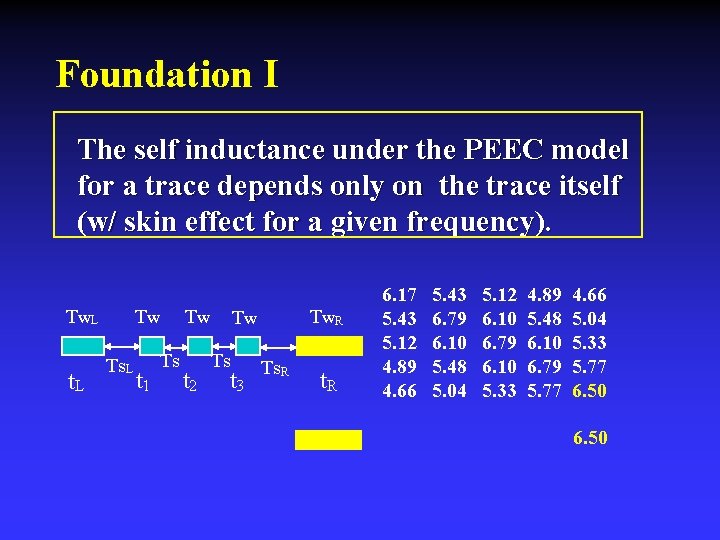

Foundation I The self inductance under the PEEC model for a trace depends only on the trace itself (w/ skin effect for a given frequency). T w. L t. L Tw Ts. L t 1 Ts Tw t 2 T w. R Tw Ts t 3 Ts. R t. R 6. 17 5. 43 5. 12 4. 89 4. 66 5. 43 6. 79 6. 10 5. 48 5. 04 5. 12 6. 10 6. 79 6. 10 5. 33 4. 89 5. 48 6. 10 6. 79 5. 77 4. 66 5. 04 5. 33 5. 77 6. 50

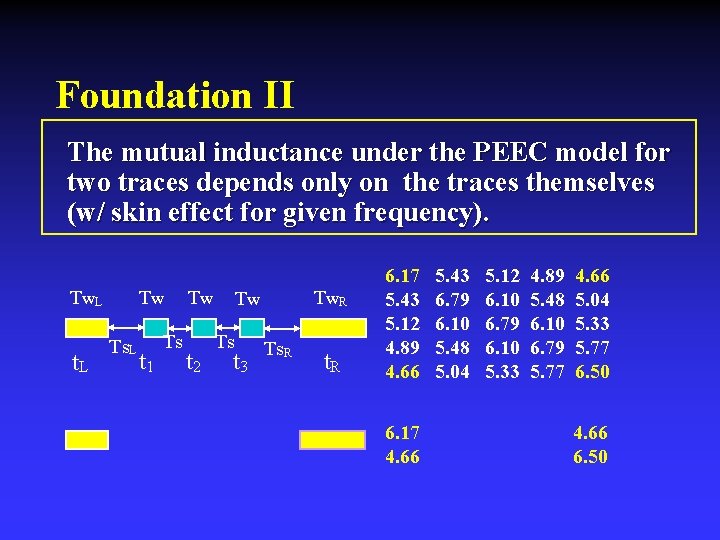

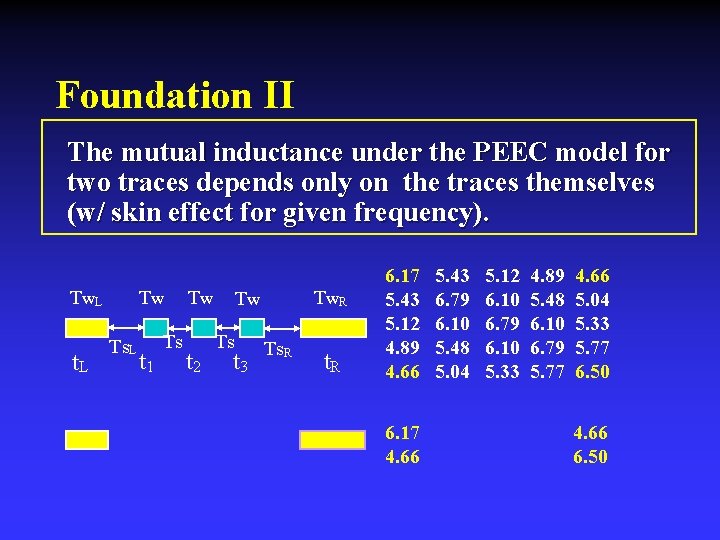

Foundation II The mutual inductance under the PEEC model for two traces depends only on the traces themselves (w/ skin effect for given frequency). Tw T w. L t. L Ts. L t 1 Ts Tw t 2 T w. R Tw Ts t 3 Ts. R t. R 6. 17 5. 43 5. 12 4. 89 4. 66 6. 17 4. 66 5. 43 6. 79 6. 10 5. 48 5. 04 5. 12 6. 10 6. 79 6. 10 5. 33 4. 89 5. 48 6. 10 6. 79 5. 77 4. 66 5. 04 5. 33 5. 77 6. 50 4. 66 6. 50

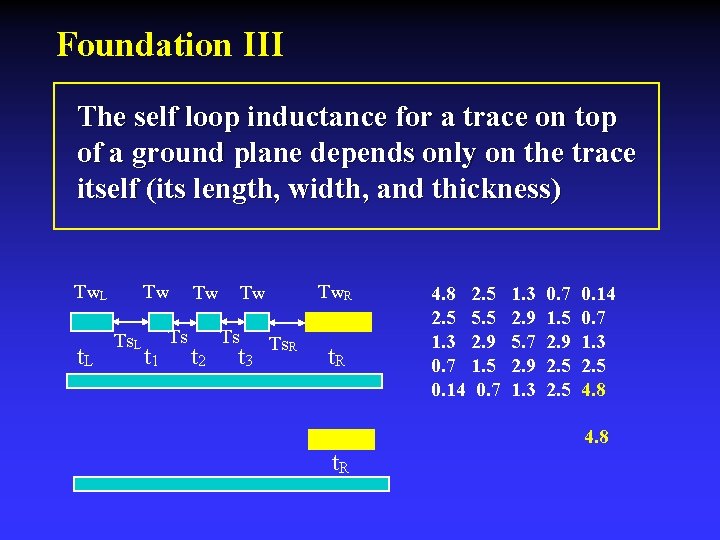

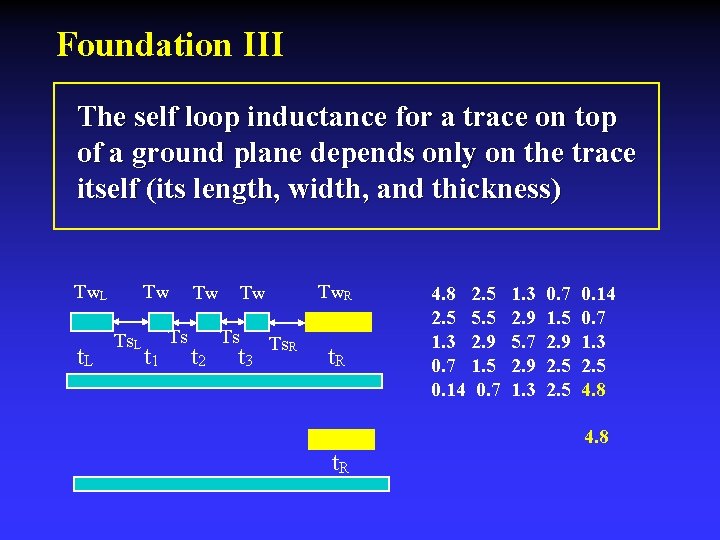

Foundation III The self loop inductance for a trace on top of a ground plane depends only on the trace itself (its length, width, and thickness) T w. L t. L Tw Ts. L t 1 Ts Tw t 2 T w. R Tw Ts t 3 Ts. R t. R 4. 8 2. 5 5. 5 1. 3 2. 9 0. 7 1. 5 0. 14 0. 7 1. 3 2. 9 5. 7 2. 9 1. 3 0. 7 1. 5 2. 9 2. 5 0. 14 0. 7 1. 3 2. 5 4. 8 t. R

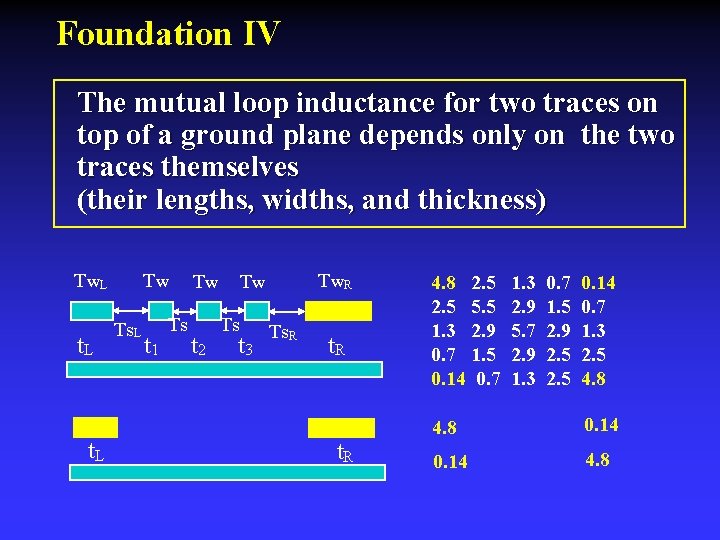

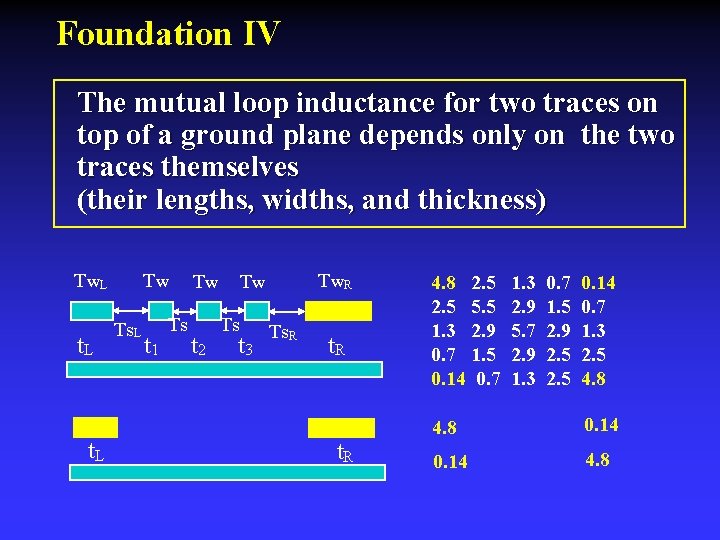

Foundation IV The mutual loop inductance for two traces on top of a ground plane depends only on the two traces themselves (their lengths, widths, and thickness) T w. L t. L Tw Ts. L t 1 Ts Tw t 2 T w. R Tw Ts t 3 Ts. R t. R 4. 8 2. 5 5. 5 1. 3 2. 9 0. 7 1. 5 0. 14 0. 7 1. 3 2. 9 5. 7 2. 9 1. 3 0. 7 1. 5 2. 9 2. 5 0. 14 0. 7 1. 3 2. 5 4. 8 0. 14 4. 8

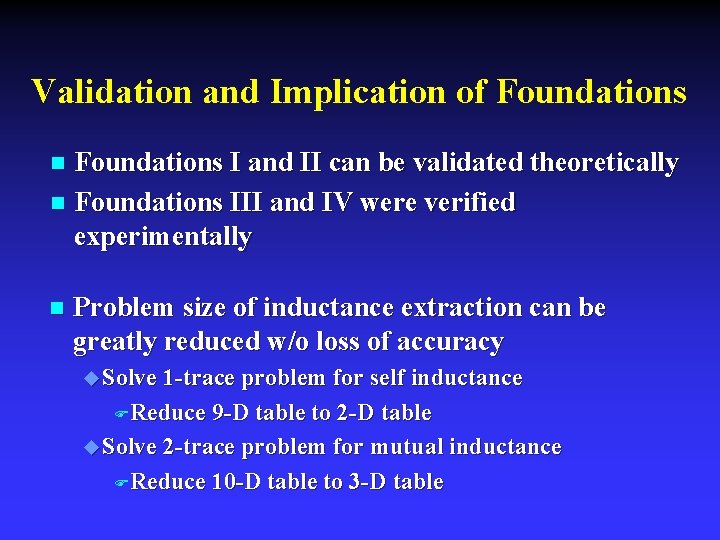

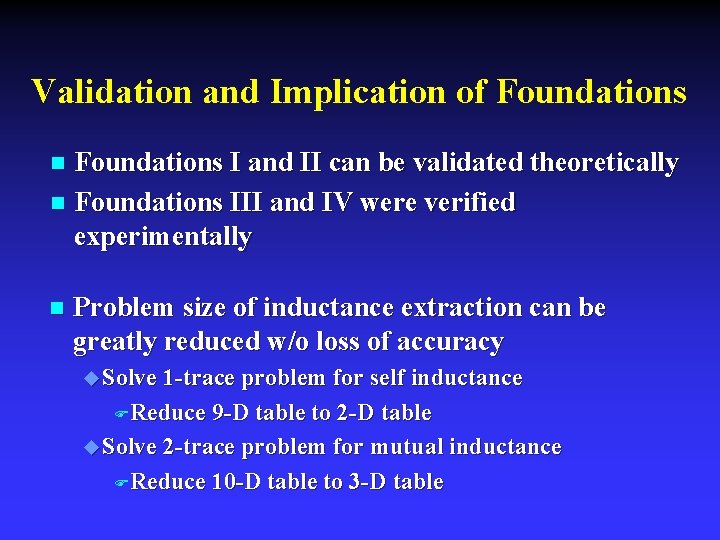

Validation and Implication of Foundations I and II can be validated theoretically n Foundations III and IV were verified experimentally n n Problem size of inductance extraction can be greatly reduced w/o loss of accuracy u Solve 1 -trace problem for self inductance F Reduce 9 -D table to 2 -D table u Solve 2 -trace problem for mutual inductance F Reduce 10 -D table to 3 -D table

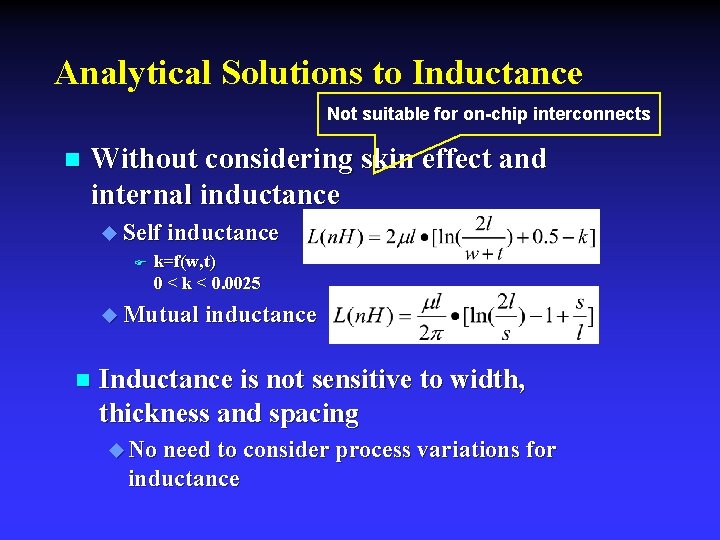

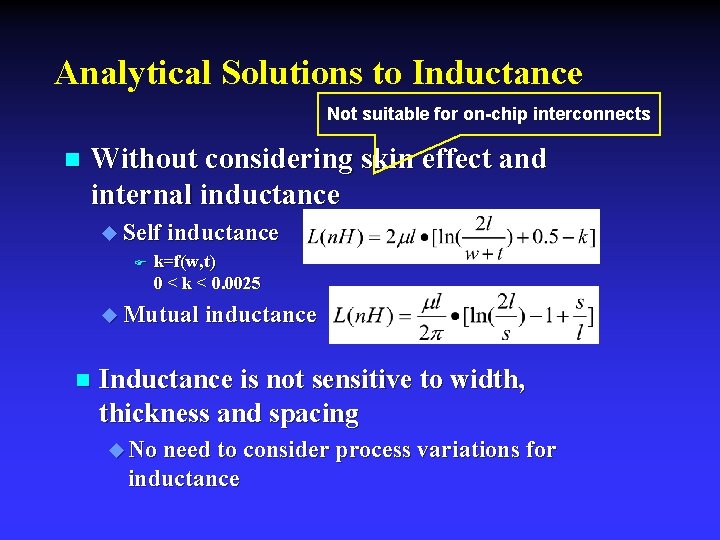

Analytical Solutions to Inductance Not suitable for on-chip interconnects n Without considering skin effect and internal inductance u Self inductance F k=f(w, t) 0 < k < 0. 0025 u Mutual inductance n Inductance is not sensitive to width, thickness and spacing u No need to consider process variations for inductance

![Extension to Random Nets XuHE GLSVLSI 01 n Nets with arbitrary locations lengths thickness Extension to Random Nets [Xu-HE, GLSVLSI’ 01] n Nets with arbitrary locations, lengths, thickness,](https://slidetodoc.com/presentation_image_h/a1b82c4c245c7e3a109ce67434c323c4/image-18.jpg)

Extension to Random Nets [Xu-HE, GLSVLSI’ 01] n Nets with arbitrary locations, lengths, thickness, and etc. u n available as a web-based tool http: //eda. ece. wisc. edu/Web. Henry Mutual inductance Lab = a b Mutual inductance Lm 1 + Lm 2 Lm 3 Lm 4

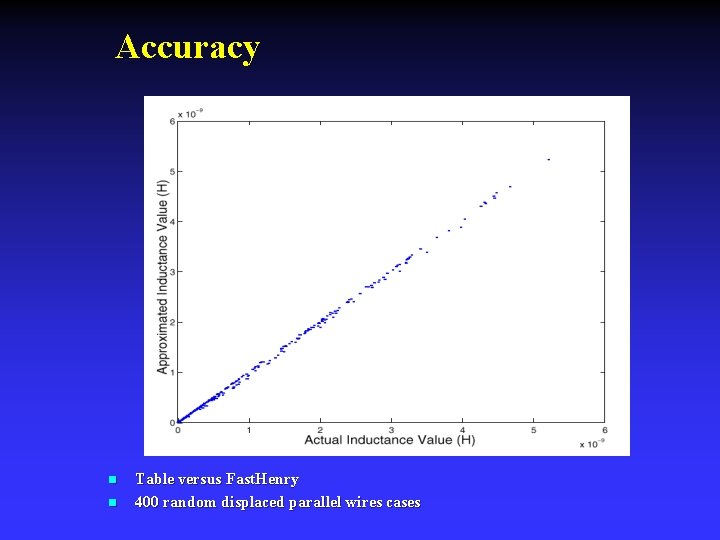

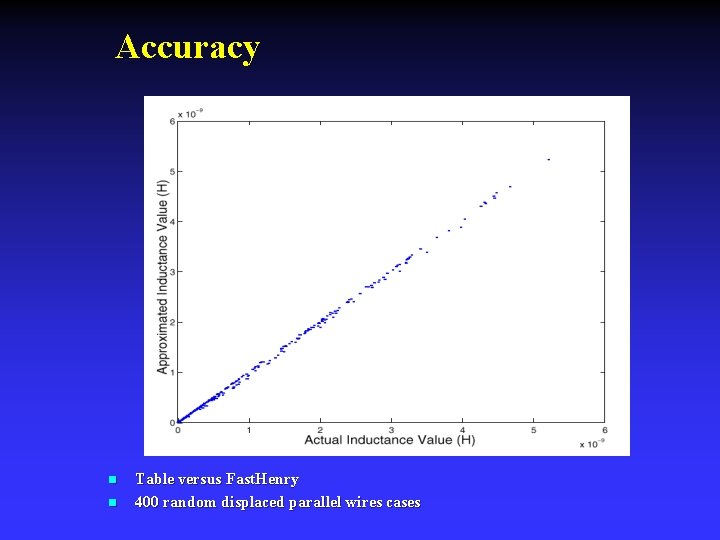

Accuracy n n Table versus Fast. Henry 400 random displaced parallel wires cases

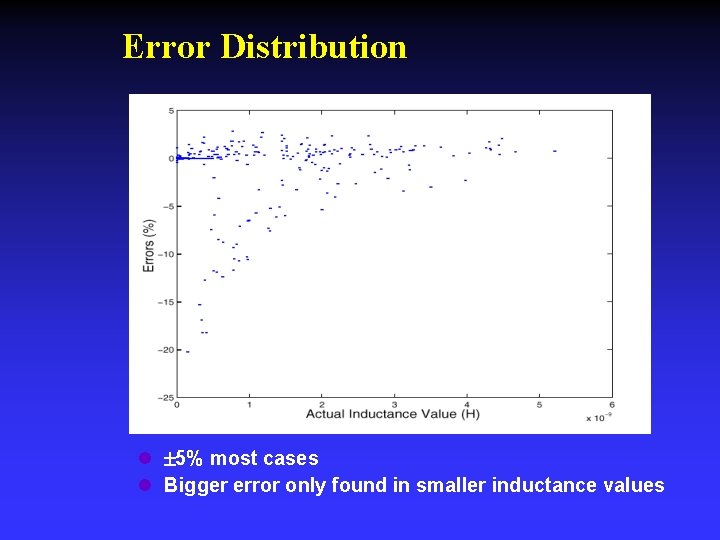

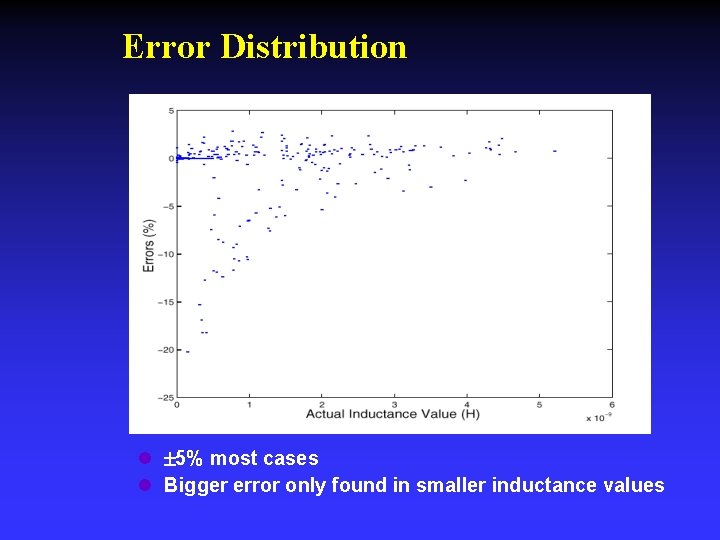

Error Distribution l 5% most cases l Bigger error only found in smaller inductance values

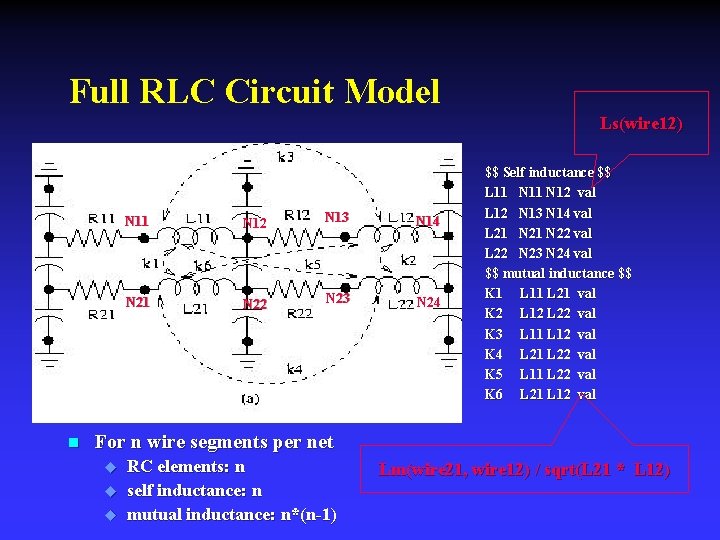

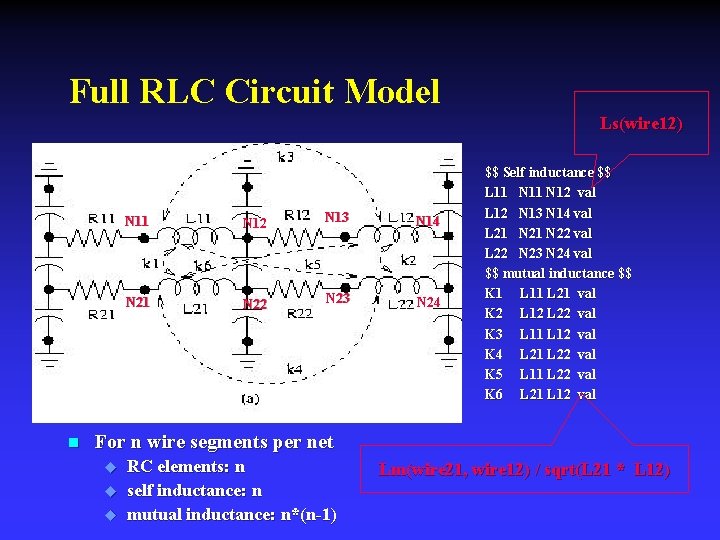

Full RLC Circuit Model Ls(wire 12) n N 11 N 12 N 13 N 14 N 21 N 22 N 23 N 24 $$ Self inductance $$ L 11 N 12 val L 12 N 13 N 14 val L 21 N 22 val L 22 N 23 N 24 val $$ mutual inductance $$ K 1 L 11 L 21 val K 2 L 12 L 22 val K 3 L 11 L 12 val K 4 L 21 L 22 val K 5 L 11 L 22 val K 6 L 21 L 12 val For n wire segments per net u u u RC elements: n self inductance: n mutual inductance: n*(n-1) Lm(wire 21, wire 12) / sqrt(L 21 * L 12)

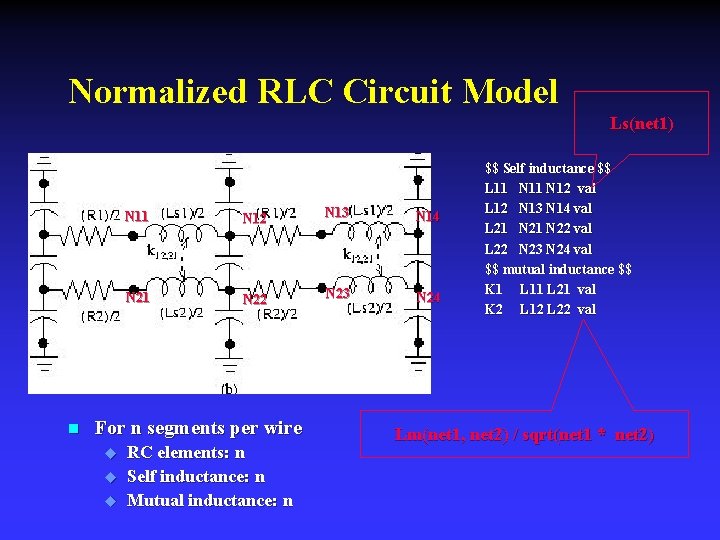

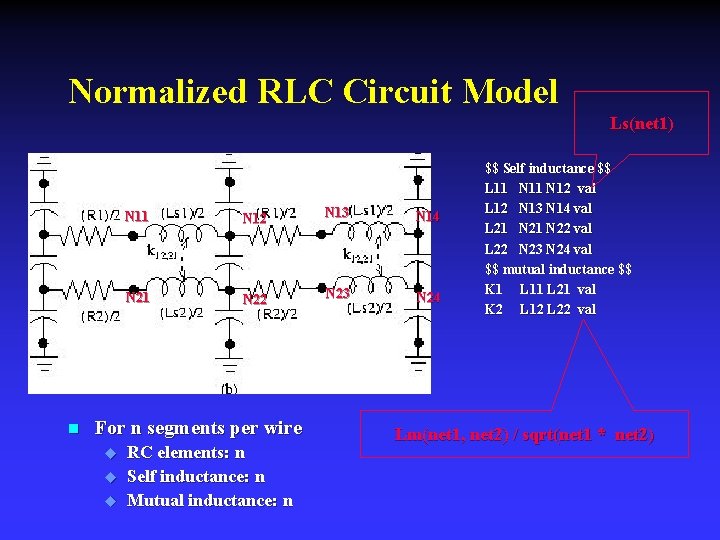

Normalized RLC Circuit Model Ls(net 1) n N 11 N 12 N 13 N 14 N 21 N 22 N 23 N 24 For n segments per wire u u u RC elements: n Self inductance: n Mutual inductance: n $$ Self inductance $$ L 11 N 12 val L 12 N 13 N 14 val L 21 N 22 val L 22 N 23 N 24 val $$ mutual inductance $$ K 1 L 11 L 21 val K 2 L 12 L 22 val Lm(net 1, net 2) / sqrt(net 1 * net 2)

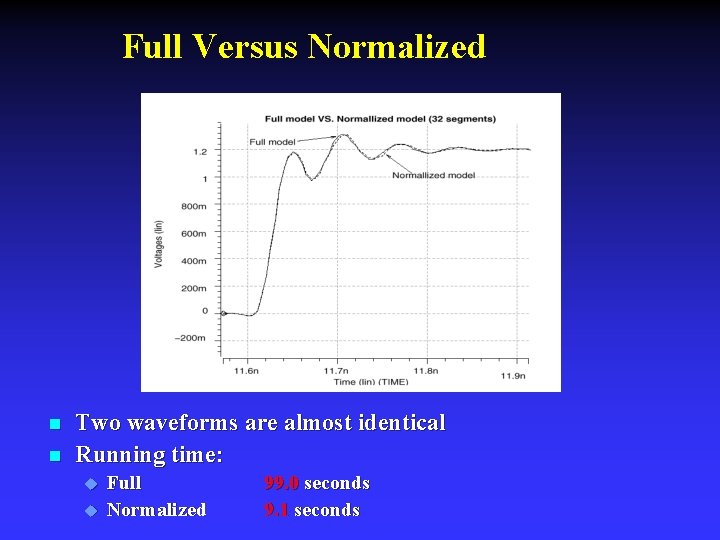

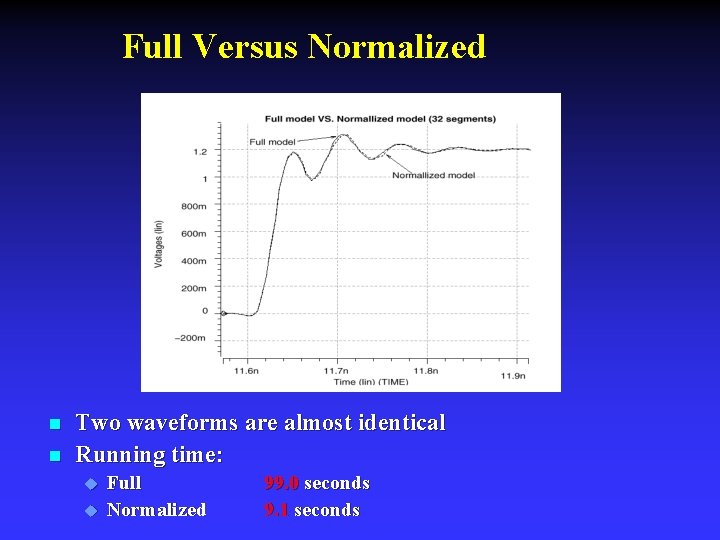

Full Versus Normalized n n Two waveforms are almost identical Running time: u u Full Normalized 99. 0 seconds 9. 1 seconds

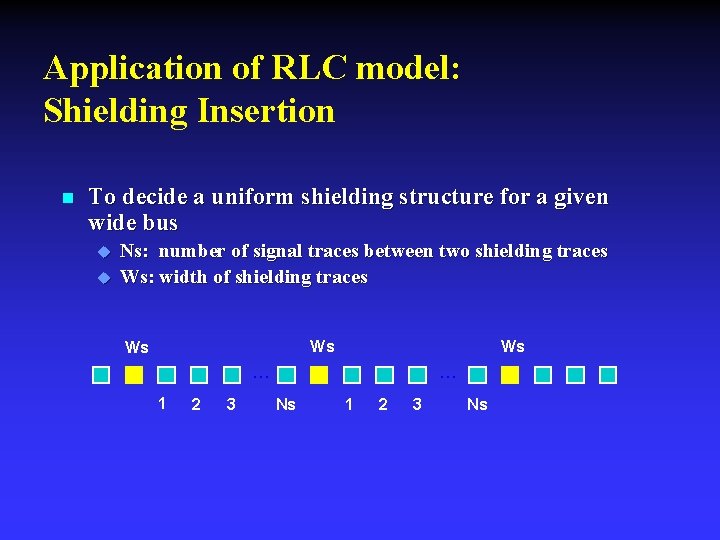

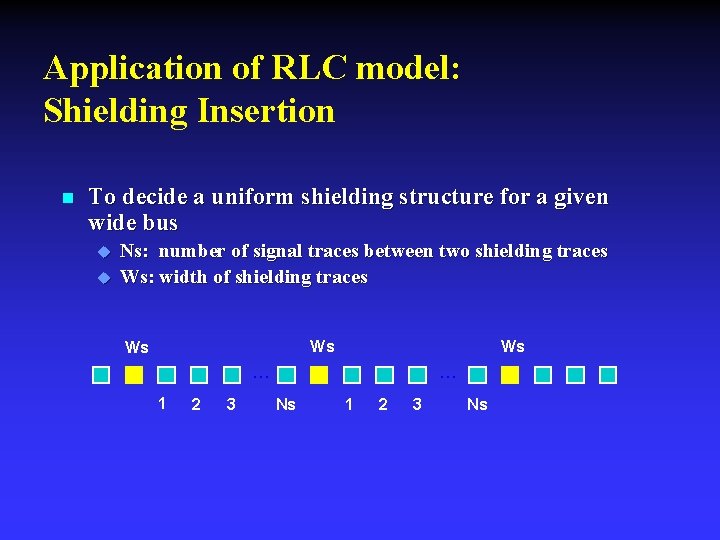

Application of RLC model: Shielding Insertion n To decide a uniform shielding structure for a given wide bus u u Ns: number of signal traces between two shielding traces Ws: width of shielding traces Ws Ws Ws . . . 1 2 3 . . . Ns 1 2 3 Ns

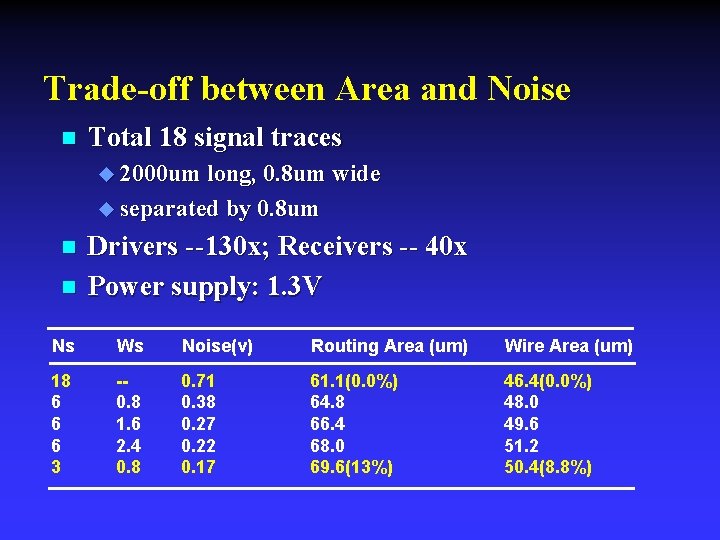

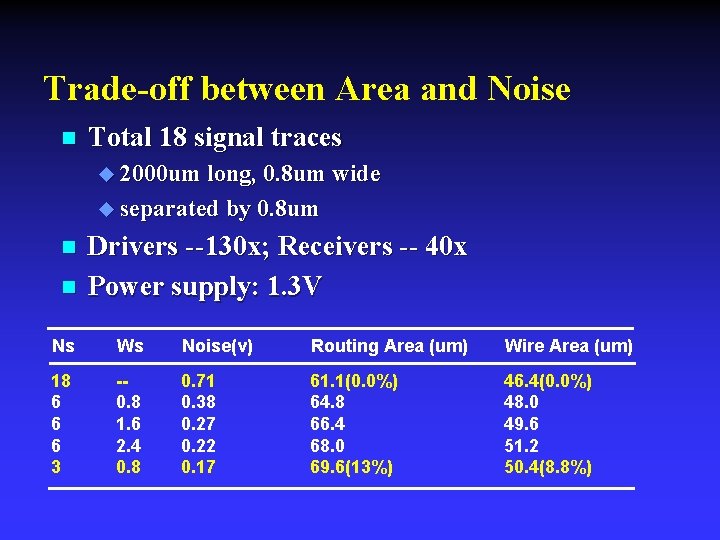

Trade-off between Area and Noise n Total 18 signal traces u 2000 um long, 0. 8 um wide u separated by 0. 8 um n n Drivers -- 130 x; Receivers -- 40 x Power supply: 1. 3 V Ns Ws Noise(v) Routing Area (um) Wire Area (um) 18 6 6 6 3 -0. 8 1. 6 2. 4 0. 8 0. 71 0. 38 0. 27 0. 22 0. 17 61. 1(0. 0%) 64. 8 66. 4 68. 0 69. 6(13%) 46. 4(0. 0%) 48. 0 49. 6 51. 2 50. 4(8. 8%)

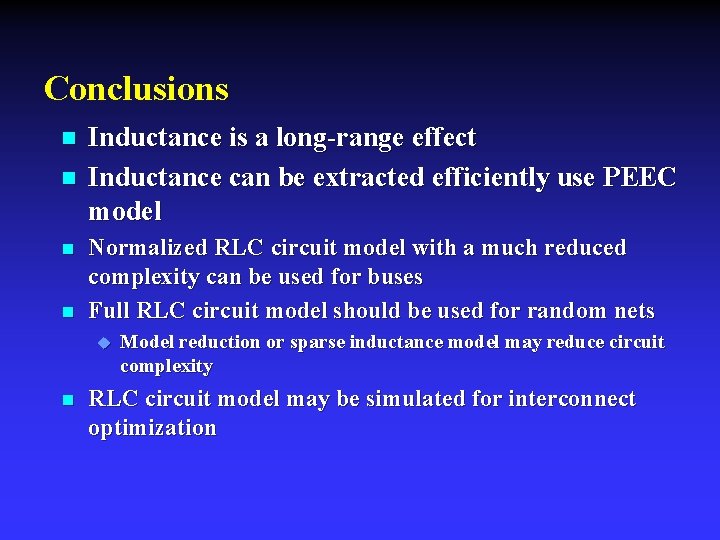

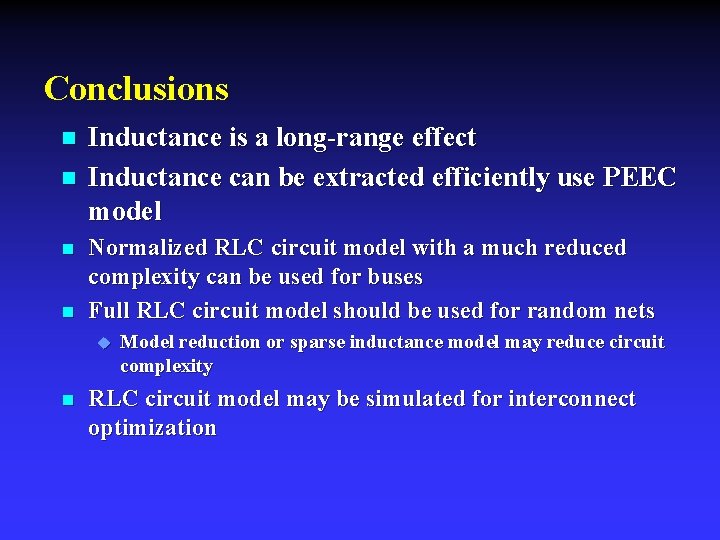

Conclusions n n Inductance is a long-range effect Inductance can be extracted efficiently use PEEC model Normalized RLC circuit model with a much reduced complexity can be used for buses Full RLC circuit model should be used for random nets u n Model reduction or sparse inductance model may reduce circuit complexity RLC circuit model may be simulated for interconnect optimization