Chapter 5 Instructor Mozafar BagMohammadi Spring 2010 Ilam

Chapter 5 Instructor: Mozafar Bag-Mohammadi Spring 2010 Ilam University

Processor Implementation l l l Sequential logic design review (brief) Clock methodology (FSD) Datapath – 1 CPI l Single instruction, 2’s complement, unsigned Control Multiple cycle implementation (information only) Microprogramming Exceptions

Review: Sequential Logic is combinational if output is solely function of inputs l l E. g. ALU of previous lecture Logic is sequential or “has state” if output function of: l l Past and current inputs Past inputs remembered in “state”

Review: Sequential Logic l l Clock high, Q = D, ~Q = ~D after prop. delay Clock low Q, ~Q remain unchanged l Level-sensitive latch

Review: Sequential Logic l E. g. Master/Slave D flip-flop l l While clock high, QM follows D, but QS holds At falling edge QM propagates to QS

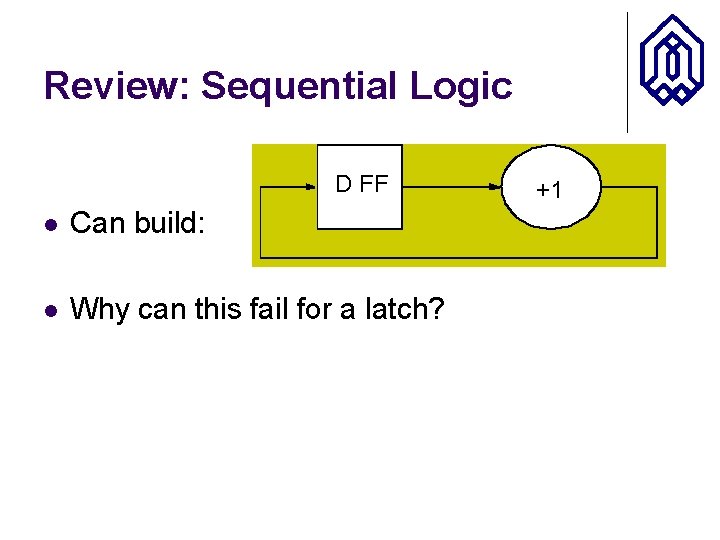

Review: Sequential Logic D FF l Can build: l Why can this fail for a latch? +1

Clocking Methodology l Motivation l l Design data and control without considering clock Use Fully Synchronous Design (FSD) l Just a convention to simplify design process l Restricts design freedom l Eliminates complexity, can guarantee timing correctness l Not really feasible in real designs l Even in this course you will violate FSD

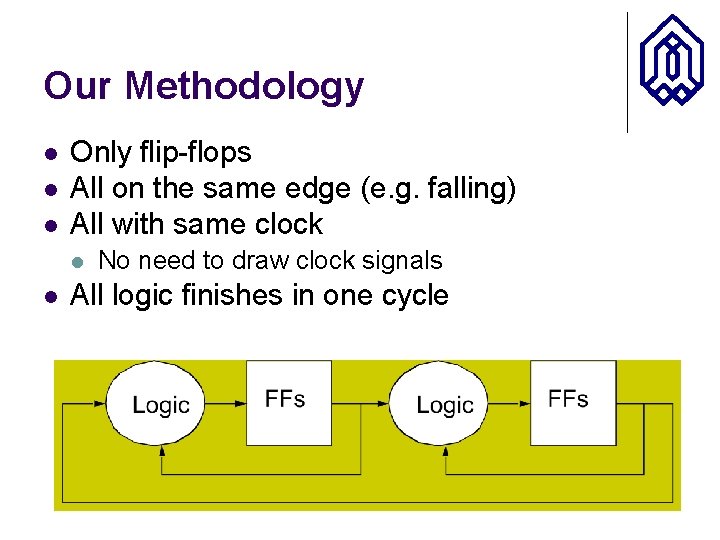

Our Methodology l l l Only flip-flops All on the same edge (e. g. falling) All with same clock l l No need to draw clock signals All logic finishes in one cycle

Our Methodology, cont’d l No clock gating! l l Book has bad examples Correct design:

Datapath – 1 CPI l l Assumption: get whole instruction done in one long cycle Instructions: l l add, sub, and, or slt, lw, sw, & beq To do l l For each instruction type Putting it all together

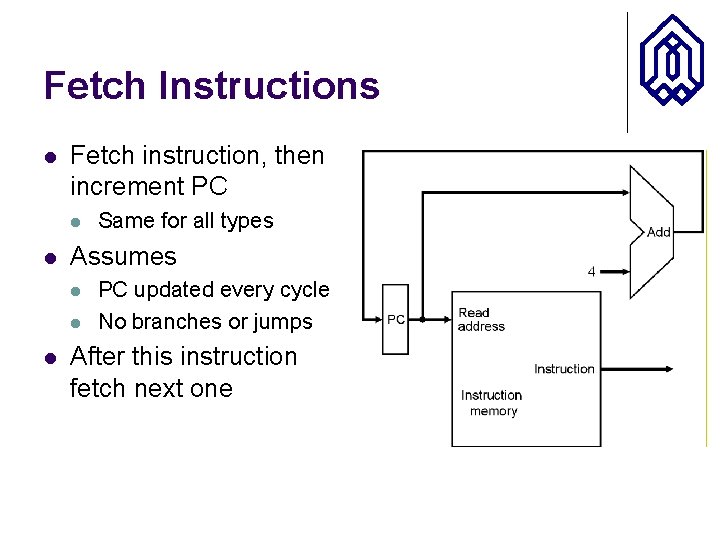

Fetch Instructions l Fetch instruction, then increment PC l l Assumes l l l Same for all types PC updated every cycle No branches or jumps After this instruction fetch next one

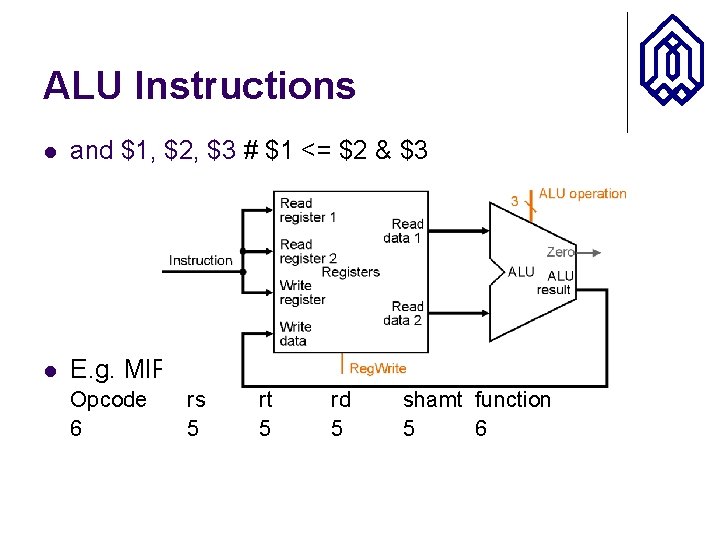

ALU Instructions l and $1, $2, $3 # $1 <= $2 & $3 l E. g. MIPS R-format Opcode 6 rs 5 rt 5 rd 5 shamt function 5 6

![Load/Store Instructions l l lw $1, immed($2) # $1 <= M[SE(immed)+$2] E. g. MIPS Load/Store Instructions l l lw $1, immed($2) # $1 <= M[SE(immed)+$2] E. g. MIPS](http://slidetodoc.com/presentation_image/901d7af069098b1af411658793354585/image-13.jpg)

Load/Store Instructions l l lw $1, immed($2) # $1 <= M[SE(immed)+$2] E. g. MIPS I-format: Opcode 6 rt 5 immed 16

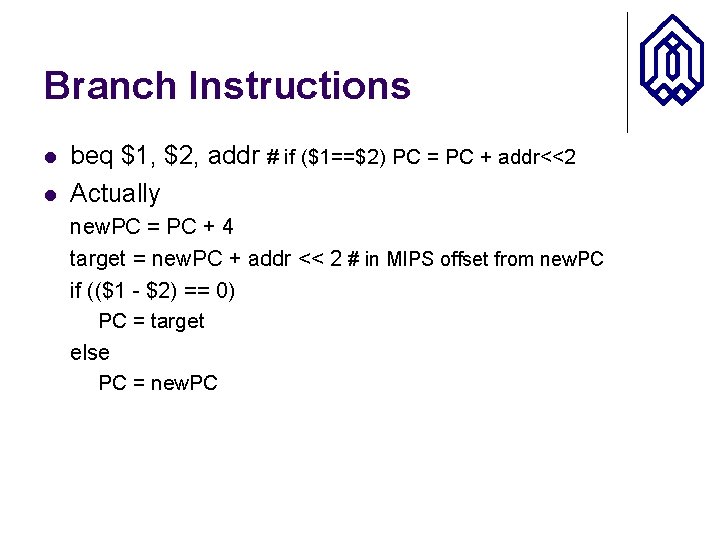

Branch Instructions l l beq $1, $2, addr # if ($1==$2) PC = PC + addr<<2 Actually new. PC = PC + 4 target = new. PC + addr << 2 # in MIPS offset from new. PC if (($1 - $2) == 0) PC = target else PC = new. PC

Branch Instructions

All Together

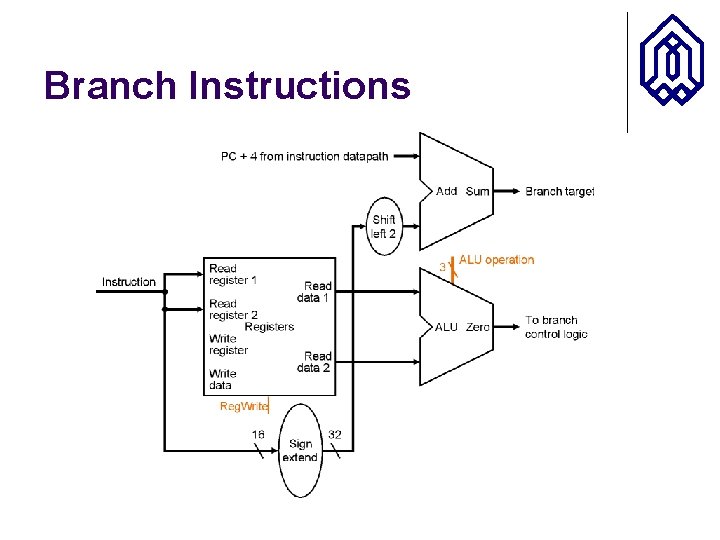

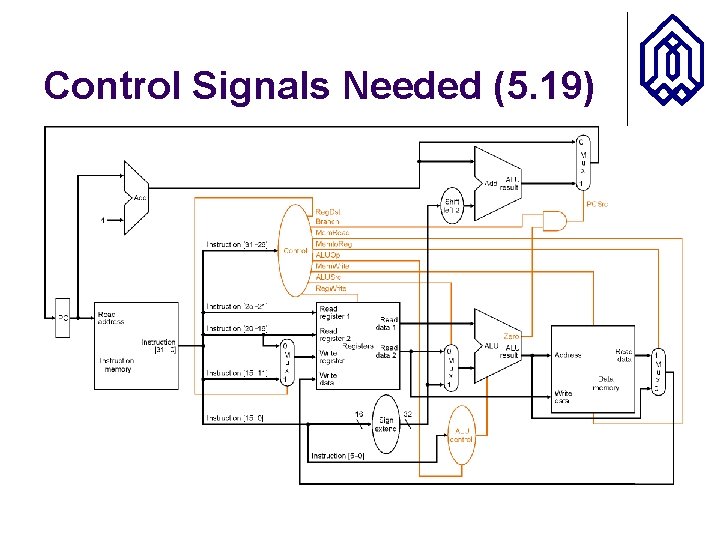

Control Overview l Single-cycle implementation l l Datapath: combinational logic, I-mem, regs, D-mem, PC l Last three written at end of cycle Need control – just combinational logic! Inputs: l Instruction (I-mem out) l Zero (for beq) Outputs: l Control lines for muxes l ALUop l Write-enables

Control Overview l Fast control l Divide up work on “need to know” basis Logic with fewer inputs is faster E. g. l Global control need not know which ALUop

ALU Control l Assume ALU uses 000 and 001 or 010 add 110 sub 111 slt (set less than) others don’t care

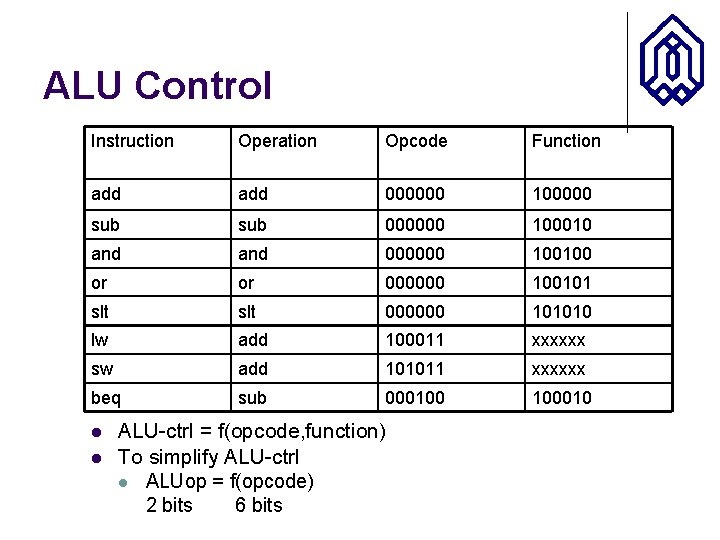

ALU Control Instruction Operation Opcode Function add 000000 100000 sub 000000 100010 and 000000 100100 or or 000000 100101 slt 000000 101010 lw add 100011 xxxxxx sw add 101011 xxxxxx beq sub 000100 100010 l l ALU-ctrl = f(opcode, function) To simplify ALU-ctrl l ALUop = f(opcode) 2 bits 6 bits

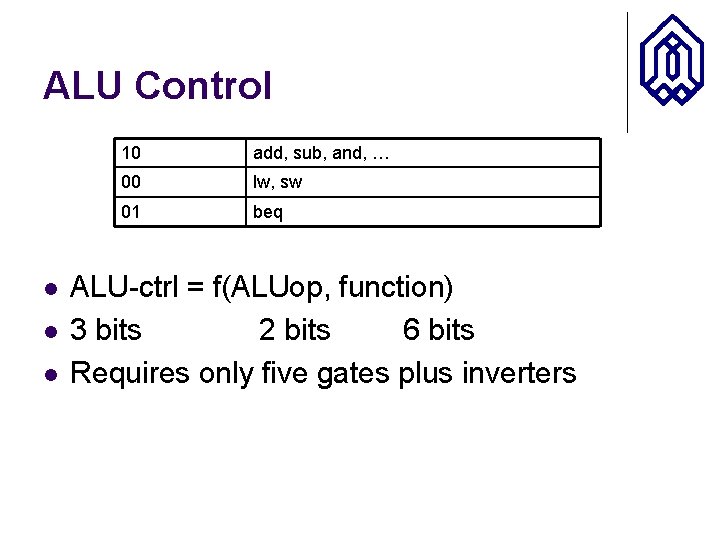

ALU Control l 10 add, sub, and, … 00 lw, sw 01 beq ALU-ctrl = f(ALUop, function) 3 bits 2 bits 6 bits Requires only five gates plus inverters

Control Signals Needed (5. 19)

Global Control l R-format: opcode 6 l I-format: opcode 6 l J-format: opcode 6 rs rt rd shamt function 5 5 6 rs rt address/immediate 5 5 16 address 26

![Global Control l Route instruction[25: 21] as read reg 1 spec Route instruction[20: 16] Global Control l Route instruction[25: 21] as read reg 1 spec Route instruction[20: 16]](http://slidetodoc.com/presentation_image/901d7af069098b1af411658793354585/image-24.jpg)

Global Control l Route instruction[25: 21] as read reg 1 spec Route instruction[20: 16] are read reg 2 spec Route instruction[20: 16] (load) and instruction[15: 11] (others) to l l Write reg mux Call instruction[31: 26] op[5: 0]

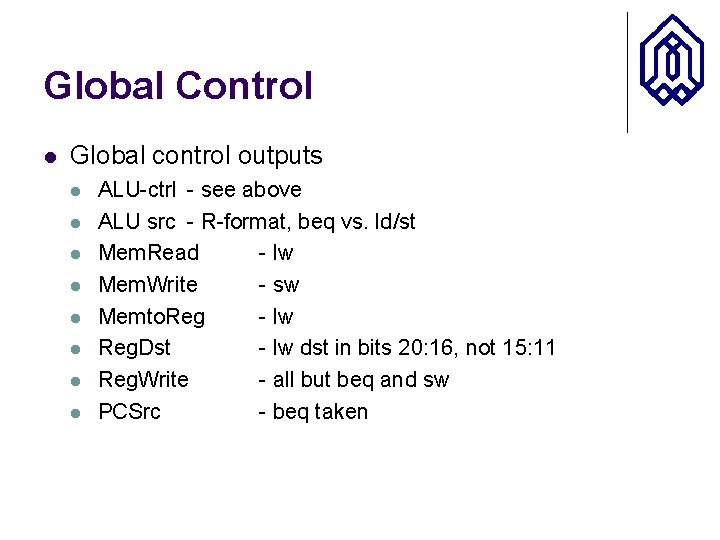

Global Control l Global control outputs l l l l ALU-ctrl - see above ALU src - R-format, beq vs. ld/st Mem. Read - lw Mem. Write - sw Memto. Reg - lw Reg. Dst - lw dst in bits 20: 16, not 15: 11 Reg. Write - all but beq and sw PCSrc - beq taken

Global Control l Global control outputs l Replace PCsrc with l l l Branch beq PCSrc = Branch * Zero What are the inputs needed to determine above global control signals? l Just Op[5: 0]

Global Control (Fig. 5. 20) l l l Instruction Opcode Reg. Dst ALUSrc rrr 000000 1 0 lw 100011 0 1 sw 101011 x 1 beq 000100 x 0 ? ? ? others x x Reg. Dst = ~Op[0] ALUSrc = Op[0] Reg. Write = ~Op[3] * ~Op[2]

Global Control l More complex with entire MIPS ISA l l l Common solution: PLA l l Need more systematic structure Want to share gates between control signals MIPS opcode space designed to minimize PLA inputs, minterms, and outputs See MIPS Opcode map (Fig A. 19)

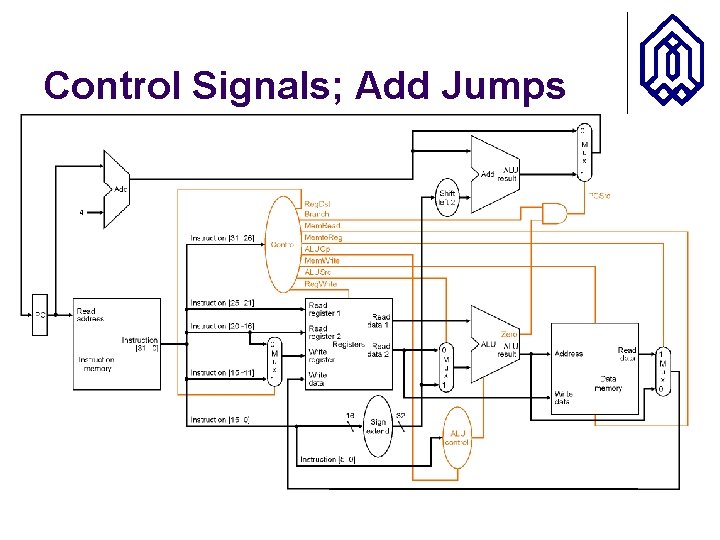

Control Signals; Add Jumps

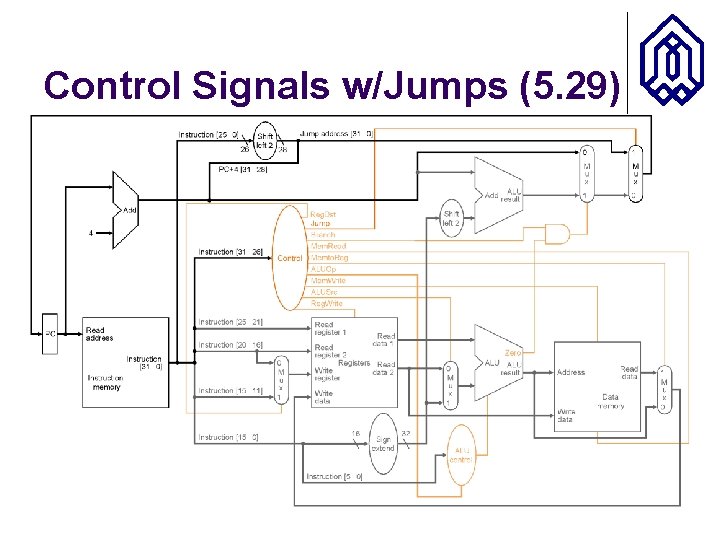

Control Signals w/Jumps (5. 29)

What’s wrong with single cycle? Instructions Program X (code size) l Time Cycle (cycle time) I-mem, reg-read, alu, d-mem, reg-write Other instructions faster l l (CPI) Critical path probably lw: l l Cycles X Instruction E. g. rrr: skip d-mem Instruction variation much worse for full ISA and real implementation: l l FP divide Cache misses (what the heck is this? – chapter 7)

Single Cycle Implementation l Solution l Variable clock? l l Too hard to control, design Fixed short clock l Variable cycles per instruction

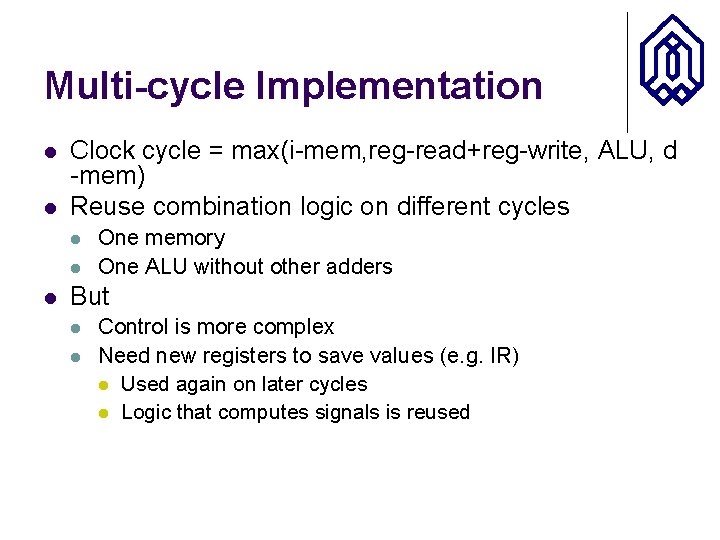

Multi-cycle Implementation l l Clock cycle = max(i-mem, reg-read+reg-write, ALU, d -mem) Reuse combination logic on different cycles l l l One memory One ALU without other adders But l l Control is more complex Need new registers to save values (e. g. IR) l Used again on later cycles l Logic that computes signals is reused

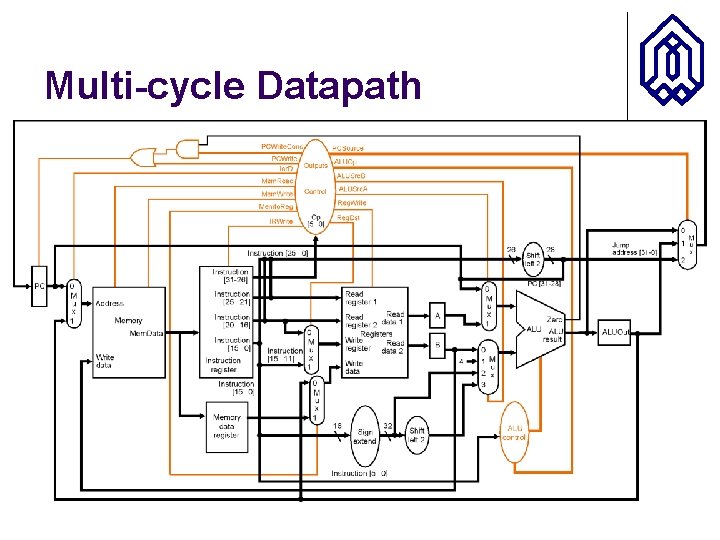

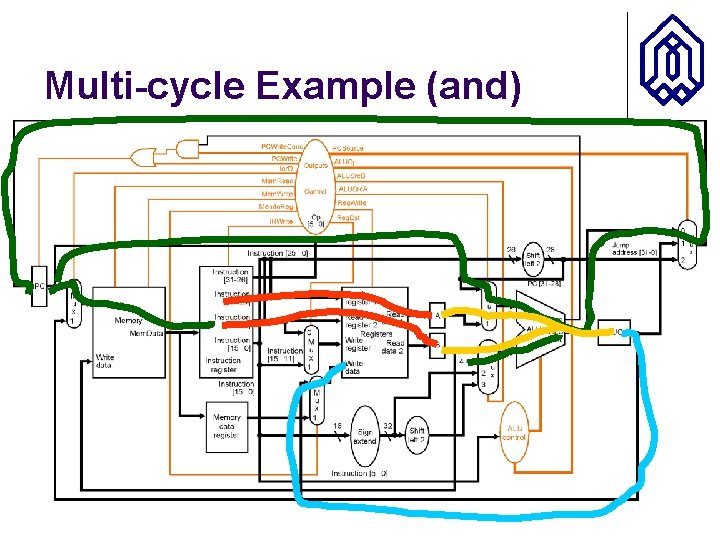

High-level Multi-cycle Datapath l Note: l l l Instruction register, memory data register One memory with address bus One ALU with ALUOut register

Comment on busses l Share wires to reduce #signals l l Distributed multiplexor Multiple sources driving one bus l Ensure only one is active!

Multi-cycle Ctrl Signals (Fig 5. 32)

Multi-cycle Datapath

![Multi-cycle Steps Step Description Sample Actions IF Fetch IR=MEM[PC] PC=PC+4 ID Decode A=RF(IR[25: 21]) Multi-cycle Steps Step Description Sample Actions IF Fetch IR=MEM[PC] PC=PC+4 ID Decode A=RF(IR[25: 21])](http://slidetodoc.com/presentation_image/901d7af069098b1af411658793354585/image-38.jpg)

Multi-cycle Steps Step Description Sample Actions IF Fetch IR=MEM[PC] PC=PC+4 ID Decode A=RF(IR[25: 21]) B=RF(IR[20: 16]) ALUout=PC+SE(IR[15: 0] << 2) EX Execute ALUout = A + SE(IR[15: 0]) # lw/sw ALUout = A op B # rrr if (A==B) PC = ALUout # beq Memory MEM[ALUout] = B # sw MDR = MEM[ALUout] #lw RF(IR[15: 11]) = ALUout # rrr WB Writeback Reg(IR[20: 16]) = MDR # lw

![Multi-cycle Control l l Function of Op[5: 0] and current step Defined as Finite Multi-cycle Control l l Function of Op[5: 0] and current step Defined as Finite](http://slidetodoc.com/presentation_image/901d7af069098b1af411658793354585/image-39.jpg)

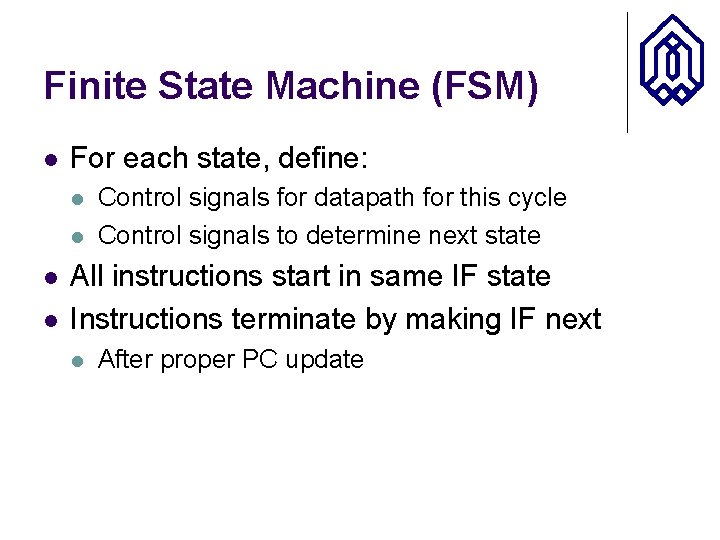

Multi-cycle Control l l Function of Op[5: 0] and current step Defined as Finite State Machine (FSM) or l l Micro-program or microcode (later) FSM – App. B l State is combination of step and which path Current state Inputs Next State Fn Output Fn Next State outputs

Finite State Machine (FSM) l For each state, define: l l Control signals for datapath for this cycle Control signals to determine next state All instructions start in same IF state Instructions terminate by making IF next l After proper PC update

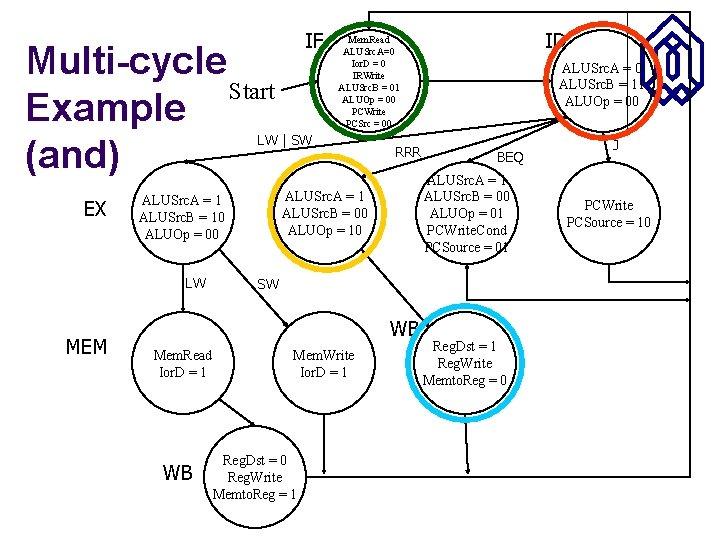

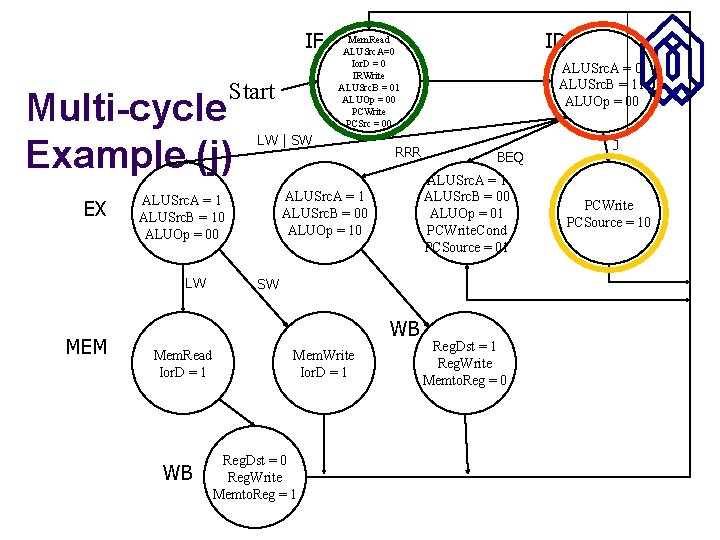

IF Multi-cycle Start Example (and) LW | SW EX LW MEM RRR WB BEQ SW WB Mem. Read Ior. D = 1 ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCWrite. Cond PCSource = 01 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 ID Mem. Read ALUSrc. A=0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSrc = 00 Mem. Write Ior. D = 1 Reg. Dst = 0 Reg. Write Memto. Reg = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 J PCWrite PCSource = 10

Multi-cycle Example (and)

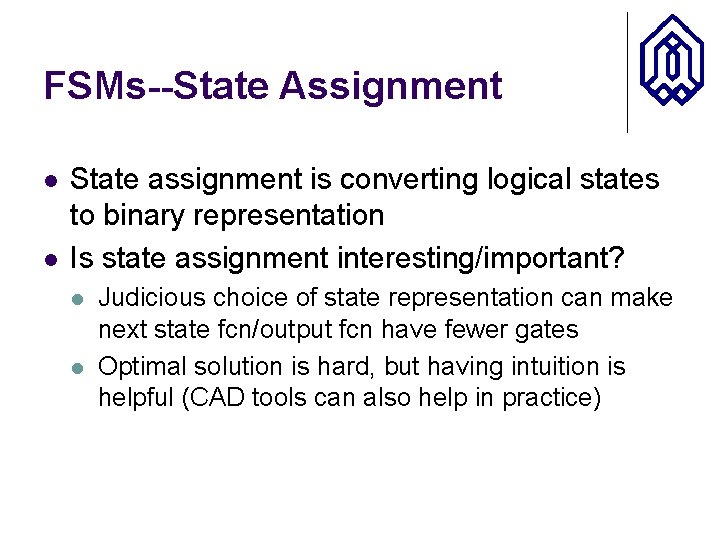

Nuts and Bolts--More on FSMs l l l You will be using FSM control for your processor implementation You will be producing the state machine and control outputs from binary (ISA/datapath controls) There are multiple methods for specifying a state machine l l l Moore machine (output is function of state only) Mealy machine (output is function of state/input) There are different methods of assigning states

FSMs--State Assignment l l State assignment is converting logical states to binary representation Is state assignment interesting/important? l l Judicious choice of state representation can make next state fcn/output fcn have fewer gates Optimal solution is hard, but having intuition is helpful (CAD tools can also help in practice)

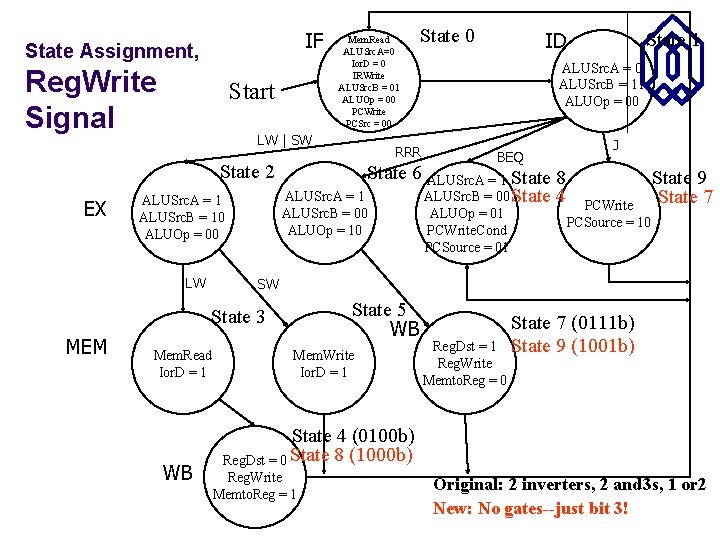

State Assignment--Example l 10 states in multicycle control FSM l l l Each state can have 1 of 16 (2^4) encodings with “dense” state representation Any choice of encoding is fine functionally as long as all states are unique Appendix C-26 example: Reg. Write signal

IF State Assignment, Reg. Write Signal Start LW | SW State 2 EX ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 LW RRR ALUSrc. B = 00 ALUOp = 10 State 1 ID ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 BEQ ALUOp = 01 PCWrite. Cond PCSource = 01 J PCWrite PCSource = 10 State 9 State 7 SW Mem. Read Ior. D = 1 WB State 0 State 6 ALUSrc. A = 1 State 8 ALUSrc. A = 1 ALUSrc. B = 00 State 4 State 5 WB State 3 MEM Mem. Read ALUSrc. A=0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSrc = 00 Mem. Write Ior. D = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 State 7 (0111 b) State 9 (1001 b) State 4 (0100 b) Reg. Dst = 0 State 8 (1000 b) Reg. Write Memto. Reg = 1 Original: 2 inverters, 2 and 3 s, 1 or 2 New: No gates--just bit 3!

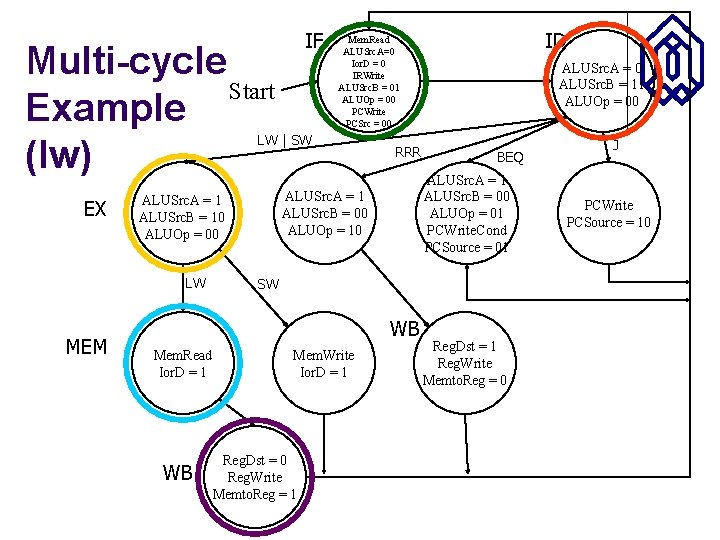

IF Multi-cycle Start Example (lw) LW | SW EX LW MEM RRR WB BEQ SW WB Mem. Read Ior. D = 1 ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCWrite. Cond PCSource = 01 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 ID Mem. Read ALUSrc. A=0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSrc = 00 Mem. Write Ior. D = 1 Reg. Dst = 0 Reg. Write Memto. Reg = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 J PCWrite PCSource = 10

Multi-cycle Example (lw)

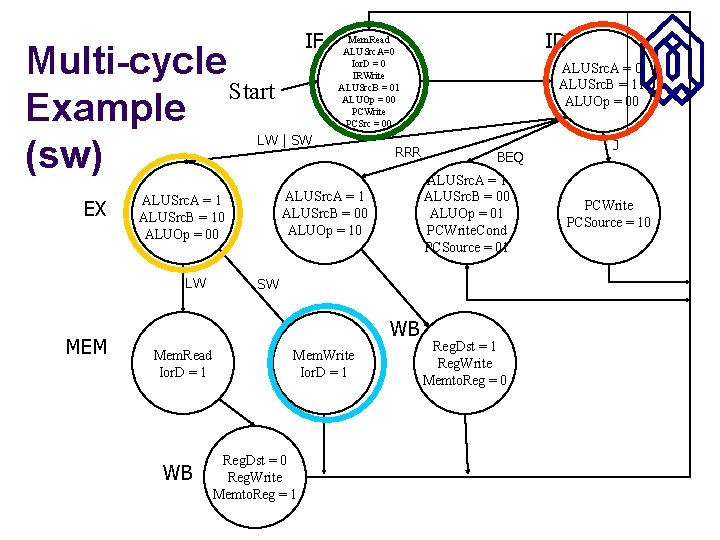

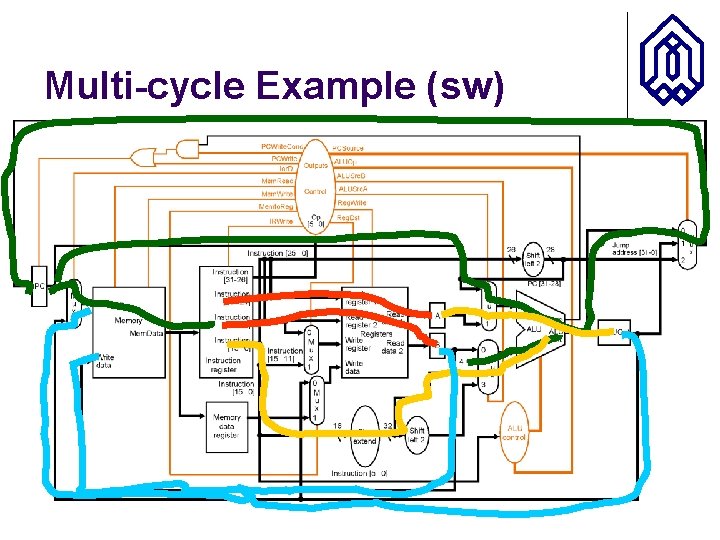

IF Multi-cycle Start Example (sw) LW | SW EX LW MEM RRR WB BEQ SW WB Mem. Read Ior. D = 1 ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCWrite. Cond PCSource = 01 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 ID Mem. Read ALUSrc. A=0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSrc = 00 Mem. Write Ior. D = 1 Reg. Dst = 0 Reg. Write Memto. Reg = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 J PCWrite PCSource = 10

Multi-cycle Example (sw)

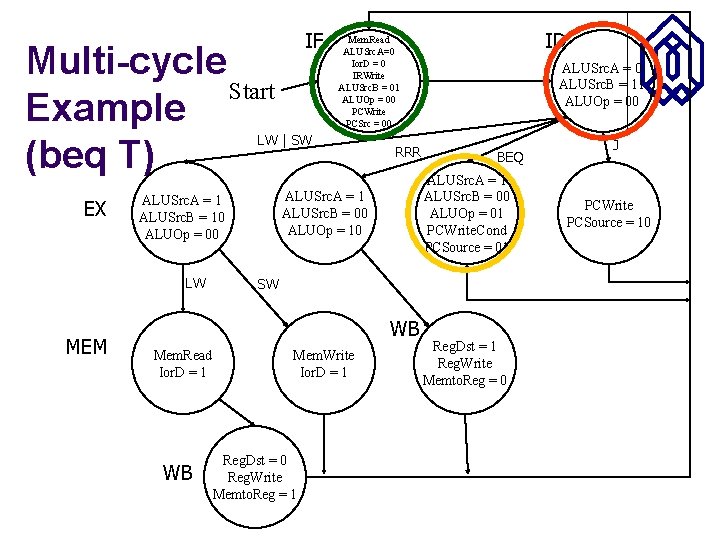

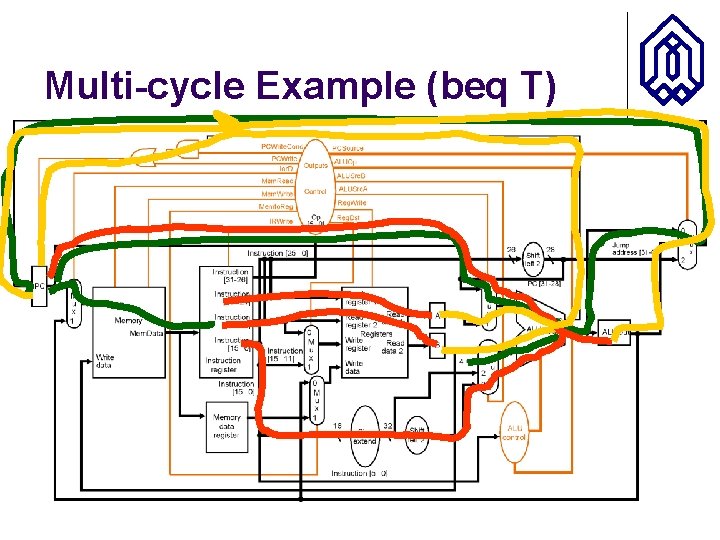

IF Multi-cycle Start Example (beq T) LW | SW EX LW MEM RRR WB BEQ SW WB Mem. Read Ior. D = 1 ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCWrite. Cond PCSource = 01 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 ID Mem. Read ALUSrc. A=0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSrc = 00 Mem. Write Ior. D = 1 Reg. Dst = 0 Reg. Write Memto. Reg = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 J PCWrite PCSource = 10

Multi-cycle Example (beq T)

Multi-cycle Example (beq NT)

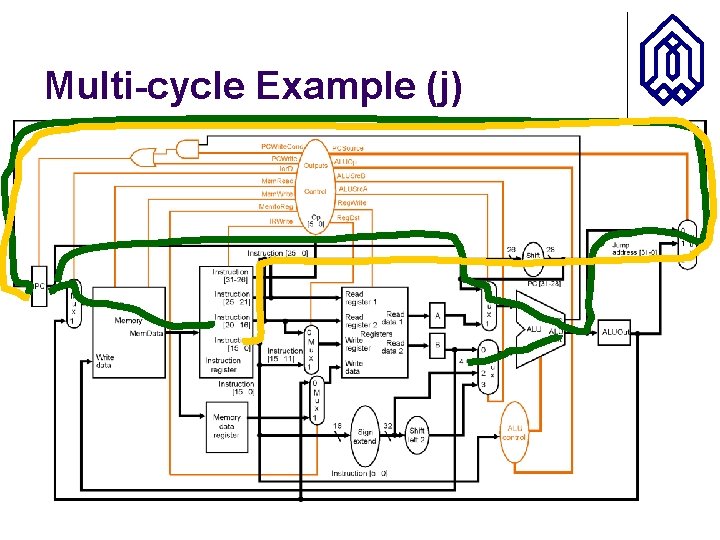

IF Start Multi-cycle Example (j) EX LW MEM LW | SW RRR WB BEQ SW WB Mem. Read Ior. D = 1 ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCWrite. Cond PCSource = 01 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 ID Mem. Read ALUSrc. A=0 Ior. D = 0 IRWrite ALUSrc. B = 01 ALUOp = 00 PCWrite PCSrc = 00 Mem. Write Ior. D = 1 Reg. Dst = 0 Reg. Write Memto. Reg = 1 Reg. Dst = 1 Reg. Write Memto. Reg = 0 J PCWrite PCSource = 10

Multi-cycle Example (j)

Summary l Processor implementation l l Datapath Control Single cycle implementation Next: microprogramming

- Slides: 56