Chapter 5 Freescale ARM Timer Programming 1 A

- Slides: 45

Chapter 5 Freescale ARM Timer Programming 1

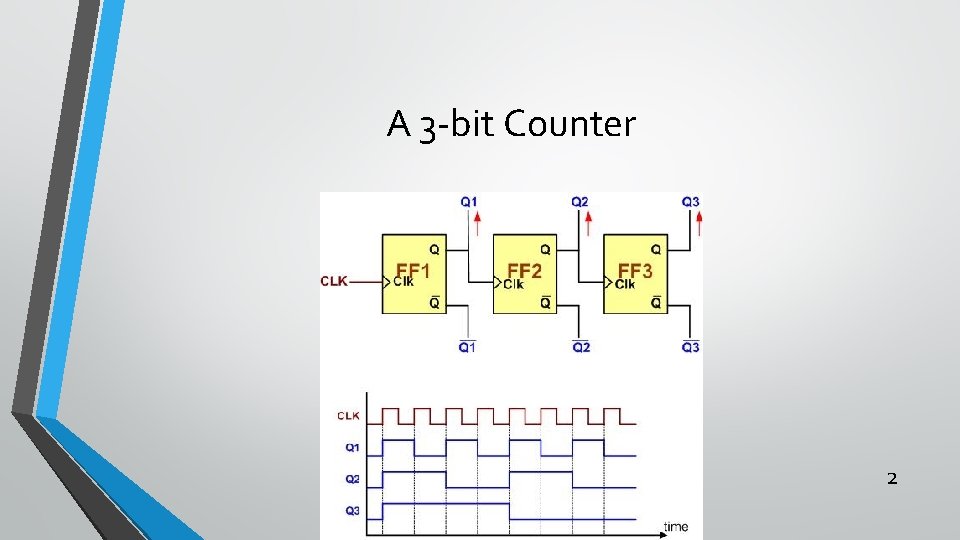

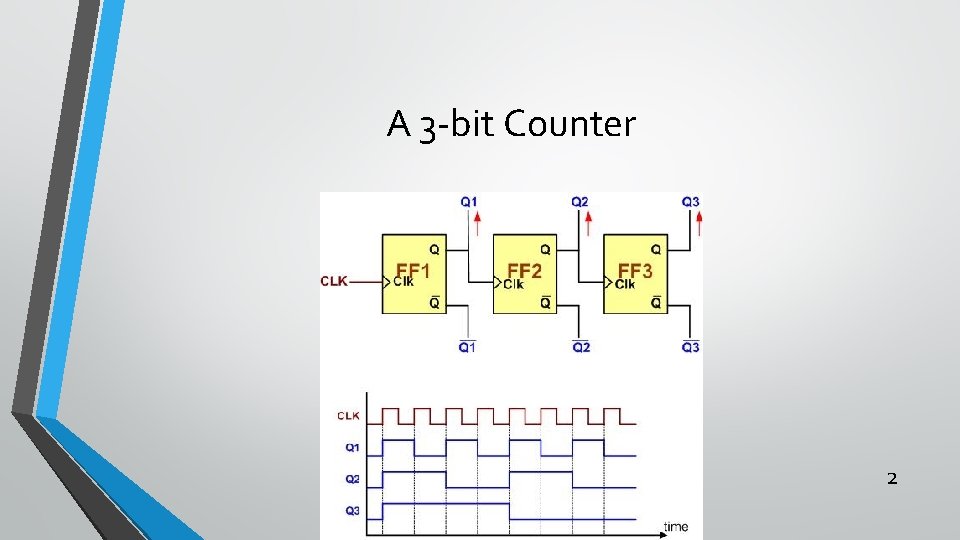

A 3 -bit Counter 2

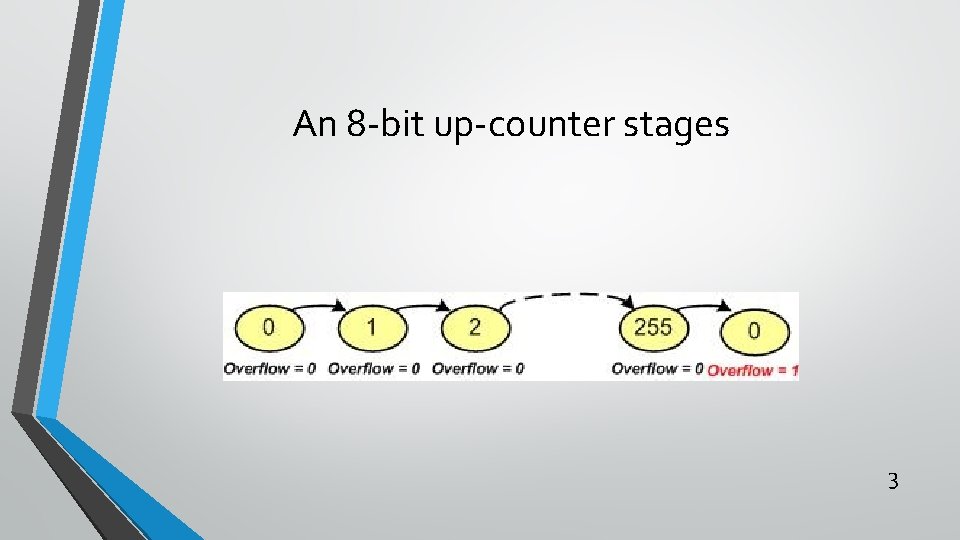

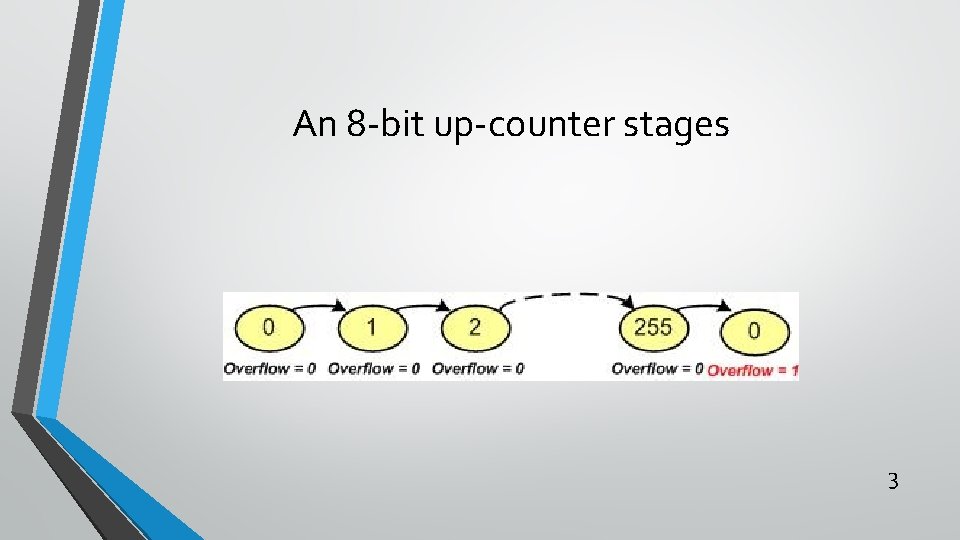

An 8 -bit up-counter stages 3

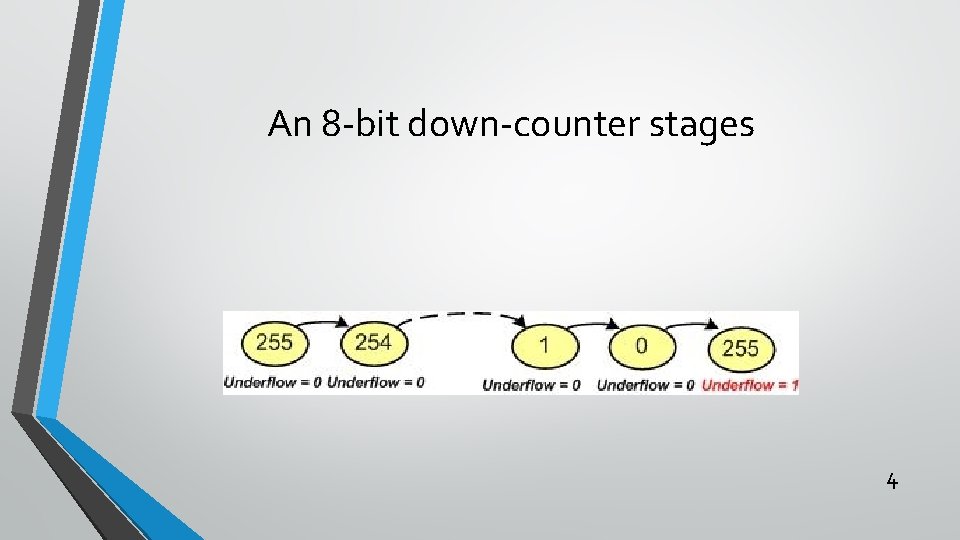

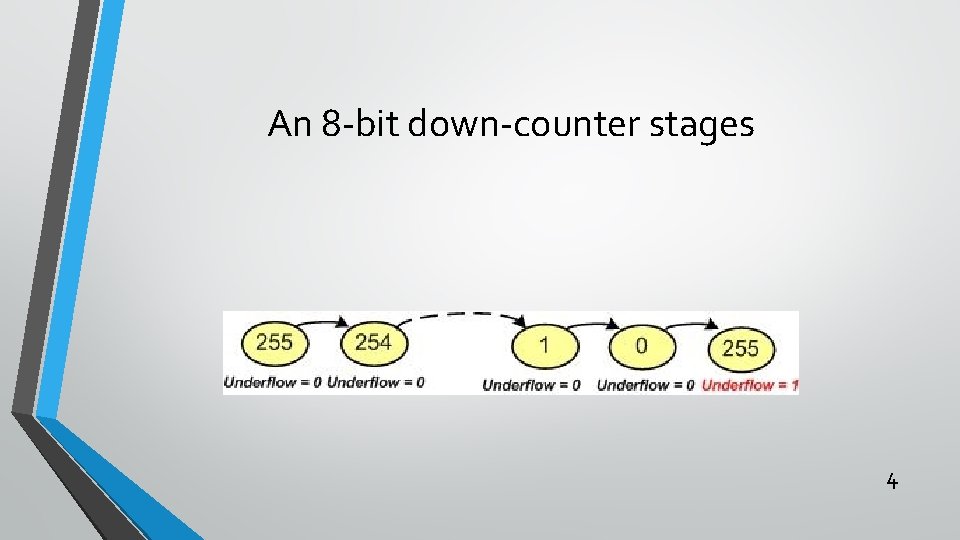

An 8 -bit down-counter stages 4

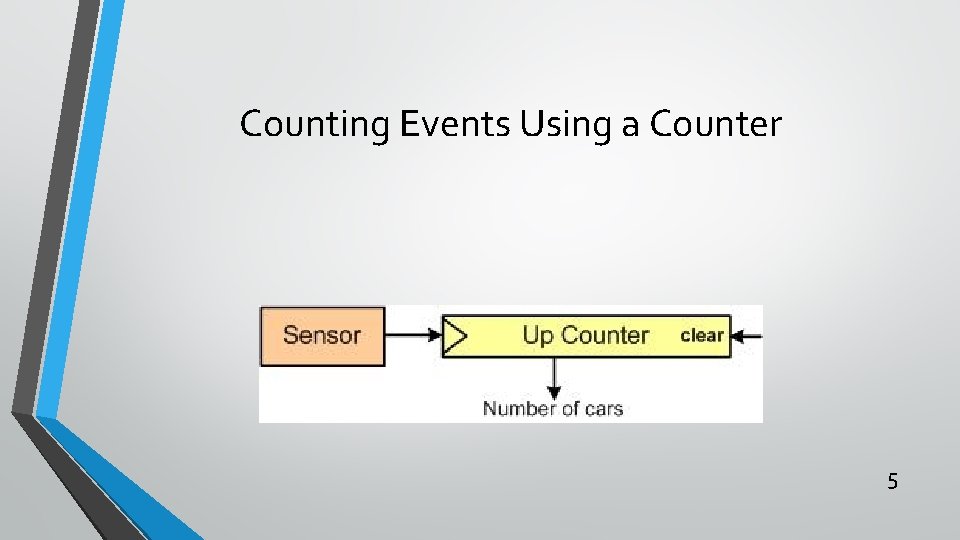

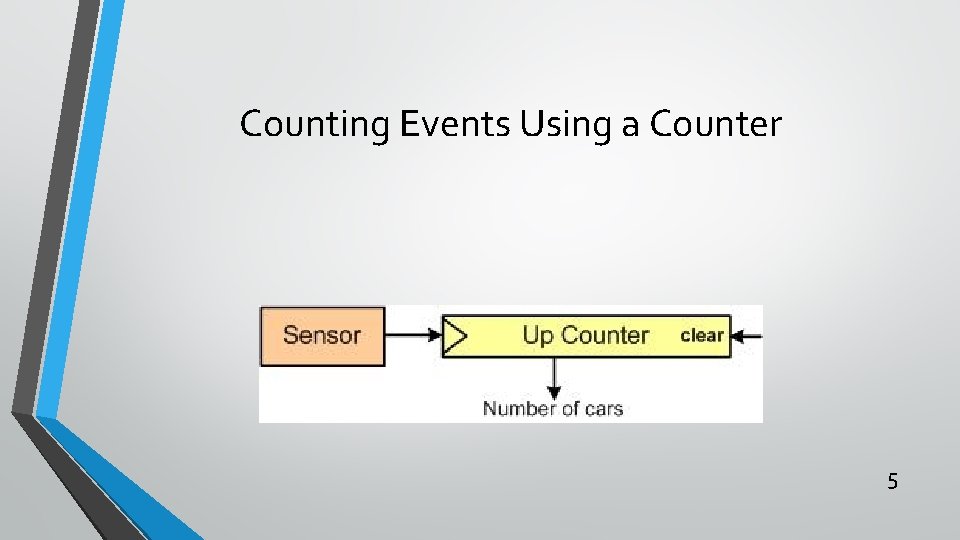

Counting Events Using a Counter 5

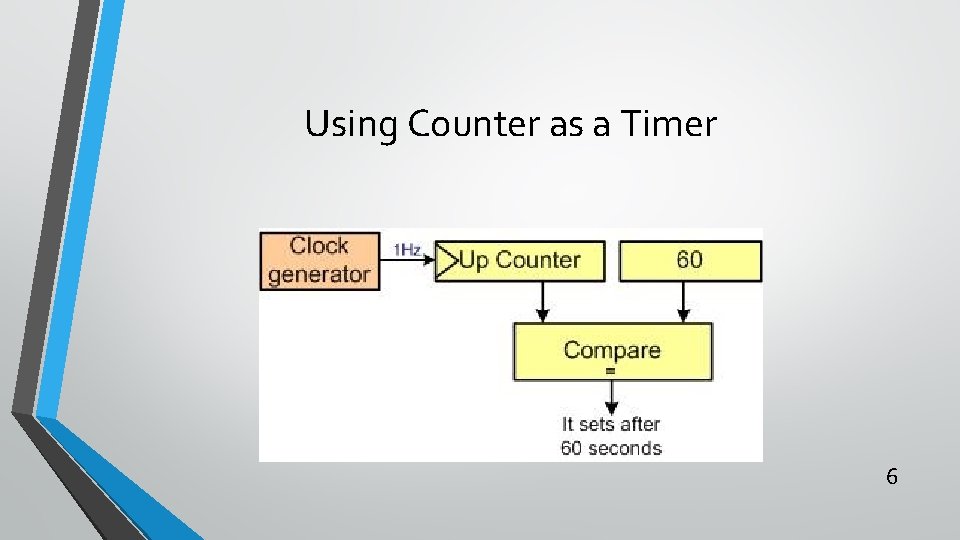

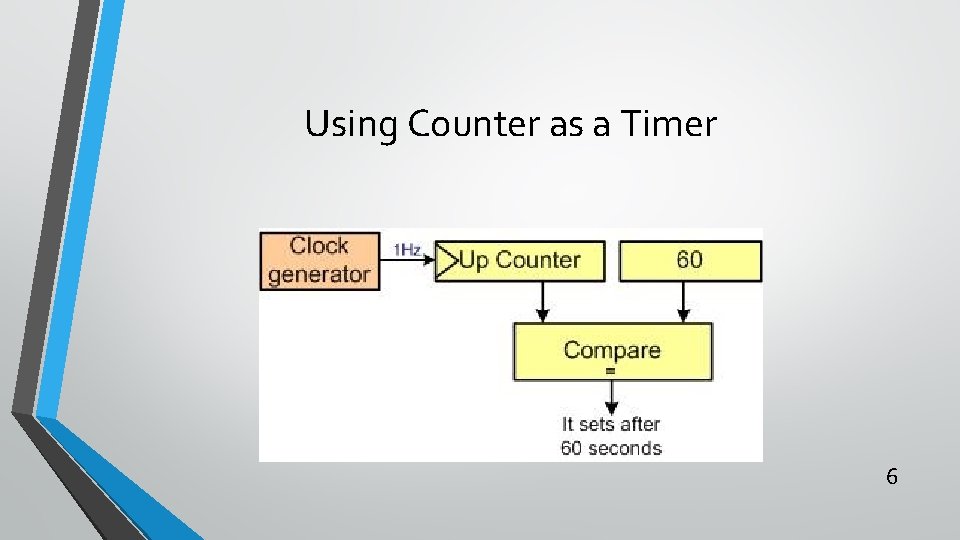

Using Counter as a Timer 6

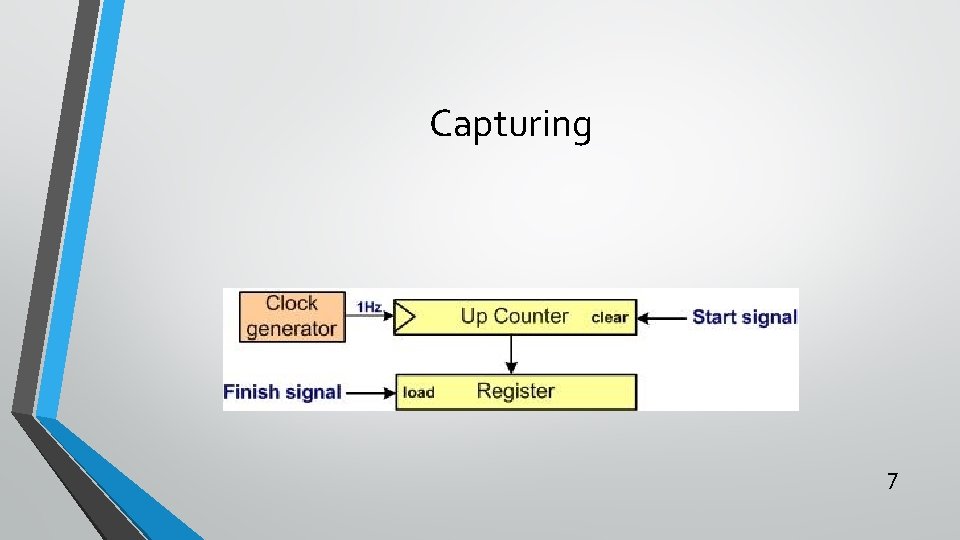

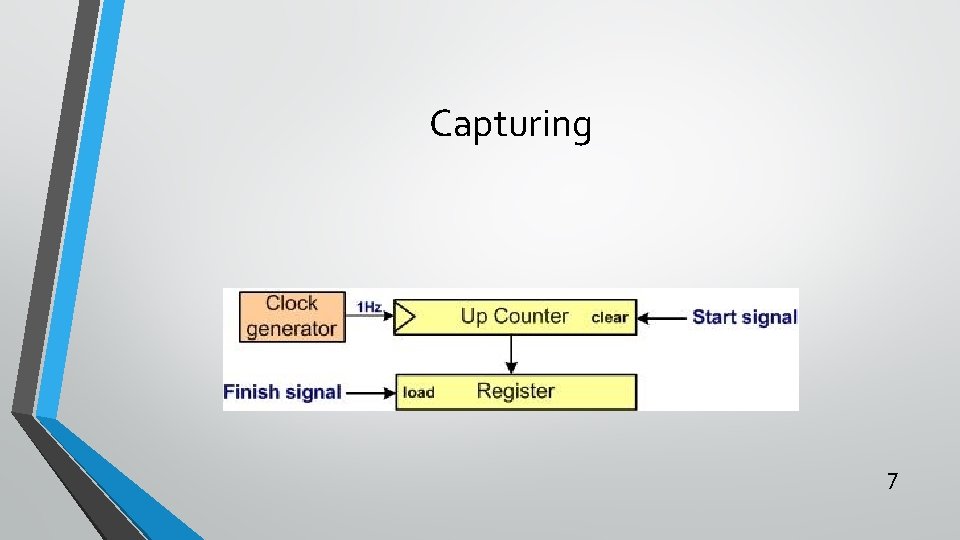

Capturing 7

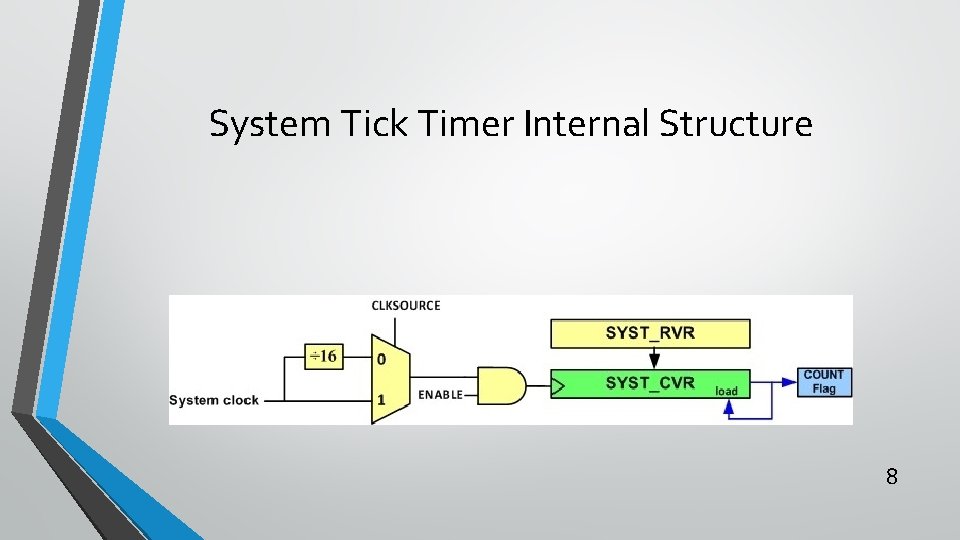

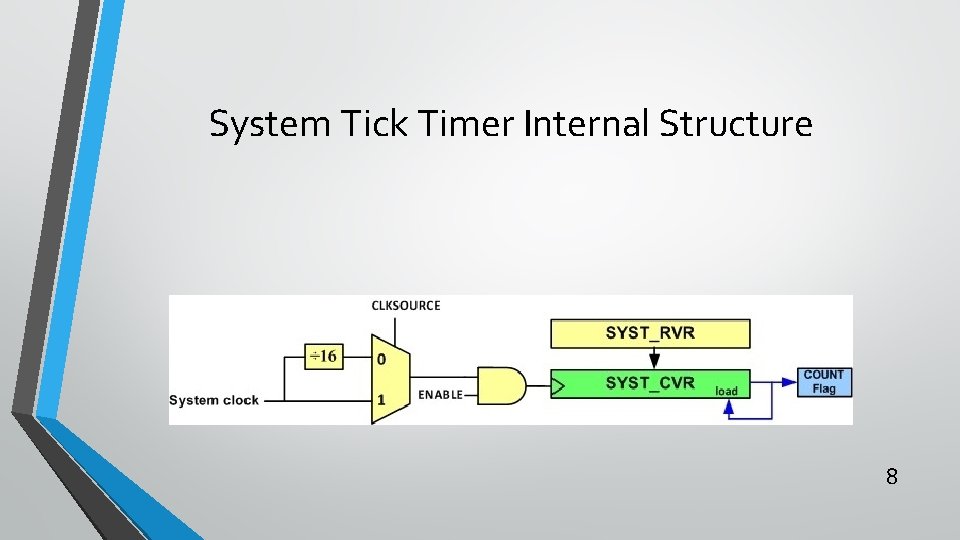

System Tick Timer Internal Structure 8

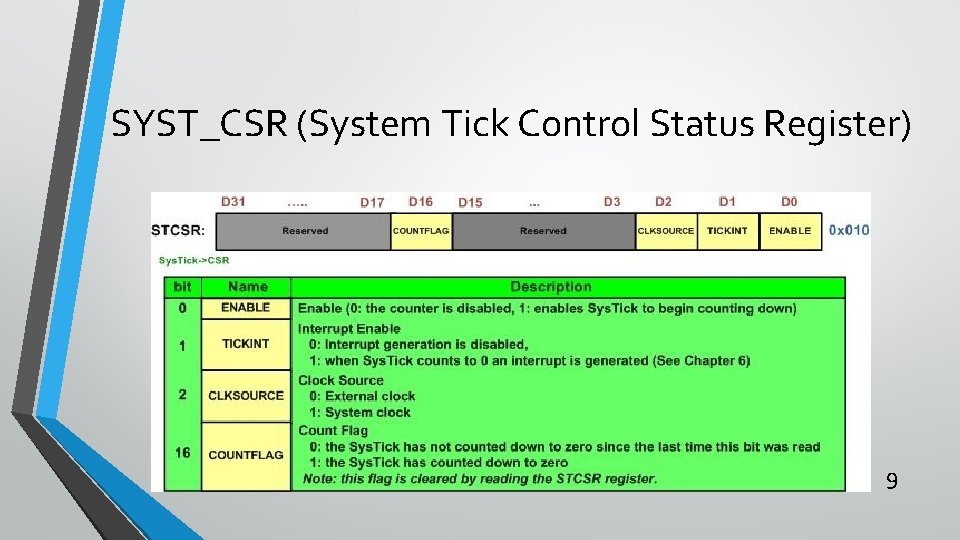

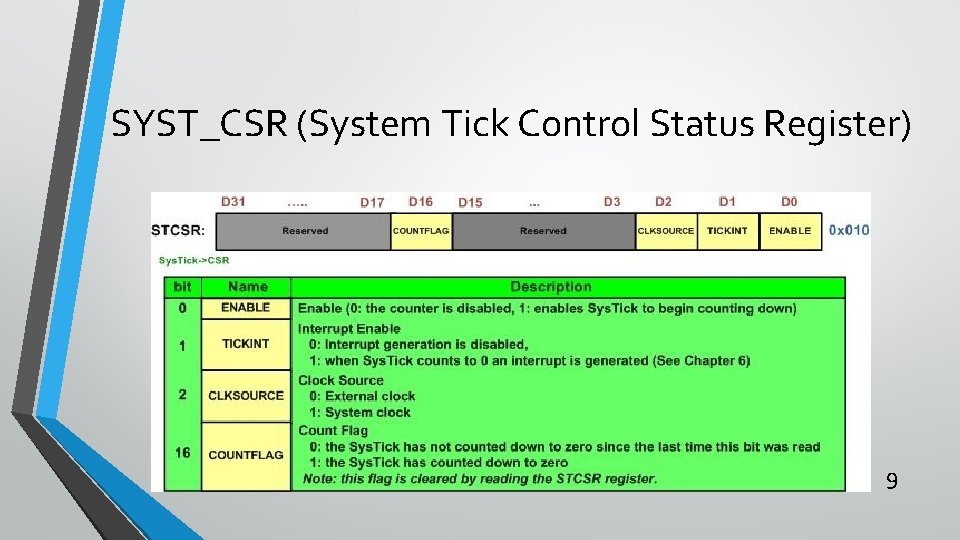

SYST_CSR (System Tick Control Status Register) 9

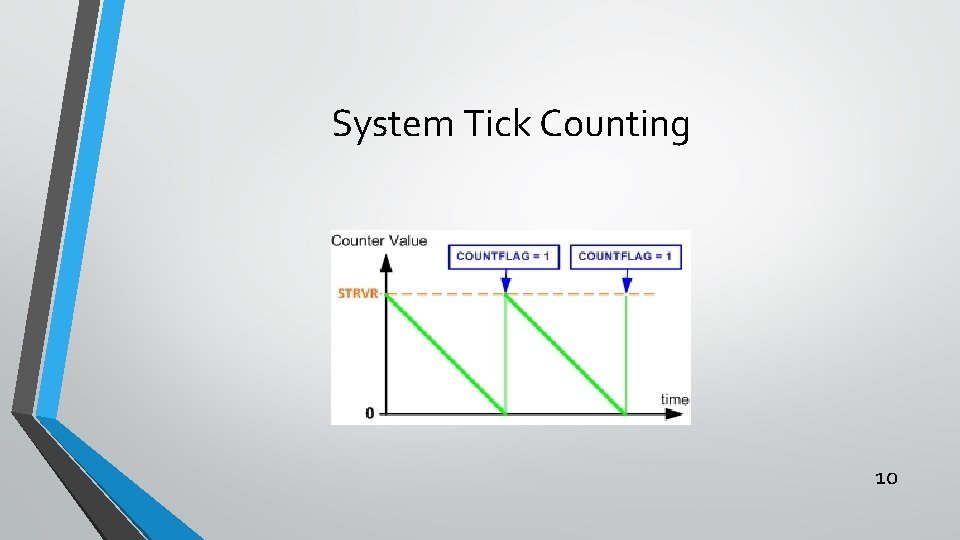

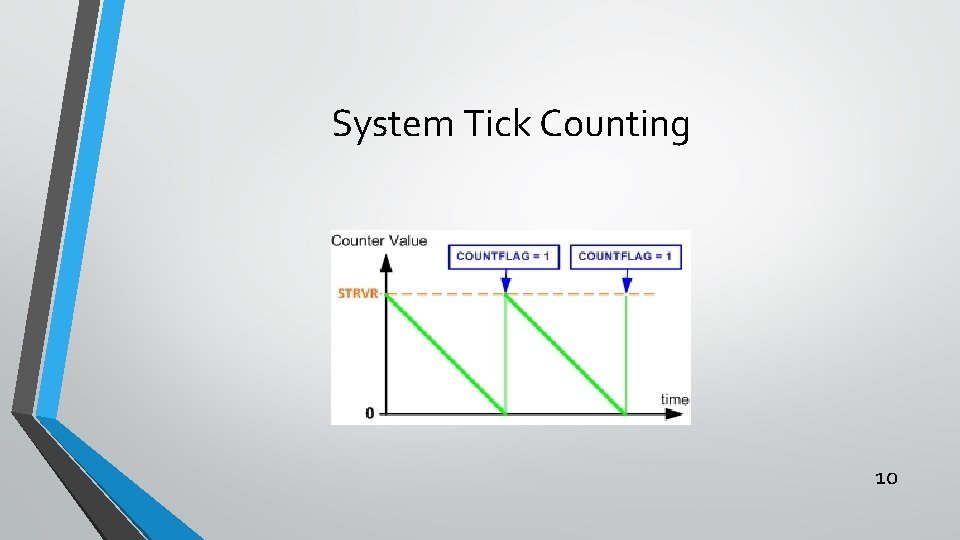

System Tick Counting 10

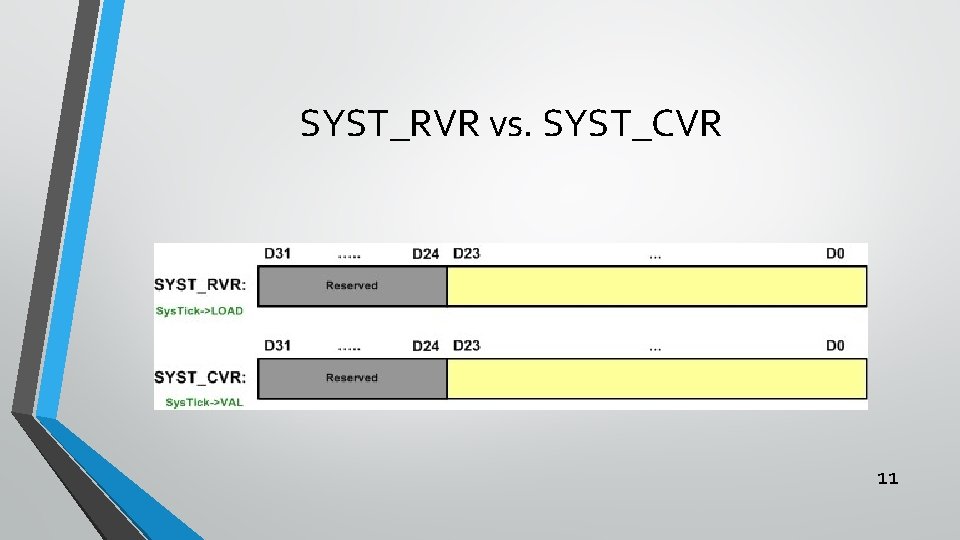

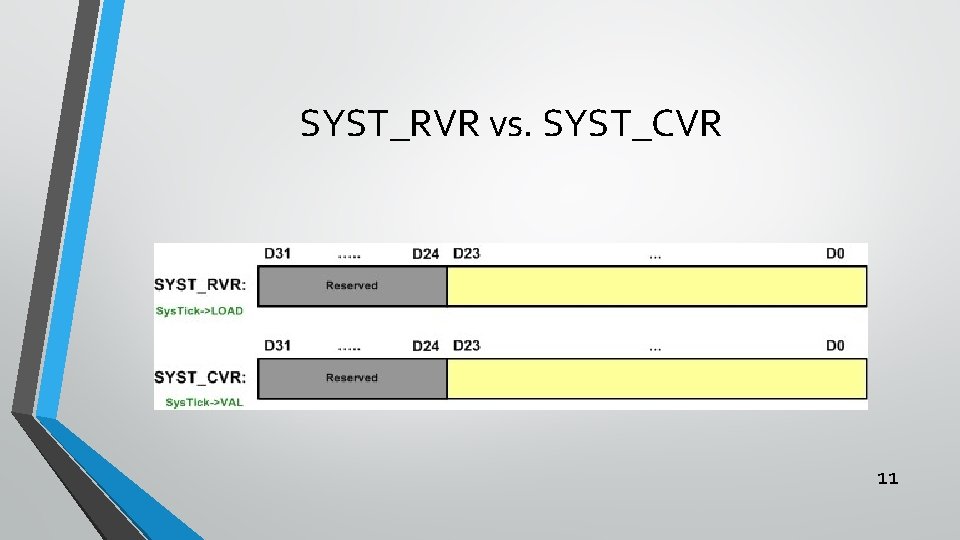

SYST_RVR vs. SYST_CVR 11

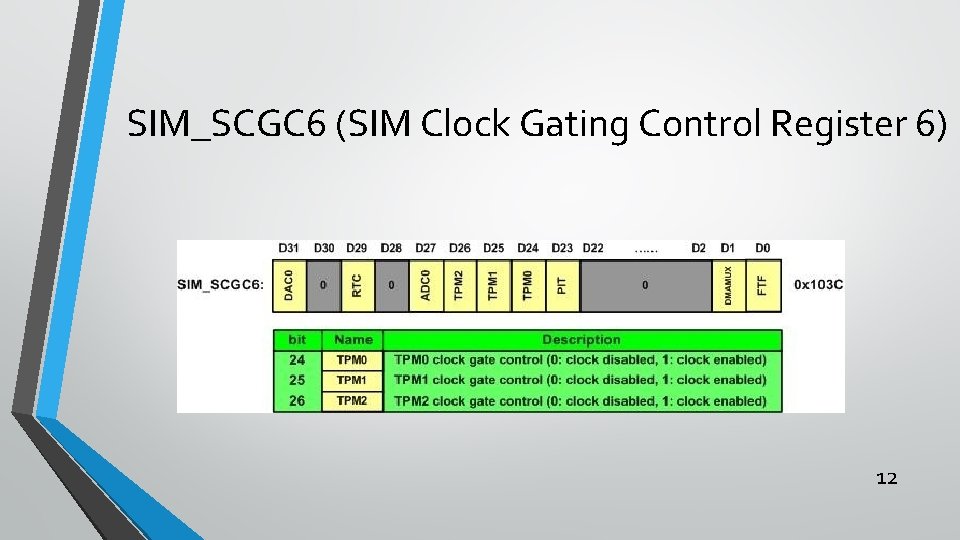

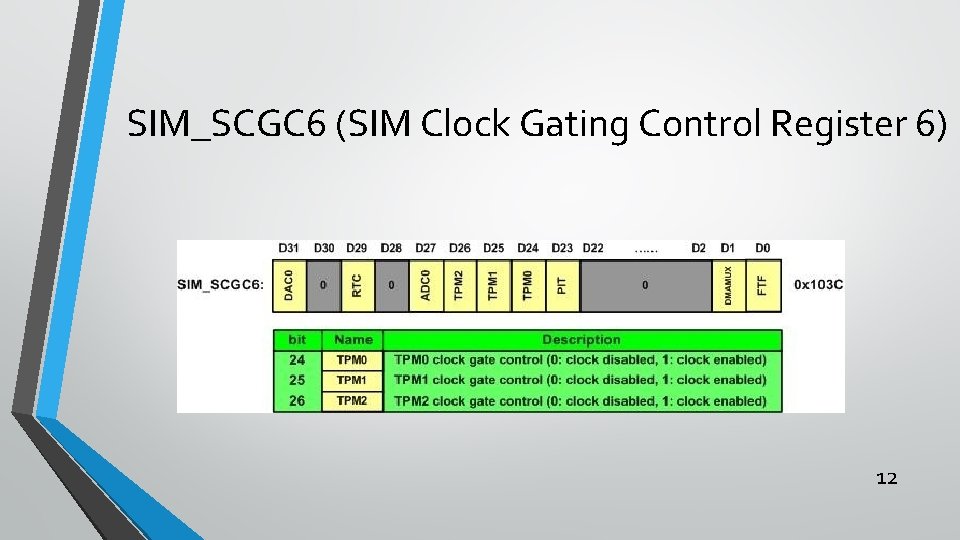

SIM_SCGC 6 (SIM Clock Gating Control Register 6) 12

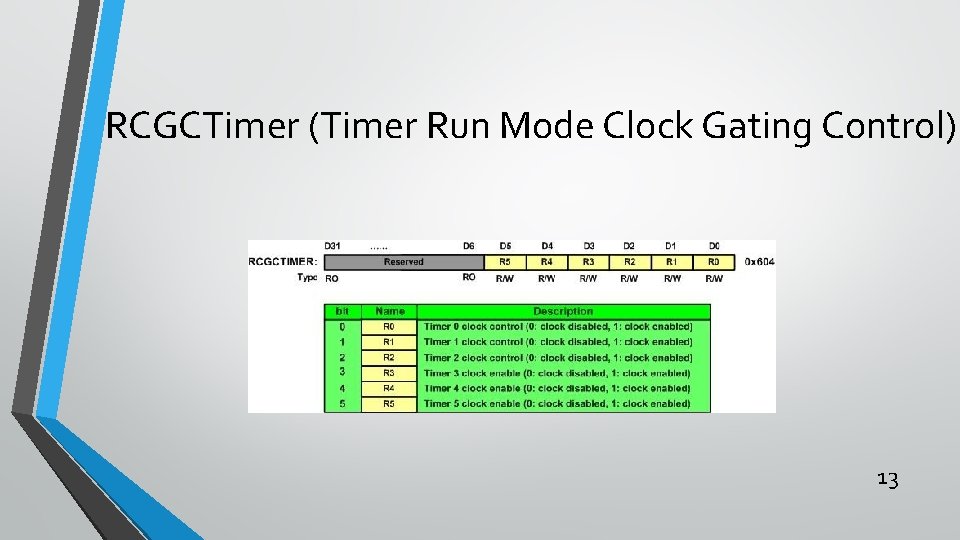

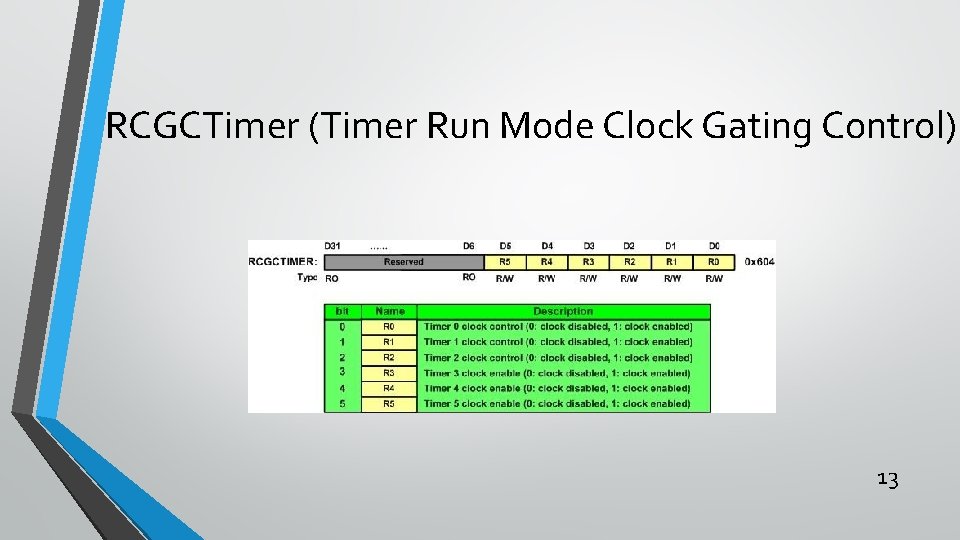

RCGCTimer (Timer Run Mode Clock Gating Control) 13

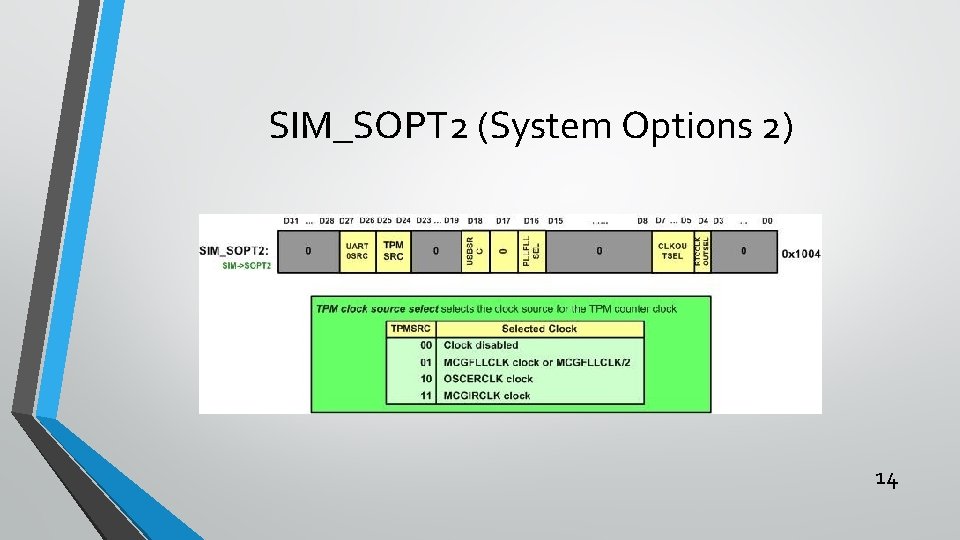

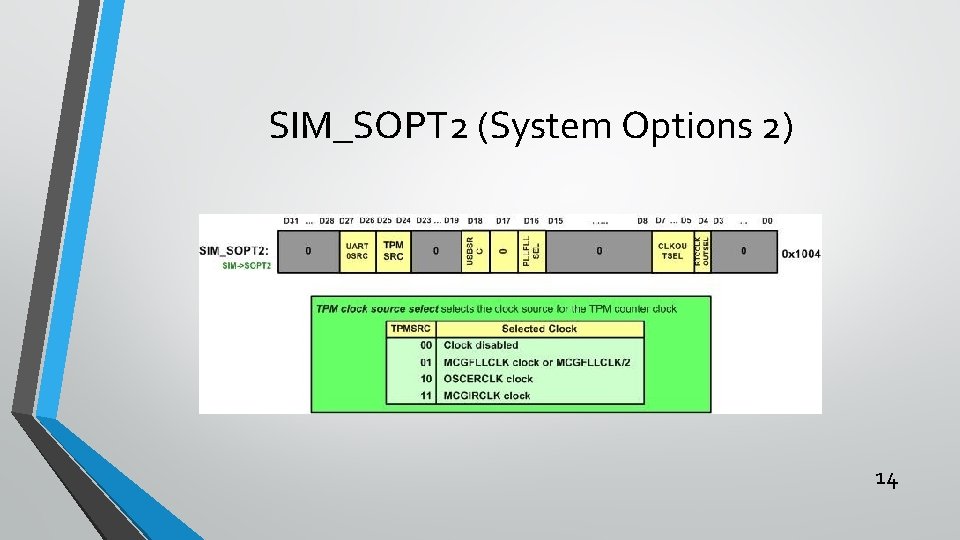

SIM_SOPT 2 (System Options 2) 14

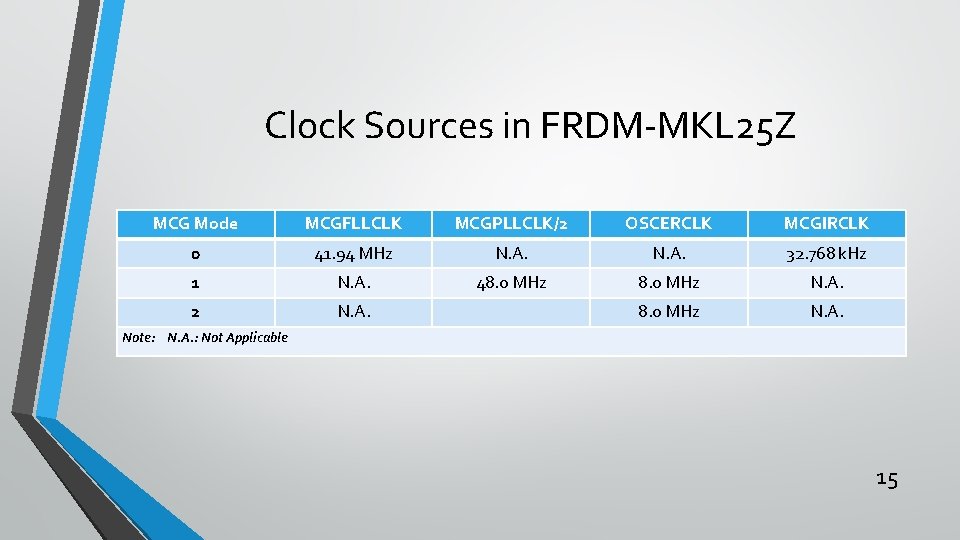

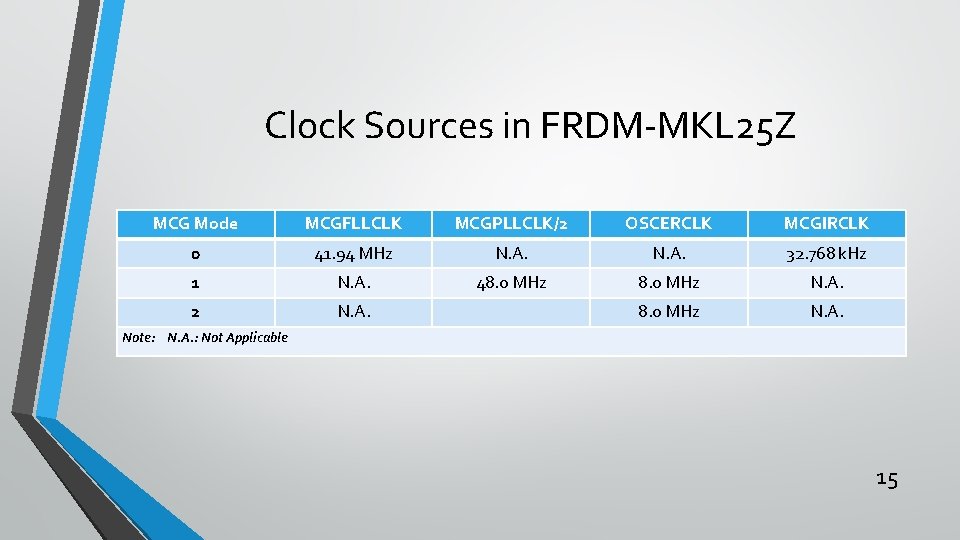

Clock Sources in FRDM-MKL 25 Z MCG Mode MCGFLLCLK MCGPLLCLK/2 OSCERCLK MCGIRCLK 0 41. 94 MHz N. A. 32. 768 k. Hz 1 N. A. 48. 0 MHz N. A. 2 N. A. 8. 0 MHz N. A. Note: N. A. : Not Applicable 15

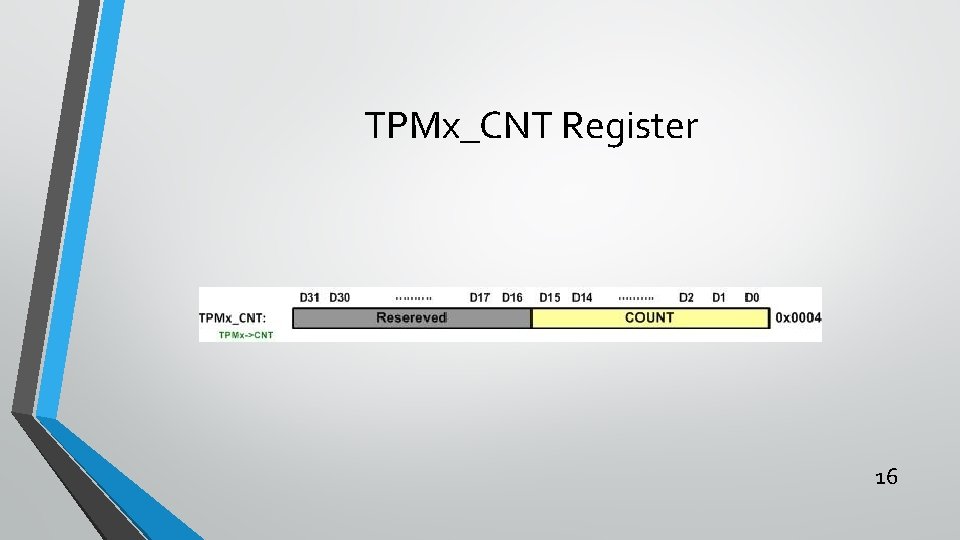

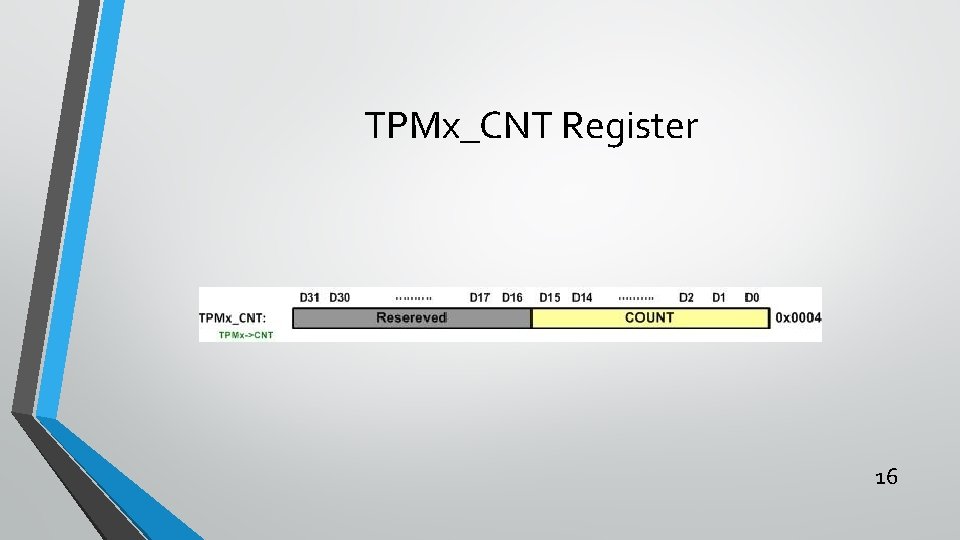

TPMx_CNT Register 16

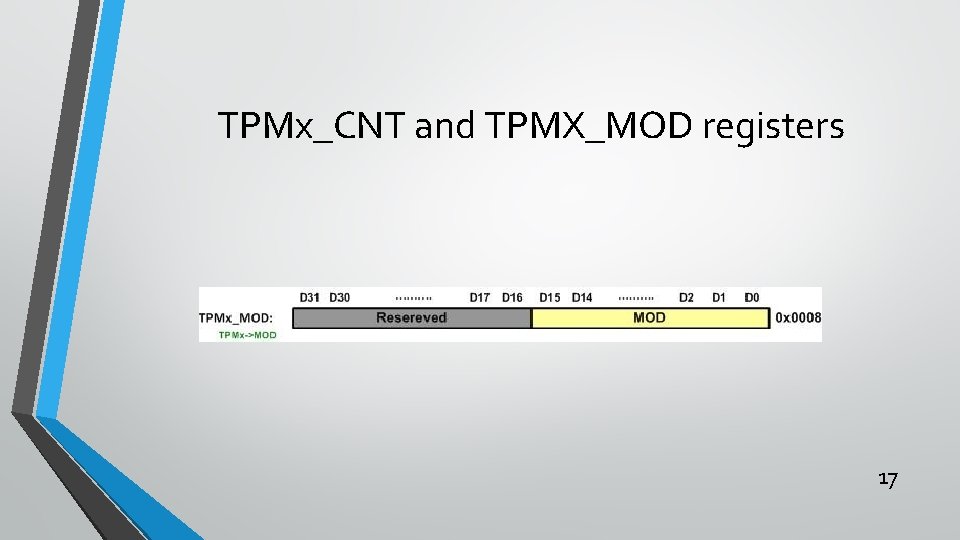

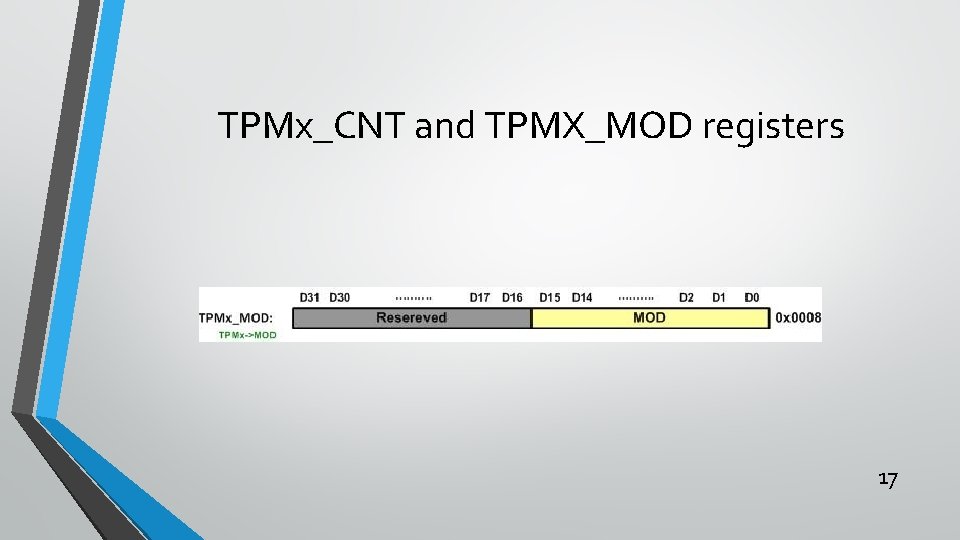

TPMx_CNT and TPMX_MOD registers 17

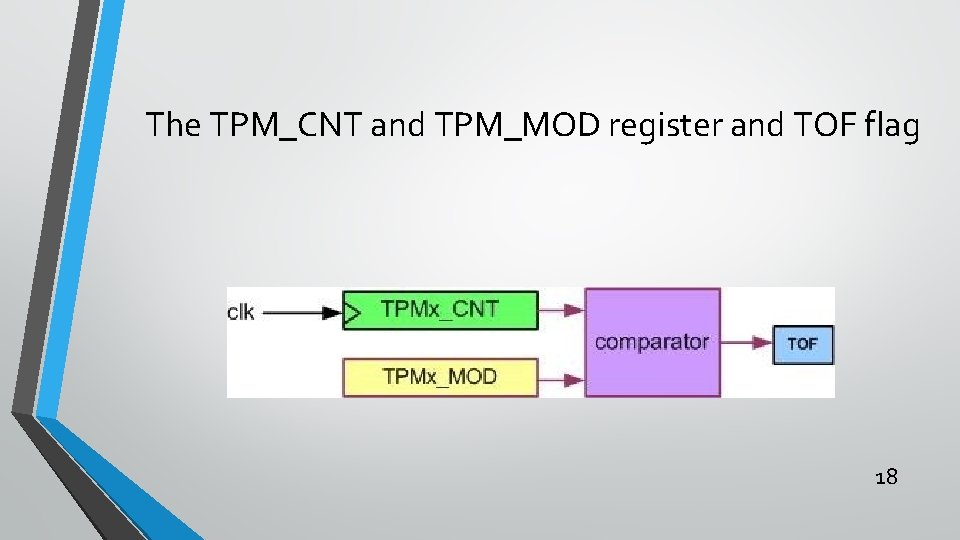

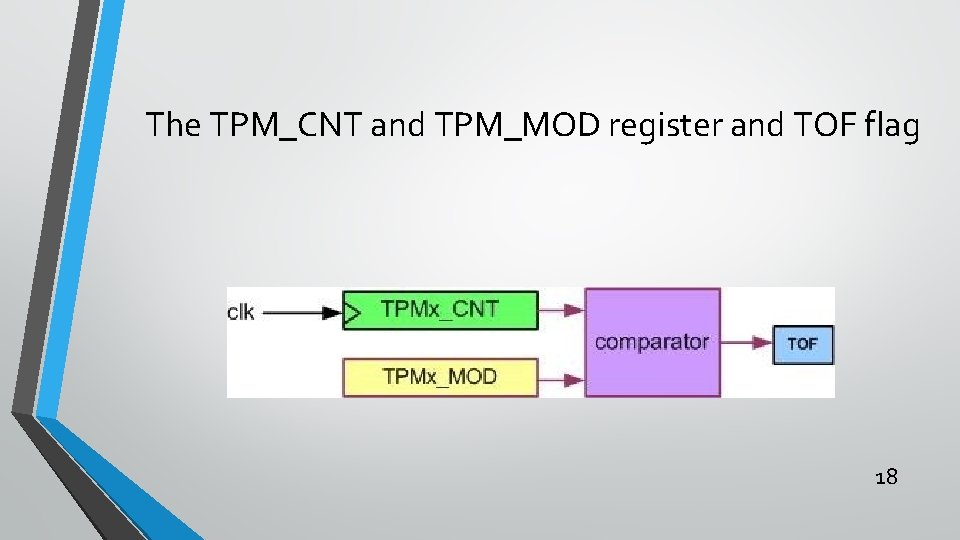

The TPM_CNT and TPM_MOD register and TOF flag 18

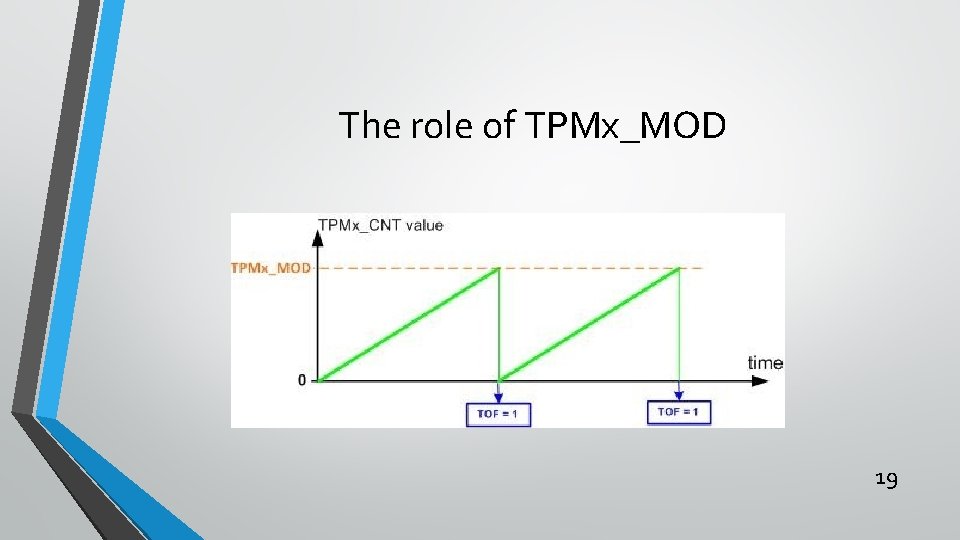

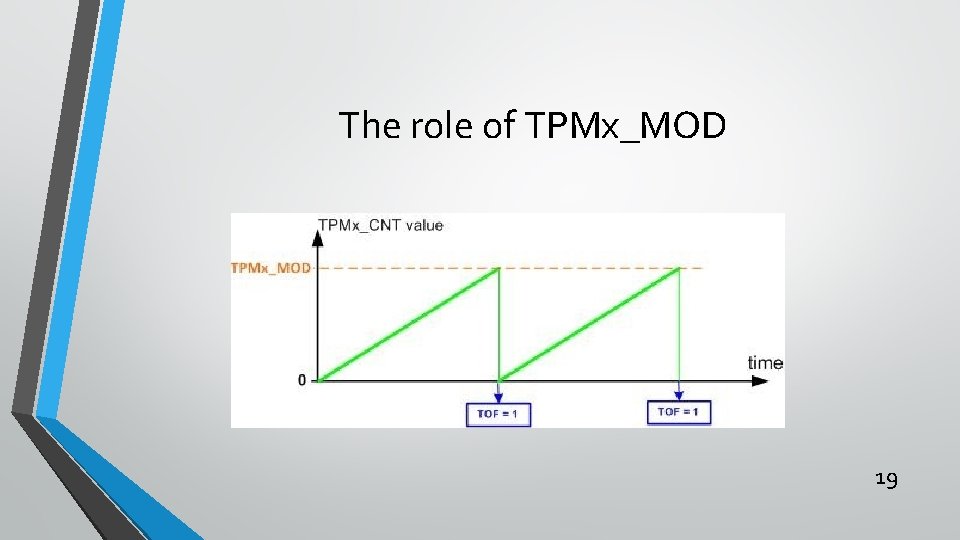

The role of TPMx_MOD 19

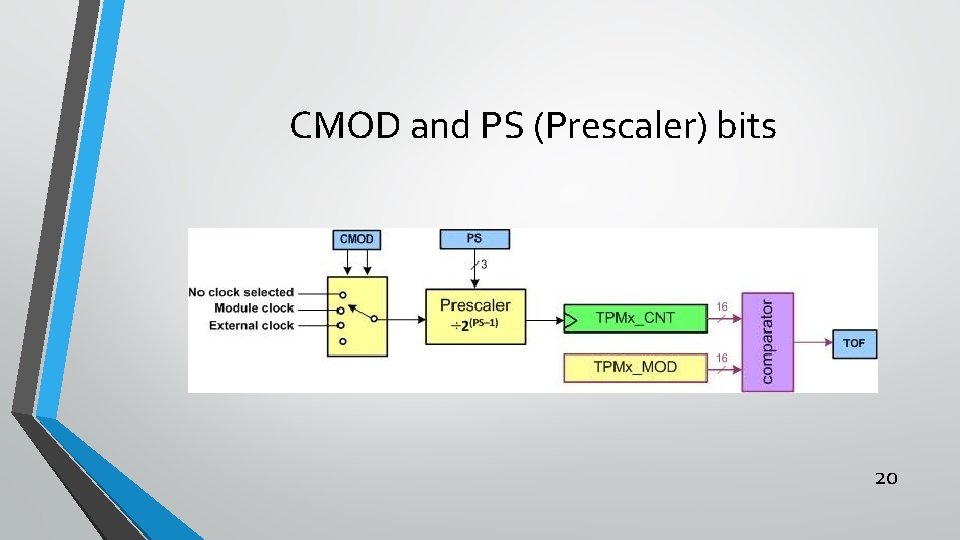

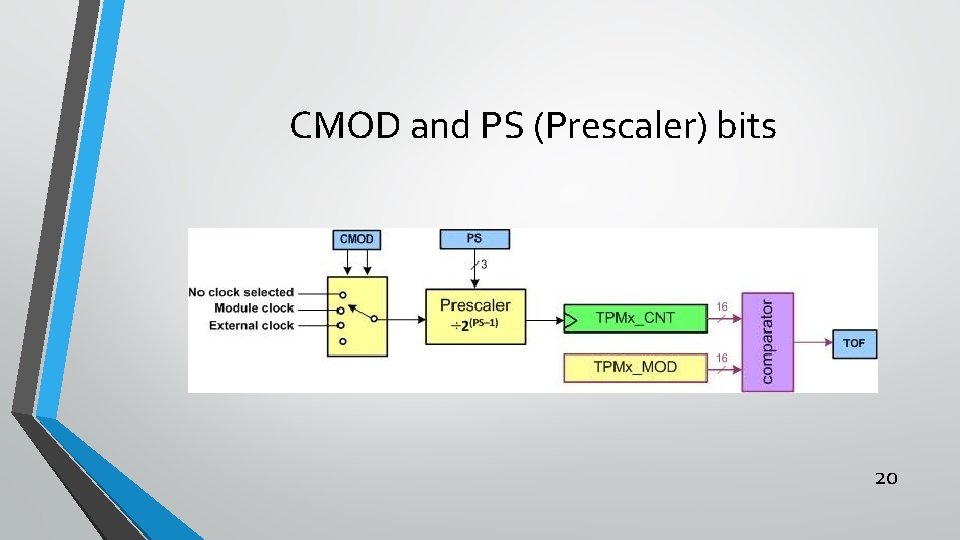

CMOD and PS (Prescaler) bits 20

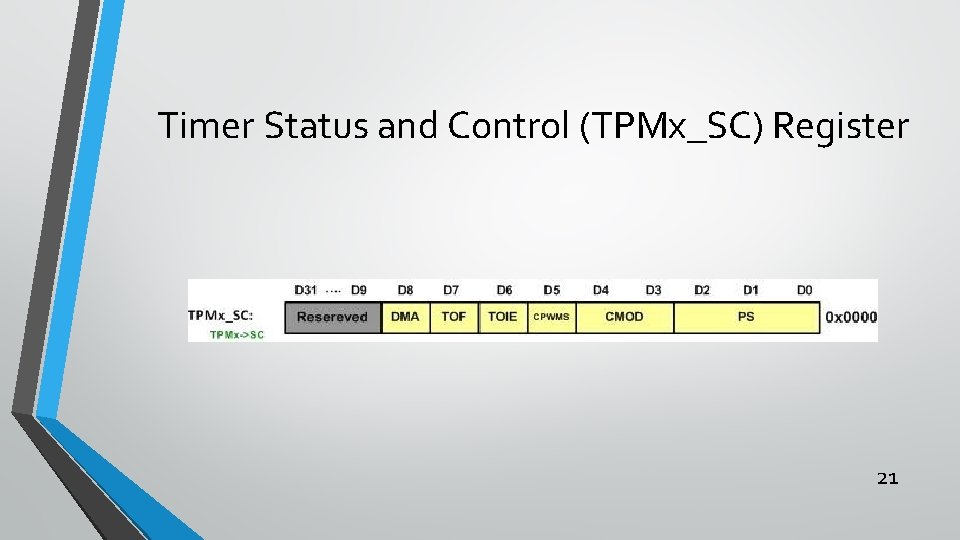

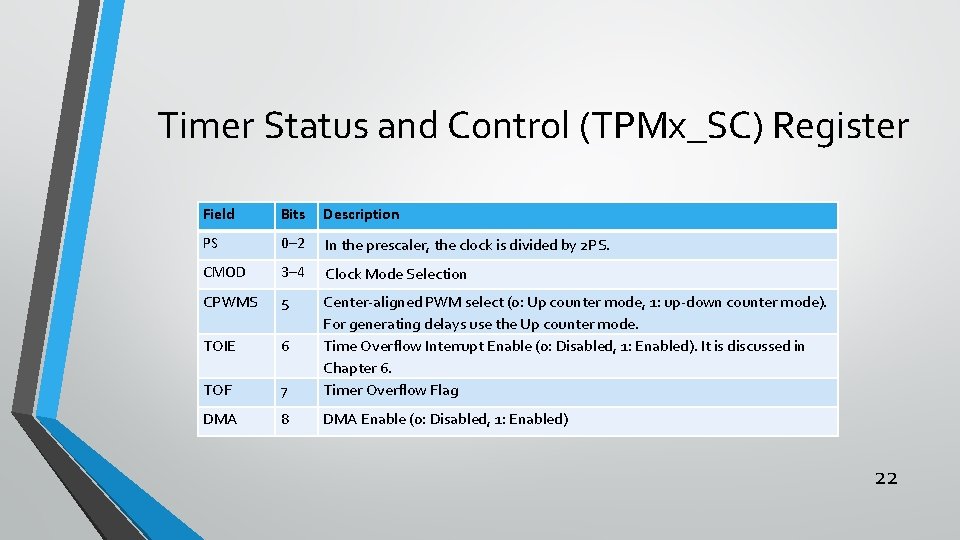

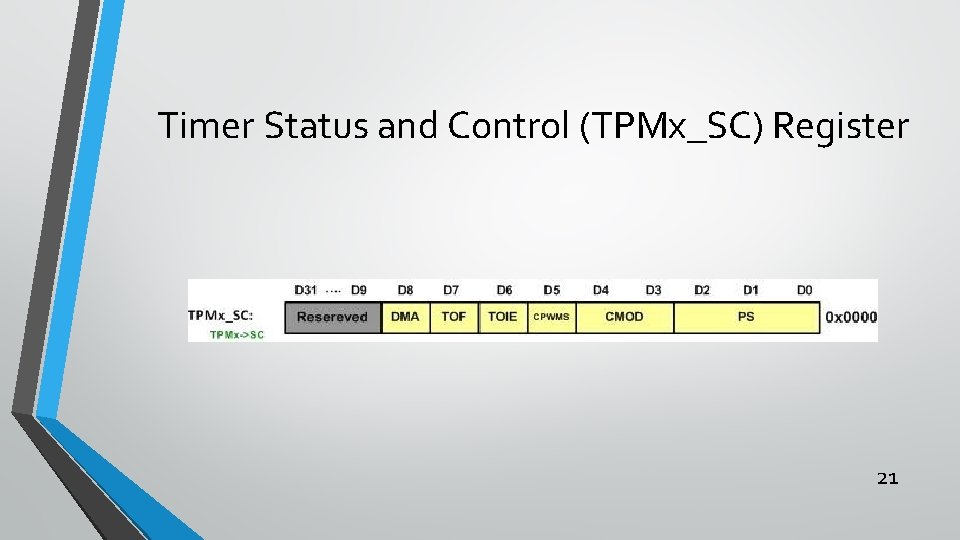

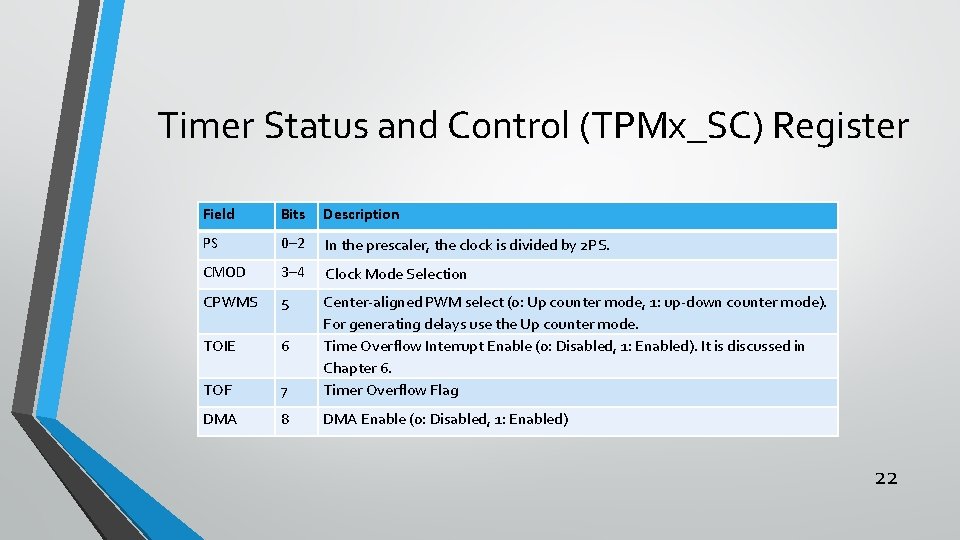

Timer Status and Control (TPMx_SC) Register 21

Timer Status and Control (TPMx_SC) Register Field Bits Description PS 0– 2 In the prescaler, the clock is divided by 2 PS. CMOD 3– 4 Clock Mode Selection CPWMS 5 TOIE 6 TOF 7 Center-aligned PWM select (0: Up counter mode, 1: up-down counter mode). For generating delays use the Up counter mode. Time Overflow Interrupt Enable (0: Disabled, 1: Enabled). It is discussed in Chapter 6. Timer Overflow Flag DMA 8 DMA Enable (0: Disabled, 1: Enabled) 22

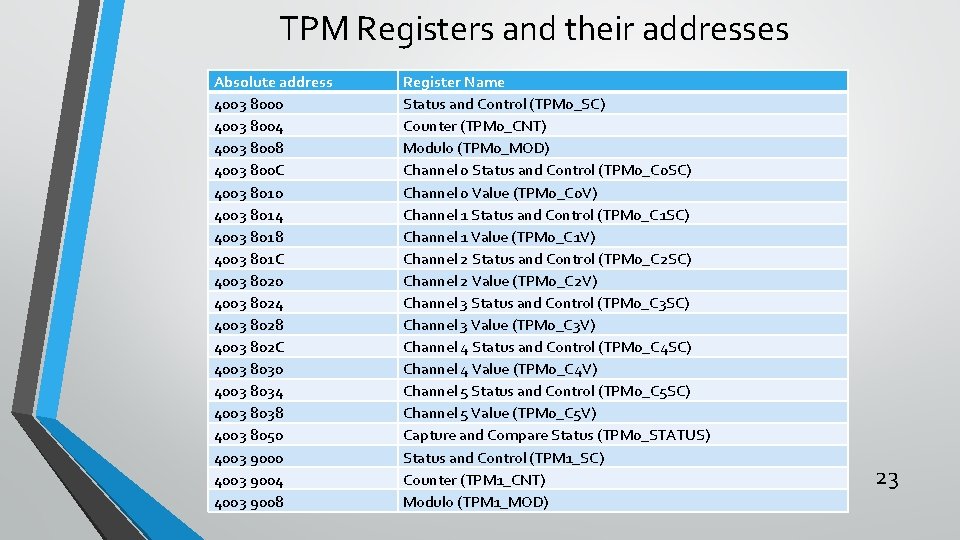

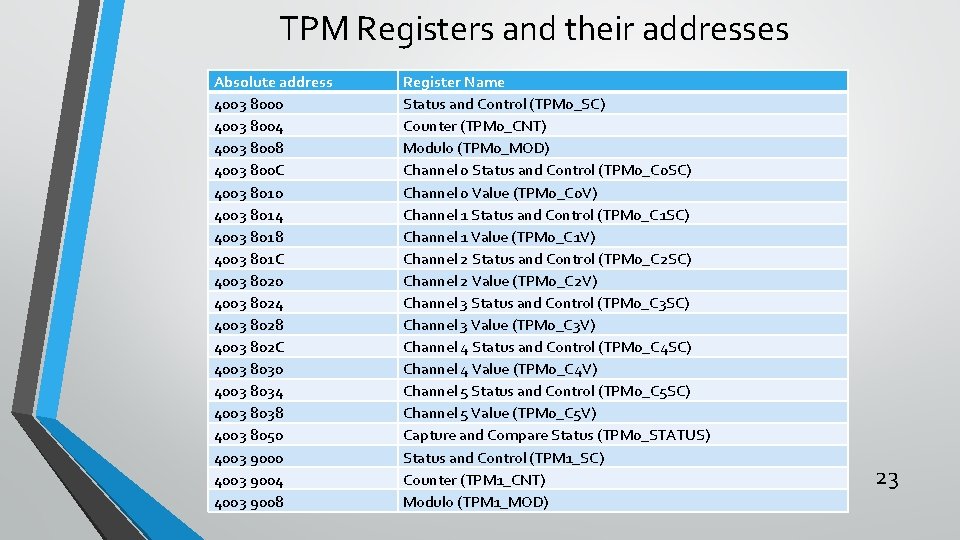

TPM Registers and their addresses Absolute address 4003 8000 4003 8004 4003 8008 4003 800 C 4003 8010 4003 8014 4003 8018 4003 801 C 4003 8020 4003 8024 4003 8028 4003 802 C 4003 8030 4003 8034 4003 8038 4003 8050 4003 9004 4003 9008 Register Name Status and Control (TPM 0_SC) Counter (TPM 0_CNT) Modulo (TPM 0_MOD) Channel 0 Status and Control (TPM 0_C 0 SC) Channel 0 Value (TPM 0_C 0 V) Channel 1 Status and Control (TPM 0_C 1 SC) Channel 1 Value (TPM 0_C 1 V) Channel 2 Status and Control (TPM 0_C 2 SC) Channel 2 Value (TPM 0_C 2 V) Channel 3 Status and Control (TPM 0_C 3 SC) Channel 3 Value (TPM 0_C 3 V) Channel 4 Status and Control (TPM 0_C 4 SC) Channel 4 Value (TPM 0_C 4 V) Channel 5 Status and Control (TPM 0_C 5 SC) Channel 5 Value (TPM 0_C 5 V) Capture and Compare Status (TPM 0_STATUS) Status and Control (TPM 1_SC) Counter (TPM 1_CNT) Modulo (TPM 1_MOD) 23

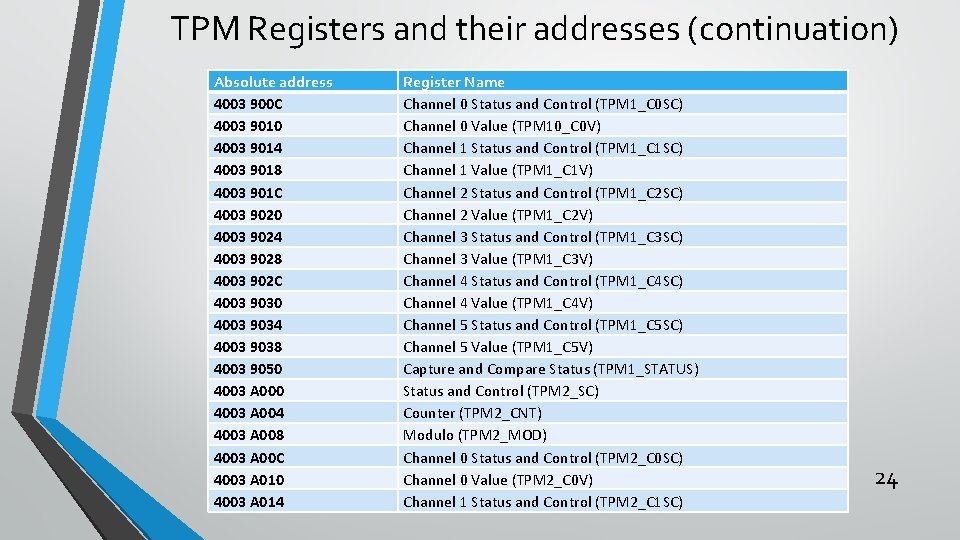

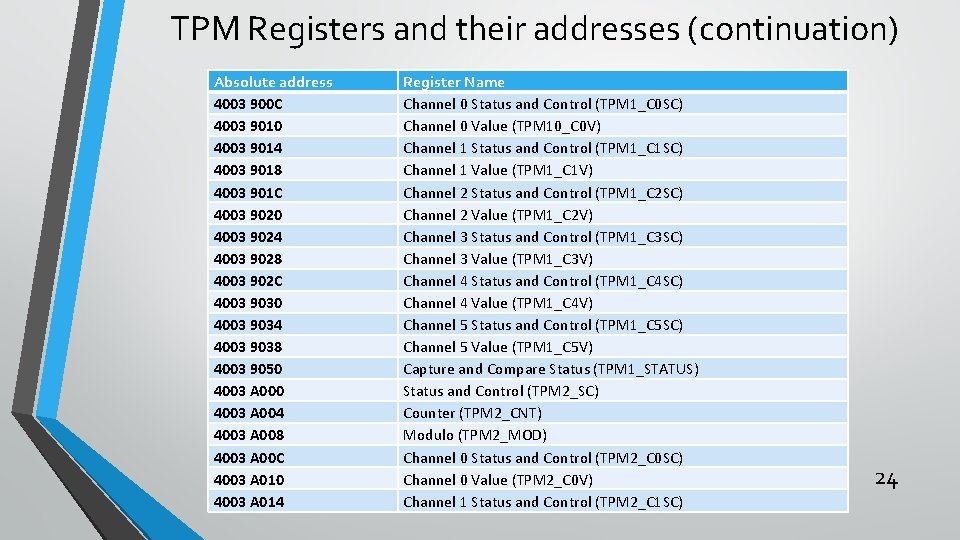

TPM Registers and their addresses (continuation) Absolute address 4003 900 C 4003 9010 4003 9014 4003 9018 4003 901 C 4003 9020 4003 9024 4003 9028 4003 902 C 4003 9030 4003 9034 4003 9038 4003 9050 4003 A 004 4003 A 008 4003 A 00 C 4003 A 010 4003 A 014 Register Name Channel 0 Status and Control (TPM 1_C 0 SC) Channel 0 Value (TPM 10_C 0 V) Channel 1 Status and Control (TPM 1_C 1 SC) Channel 1 Value (TPM 1_C 1 V) Channel 2 Status and Control (TPM 1_C 2 SC) Channel 2 Value (TPM 1_C 2 V) Channel 3 Status and Control (TPM 1_C 3 SC) Channel 3 Value (TPM 1_C 3 V) Channel 4 Status and Control (TPM 1_C 4 SC) Channel 4 Value (TPM 1_C 4 V) Channel 5 Status and Control (TPM 1_C 5 SC) Channel 5 Value (TPM 1_C 5 V) Capture and Compare Status (TPM 1_STATUS) Status and Control (TPM 2_SC) Counter (TPM 2_CNT) Modulo (TPM 2_MOD) Channel 0 Status and Control (TPM 2_C 0 SC) Channel 0 Value (TPM 2_C 0 V) Channel 1 Status and Control (TPM 2_C 1 SC) 24

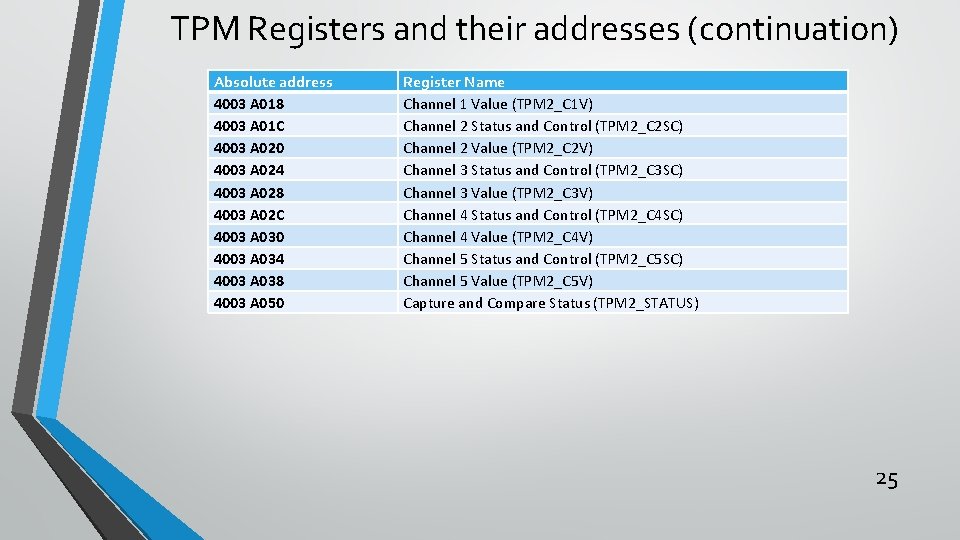

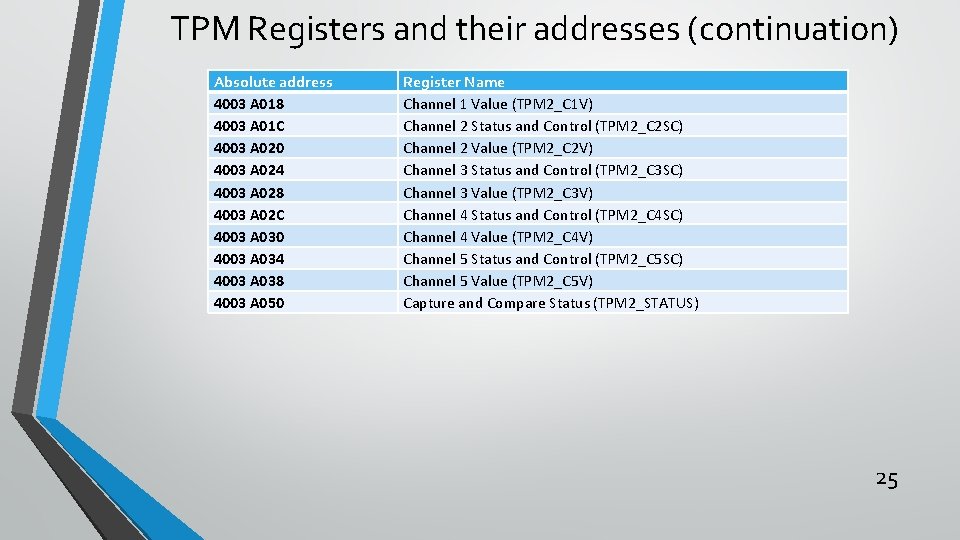

TPM Registers and their addresses (continuation) Absolute address 4003 A 018 4003 A 01 C 4003 A 020 4003 A 024 4003 A 028 4003 A 02 C 4003 A 030 4003 A 034 4003 A 038 4003 A 050 Register Name Channel 1 Value (TPM 2_C 1 V) Channel 2 Status and Control (TPM 2_C 2 SC) Channel 2 Value (TPM 2_C 2 V) Channel 3 Status and Control (TPM 2_C 3 SC) Channel 3 Value (TPM 2_C 3 V) Channel 4 Status and Control (TPM 2_C 4 SC) Channel 4 Value (TPM 2_C 4 V) Channel 5 Status and Control (TPM 2_C 5 SC) Channel 5 Value (TPM 2_C 5 V) Capture and Compare Status (TPM 2_STATUS) 25

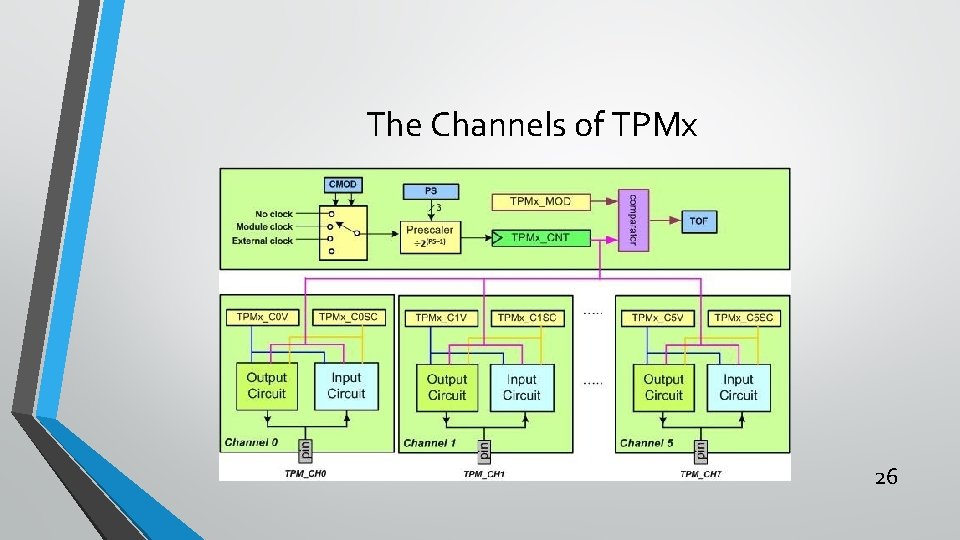

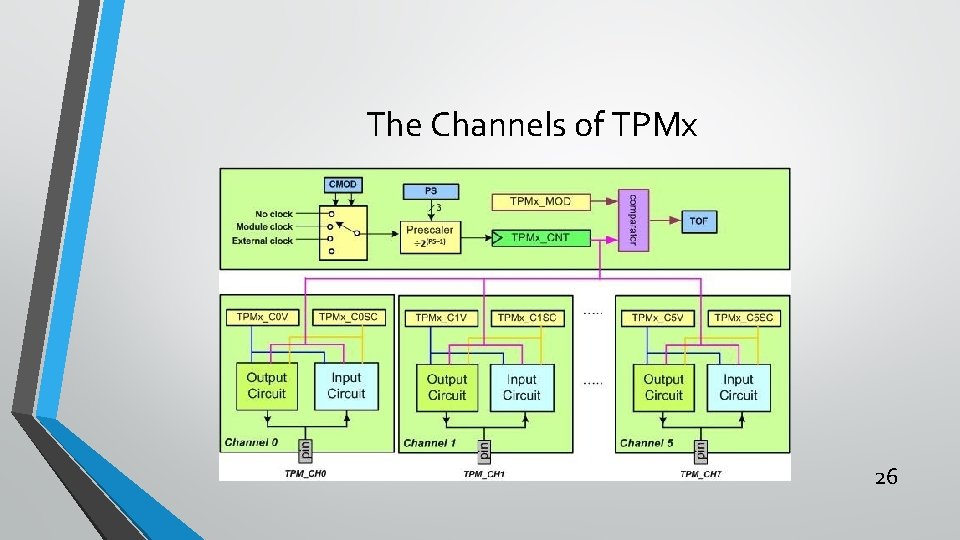

The Channels of TPMx 26

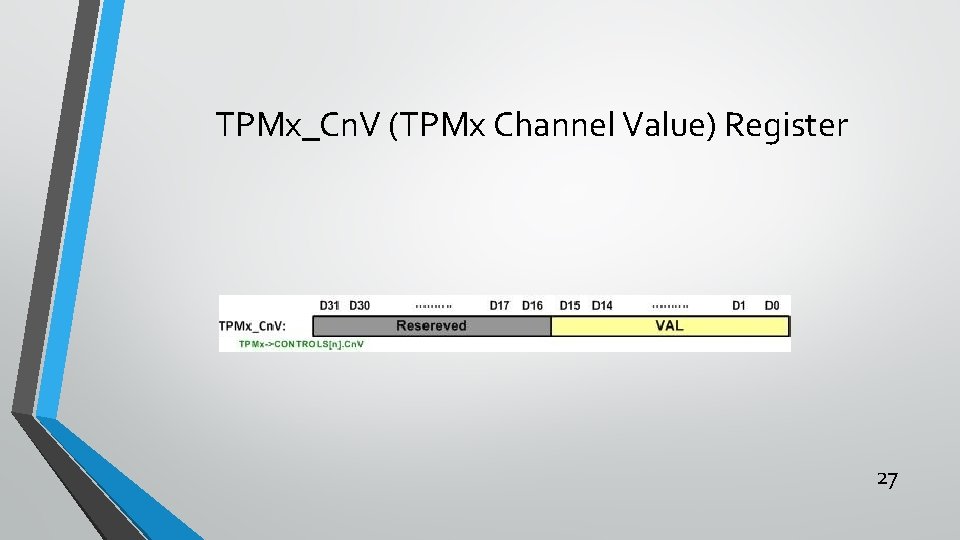

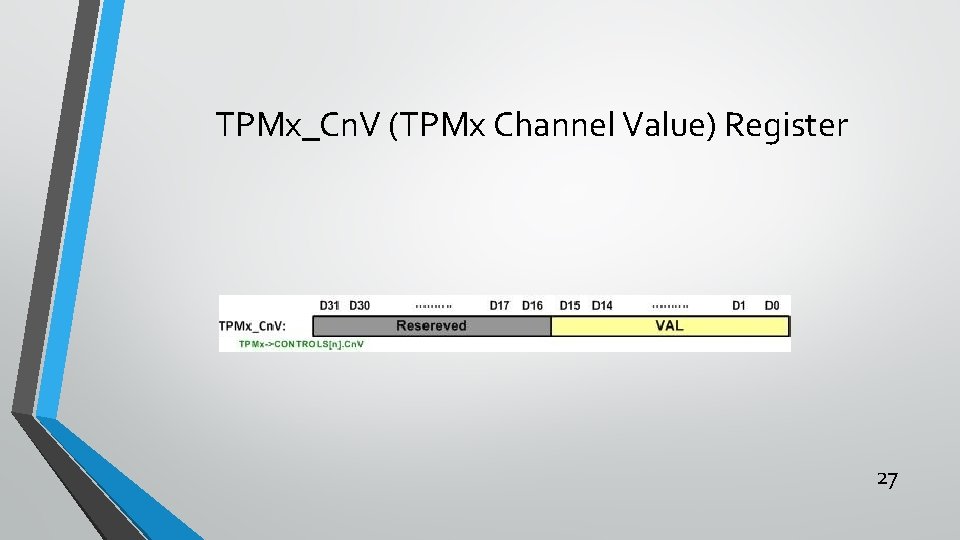

TPMx_Cn. V (TPMx Channel Value) Register 27

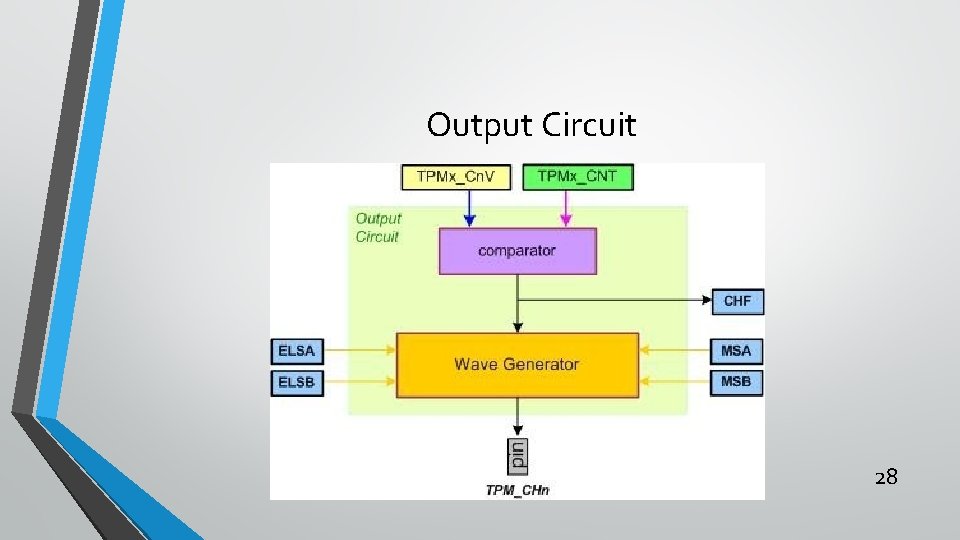

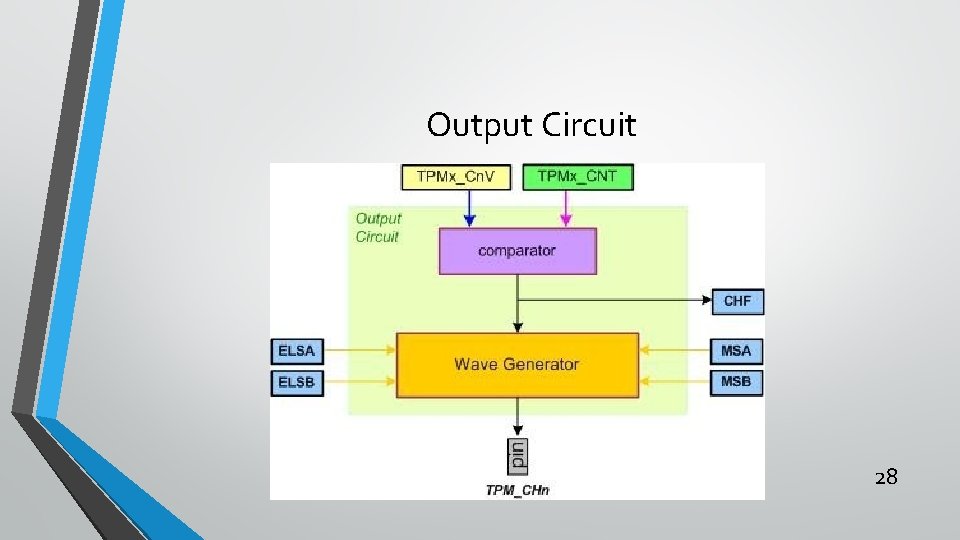

Output Circuit 28

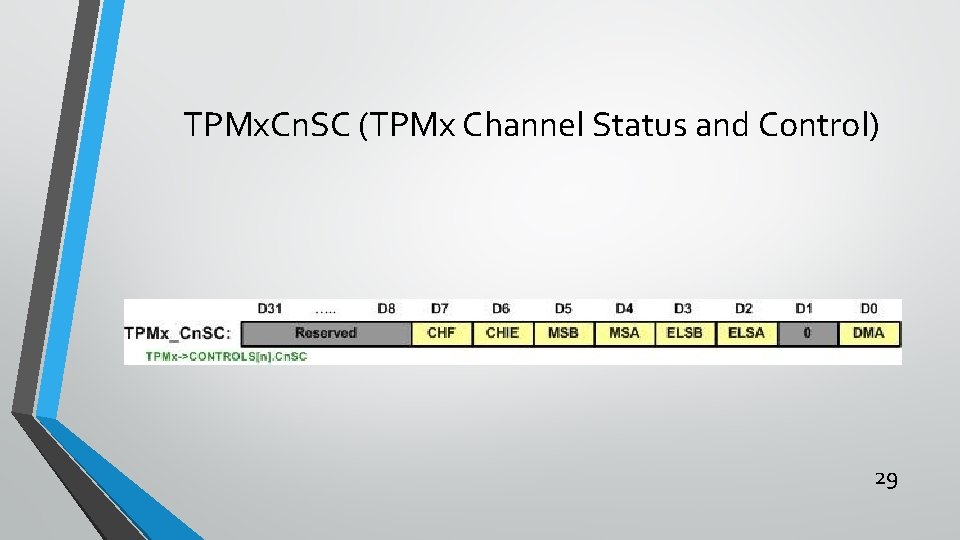

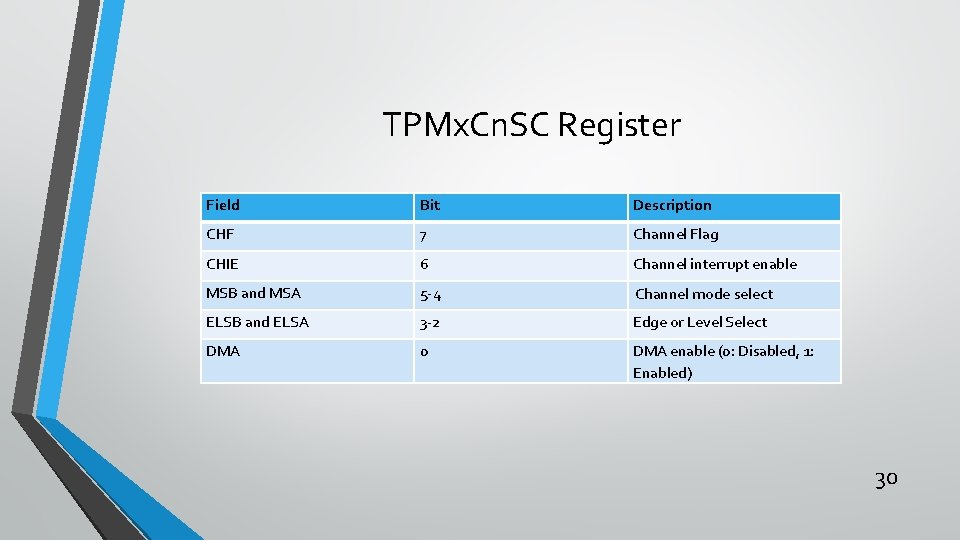

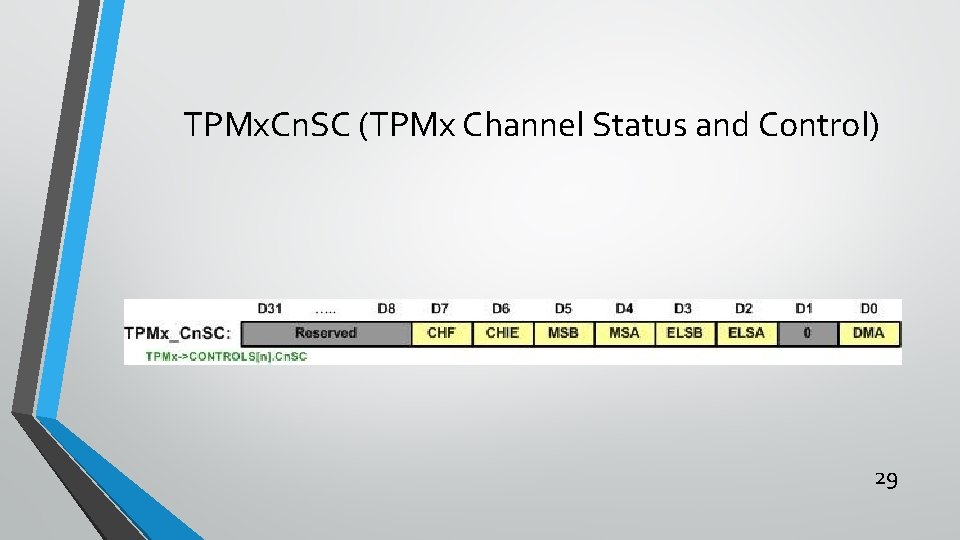

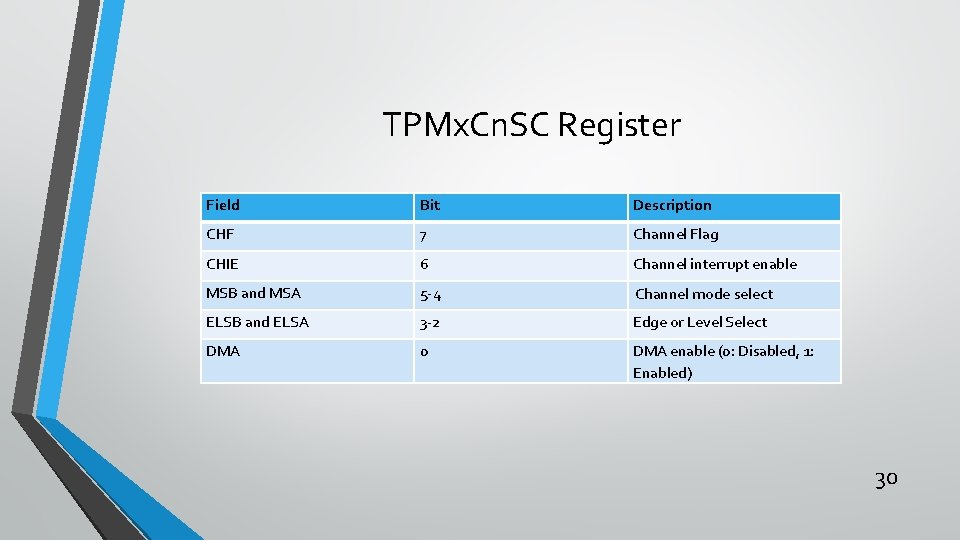

TPMx. Cn. SC (TPMx Channel Status and Control) 29

TPMx. Cn. SC Register Field Bit Description CHF 7 Channel Flag CHIE 6 Channel interrupt enable MSB and MSA 5 -4 Channel mode select ELSB and ELSA 3 -2 Edge or Level Select DMA 0 DMA enable (0: Disabled, 1: Enabled) 30

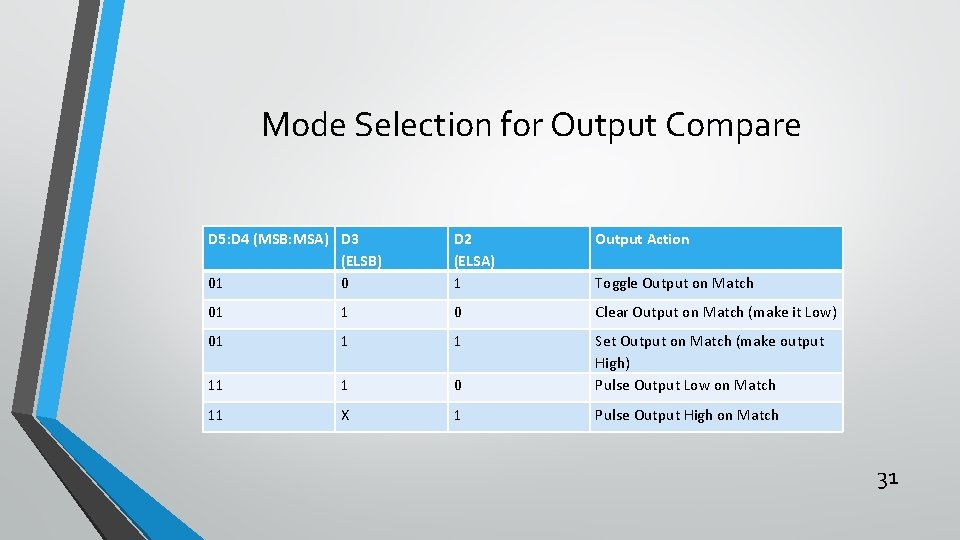

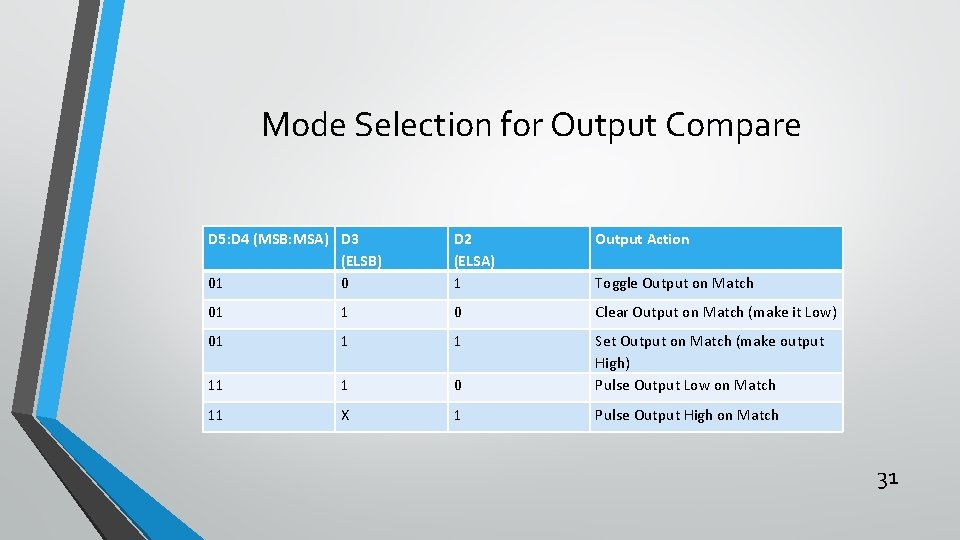

Mode Selection for Output Compare D 5: D 4 (MSB: MSA) D 3 (ELSB) 01 0 D 2 (ELSA) 1 Output Action 01 1 0 Clear Output on Match (make it Low) 01 1 1 11 1 0 Set Output on Match (make output High) Pulse Output Low on Match 11 X 1 Pulse Output High on Match Toggle Output on Match 31

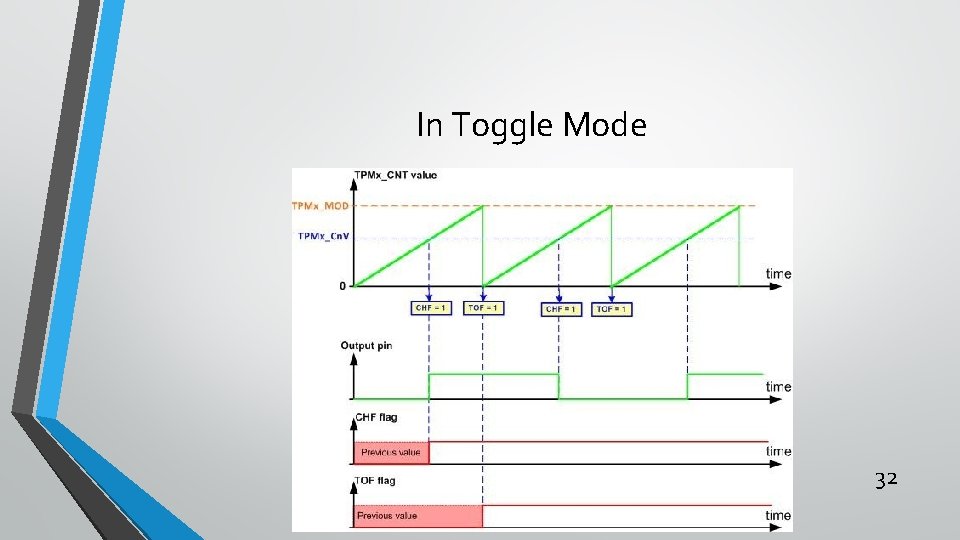

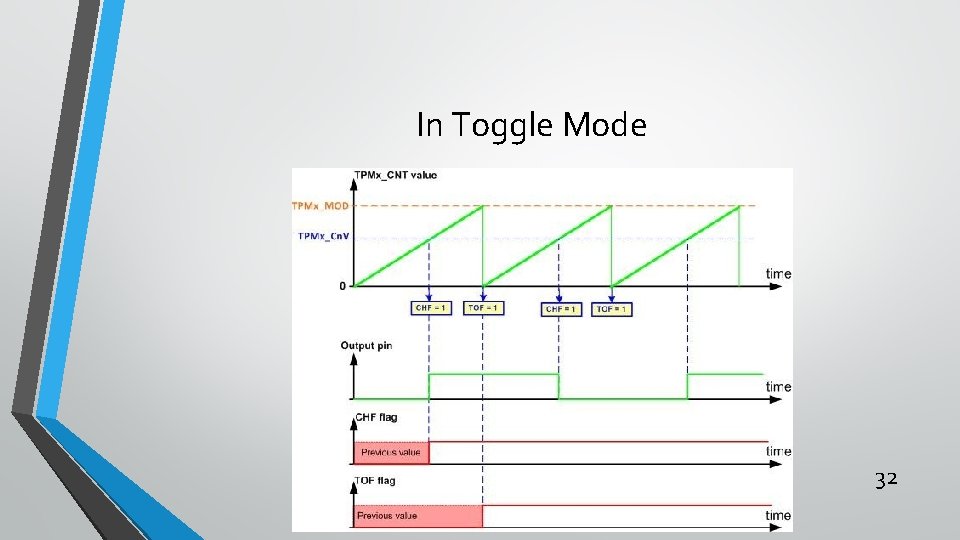

In Toggle Mode 32

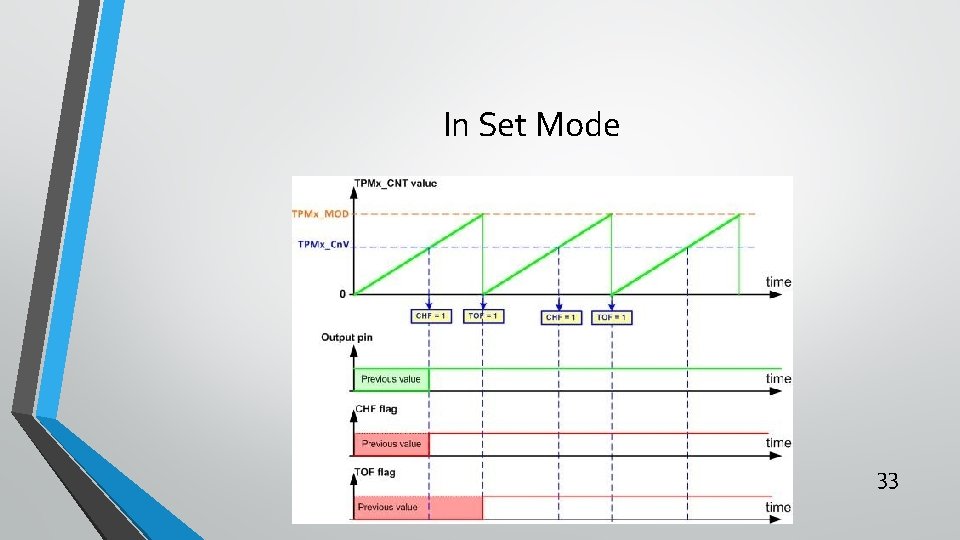

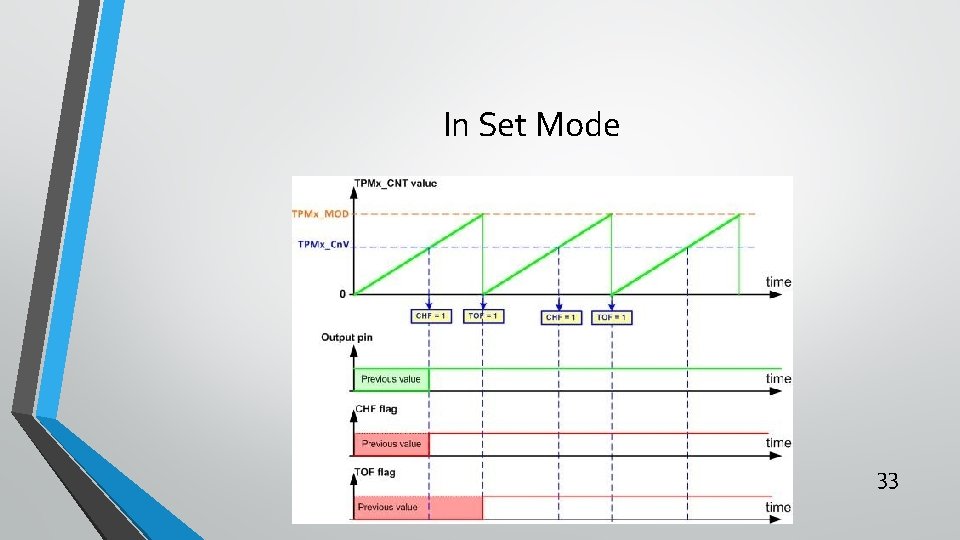

In Set Mode 33

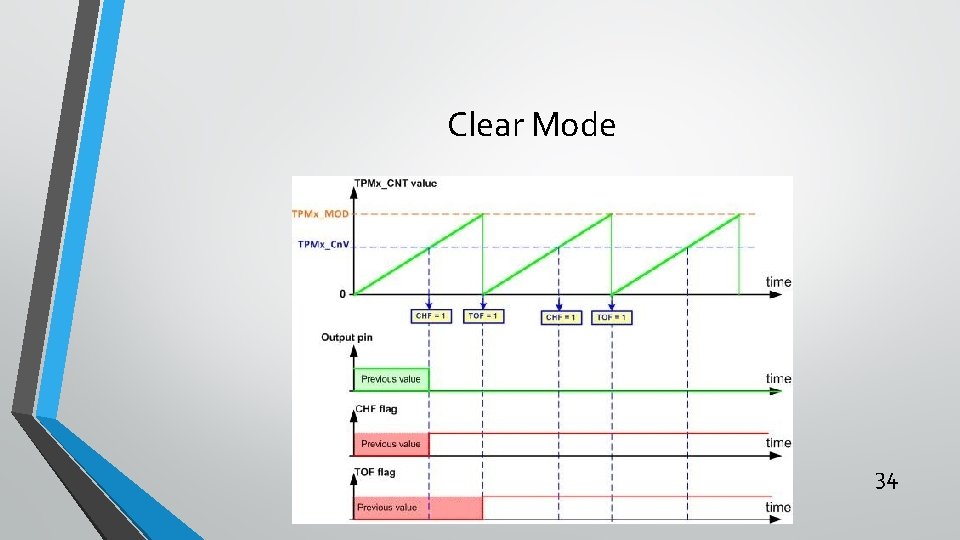

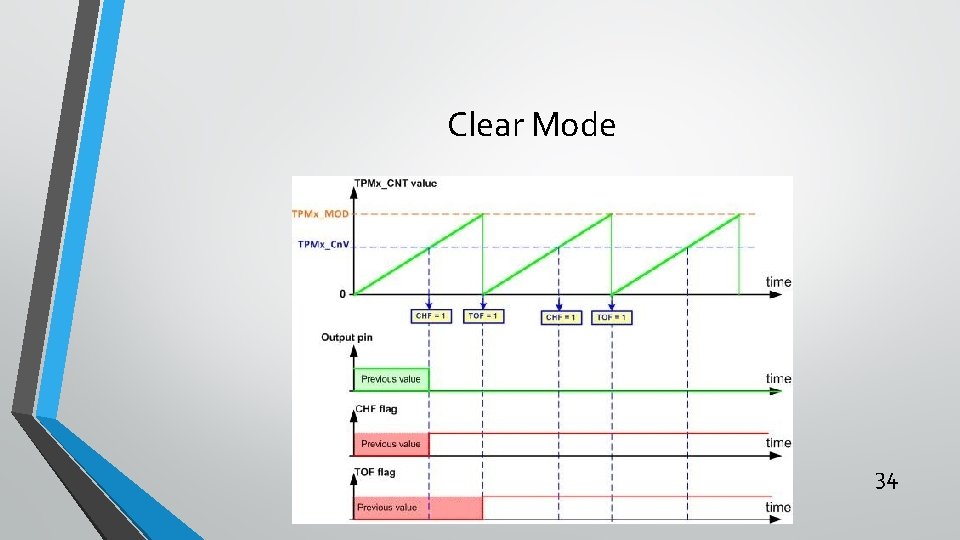

Clear Mode 34

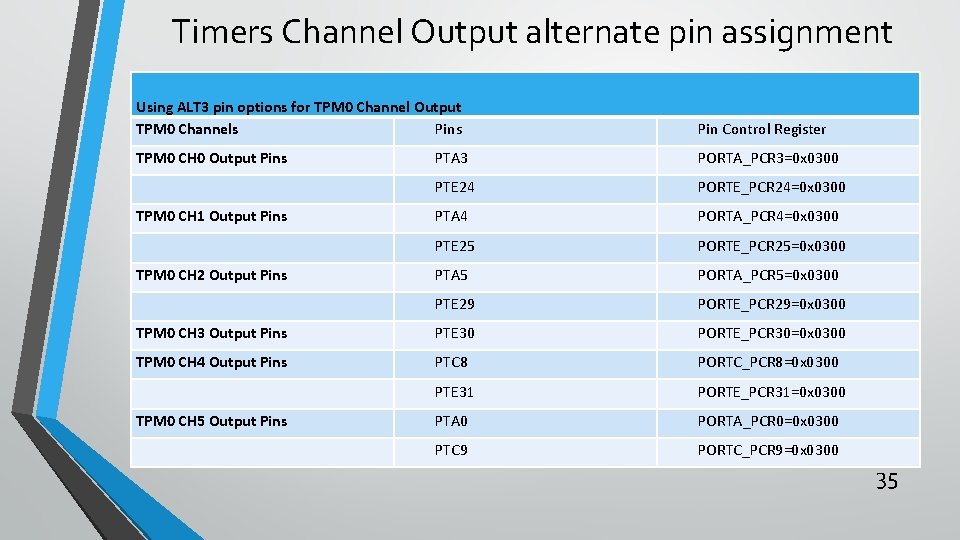

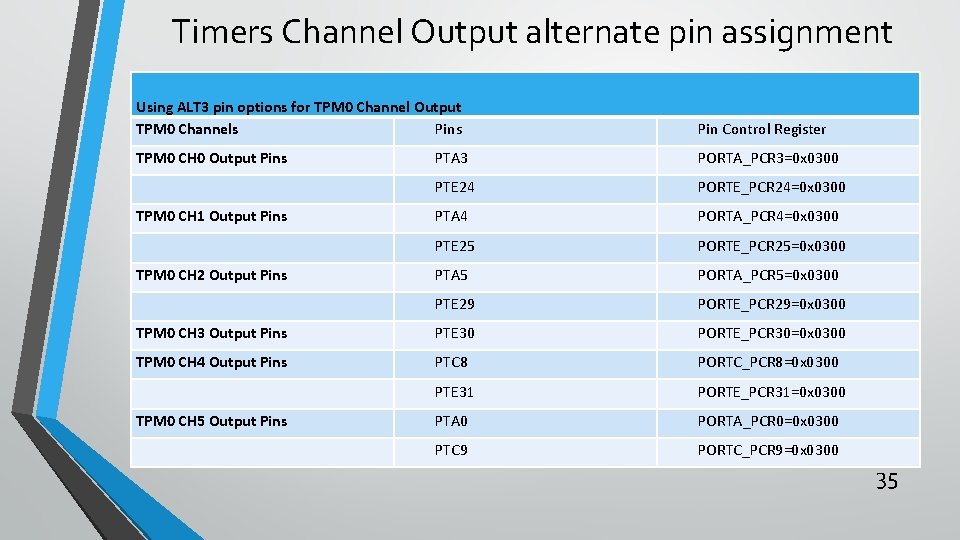

Timers Channel Output alternate pin assignment Using ALT 3 pin options for TPM 0 Channel Output TPM 0 Channels Pin Control Register TPM 0 CH 0 Output Pins PTA 3 PORTA_PCR 3=0 x 0300 PTE 24 PORTE_PCR 24=0 x 0300 PTA 4 PORTA_PCR 4=0 x 0300 PTE 25 PORTE_PCR 25=0 x 0300 PTA 5 PORTA_PCR 5=0 x 0300 PTE 29 PORTE_PCR 29=0 x 0300 TPM 0 CH 3 Output Pins PTE 30 PORTE_PCR 30=0 x 0300 TPM 0 CH 4 Output Pins PTC 8 PORTC_PCR 8=0 x 0300 PTE 31 PORTE_PCR 31=0 x 0300 PTA 0 PORTA_PCR 0=0 x 0300 PTC 9 PORTC_PCR 9=0 x 0300 TPM 0 CH 1 Output Pins TPM 0 CH 2 Output Pins TPM 0 CH 5 Output Pins 35

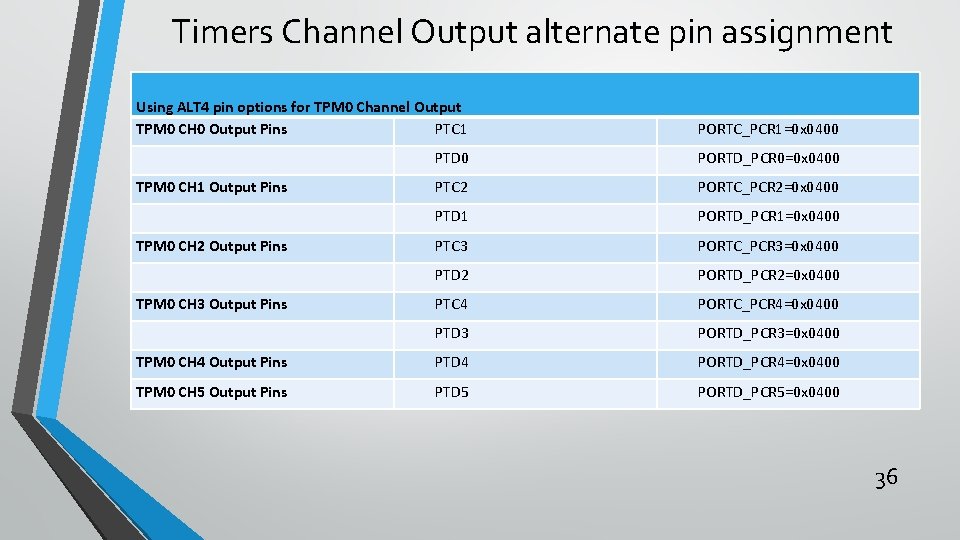

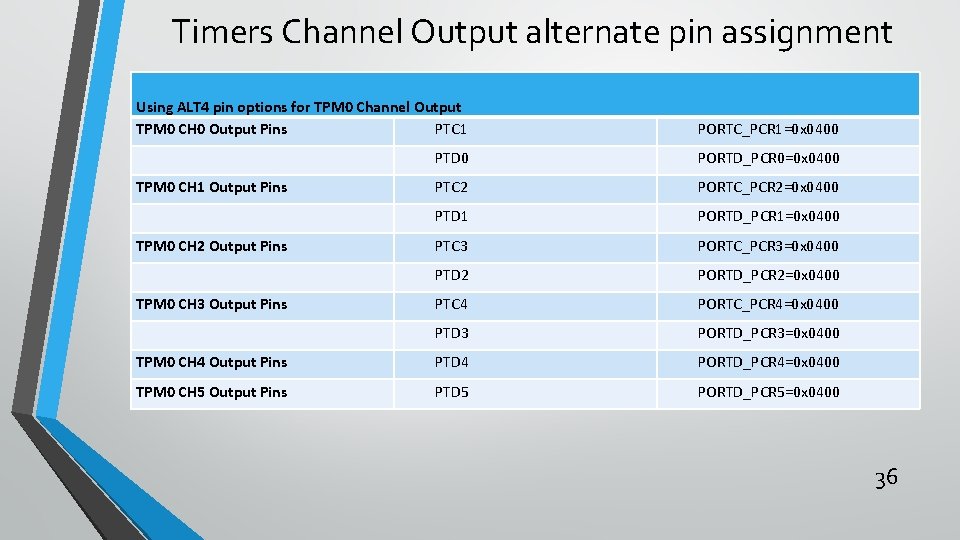

Timers Channel Output alternate pin assignment Using ALT 4 pin options for TPM 0 Channel Output TPM 0 CH 0 Output Pins PTC 1 PORTC_PCR 1=0 x 0400 PTD 0 PORTD_PCR 0=0 x 0400 PTC 2 PORTC_PCR 2=0 x 0400 PTD 1 PORTD_PCR 1=0 x 0400 PTC 3 PORTC_PCR 3=0 x 0400 PTD 2 PORTD_PCR 2=0 x 0400 PTC 4 PORTC_PCR 4=0 x 0400 PTD 3 PORTD_PCR 3=0 x 0400 TPM 0 CH 4 Output Pins PTD 4 PORTD_PCR 4=0 x 0400 TPM 0 CH 5 Output Pins PTD 5 PORTD_PCR 5=0 x 0400 TPM 0 CH 1 Output Pins TPM 0 CH 2 Output Pins TPM 0 CH 3 Output Pins 36

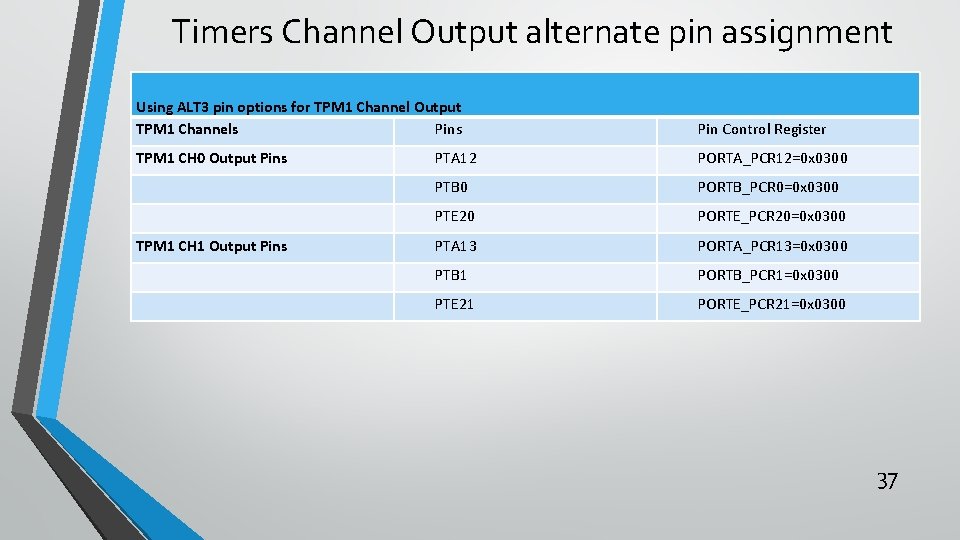

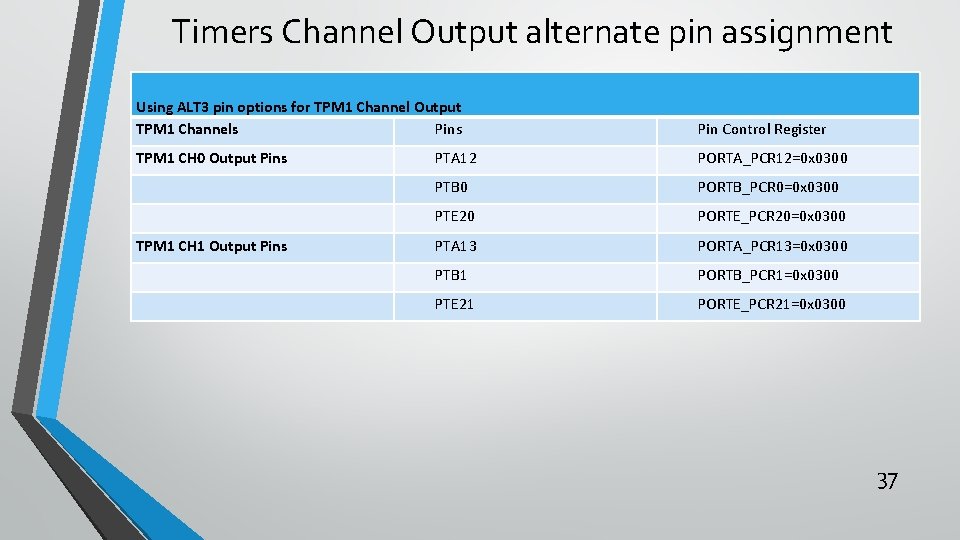

Timers Channel Output alternate pin assignment Using ALT 3 pin options for TPM 1 Channel Output TPM 1 Channels Pin Control Register TPM 1 CH 0 Output Pins PTA 12 PORTA_PCR 12=0 x 0300 PTB 0 PORTB_PCR 0=0 x 0300 PTE 20 PORTE_PCR 20=0 x 0300 PTA 13 PORTA_PCR 13=0 x 0300 PTB 1 PORTB_PCR 1=0 x 0300 PTE 21 PORTE_PCR 21=0 x 0300 TPM 1 CH 1 Output Pins 37

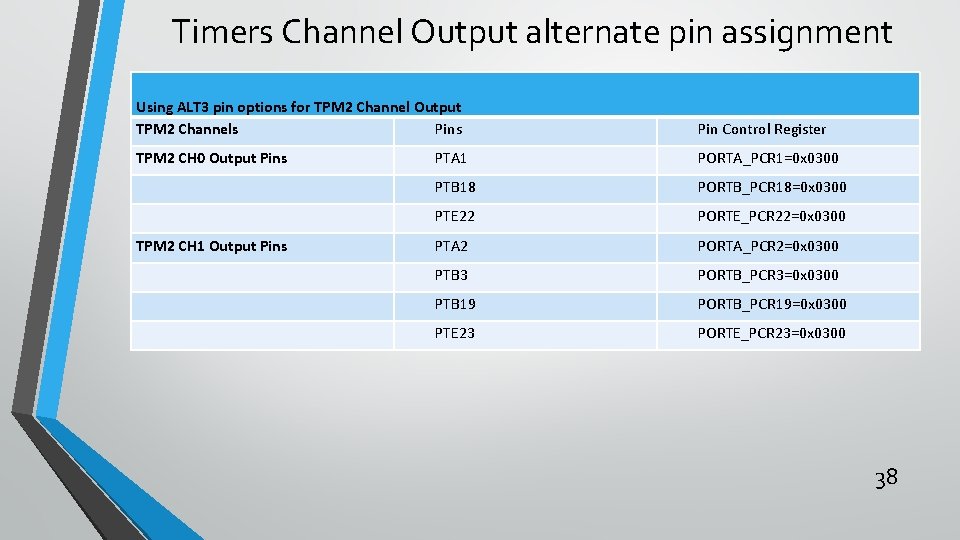

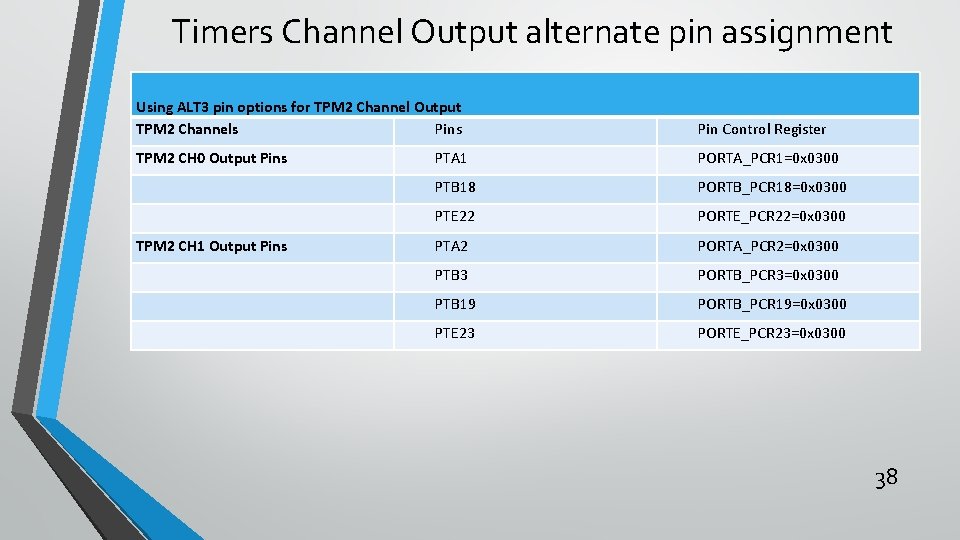

Timers Channel Output alternate pin assignment Using ALT 3 pin options for TPM 2 Channel Output TPM 2 Channels Pin Control Register TPM 2 CH 0 Output Pins PTA 1 PORTA_PCR 1=0 x 0300 PTB 18 PORTB_PCR 18=0 x 0300 PTE 22 PORTE_PCR 22=0 x 0300 PTA 2 PORTA_PCR 2=0 x 0300 PTB 3 PORTB_PCR 3=0 x 0300 PTB 19 PORTB_PCR 19=0 x 0300 PTE 23 PORTE_PCR 23=0 x 0300 TPM 2 CH 1 Output Pins 38

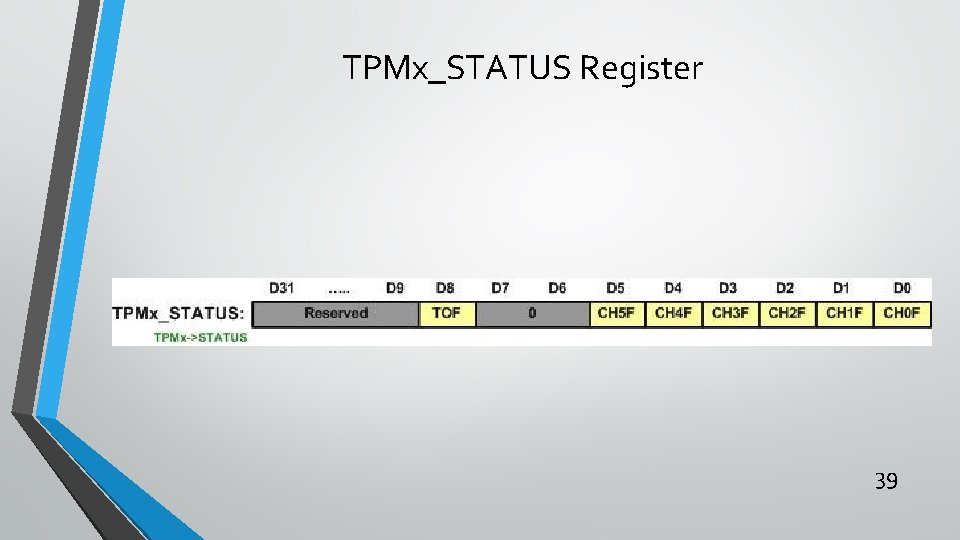

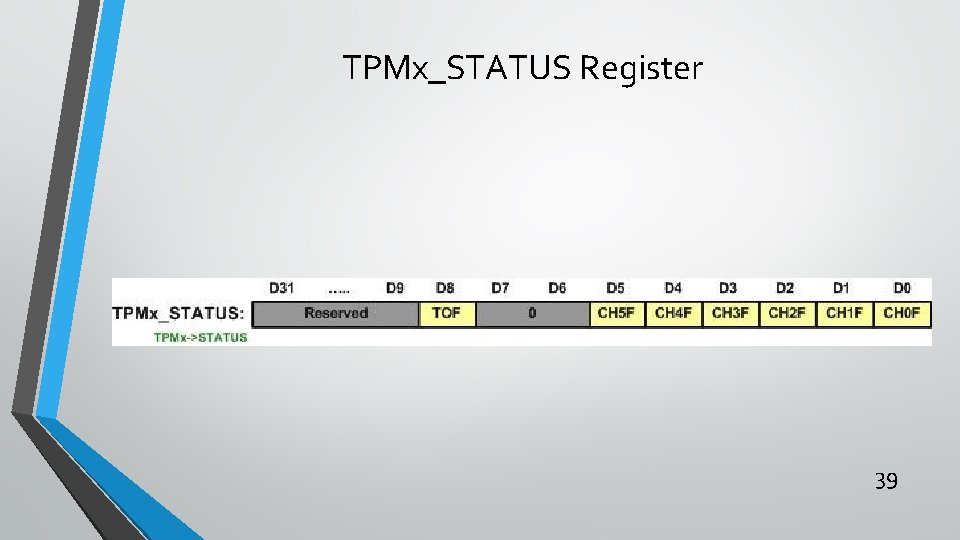

TPMx_STATUS Register 39

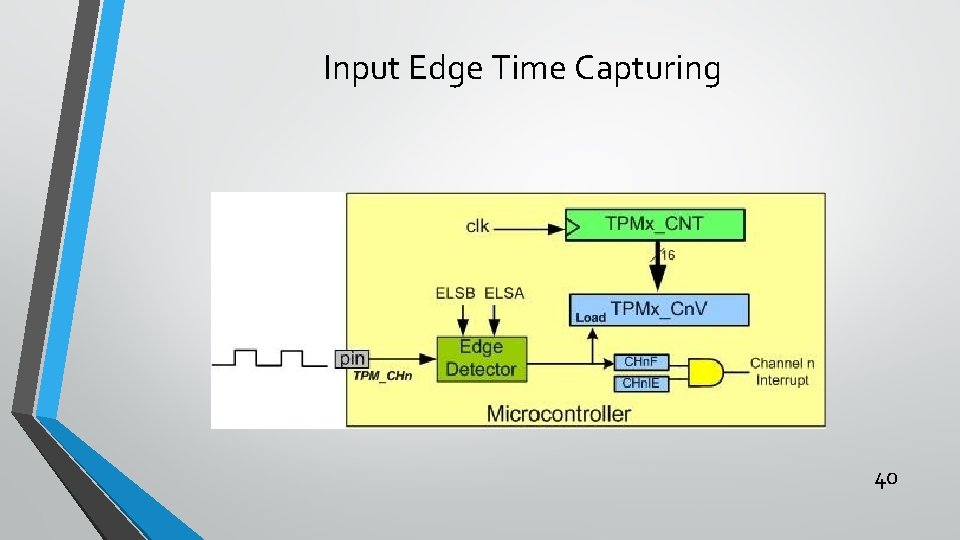

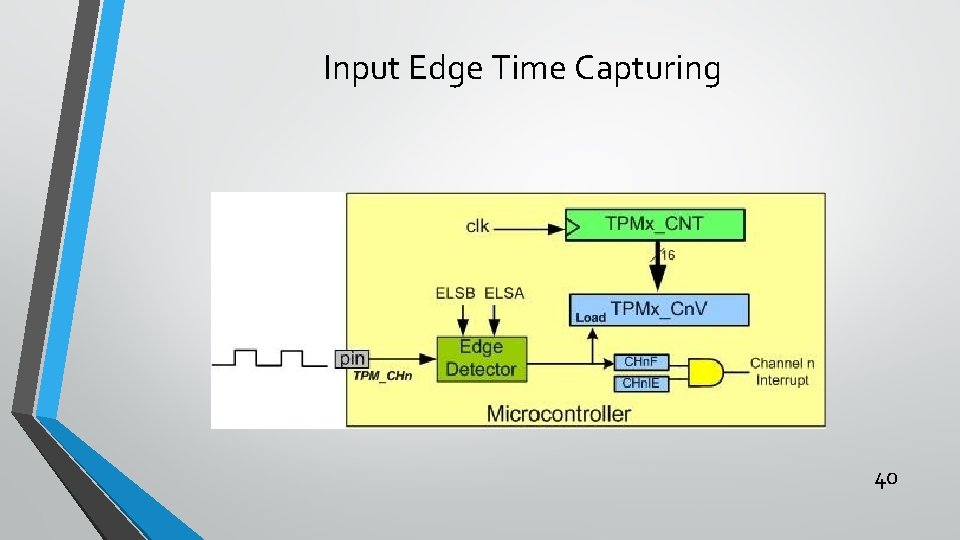

Input Edge Time Capturing 40

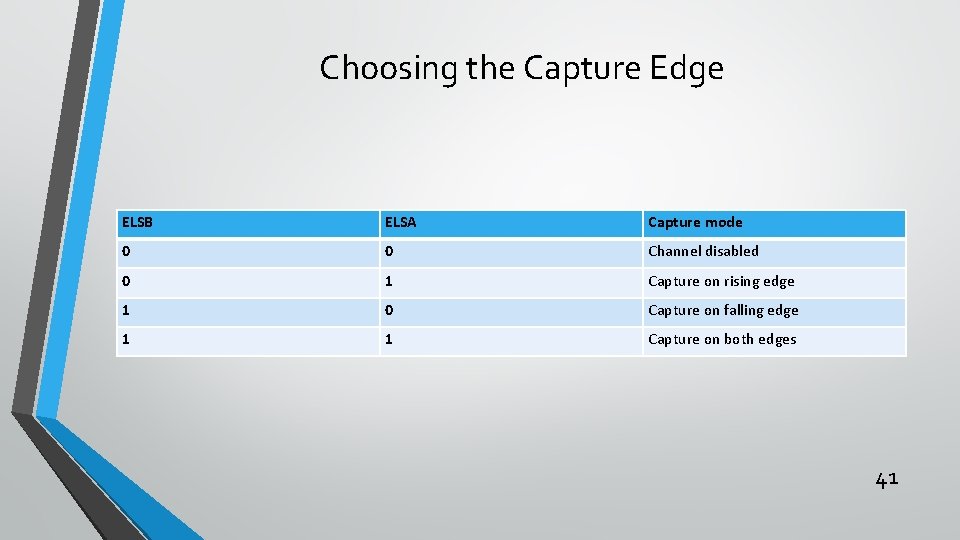

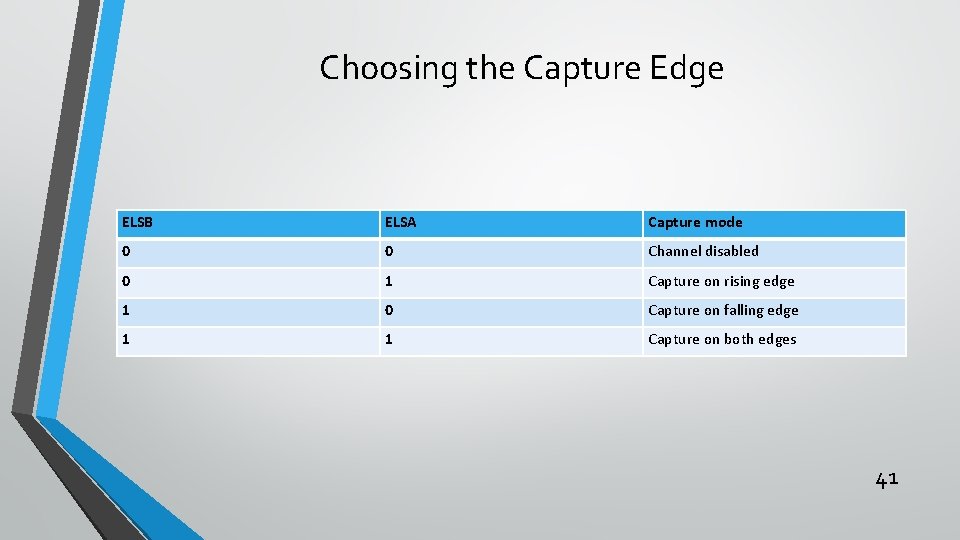

Choosing the Capture Edge ELSB ELSA Capture mode 0 0 Channel disabled 0 1 Capture on rising edge 1 0 Capture on falling edge 1 1 Capture on both edges 41

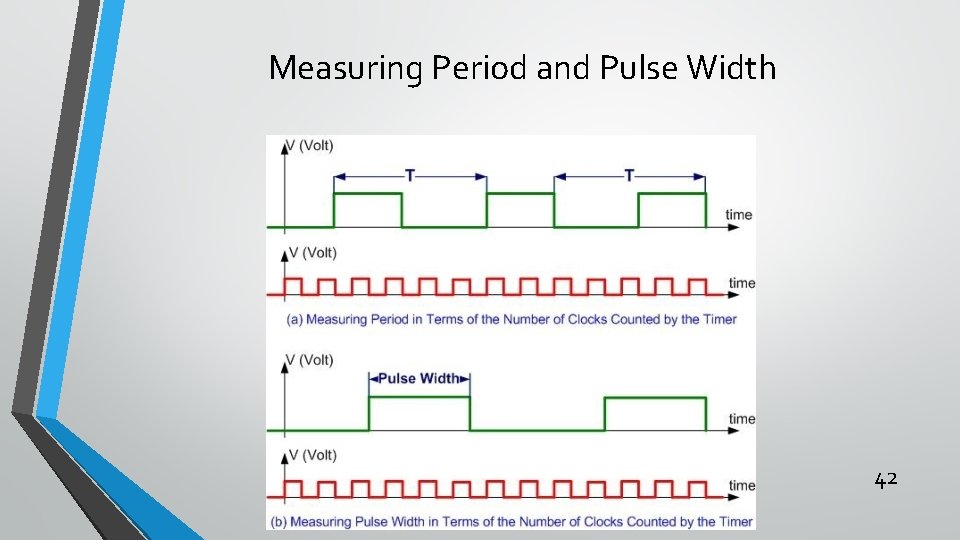

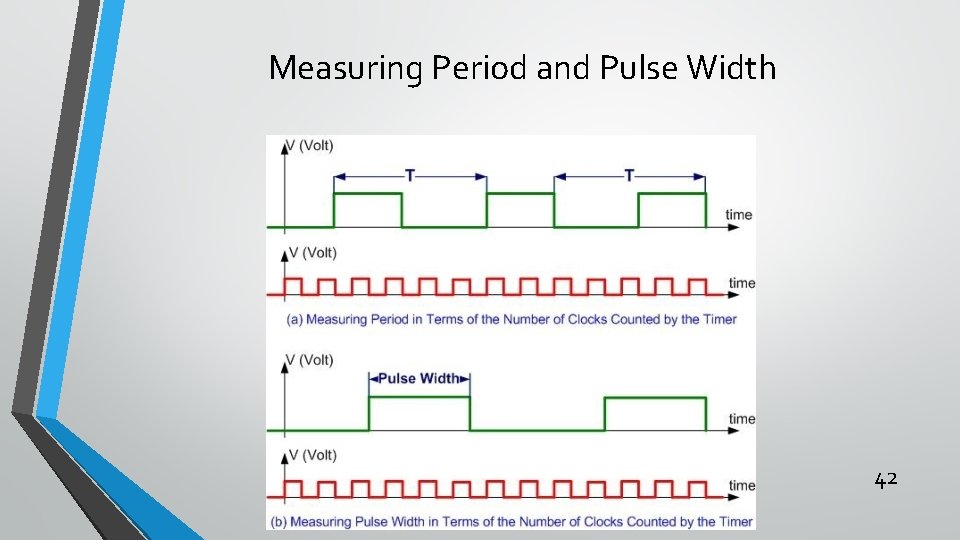

Measuring Period and Pulse Width 42

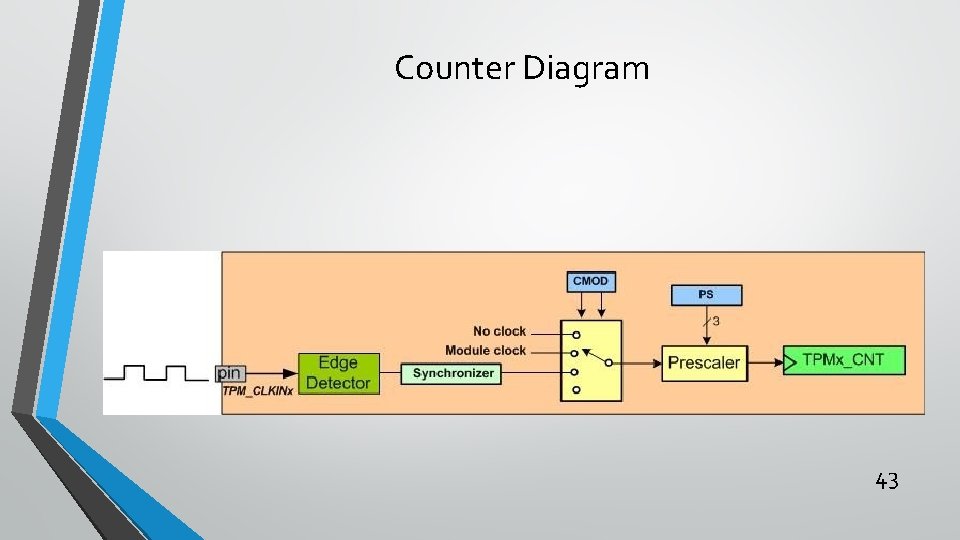

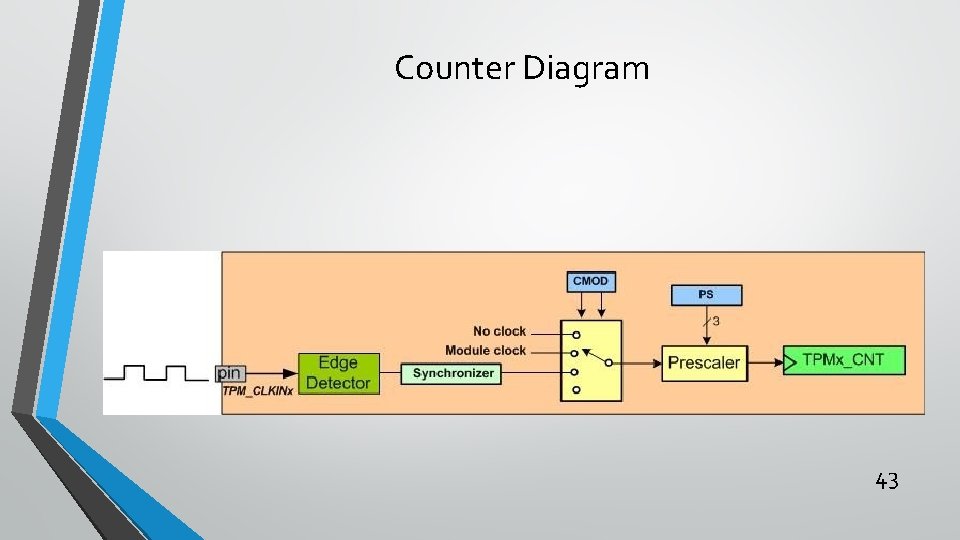

Counter Diagram 43

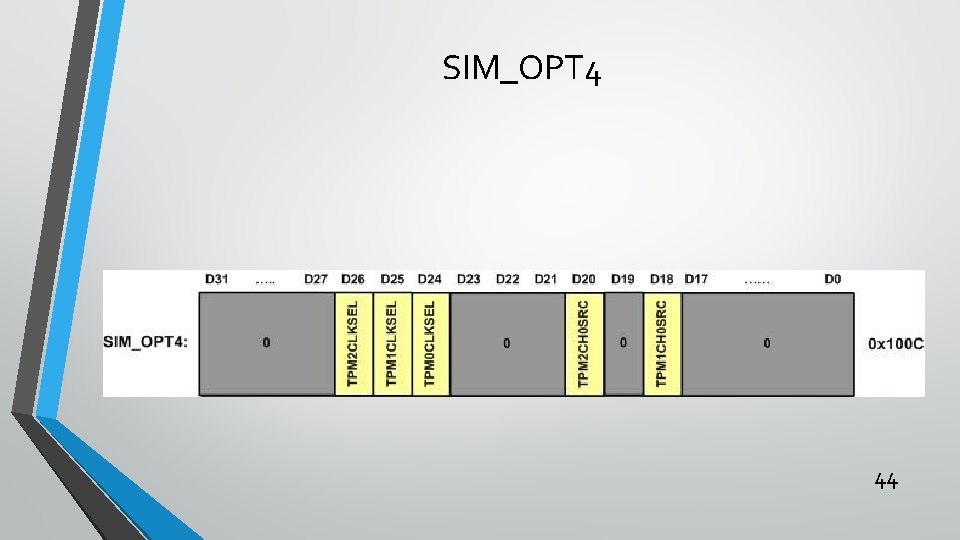

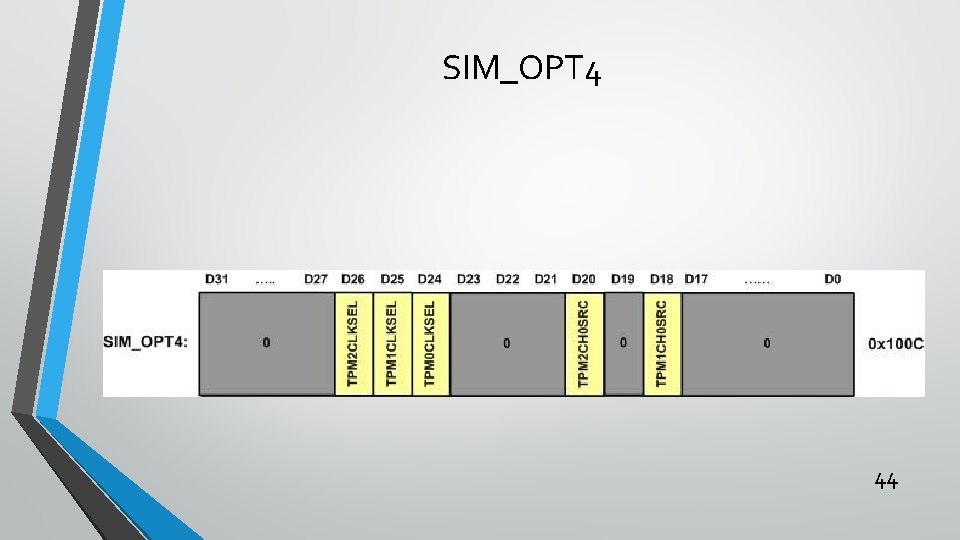

SIM_OPT 4 44

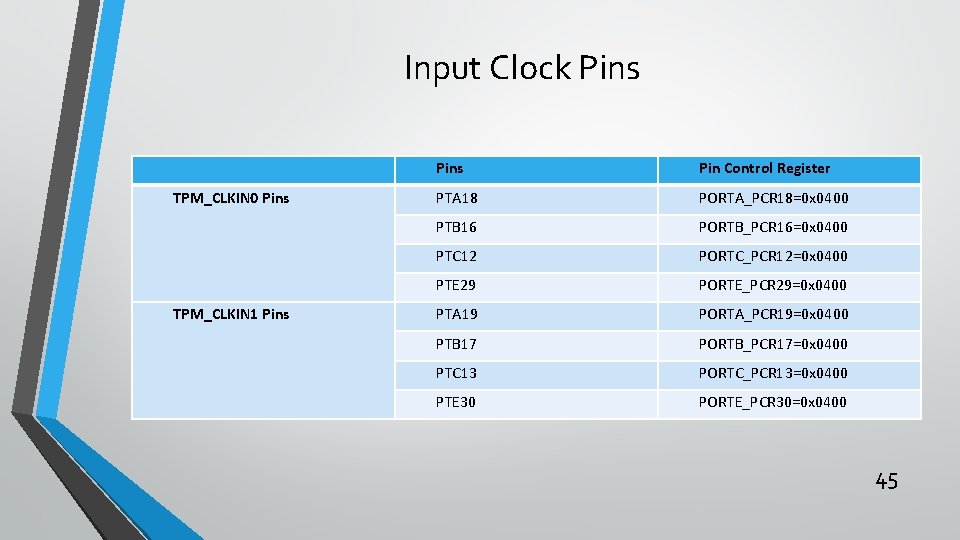

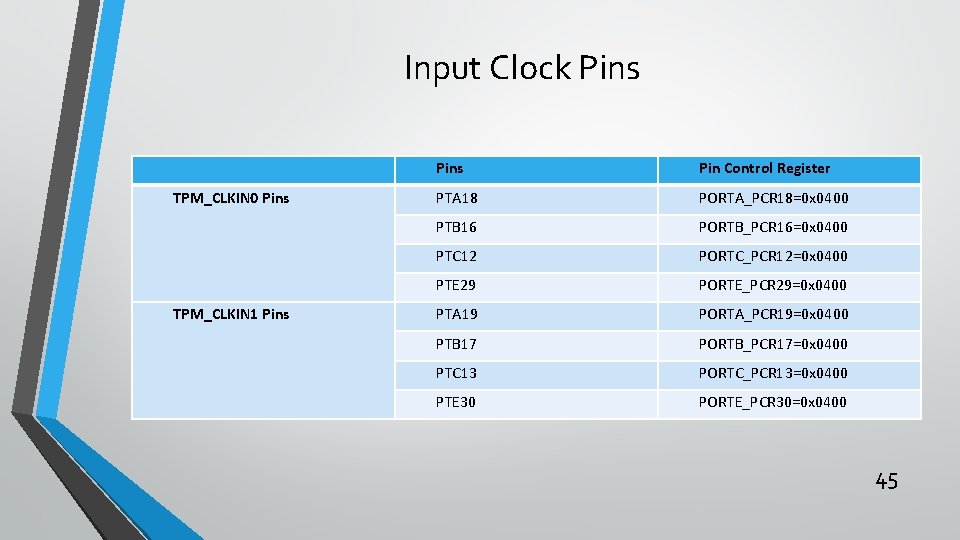

Input Clock Pins TPM_CLKIN 0 Pins TPM_CLKIN 1 Pins Pin Control Register PTA 18 PORTA_PCR 18=0 x 0400 PTB 16 PORTB_PCR 16=0 x 0400 PTC 12 PORTC_PCR 12=0 x 0400 PTE 29 PORTE_PCR 29=0 x 0400 PTA 19 PORTA_PCR 19=0 x 0400 PTB 17 PORTB_PCR 17=0 x 0400 PTC 13 PORTC_PCR 13=0 x 0400 PTE 30 PORTE_PCR 30=0 x 0400 45