Chapter 5 Boolean Algebra and Reduction Techniques 1

Chapter 5 Boolean Algebra and Reduction Techniques 1

Objectives n You should be able to: Write Boolean equations for combinational logic applications. n Use Boolean algebra laws and rules to simplify combinational logic circuits. n Apply De. Morgan’s theorem to complex Boolean equations to arrive at simplified equivalent equations. n 2

Objectives (Continued) Design single-gate logic circuits by using the universal capability of NAND and NOR gates. n Troubleshoot combinational logic circuits. n Implement sum-of-products expressions using AND-OR-INVERT gates. n 3

Objectives (Continued) Use the Karnaugh mapping procedure to systematically reduce complex Boolean equations to their simplest form. n Describe the steps involved in solving a complete system design application. n 4

Combinational Logic Using two or more logic gates to perform a more useful, complex function n A combination of logic functions n B = KD + HD n Boolean Reduction B = D(K+H) 5

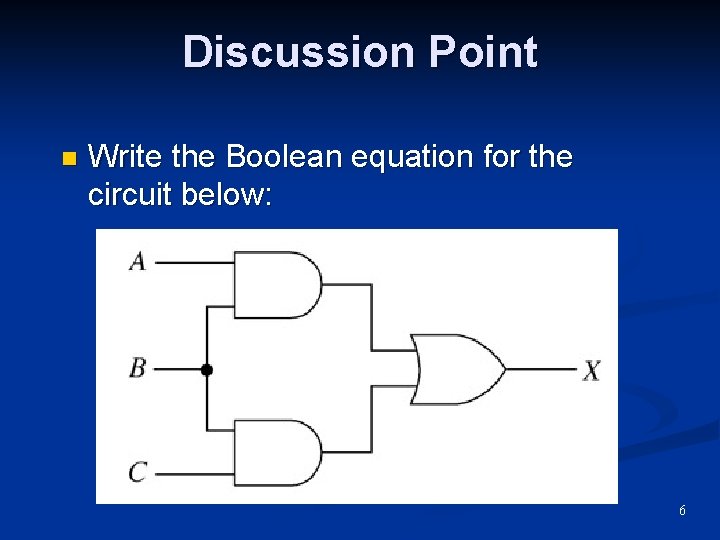

Discussion Point n Write the Boolean equation for the circuit below: 6

VHDL Proof A circuit reduction can easily be proved using VHDL n Write a program for each equation n Run a simulation for all possible input conditions n Compare the results n

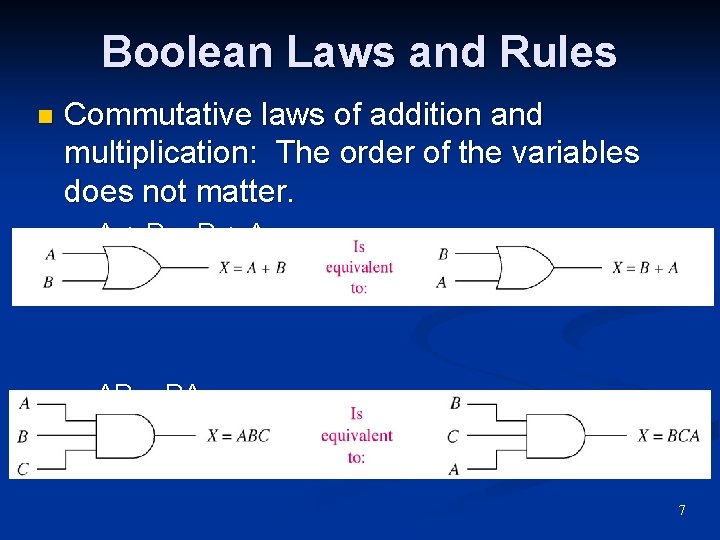

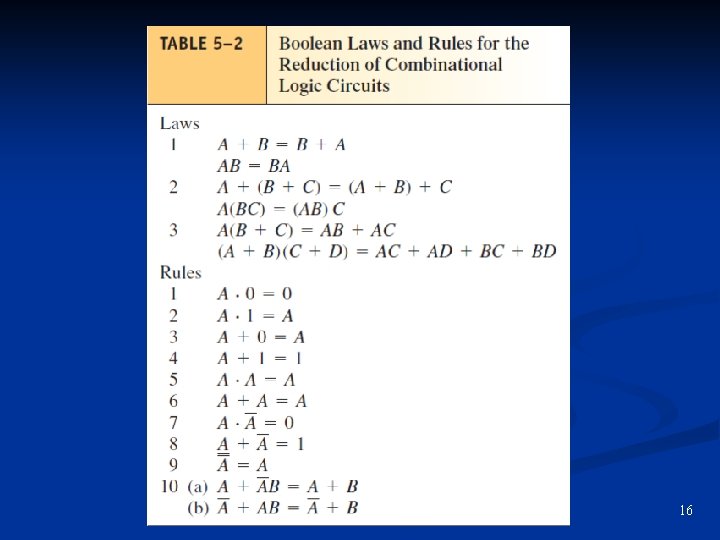

Boolean Laws and Rules n Commutative laws of addition and multiplication: The order of the variables does not matter. n A+B=B+A n AB = BA 7

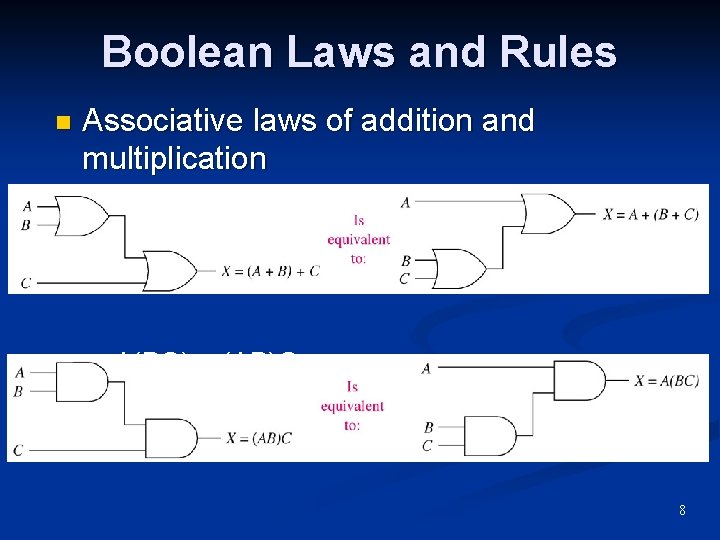

Boolean Laws and Rules n Associative laws of addition and multiplication n A + (B + C) = (A + B) + C n A(BC) = (AB)C 8

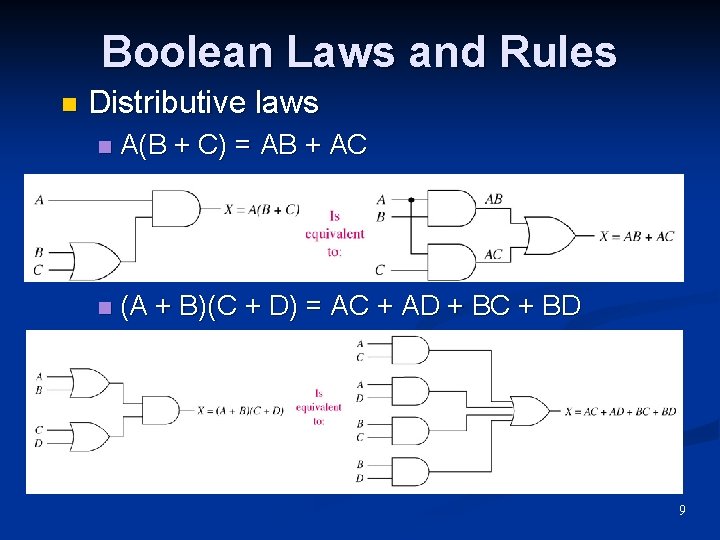

Boolean Laws and Rules n Distributive laws n A(B + C) = AB + AC n (A + B)(C + D) = AC + AD + BC + BD 9

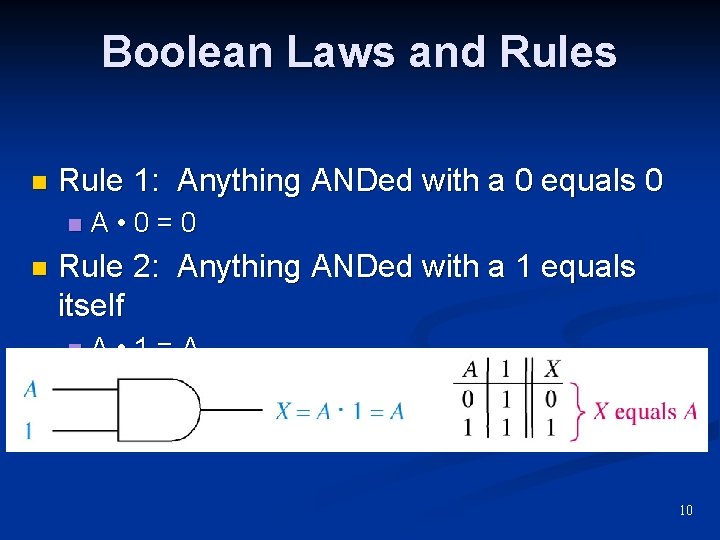

Boolean Laws and Rules n Rule 1: Anything ANDed with a 0 equals 0 n n A • 0=0 Rule 2: Anything ANDed with a 1 equals itself n A • 1=A 10

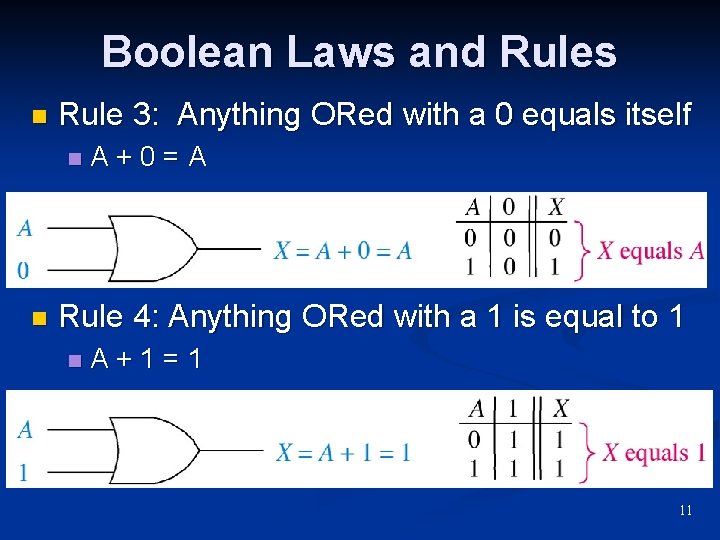

Boolean Laws and Rules n Rule 3: Anything ORed with a 0 equals itself n n A+0=A Rule 4: Anything ORed with a 1 is equal to 1 n A+1=1 11

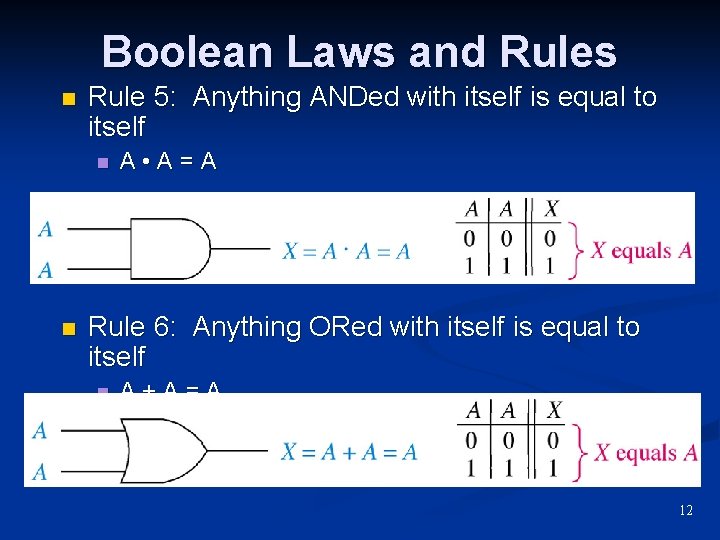

Boolean Laws and Rules n Rule 5: Anything ANDed with itself is equal to itself n n A • A=A Rule 6: Anything ORed with itself is equal to itself n A+A=A 12

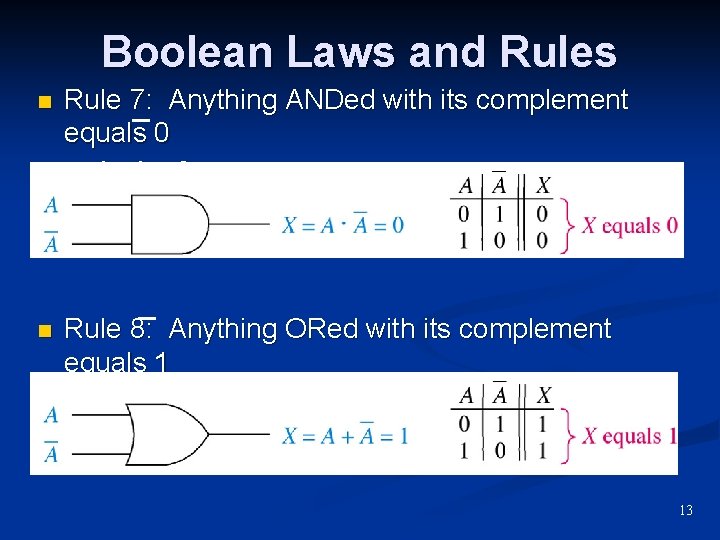

Boolean Laws and Rules n Rule 7: Anything ANDed with its complement equals 0 n n A • A=0 Rule 8: Anything ORed with its complement equals 1 n A+A=1 13

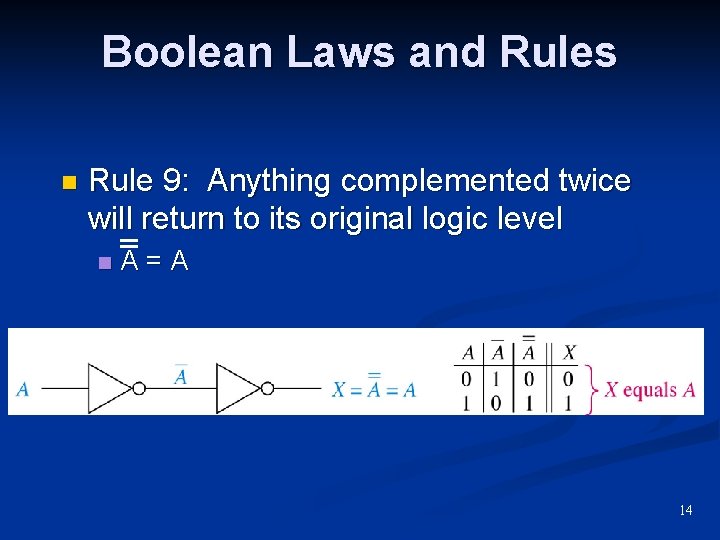

Boolean Laws and Rules n Rule 9: Anything complemented twice will return to its original logic level n A=A 14

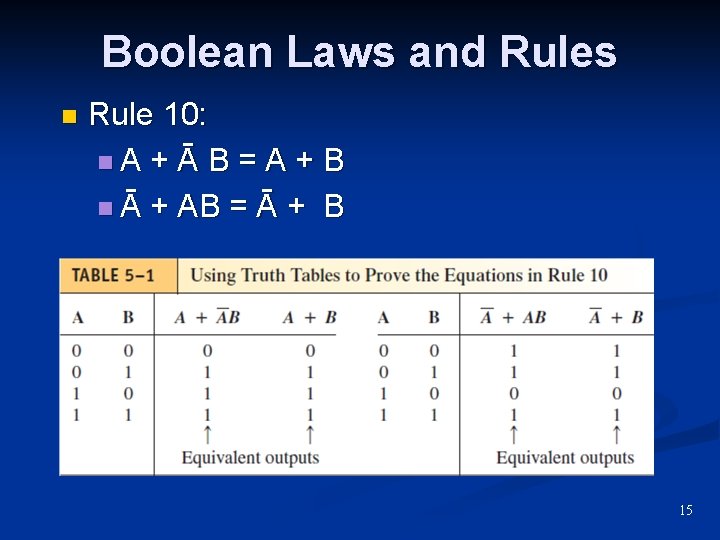

Boolean Laws and Rules n Rule 10: n. A + Ā B = A + B n Ā + AB = Ā + B 15

16

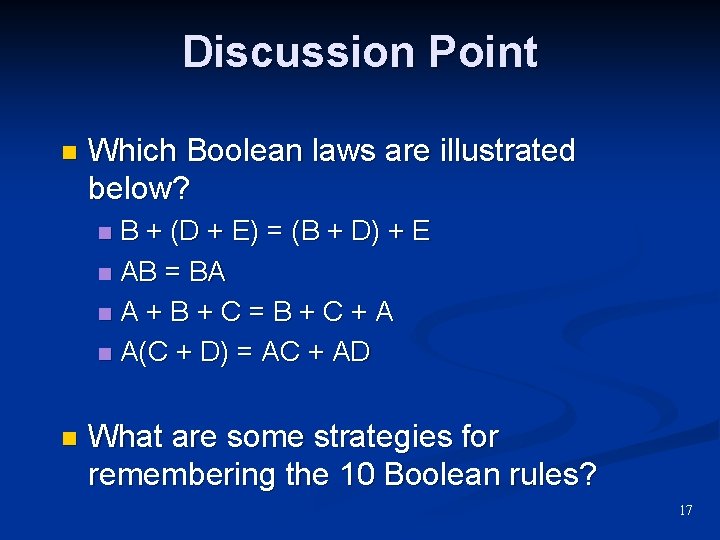

Discussion Point n Which Boolean laws are illustrated below? B + (D + E) = (B + D) + E n AB = BA n. A+B+C=B+C+A n A(C + D) = AC + AD n n What are some strategies for remembering the 10 Boolean rules? 17

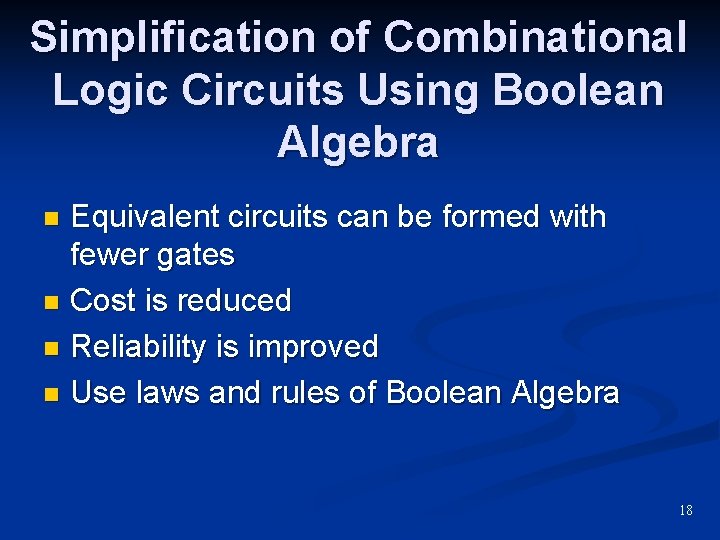

Simplification of Combinational Logic Circuits Using Boolean Algebra Equivalent circuits can be formed with fewer gates n Cost is reduced n Reliability is improved n Use laws and rules of Boolean Algebra n 18

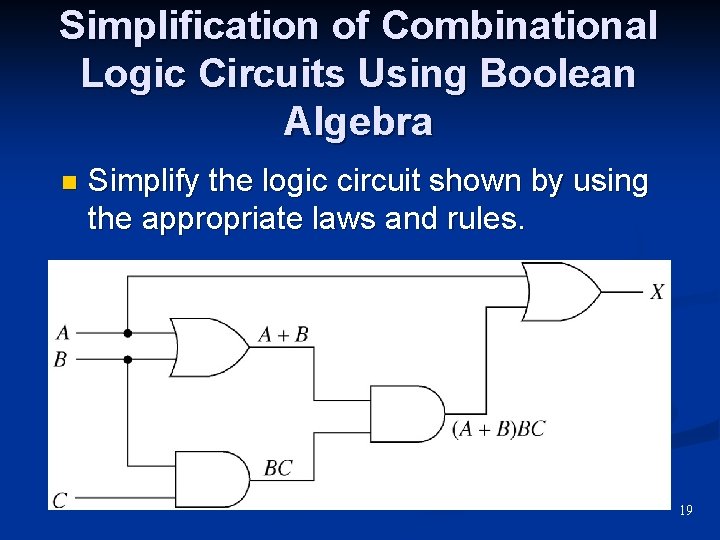

Simplification of Combinational Logic Circuits Using Boolean Algebra n Simplify the logic circuit shown by using the appropriate laws and rules. 19

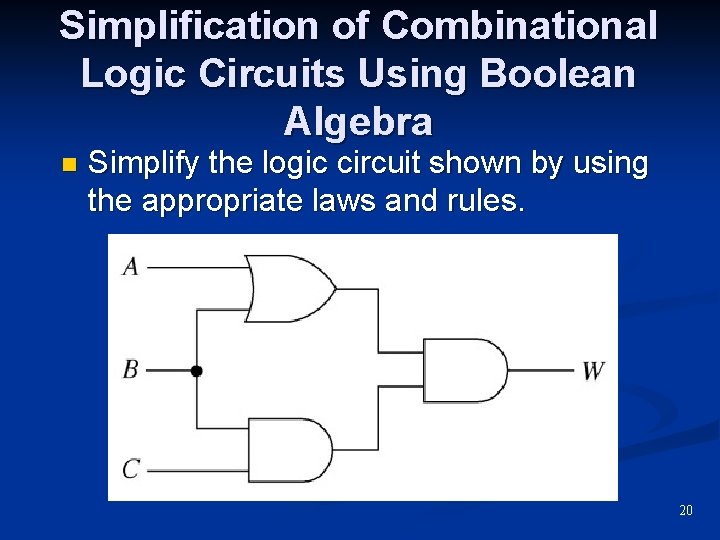

Simplification of Combinational Logic Circuits Using Boolean Algebra n Simplify the logic circuit shown by using the appropriate laws and rules. 20

Using Quartus II to Simplify Equations n Quartus II software determines the simplest form of an equation during compiling. n It eliminates unnecessary gates n Minimizes the number of gates in the FPGA

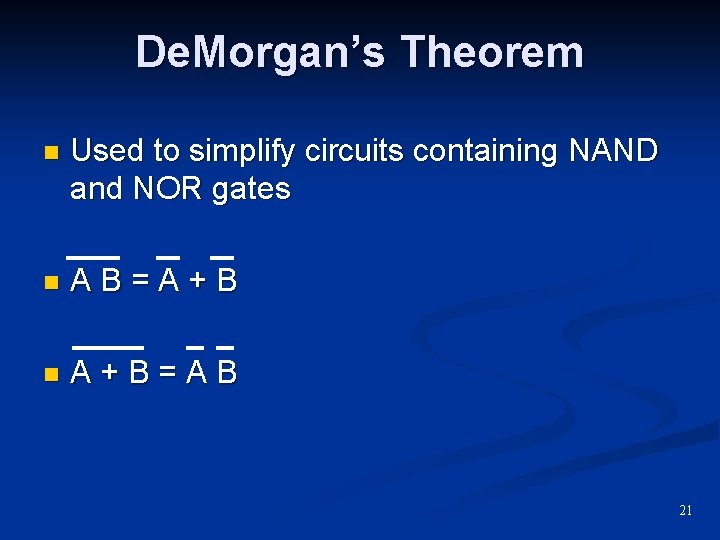

De. Morgan’s Theorem n Used to simplify circuits containing NAND and NOR gates n AB=A+B n A+B=AB 21

De. Morgan’s Theorem Break the bar over the variables and change the sign between them n Inversion bubbles - used instead of inverters to show inversion. n Use parentheses to maintain proper groupings n Results in Sum-of-Products (SOP) form n 22

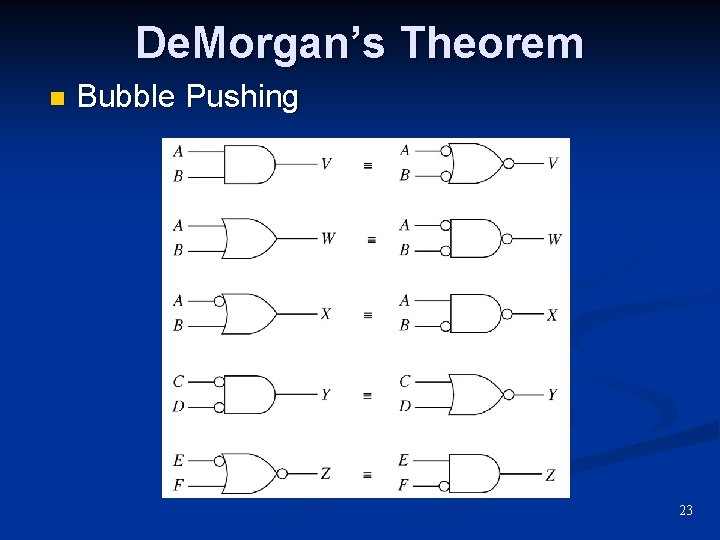

De. Morgan’s Theorem n Bubble Pushing 23

De. Morgan’s Theorem n Bubble Pushing n Change the logic gate n (AND n to OR or OR to AND) Add bubbles to the inputs and outputs where there were none and remove original bubbles 24

Truth Tables in VHDL using Vector Signals n Define inputs as an internal signal n Inputs are grouped as vectors n Assign values to the elements of the vector n Assign outputs for each input combination

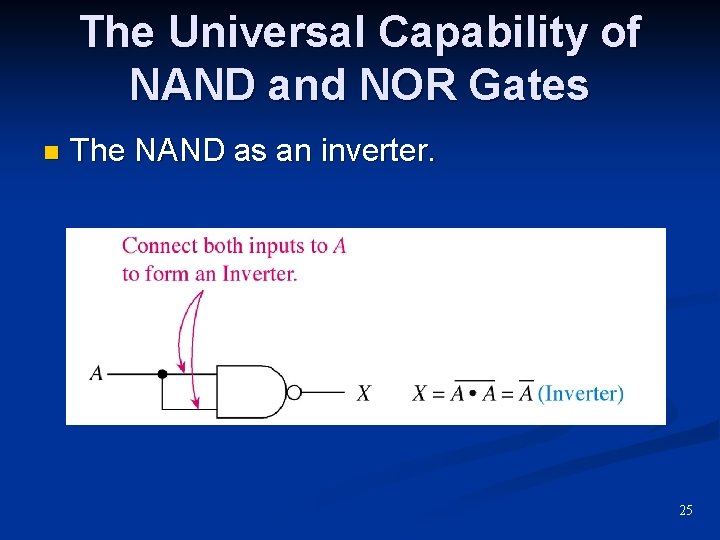

The Universal Capability of NAND and NOR Gates n The NAND as an inverter. 25

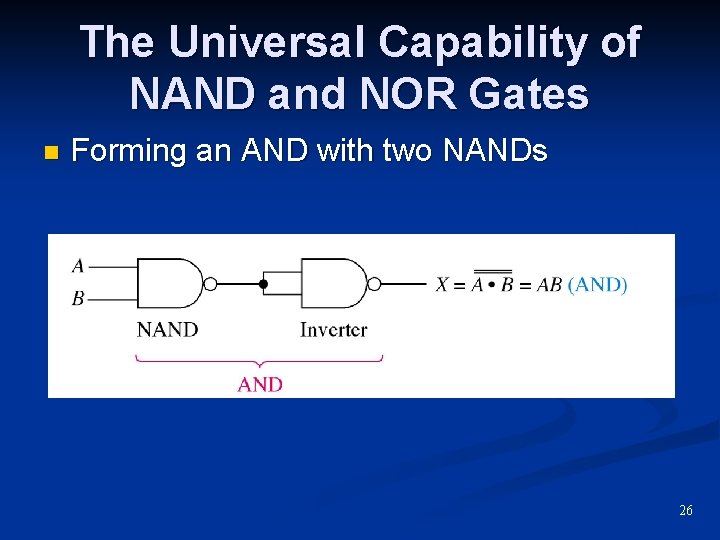

The Universal Capability of NAND and NOR Gates n Forming an AND with two NANDs 26

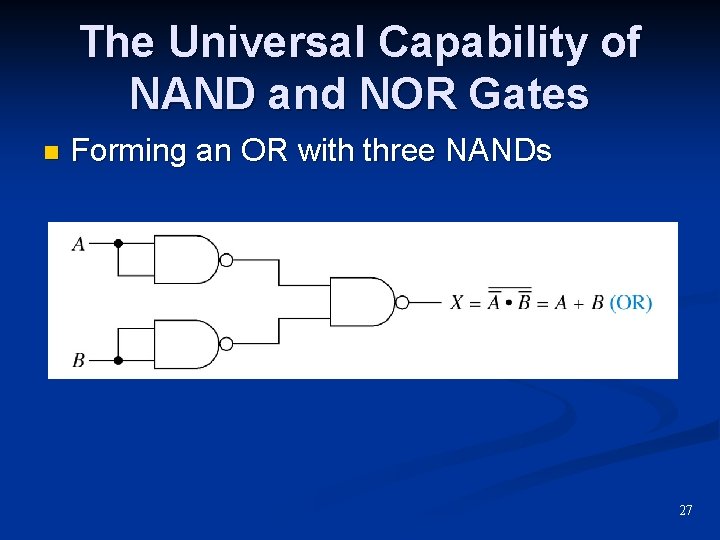

The Universal Capability of NAND and NOR Gates n Forming an OR with three NANDs 27

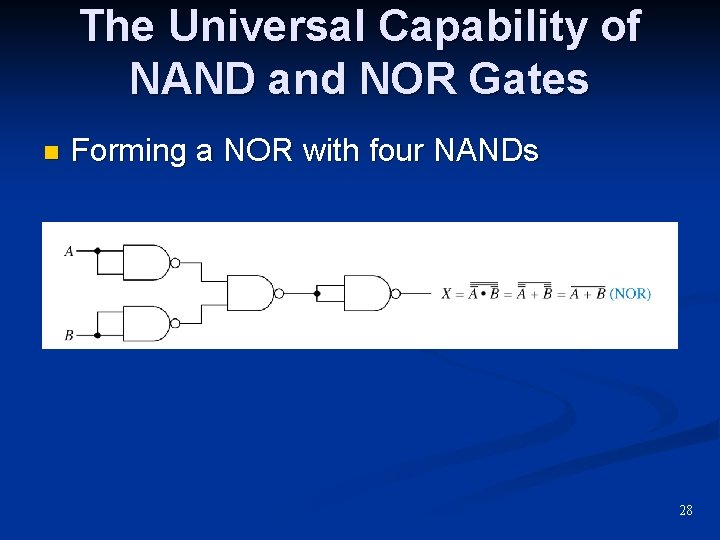

The Universal Capability of NAND and NOR Gates n Forming a NOR with four NANDs 28

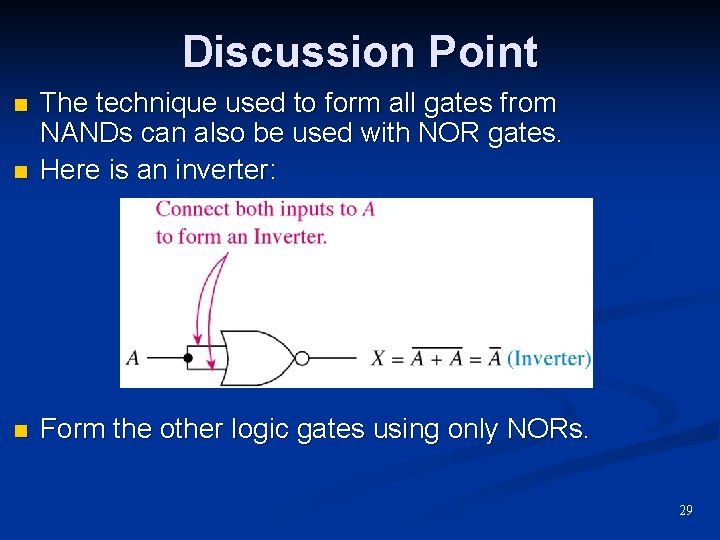

Discussion Point n The technique used to form all gates from NANDs can also be used with NOR gates. Here is an inverter: n Form the other logic gates using only NORs. n 29

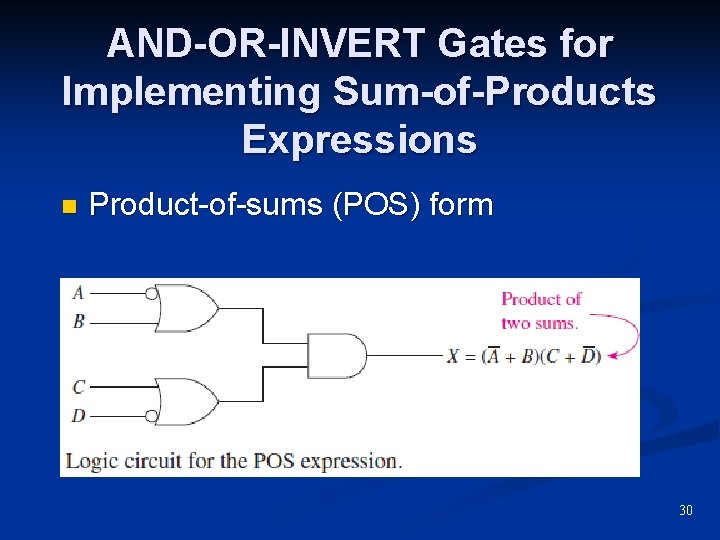

AND-OR-INVERT Gates for Implementing Sum-of-Products Expressions n Product-of-sums (POS) form 30

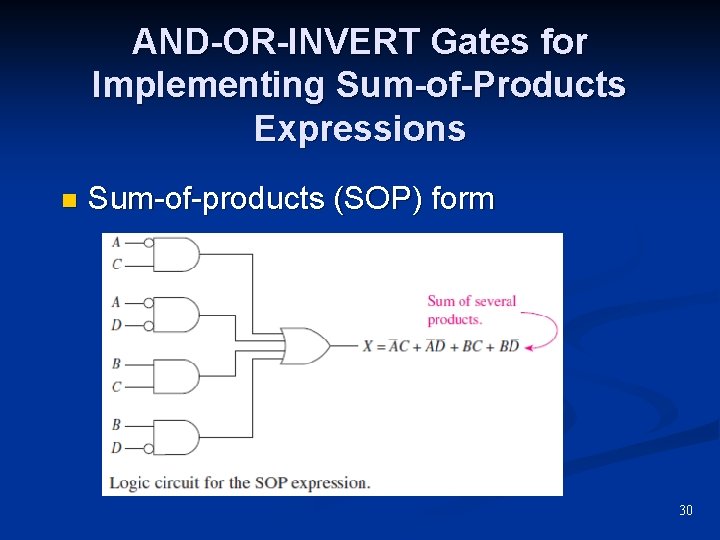

AND-OR-INVERT Gates for Implementing Sum-of-Products Expressions n Sum-of-products (SOP) form 30

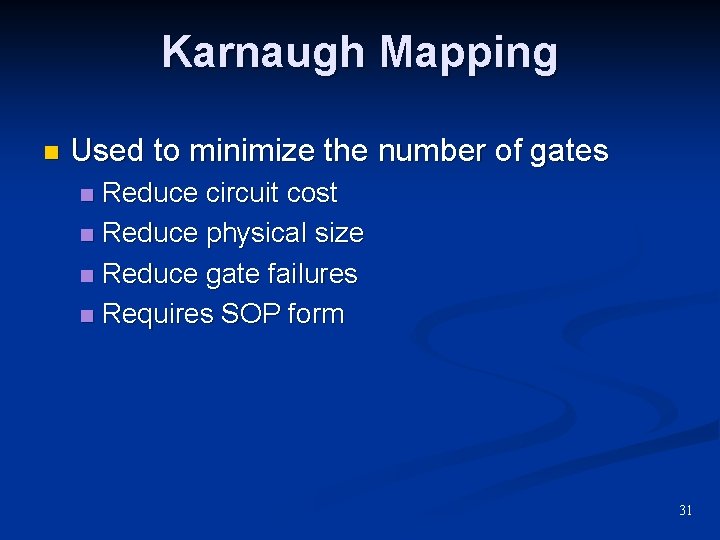

Karnaugh Mapping n Used to minimize the number of gates Reduce circuit cost n Reduce physical size n Reduce gate failures n Requires SOP form n 31

Karnaugh Mapping Graphically shows output level for all possible input combinations n Moving from one cell to an adjacent cell, only one variable changes n 32

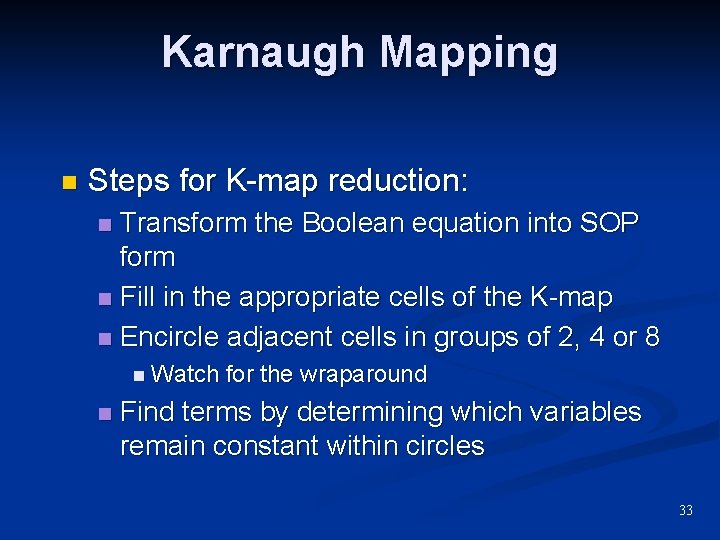

Karnaugh Mapping n Steps for K-map reduction: Transform the Boolean equation into SOP form n Fill in the appropriate cells of the K-map n Encircle adjacent cells in groups of 2, 4 or 8 n n Watch n for the wraparound Find terms by determining which variables remain constant within circles 33

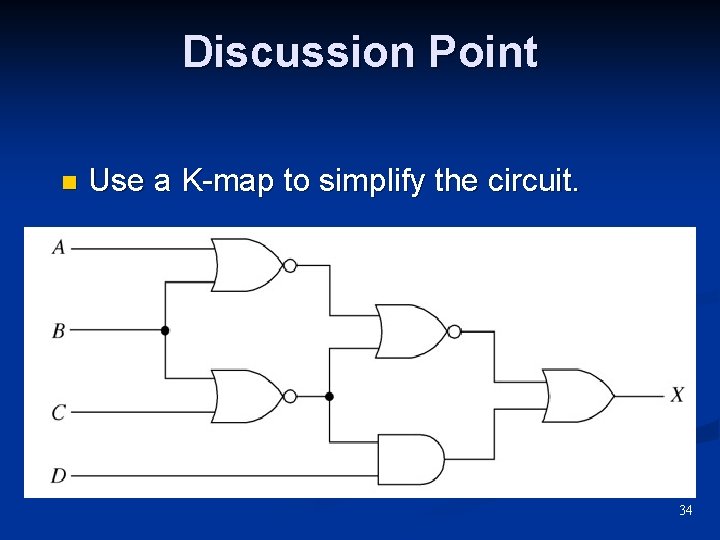

Discussion Point n Use a K-map to simplify the circuit. 34

System Design Applications Use Karnaugh Mapping to reduce equations n Use AND-OR-INVERT gates to implement logic n 35

System Design Applications Use K-maps to simplify less complex circuits before implementing the circuit using an AOI. n More complex circuits are better suited for implementation using PLDs. n 36

Summary Several logic gates can be connected together to form combinational logic. n There are several Boolean laws and rules that provide the means to form equivalent circuits. n Boolean algebra is used to reduce logic circuits to simpler equivalent circuits that function identically to the original circuit. n 41

Summary De. Morgan’s theorem is required in the reduction process whenever inversion bars cover more than one variable in the original Boolean equation. n NAND and NOR gates are sometimes referred to as universal gates, because they can be used to form any of the other gates. n 42

Summary AND-OR-INVERT (AOI) gates are often used to implement sum-of-products (SOP) equations. n Karnaugh mapping provides a systematic method of reducing logic circuits. n Combinational logic designs can be entered into a computer using schematic block design software or VHDL. n 43

Summary Using vectors in VHDL is a convenient way to group like signals together similar to an array. n Truth tables can be implemented in VHDL using vector signals with the selected signal assignment statement. n Quartus II can be used to determine the simplified equation of combinational circuits. n 43

- Slides: 44