Chapter 5 2 23 09 1 Read pages

- Slides: 58

Chapter 5 2 -23 -09 1

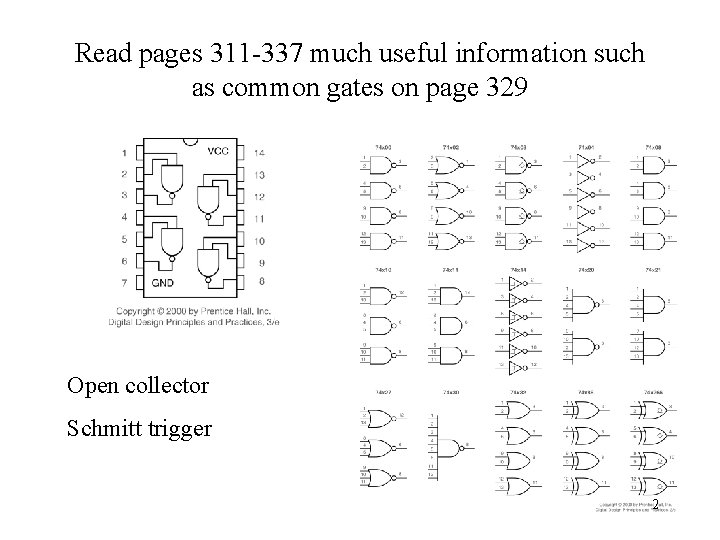

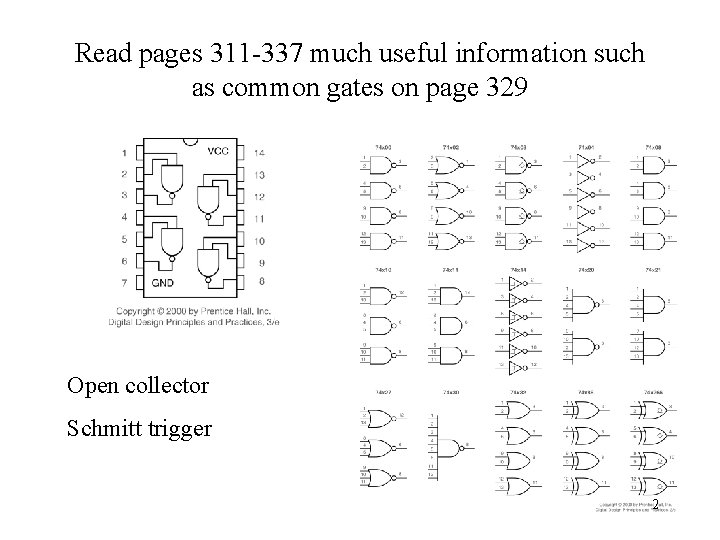

Read pages 311 -337 much useful information such as common gates on page 329 Open collector Schmitt trigger 2

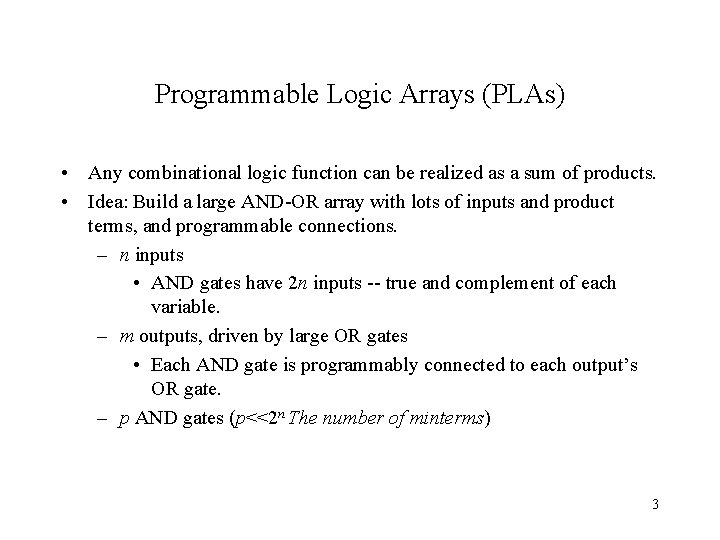

Programmable Logic Arrays (PLAs) • Any combinational logic function can be realized as a sum of products. • Idea: Build a large AND-OR array with lots of inputs and product terms, and programmable connections. – n inputs • AND gates have 2 n inputs -- true and complement of each variable. – m outputs, driven by large OR gates • Each AND gate is programmably connected to each output’s OR gate. – p AND gates (p<<2 n The number of minterms) 3

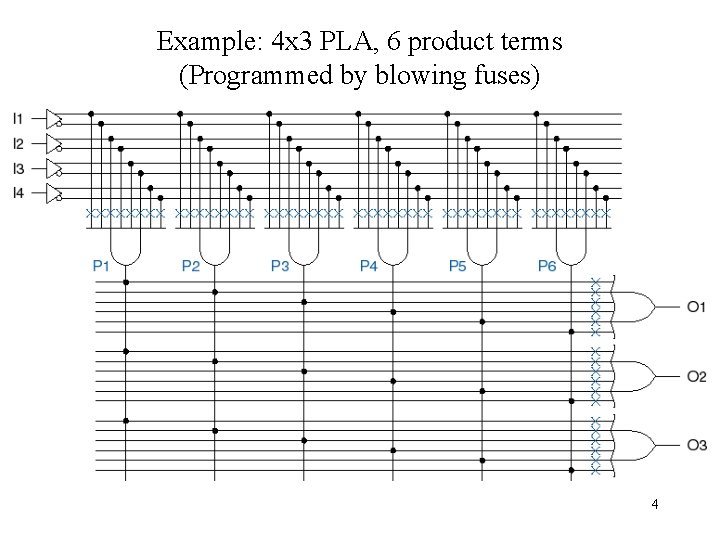

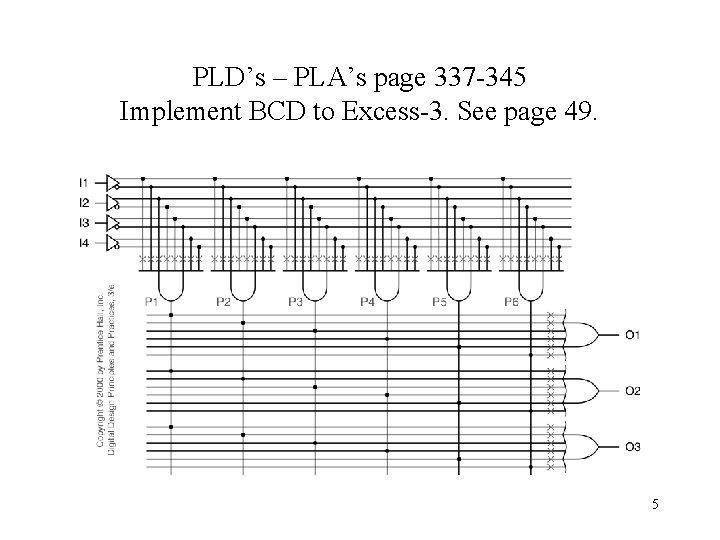

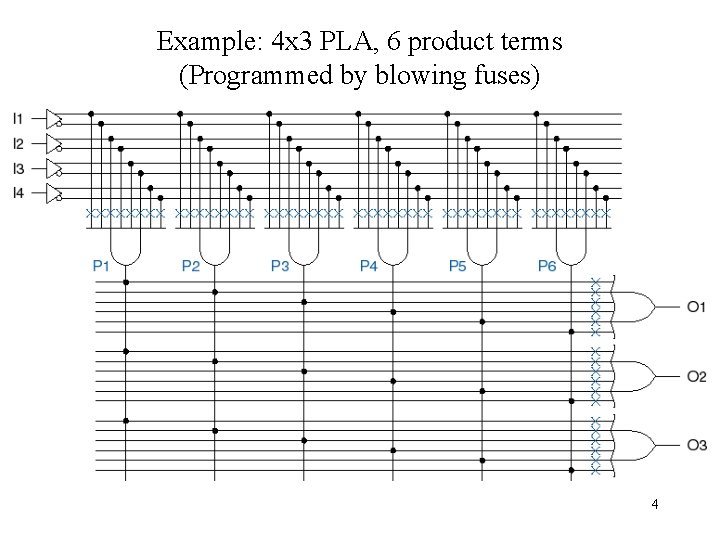

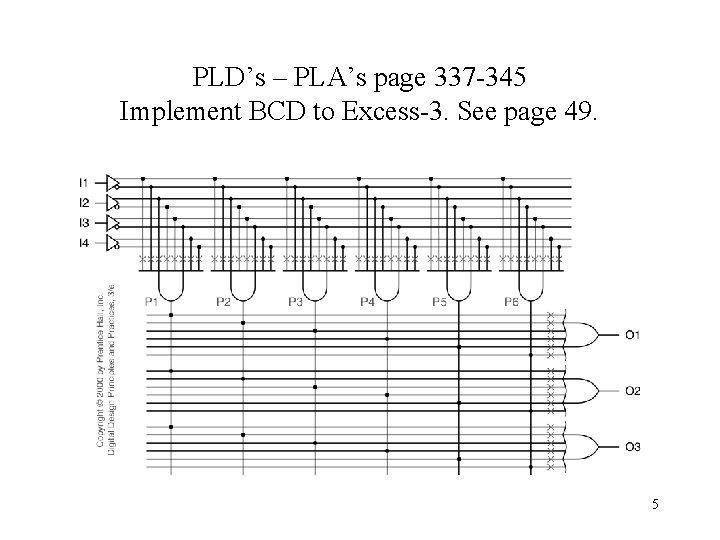

Example: 4 x 3 PLA, 6 product terms (Programmed by blowing fuses) 4

PLD’s – PLA’s page 337 -345 Implement BCD to Excess-3. See page 49. 5

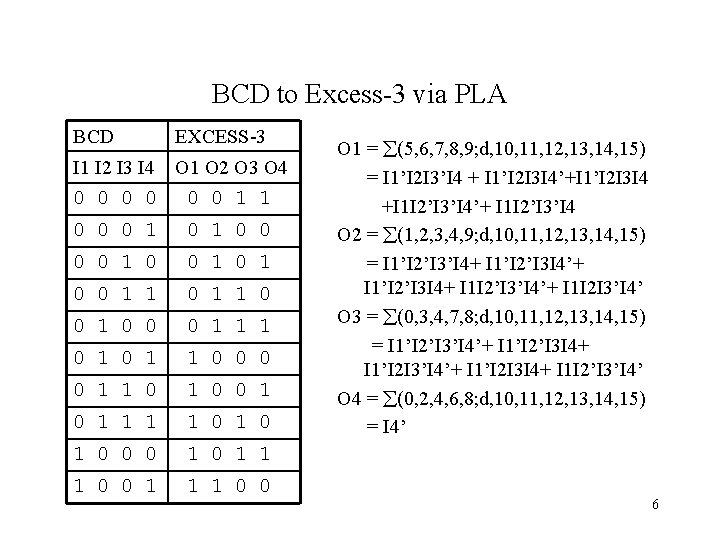

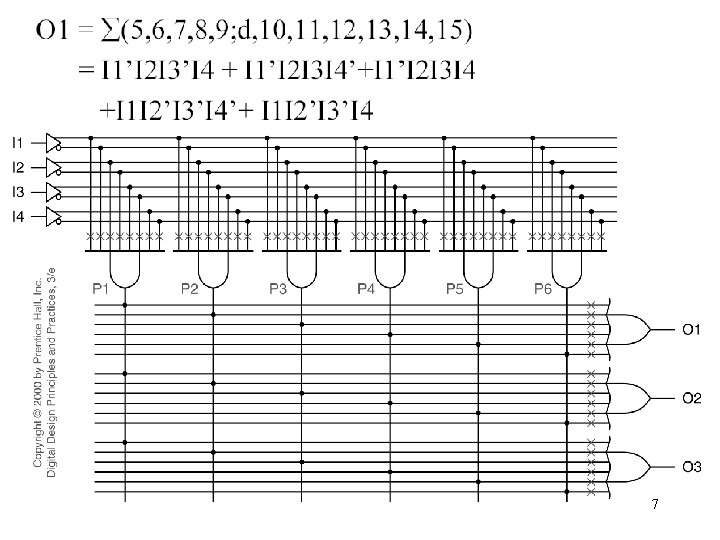

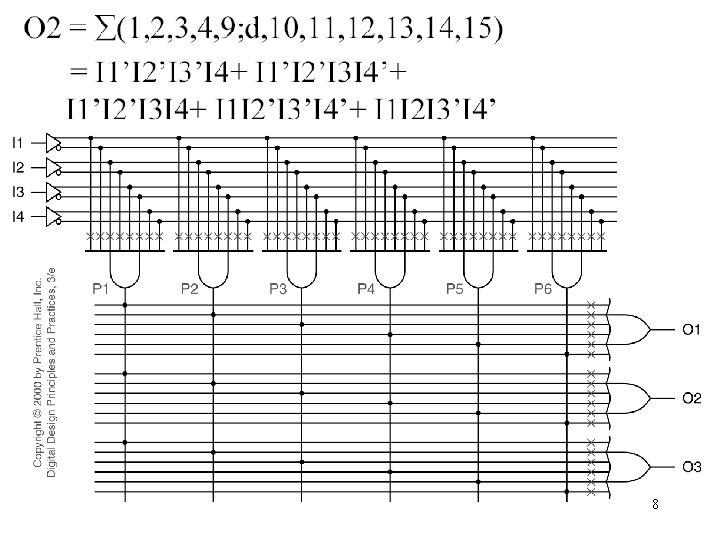

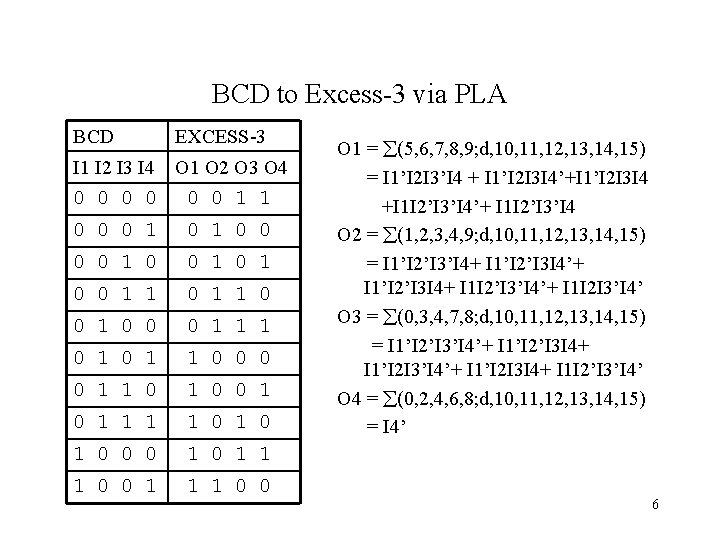

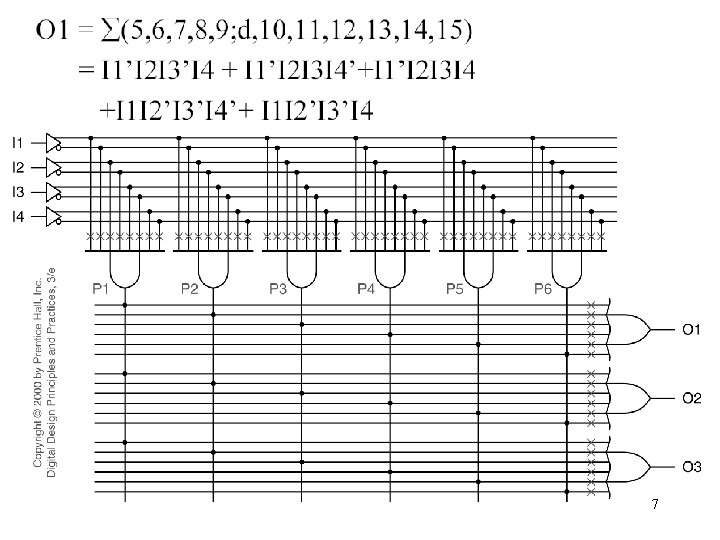

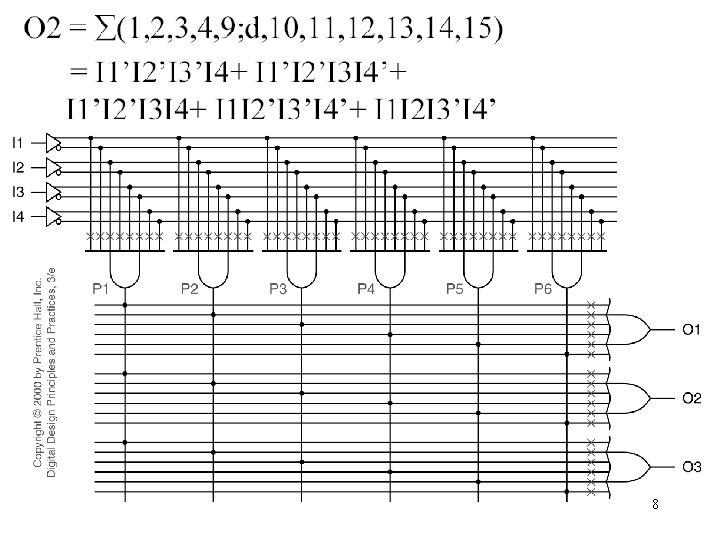

BCD to Excess-3 via PLA BCD EXCESS-3 I 1 I 2 I 3 I 4 O 1 O 2 O 3 O 4 0 0 0 1 1 0 0 0 1 0 0 1 1 0 0 0 1 1 1 0 0 1 1 0 0 1 1 1 1 0 1 0 0 0 1 1 1 0 0 O 1 = (5, 6, 7, 8, 9; d, 10, 11, 12, 13, 14, 15) = I 1’I 2 I 3’I 4 + I 1’I 2 I 3 I 4’+I 1’I 2 I 3 I 4 +I 1 I 2’I 3’I 4’+ I 1 I 2’I 3’I 4 O 2 = (1, 2, 3, 4, 9; d, 10, 11, 12, 13, 14, 15) = I 1’I 2’I 3’I 4+ I 1’I 2’I 3 I 4’+ I 1’I 2’I 3 I 4+ I 1 I 2’I 3’I 4’+ I 1 I 2 I 3’I 4’ O 3 = (0, 3, 4, 7, 8; d, 10, 11, 12, 13, 14, 15) = I 1’I 2’I 3’I 4’+ I 1’I 2’I 3 I 4+ I 1’I 2 I 3’I 4’+ I 1’I 2 I 3 I 4+ I 1 I 2’I 3’I 4’ O 4 = (0, 2, 4, 6, 8; d, 10, 11, 12, 13, 14, 15) = I 4’ 6

7

8

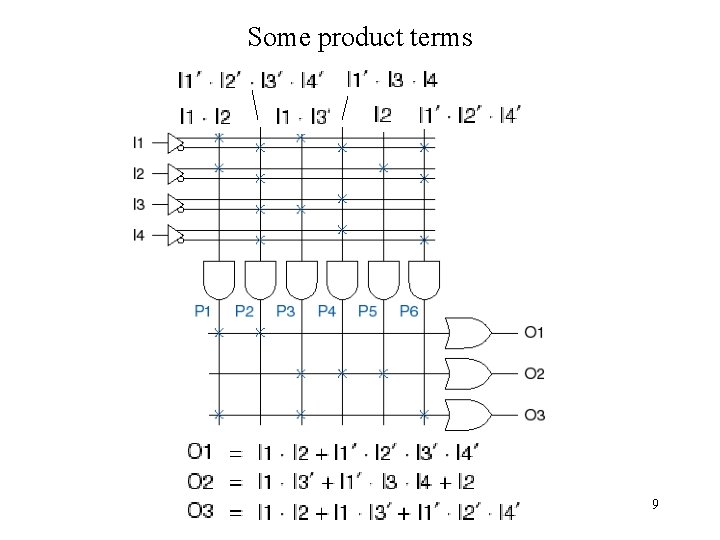

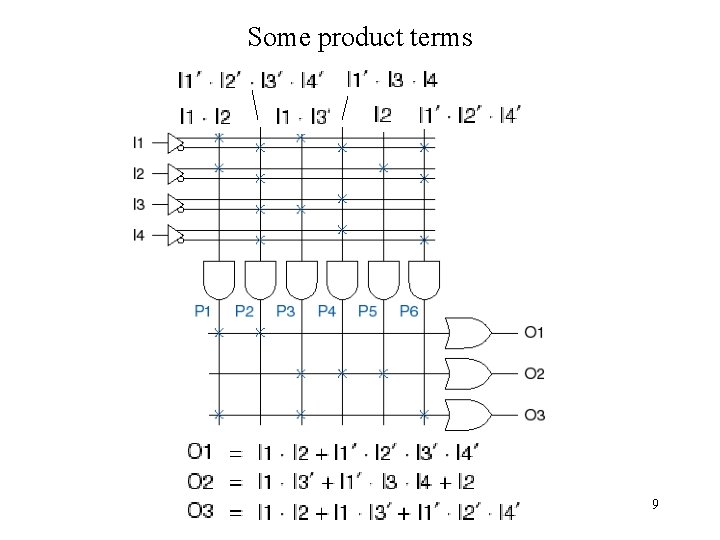

Some product terms 9

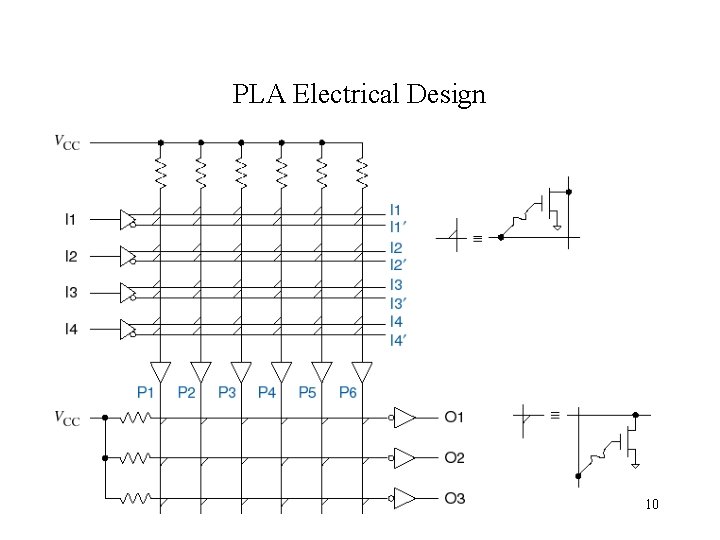

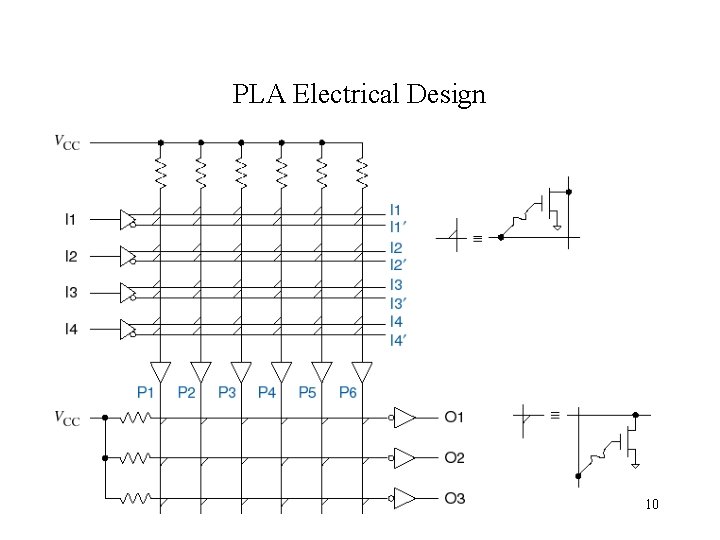

PLA Electrical Design • See Section 5. 3. 5 -- wired-AND logic 10

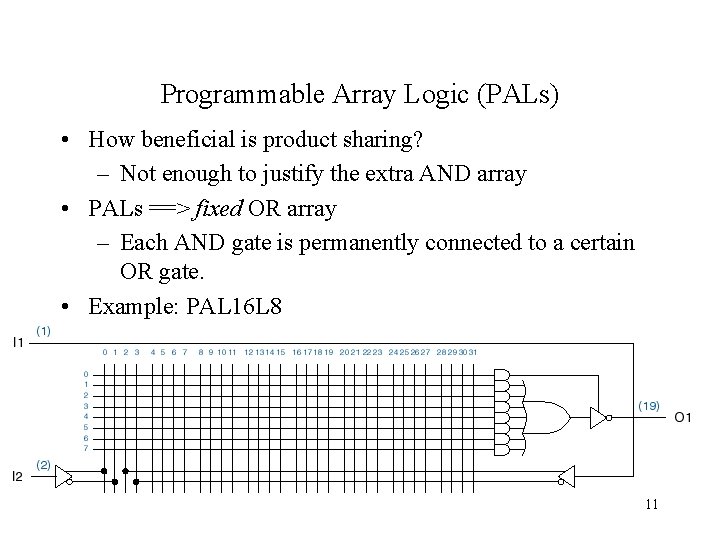

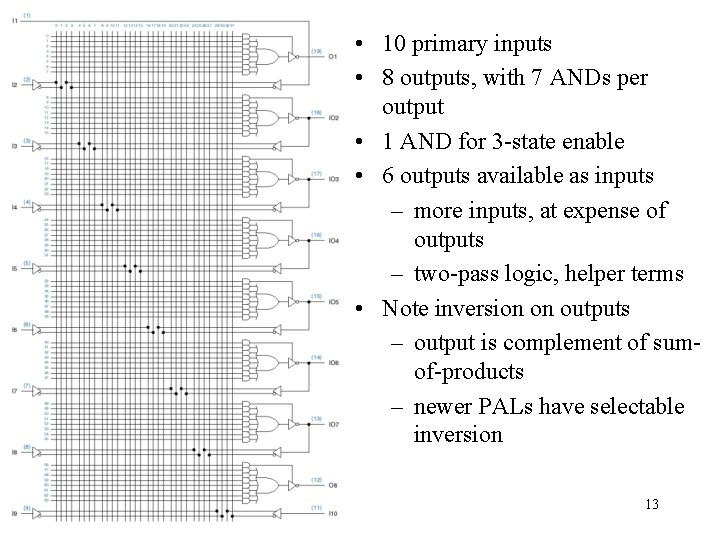

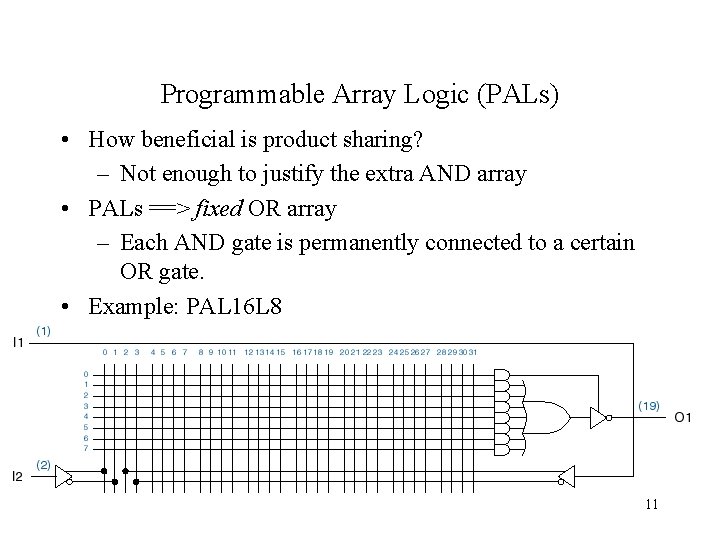

Programmable Array Logic (PALs) • How beneficial is product sharing? – Not enough to justify the extra AND array • PALs ==> fixed OR array – Each AND gate is permanently connected to a certain OR gate. • Example: PAL 16 L 8 11

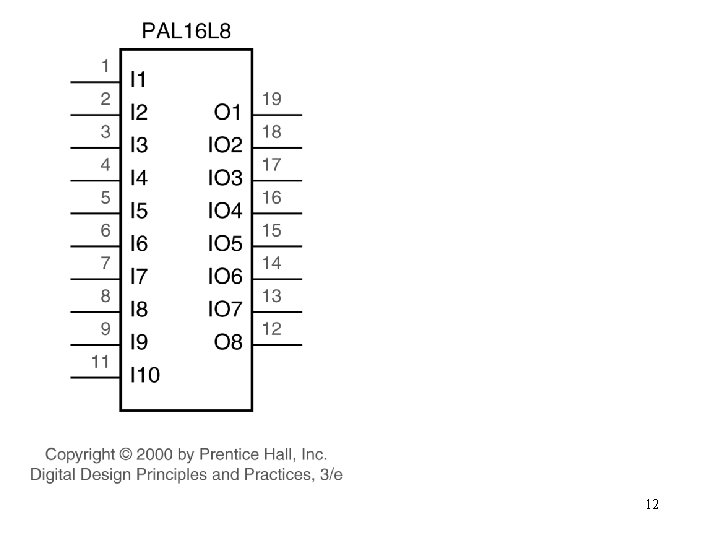

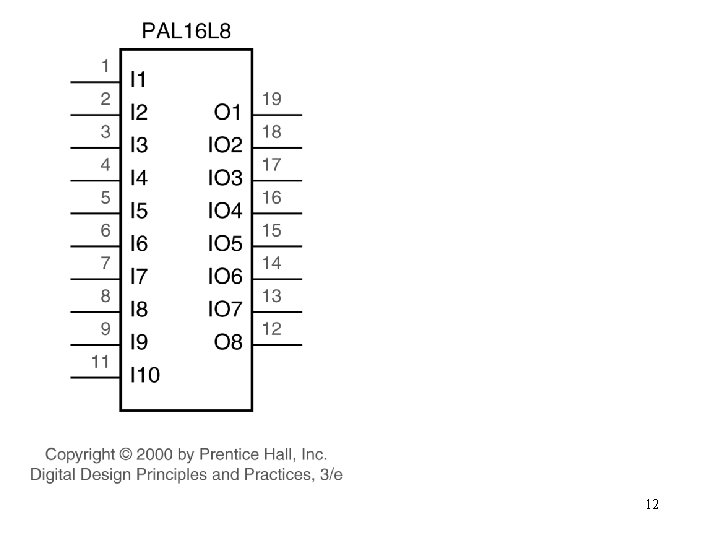

12

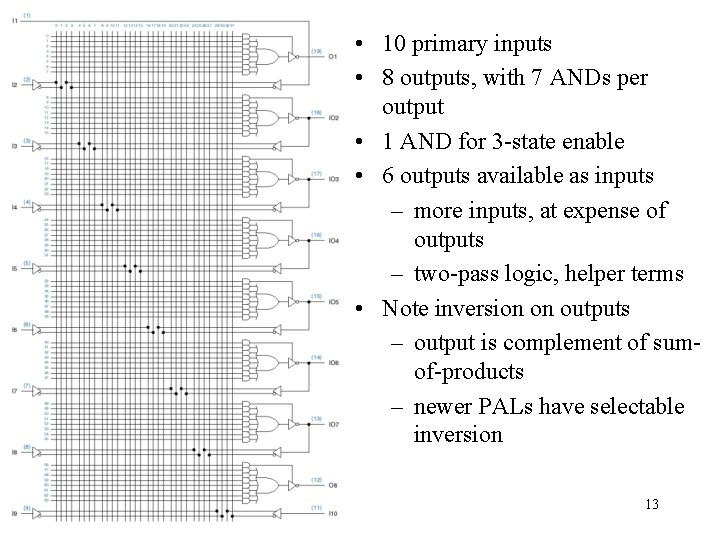

• 10 primary inputs • 8 outputs, with 7 ANDs per output • 1 AND for 3 -state enable • 6 outputs available as inputs – more inputs, at expense of outputs – two-pass logic, helper terms • Note inversion on outputs – output is complement of sumof-products – newer PALs have selectable inversion 13

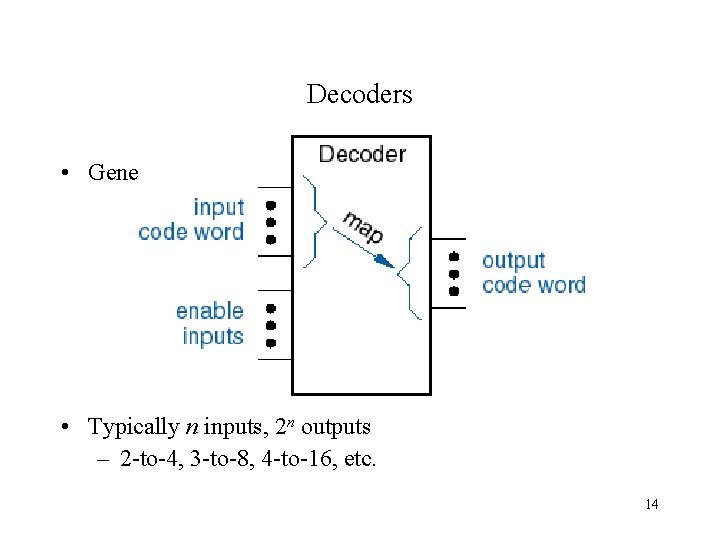

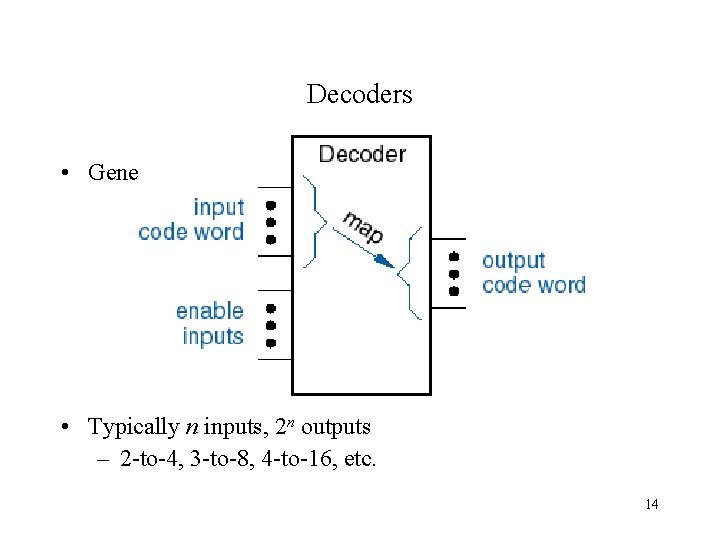

Decoders • General decoder structure • Typically n inputs, 2 n outputs – 2 -to-4, 3 -to-8, 4 -to-16, etc. 14

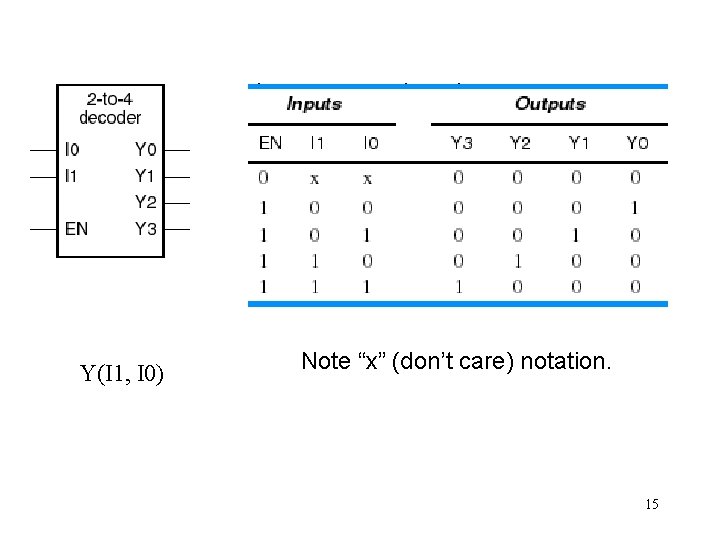

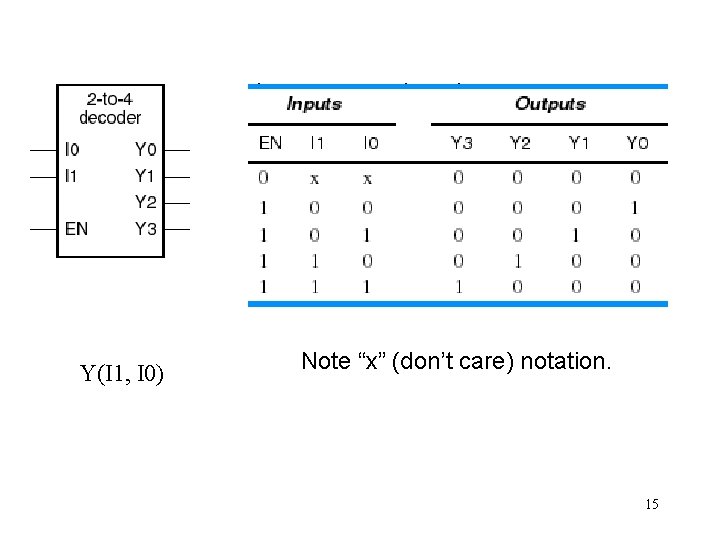

Binary 2 -to-4 decoder Y(I 1, I 0) Note “x” (don’t care) notation. 15

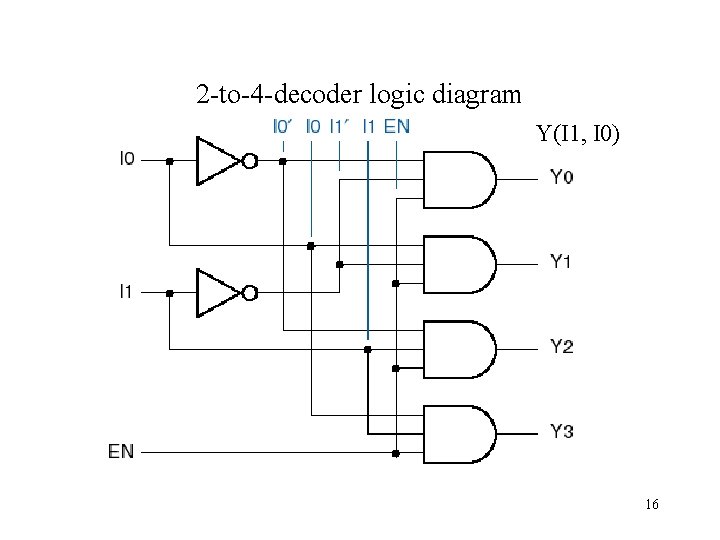

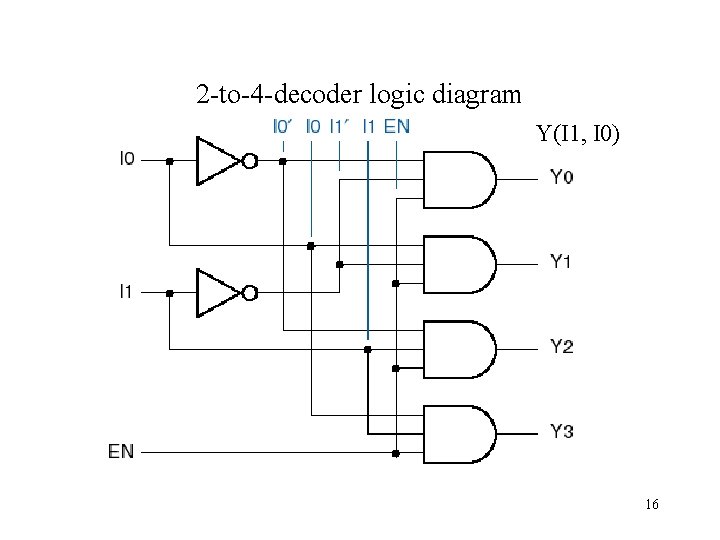

2 -to-4 -decoder logic diagram Y(I 1, I 0) 16

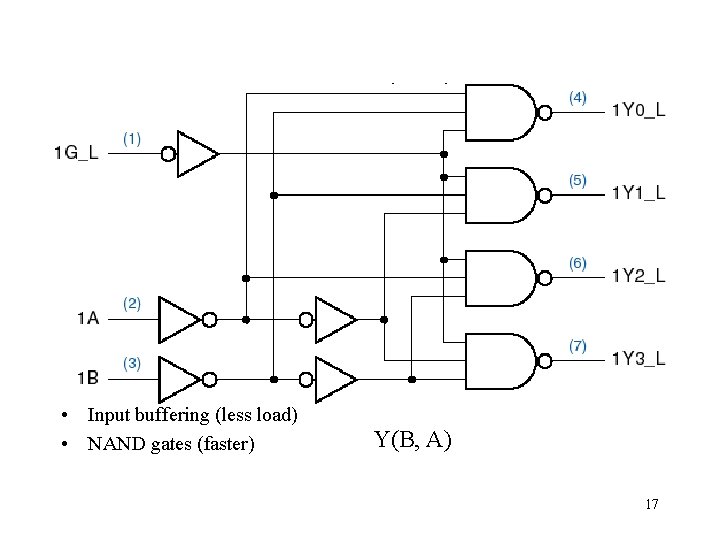

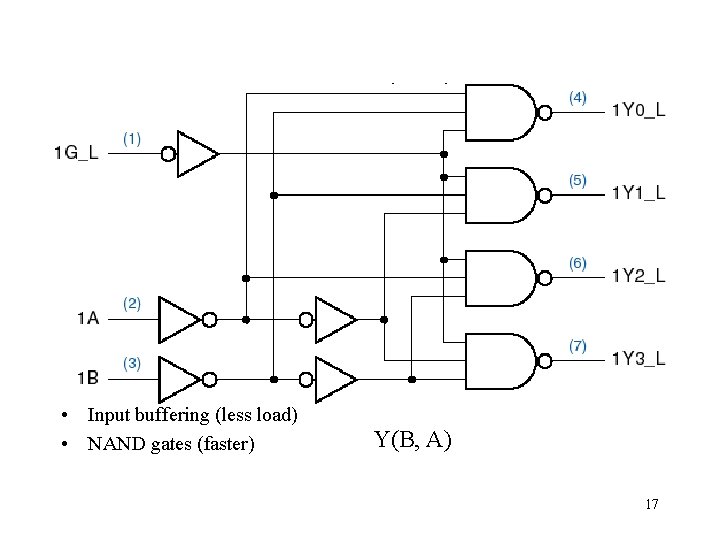

MSI 2 -to-4 decoder • Input buffering (less load) • NAND gates (faster) Y(B, A) 17

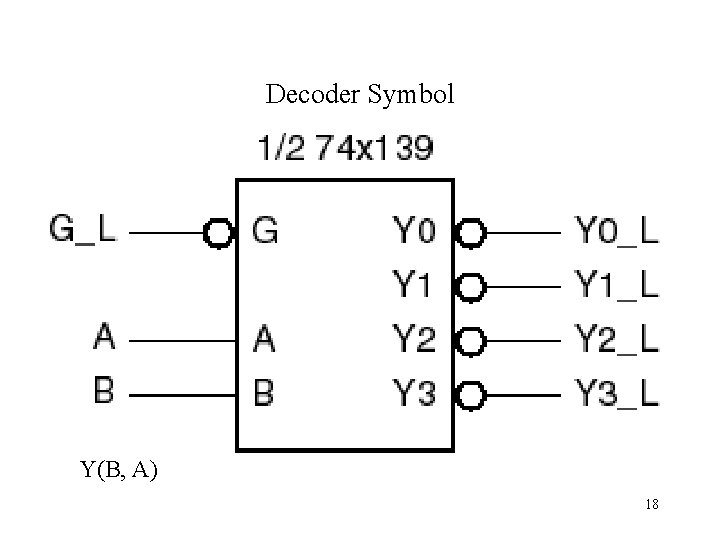

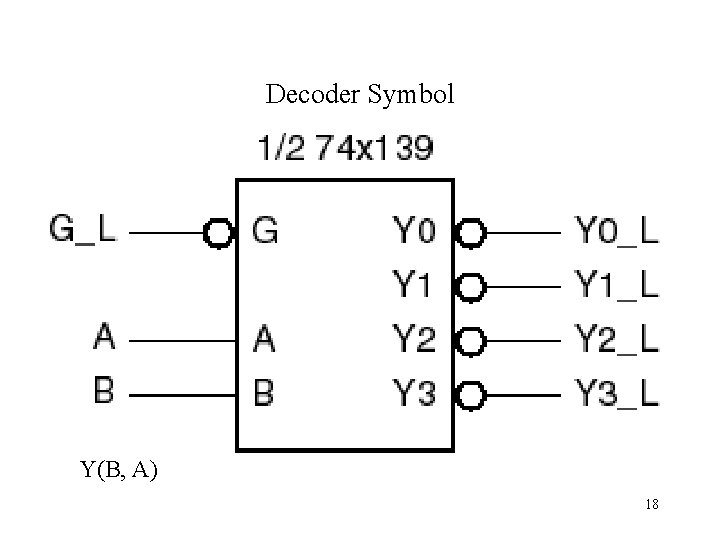

Decoder Symbol Y(B, A) 18

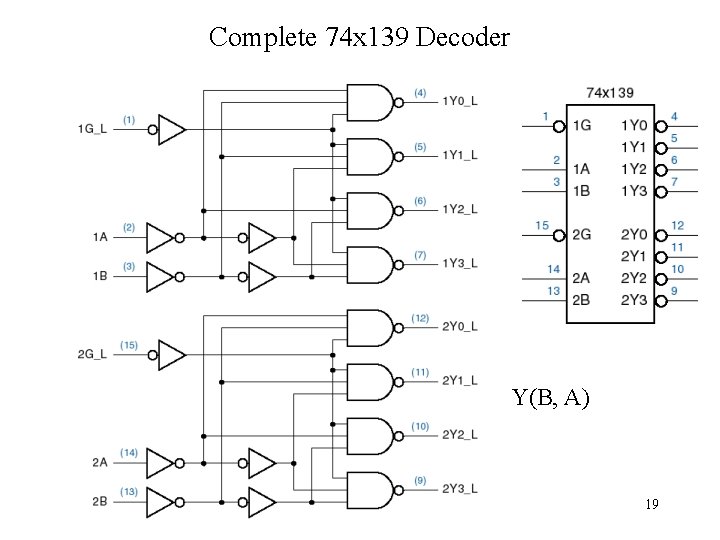

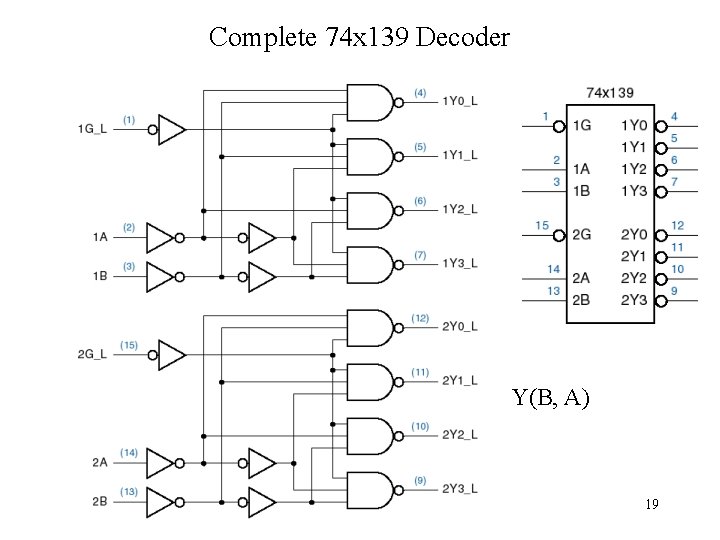

Complete 74 x 139 Decoder Y(B, A) 19

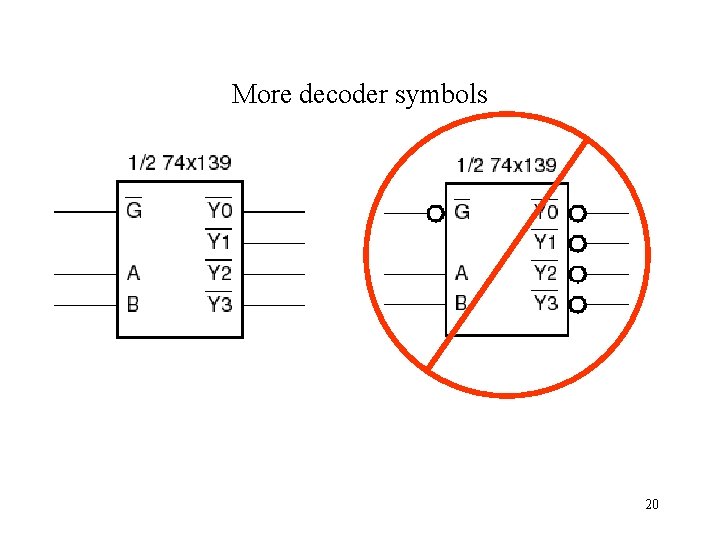

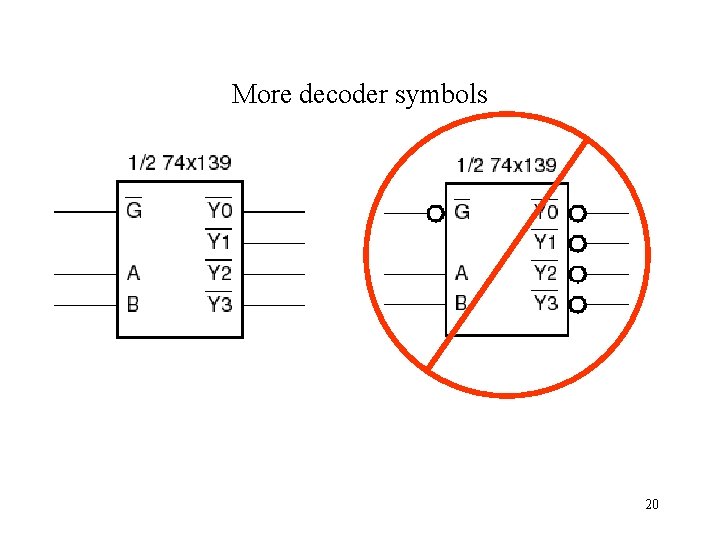

More decoder symbols 20

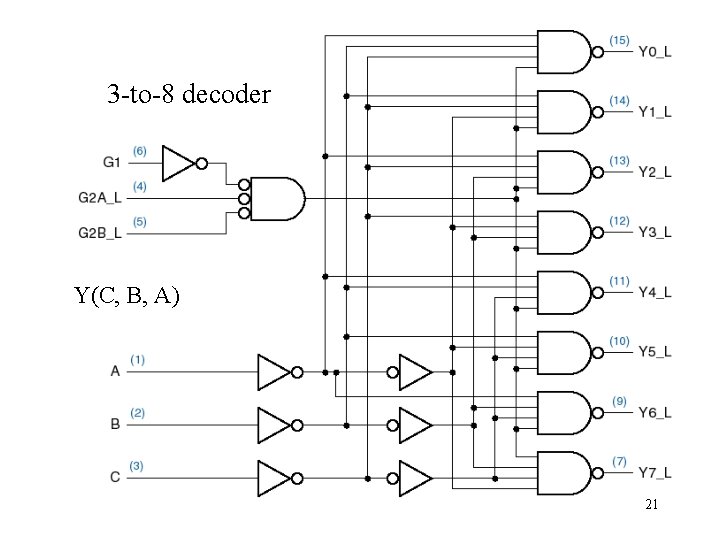

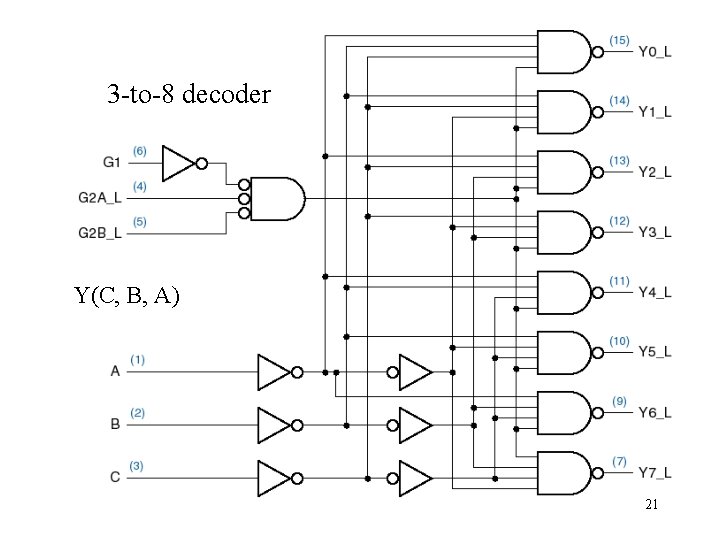

3 -to-8 decoder Y(C, B, A) 21

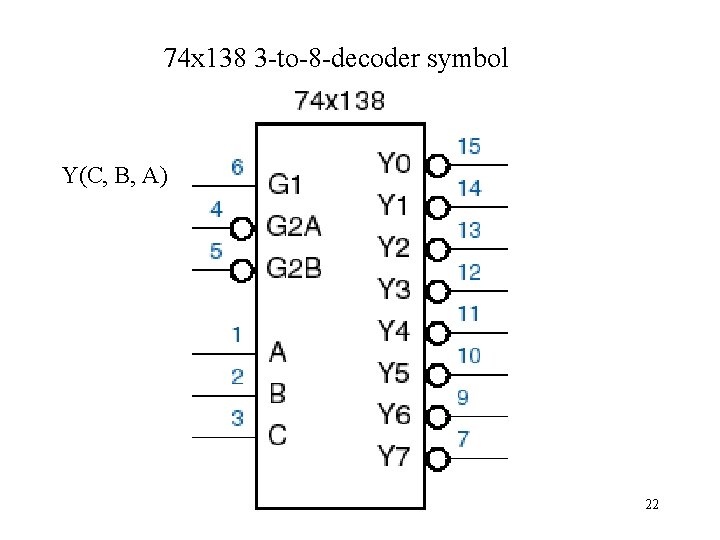

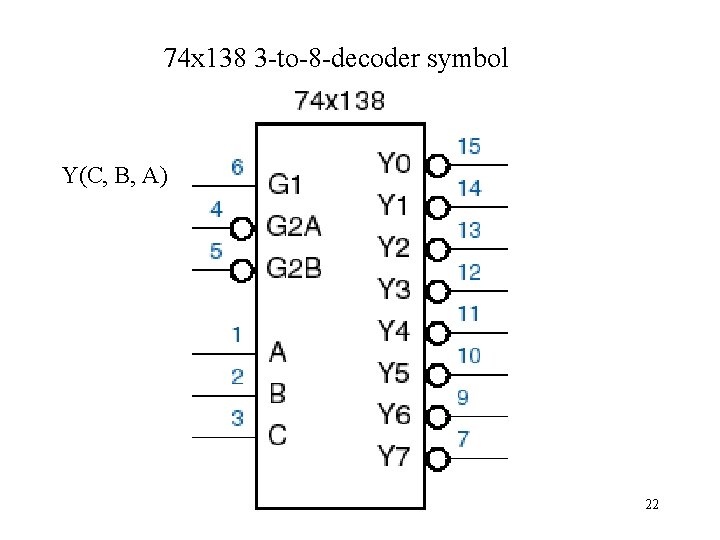

74 x 138 3 -to-8 -decoder symbol Y(C, B, A) 22

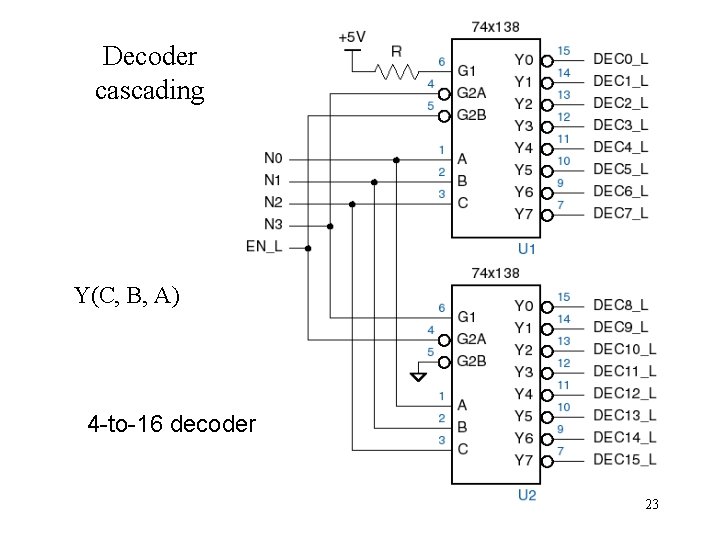

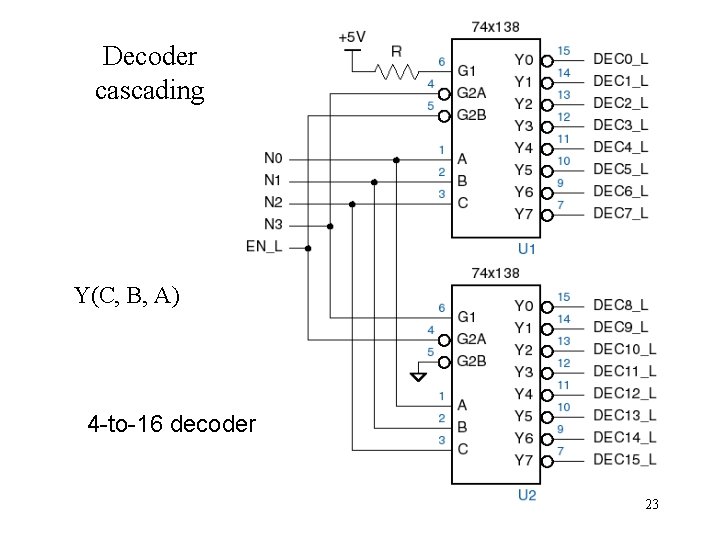

Decoder cascading Y(C, B, A) 4 -to-16 decoder 23

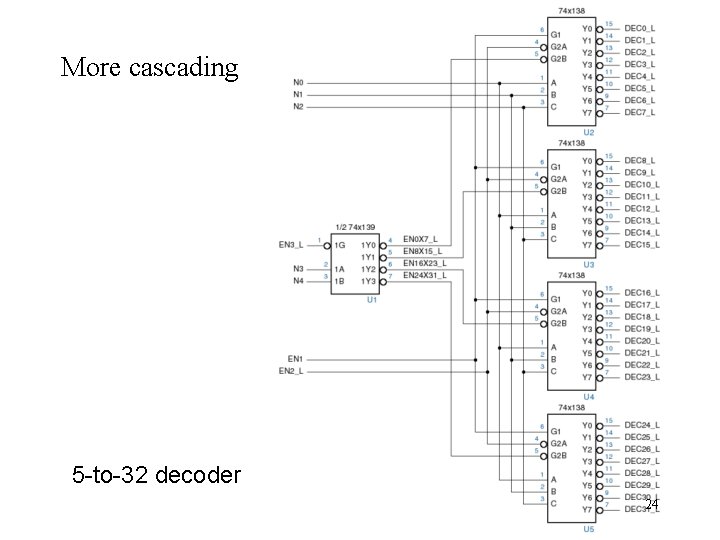

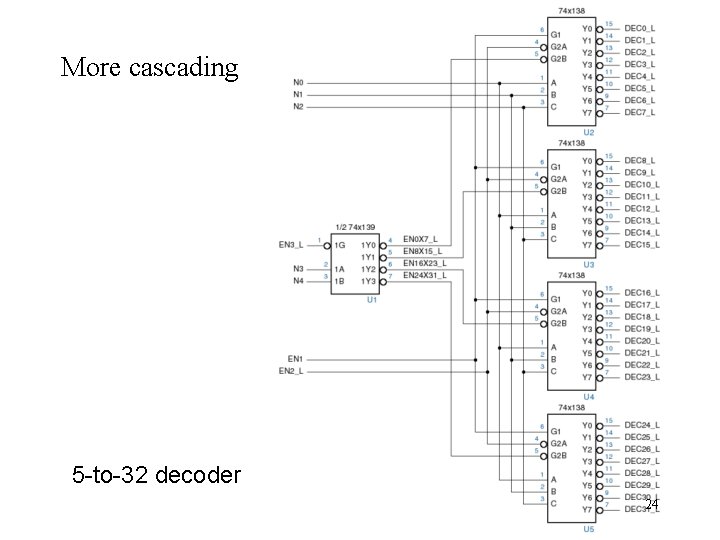

More cascading 5 -to-32 decoder 24

Decoder applications • Microprocessor memory systems – selecting different banks of memory • Microprocessor input/output systems – selecting different devices • Microprocessor instruction decoding – enabling different functional units • Memory chips – enabling different rows of memory depending on address • Lots of other applications 25

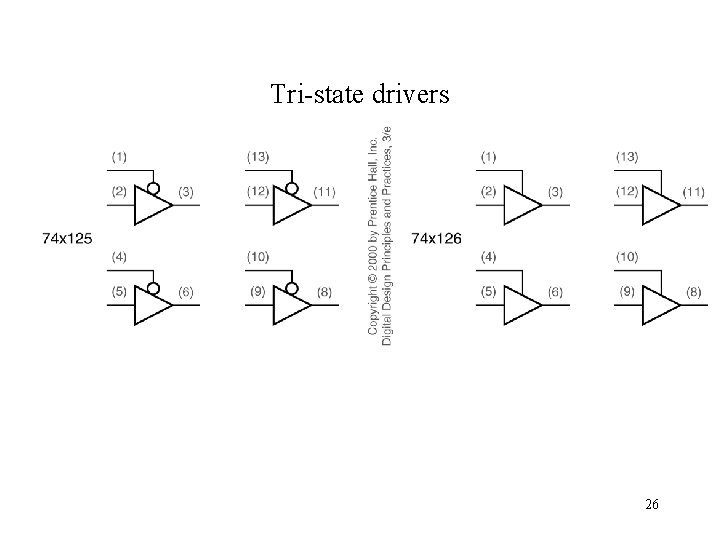

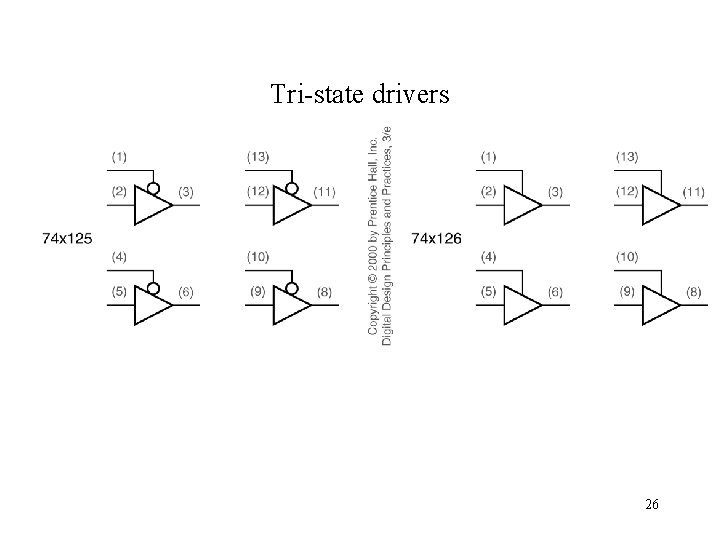

Tri-state drivers 26

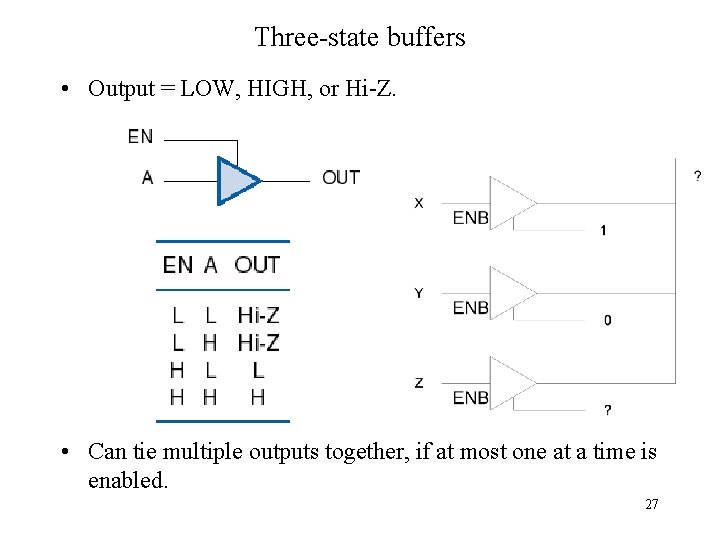

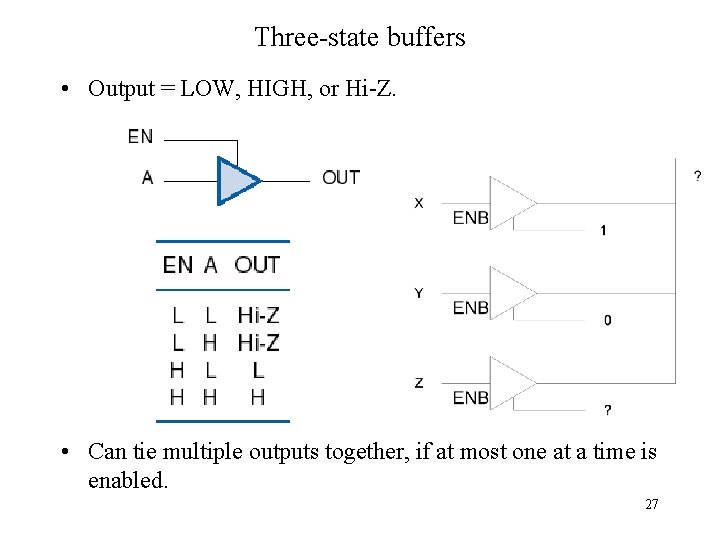

Three-state buffers • Output = LOW, HIGH, or Hi-Z. • Can tie multiple outputs together, if at most one at a time is enabled. 27

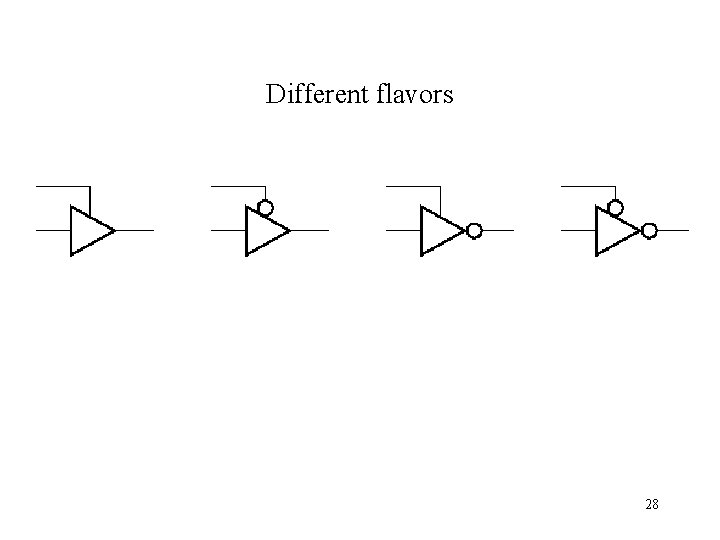

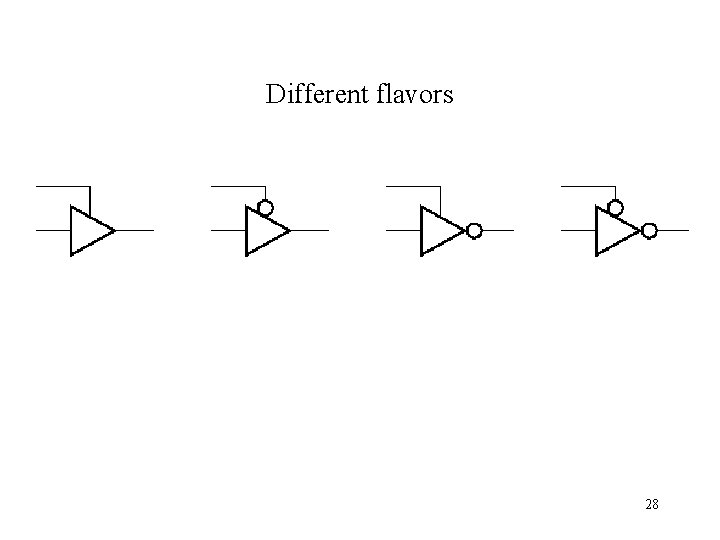

Different flavors 28

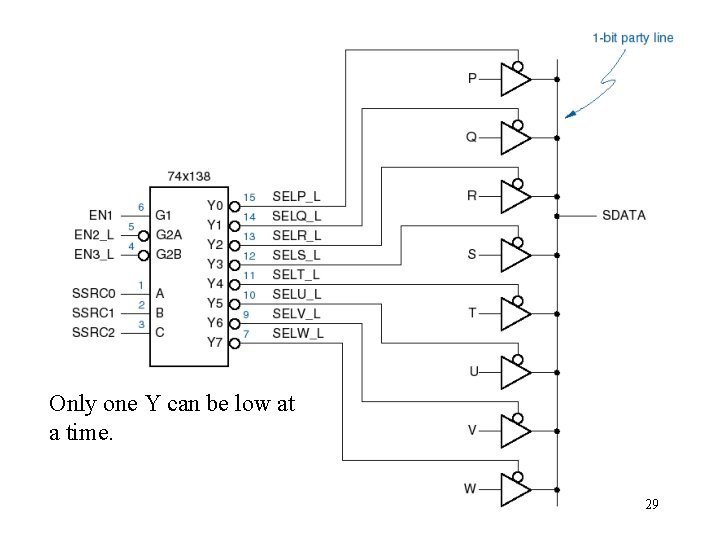

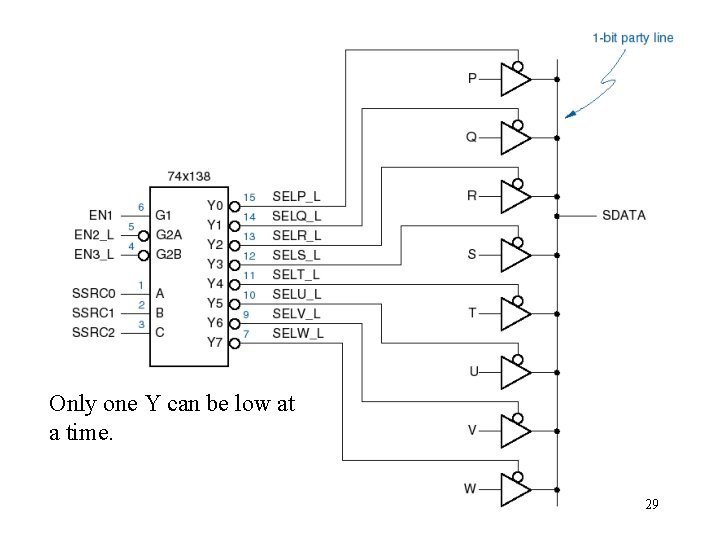

Only one Y can be low at a time. 29

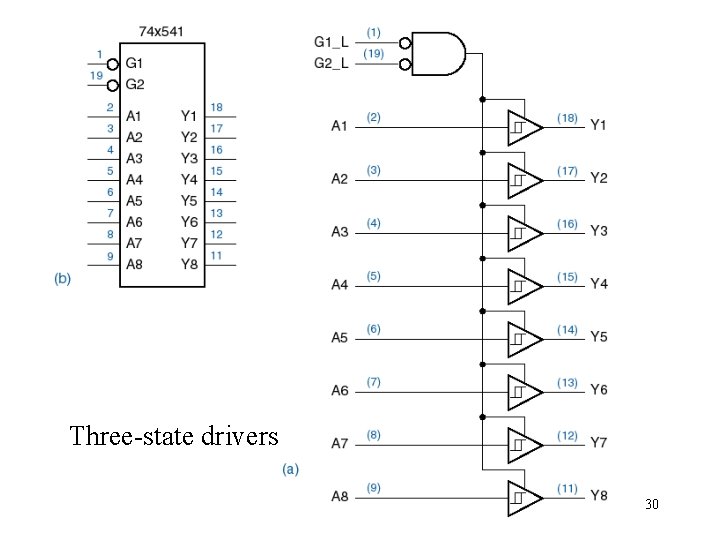

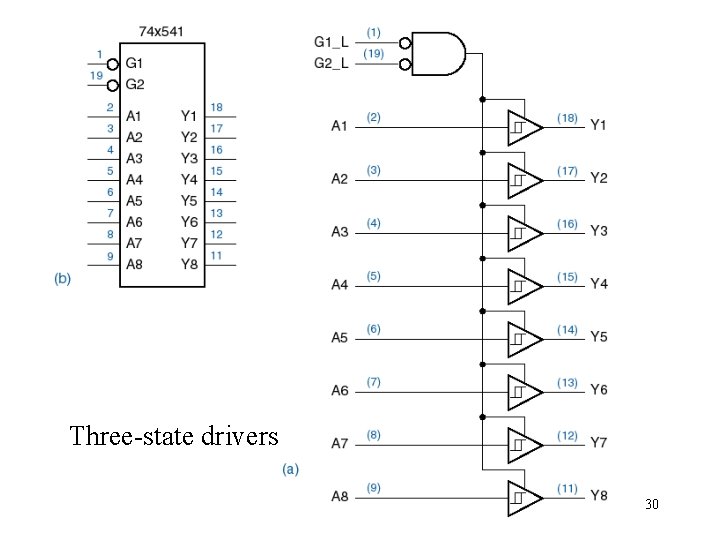

Three-state drivers 30

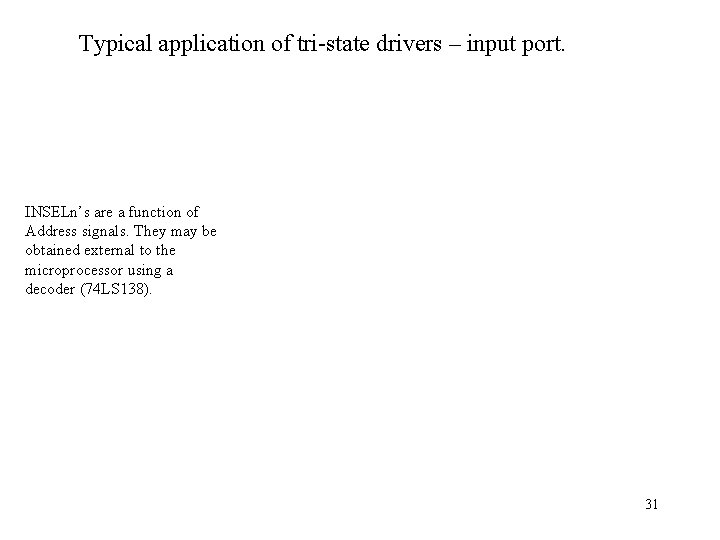

Typical application of tri-state drivers – input port. INSELn’s are a function of Address signals. They may be obtained external to the microprocessor using a decoder (74 LS 138). 31

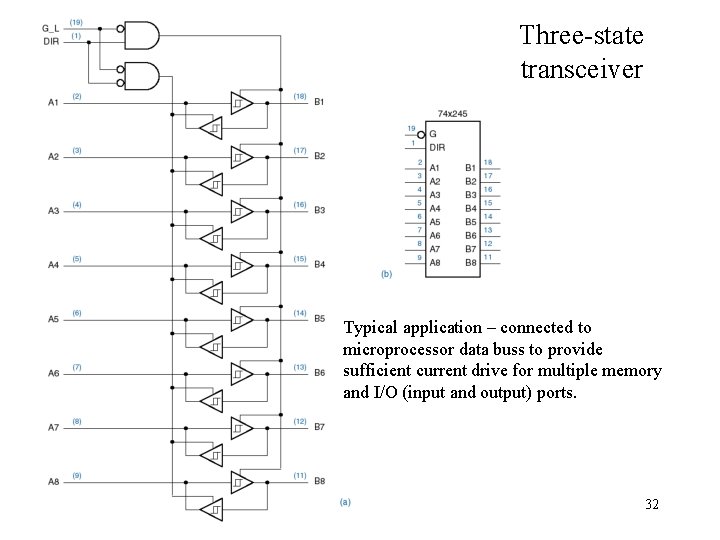

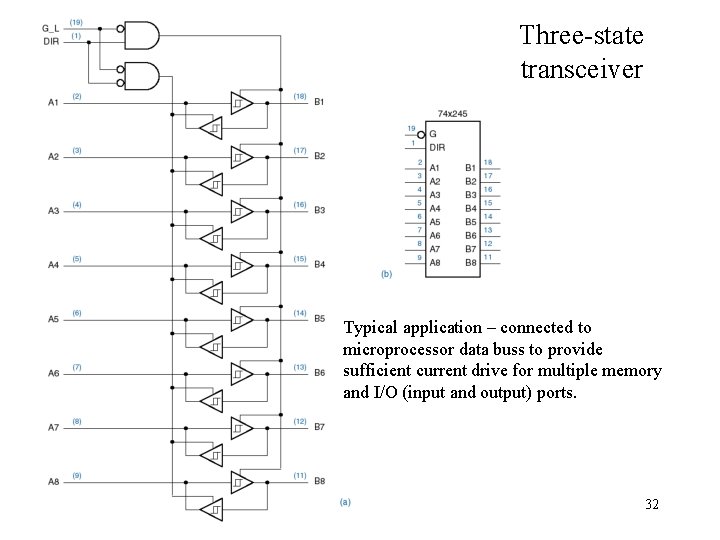

Three-state transceiver Typical application – connected to microprocessor data buss to provide sufficient current drive for multiple memory and I/O (input and output) ports. 32

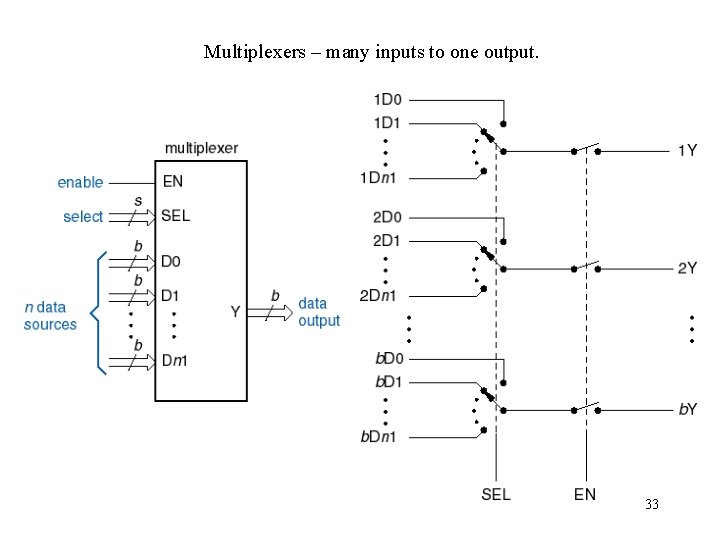

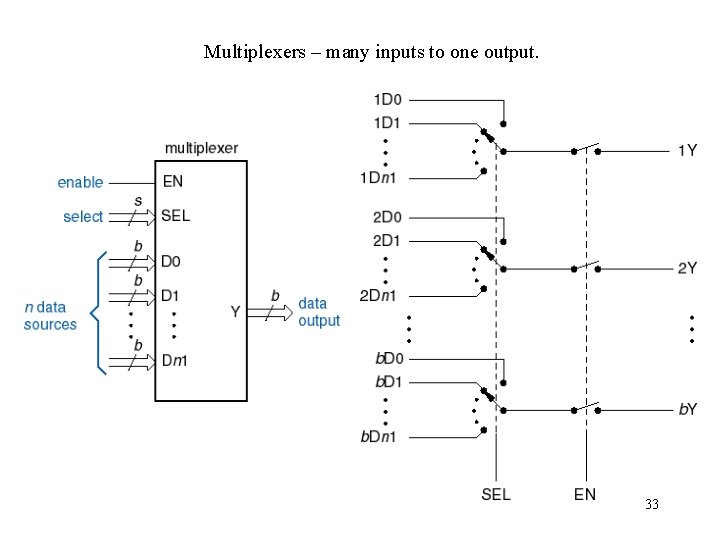

Multiplexers – many inputs to one output. 33

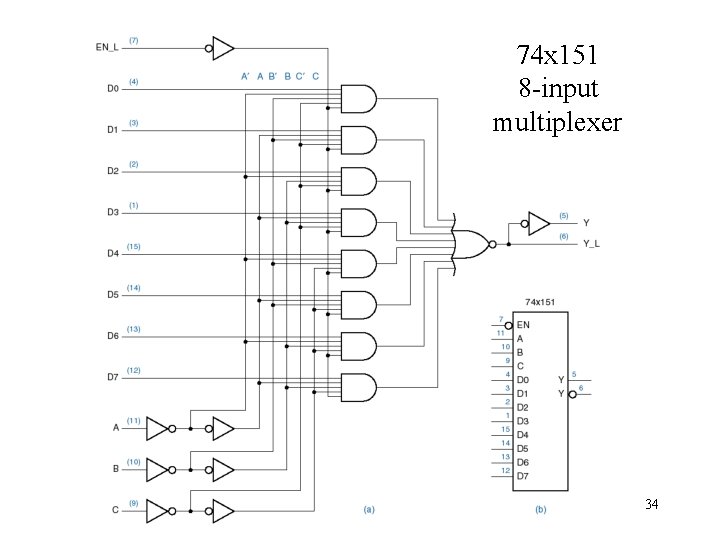

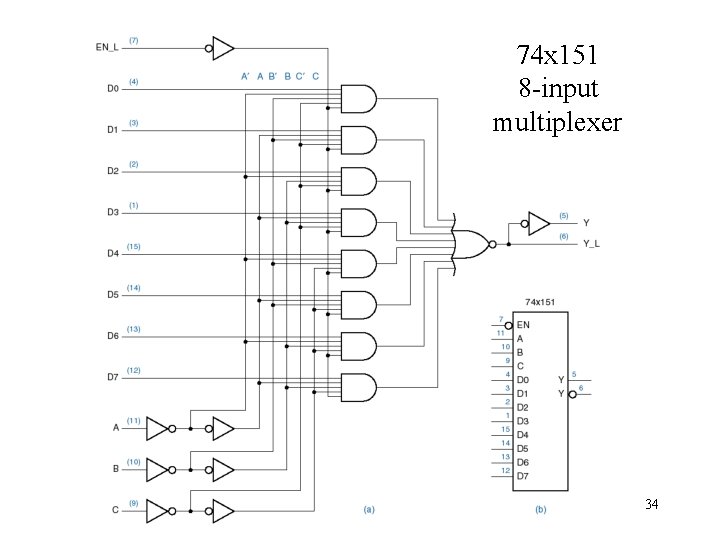

74 x 151 8 -input multiplexer 34

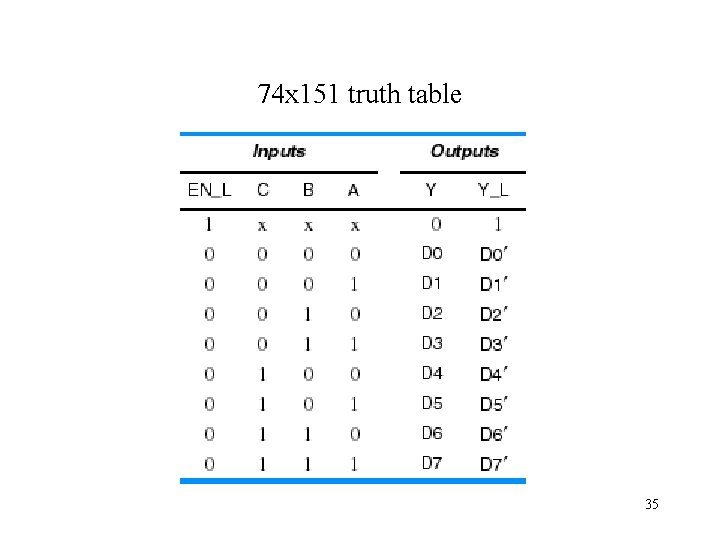

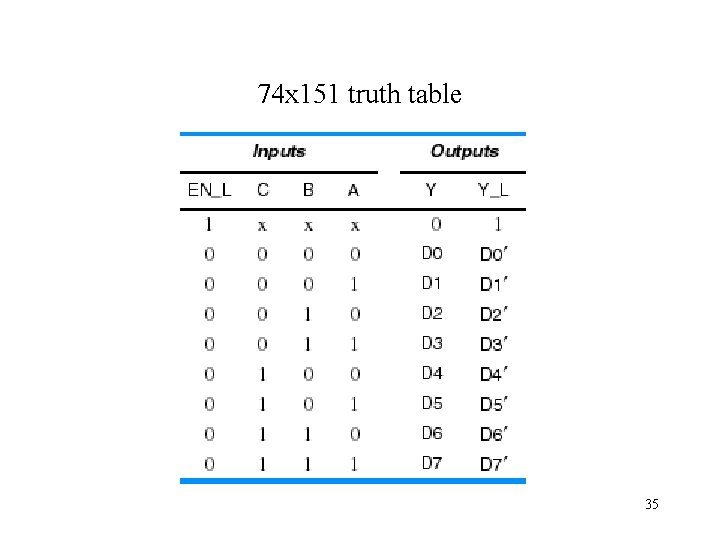

74 x 151 truth table 35

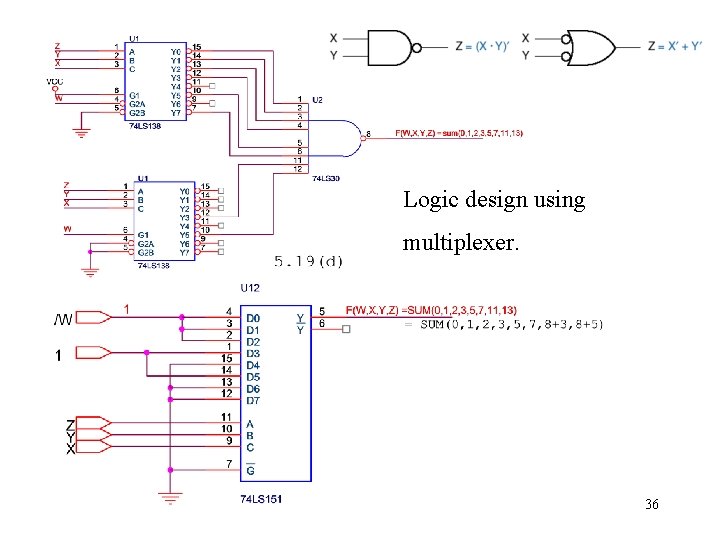

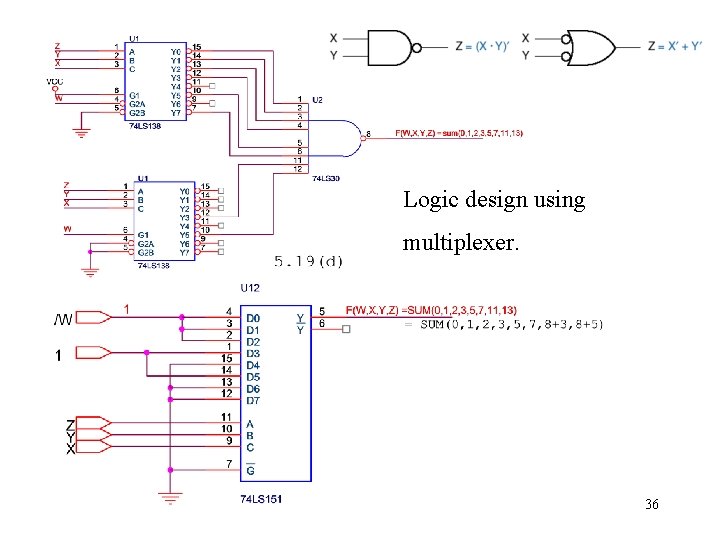

Logic design using multiplexer. 36

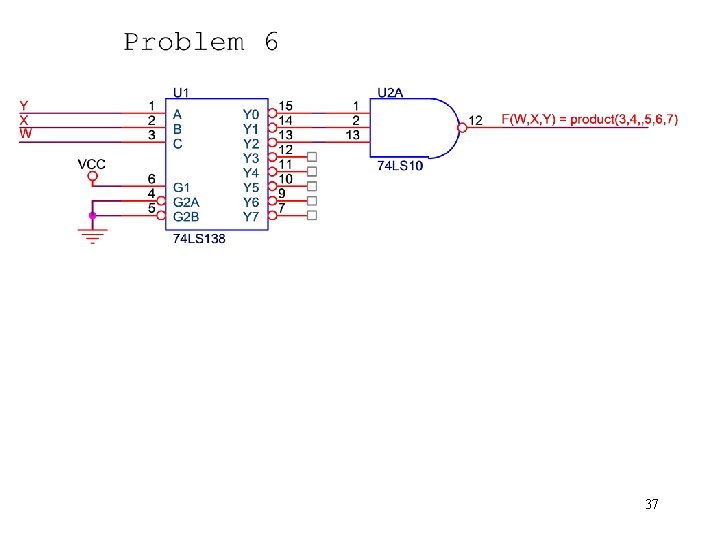

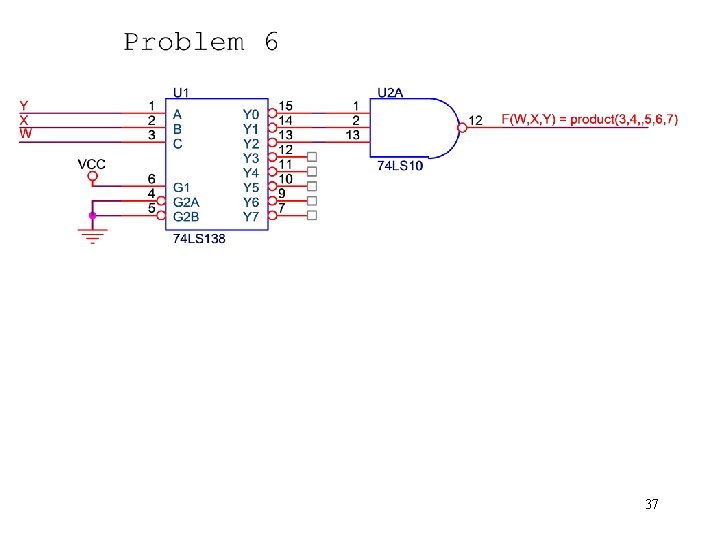

37

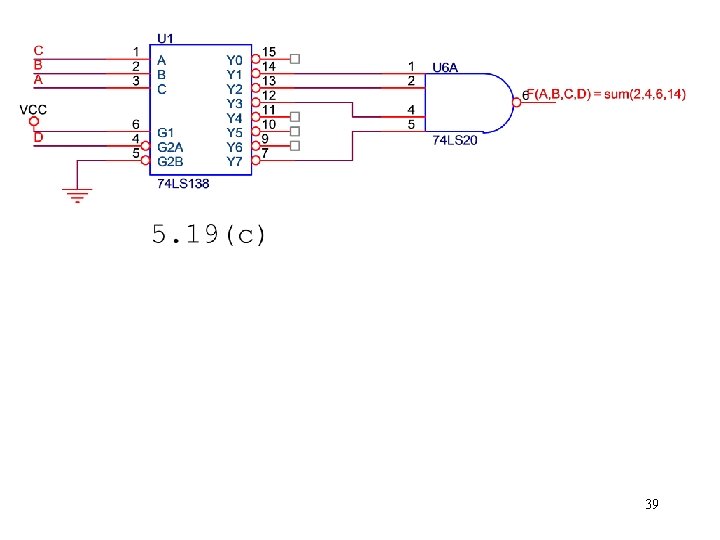

38

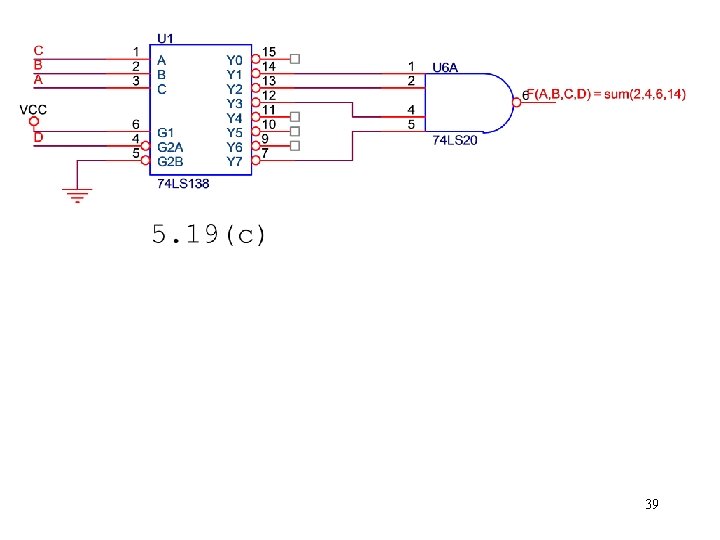

39

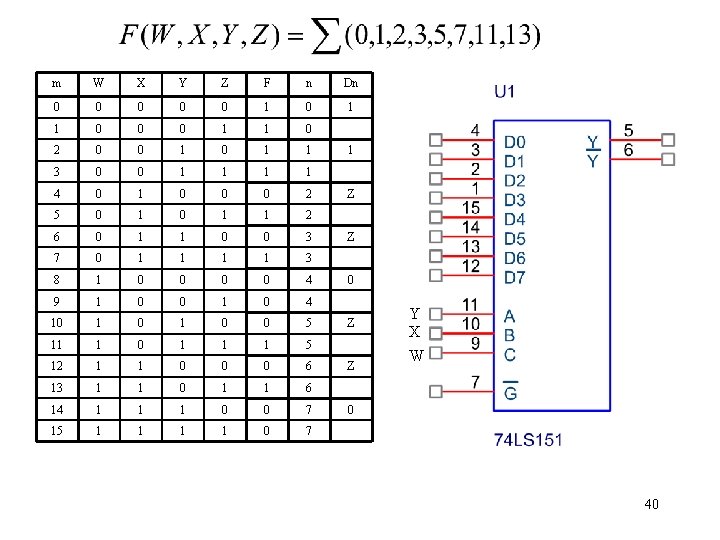

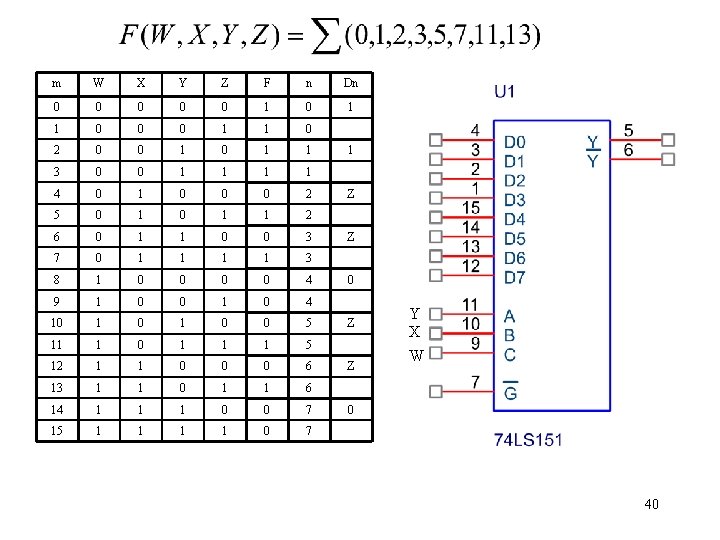

m W X Y Z F n Dn 0 0 0 1 1 0 2 0 0 1 1 3 0 0 1 1 4 0 1 0 0 0 2 5 0 1 1 2 6 0 1 1 0 0 3 7 0 1 1 3 8 1 0 0 4 9 1 0 0 1 0 4 10 1 0 0 5 11 1 0 1 1 1 5 12 1 1 0 0 0 6 13 1 1 0 1 1 6 14 1 1 1 0 0 7 15 1 1 0 7 1 Z Z 0 Z Z Y X W 0 40

41

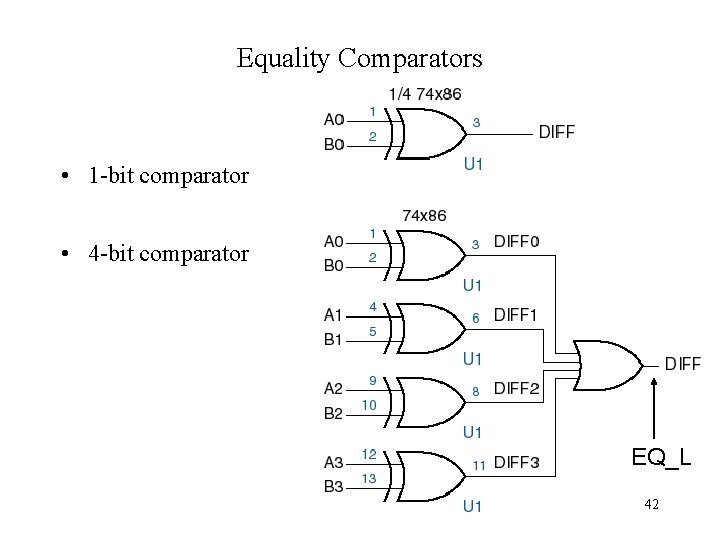

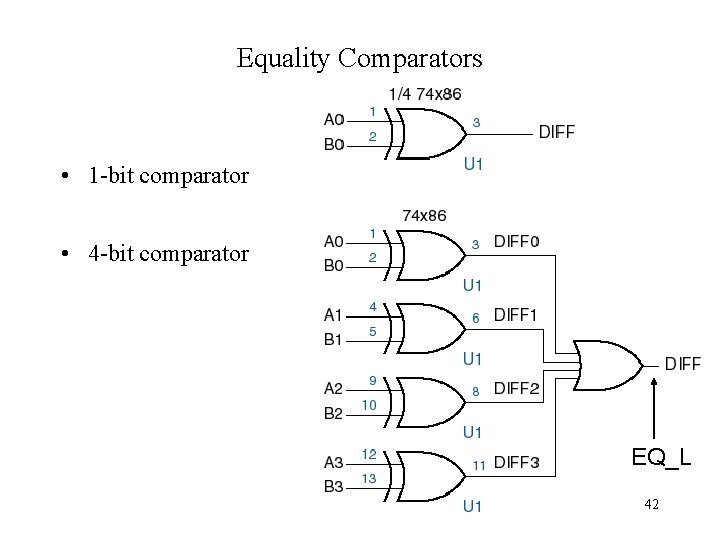

Equality Comparators • 1 -bit comparator • 4 -bit comparator EQ_L 42

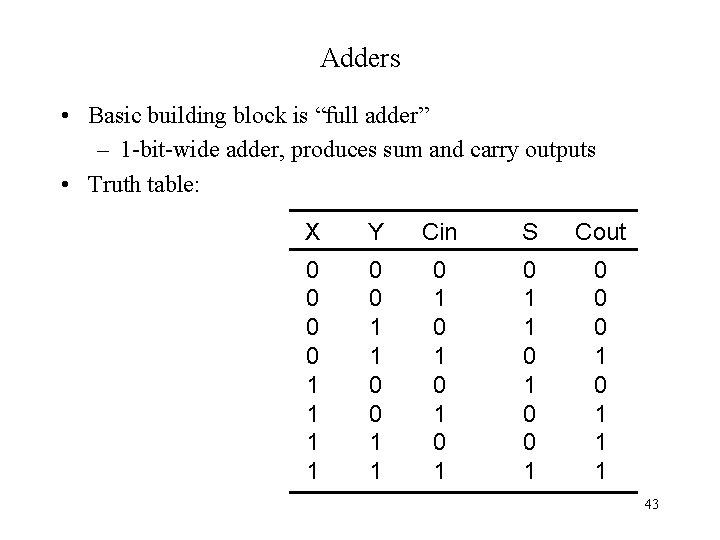

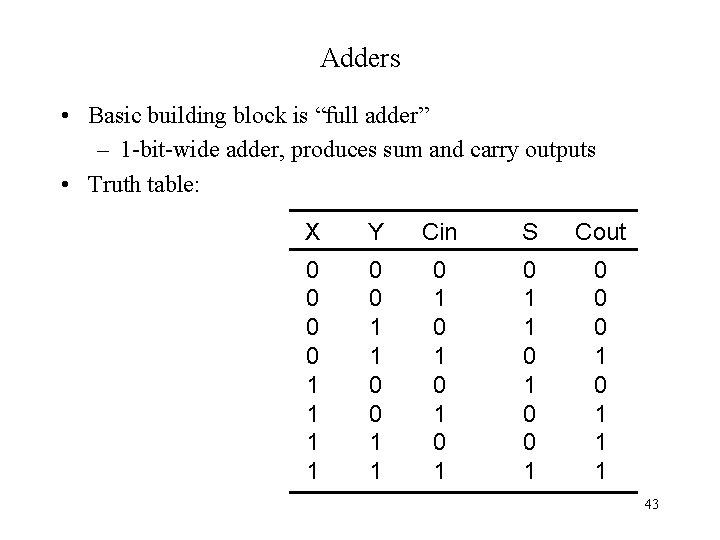

Adders • Basic building block is “full adder” – 1 -bit-wide adder, produces sum and carry outputs • Truth table: X Y Cin S Cout 0 0 1 1 0 1 0 1 0 1 1 0 0 0 1 1 1 43

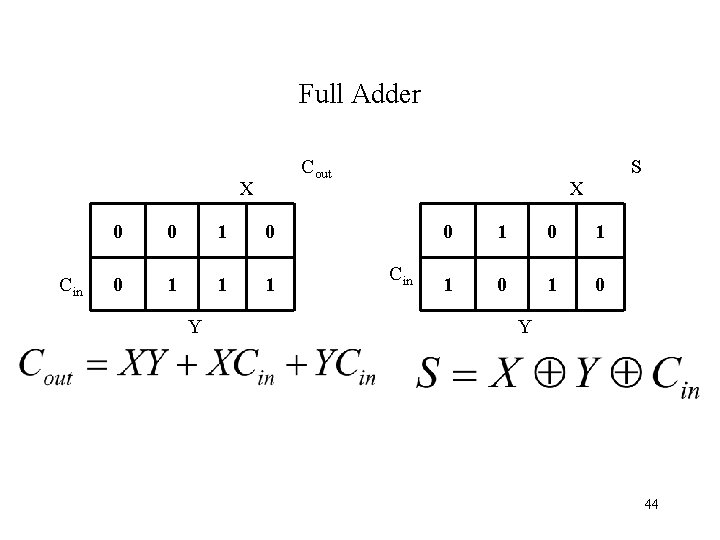

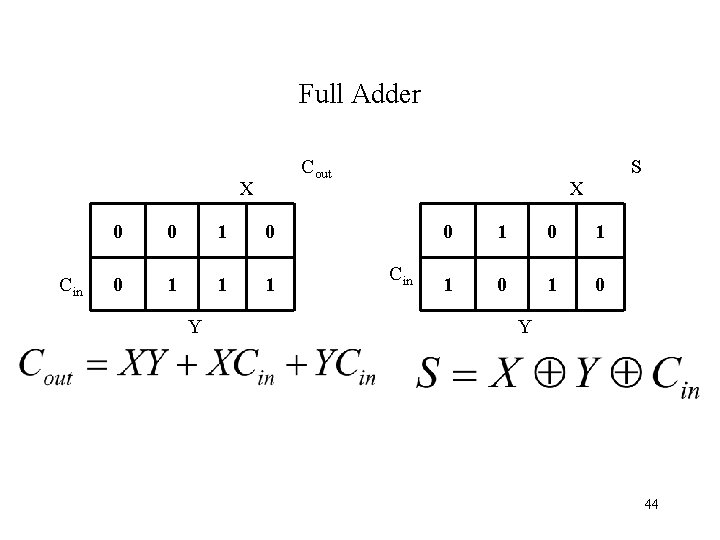

Full Adder Cout X Cin 0 0 1 1 1 Y S X Cin 0 1 1 0 Y 44

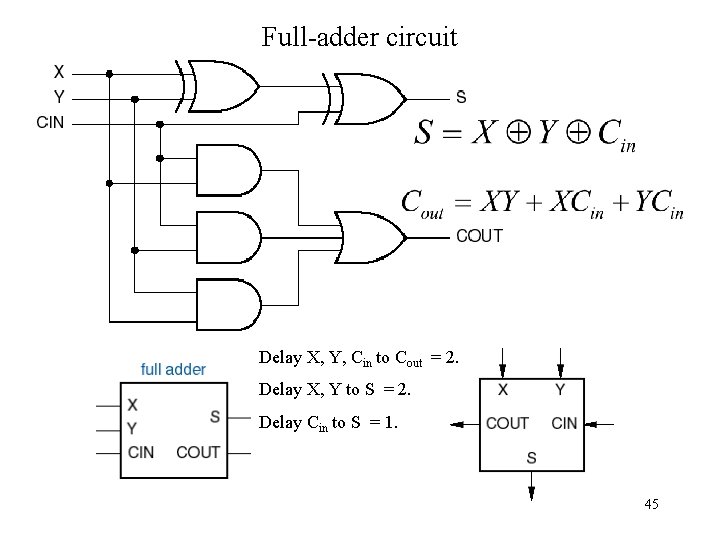

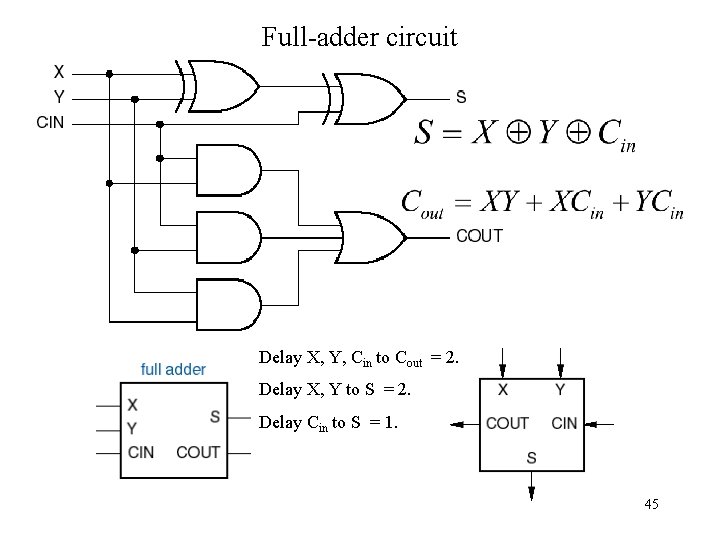

Full-adder circuit Delay X, Y, Cin to Cout = 2. Delay X, Y to S = 2. Delay Cin to S = 1. 45

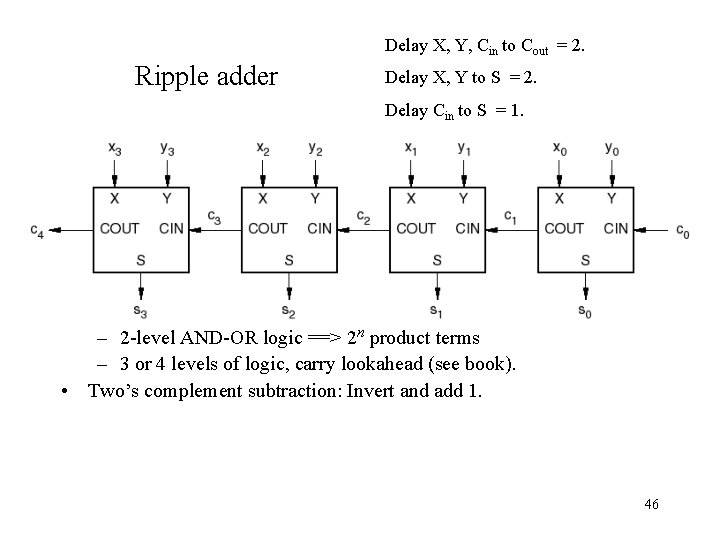

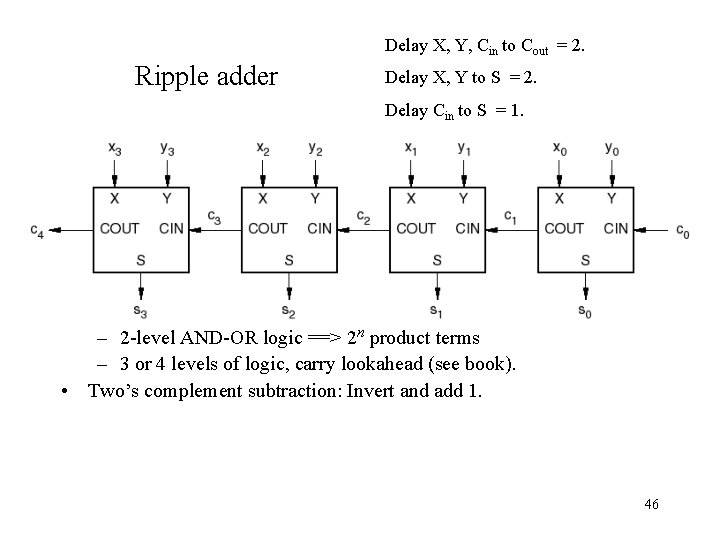

Delay X, Y, Cin to Cout = 2. Ripple adder Delay X, Y to S = 2. Delay Cin to S = 1. • Speed limited by carry chain • Faster adders eliminate or limit carry chain – 2 -level AND-OR logic ==> 2 n product terms – 3 or 4 levels of logic, carry lookahead (see book). • Two’s complement subtraction: Invert and add 1. 46

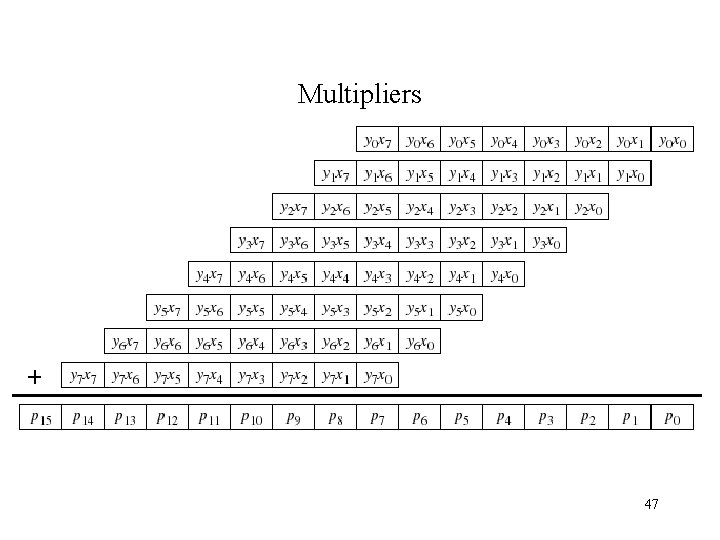

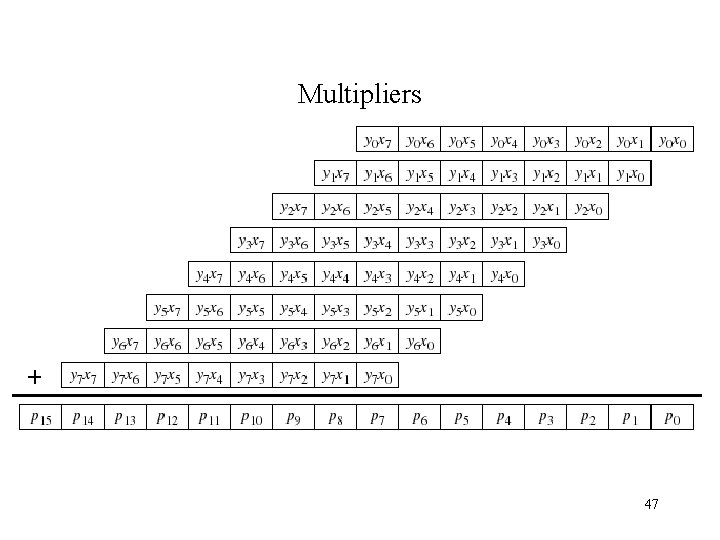

Multipliers • 8 x 8 multiplier 47

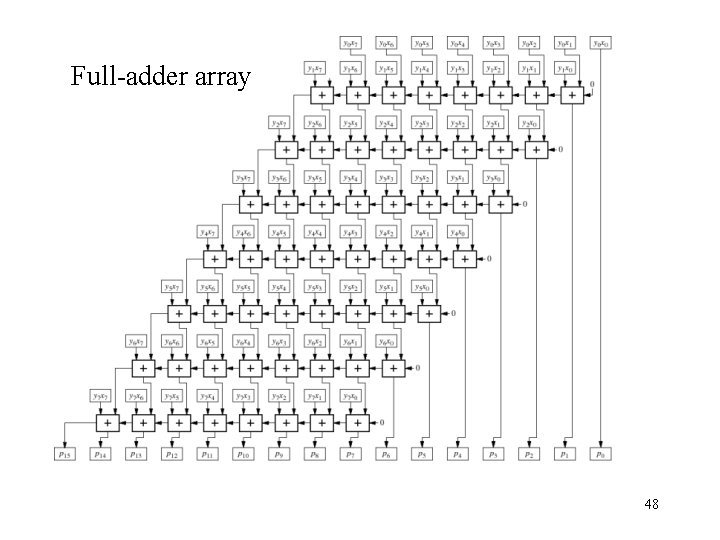

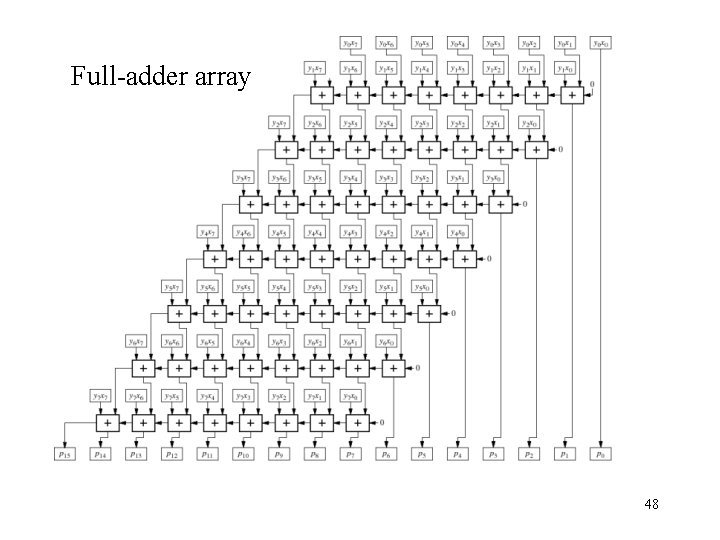

Full-adder array 48

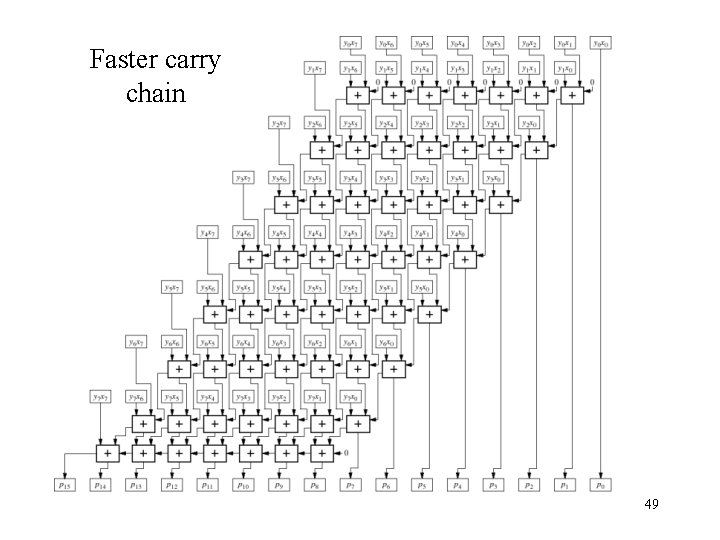

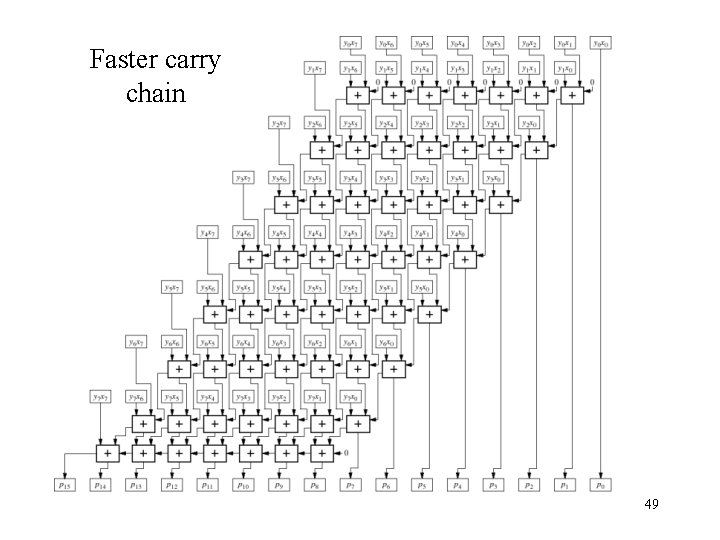

Faster carry chain 49

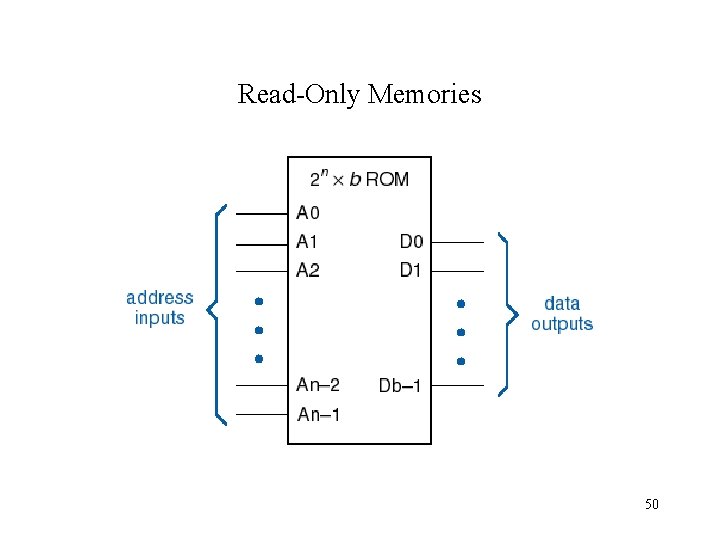

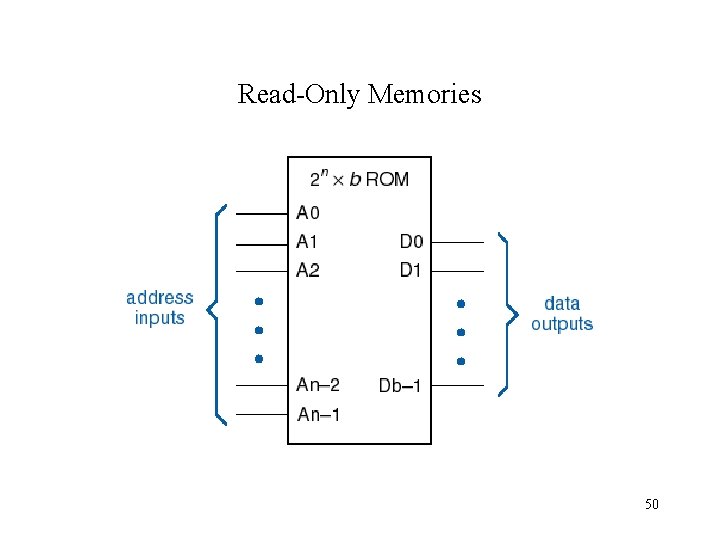

Read-Only Memories 50

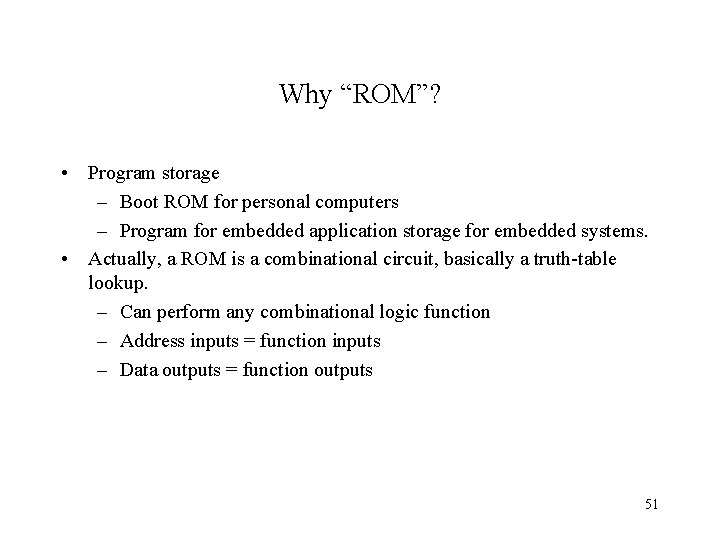

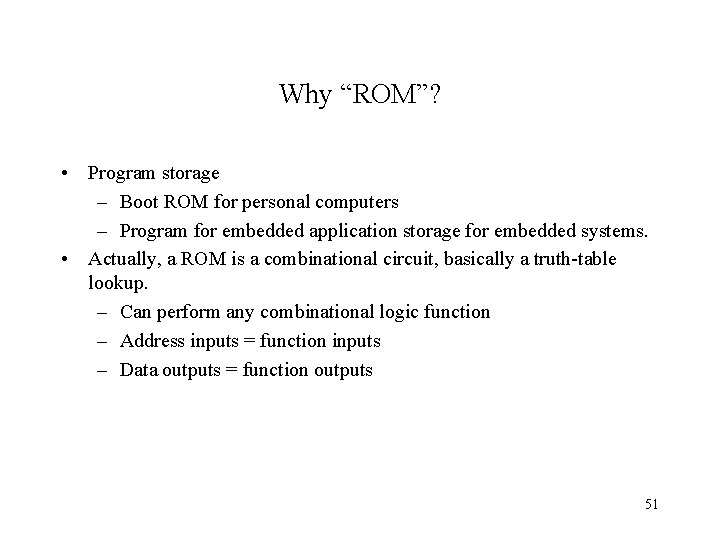

Why “ROM”? • Program storage – Boot ROM for personal computers – Program for embedded application storage for embedded systems. • Actually, a ROM is a combinational circuit, basically a truth-table lookup. – Can perform any combinational logic function – Address inputs = function inputs – Data outputs = function outputs 51

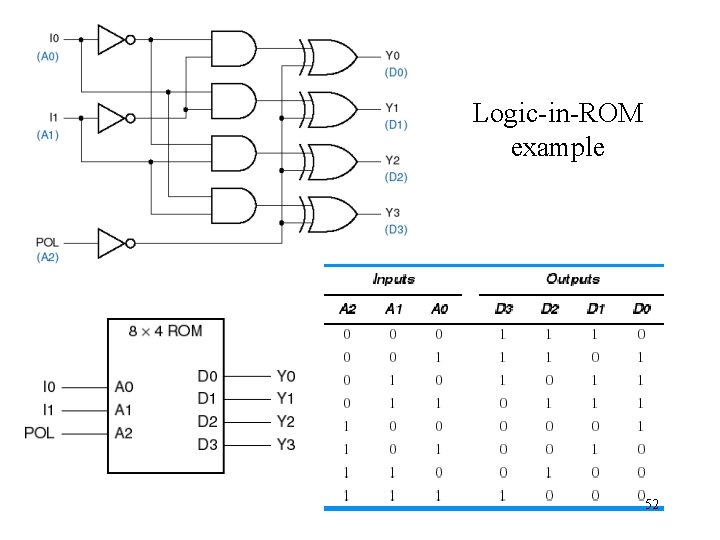

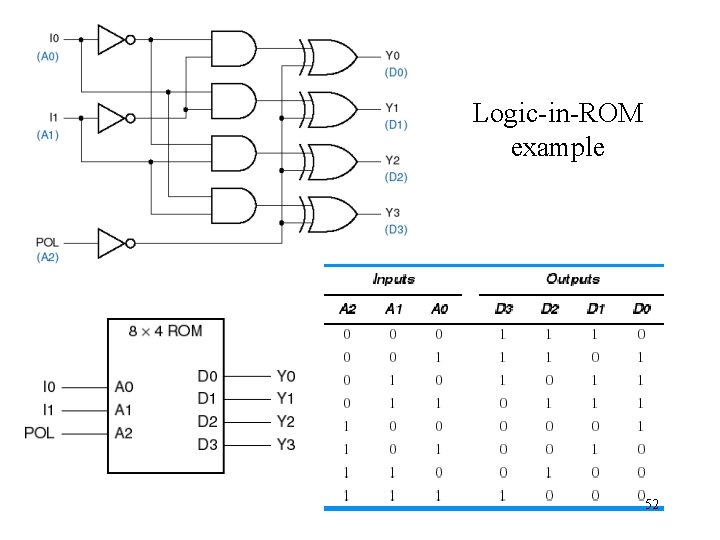

Logic-in-ROM example 52

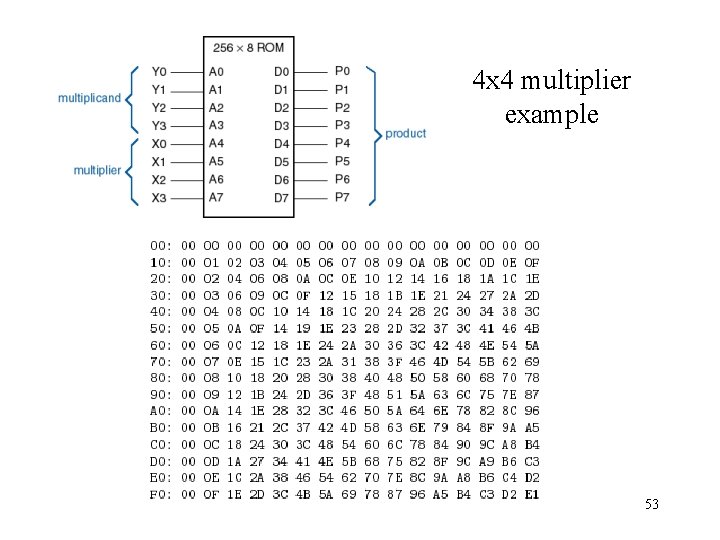

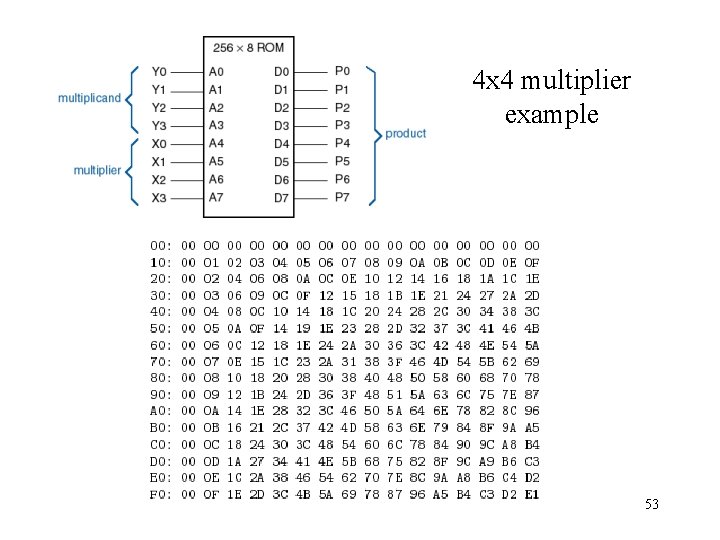

4 x 4 multiplier example 53

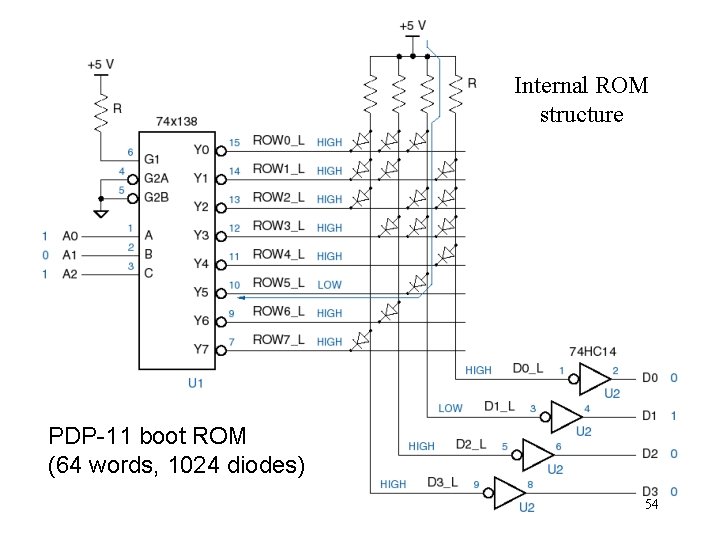

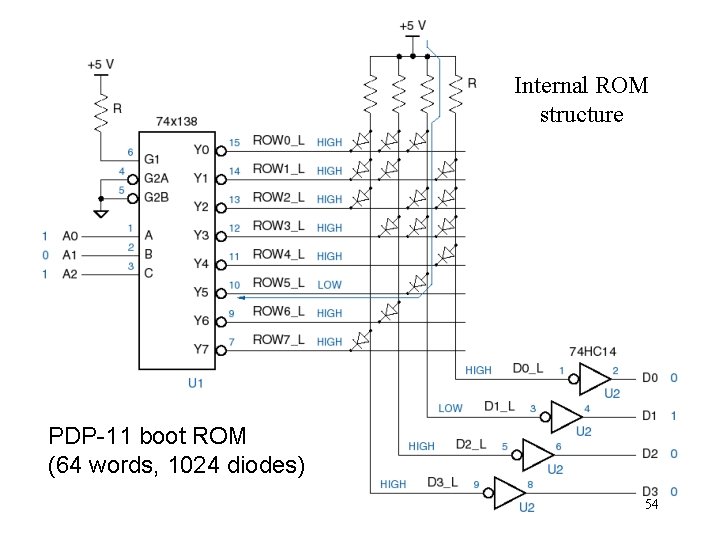

Internal ROM structure PDP-11 boot ROM (64 words, 1024 diodes) 54

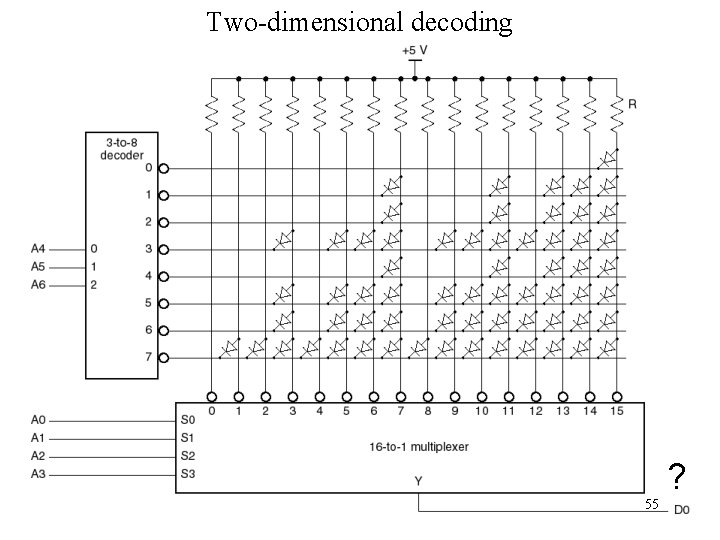

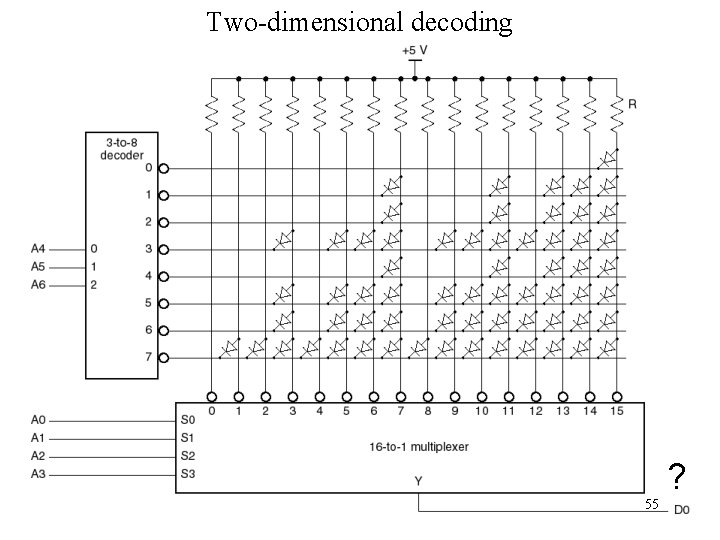

Two-dimensional decoding ? 55

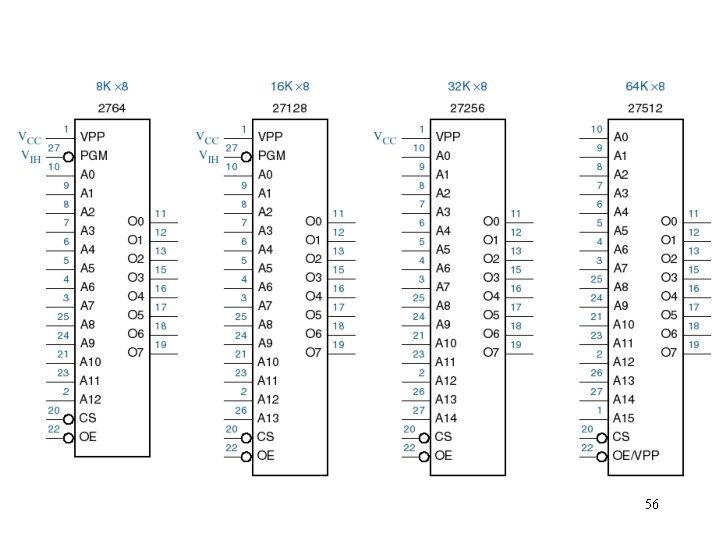

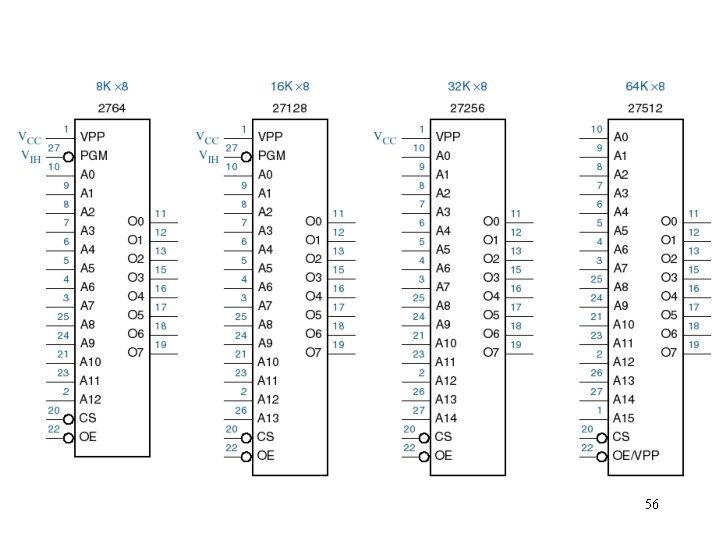

Typical commercial EEPROMs 56

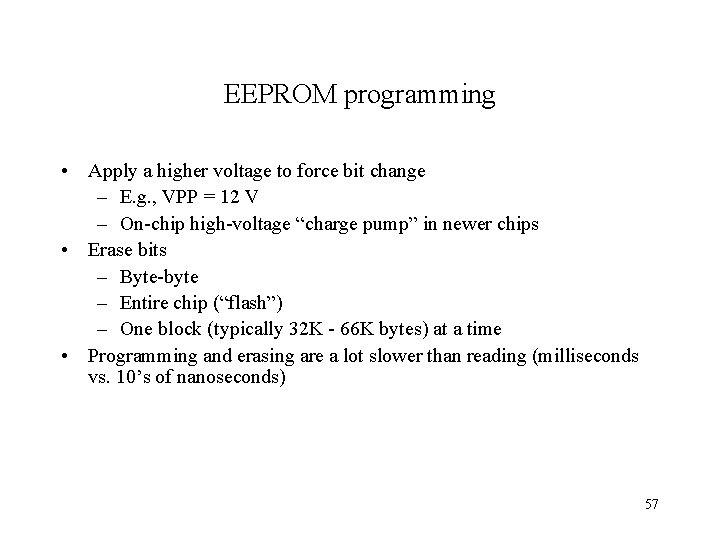

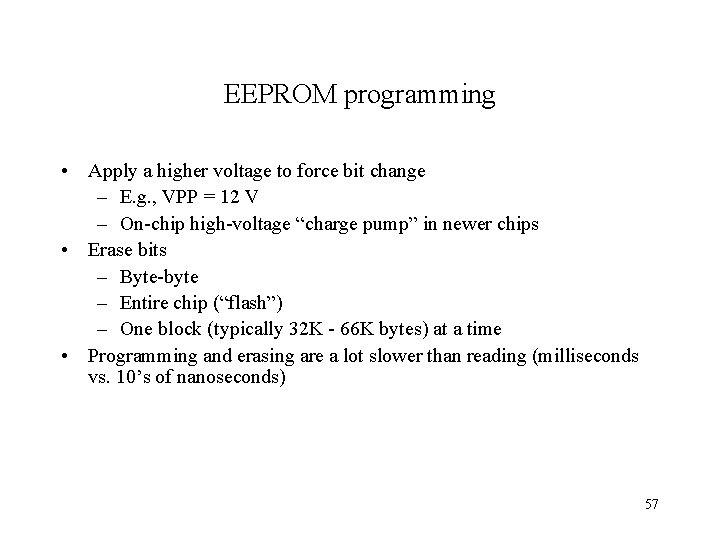

EEPROM programming • Apply a higher voltage to force bit change – E. g. , VPP = 12 V – On-chip high-voltage “charge pump” in newer chips • Erase bits – Byte-byte – Entire chip (“flash”) – One block (typically 32 K - 66 K bytes) at a time • Programming and erasing are a lot slower than reading (milliseconds vs. 10’s of nanoseconds) 57

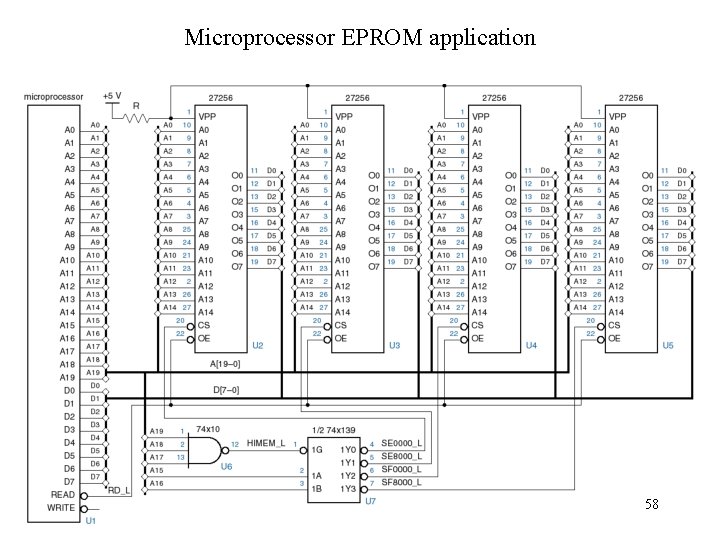

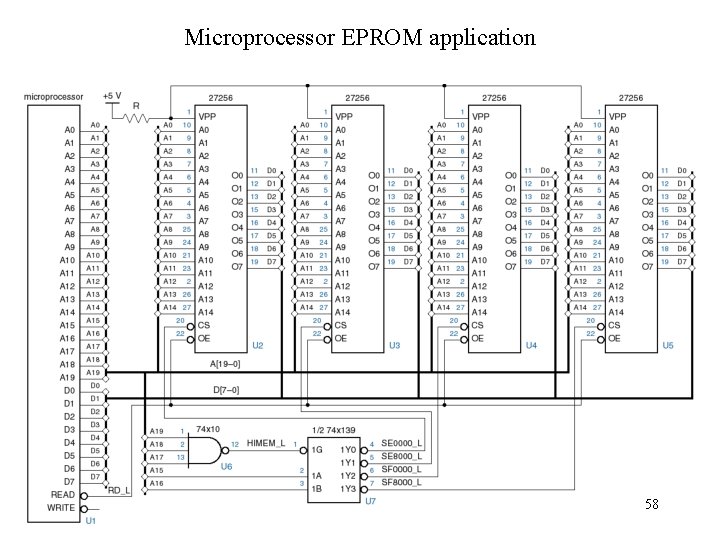

Microprocessor EPROM application 58