CHAPTER 4 The Macro Design Process The Issues

- Slides: 27

CHAPTER 4 The Macro Design Process The Issues 1. Overview of IP Design 2. Key Features 3. Planning and Specification 4. Macro Design and Verification 5. Soft Macro Productization

The Issues • An Overview of the macro design • Contents of a design specification • Top-level macro design and partitioning into subblocks • Designing subblocks • Integrating subblocks and macro verfication • Productization and prototyping issues

4. 1 Overview of IP Design • The process of designing reusable components or IP 1. Characteristics of Good IP 2. Implementation and Verification IP 3. Overview of Design Process

4. 1. 1 Characteristics of Good IP • • Configurability Standard Interfaces Compliance to Defensive Design Practices Complete Set of Deliverables • Syn. Thesizable RTL (encrypted or unencrypted) • Verification IP for verifying the core stand-alone and for chip-level verification • Synthesis scripts • Documentaton

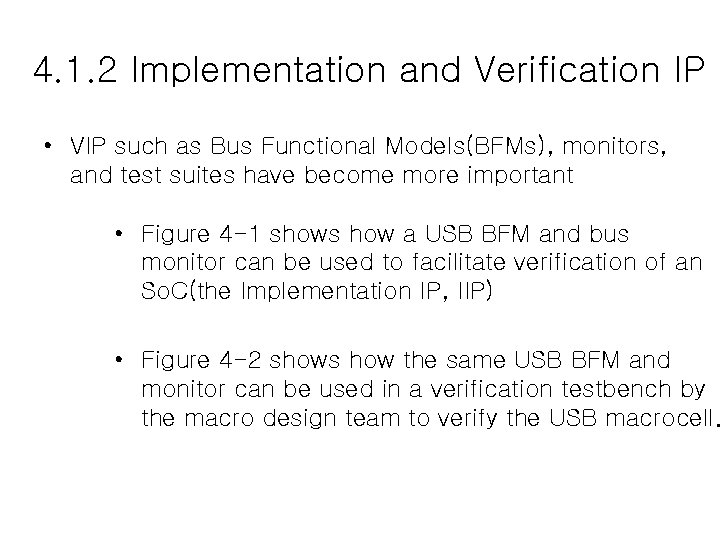

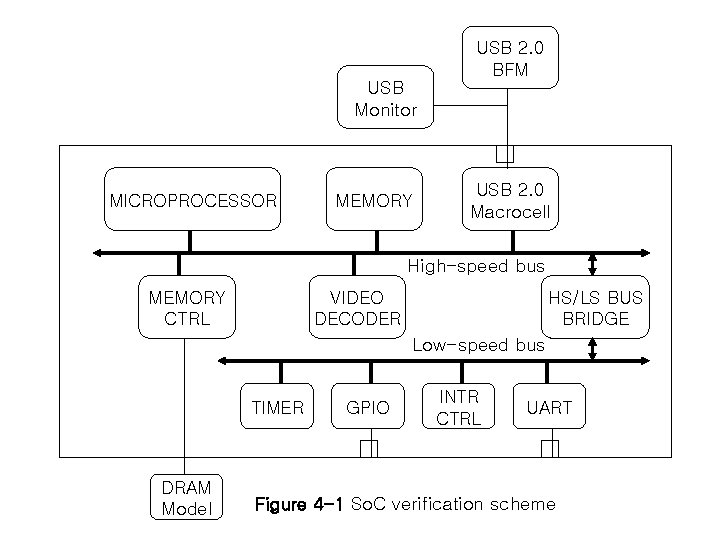

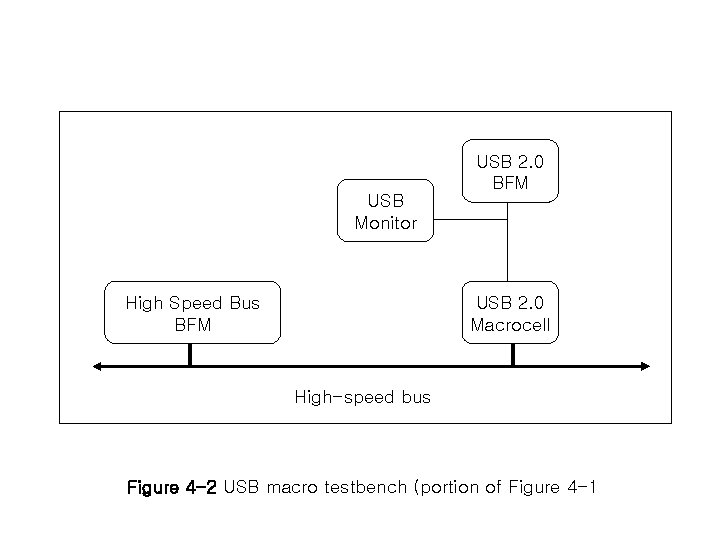

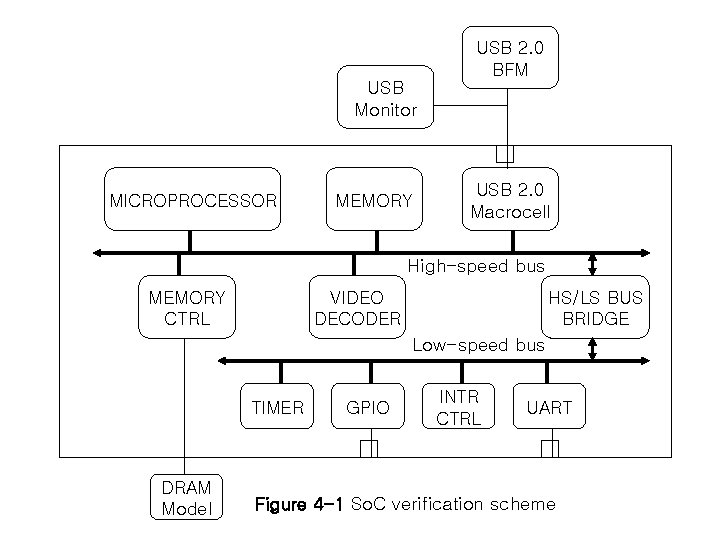

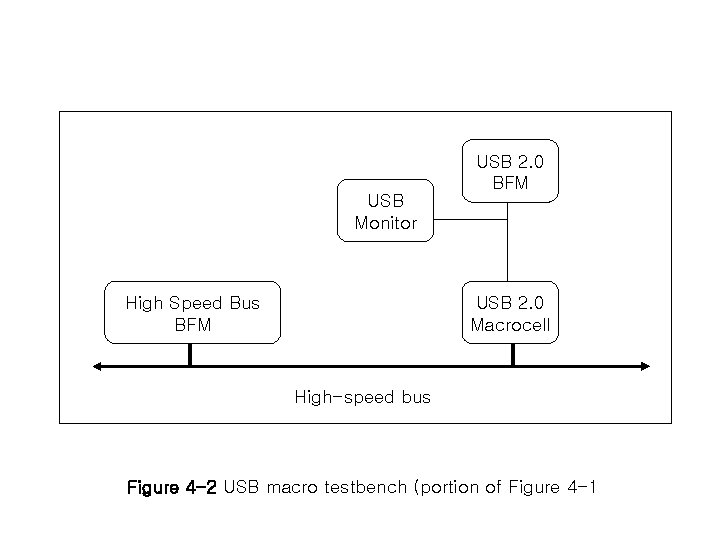

4. 1. 2 Implementation and Verification IP • VIP such as Bus Functional Models(BFMs), monitors, and test suites have become more important • Figure 4 -1 shows how a USB BFM and bus monitor can be used to facilitate verification of an So. C(the Implementation IP, IIP) • Figure 4 -2 shows how the same USB BFM and monitor can be used in a verification testbench by the macro design team to verify the USB macrocell.

4. 1. 2 Implementation and Verification IP • VIP - A high-level mechanism for generating transactions on the interface of the IIP - is useful to • Do initial verification of the RTL • Allow rapid configuration of the test bench for testing different configurations of the IP • Ship with the IP to allow the integrator to test his configuration of the IIP • Integrate into the chip-level test bench

USB 2. 0 BFM USB Monitor MICROPROCESSOR MEMORY USB 2. 0 Macrocell High-speed bus MEMORY CTRL VIDEO DECODER HS/LS BUS BRIDGE Low-speed bus TIMER DRAM Model GPIO INTR CTRL UART Figure 4 -1 So. C verification scheme

USB 2. 0 BFM USB Monitor High Speed Bus BFM USB 2. 0 Macrocell High-speed bus Figure 4 -2 USB macro testbench (portion of Figure 4 -1

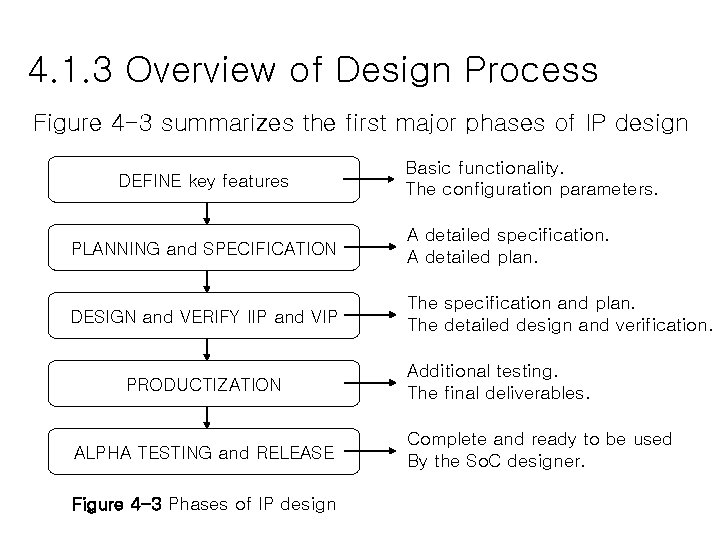

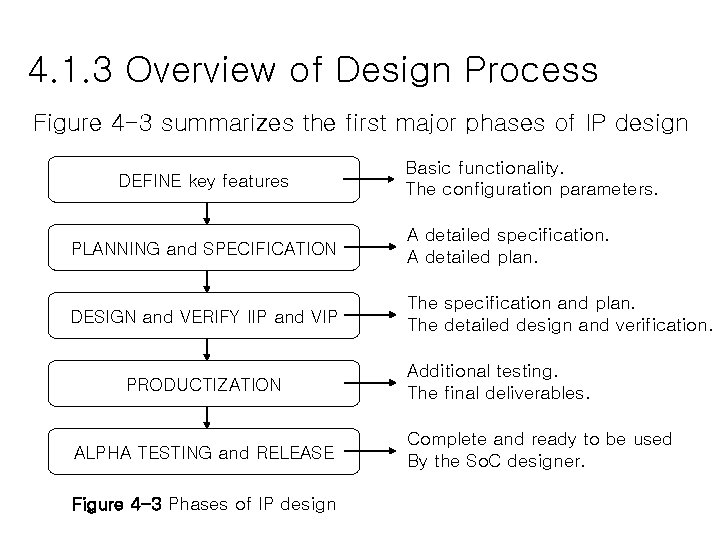

4. 1. 3 Overview of Design Process Figure 4 -3 summarizes the first major phases of IP design DEFINE key features Basic functionality. The configuration parameters. PLANNING and SPECIFICATION A detailed specification. A detailed plan. DESIGN and VERIFY IIP and VIP The specification and plan. The detailed design and verification. PRODUCTIZATION ALPHA TESTING and RELEASE Figure 4 -3 Phases of IP design Additional testing. The final deliverables. Complete and ready to be used By the So. C designer.

4. 2 Key Features • • • The key features for an IP are basically an initial specification. The key features are should define the configuration parameters for the IP. The key features are typically captured in a brief document or a set of slides.

4. 3 Planning and Specification Key documents developed during the planning and specification phase typically include: 1. 2. 3. 4. 5. Functional Specification Verification Specification Packaging Specification Development Plan High-Level Models as Executable Specifications

4. 3. 1 Functional Specification • • A functional specification would include : Pin definitions Parameter definitions Register definitions Additional information to explain how the pins, parameters, and registers work • Performance and physical implementation requirements

4. 3. 2 Verification Specification - A verification specification : • Defines the test environment • Describes the approach to verifying the IP: - What will be tested by directed test - What random testing will be done - What matrics will be used to determine that it is ready to ship.

4. 3. 3 Packaging Specification - The packaging specification defines any special scripts that are provided as part of the final deliverables. - These scripts typically include installation scripts, configuration scripts, and synthesis scripts. - For hardened IP, this specification also lists additional views that must be created.

4. 3. 4 Development Plan • • • The development plan includes : Deliverables -> what files and documents Schedule -> key milestones and dates Resource Plan -> people, tools, software, computer, networks requirements • Exceptions to Coding and Design Guidelines • Supported Environments -> what versions of what tools and libraries, what languages, what simulators, what standard cell libraries.

4. 3. 4 Development Plan - The development plan includes : • Support Plan -> who will support the product, what application notes will be developed • Documentation Plan -> what user document will be developed, by whom, and when. • Licensing Plan -> Will the macro be licensed. • Release Plan -> This includes some form of alpha testing before release, and then some form of beta or limited production period before final release.

4. 3. 5 High-Level Models as Excutable Specification • • • Developing a high-level midel also allows the development of testbenches and test suites early in the project High-level models are developed as part of the functional specification phase of the project High-level models can be written at the algorithmic or transaction level -> particularly useful for designs in multimedia or wireless

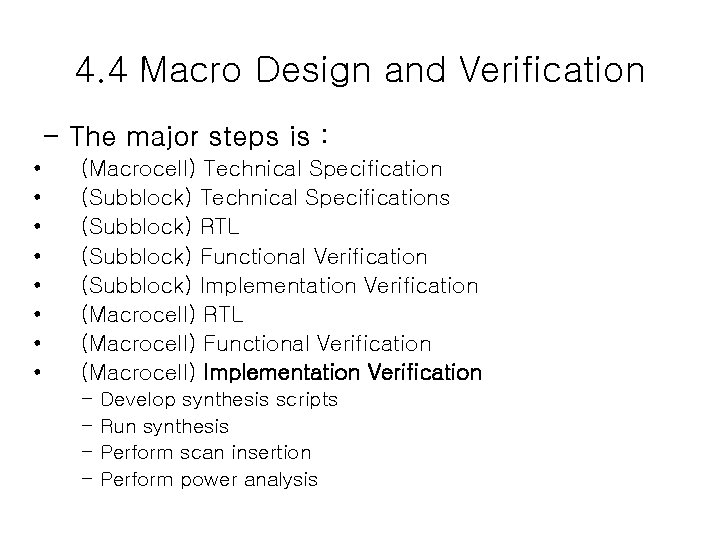

4. 4 Macro Design and Verification - The major steps is : • • (Macrocell) Technical Specification (Subblock) Technical Specifications (Subblock) RTL (Subblock) Functional Verification (Subblock) Implementation Verification (Macrocell) RTL (Macrocell) Functional Verification (Macrocell) Implementation Verification - Develop synthesis scripts Run synthesis Perform scan insertion Perform power analysis

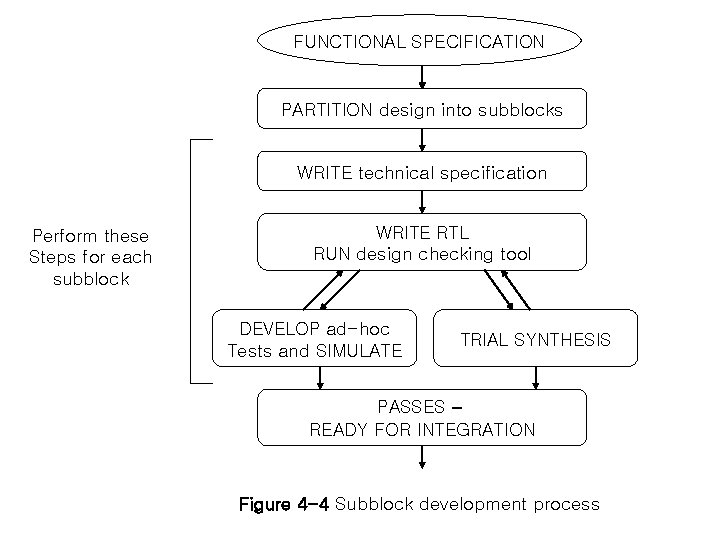

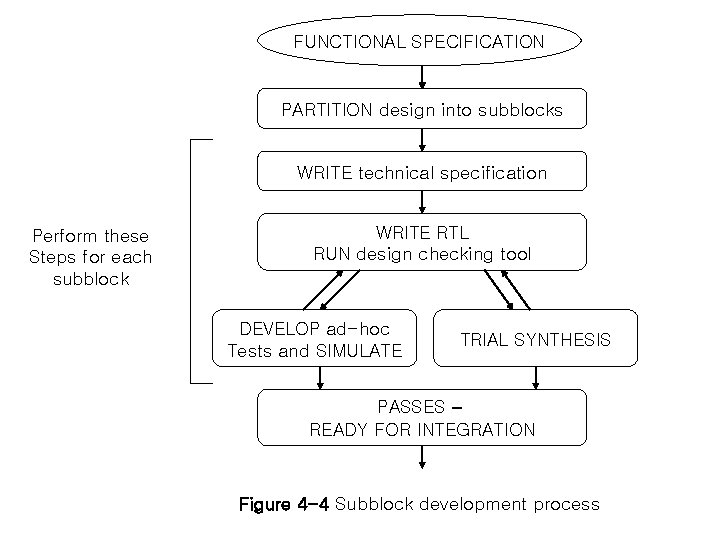

FUNCTIONAL SPECIFICATION PARTITION design into subblocks WRITE technical specification Perform these Steps for each subblock WRITE RTL RUN design checking tool DEVELOP ad-hoc Tests and SIMULATE TRIAL SYNTHESIS PASSES – READY FOR INTEGRATION Figure 4 -4 Subblock development process

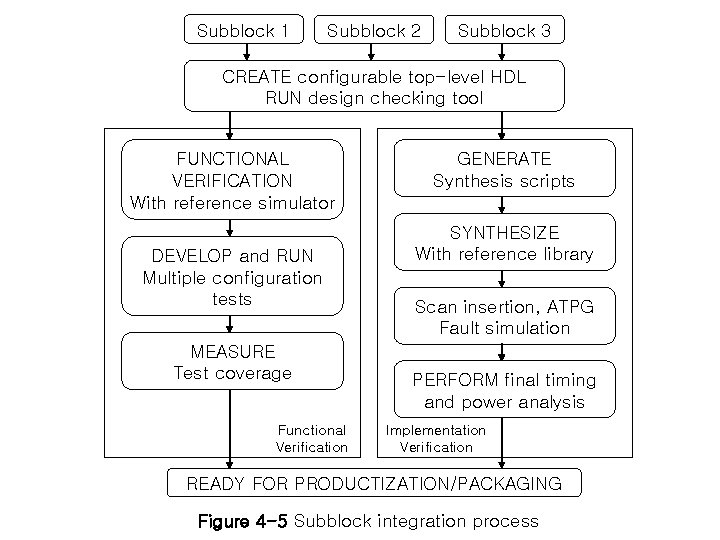

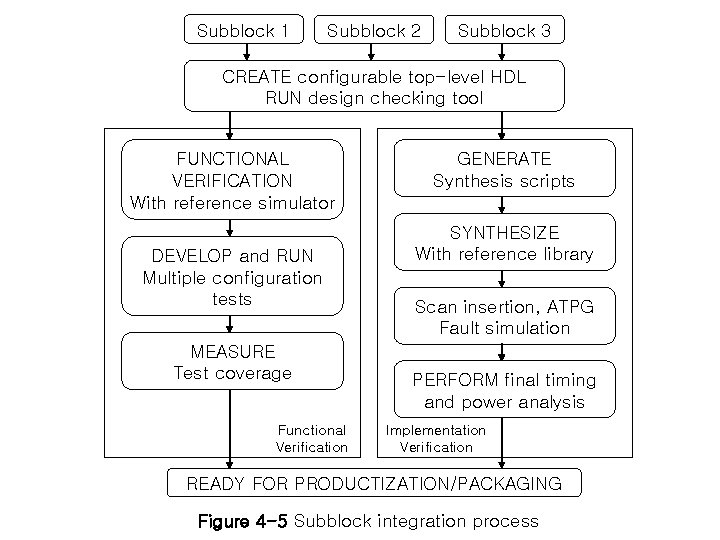

Subblock 1 Subblock 2 Subblock 3 CREATE configurable top-level HDL RUN design checking tool FUNCTIONAL VERIFICATION With reference simulator DEVELOP and RUN Multiple configuration tests MEASURE Test coverage Functional Verification GENERATE Synthesis scripts SYNTHESIZE With reference library Scan insertion, ATPG Fault simulation PERFORM final timing and power analysis Implementation Verification READY FOR PRODUCTIZATION/PACKAGING Figure 4 -5 Subblock integration process

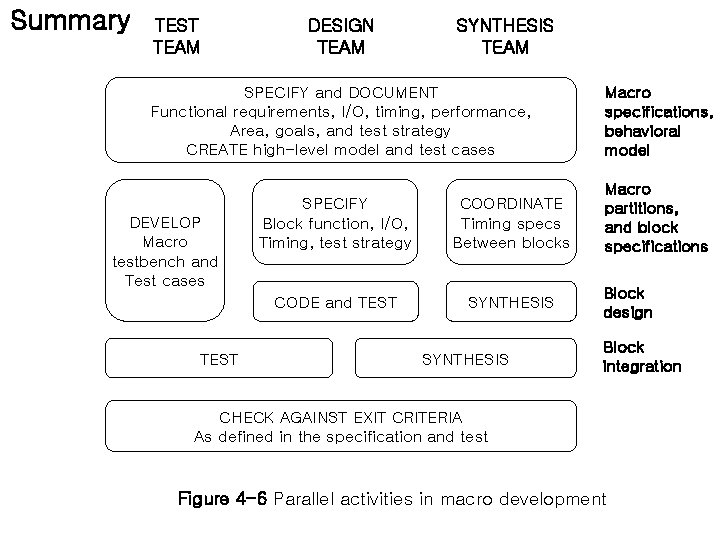

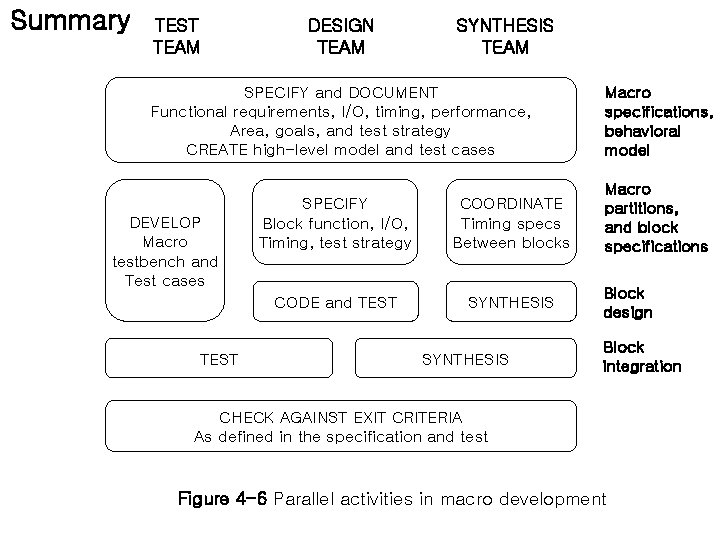

Summary TEST TEAM DESIGN TEAM SYNTHESIS TEAM SPECIFY and DOCUMENT Functional requirements, I/O, timing, performance, Area, goals, and test strategy CREATE high-level model and test cases DEVELOP Macro testbench and Test cases TEST SPECIFY Block function, I/O, Timing, test strategy COORDINATE Timing specs Between blocks CODE and TEST SYNTHESIS Macro specifications, behavioral model Macro partitions, and block specifications Block design Block integration CHECK AGAINST EXIT CRITERIA As defined in the specification and test Figure 4 -6 Parallel activities in macro development

4. 5 Soft Macro Productization The final phase of macro design consists of productizing the macro, which means creating the remaining deliverables. 1. Productization Process 2. Activities and Tools

4. 5. 1 Productization Process • • Versions of the code, testbenches, and tests that work in both Verilog and VHDL environments Supportion scripts for the design This includes the installation scripts and synthesis scripts required to build the different configurations of the macro. Documentation This includes updating all functional specifications and generating the final user documentation from them. Final version locked in a version control system All deliverables must be in a revision control system to allow future maintenance.

4. 5. 2 Activities and Tools 1. Develop a prototype chip : A prototype chip is esential for verifying both the robustness of the design and the correctness of the original specification • Verify that the design is functionally correct. • Verify that the design complies with the appropriate standards (for instance, we can take a PCI test chip to the PCI SIG for compliance testing). • Verify that the design is compatible with the kind of hardware/software environment that other integrators are likely to use

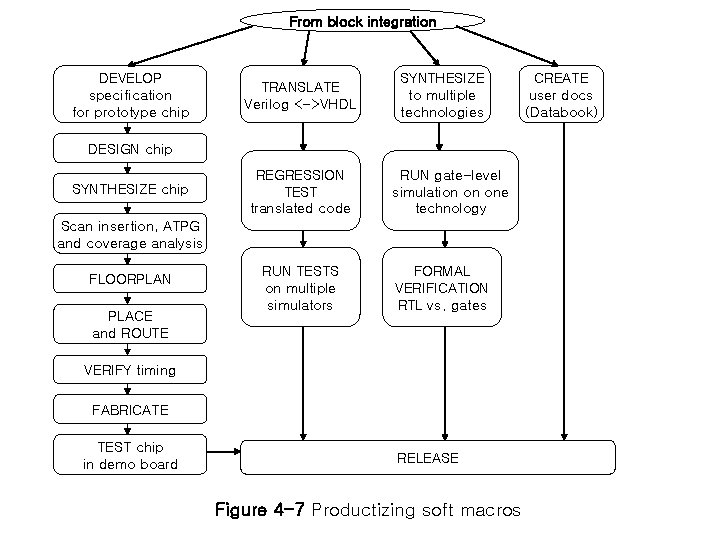

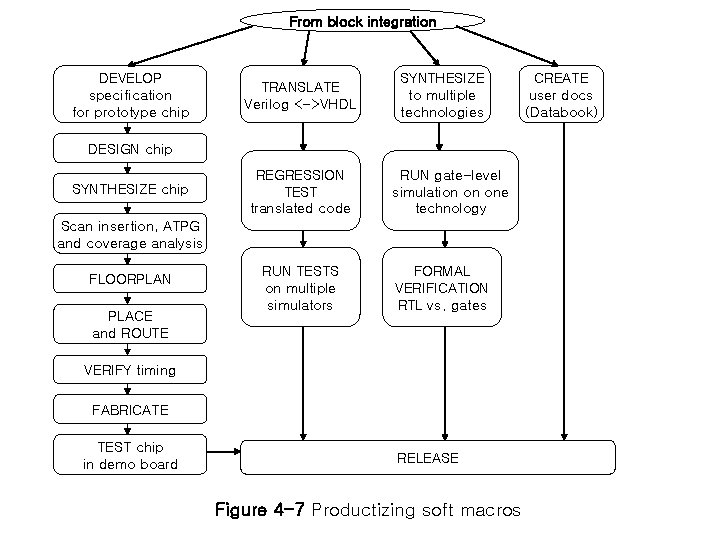

From block integration DEVELOP specification for prototype chip TRANSLATE Verilog <->VHDL SYNTHESIZE to multiple technologies DESIGN chip SYNTHESIZE chip REGRESSION TEST translated code RUN gate-level simulation on one technology Scan insertion, ATPG and coverage analysis FLOORPLAN PLACE and ROUTE RUN TESTS on multiple simulators FORMAL VERIFICATION RTL vs. gates VERIFY timing FABRICATE TEST chip in demo board RELEASE Figure 4 -7 Productizing soft macros CREATE user docs (Databook)

Productizing soft macros 2. Provide macro and testbench in both Verilog and VHDL 3. Test on several simulators 4. Synthesize on multiple technologies 5. Perform gate-level simulation 6. Formal verification 7. Create/update user documentation 8. Alpha testing and release

Productizing soft macros 8. Alpha testing and release - Once productization is complete, the macro is ready for alph testing - This testing is typically done by someone outside the design team. - Purpose of alpha testing is to test the usability of the final deliverables, especially the documentation. - Alpha testing involves designing the macro into a small kit, thus using the macro deliverables exactly as an integrator would.