Chapter 4 Sequential Statements Variable assignment statement Signal

Chapter 4 Sequential Statements ä ä ä Variable assignment statement Signal assignment statement If statement Case statement Loop statement Next statement 07 -Jun-21 EE 514 ä ä ä ä Exit statement Null statement Return statement Procedure call statement Assertion statement Wait statement Exercises 1

Null statement Null_statement: : =null; Note: Null is used to explicitly specify that no action is to be performed. This is especially useful in the case statement when no action is required for a choice. 07 -Jun-21 EE 514 2

![Return statement Return_statement: : =return [expression]; Note: A return statement is used to complete Return statement Return_statement: : =return [expression]; Note: A return statement is used to complete](http://slidetodoc.com/presentation_image_h2/5bb3476ef4f16206c5836c2fd63953f1/image-3.jpg)

Return statement Return_statement: : =return [expression]; Note: A return statement is used to complete the execution of the innermost enclosing function or procedure body. It is allowed only within the body of a function or a procedure. 07 -Jun-21 EE 514 3

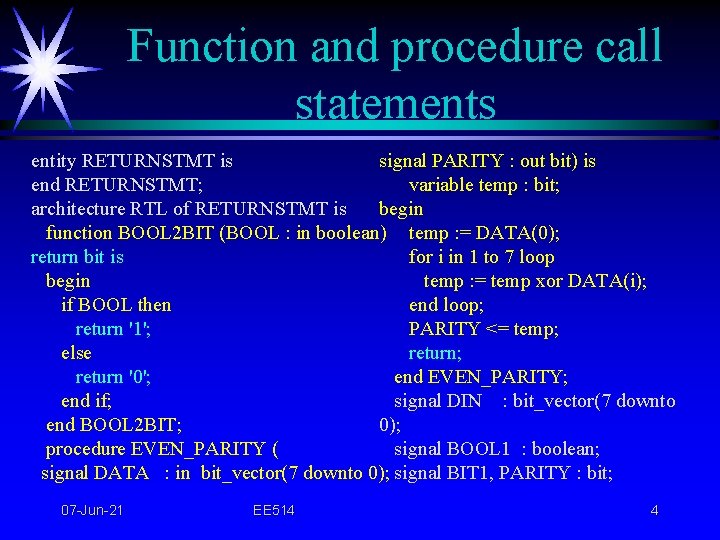

Function and procedure call statements entity RETURNSTMT is signal PARITY : out bit) is end RETURNSTMT; variable temp : bit; architecture RTL of RETURNSTMT is begin function BOOL 2 BIT (BOOL : in boolean) temp : = DATA(0); return bit is for i in 1 to 7 loop begin temp : = temp xor DATA(i); if BOOL then end loop; return '1'; PARITY <= temp; else return; return '0'; end EVEN_PARITY; end if; signal DIN : bit_vector(7 downto end BOOL 2 BIT; 0); procedure EVEN_PARITY ( signal BOOL 1 : boolean; signal DATA : in bit_vector(7 downto 0); signal BIT 1, PARITY : bit; 07 -Jun-21 EE 514 4

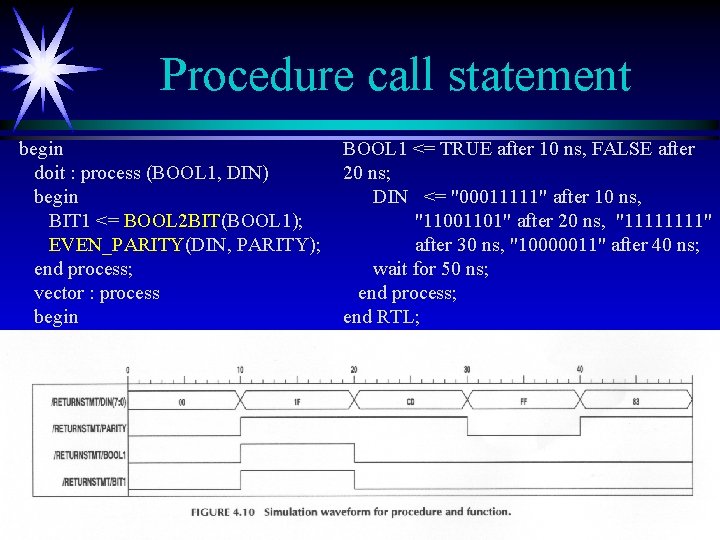

Procedure call statement begin doit : process (BOOL 1, DIN) begin BIT 1 <= BOOL 2 BIT(BOOL 1); EVEN_PARITY(DIN, PARITY); end process; vector : process begin 07 -Jun-21 EE 514 BOOL 1 <= TRUE after 10 ns, FALSE after 20 ns; DIN <= "00011111" after 10 ns, "11001101" after 20 ns, "1111" after 30 ns, "10000011" after 40 ns; wait for 50 ns; end process; end RTL; 5

![Assertion statement assertion_statement: : =assert condition [report expression][severity expression]; Note: The report expression is Assertion statement assertion_statement: : =assert condition [report expression][severity expression]; Note: The report expression is](http://slidetodoc.com/presentation_image_h2/5bb3476ef4f16206c5836c2fd63953f1/image-6.jpg)

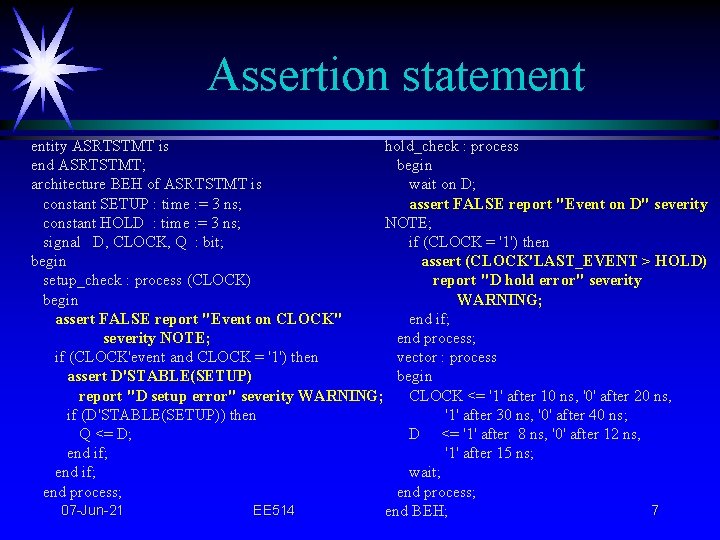

Assertion statement assertion_statement: : =assert condition [report expression][severity expression]; Note: The report expression is an expression of a STRING type to be reported. The severity expression is an enumerated type with four values NOTE, WARNING, ERROR and FAILURE. The default severity level is ERROR if the severity clause is not specified. 07 -Jun-21 EE 514 6

Assertion statement entity ASRTSTMT is hold_check : process end ASRTSTMT; begin architecture BEH of ASRTSTMT is wait on D; constant SETUP : time : = 3 ns; assert FALSE report "Event on D" severity constant HOLD : time : = 3 ns; NOTE; signal D, CLOCK, Q : bit; if (CLOCK = '1') then begin assert (CLOCK'LAST_EVENT > HOLD) setup_check : process (CLOCK) report "D hold error" severity begin WARNING; assert FALSE report "Event on CLOCK" end if; severity NOTE; end process; if (CLOCK'event and CLOCK = '1') then vector : process assert D'STABLE(SETUP) begin report "D setup error" severity WARNING; CLOCK <= '1' after 10 ns, '0' after 20 ns, if (D'STABLE(SETUP)) then '1' after 30 ns, '0' after 40 ns; Q <= D; D <= '1' after 8 ns, '0' after 12 ns, end if; '1' after 15 ns; end if; wait; end process; 07 -Jun-21 EE 514 7 end BEH;

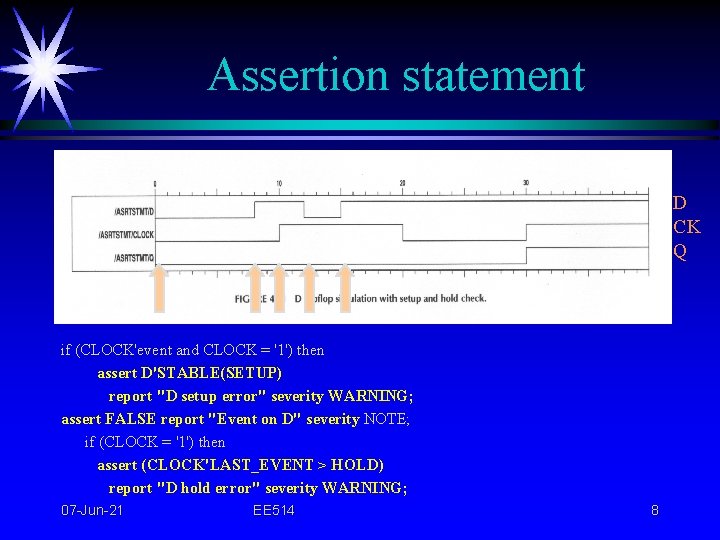

Assertion statement D CK Q if (CLOCK'event and CLOCK = '1') then assert D'STABLE(SETUP) report "D setup error" severity WARNING; assert FALSE report "Event on D" severity NOTE; if (CLOCK = '1') then assert (CLOCK'LAST_EVENT > HOLD) report "D hold error" severity WARNING; 07 -Jun-21 EE 514 8

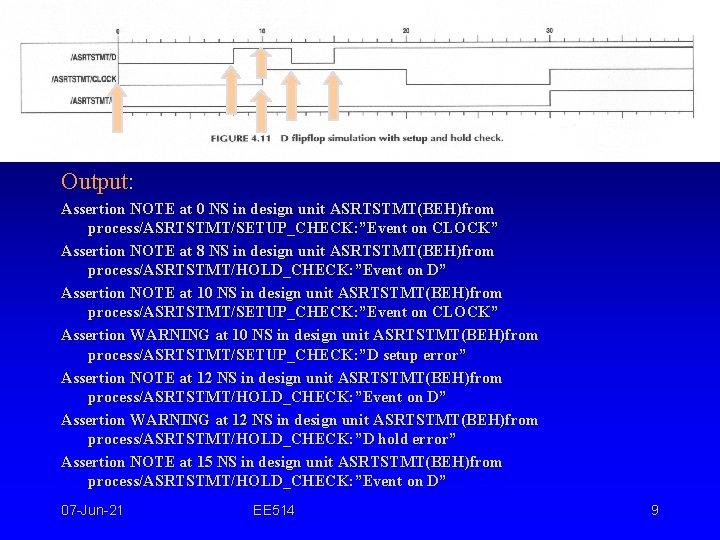

Assertion statement Output: Assertion NOTE at 0 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/SETUP_CHECK: ”Event on CLOCK” Assertion NOTE at 8 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/HOLD_CHECK: ”Event on D” Assertion NOTE at 10 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/SETUP_CHECK: ”Event on CLOCK” Assertion WARNING at 10 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/SETUP_CHECK: ”D setup error” Assertion NOTE at 12 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/HOLD_CHECK: ”Event on D” Assertion WARNING at 12 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/HOLD_CHECK: ”D hold error” Assertion NOTE at 15 NS in design unit ASRTSTMT(BEH)from process/ASRTSTMT/HOLD_CHECK: ”Event on D” 07 -Jun-21 EE 514 9

![Wait statement wait_statement: : =wait [sensitivity_clause][conditional_clause] [timout_clause]; sensitivity_clause: : =on sensitivity_list conditional_clause: : =until Wait statement wait_statement: : =wait [sensitivity_clause][conditional_clause] [timout_clause]; sensitivity_clause: : =on sensitivity_list conditional_clause: : =until](http://slidetodoc.com/presentation_image_h2/5bb3476ef4f16206c5836c2fd63953f1/image-10.jpg)

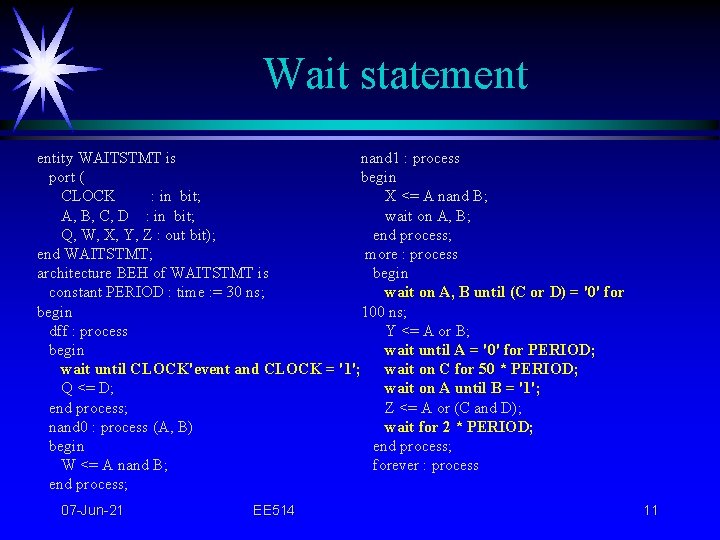

Wait statement wait_statement: : =wait [sensitivity_clause][conditional_clause] [timout_clause]; sensitivity_clause: : =on sensitivity_list conditional_clause: : =until boolean_expression timout_clause: : =for time_expression 07 -Jun-21 EE 514 10

Wait statement entity WAITSTMT is nand 1 : process port ( begin CLOCK : in bit; X <= A nand B; A, B, C, D : in bit; wait on A, B; Q, W, X, Y, Z : out bit); end process; end WAITSTMT; more : process architecture BEH of WAITSTMT is begin constant PERIOD : time : = 30 ns; wait on A, B until (C or D) = '0' for begin 100 ns; dff : process Y <= A or B; begin wait until A = '0' for PERIOD; wait until CLOCK'event and CLOCK = '1'; wait on C for 50 * PERIOD; Q <= D; wait on A until B = '1'; end process; Z <= A or (C and D); nand 0 : process (A, B) wait for 2 * PERIOD; begin end process; W <= A nand B; forever : process end process; 07 -Jun-21 EE 514 11

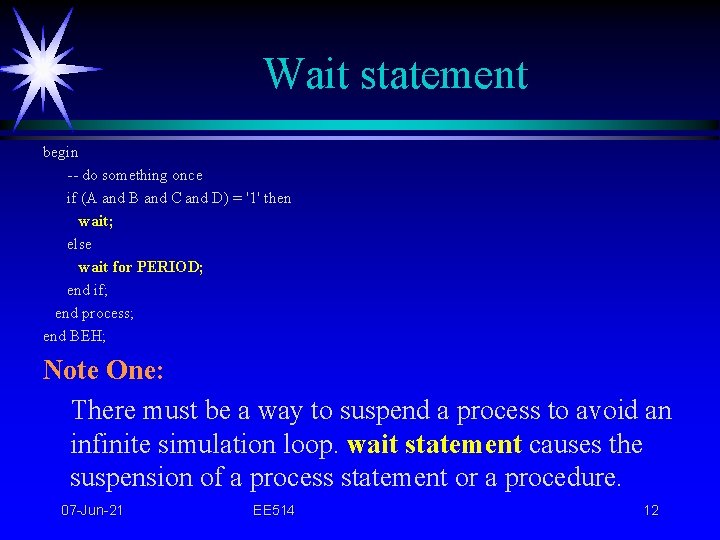

Wait statement begin -- do something once if (A and B and C and D) = '1' then wait; else wait for PERIOD; end if; end process; end BEH; Note One: There must be a way to suspend a process to avoid an infinite simulation loop. wait statement causes the suspension of a process statement or a procedure. 07 -Jun-21 EE 514 12

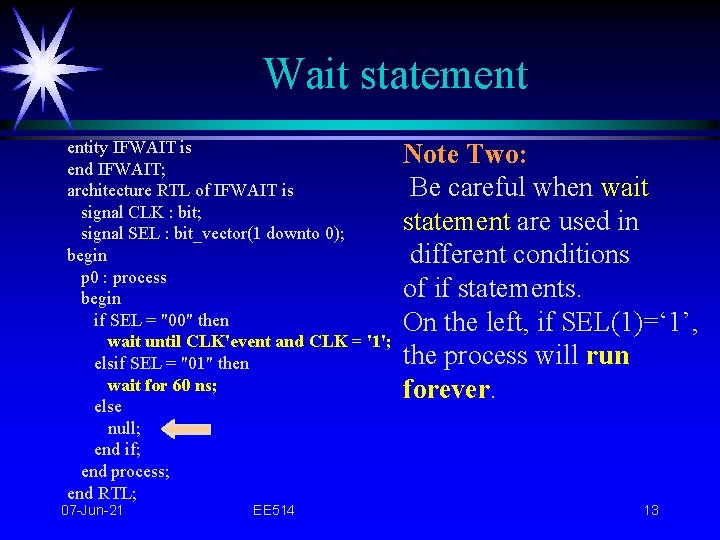

Wait statement entity IFWAIT is end IFWAIT; architecture RTL of IFWAIT is signal CLK : bit; signal SEL : bit_vector(1 downto 0); begin p 0 : process begin if SEL = "00" then wait until CLK'event and CLK = '1'; elsif SEL = "01" then wait for 60 ns; else null; end if; end process; end RTL; 07 -Jun-21 EE 514 Note Two: Be careful when wait statement are used in different conditions of if statements. On the left, if SEL(1)=‘ 1’, the process will run forever. 13

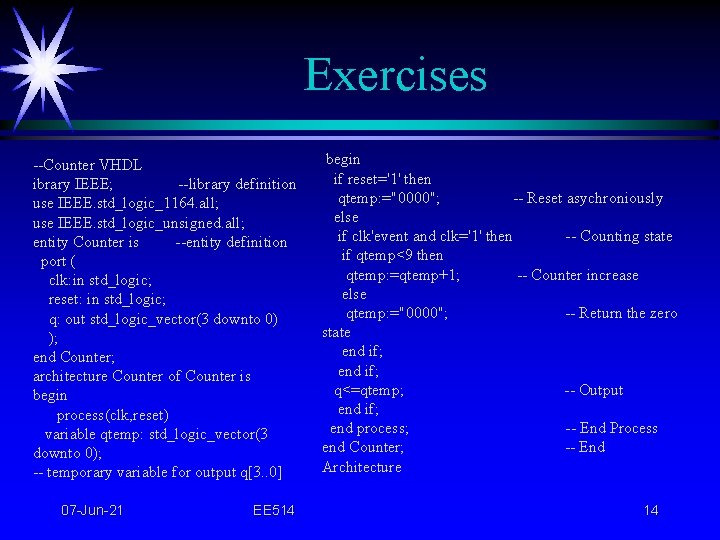

Exercises --Counter VHDL ibrary IEEE; --library definition use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity Counter is --entity definition port ( clk: in std_logic; reset: in std_logic; q: out std_logic_vector(3 downto 0) ); end Counter; architecture Counter of Counter is begin process(clk, reset) variable qtemp: std_logic_vector(3 downto 0); -- temporary variable for output q[3. . 0] 07 -Jun-21 EE 514 begin if reset='1' then qtemp: ="0000"; -- Reset asychroniously else if clk'event and clk='1' then -- Counting state if qtemp<9 then qtemp: =qtemp+1; -- Counter increase else qtemp: ="0000"; -- Return the zero state end if; q<=qtemp; -- Output end if; end process; -- End Process end Counter; -- End Architecture 14

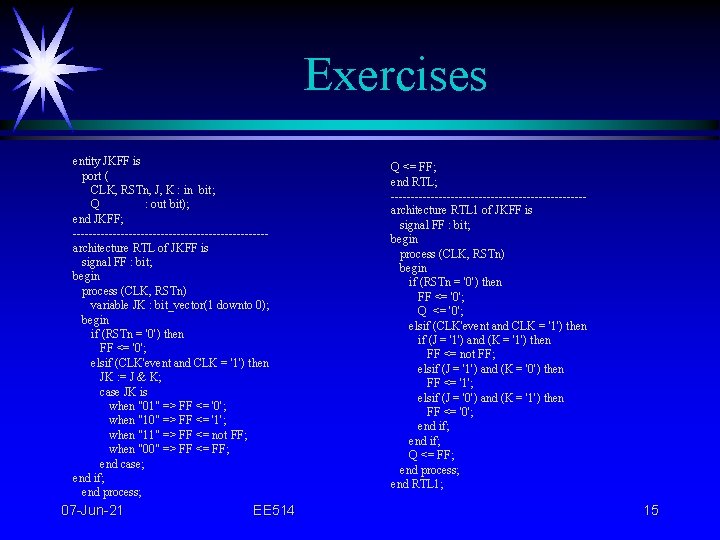

Exercises entity JKFF is port ( CLK, RSTn, J, K : in bit; Q : out bit); end JKFF; ------------------------architecture RTL of JKFF is signal FF : bit; begin process (CLK, RSTn) variable JK : bit_vector(1 downto 0); begin if (RSTn = '0') then FF <= '0'; elsif (CLK'event and CLK = '1') then JK : = J & K; case JK is when "01" => FF <= '0'; when "10" => FF <= '1'; when "11" => FF <= not FF; when "00" => FF <= FF; end case; end if; end process; 07 -Jun-21 EE 514 Q <= FF; end RTL; ------------------------architecture RTL 1 of JKFF is signal FF : bit; begin process (CLK, RSTn) begin if (RSTn = '0') then FF <= '0'; Q <= '0'; elsif (CLK'event and CLK = '1') then if (J = '1') and (K = '1') then FF <= not FF; elsif (J = '1') and (K = '0') then FF <= '1'; elsif (J = '0') and (K = '1') then FF <= '0'; end if; Q <= FF; end process; end RTL 1; 15

- Slides: 15