Chapter 4 Machine Structure and Instruction Format in

- Slides: 21

Chapter 4 Machine Structure and Instruction Format in MC 68000

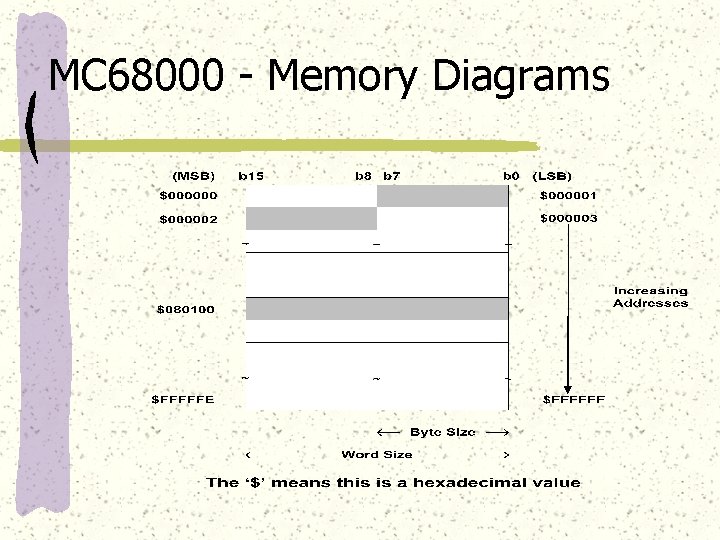

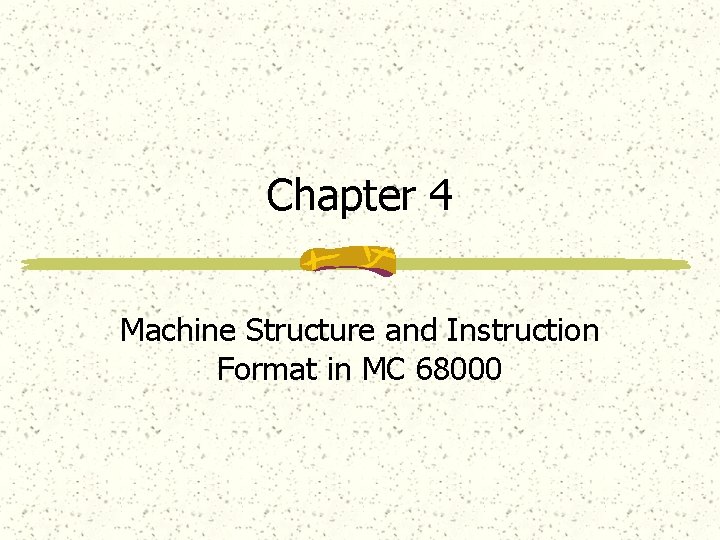

MC 68000 - Memory Diagrams

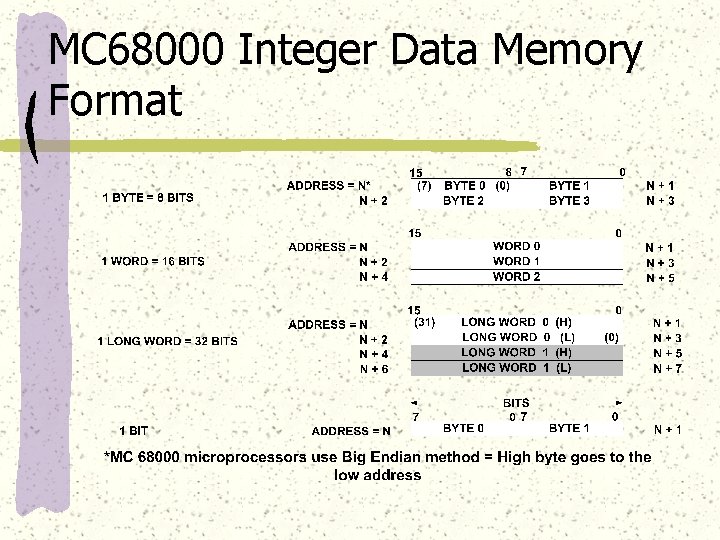

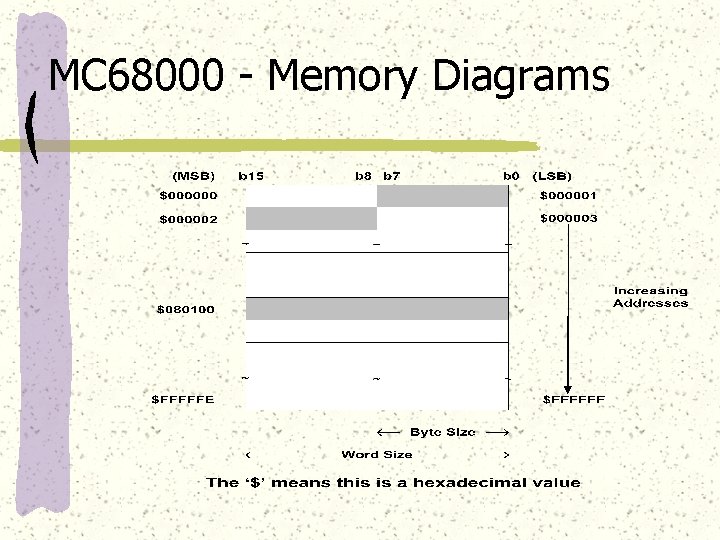

MC 68000 Integer Data Memory Format

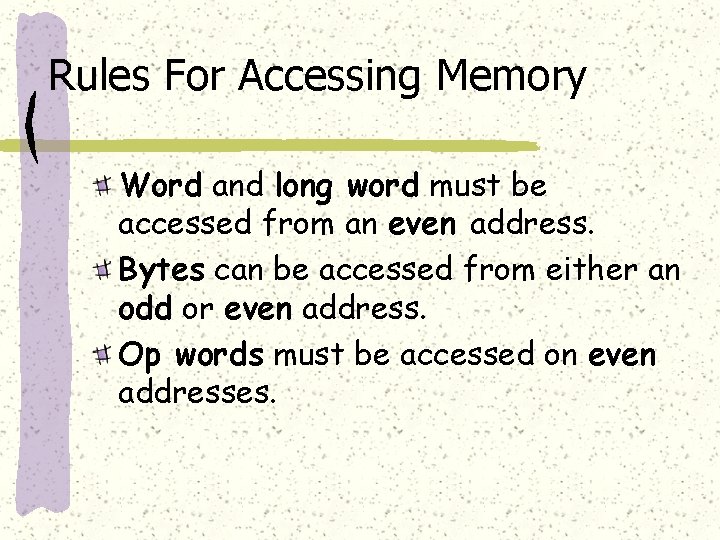

Rules For Accessing Memory Word and long word must be accessed from an even address. Bytes can be accessed from either an odd or even address. Op words must be accessed on even addresses.

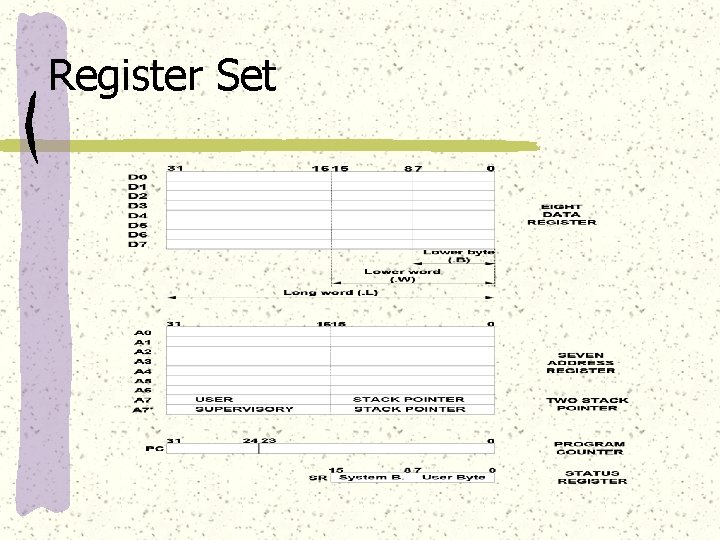

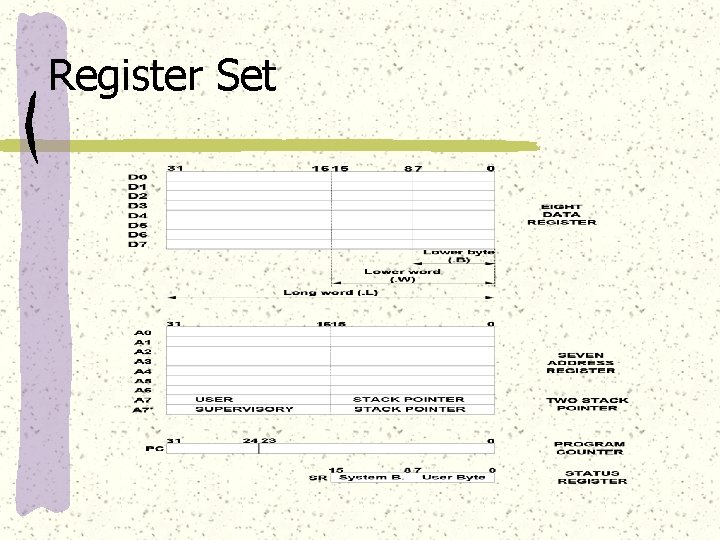

Register Set

Data Register The register set is divided into two groups, the data register and address register. There are eight data register denoted by D 0 -D 7. Each can be used as a source or destination operand.

Address Register & Stack Pointer The address register (A 0 -A 6) are primarily for generating memory operand addresses. An address register cannot be referenced as a byte operand. Two stack pointer (A 7) are the supervisor stack pointer (SSP) and user stack pointer (USP). Only one stack pointer will active in one time.

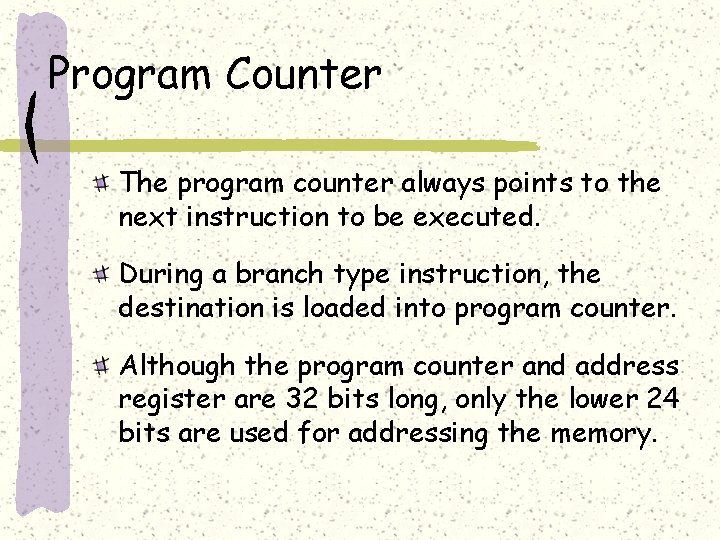

Program Counter The program counter always points to the next instruction to be executed. During a branch type instruction, the destination is loaded into program counter. Although the program counter and address register are 32 bits long, only the lower 24 bits are used for addressing the memory.

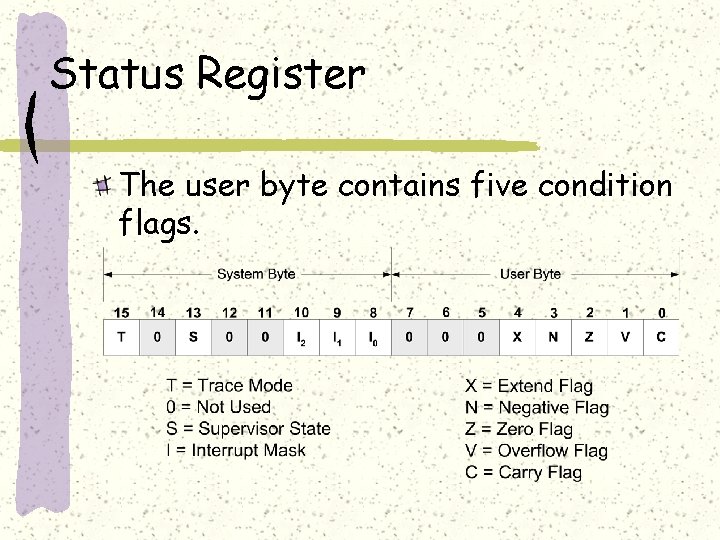

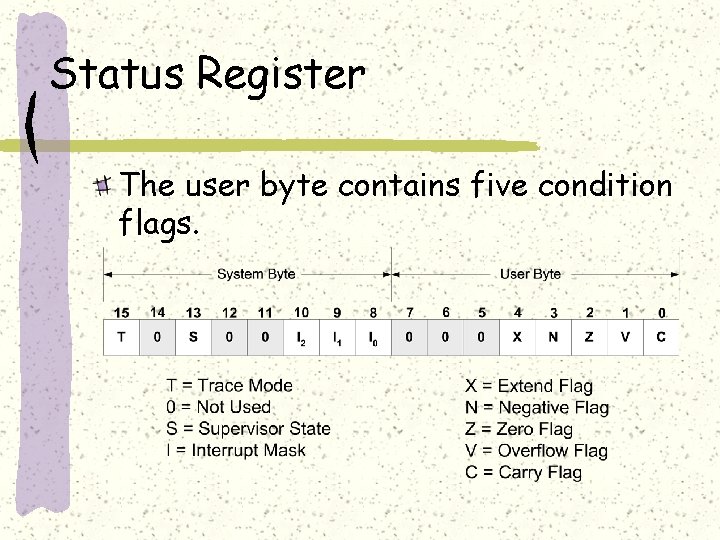

Status Register The user byte contains five condition flags.

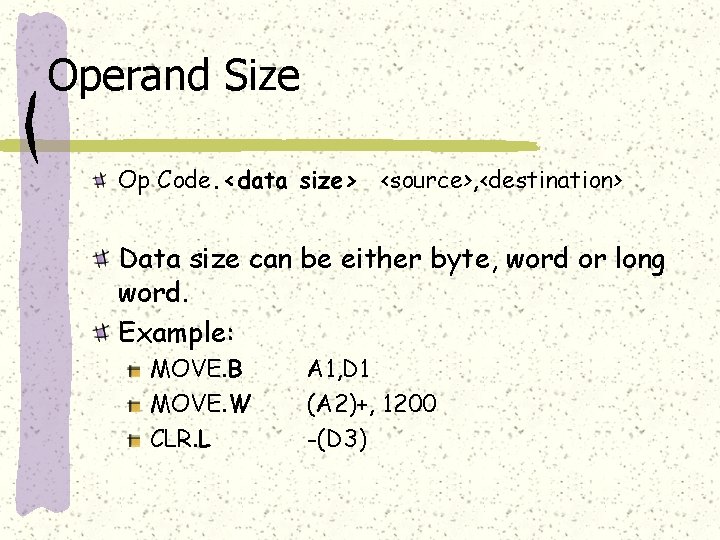

Operand Size Op Code. <data size> <source>, <destination> Data size can be either byte, word or long word. Example: MOVE. B MOVE. W CLR. L A 1, D 1 (A 2)+, 1200 -(D 3)

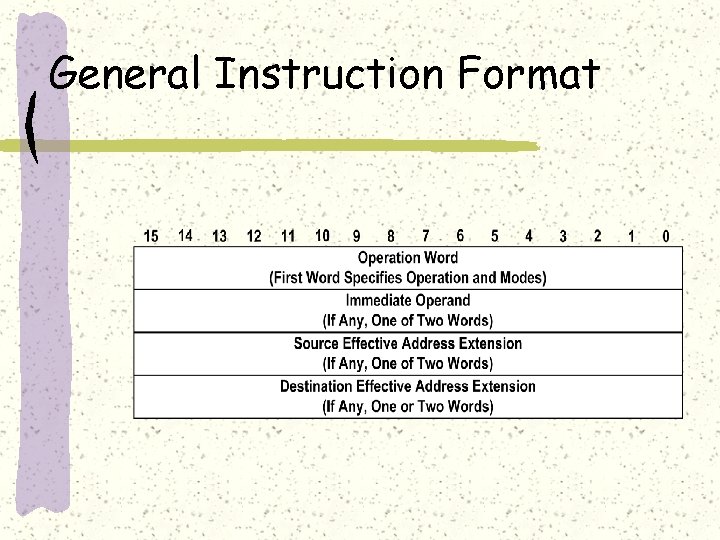

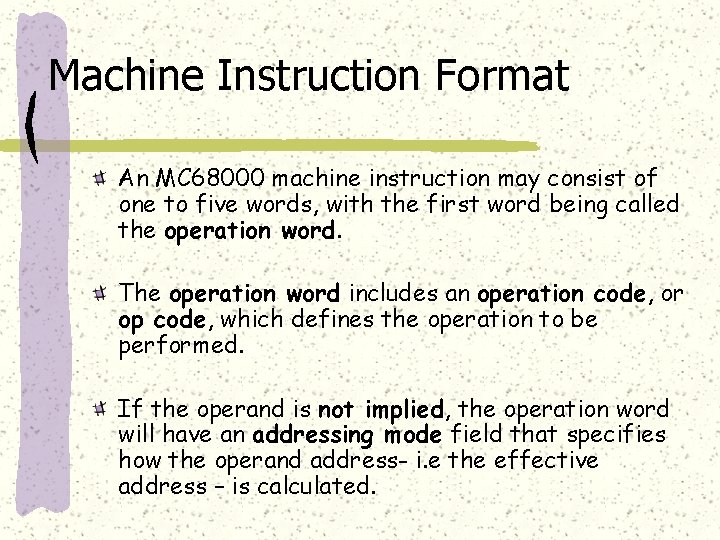

Machine Instruction Format An MC 68000 machine instruction may consist of one to five words, with the first word being called the operation word. The operation word includes an operation code, or op code, which defines the operation to be performed. If the operand is not implied, the operation word will have an addressing mode field that specifies how the operand address- i. e the effective address – is calculated.

Machine Instruction Format… Additional indicators such as operation size and second operand may also be included for some instructions. For those addressing modes that required additional information – i. e. , immediate data, an index register, or a displacementthe operation word is followed by one or more extension words, which are considered as part of the instruction.

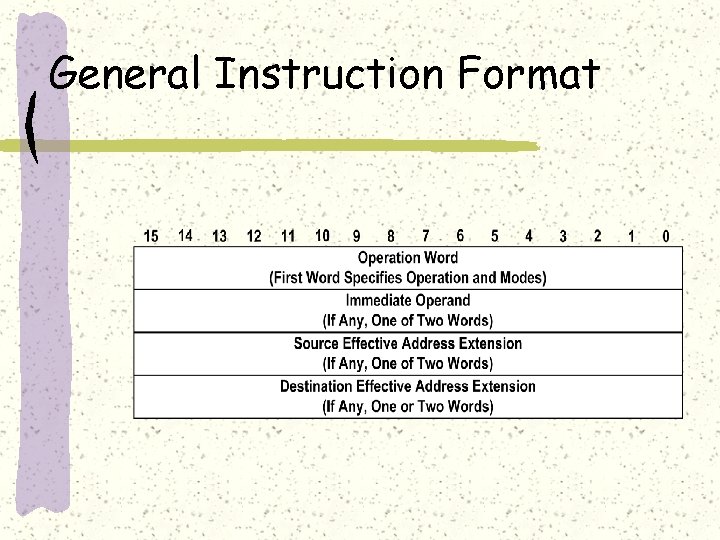

General Instruction Format

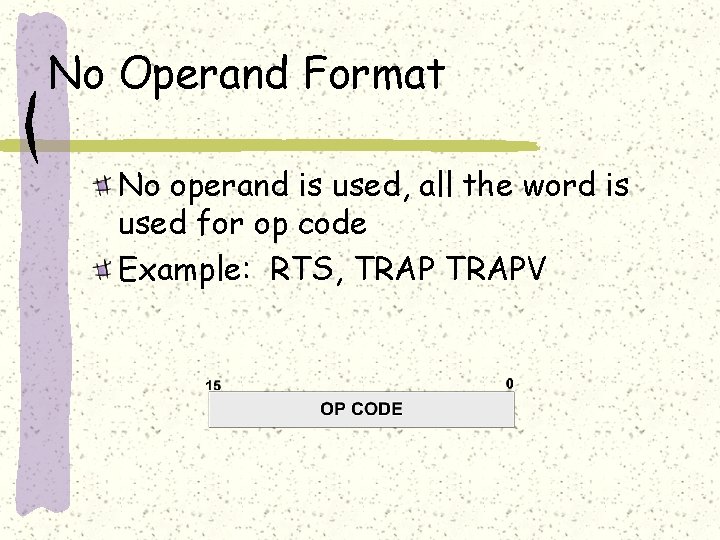

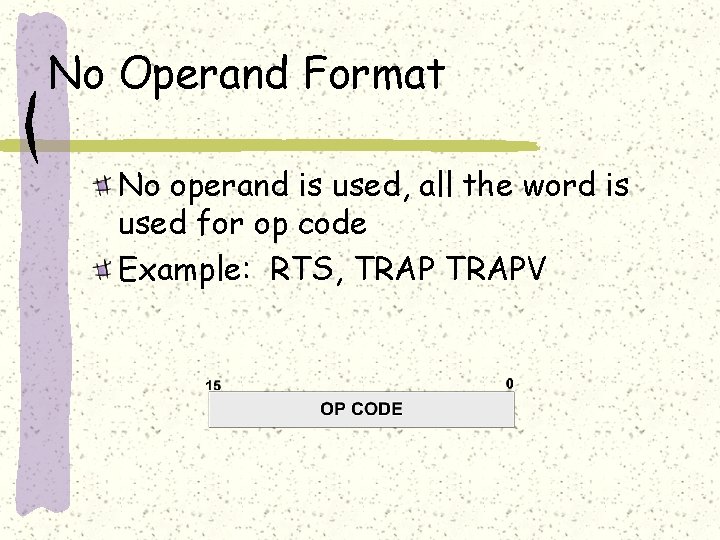

No Operand Format No operand is used, all the word is used for op code Example: RTS, TRAPV

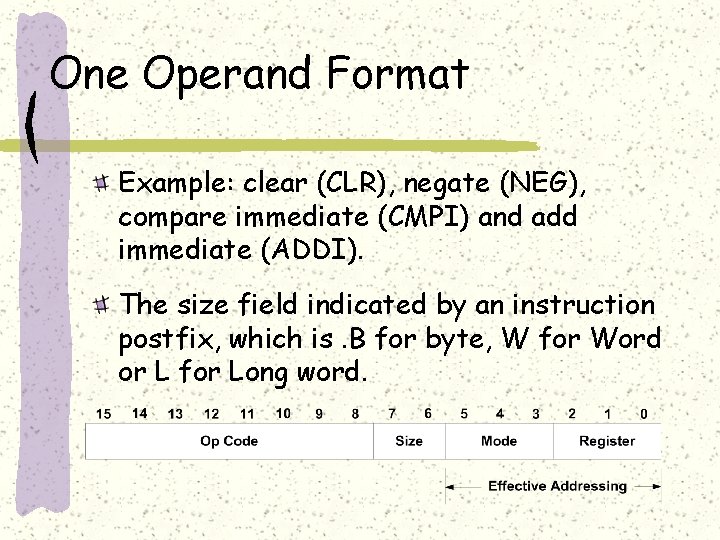

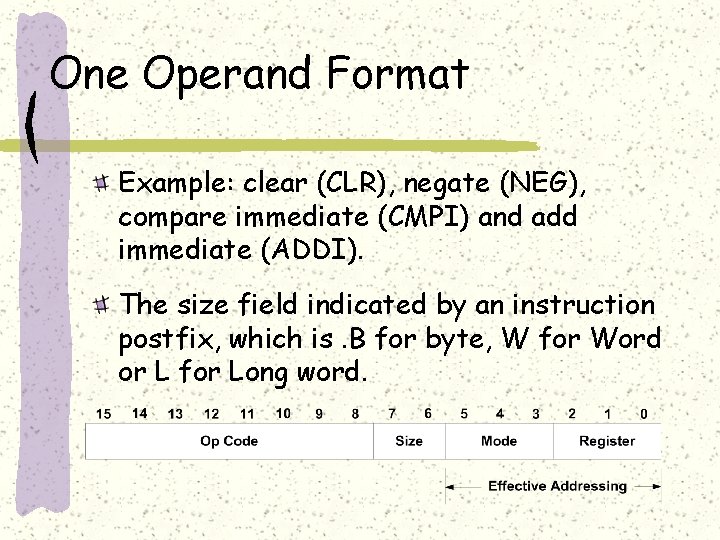

One Operand Format Example: clear (CLR), negate (NEG), compare immediate (CMPI) and add immediate (ADDI). The size field indicated by an instruction postfix, which is. B for byte, W for Word or L for Long word.

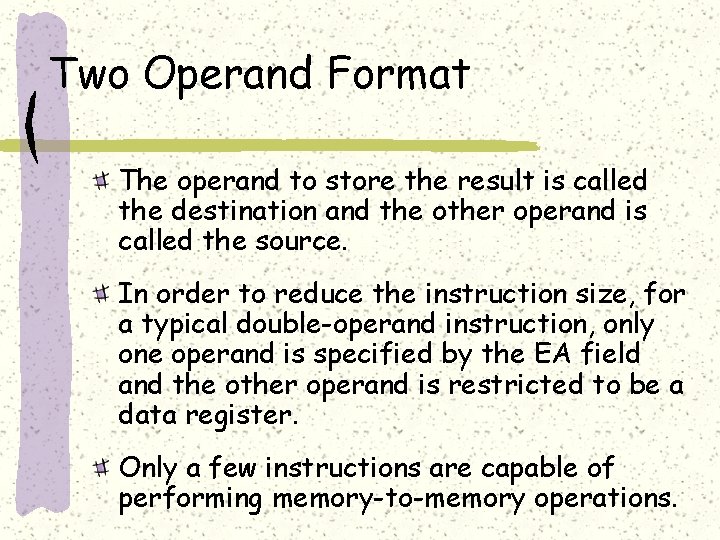

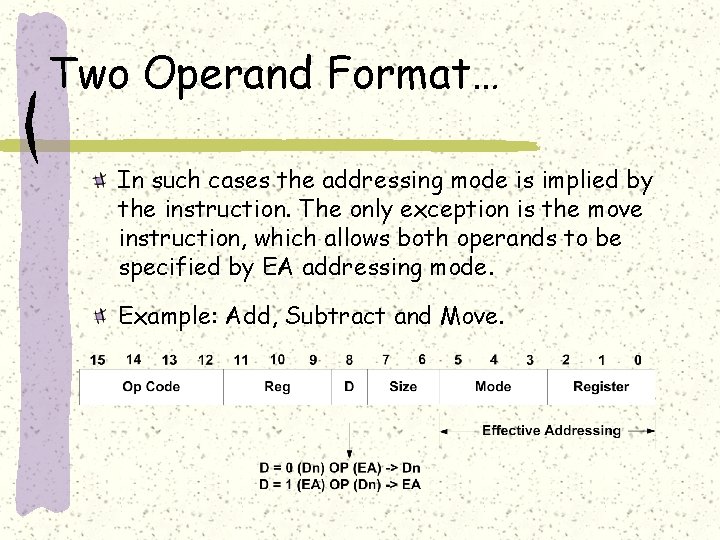

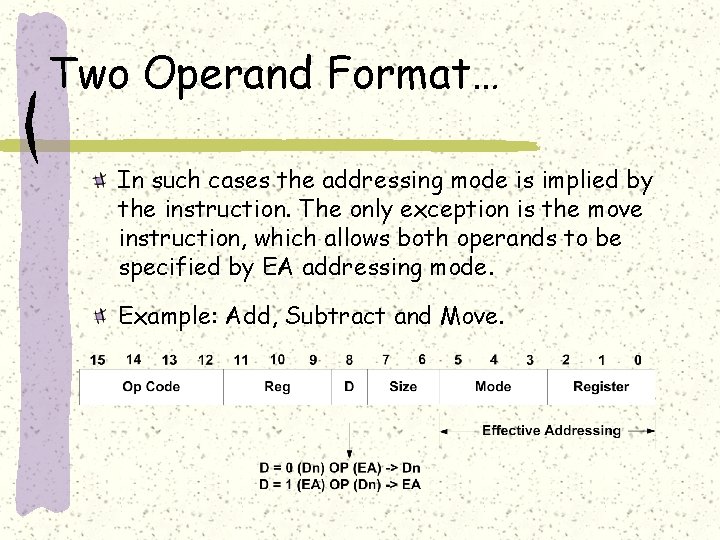

Two Operand Format The operand to store the result is called the destination and the other operand is called the source. In order to reduce the instruction size, for a typical double-operand instruction, only one operand is specified by the EA field and the other operand is restricted to be a data register. Only a few instructions are capable of performing memory-to-memory operations.

Two Operand Format… In such cases the addressing mode is implied by the instruction. The only exception is the move instruction, which allows both operands to be specified by EA addressing mode. Example: Add, Subtract and Move.

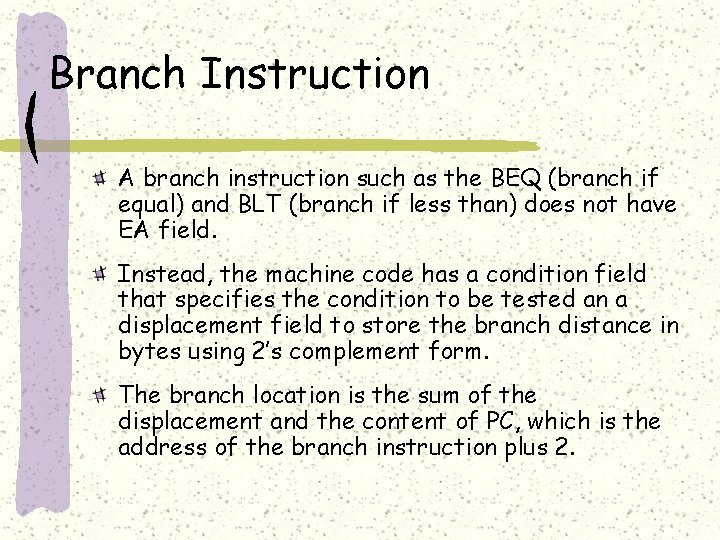

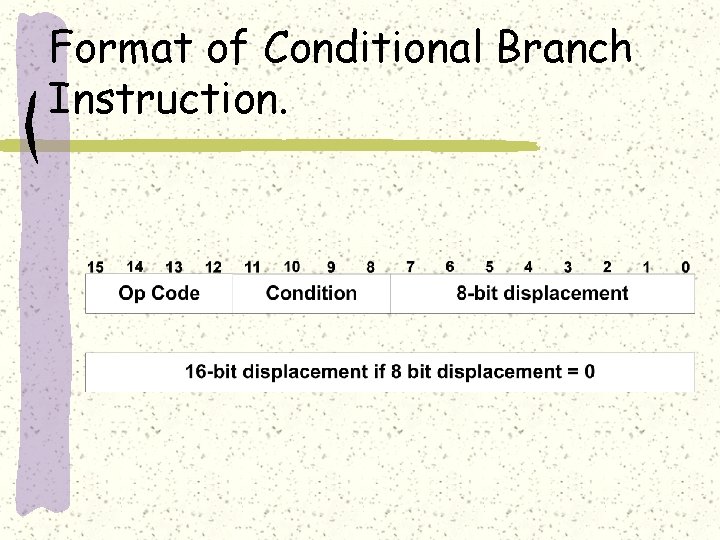

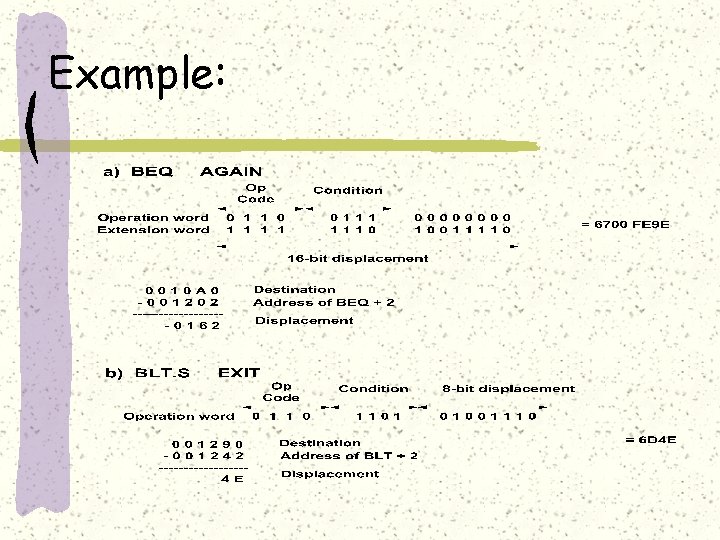

Branch Instruction A branch instruction such as the BEQ (branch if equal) and BLT (branch if less than) does not have EA field. Instead, the machine code has a condition field that specifies the condition to be tested an a displacement field to store the branch distance in bytes using 2’s complement form. The branch location is the sum of the displacement and the content of PC, which is the address of the branch instruction plus 2.

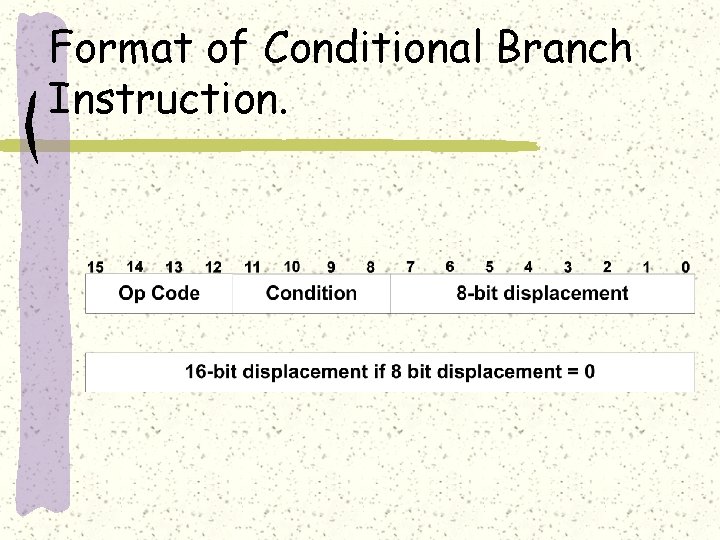

Format of Conditional Branch Instruction.

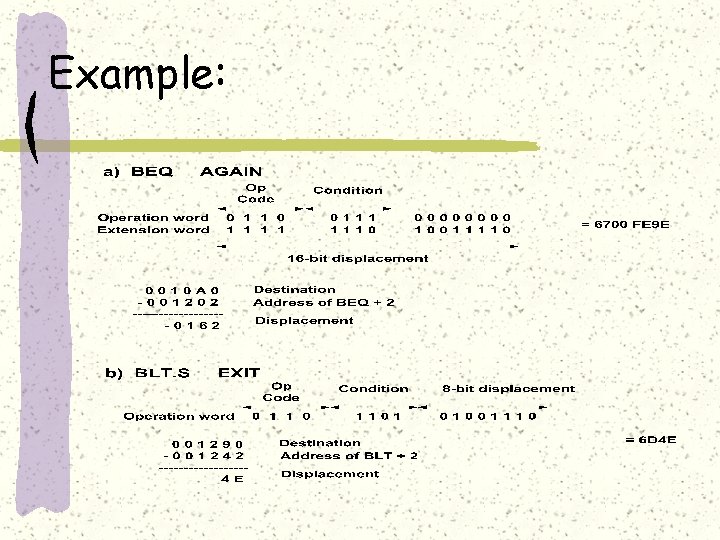

Example:

Effective Address Most instructions operate on an effective address <ea>. The <ea> is supplied as a part of the instruction, by the programmer. The <ea> is specified by the addressing mode, encoded in the operation word.