Chapter 4 Interrupts Serial Communication 8051 Microcontroller Prof

- Slides: 23

Chapter 4: Interrupts & Serial Communication 8051 Microcontroller Prof. Swati A. Thete J. E. S. I. T. M. R. Nashik 330_02 1

Unit-4 : 8051 -Interrupts z. Interrupts- timer flag interrupt, serial port interrupt, external interrupts, software generated, interrupt control and interrupt programming. z Serial communication and its programming. z. Serial data input, output, Serial data modes, interfacing of 8051 with PC through RS 232. 2

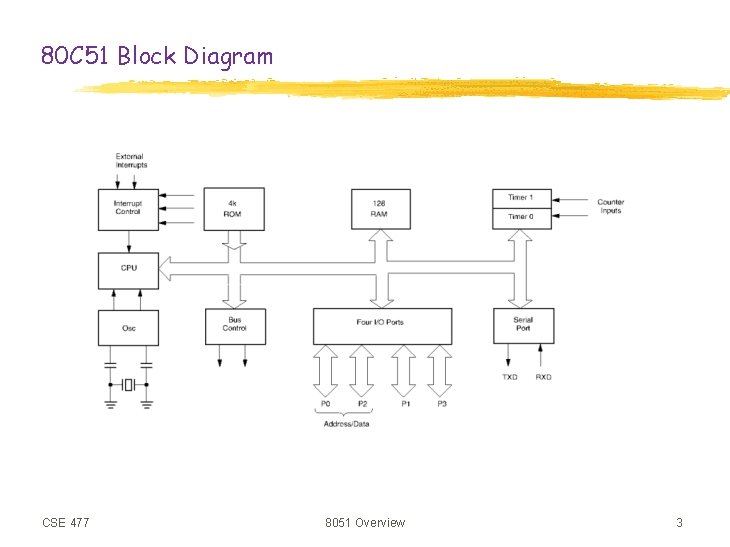

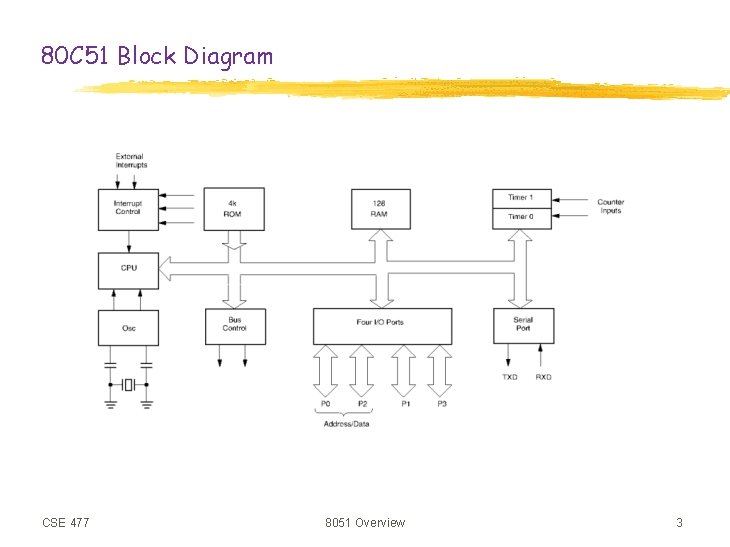

80 C 51 Block Diagram CSE 477 8051 Overview 3

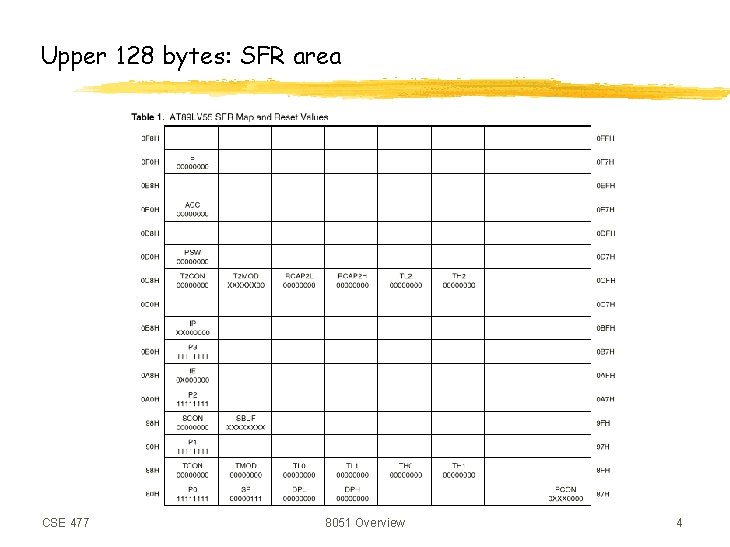

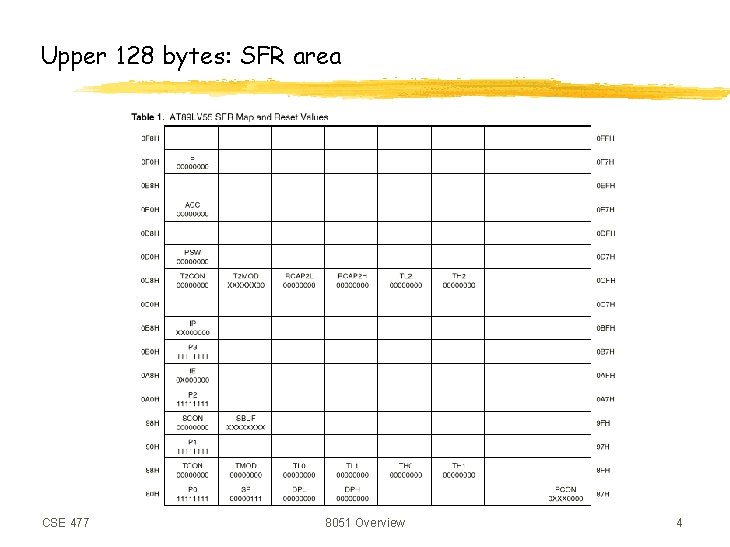

Upper 128 bytes: SFR area CSE 477 8051 Overview 4

Interrupts Definition of ‘Interrupt’ Event that disrupts the normal execution of a program and causes the execution of special instructions UBC 104 Embedded Systems 5

Interrupts Program time t UBC 104 Embedded Systems 6

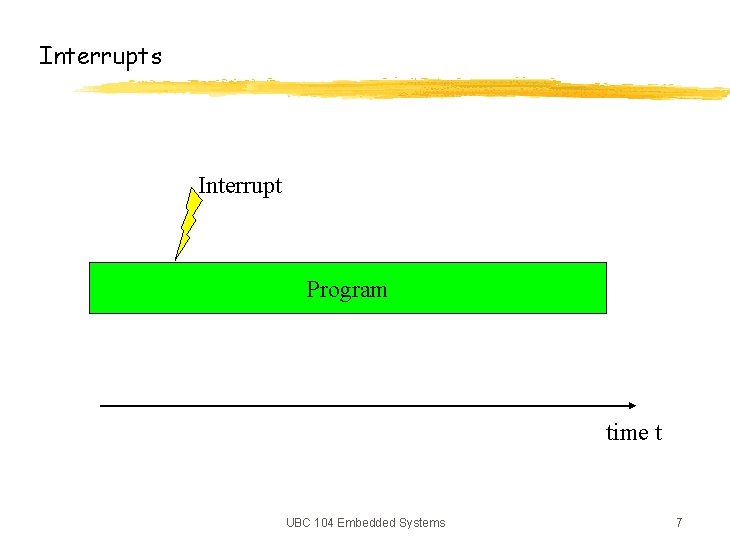

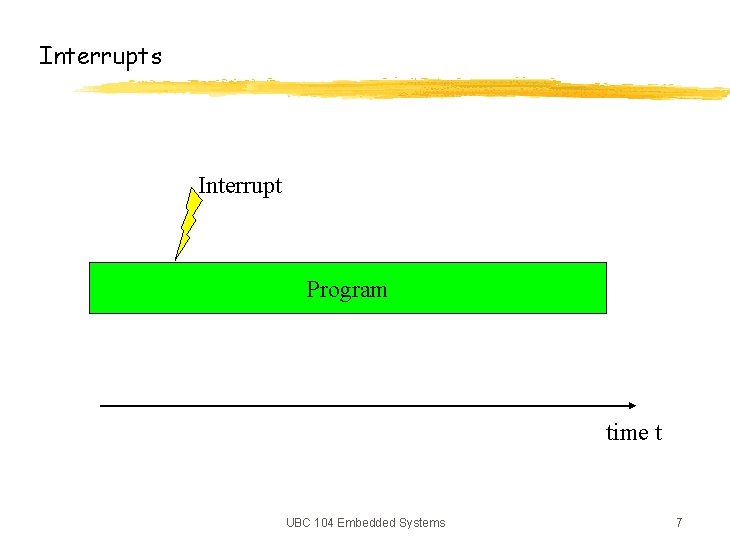

Interrupts Interrupt Program time t UBC 104 Embedded Systems 7

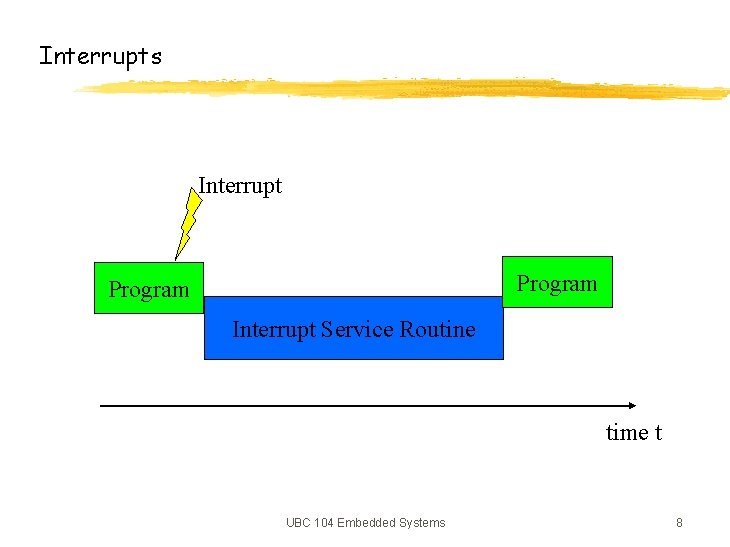

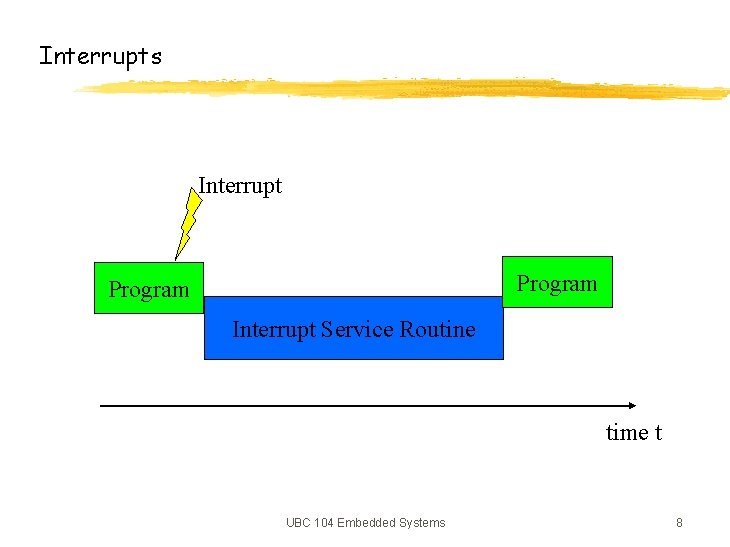

Interrupts Interrupt Program Interrupt Service Routine time t UBC 104 Embedded Systems 8

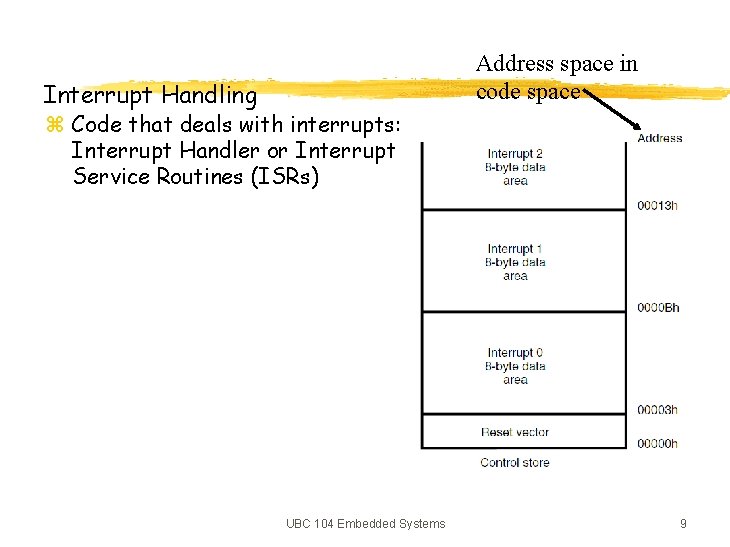

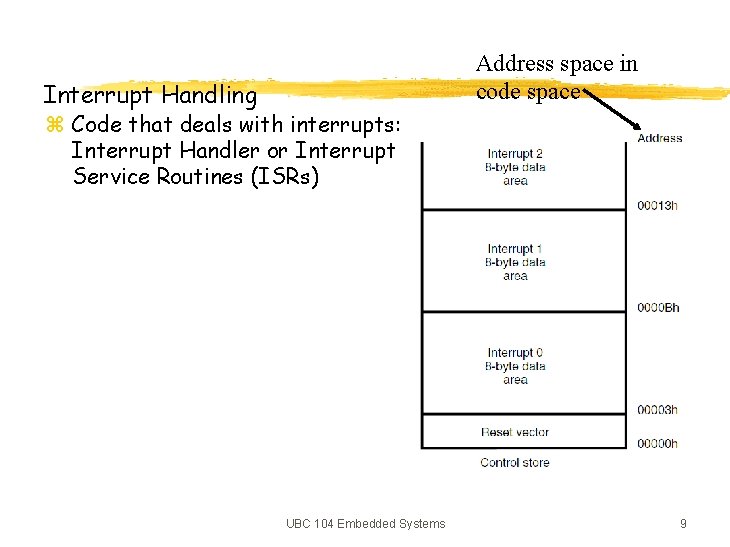

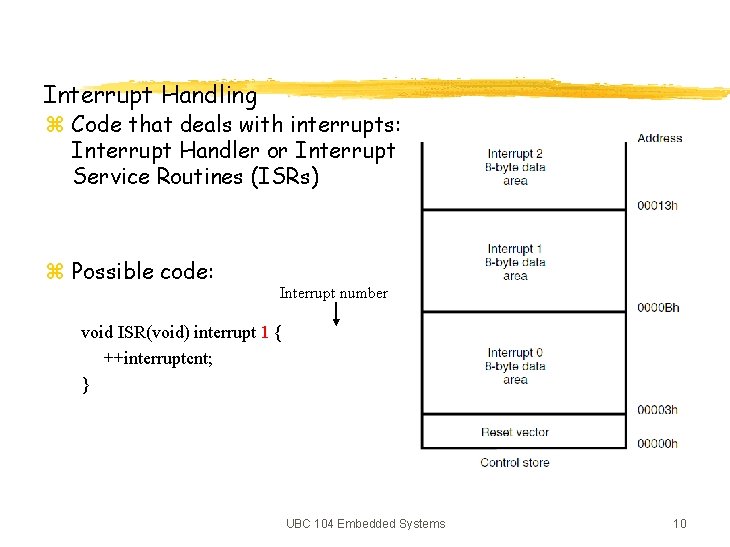

Address space in code space Interrupt Handling z Code that deals with interrupts: Interrupt Handler or Interrupt Service Routines (ISRs) UBC 104 Embedded Systems 9

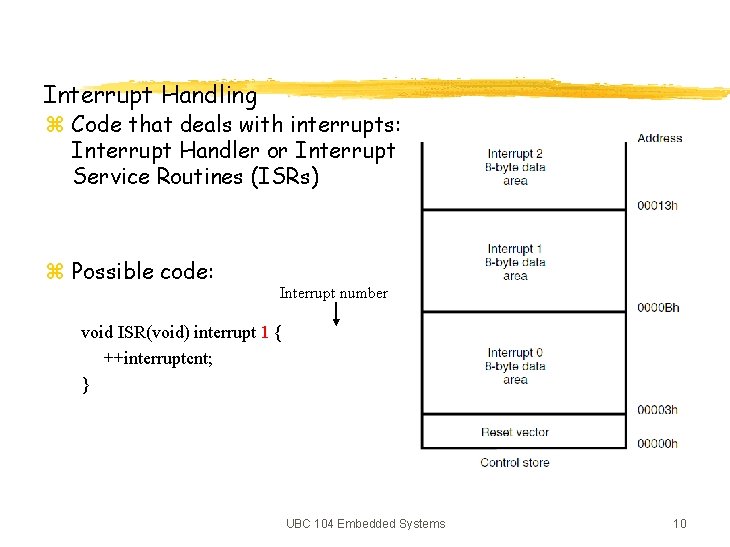

Interrupt Handling z Code that deals with interrupts: Interrupt Handler or Interrupt Service Routines (ISRs) z Possible code: Interrupt number void ISR(void) interrupt 1 { ++interruptcnt; } UBC 104 Embedded Systems 10

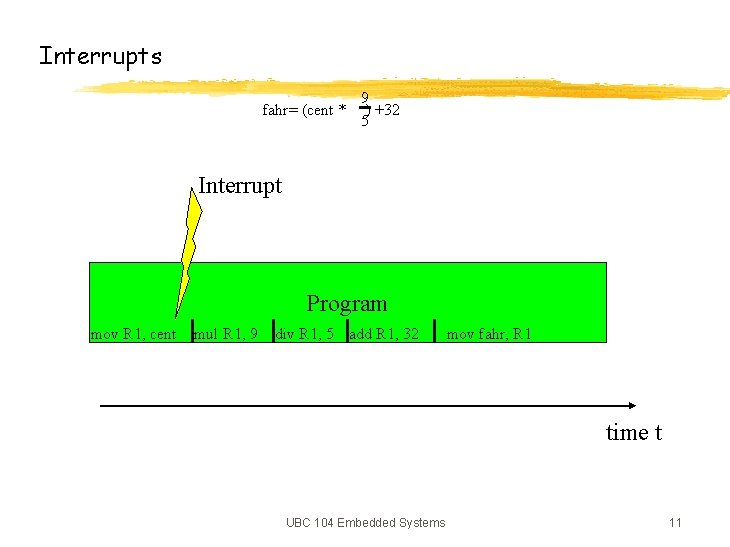

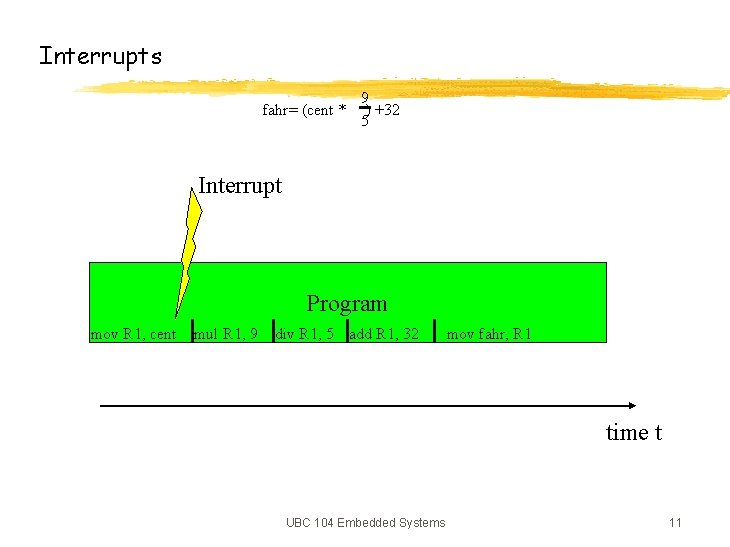

Interrupts fahr= (cent * 9 ) +32 5 Interrupt Program mov R 1, cent mul R 1, 9 div R 1, 5 add R 1, 32 mov fahr, R 1 time t UBC 104 Embedded Systems 11

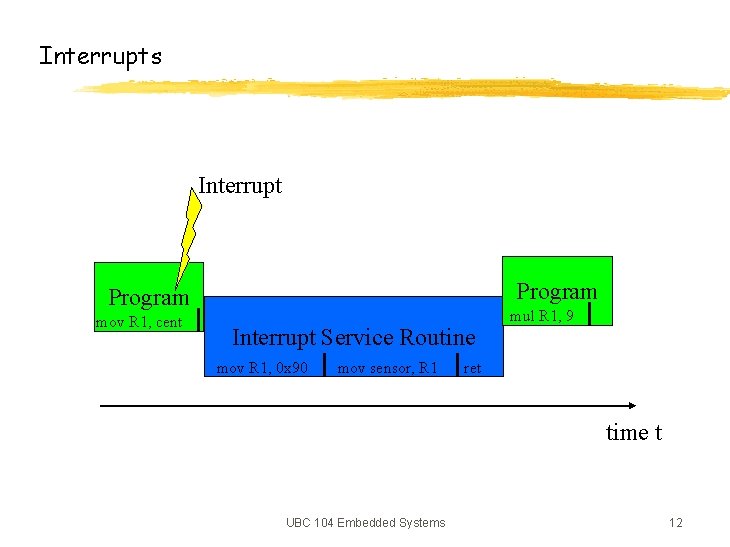

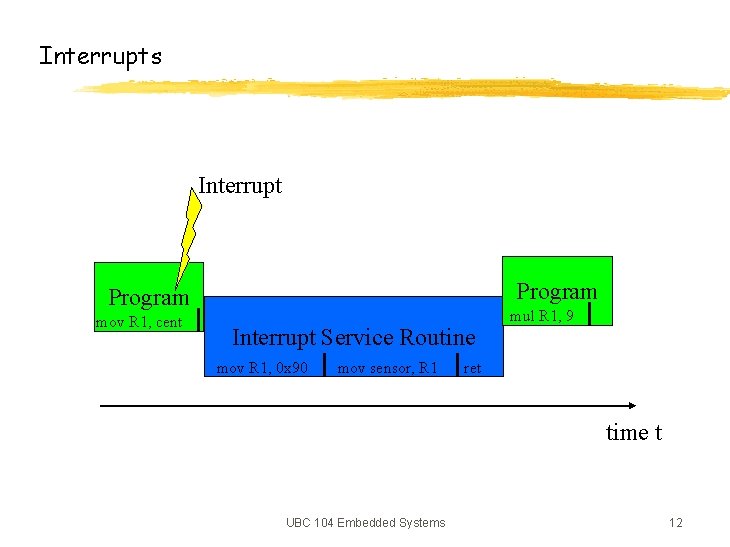

Interrupts Interrupt Program mov R 1, cent Interrupt Service Routine mov R 1, 0 x 90 mov sensor, R 1 mul R 1, 9 ret time t UBC 104 Embedded Systems 12

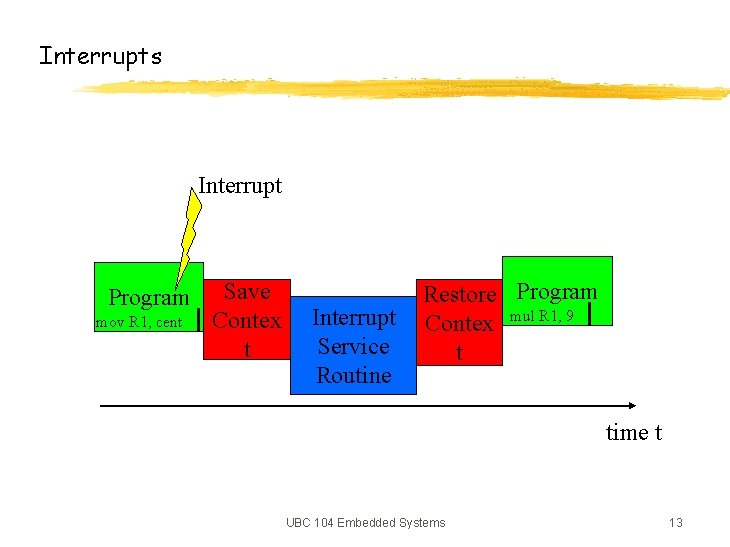

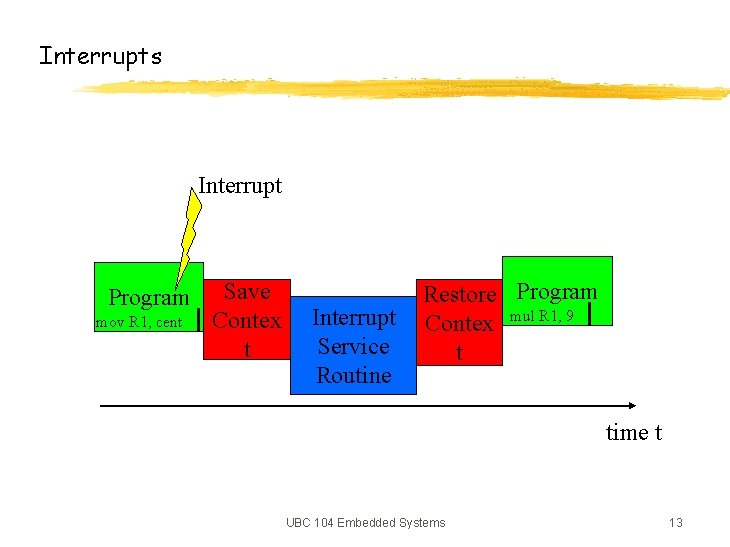

Interrupts Interrupt Program mov R 1, cent Save Contex t Interrupt Service Routine Restore Program Contex mul R 1, 9 t time t UBC 104 Embedded Systems 13

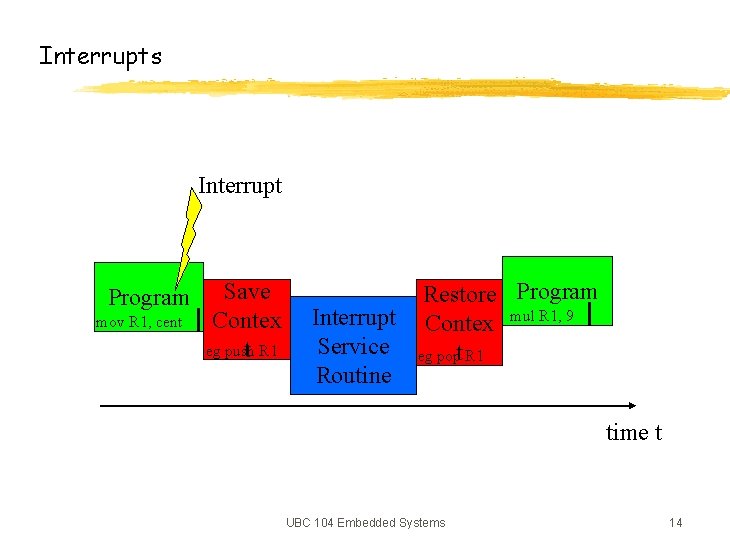

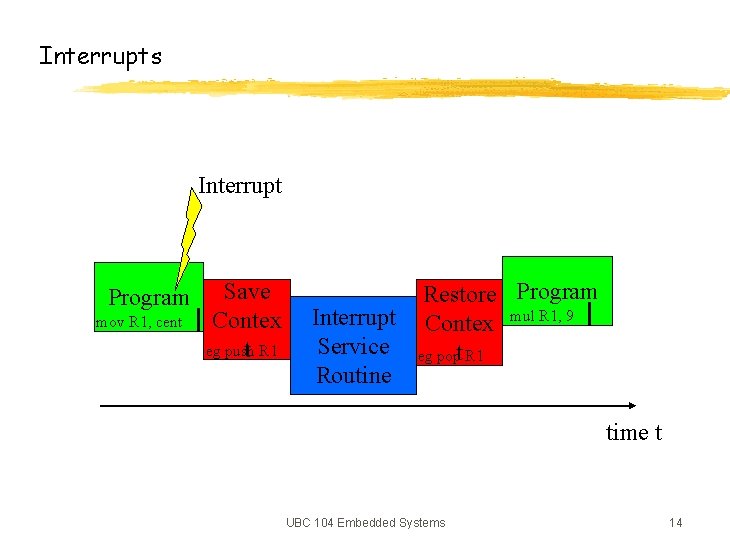

Interrupts Interrupt Program mov R 1, cent Save Contex eg push t R 1 Restore Program Interrupt Contex mul R 1, 9 Service eg popt R 1 Routine time t UBC 104 Embedded Systems 14

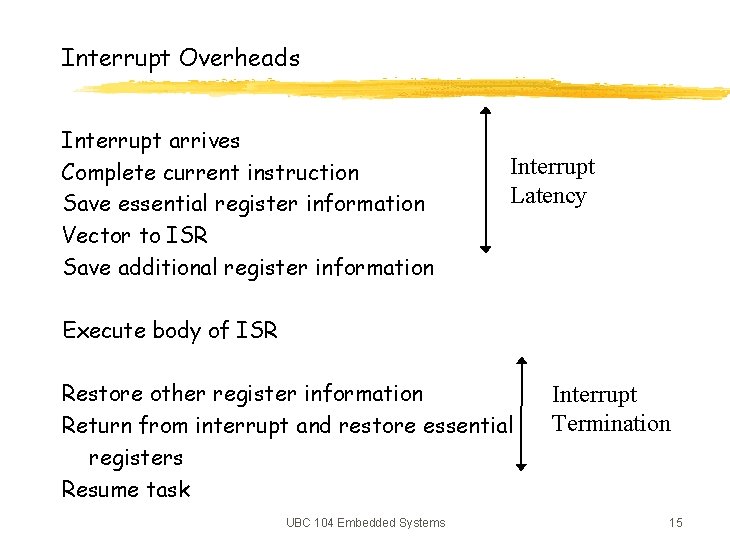

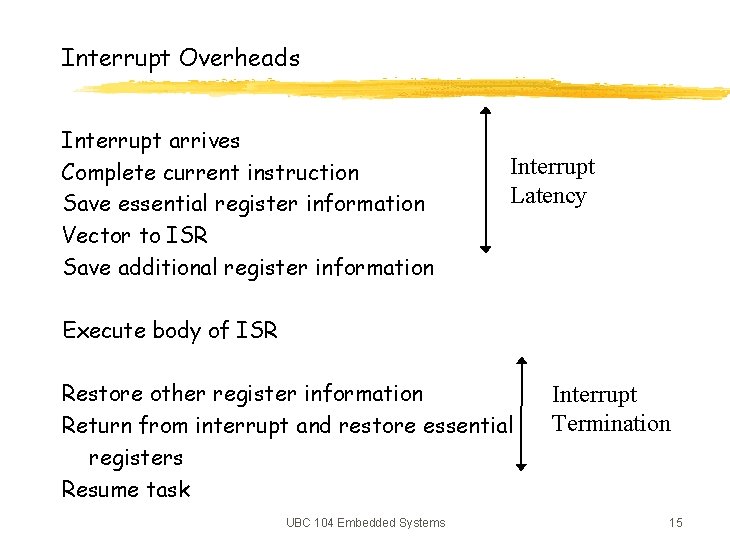

Interrupt Overheads Interrupt arrives Complete current instruction Save essential register information Vector to ISR Save additional register information Interrupt Latency Execute body of ISR Restore other register information Return from interrupt and restore essential registers Resume task UBC 104 Embedded Systems Interrupt Termination 15

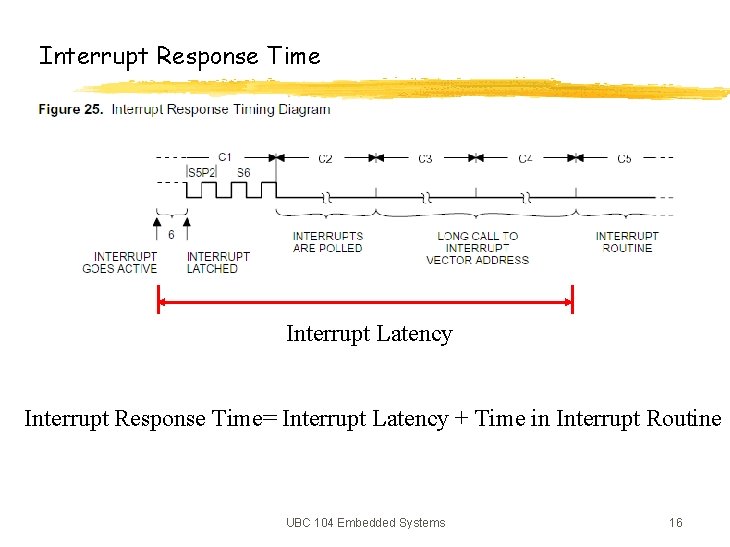

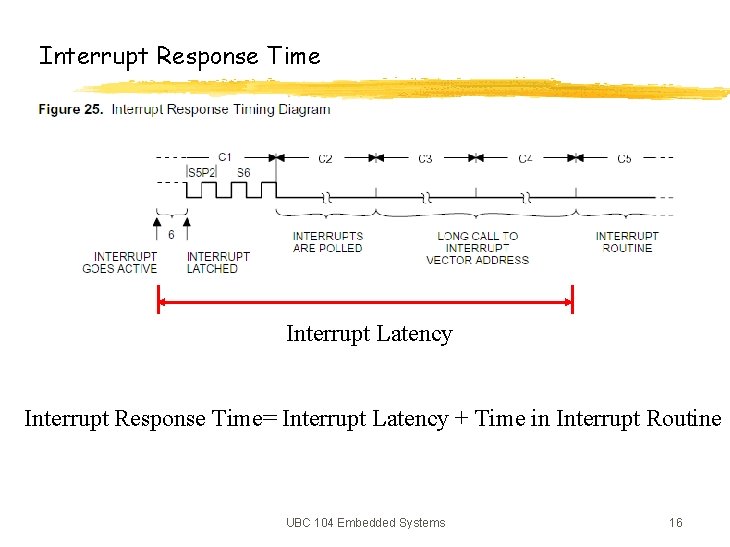

Interrupt Response Time Interrupt Latency Interrupt Response Time= Interrupt Latency + Time in Interrupt Routine UBC 104 Embedded Systems 16

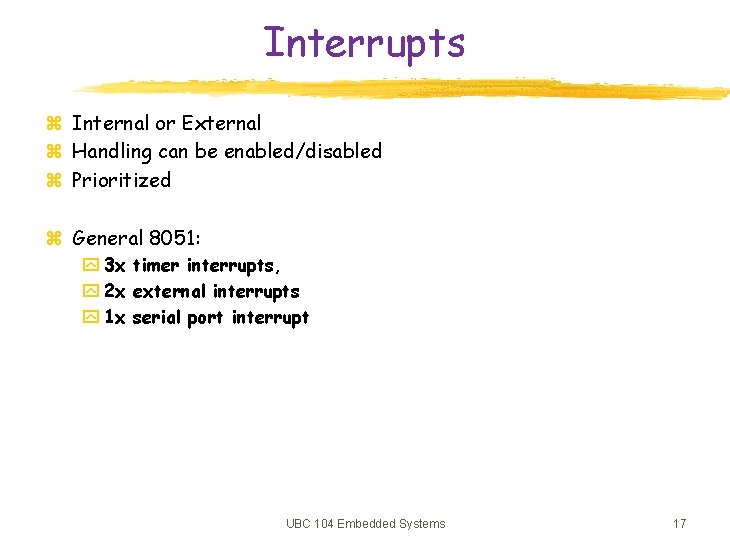

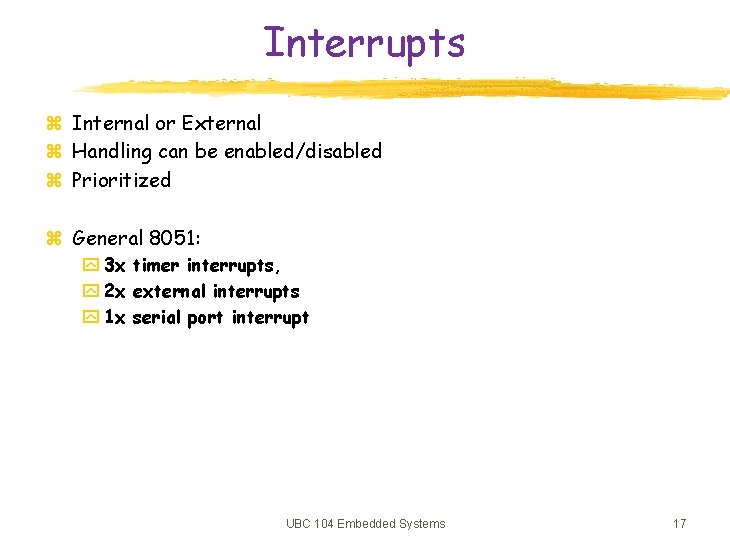

Interrupts z Internal or External z Handling can be enabled/disabled z Prioritized z General 8051: y 3 x timer interrupts, y 2 x external interrupts y 1 x serial port interrupt UBC 104 Embedded Systems 17

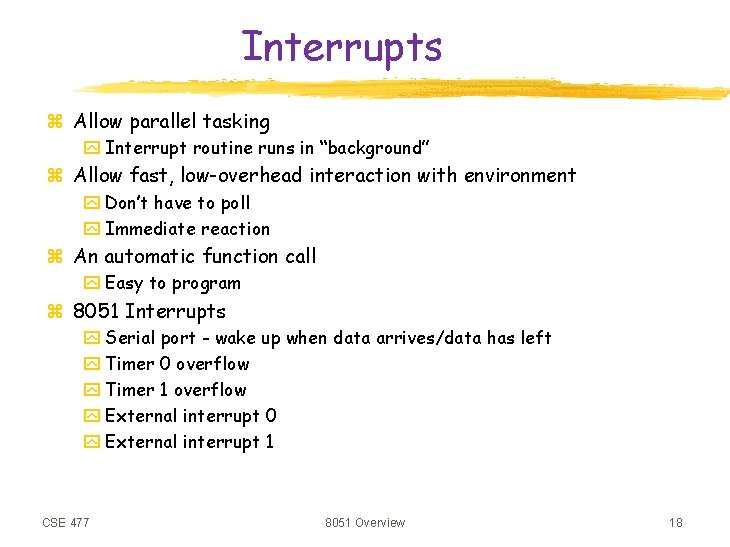

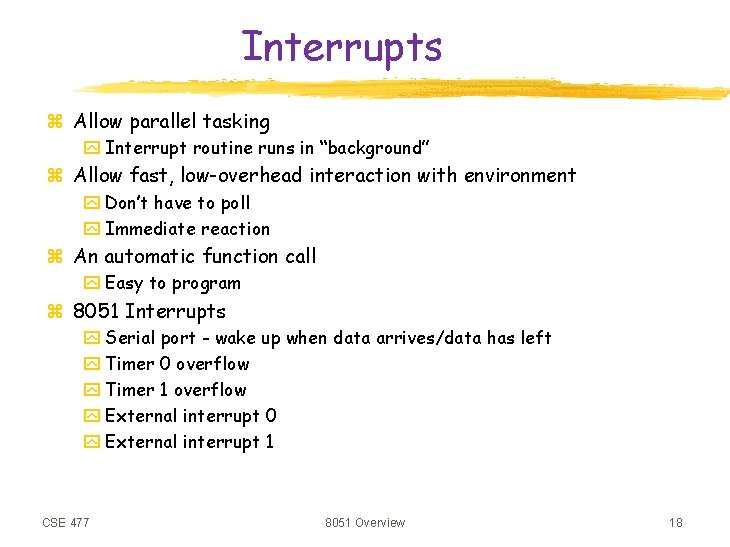

Interrupts z Allow parallel tasking y Interrupt routine runs in “background” z Allow fast, low-overhead interaction with environment y Don’t have to poll y Immediate reaction z An automatic function call y Easy to program z 8051 Interrupts y Serial port - wake up when data arrives/data has left y Timer 0 overflow y Timer 1 overflow y External interrupt 0 y External interrupt 1 CSE 477 8051 Overview 18

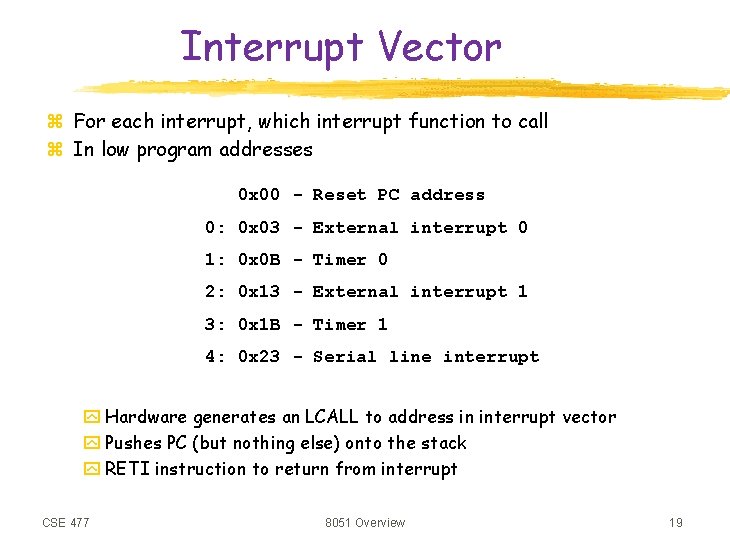

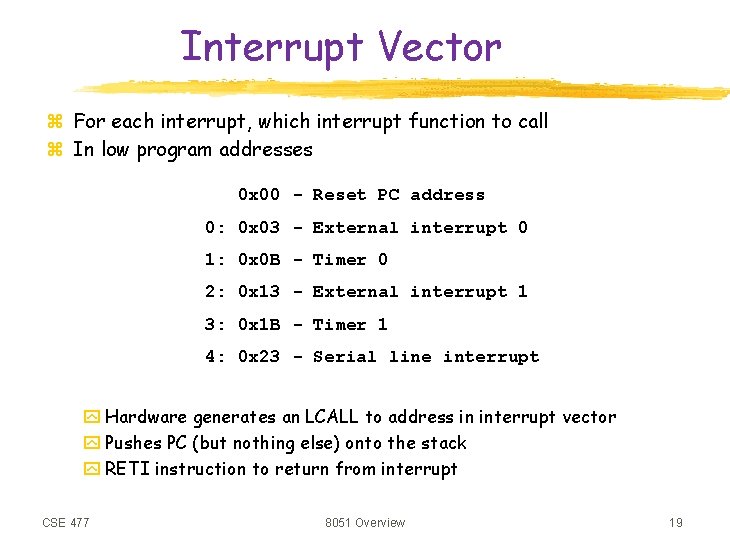

Interrupt Vector z For each interrupt, which interrupt function to call z In low program addresses 0 x 00 - Reset PC address 0: 0 x 03 - External interrupt 0 1: 0 x 0 B - Timer 0 2: 0 x 13 - External interrupt 1 3: 0 x 1 B - Timer 1 4: 0 x 23 - Serial line interrupt y Hardware generates an LCALL to address in interrupt vector y Pushes PC (but nothing else) onto the stack y RETI instruction to return from interrupt CSE 477 8051 Overview 19

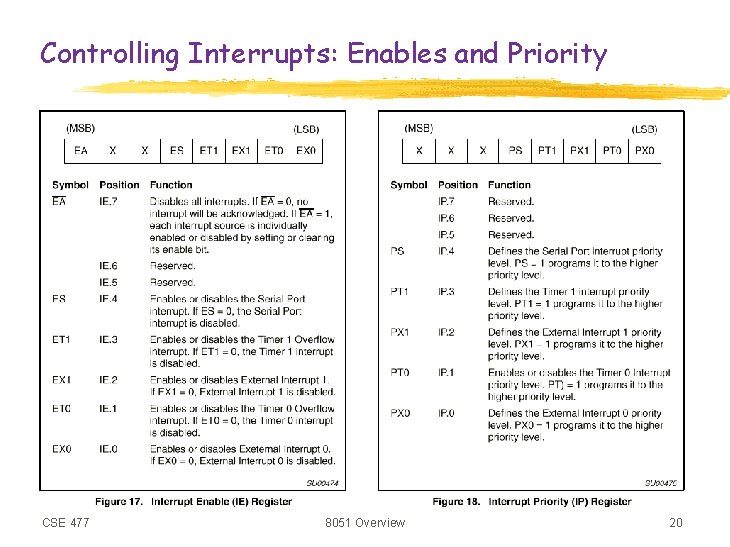

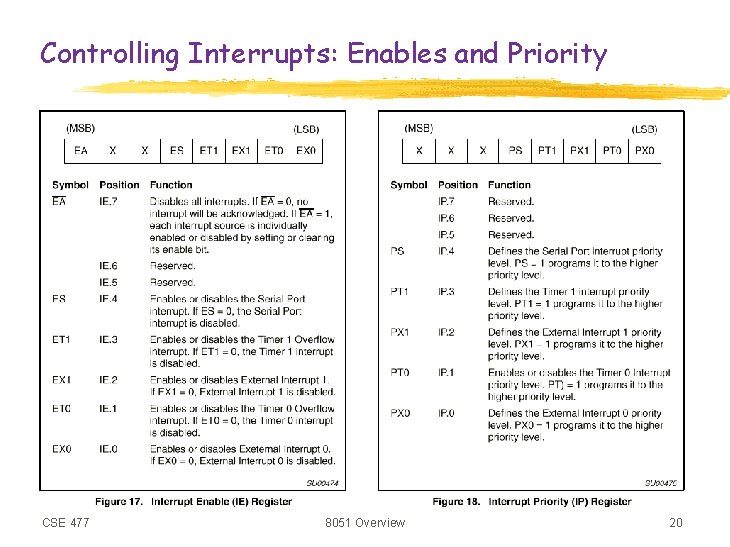

Controlling Interrupts: Enables and Priority CSE 477 8051 Overview 20

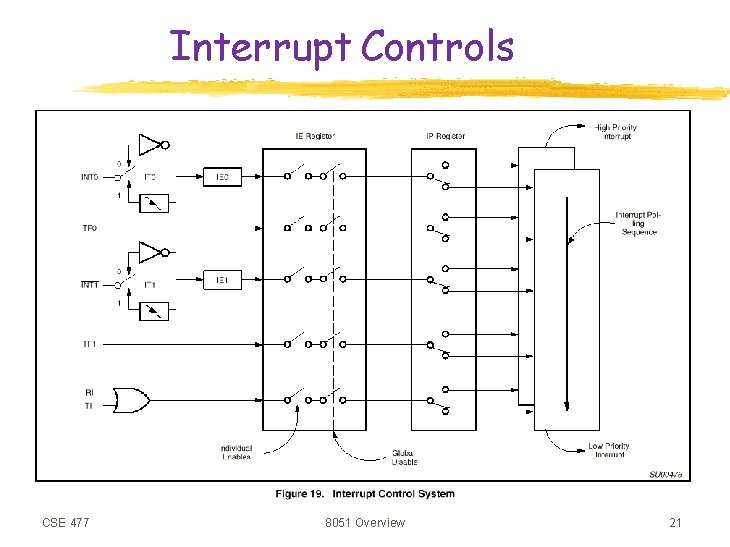

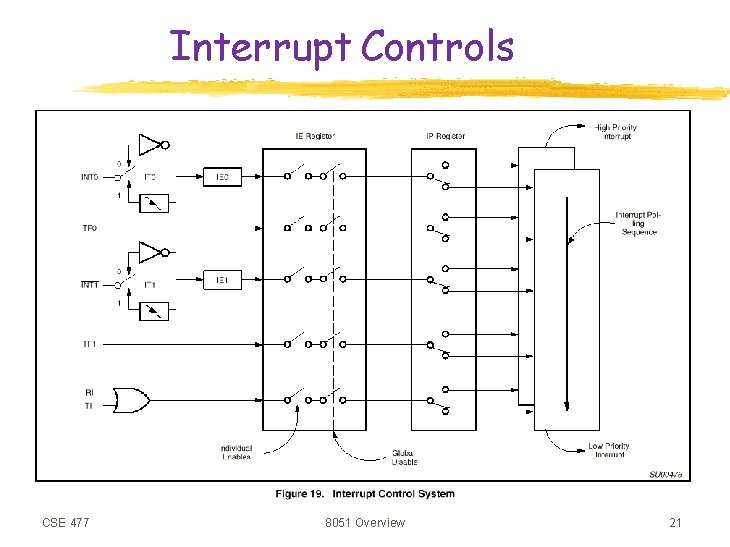

Interrupt Controls CSE 477 8051 Overview 21

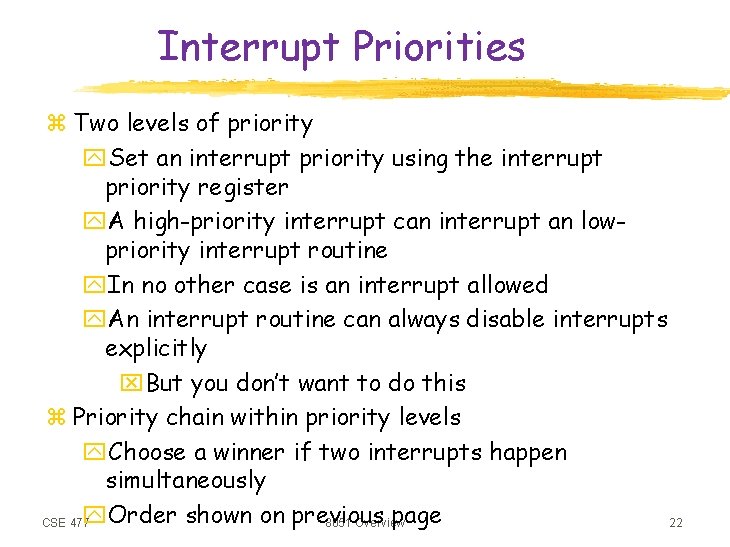

Interrupt Priorities z Two levels of priority y. Set an interrupt priority using the interrupt priority register y. A high-priority interrupt can interrupt an lowpriority interrupt routine y. In no other case is an interrupt allowed y. An interrupt routine can always disable interrupts explicitly x. But you don’t want to do this z Priority chain within priority levels y. Choose a winner if two interrupts happen simultaneously y. Order shown on previous page CSE 477 8051 Overview 22

External Interrupts z Can interrupt using the INT 0 or INT 1 pins (port 3: pin 2, 3) y. Interrupt on level or falling edge of signal (TCON specifies which) y. Pin is sampled once every 12 clock cycles xfor interrupt on edge, signal must be high 12 cycles, low 12 cycles y. Response time takes at least 3 instructions cycles x 1 to sample x 2 for call to interrupt routine xmore if a long instruction is in progress (up to 6 more) CSE 477 8051 Overview 23