Chapter 4 Circuit characterization and Performance Estimation 1

- Slides: 48

Chapter 4 Circuit characterization and Performance Estimation 1

Introduction Ø Need simple models to estimate system performance in terms of signal delay and power dissipation. Ø Each layer in an MOS transistor has both resistance and capacitance that are fundamental components in estimating the performance of a circuit or system. Ø They also have inductance characteristics that is assumed to be negligible. 2

Introduction • Issues include: Ø Resistance, capacitance and inductance calculations. Ø Delay estimations. Ø Determination of conductor size for power and clock distribution. Ø Power consumption. Ø Charge sharing mechanisms. Ø Design Margining. Ø Reliability. Ø Effects of scaling. 3

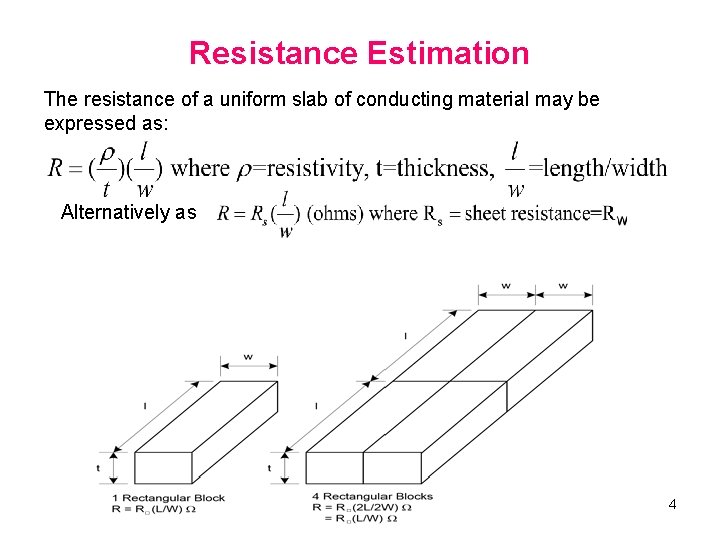

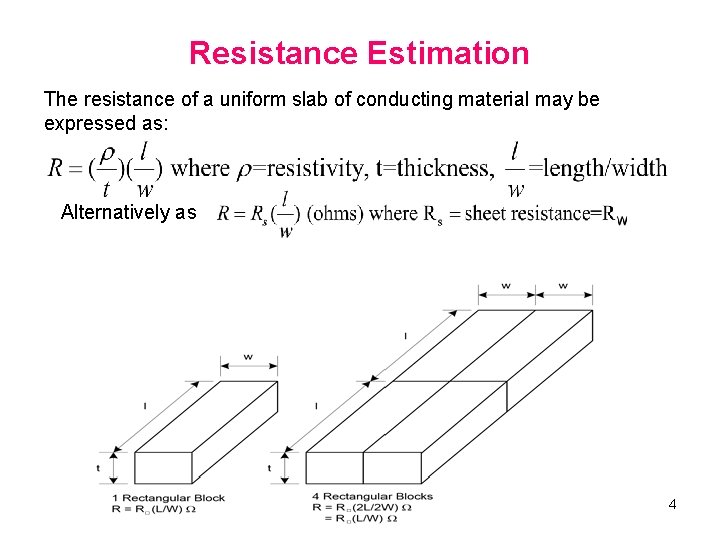

Resistance Estimation The resistance of a uniform slab of conducting material may be expressed as: Alternatively as 4

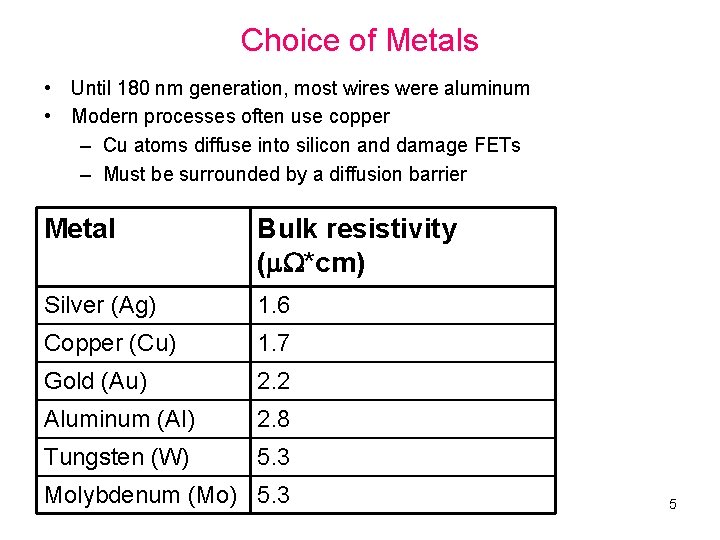

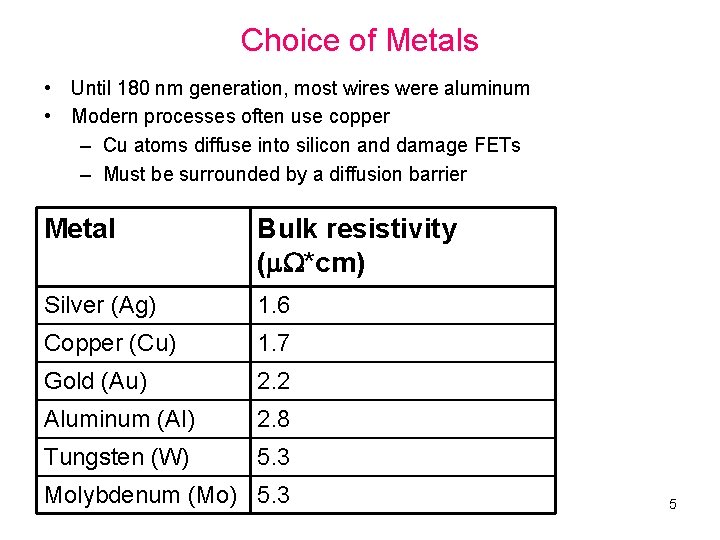

Choice of Metals • Until 180 nm generation, most wires were aluminum • Modern processes often use copper – Cu atoms diffuse into silicon and damage FETs – Must be surrounded by a diffusion barrier Metal Bulk resistivity (m. W*cm) Silver (Ag) 1. 6 Copper (Cu) 1. 7 Gold (Au) 2. 2 Aluminum (Al) 2. 8 Tungsten (W) 5. 3 Molybdenum (Mo) 5. 3 5

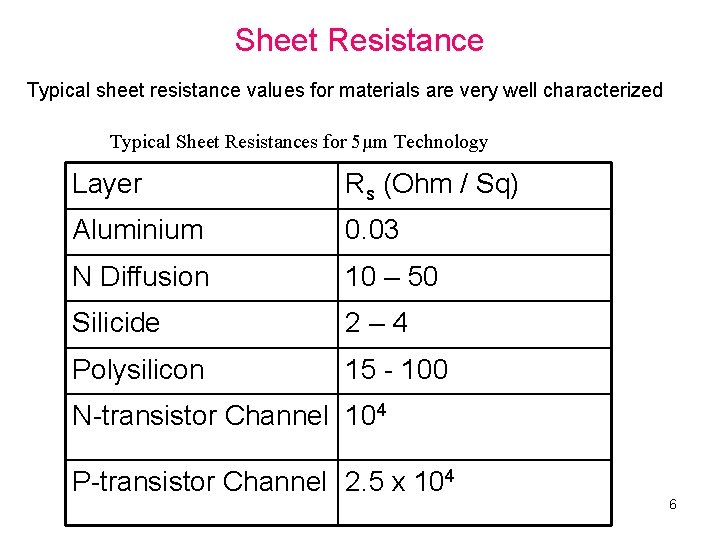

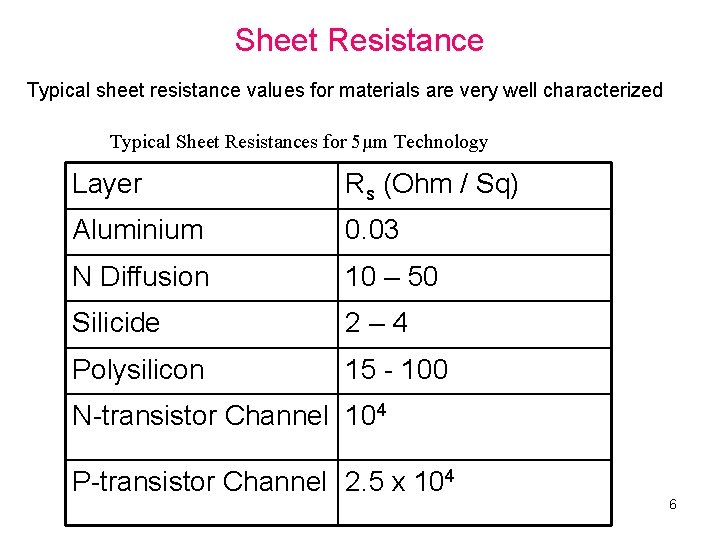

Sheet Resistance Typical sheet resistance values for materials are very well characterized Typical Sheet Resistances for 5µm Technology Layer Rs (Ohm / Sq) Aluminium 0. 03 N Diffusion 10 – 50 Silicide 2– 4 Polysilicon 15 - 100 N-transistor Channel 104 P-transistor Channel 2. 5 x 104 6

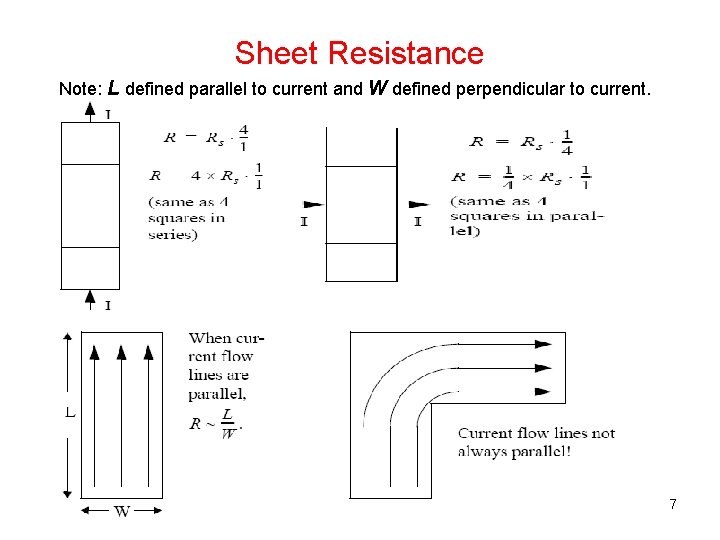

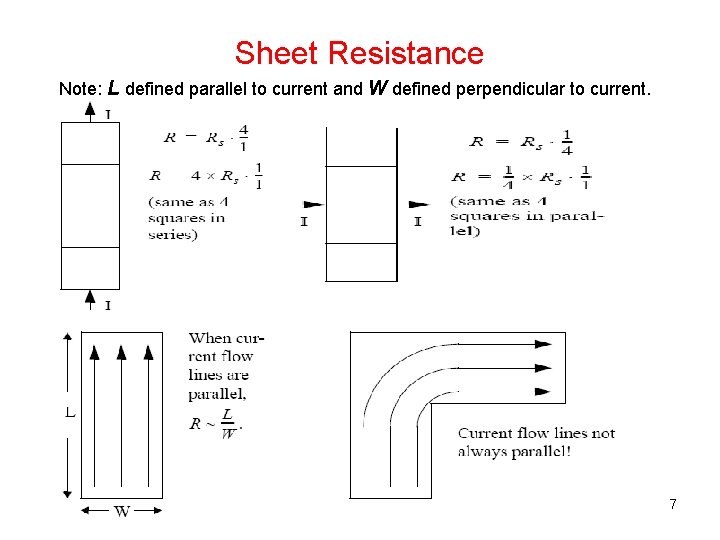

Sheet Resistance Note: L defined parallel to current and W defined perpendicular to current. 7

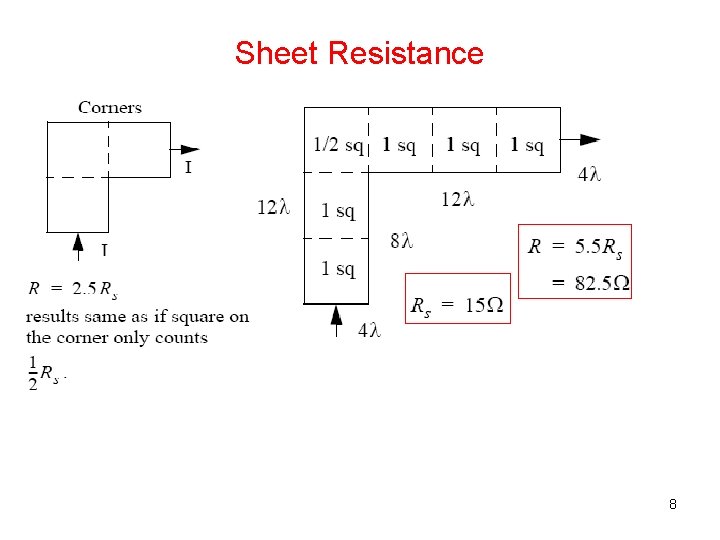

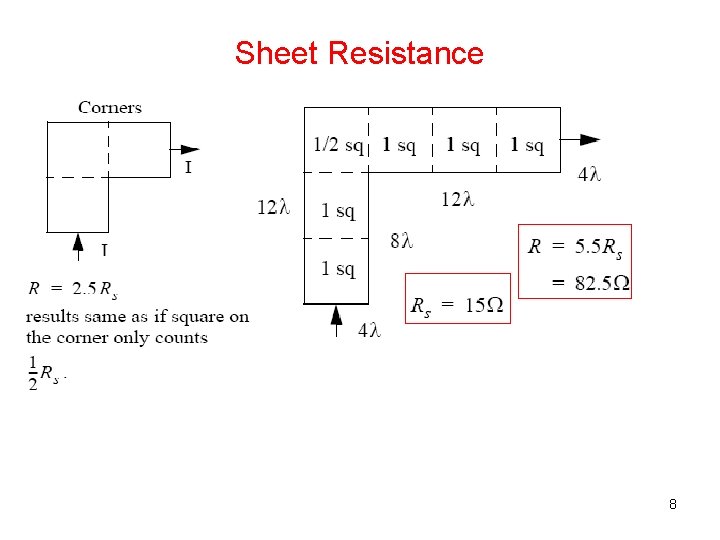

Sheet Resistance 8

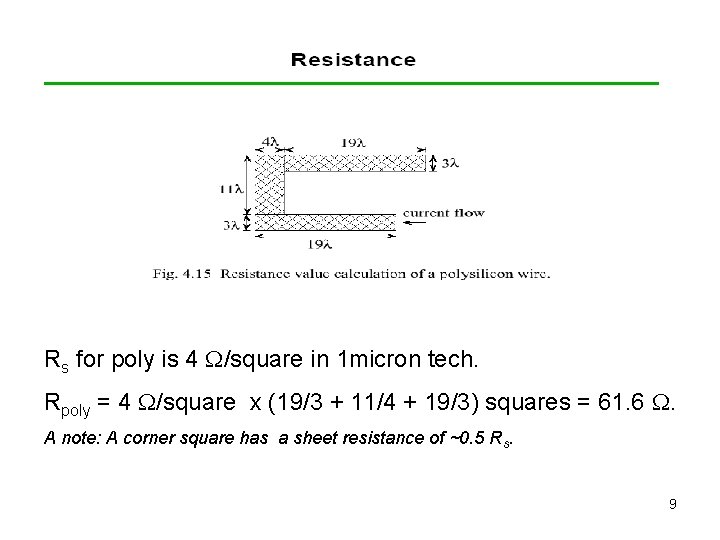

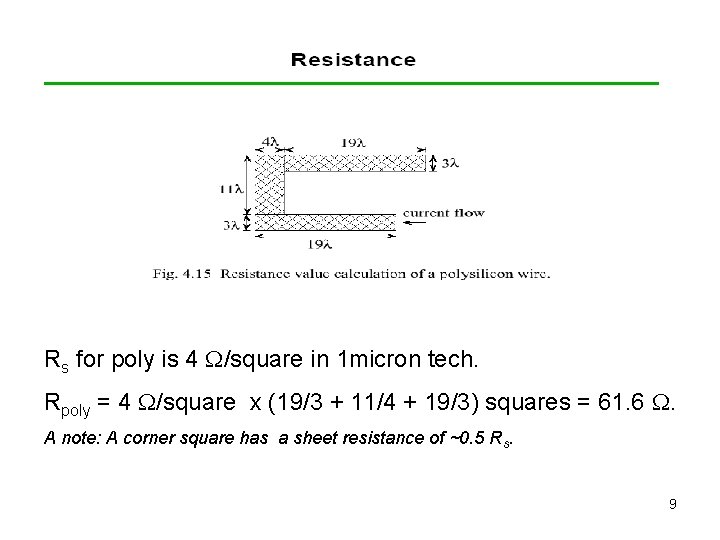

Rs for poly is 4 /square in 1 micron tech. Rpoly = 4 /square x (19/3 + 11/4 + 19/3) squares = 61. 6 . A note: A corner square has a sheet resistance of ~0. 5 Rs. 9

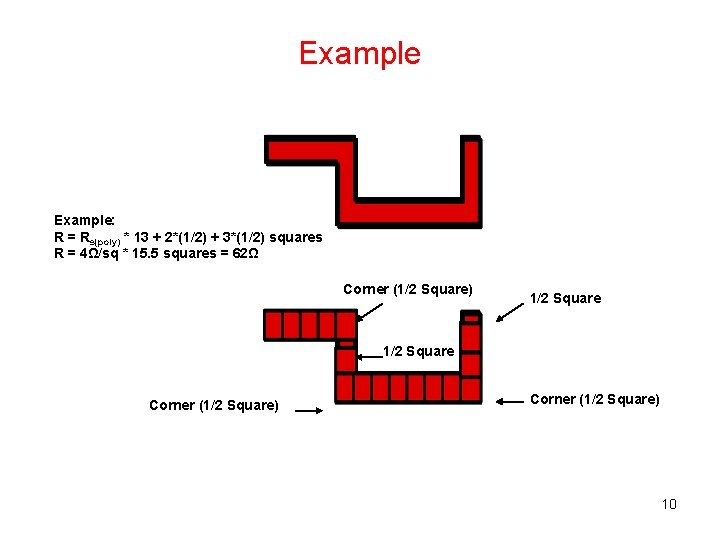

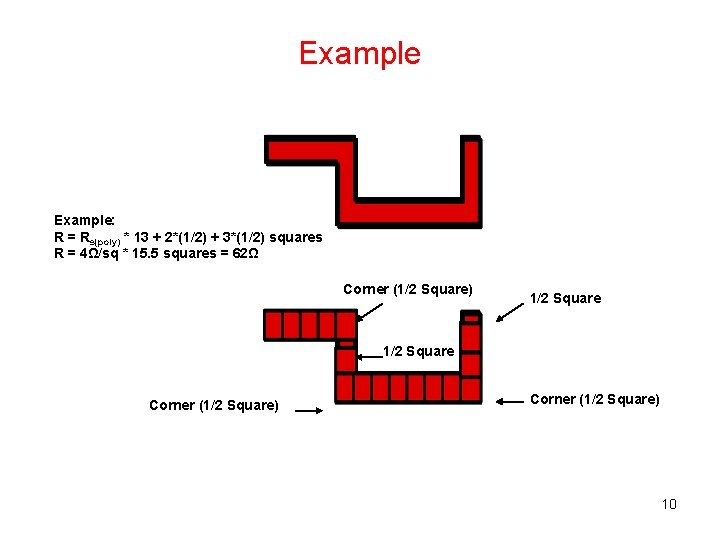

Example: R = Rs(poly) * 13 + 2*(1/2) + 3*(1/2) squares R = 4Ω/sq * 15. 5 squares = 62Ω Corner (1/2 Square) 1/2 Square Corner (1/2 Square) 10

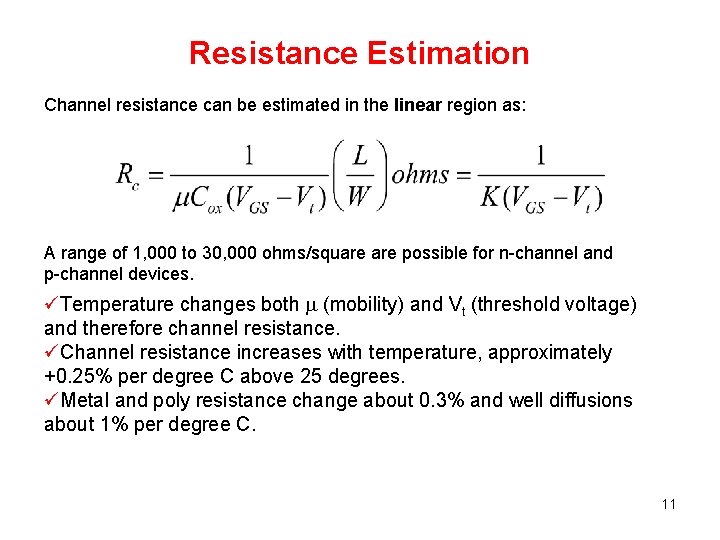

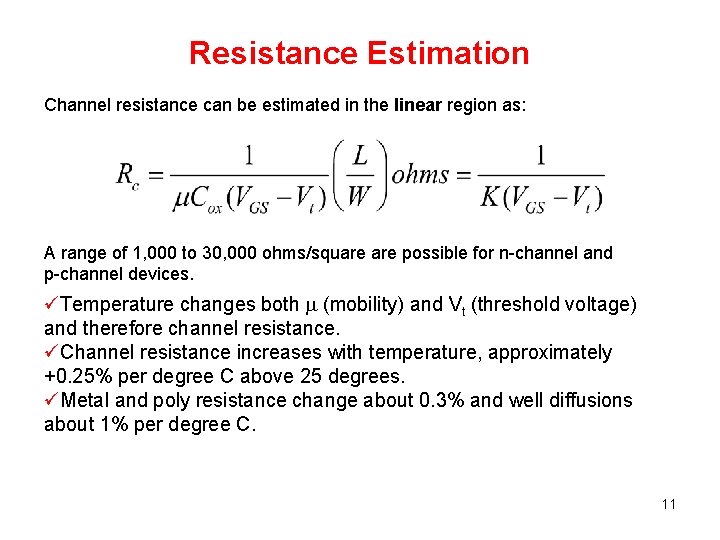

Resistance Estimation Channel resistance can be estimated in the linear region as: A range of 1, 000 to 30, 000 ohms/square possible for n-channel and p-channel devices. üTemperature changes both (mobility) and Vt (threshold voltage) and therefore channel resistance. üChannel resistance increases with temperature, approximately +0. 25% per degree C above 25 degrees. üMetal and poly resistance change about 0. 3% and well diffusions about 1% per degree C. 11

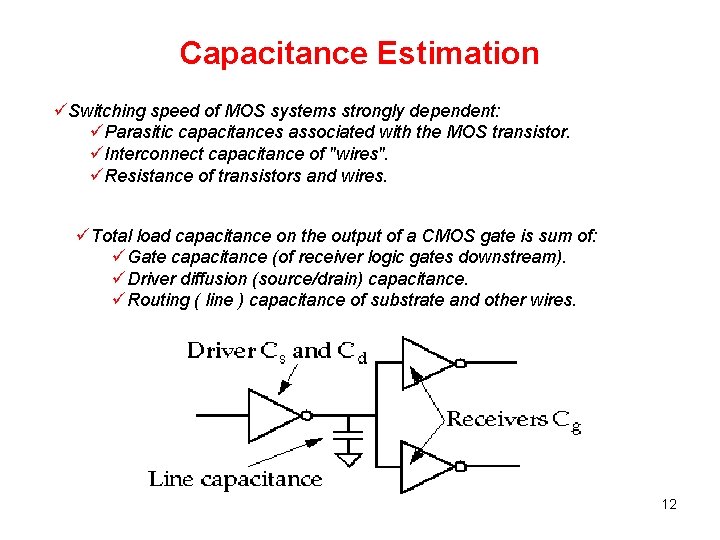

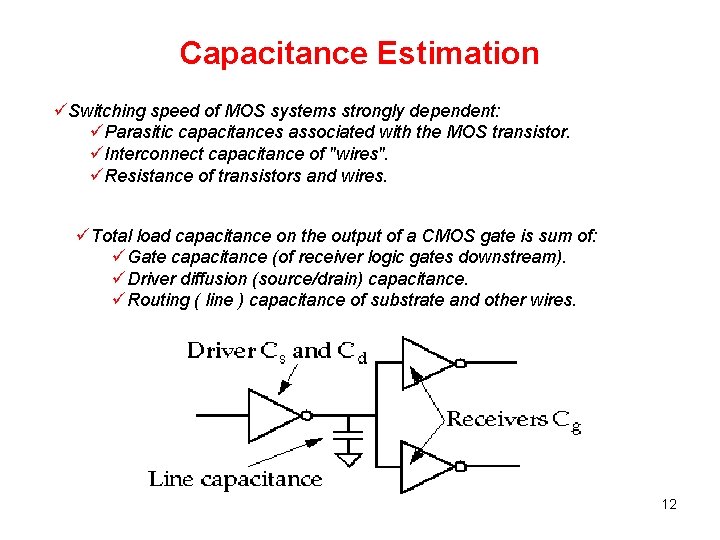

Capacitance Estimation üSwitching speed of MOS systems strongly dependent: üParasitic capacitances associated with the MOS transistor. üInterconnect capacitance of "wires". üResistance of transistors and wires. üTotal load capacitance on the output of a CMOS gate is sum of: üGate capacitance (of receiver logic gates downstream). üDriver diffusion (source/drain) capacitance. üRouting ( line ) capacitance of substrate and other wires. 12

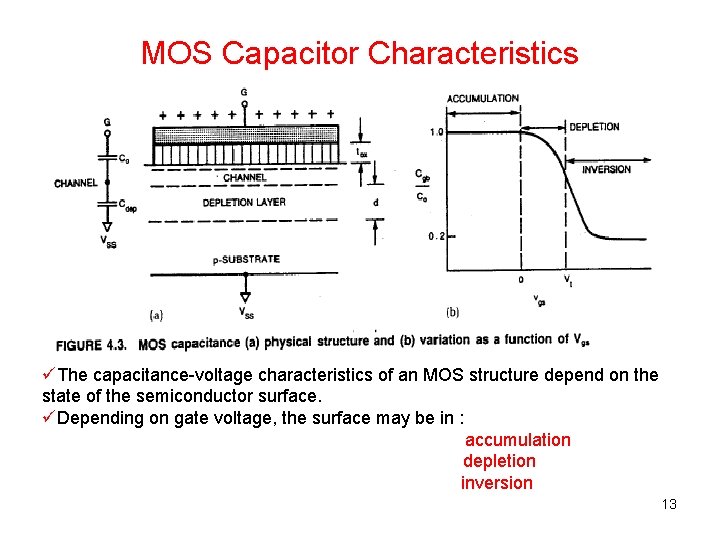

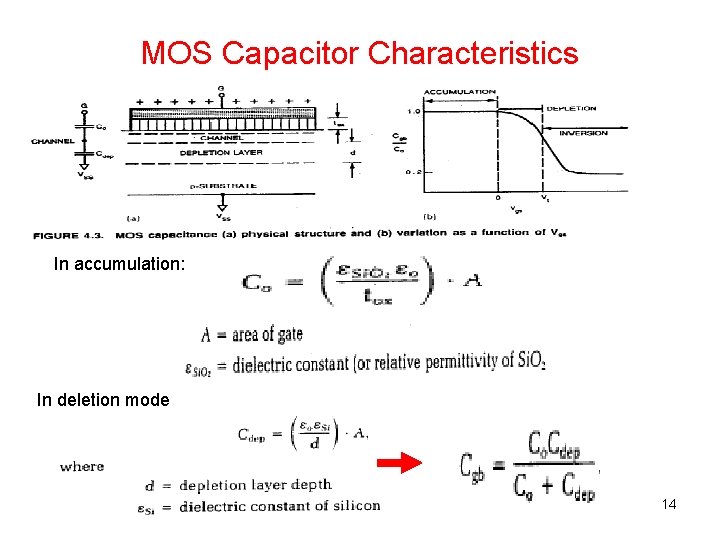

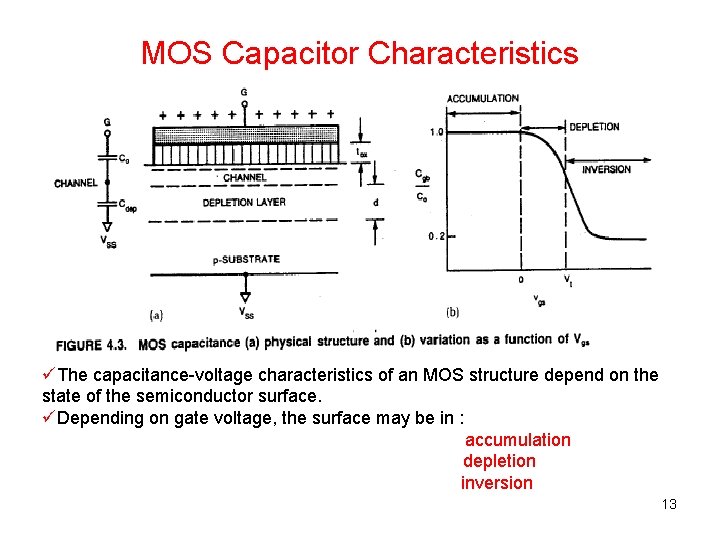

MOS Capacitor Characteristics üThe capacitance-voltage characteristics of an MOS structure depend on the state of the semiconductor surface. üDepending on gate voltage, the surface may be in : accumulation depletion inversion 13

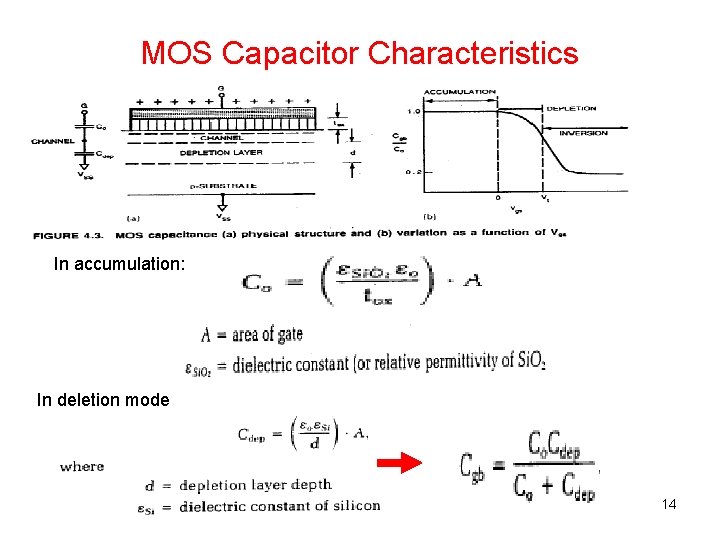

MOS Capacitor Characteristics In accumulation: In deletion mode 14

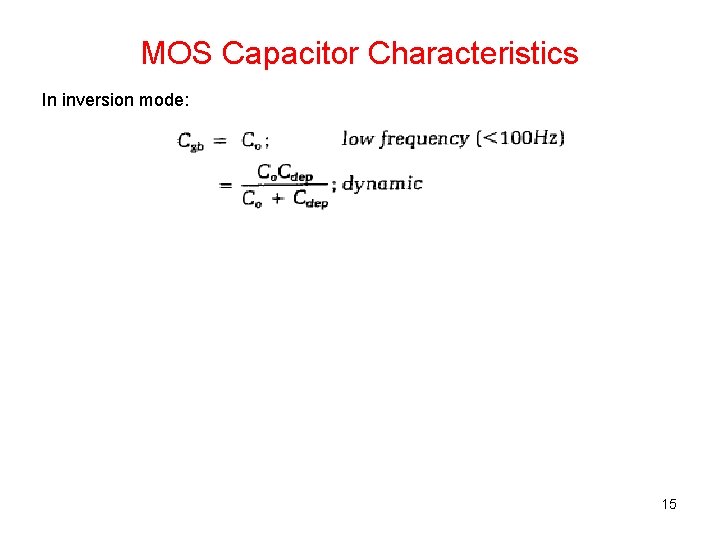

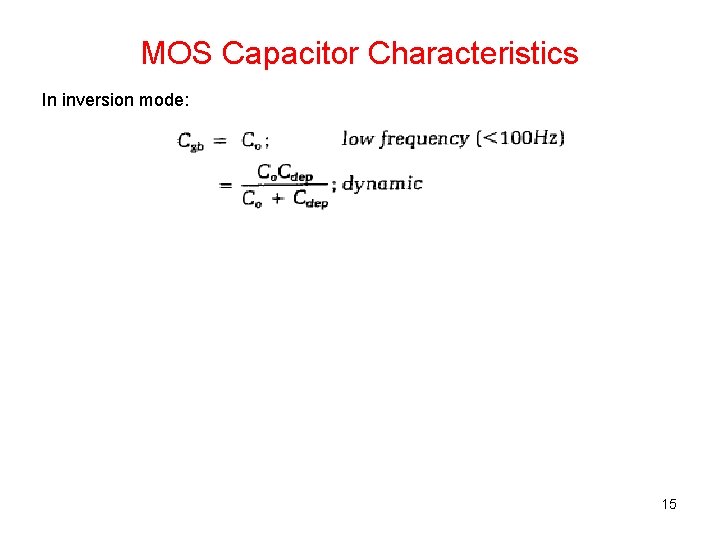

MOS Capacitor Characteristics In inversion mode: 15

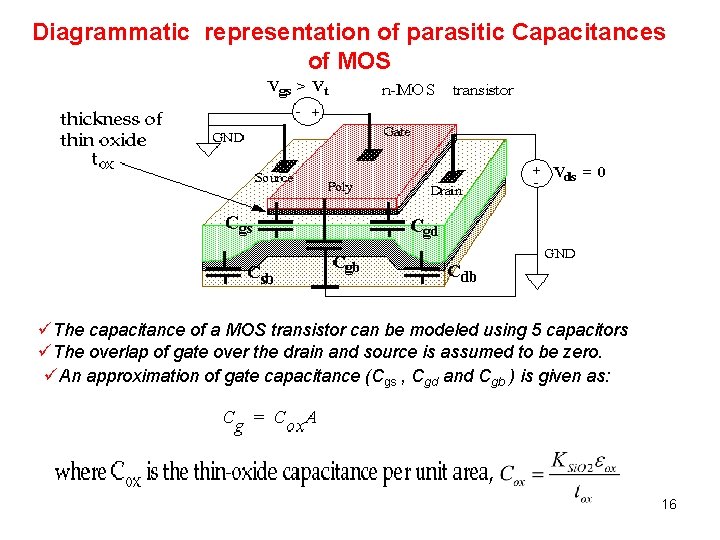

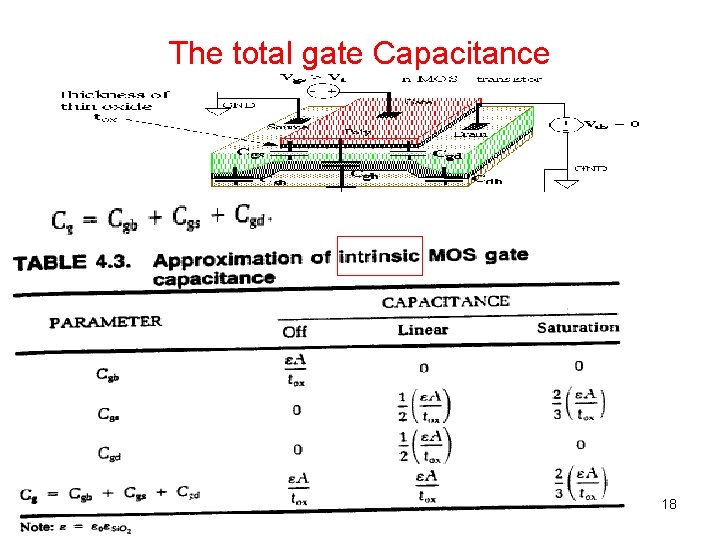

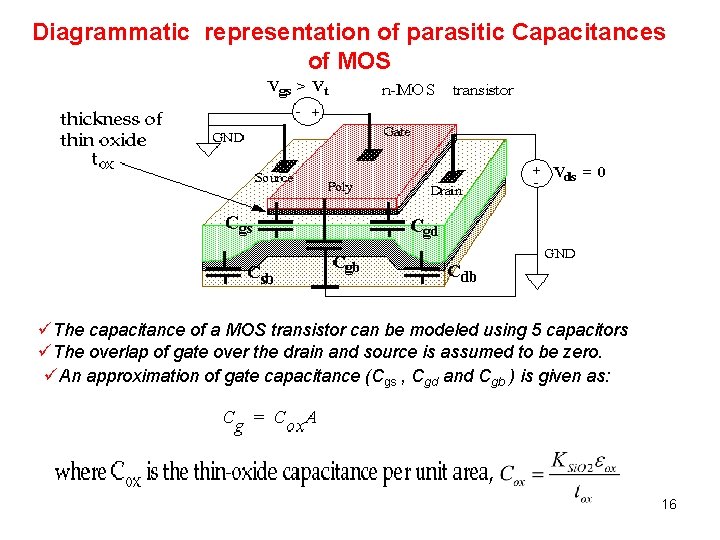

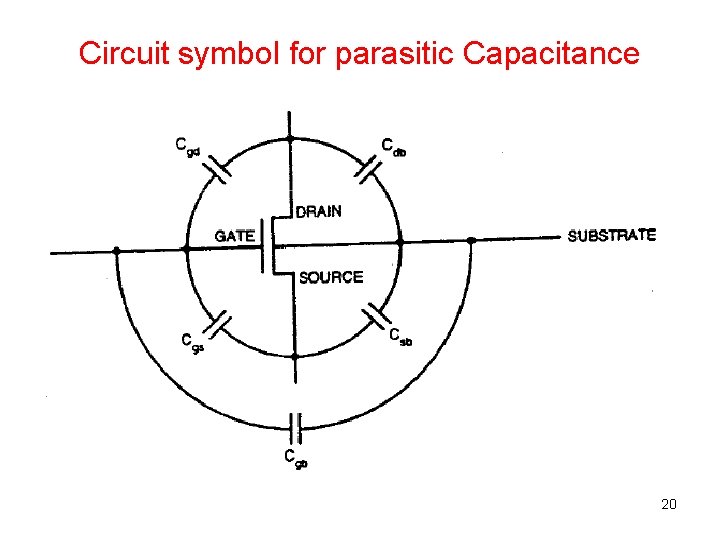

Diagrammatic representation of parasitic Capacitances of MOS üThe capacitance of a MOS transistor can be modeled using 5 capacitors üThe overlap of gate over the drain and source is assumed to be zero. üAn approximation of gate capacitance (Cgs , Cgd and Cgb ) is given as: 16

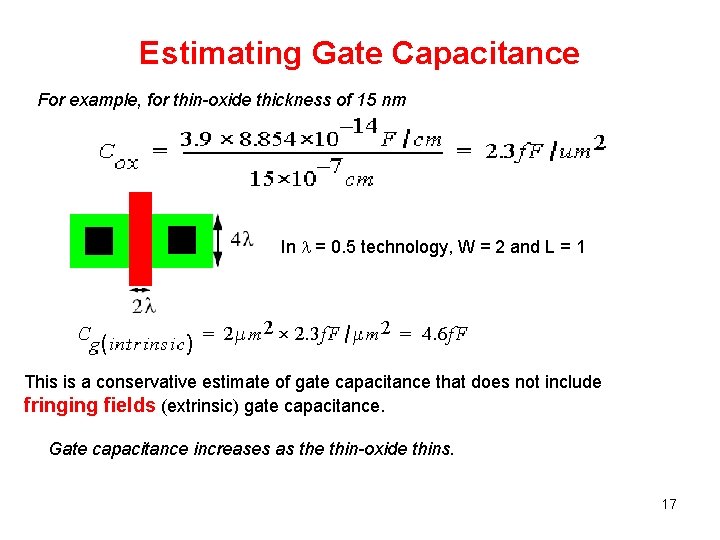

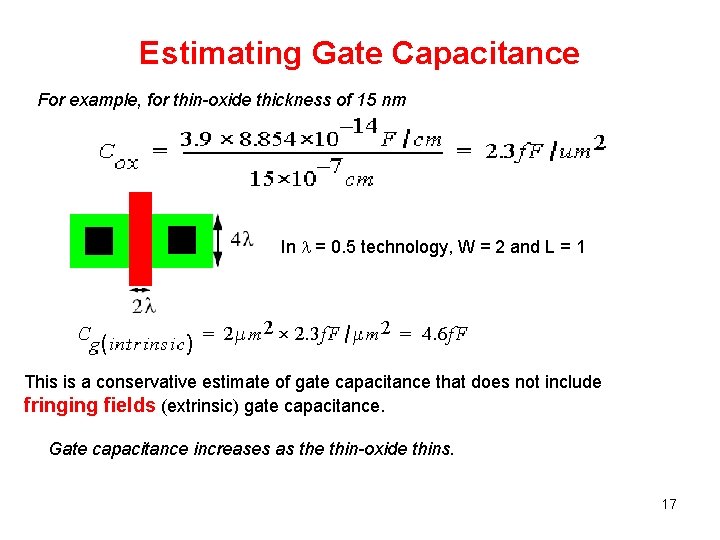

Estimating Gate Capacitance For example, for thin-oxide thickness of 15 nm In = 0. 5 technology, W = 2 and L = 1 This is a conservative estimate of gate capacitance that does not include fringing fields (extrinsic) gate capacitance. Gate capacitance increases as the thin-oxide thins. 17

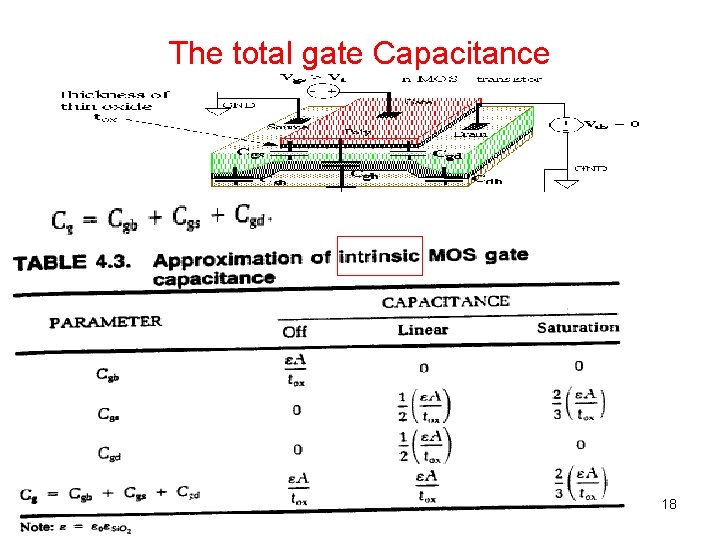

The total gate Capacitance 18

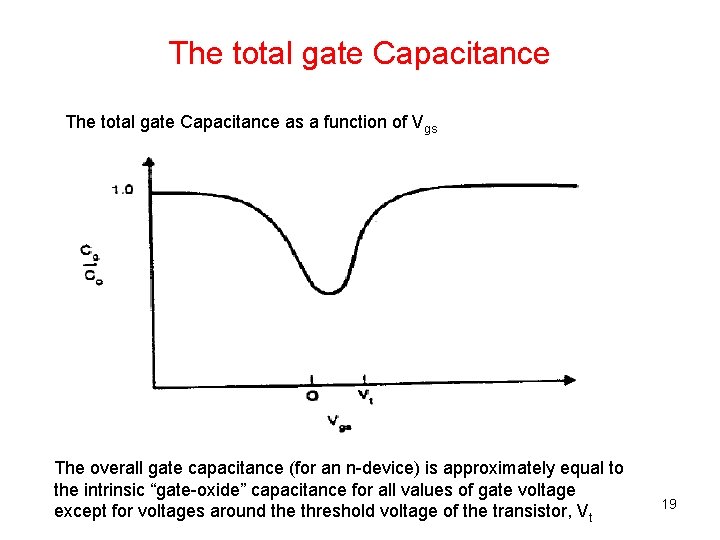

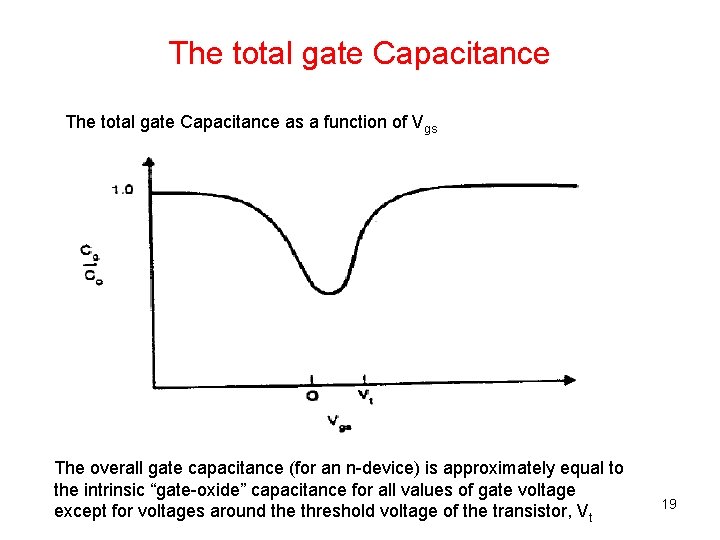

The total gate Capacitance as a function of Vgs The overall gate capacitance (for an n-device) is approximately equal to the intrinsic “gate-oxide” capacitance for all values of gate voltage except for voltages around the threshold voltage of the transistor, Vt 19

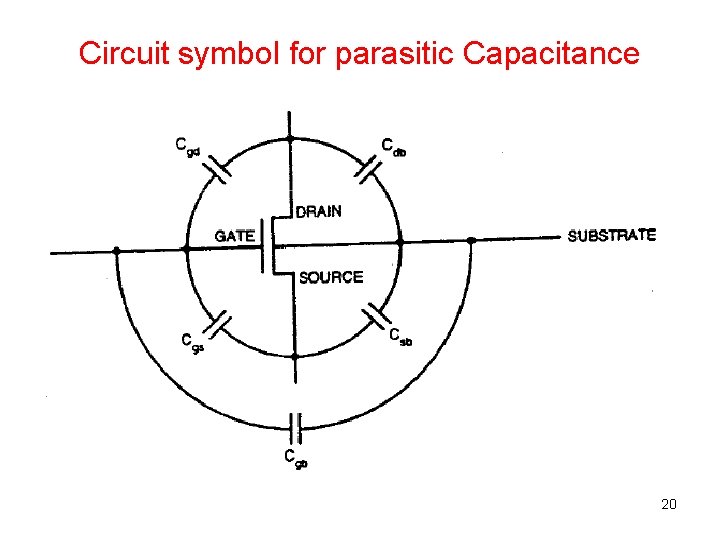

Circuit symbol for parasitic Capacitance 20

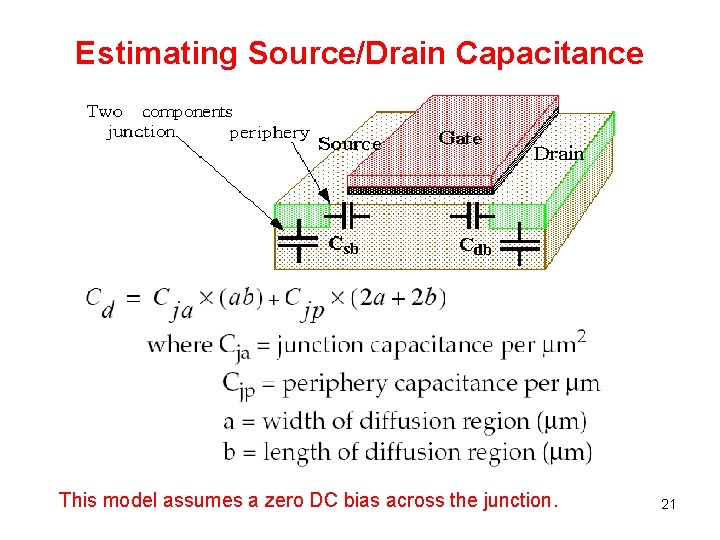

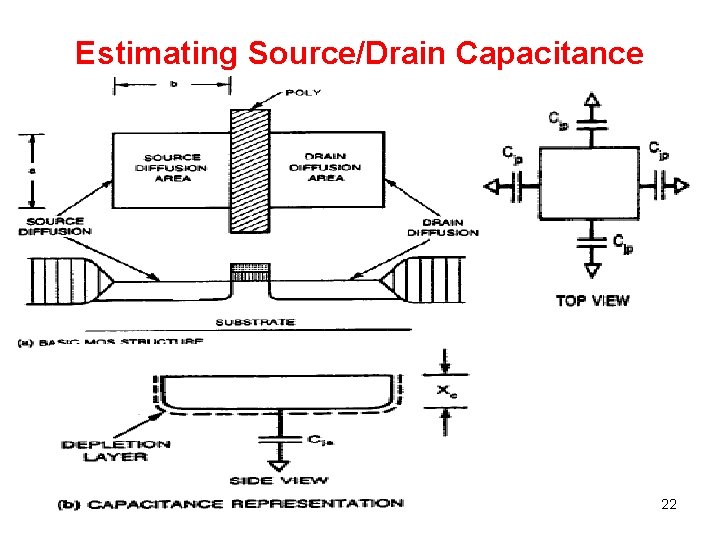

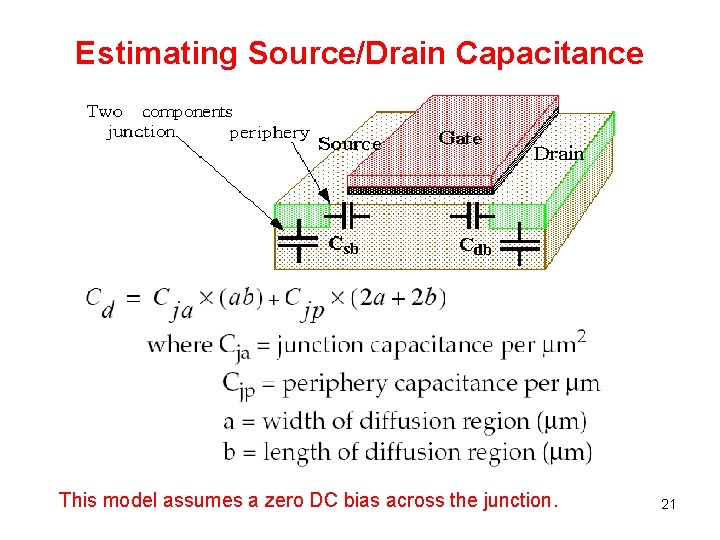

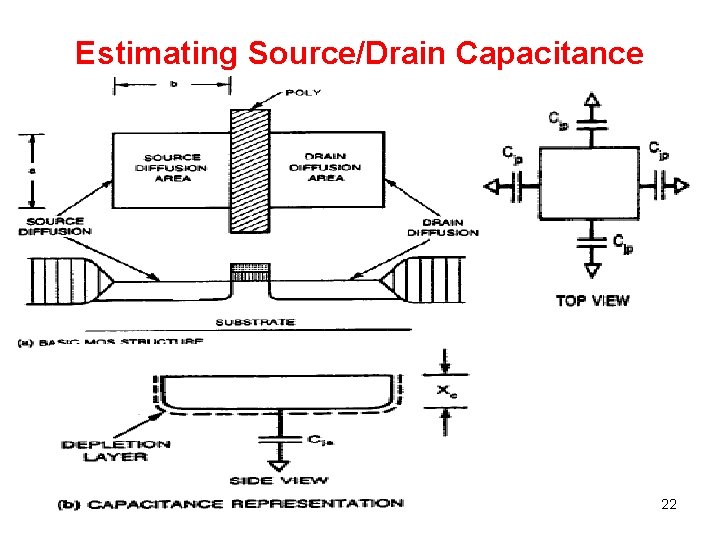

Estimating Source/Drain Capacitance This model assumes a zero DC bias across the junction. 21

Estimating Source/Drain Capacitance 22

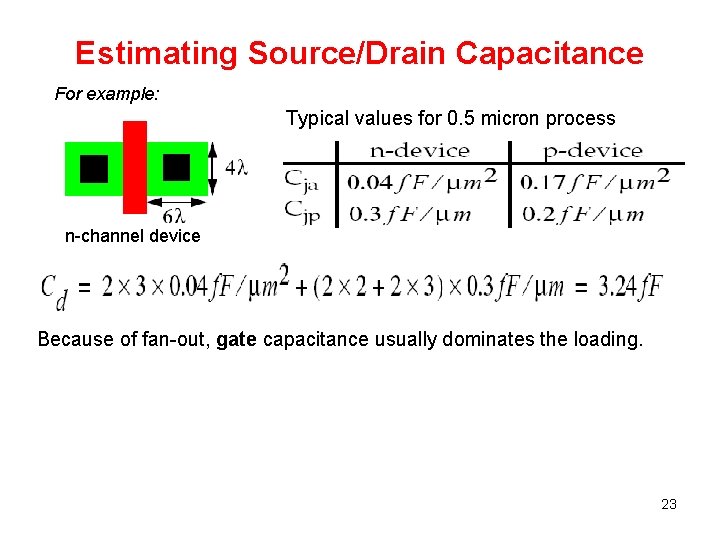

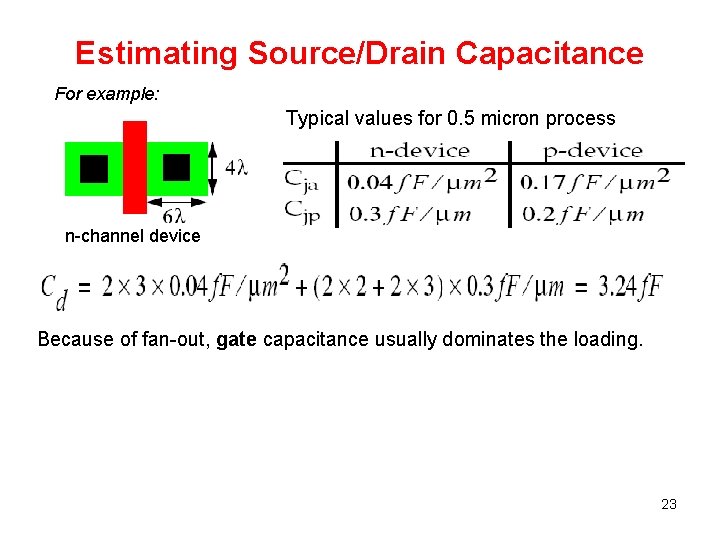

Estimating Source/Drain Capacitance For example: Typical values for 0. 5 micron process n-channel device Because of fan-out, gate capacitance usually dominates the loading. 23

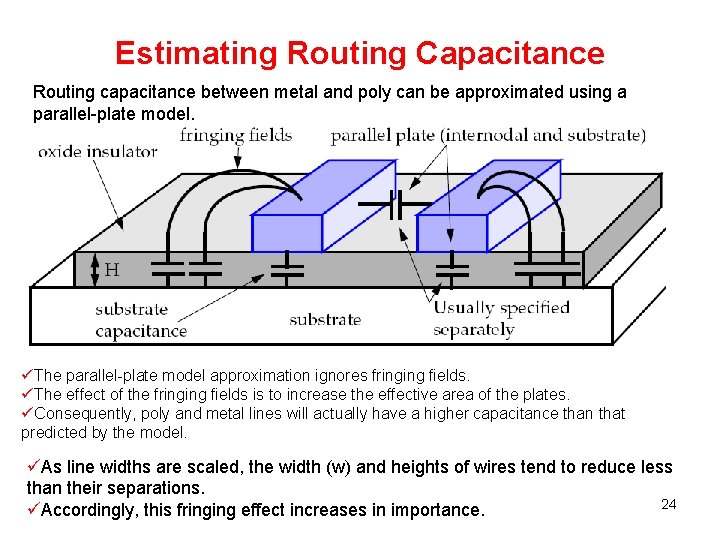

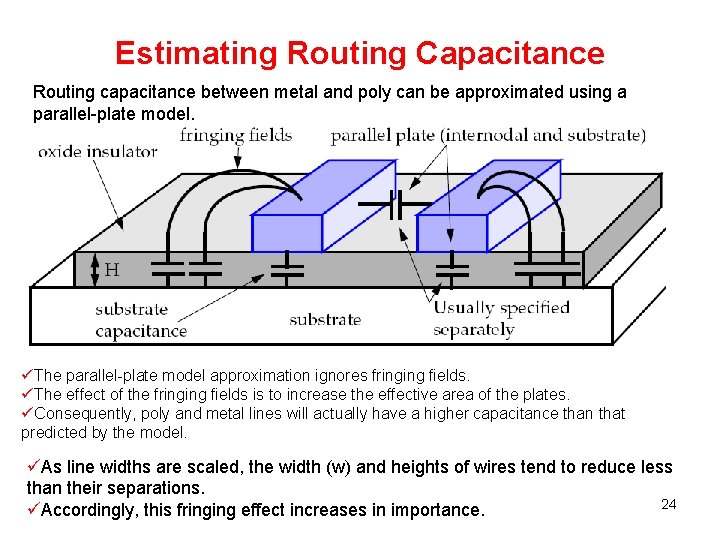

Estimating Routing Capacitance Routing capacitance between metal and poly can be approximated using a parallel-plate model. üThe parallel-plate model approximation ignores fringing fields. üThe effect of the fringing fields is to increase the effective area of the plates. üConsequently, poly and metal lines will actually have a higher capacitance than that predicted by the model. üAs line widths are scaled, the width (w) and heights of wires tend to reduce less than their separations. 24 üAccordingly, this fringing effect increases in importance.

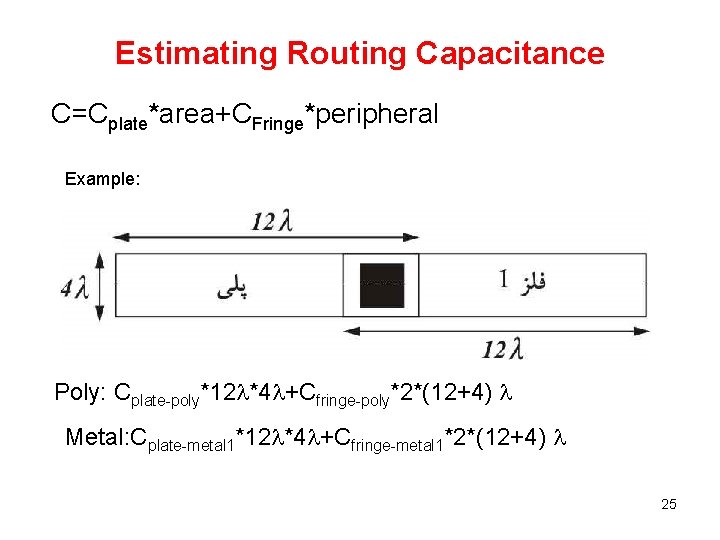

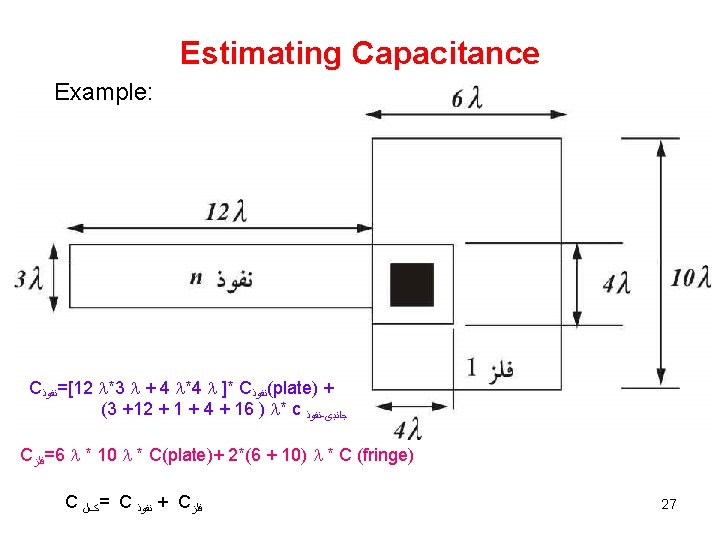

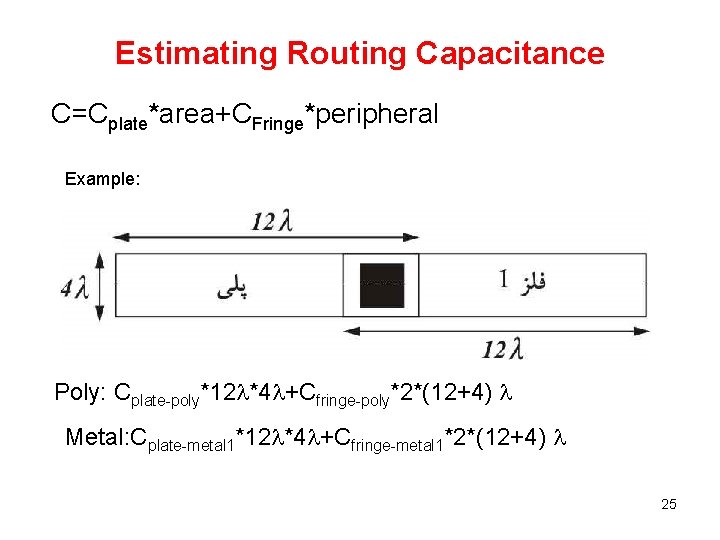

Estimating Routing Capacitance C=Cplate*area+CFringe*peripheral Example: Poly: Cplate-poly*12 *4 +Cfringe-poly*2*(12+4) Metal: Cplate-metal 1*12 *4 +Cfringe-metal 1*2*(12+4) 25

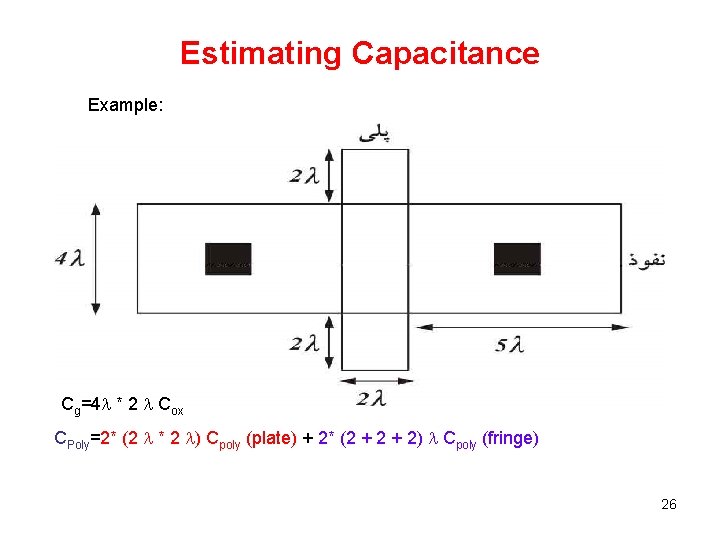

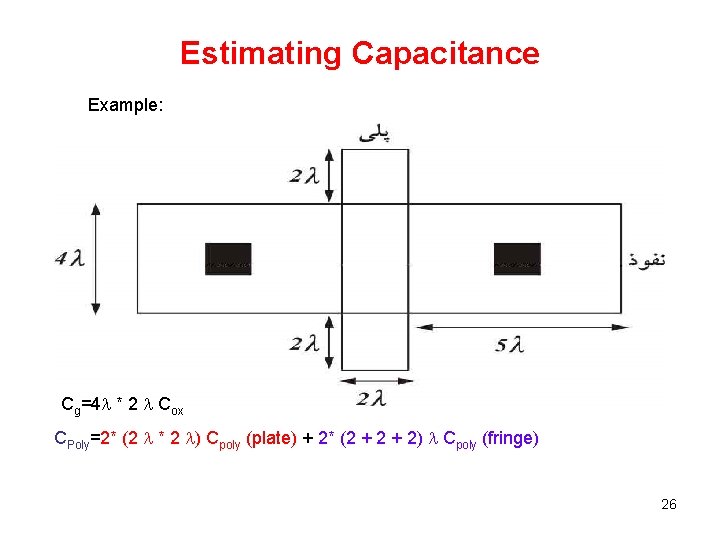

Estimating Capacitance Example: Cg=4 * 2 Cox CPoly=2* (2 * 2 ) Cpoly (plate) + 2* (2 + 2) Cpoly (fringe) 26

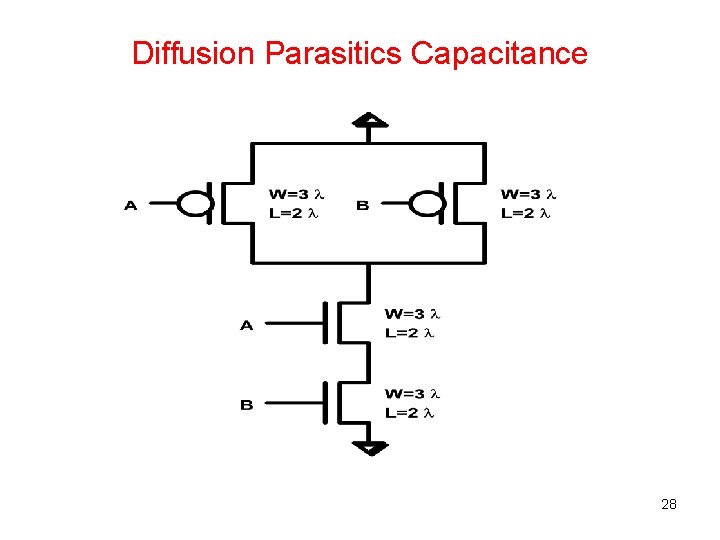

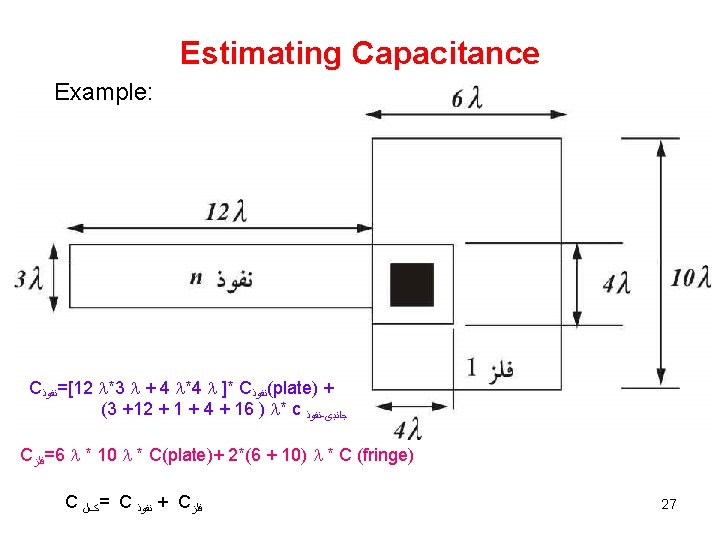

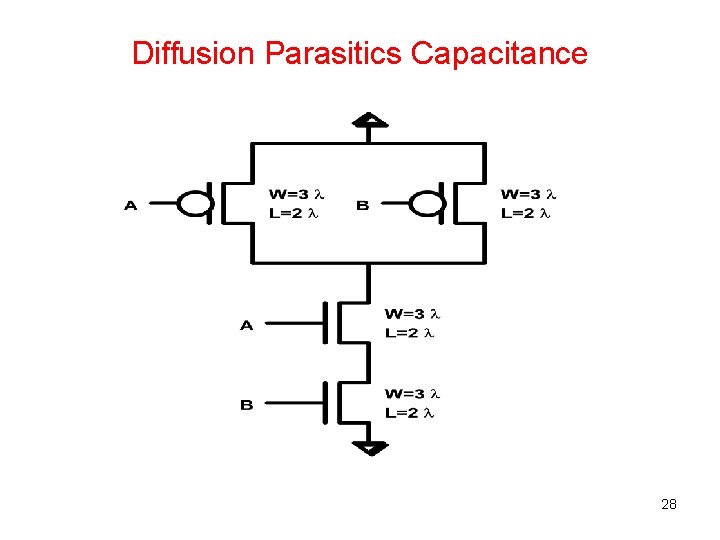

Diffusion Parasitics Capacitance 28

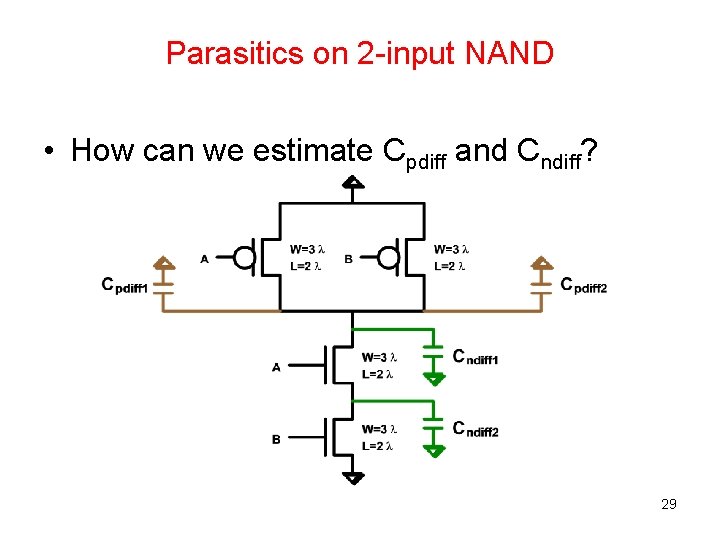

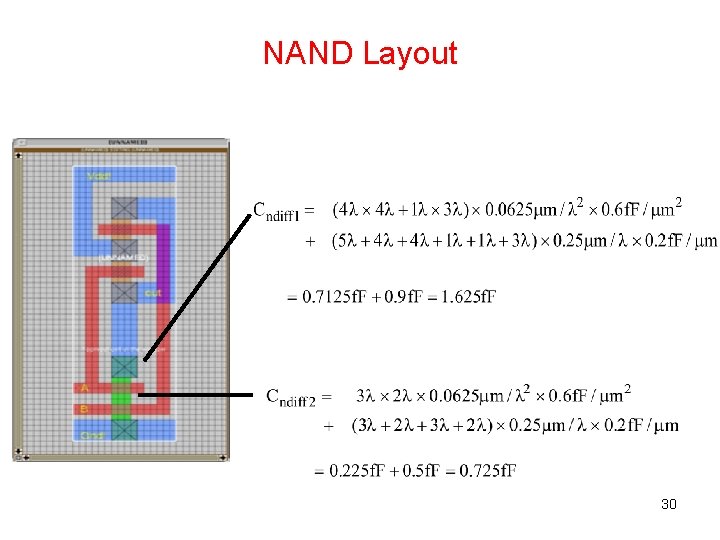

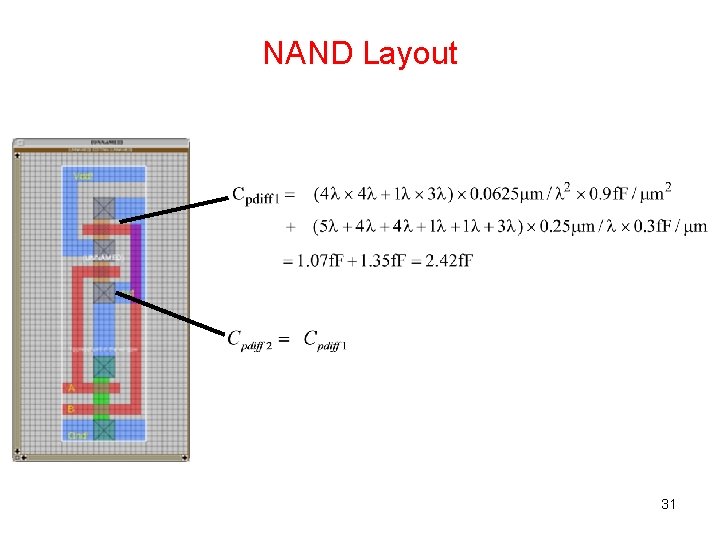

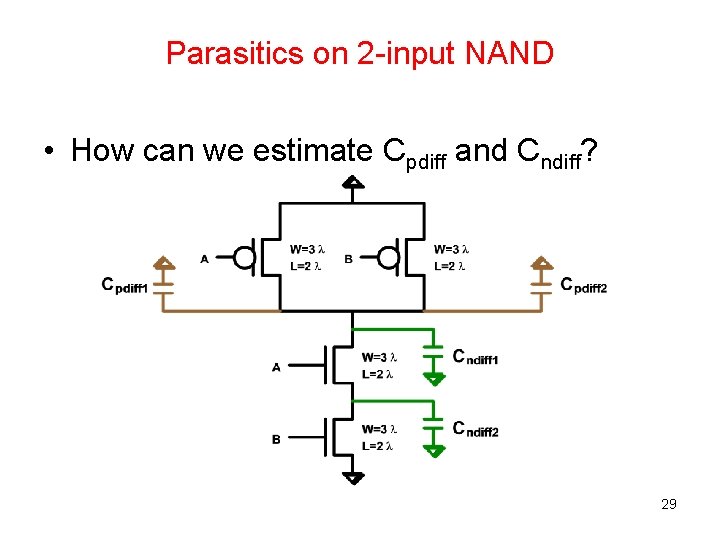

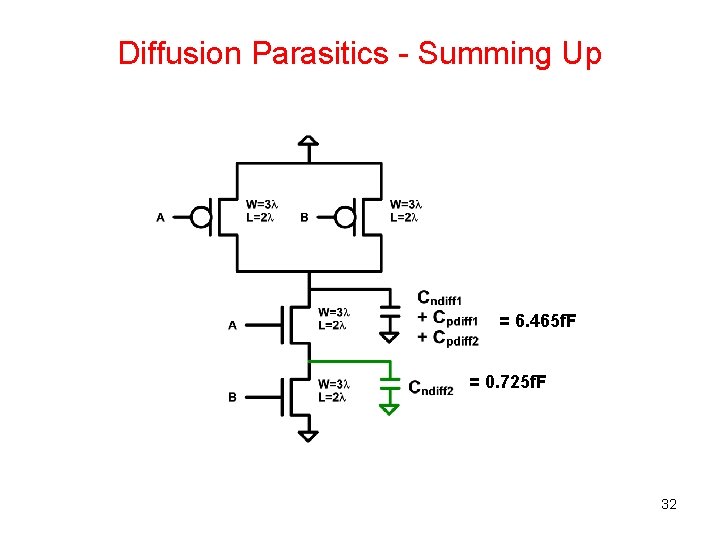

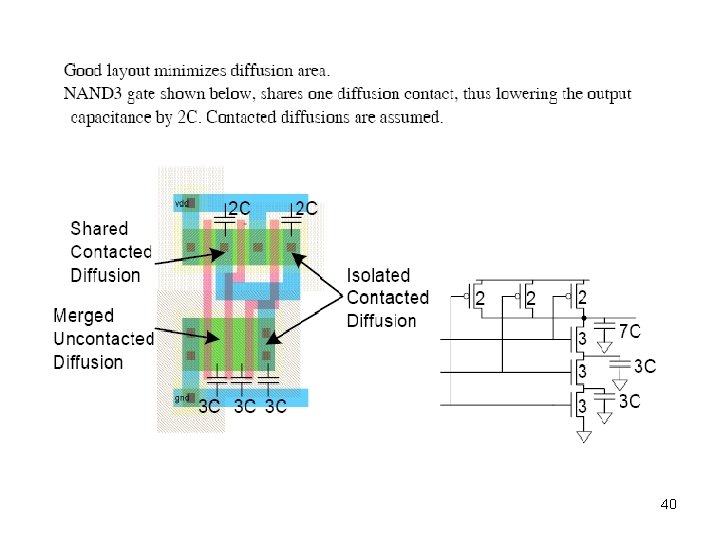

Parasitics on 2 -input NAND • How can we estimate Cpdiff and Cndiff? 29

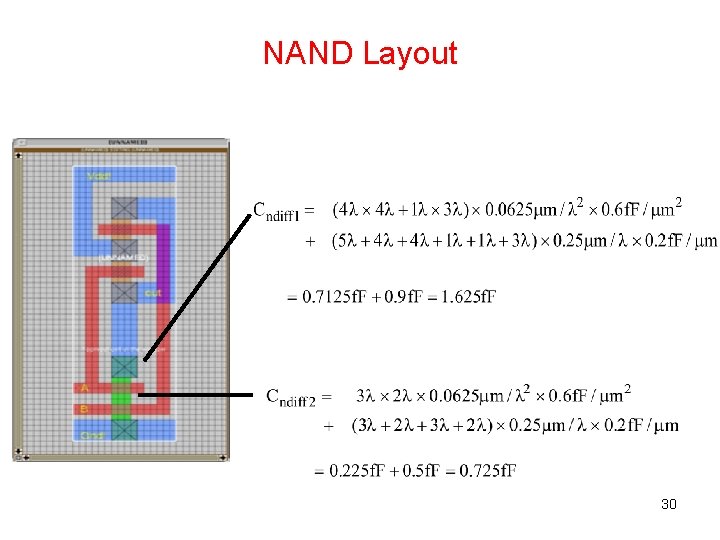

NAND Layout 30

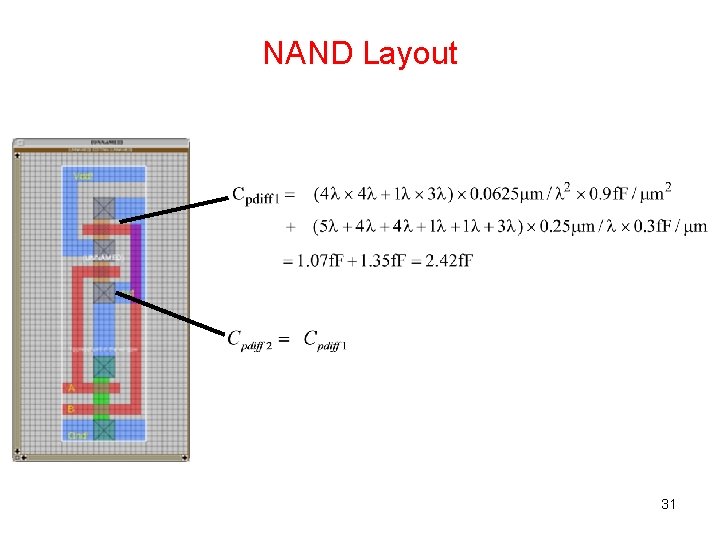

NAND Layout 31

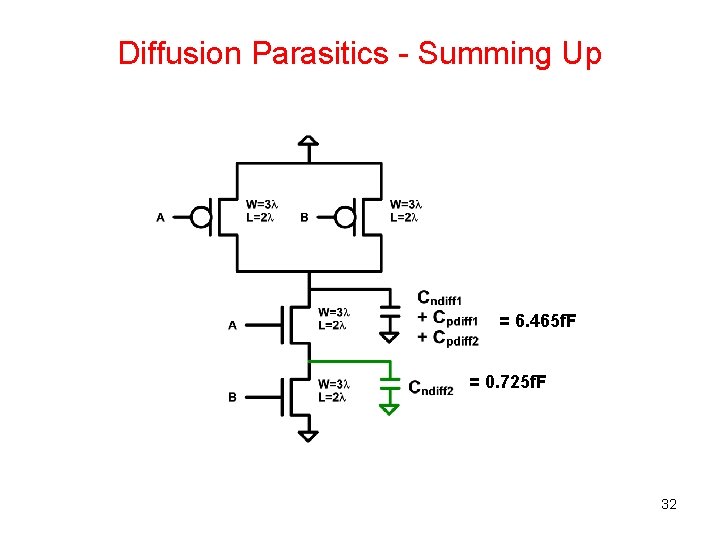

Diffusion Parasitics - Summing Up = 6. 465 f. F = 0. 725 f. F 32

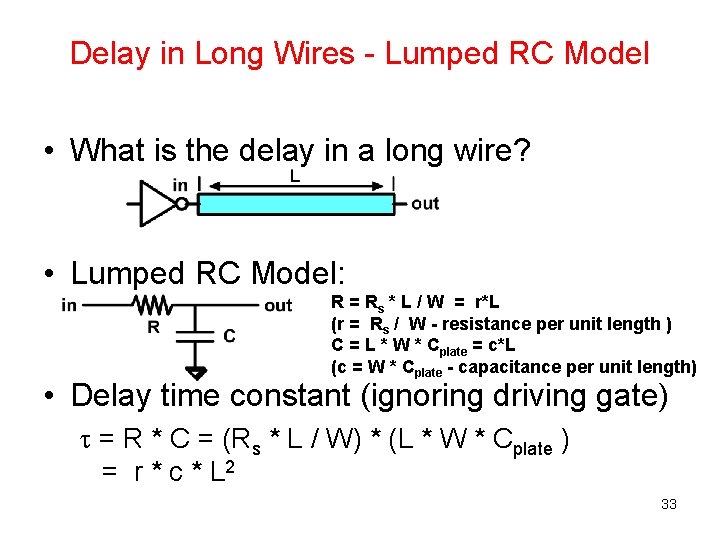

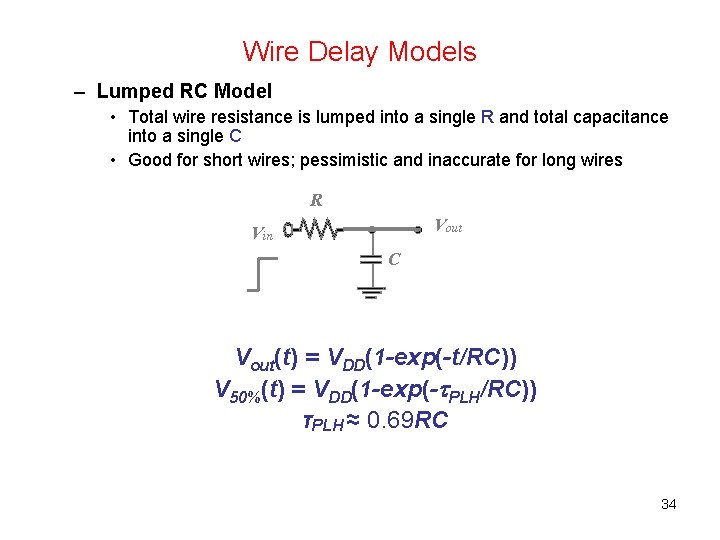

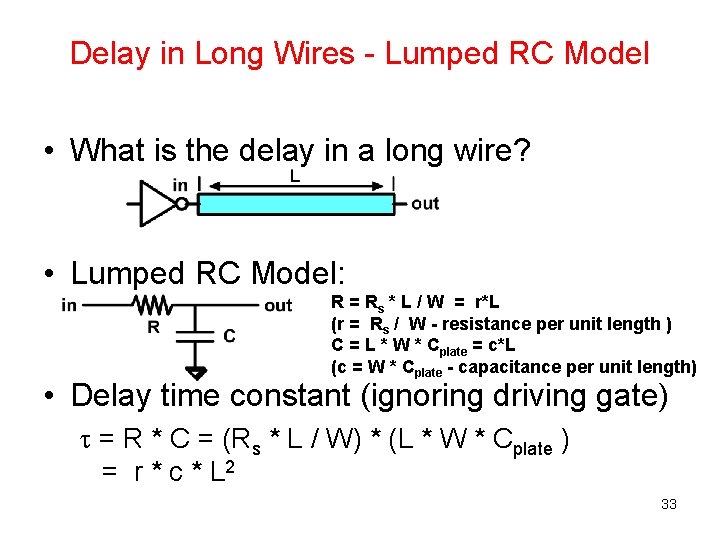

Delay in Long Wires - Lumped RC Model • What is the delay in a long wire? • Lumped RC Model: R = Rs * L / W = r*L (r = Rs / W - resistance per unit length ) C = L * W * Cplate = c*L (c = W * Cplate - capacitance per unit length) • Delay time constant (ignoring driving gate) t = R * C = (Rs * L / W) * (L * W * Cplate ) = r * c * L 2 33

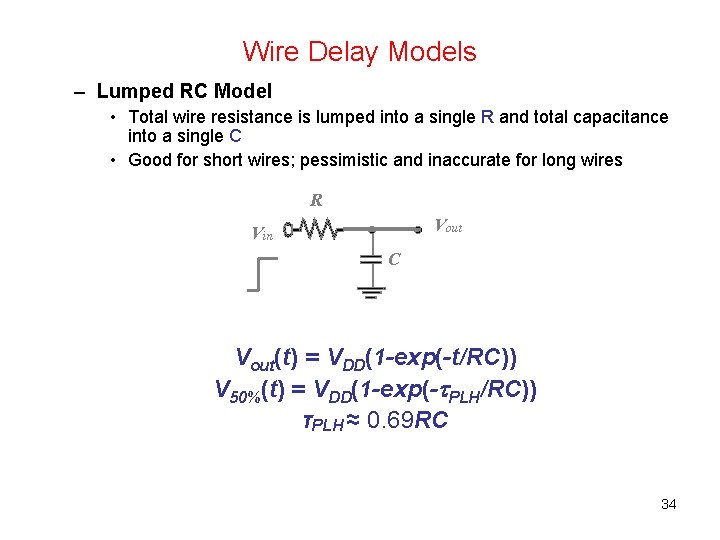

Wire Delay Models – Lumped RC Model • Total wire resistance is lumped into a single R and total capacitance into a single C • Good for short wires; pessimistic and inaccurate for long wires R Vout Vin C Vout(t) = VDD(1 -exp(-t/RC)) V 50%(t) = VDD(1 -exp(- PLH/RC)) τPLH ≈ 0. 69 RC 34

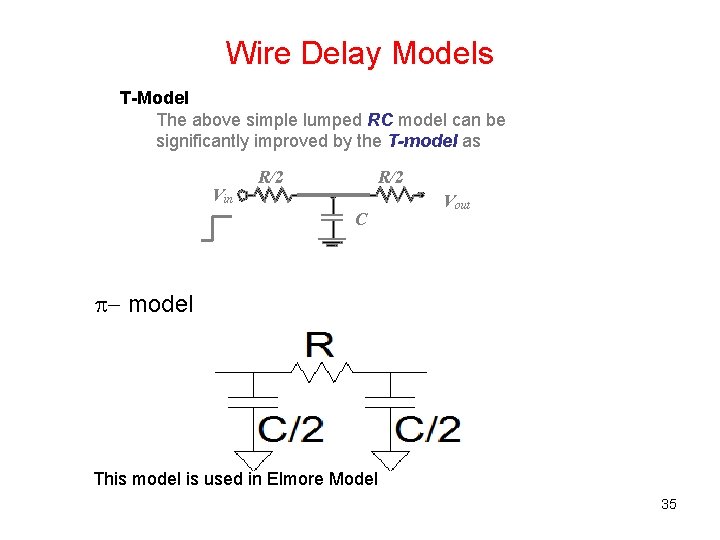

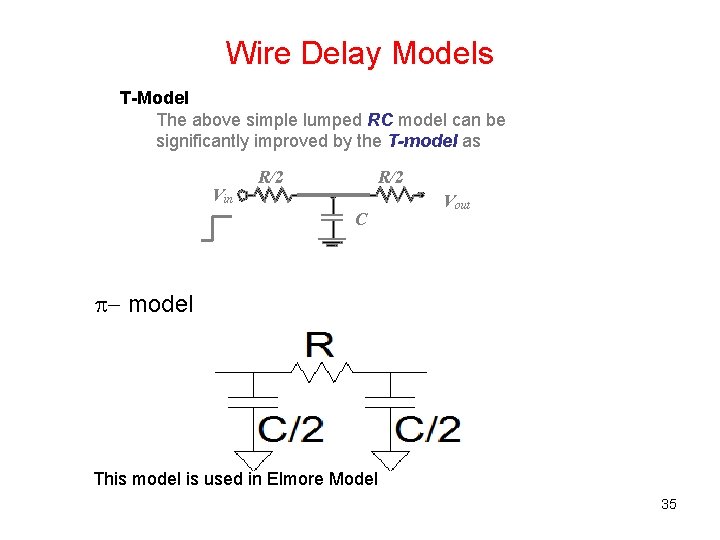

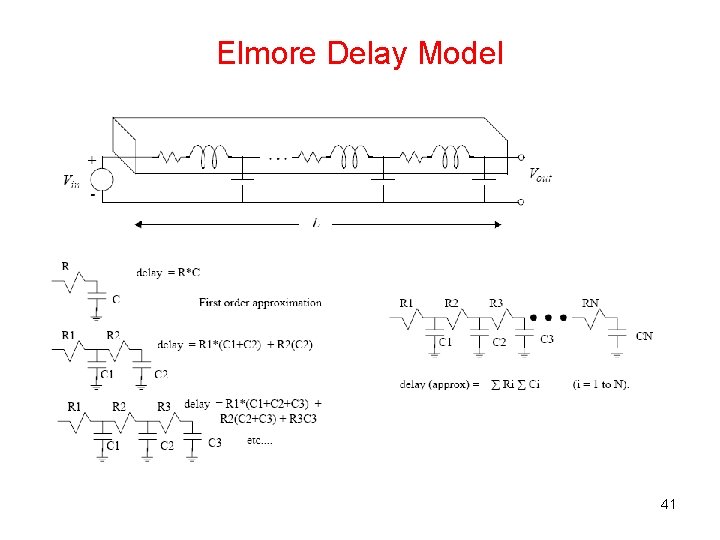

Wire Delay Models T-Model The above simple lumped RC model can be significantly improved by the T-model as Vin R/2 C Vout - model This model is used in Elmore Model 35

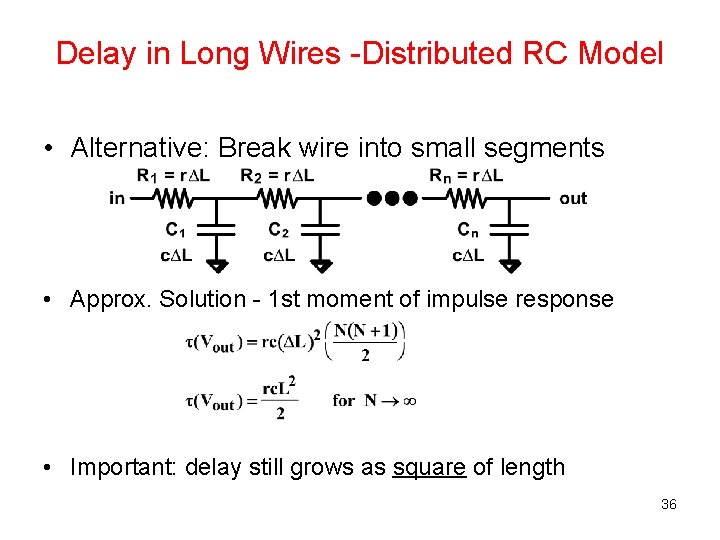

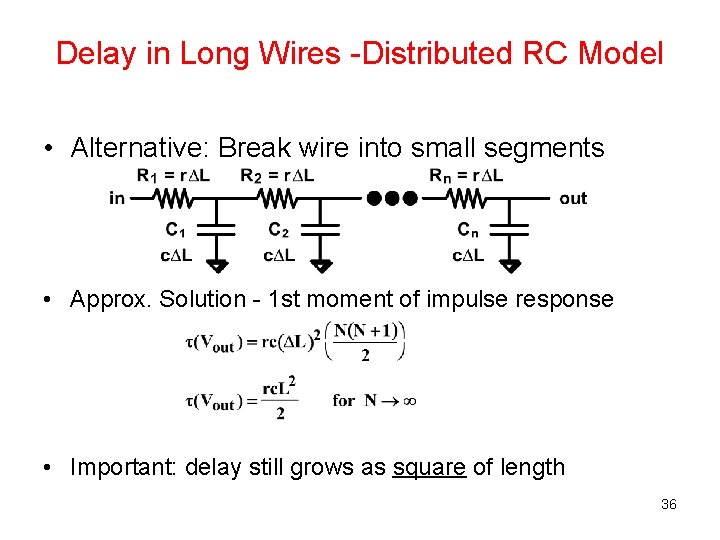

Delay in Long Wires -Distributed RC Model • Alternative: Break wire into small segments • Approx. Solution - 1 st moment of impulse response • Important: delay still grows as square of length 36

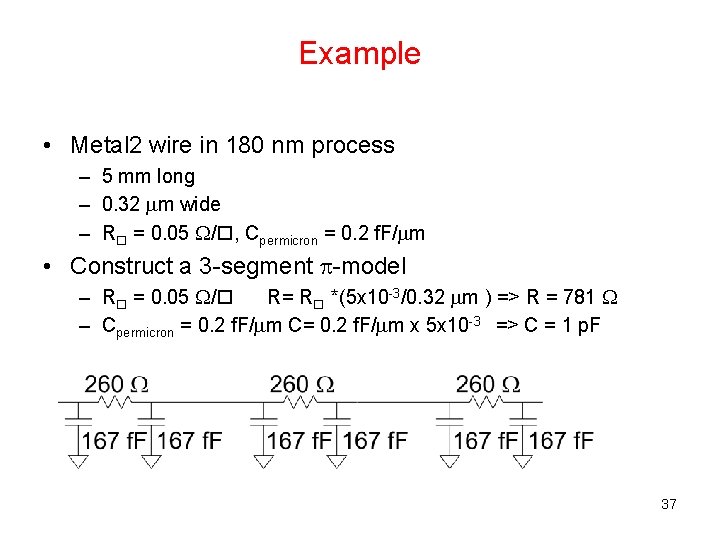

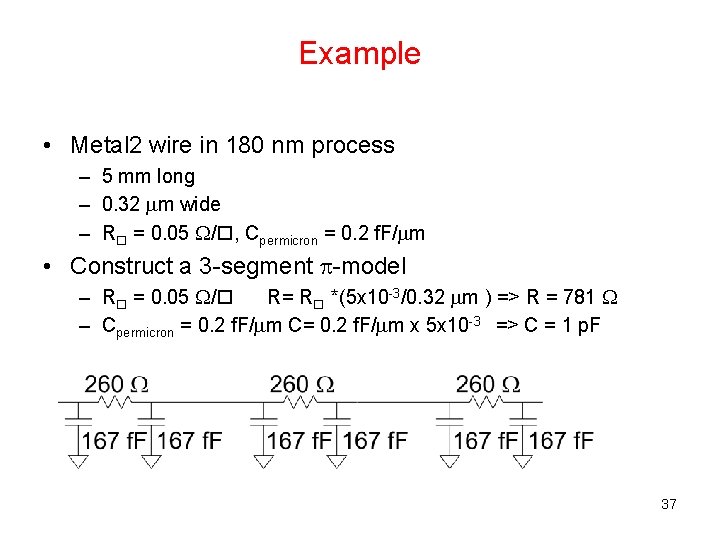

Example • Metal 2 wire in 180 nm process – 5 mm long – 0. 32 m wide – R = 0. 05 / , Cpermicron = 0. 2 f. F/ m • Construct a 3 -segment -model – R = 0. 05 / R= R *(5 x 10 -3/0. 32 m ) => R = 781 – Cpermicron = 0. 2 f. F/ m C= 0. 2 f. F/ m x 5 x 10 -3 => C = 1 p. F 37

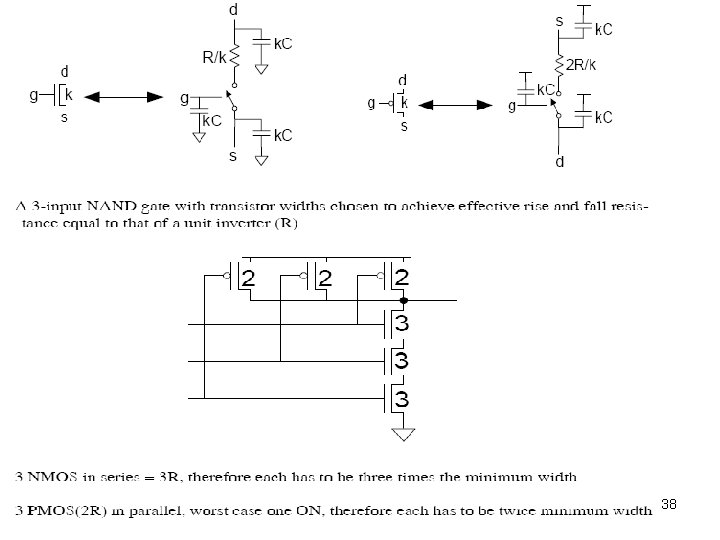

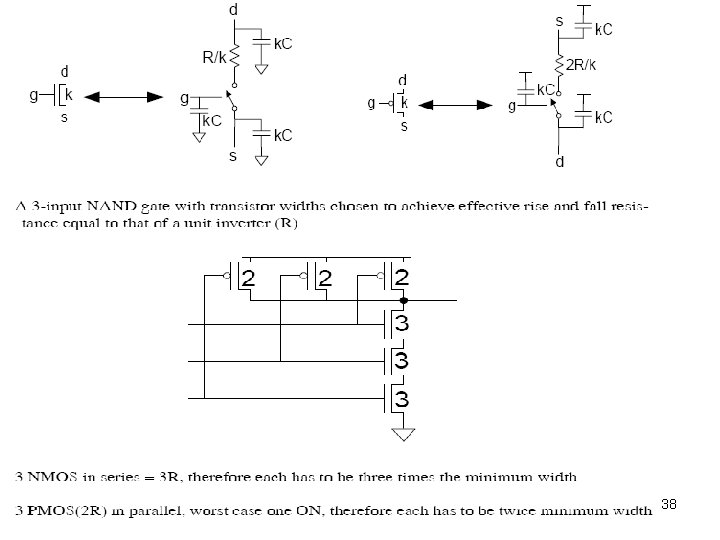

38

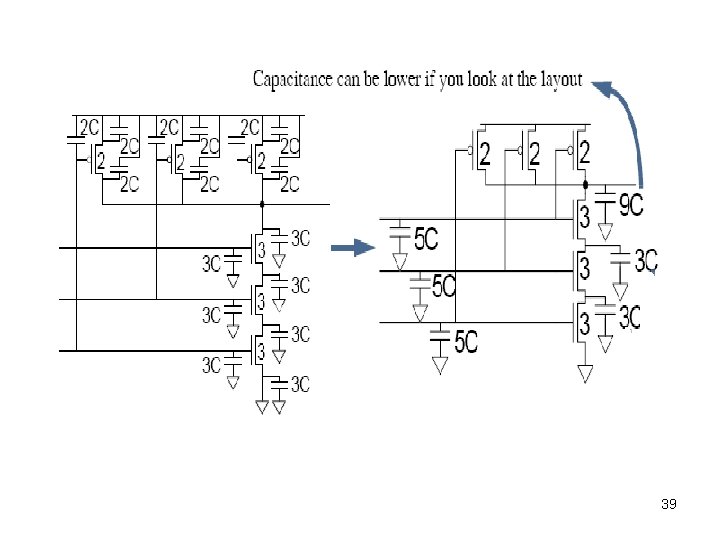

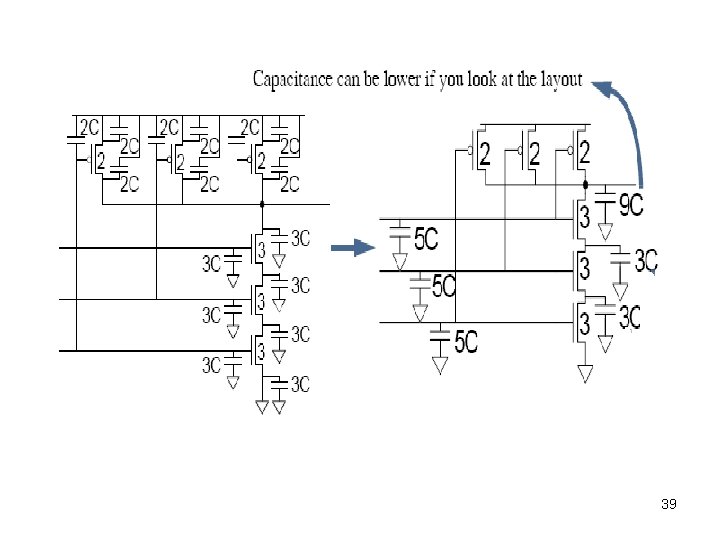

39

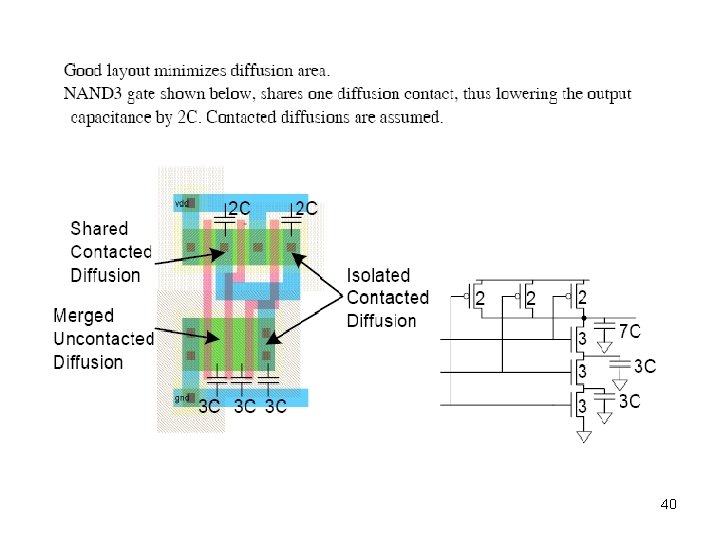

40

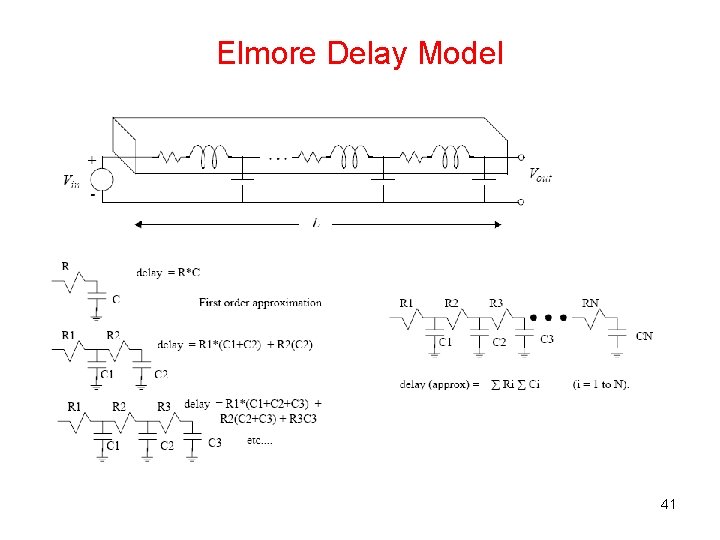

Elmore Delay Model 41

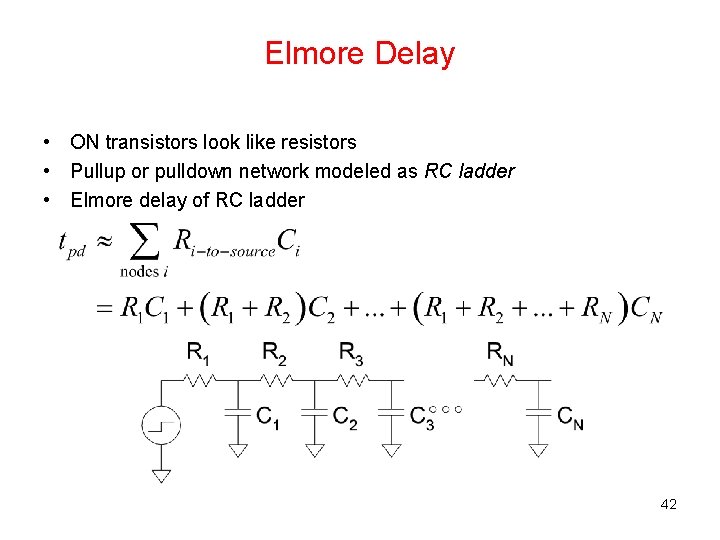

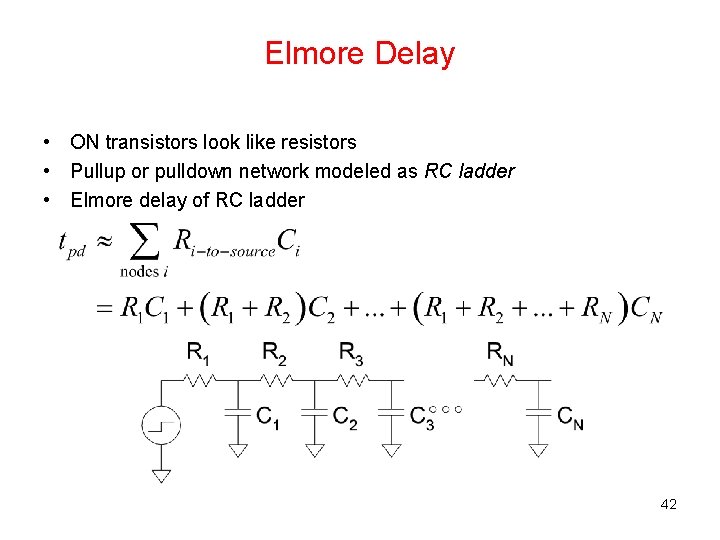

Elmore Delay • ON transistors look like resistors • Pullup or pulldown network modeled as RC ladder • Elmore delay of RC ladder 42

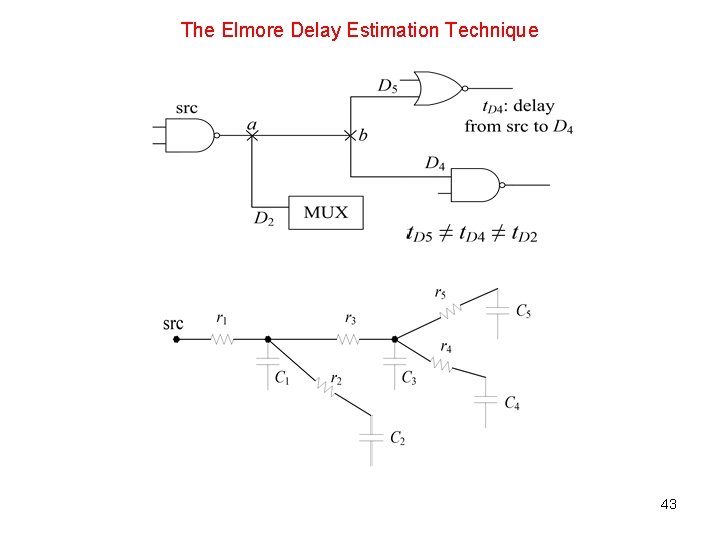

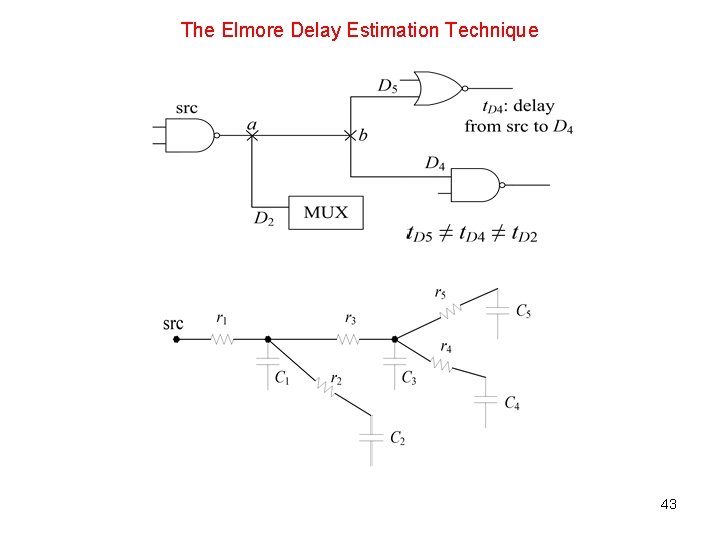

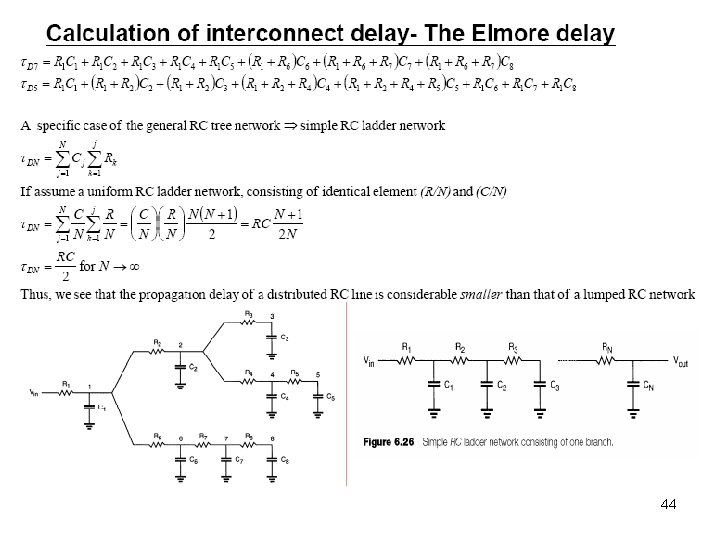

The Elmore Delay Estimation Technique 43

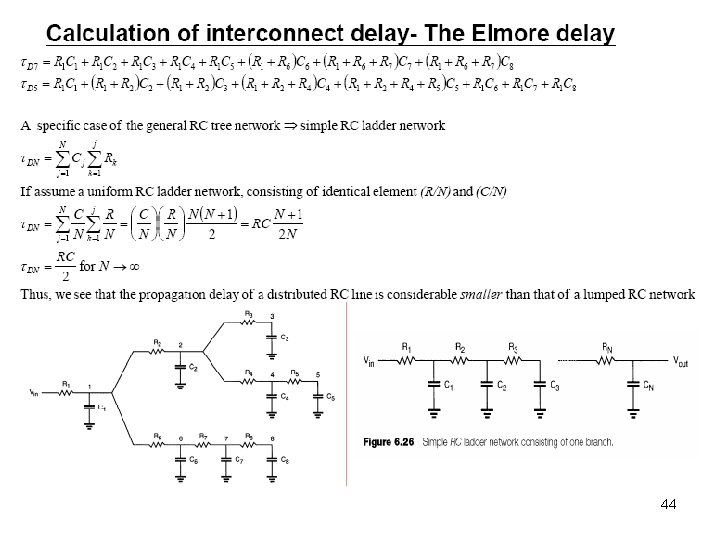

44

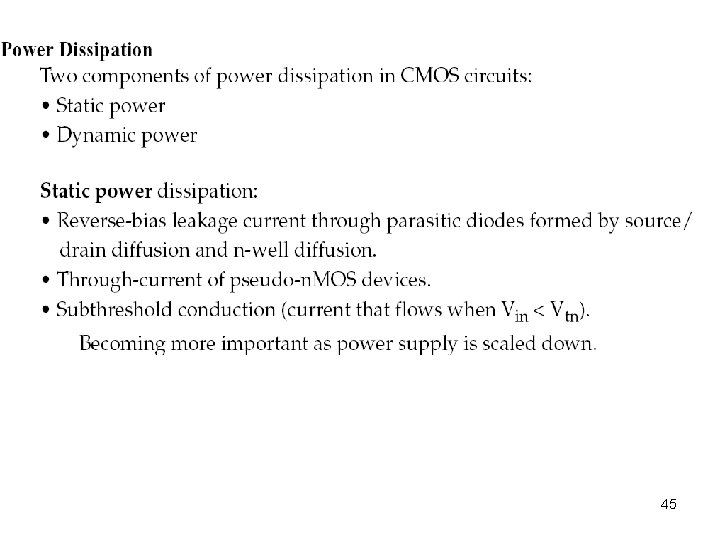

45

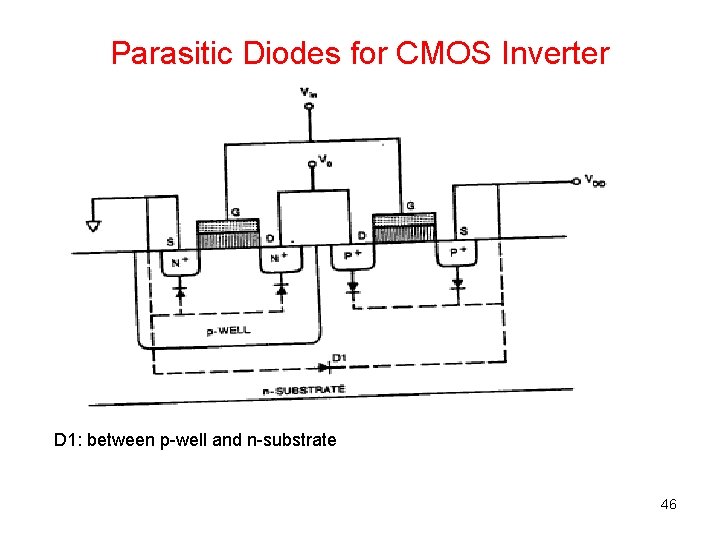

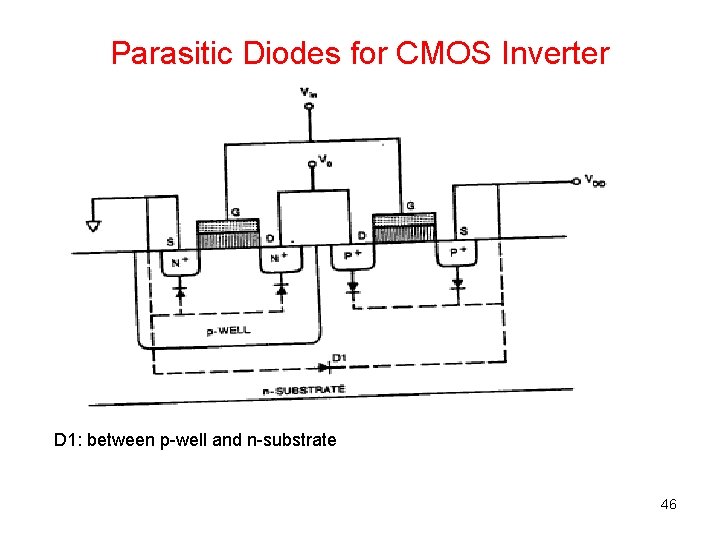

Parasitic Diodes for CMOS Inverter D 1: between p-well and n-substrate 46

47

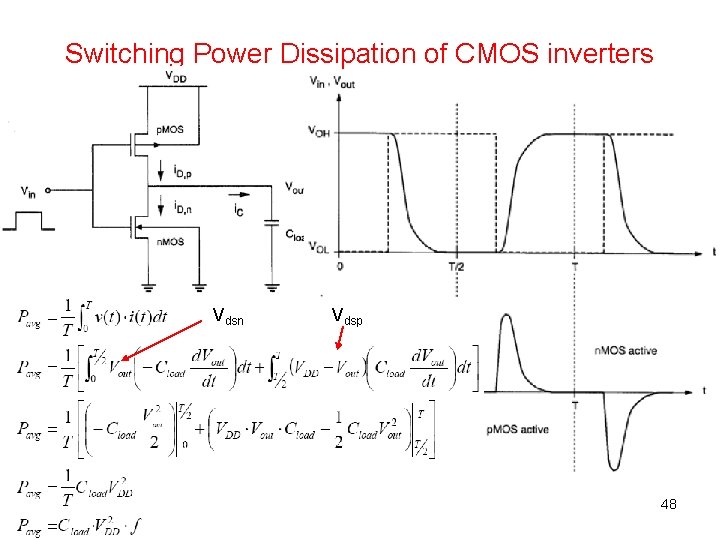

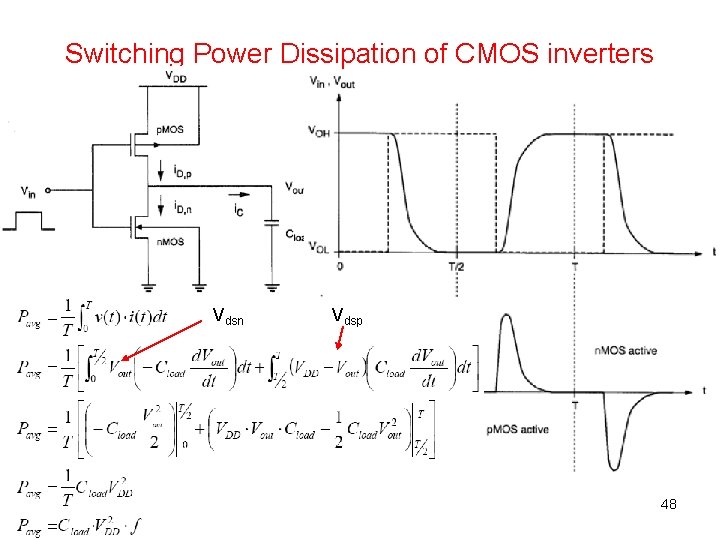

Switching Power Dissipation of CMOS inverters Vdsn Vdsp 48