Chapter 4 b Statistical Static Timing Analysis SSTA

Chapter 4 b Statistical Static Timing Analysis: SSTA Prof. Lei He Electrical Engineering Department University of California, Los Angeles URL: eda. ee. ucla. edu Email: lhe@ee. ucla. edu

Outline • Motivation • Statistic Static Timing Analysis (SSTA) n n Monte Carlo simulation Path-based and block-based SSTA

Variation-aware Timing Analysis How process variation would affect our STA? • n n Min-Max approach would be too risky Corner-based STA is too expensive: 2^n corners To be accurate, analyze timing statistically. But how? • n n Every label (delays) in the DAG is modeled as a R. V. with certain distribution Should use multivariate R. V. analysis – Correlation is the Key!

Statistical Static Timing Analysis: SSTA Fairly new (hot) topic • n n Many debates Many new ideas Not quite consistency across different ref. Unfortunately/Fortunately, live with it… In this lecture, cover some typical ones • n n Monte Carlo simulation (Golden case) One path-based approach One block-based approach More for your own entertainment

Outline • Motivation • Statistic Static Timing Analysis (SSTA) n n Monte Carlo simulation Path-based and block-based SSTA

Monte Carlo Simulation Definition: • n A technique involving the use of random numbers solving physical or mathematical problems Characteristics • n n Physical process is simulated without explicitly knowing equations that describe the system output Only requirement is that the physical system be described by PDF (probabilistic density function)

Monte Carlo for SSTA • Randomly sample each R. V. in accordance with its respective PDF • Instantiate a specific DAG • Solving STA using the technique we discussed before • This is called one Monte Carlo run • Run it many times until certain data statistics converge n Stopping condition can be fairly sophisticated Finally, extract statistics from Monte Carlo runs • n n n PDF of RAT/AT/Slack Yield curve …

Monte Carlo Simulation Pros • n n Conceptually easy Implementation not that difficult Make use of previous STA algorithm Accurate, used as golden case (benchmarking) Cons • n n n Computationally expensive No many diagnostic information if something is wrong No incremental computation possible Efficient solution • n Analytical Statistical static timing analysis (SSTA)

Outline • Motivation • Statistic Static Timing Analysis (SSTA) n n Monte Carlo simulation Path-based and block-based SSTA

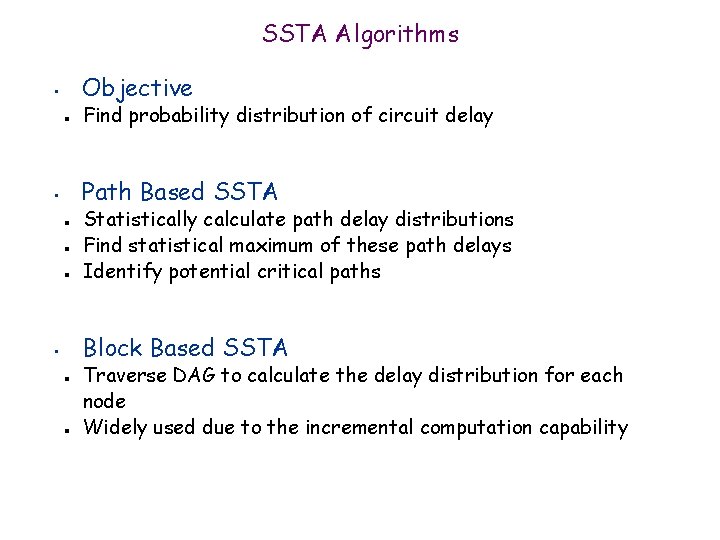

SSTA Algorithms Objective • n Find probability distribution of circuit delay Path Based SSTA • n n n Statistically calculate path delay distributions Find statistical maximum of these path delays Identify potential critical paths Block Based SSTA • n n Traverse DAG to calculate the delay distribution for each node Widely used due to the incremental computation capability

![Path-based SSTA [Orshansky DAC-02] • Key operations n n • Summation – Path delay Path-based SSTA [Orshansky DAC-02] • Key operations n n • Summation – Path delay](http://slidetodoc.com/presentation_image/4b0ae66046c07a288718e9ca0397567e/image-11.jpg)

Path-based SSTA [Orshansky DAC-02] • Key operations n n • Summation – Path delay = sum(node delay) Maximum – Critical path delay = max(path delay) Delay model n n First order approximation Obtained from SPICE simulation

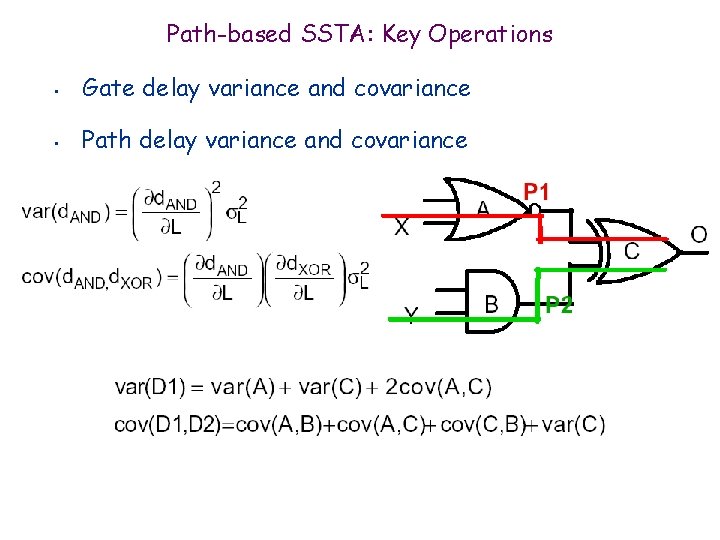

Path-based SSTA: Key Operations • Gate delay variance and covariance • Path delay variance and covariance

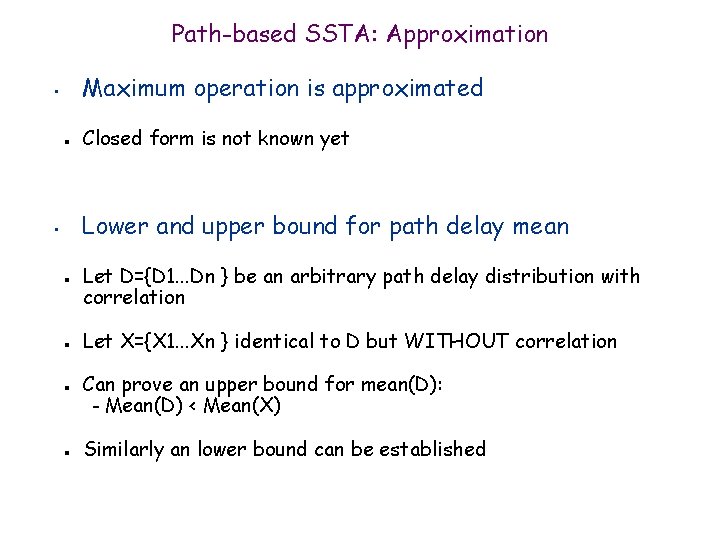

Path-based SSTA: Approximation Maximum operation is approximated • n Closed form is not known yet Lower and upper bound for path delay mean • n n Let D={D 1. . . Dn } be an arbitrary path delay distribution with correlation Let X={X 1. . . Xn } identical to D but WITHOUT correlation Can prove an upper bound for mean(D): – Mean(D) < Mean(X) Similarly an lower bound can be established

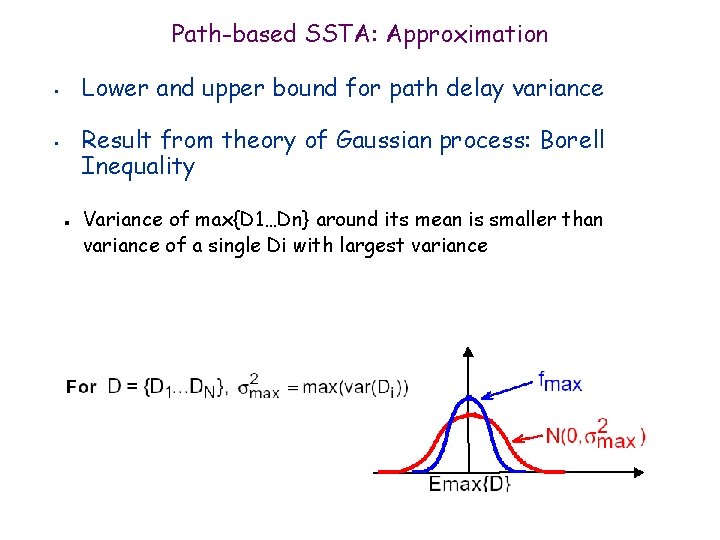

Path-based SSTA: Approximation Lower and upper bound for path delay variance • Result from theory of Gaussian process: Borell Inequality • n Variance of max{D 1…Dn} around its mean is smaller than variance of a single Di with largest variance

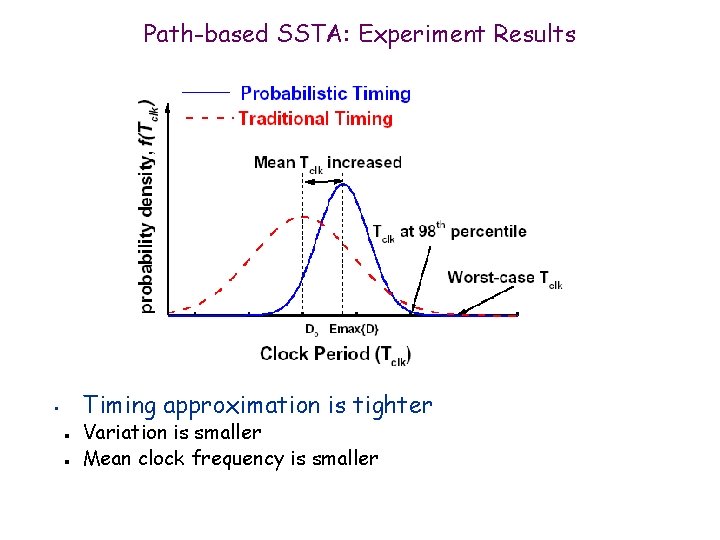

Path-based SSTA: Experiment Results Timing approximation is tighter • n n Variation is smaller Mean clock frequency is smaller

![Block-based SSTA: [Devgan ICCAD 03] AT and gate delays are modeled as R. V. Block-based SSTA: [Devgan ICCAD 03] AT and gate delays are modeled as R. V.](http://slidetodoc.com/presentation_image/4b0ae66046c07a288718e9ca0397567e/image-16.jpg)

Block-based SSTA: [Devgan ICCAD 03] AT and gate delays are modeled as R. V. • n n n AT as CDFs Gate Delays as PDFs For easy computation Delay distributions can take any form • n n Model CDFs as Piece-Wise Linear functions Model PDFs as constant step functions 1. 0 P 3 Cumulative Probability P 2 P 1 A A 1 A 2 A 3

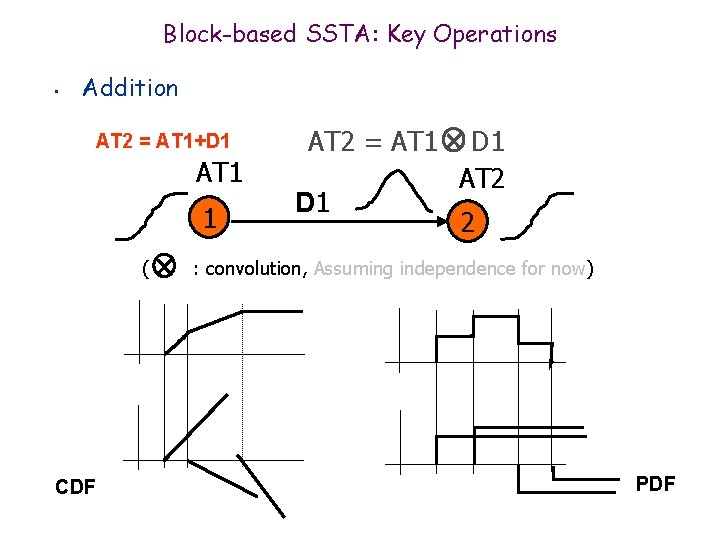

Block-based SSTA: Key Operations • Addition AT 2 = AT 1+D 1 AT 1 1 ( CDF AT 2 = AT 1 D 1 AT 2 2 : convolution, Assuming independence for now) PDF

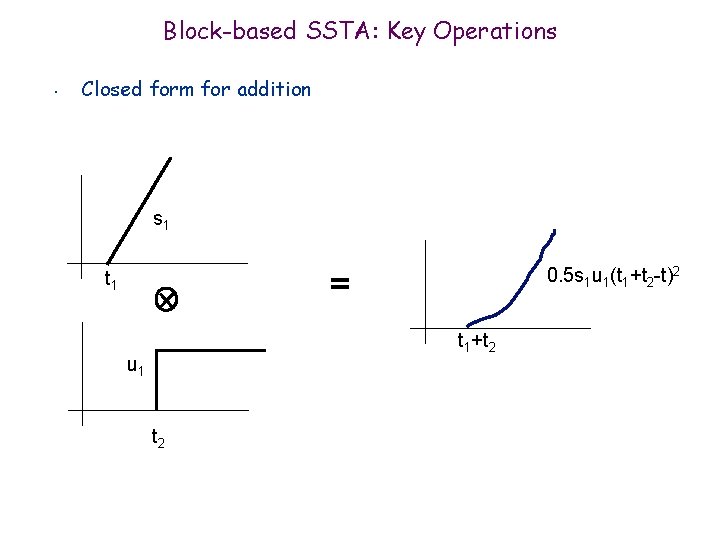

Block-based SSTA: Key Operations • Closed form for addition s 1 0. 5 s 1 u 1(t 1+t 2 -t)2 = t 1+t 2 u 1 t 2

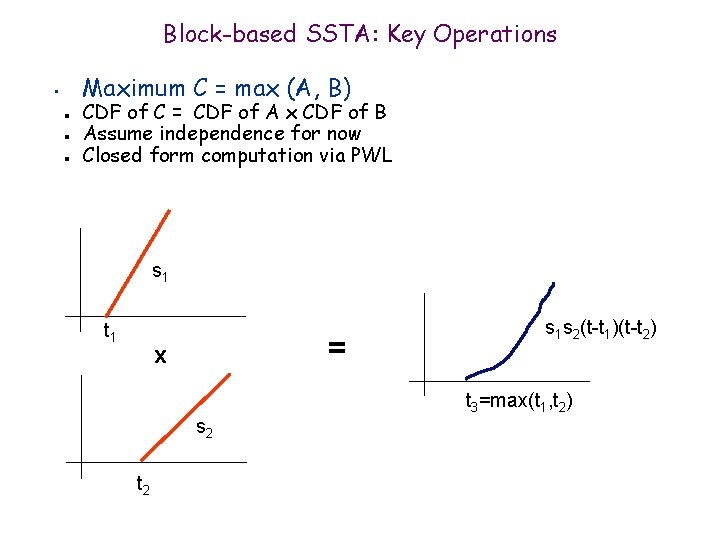

Block-based SSTA: Key Operations Maximum C = max (A, B) • n n n CDF of C = CDF of A x CDF of B Assume independence for now Closed form computation via PWL s 1 t 1 = x s 1 s 2(t-t 1)(t-t 2) t 3=max(t 1, t 2) s 2 t 2

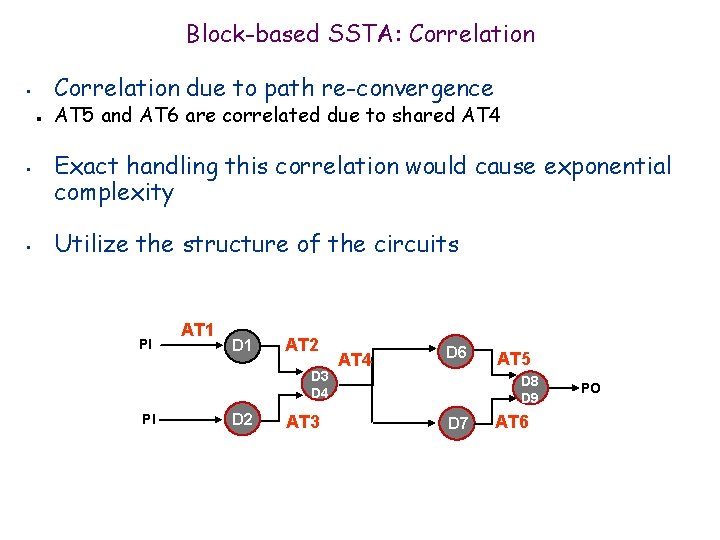

Block-based SSTA: Correlation due to path re-convergence • n • • AT 5 and AT 6 are correlated due to shared AT 4 Exact handling this correlation would cause exponential complexity Utilize the structure of the circuits PI AT 1 D 1 AT 2 D 3 D 4 PI D 2 AT 3 AT 4 D 6 AT 5 D 8 D 9 D 7 AT 6 PO

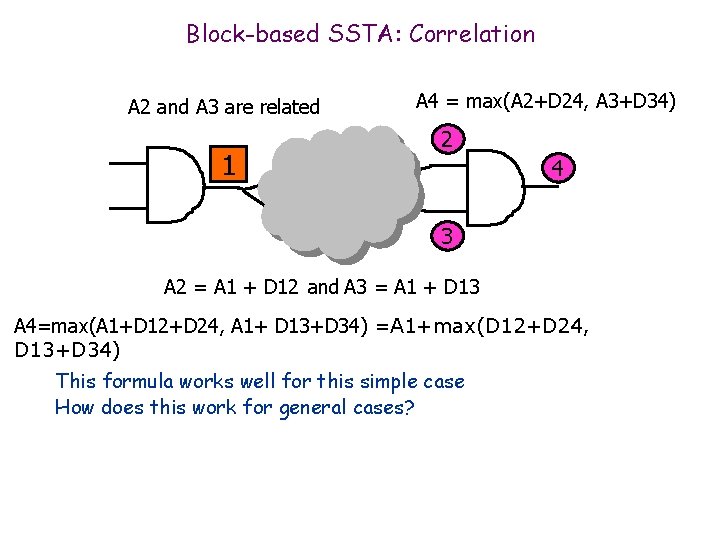

Block-based SSTA: Correlation A 2 and A 3 are related 1 A 4 = max(A 2+D 24, A 3+D 34) 2 4 3 A 2 = A 1 + D 12 and A 3 = A 1 + D 13 A 4=max(A 1+D 12+D 24, A 1+ D 13+D 34) =A 1+max(D 12+D 24, D 13+D 34) This formula works well for this simple case How does this work for general cases?

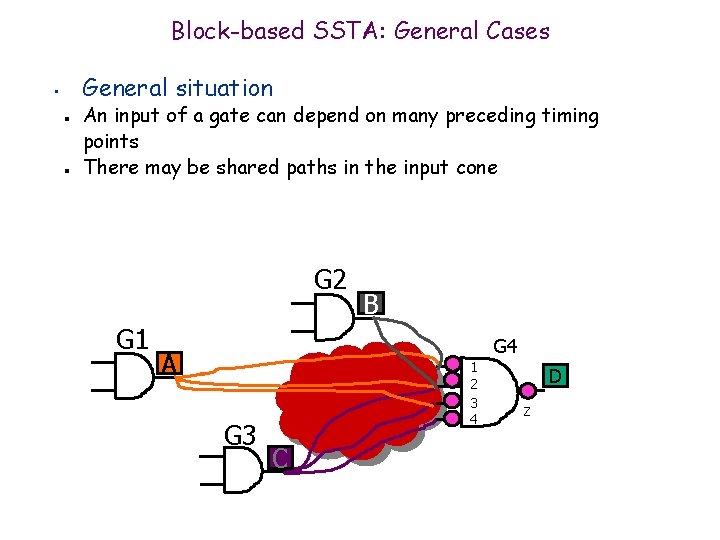

Block-based SSTA: General Cases General situation • n n An input of a gate can depend on many preceding timing points There may be shared paths in the input cone G 2 G 1 B G 4 A G 3 1 2 3 4 C D z

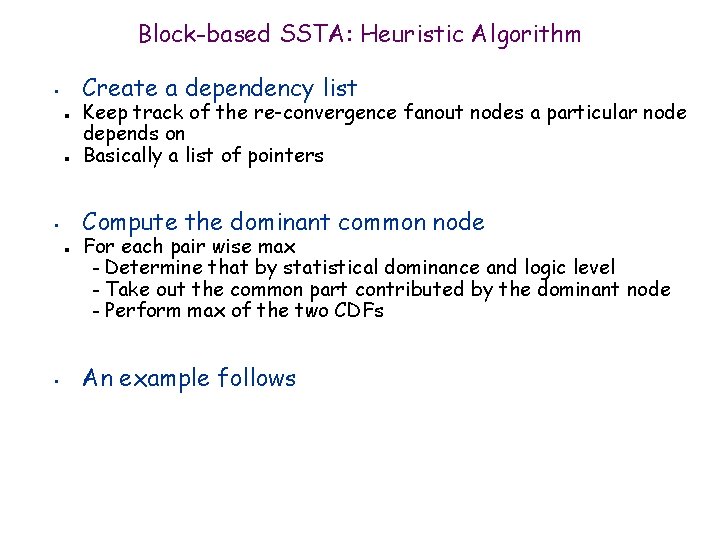

Block-based SSTA: Heuristic Algorithm Create a dependency list • n n Compute the dominant common node • n • Keep track of the re-convergence fanout nodes a particular node depends on Basically a list of pointers For each pair wise max – Determine that by statistical dominance and logic level – Take out the common part contributed by the dominant node – Perform max of the two CDFs An example follows

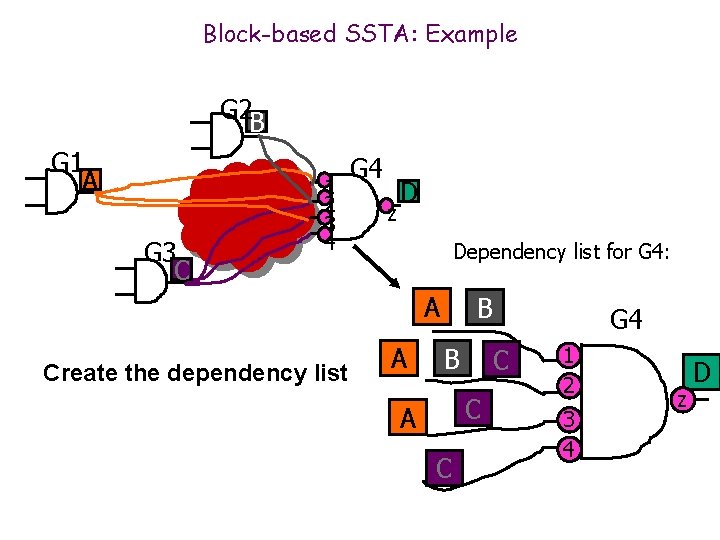

Block-based SSTA: Example G 2 B G 1 A G 3 C 1 2 3 4 G 4 z D Dependency list for G 4: A Create the dependency list A B B C C A C G 4 1 2 3 4 z D

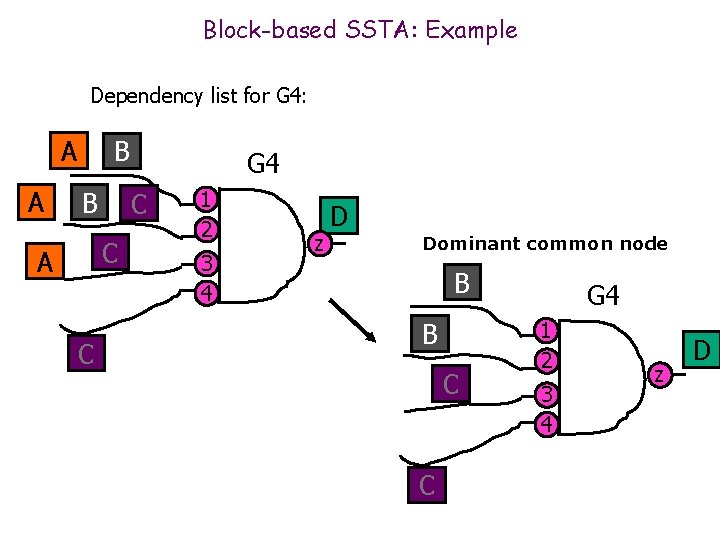

Block-based SSTA: Example Dependency list for G 4: A A B B C C A C G 4 1 2 3 4 z D Dominant common node B B C C G 4 1 2 3 4 z D

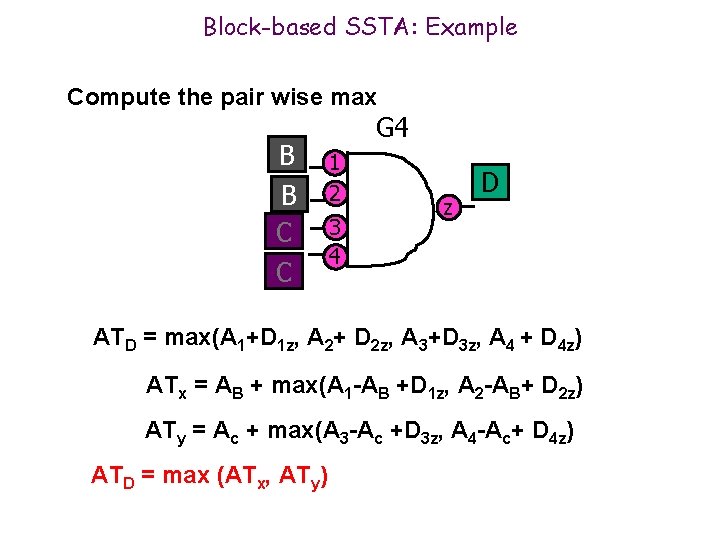

Block-based SSTA: Example Compute the pair wise max B B C C G 4 1 2 3 4 z D ATD = max(A 1+D 1 z, A 2+ D 2 z, A 3+D 3 z, A 4 + D 4 z) ATx = AB + max(A 1 -AB +D 1 z, A 2 -AB+ D 2 z) ATy = Ac + max(A 3 -Ac +D 3 z, A 4 -Ac+ D 4 z) ATD = max (ATx, ATy)

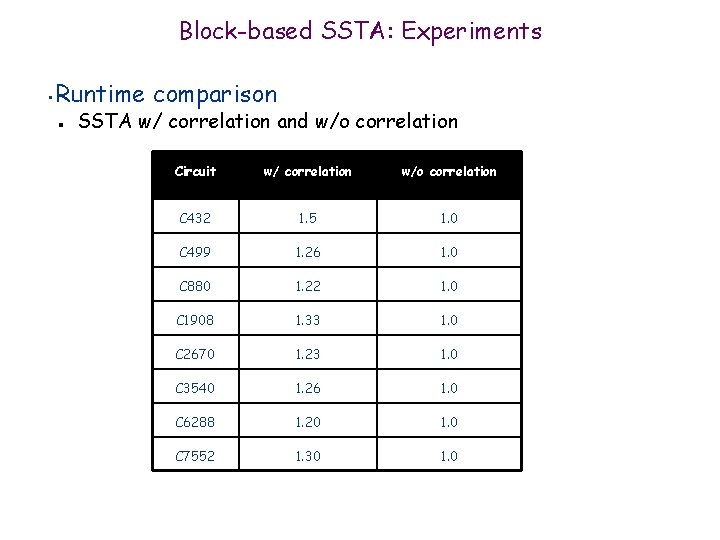

Block-based SSTA: Experiments • Runtime comparison n SSTA w/ correlation and w/o correlation Circuit w/ correlation w/o correlation C 432 1. 5 1. 0 C 499 1. 26 1. 0 C 880 1. 22 1. 0 C 1908 1. 33 1. 0 C 2670 1. 23 1. 0 C 3540 1. 26 1. 0 C 6288 1. 20 1. 0 C 7552 1. 30 1. 0

Block-based SSTA: Experiments Timing distribution • n SSTA w/ correlation and w/o correlation and Monte Carlo Simulation

Summary • Timing analysis is a key part of the design process • Statistical static timing analysis (SSTA) n Arises due to process variation when technology continues to scale More to be done for SSTA • n n n Correlations matter Interconnect variability Slew propagation Gate delay models How to guide for optimal design?

References n n Michael Orshansky and Kurt Keutzer. 2002. A general probabilistic framework for worst case timing analysis. In Proceedings of the 39 th annual Design Automation Conference (DAC '02). ACM, New York, NY, USA, 556 -561. Anirudh Devgan and Chandramouli Kashyap. 2003. Block-based Static Timing Analysis with Uncertainty. In Proceedings of the 2003 IEEE/ACM international conference on Computer-aided design (ICCAD '03). IEEE Computer Society, Washington, DC, USA

- Slides: 30