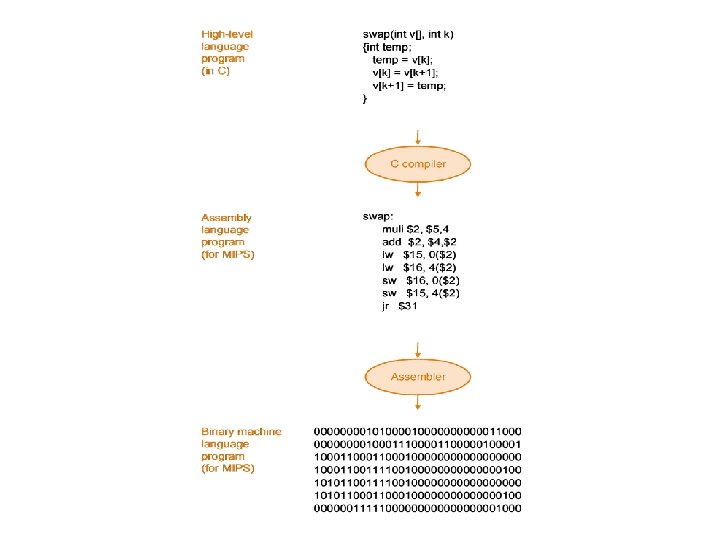

Chapter 3 System Buses Bus Interconnection Scheme Socket

Chapter 3 System Buses

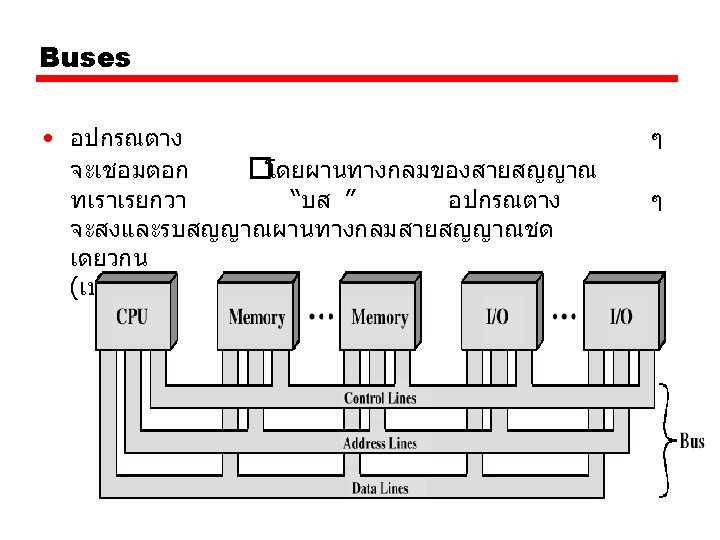

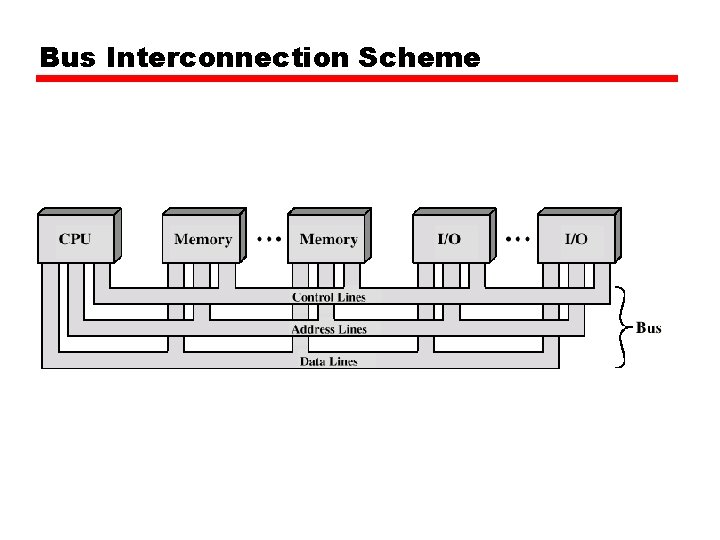

Bus Interconnection Scheme

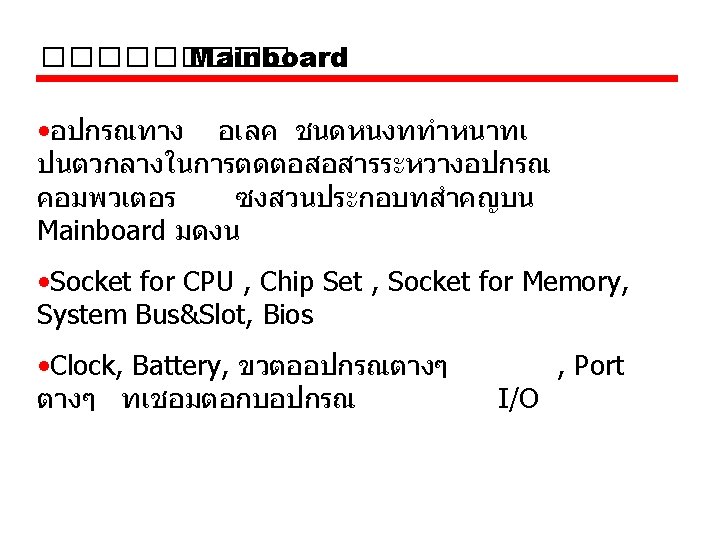

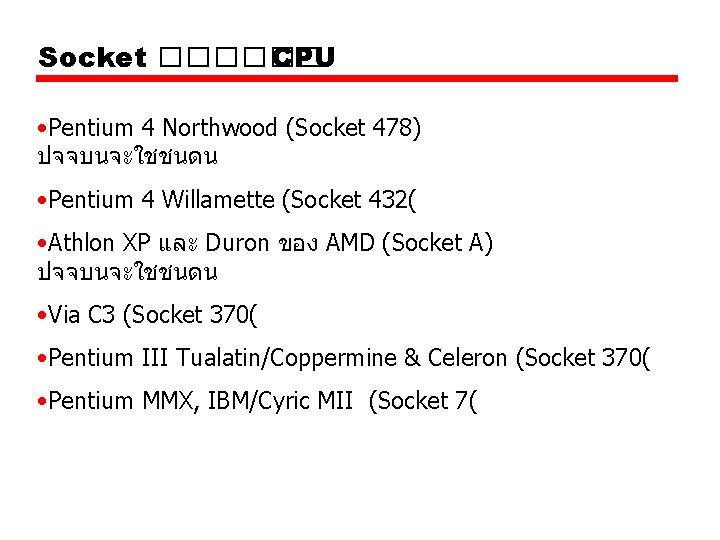

Socket ������ CPU • Pentium 4 Northwood (Socket 478) ปจจบนจะใชชนดน • Pentium 4 Willamette (Socket 432( • Athlon XP และ Duron ของ AMD (Socket A) ปจจบนจะใชชนดน • Via C 3 (Socket 370( • Pentium III Tualatin/Coppermine & Celeron (Socket 370( • Pentium MMX, IBM/Cyric MII (Socket 7(

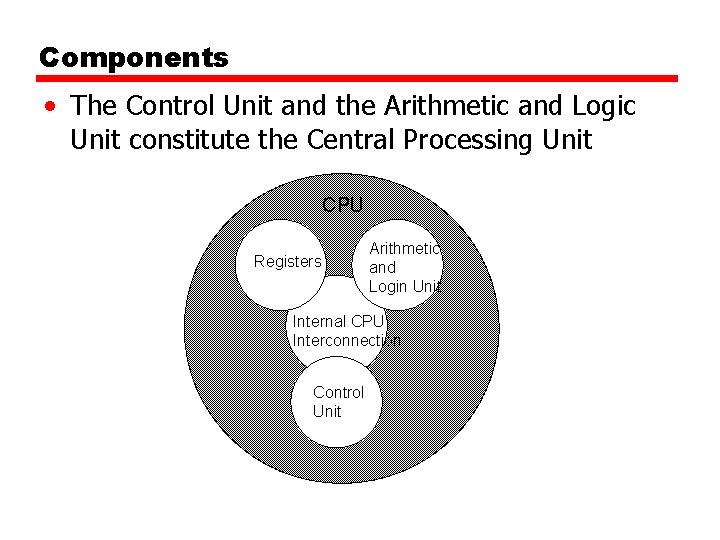

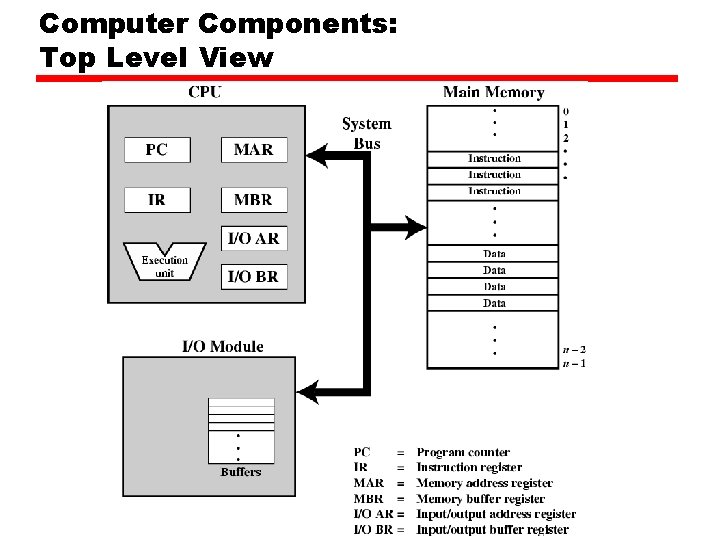

Components • The Control Unit and the Arithmetic and Logic Unit constitute the Central Processing Unit CPU Registers Arithmetic and Login Unit Internal CPU Interconnection Control Unit

Components • Data and instructions need to get into the system and results out —Input/output • Temporary storage of code and results is needed —Main memory

Computer Components: Top Level View

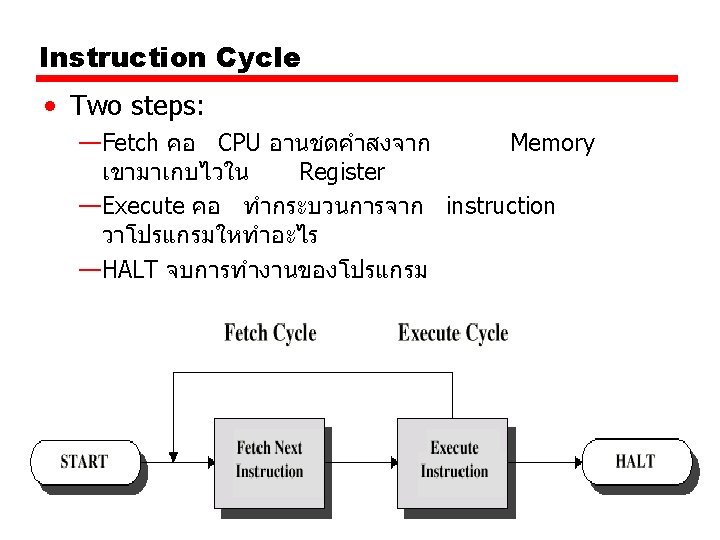

Fetch Cycle ขนตอนการ fetch วามการกระทำอะไรบาง • Program Counter (PC) holds address of next instruction to fetch • Processor fetches instruction from memory location pointed to by PC • Increment PC —Unless told otherwise • Instruction loaded into Instruction Register (IR) • Processor interprets instruction and performs required actions

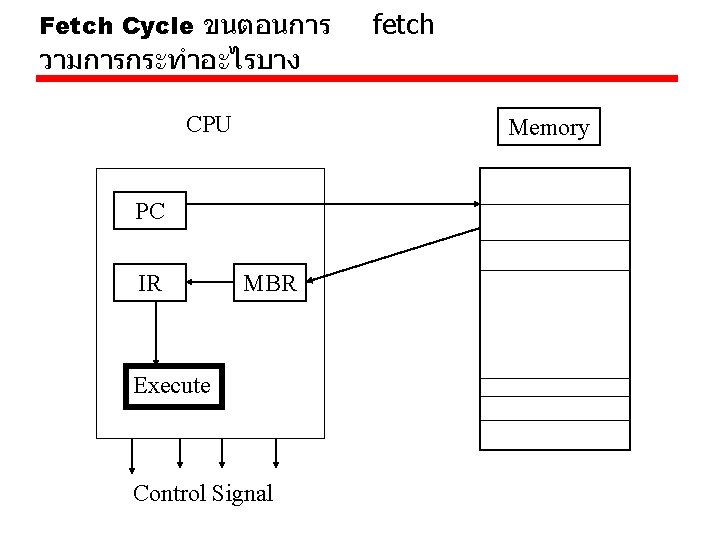

Fetch Cycle ขนตอนการ fetch วามการกระทำอะไรบาง CPU Memory PC IR MBR Execute Control Signal

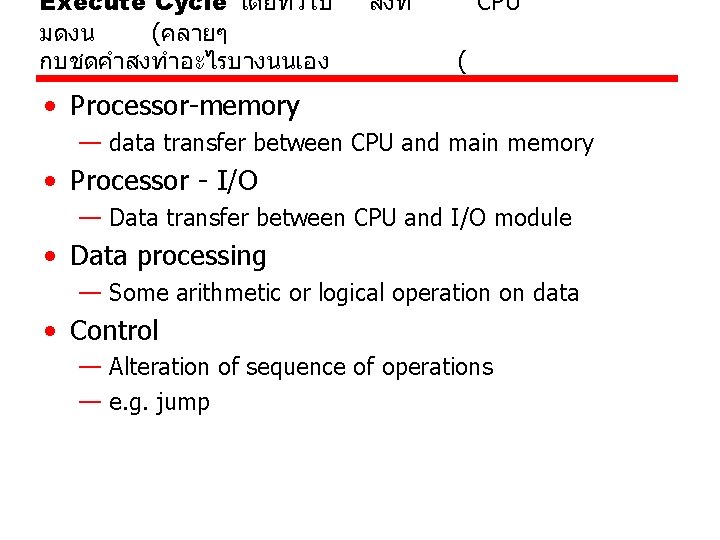

Execute Cycle โดยทวไป มดงน (คลายๆ กบชดคำสงทำอะไรบางนนเอง สงท CPU ( • Processor-memory — data transfer between CPU and main memory • Processor - I/O — Data transfer between CPU and I/O module • Data processing — Some arithmetic or logical operation on data • Control — Alteration of sequence of operations — e. g. jump

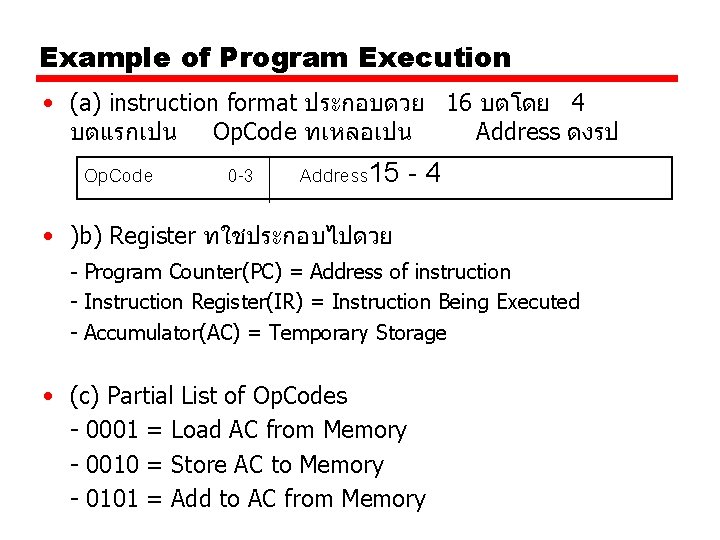

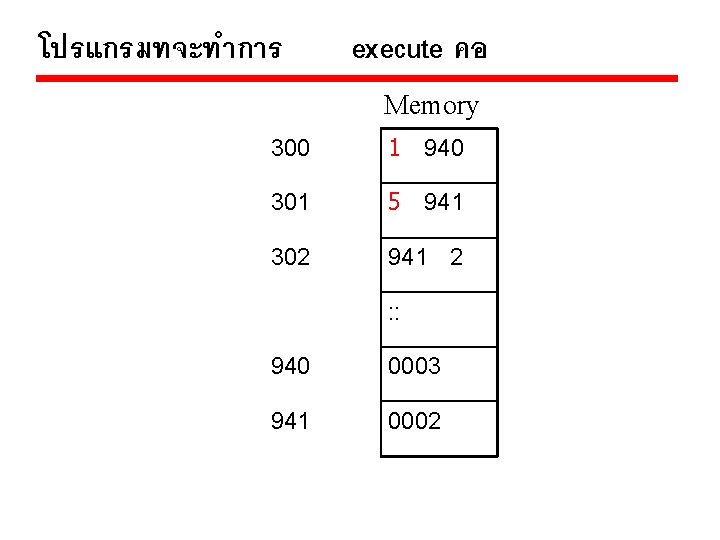

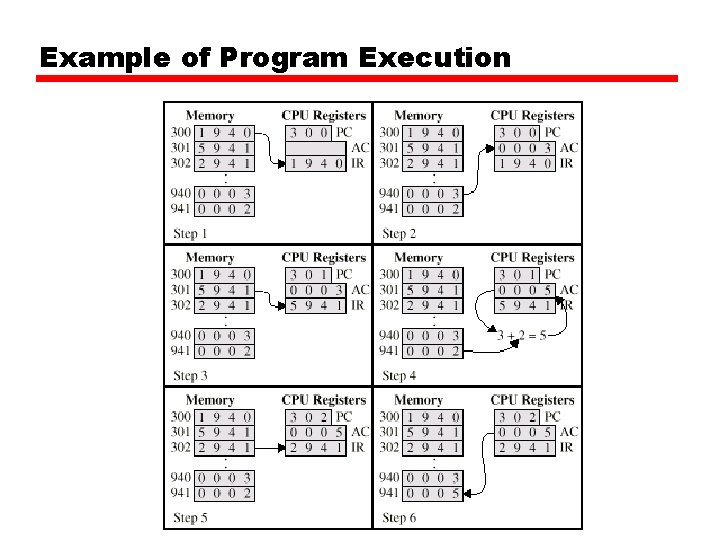

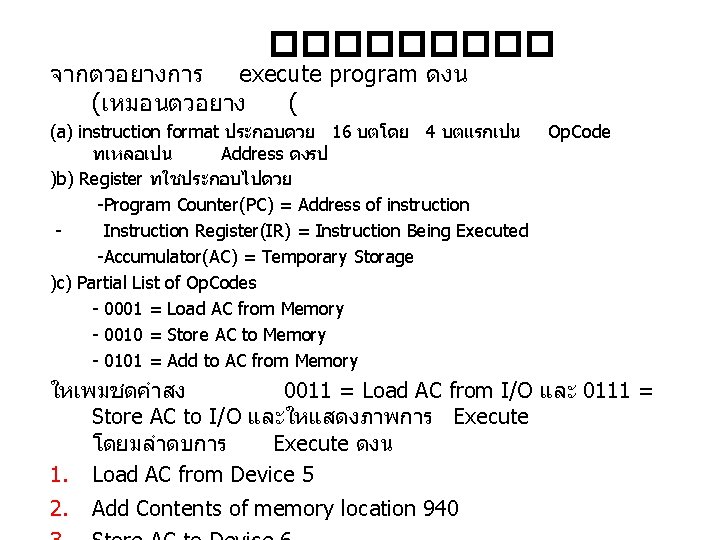

Example of Program Execution • (a) instruction format ประกอบดวย 16 บตโดย 4 บตแรกเปน Op. Code ทเหลอเปน Address ดงรป Op. Code 0 -3 Address 15 - 4 • )b) Register ทใชประกอบไปดวย - Program Counter(PC) = Address of instruction - Instruction Register(IR) = Instruction Being Executed - Accumulator(AC) = Temporary Storage • (c) Partial List of Op. Codes - 0001 = Load AC from Memory - 0010 = Store AC to Memory - 0101 = Add to AC from Memory

โปรแกรมทจะทำการ execute คอ Memory 300 1 940 301 5 941 302 941 2 : : 940 0003 941 0002

Example of Program Execution

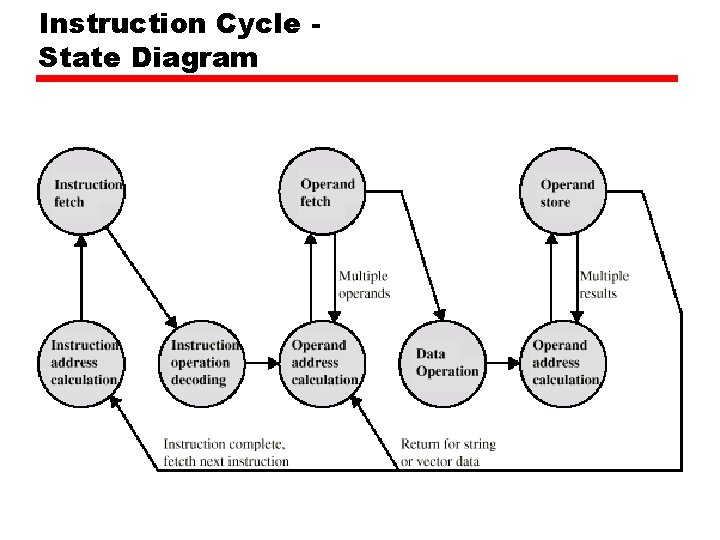

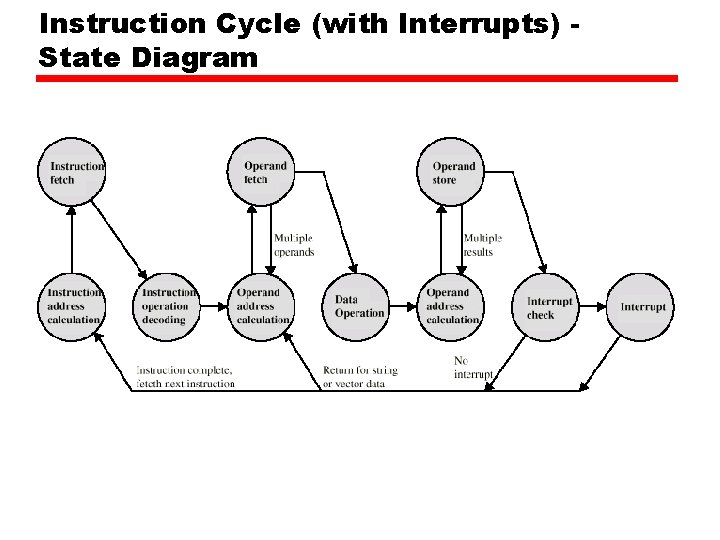

Instruction Cycle State Diagram

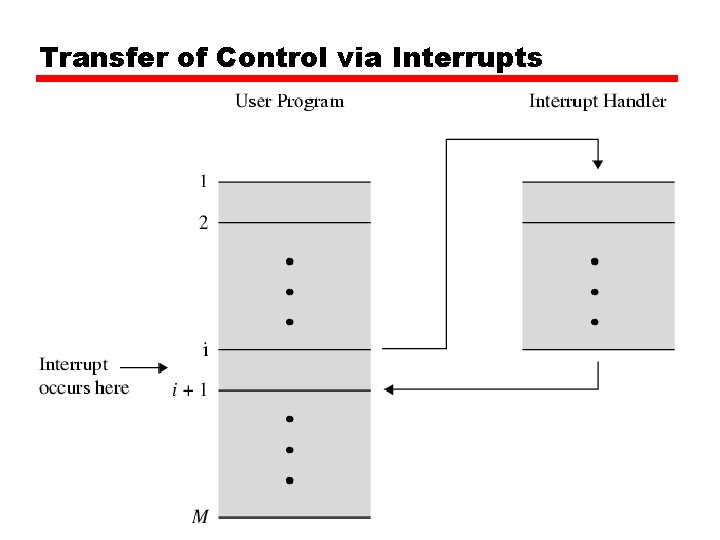

Transfer of Control via Interrupts

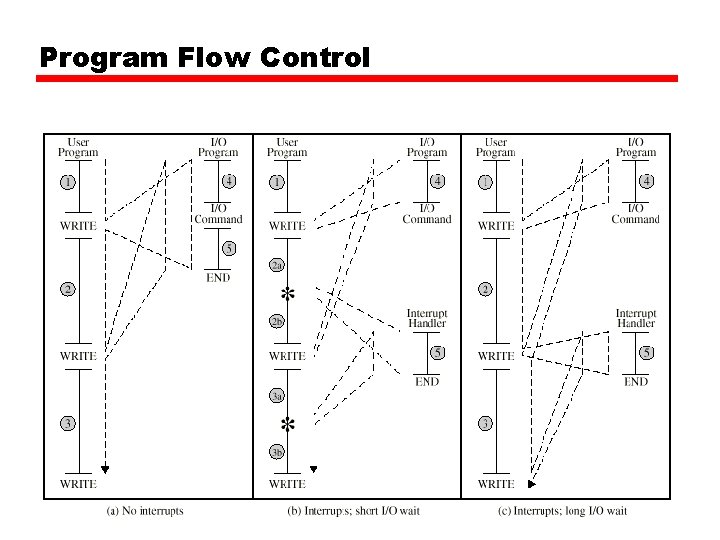

Program Flow Control

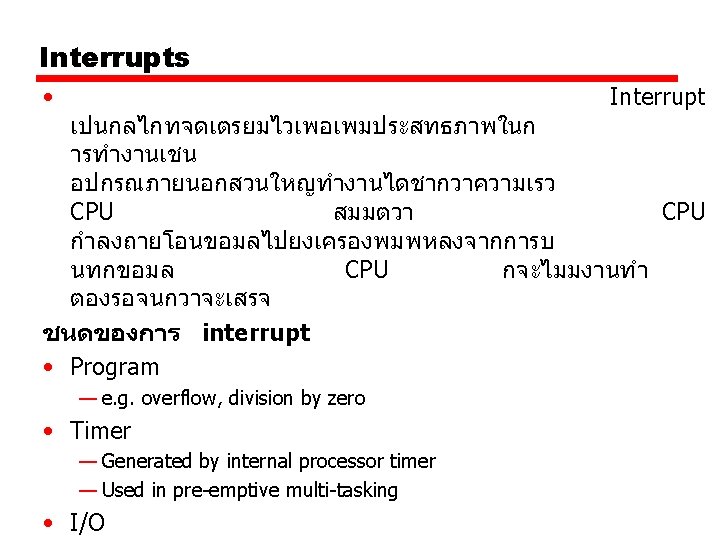

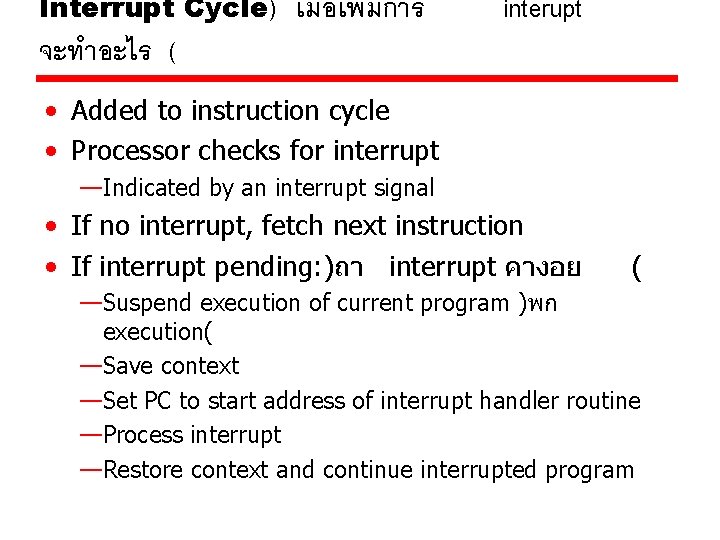

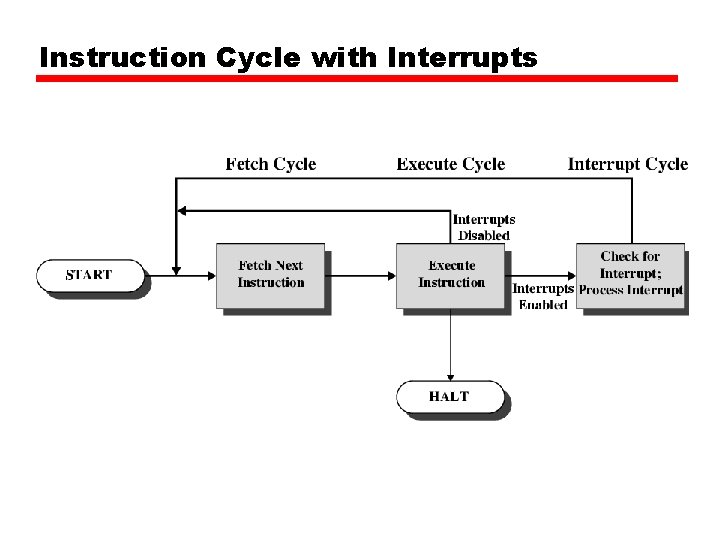

Interrupt Cycle) จะทำอะไร ( เมอเพมการ interupt • Added to instruction cycle • Processor checks for interrupt —Indicated by an interrupt signal • If no interrupt, fetch next instruction • If interrupt pending: )ถา interrupt คางอย ( —Suspend execution of current program )พก execution( —Save context —Set PC to start address of interrupt handler routine —Process interrupt —Restore context and continue interrupted program

Instruction Cycle with Interrupts

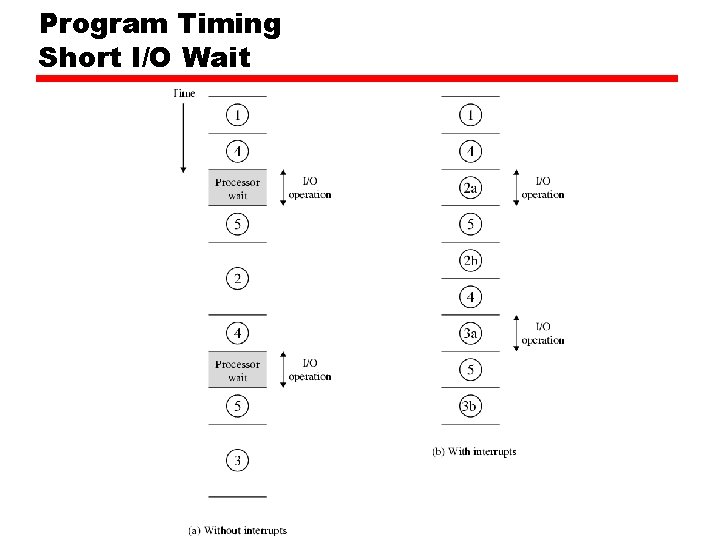

Program Timing Short I/O Wait

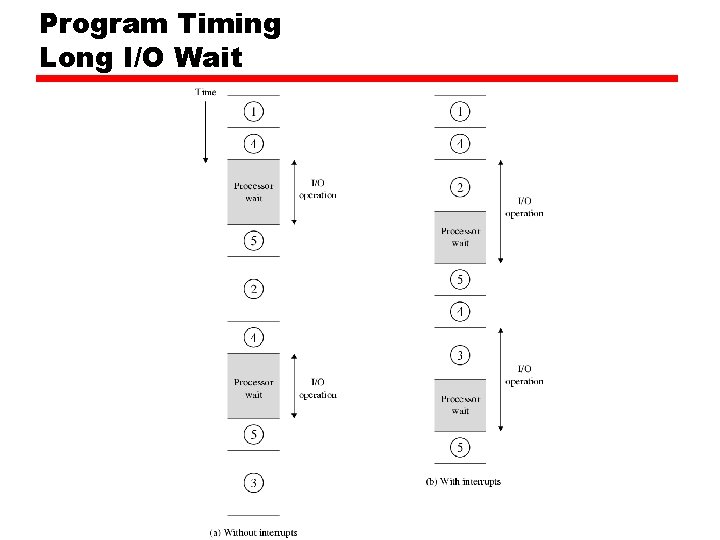

Program Timing Long I/O Wait

Instruction Cycle (with Interrupts) State Diagram

Multiple Interrupts)�������� ���� ( • Disable interrupts —Processor will ignore further interrupts whilst processing one interrupt —Interrupts remain pending and are checked after first interrupt has been processed —Interrupts handled in sequence as they occur • Define priorities —Low priority interrupts can be interrupted by higher priority interrupts —When higher priority interrupt has been processed, processor returns to previous interrupt

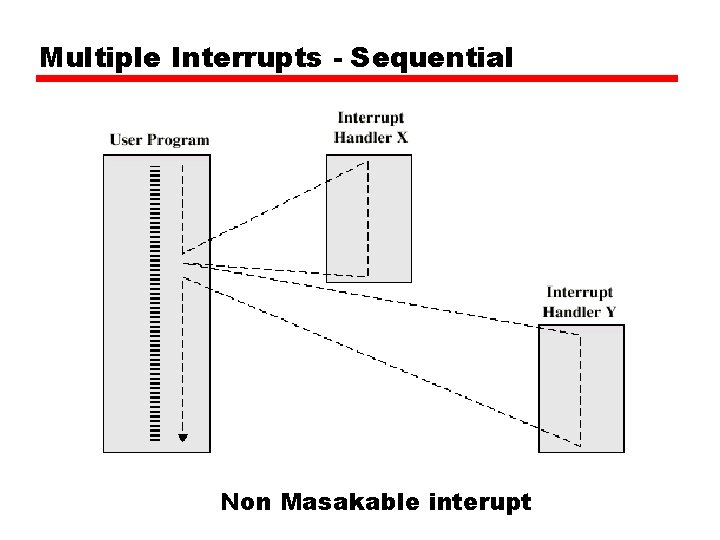

Multiple Interrupts - Sequential Non Masakable interupt

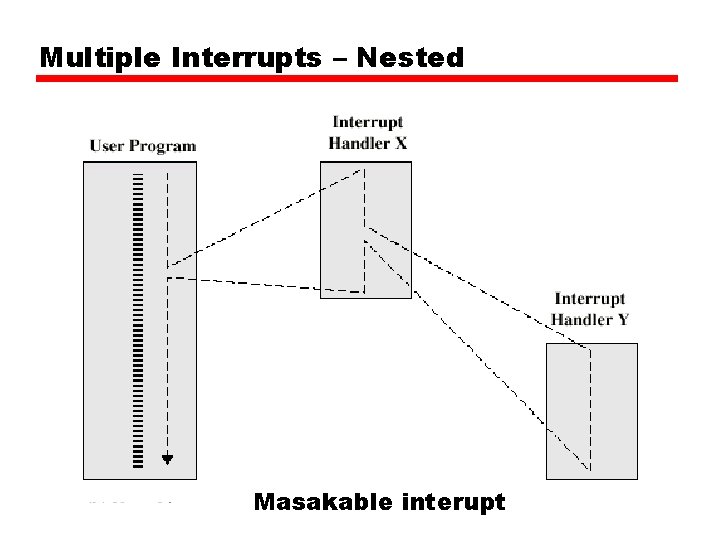

Multiple Interrupts – Nested Masakable interupt

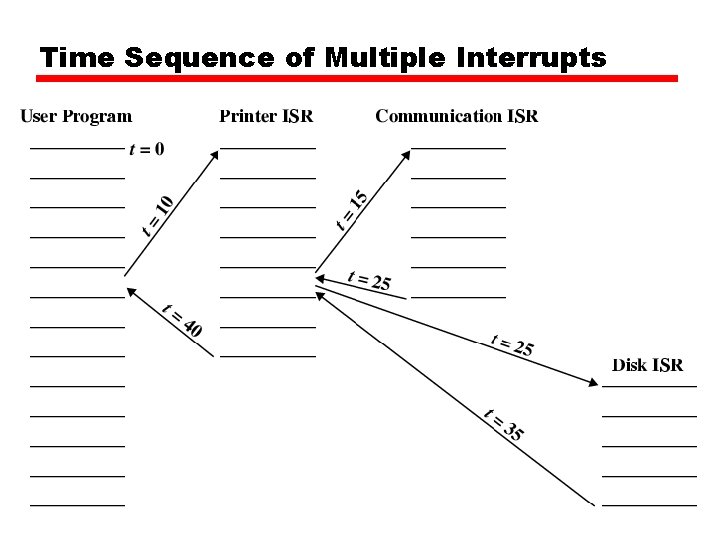

Time Sequence of Multiple Interrupts

Interconnection structure ����������� • All the units must be connected • Different type of connection for different type of unit —Memory —Input/Output —CPU

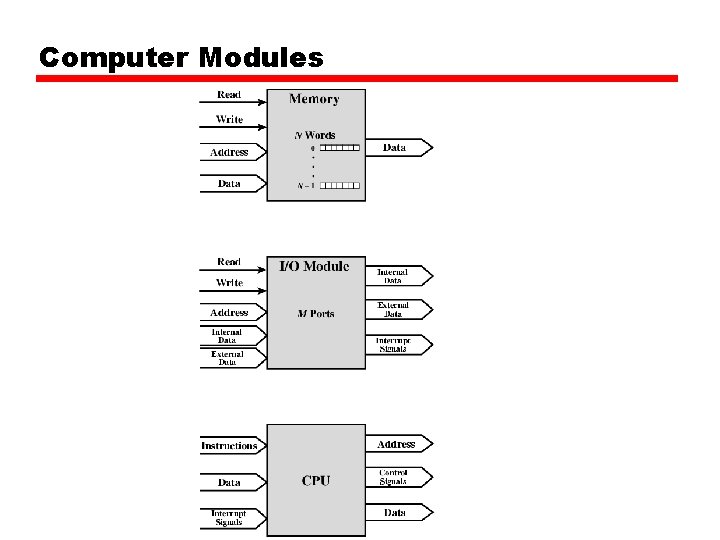

Computer Modules

Memory Connection • Receives and sends data • Receives addresses (of locations) • Receives control signals —Read —Write —Timing

Input/Output Connection(1) • Similar to memory from computer’s viewpoint • Output —Receive data from computer —Send data to peripheral • Input —Receive data from peripheral —Send data to computer

Input/Output Connection(2) • Receive control signals from computer • Send control signals to peripherals —e. g. spin disk • Receive addresses from computer —e. g. port number to identify peripheral • Send interrupt signals (control)

CPU Connection • • Reads instruction and data Writes out data (after processing) Sends control signals to other units Receives (& acts on) interrupts

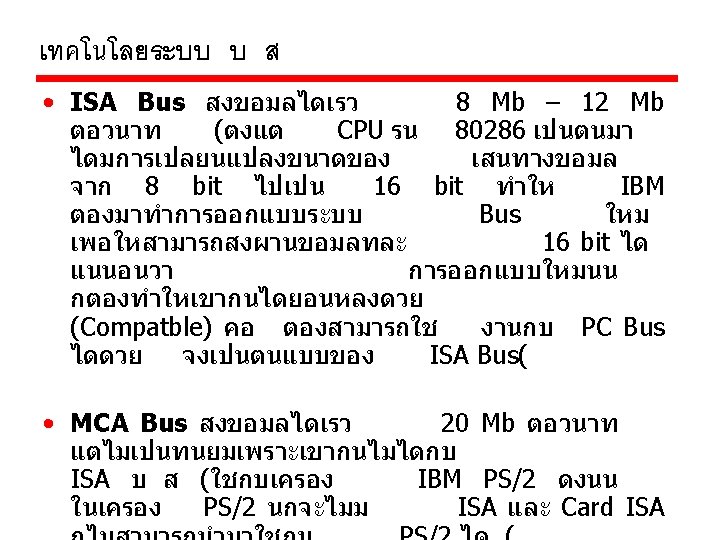

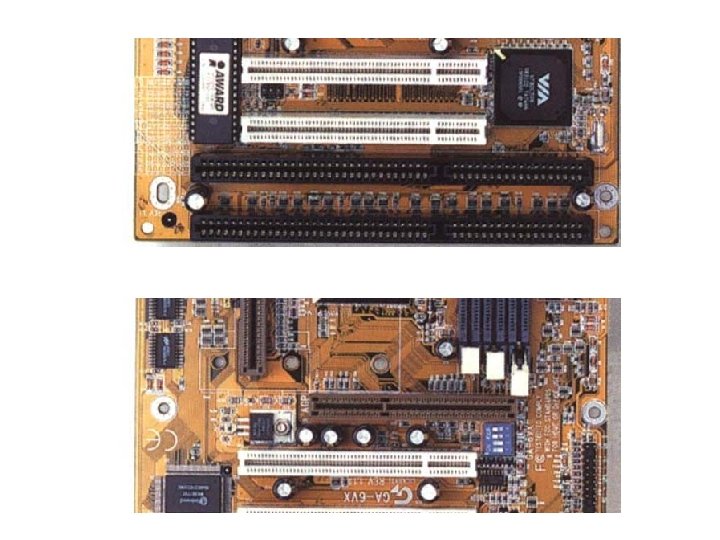

Single Bus ��� Multiple Bus • Single Bus เปนระบบ bus ทมเสนทางเดยวในการตดตอกบอปกรณ ทงหมด ทำใหระบบตดตอกนชา —Propagation delays – Long data paths mean that co-ordination of bus use can adversely affect performance – If aggregate data transfer approaches bus capacity • Multiple Bus (Most systems use multiple buses) เพอแกปญหาในระบบ Single Bus

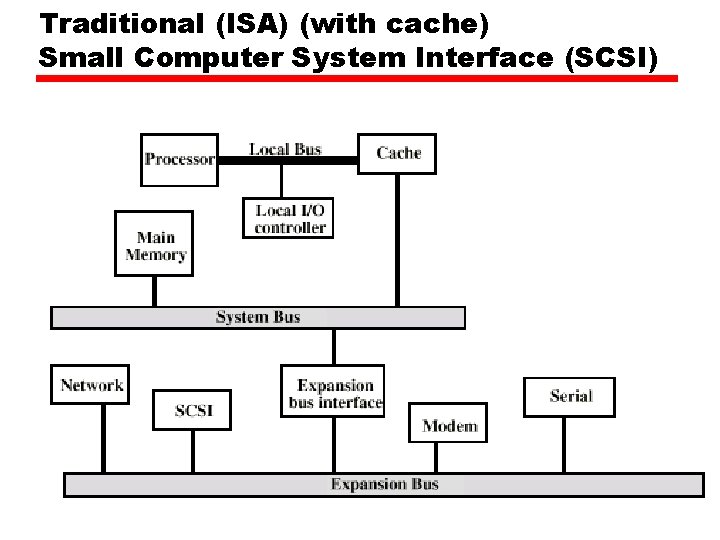

Traditional (ISA) (with cache) Small Computer System Interface (SCSI)

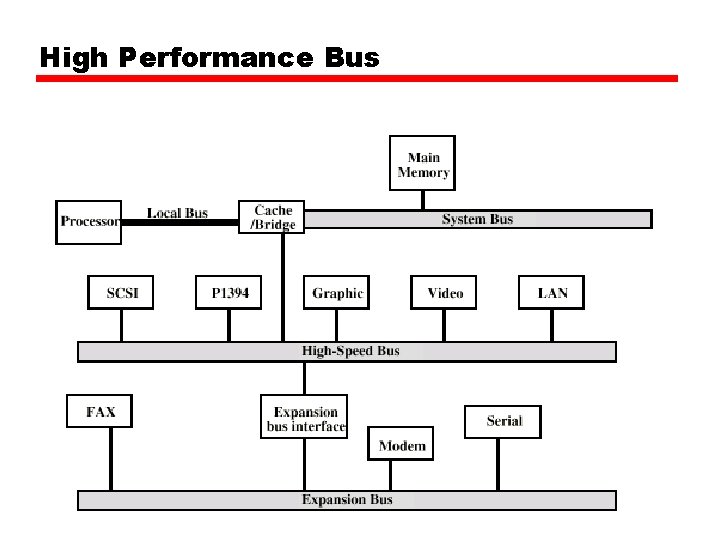

High Performance Bus

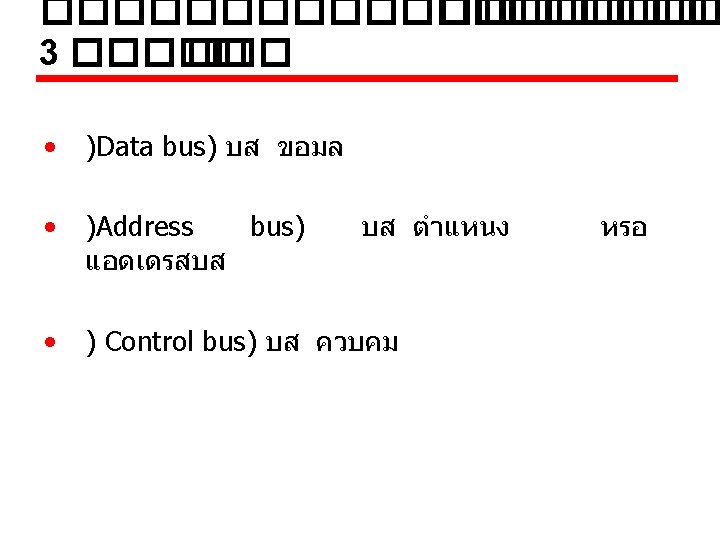

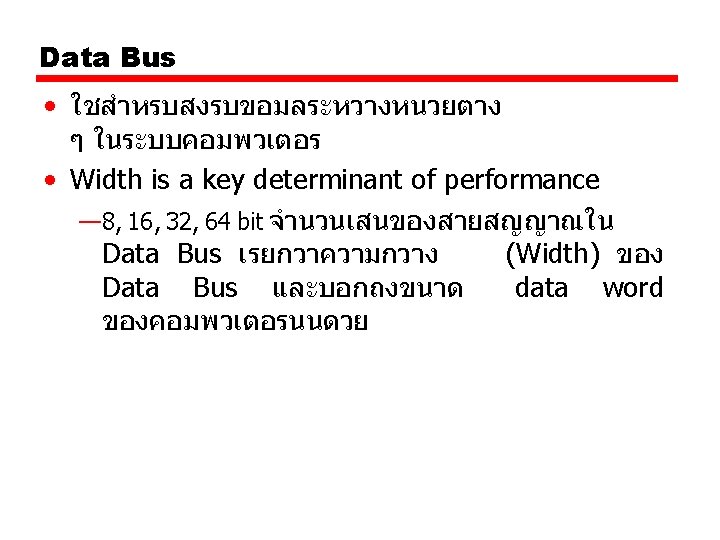

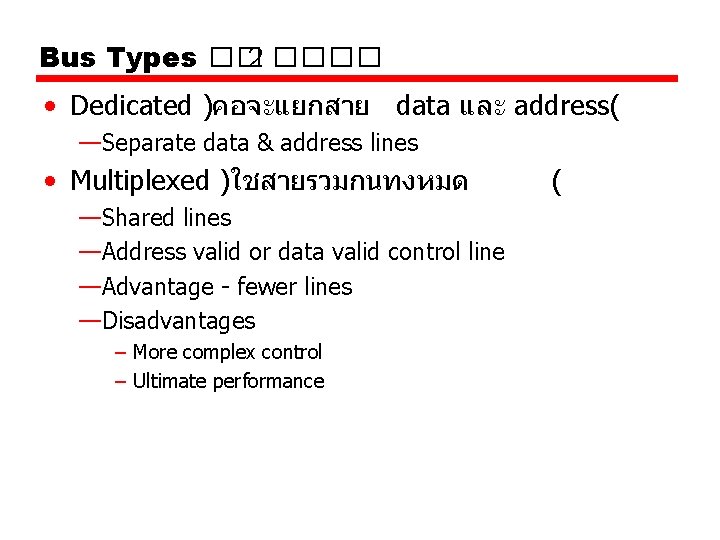

Bus Types �� 2 ���� • Dedicated )คอจะแยกสาย data และ address( —Separate data & address lines • Multiplexed )ใชสายรวมกนทงหมด —Shared lines —Address valid or data valid control line —Advantage - fewer lines —Disadvantages – More complex control – Ultimate performance (

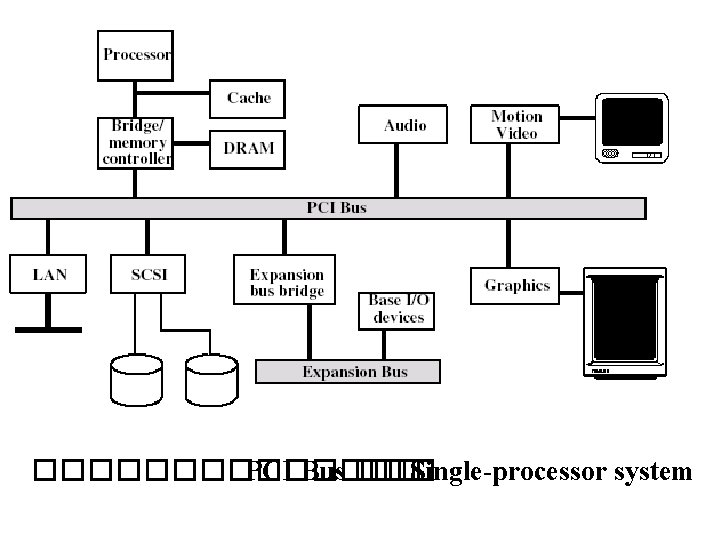

������� PCI Bus ��� Single-processor system

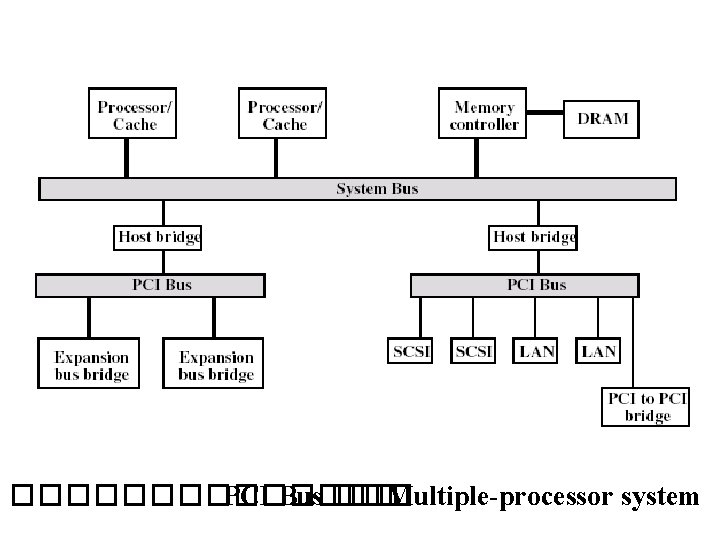

������� PCI Bus ��� Multiple-processor system

����� จากตวอยางการ execute program ดงน (เหมอนตวอยาง ( (a) instruction format ประกอบดวย 16 บตโดย 4 บตแรกเปน ทเหลอเปน Address ดงรป )b) Register ทใชประกอบไปดวย -Program Counter(PC) = Address of instruction Instruction Register(IR) = Instruction Being Executed -Accumulator(AC) = Temporary Storage )c) Partial List of Op. Codes - 0001 = Load AC from Memory - 0010 = Store AC to Memory - 0101 = Add to AC from Memory Op. Code ใหเพมชดคำสง 0011 = Load AC from I/O และ 0111 = Store AC to I/O และใหแสดงภาพการ Execute โดยมลำดบการ Execute ดงน 1. Load AC from Device 5 2. Add Contents of memory location 940

- Slides: 56