Chapter 3 METHODS OF CIRCUIT ANALYSIS I Methods

- Slides: 50

Chapter 3 METHODS OF CIRCUIT ANALYSIS I

Methods Of Analysis • 2 powerful techniques for circuit analysis: 1. Nodal Analysis (based on KCL) 2. Mesh Analysis (based on KVL)

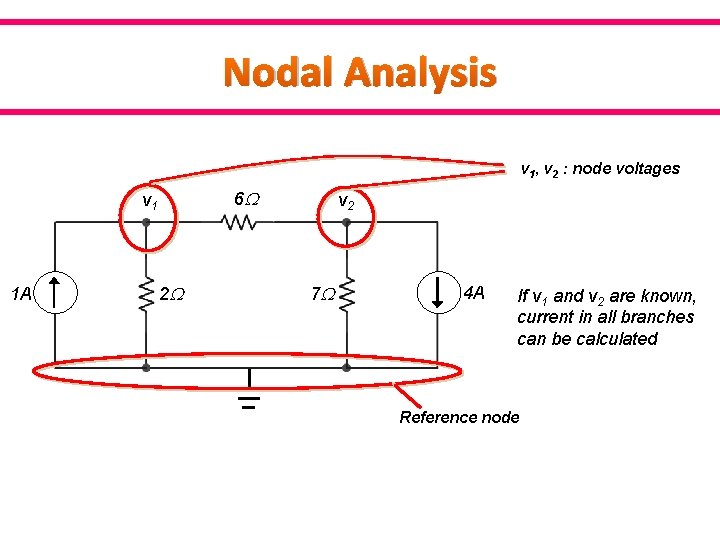

Nodal Analysis • Known as – node-voltage method • Use KCL method • Objective: finding node voltage • Assume circuit without voltage sources. • With node voltages known, current in every branch can be calculated

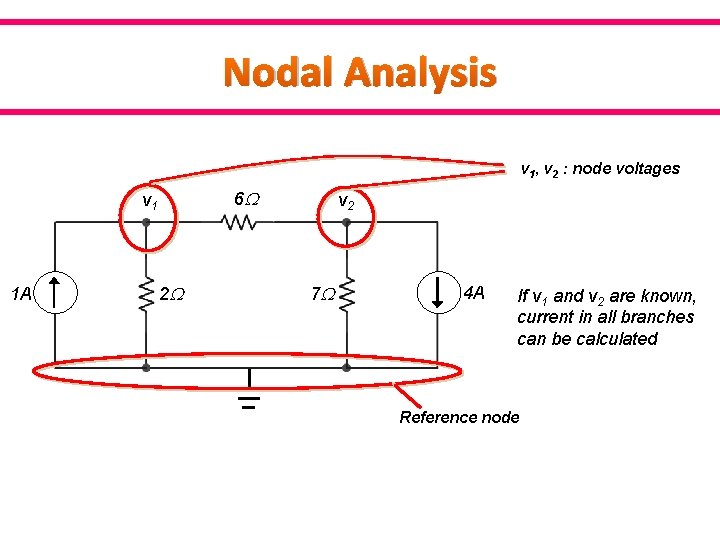

Nodal Analysis v 1, v 2 : node voltages 6 v 1 1 A 2 v 2 7 4 A If v 1 and v 2 are known, current in all branches can be calculated Reference node

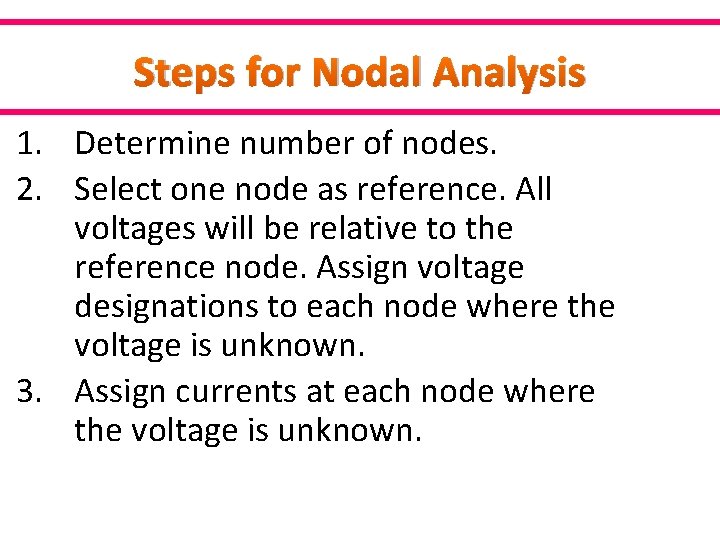

Steps for Nodal Analysis 1. Determine number of nodes. 2. Select one node as reference. All voltages will be relative to the reference node. Assign voltage designations to each node where the voltage is unknown. 3. Assign currents at each node where the voltage is unknown.

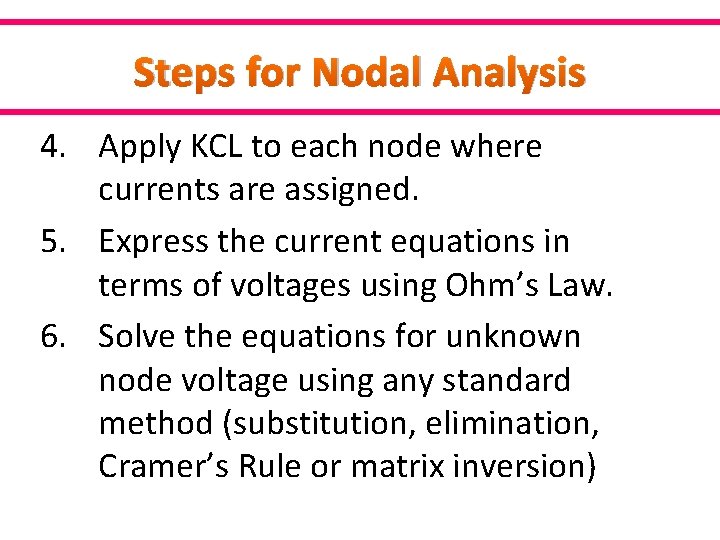

Steps for Nodal Analysis 4. Apply KCL to each node where currents are assigned. 5. Express the current equations in terms of voltages using Ohm’s Law. 6. Solve the equations for unknown node voltage using any standard method (substitution, elimination, Cramer’s Rule or matrix inversion)

Reference Node • Commonly called ground (assumed zero potential). • Usually use ground as a reference node. • Assign voltage designations to nonreference nodes.

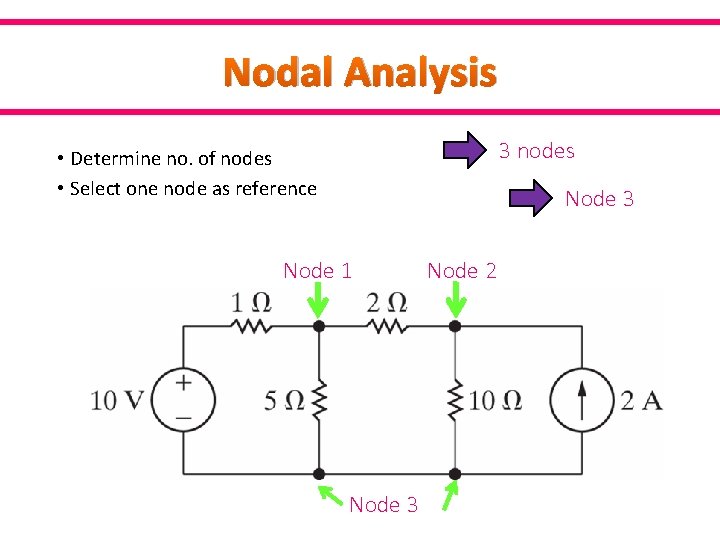

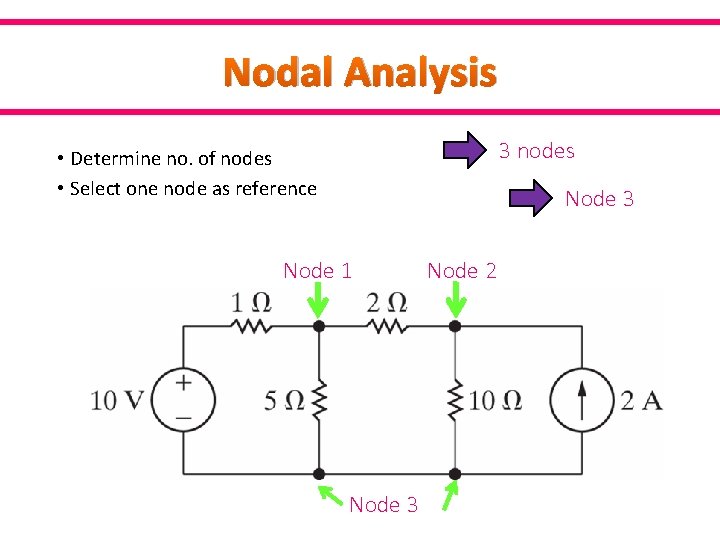

Nodal Analysis 3 nodes • Determine no. of nodes • Select one node as reference Node 3 Node 1 Node 3 Node 2

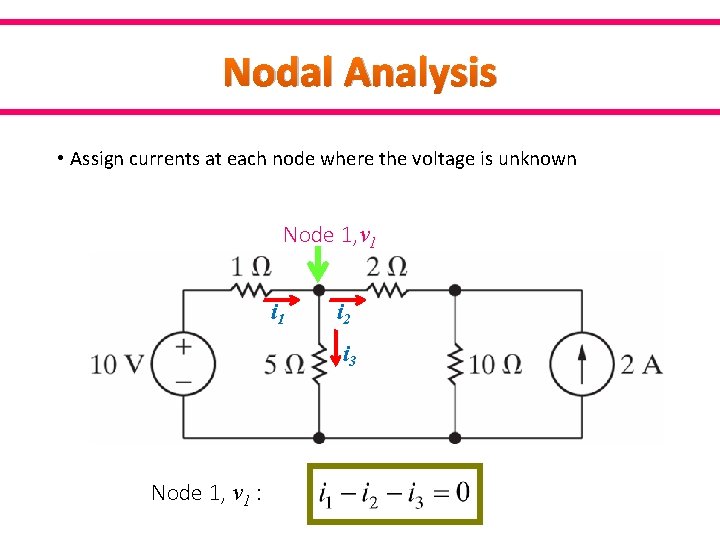

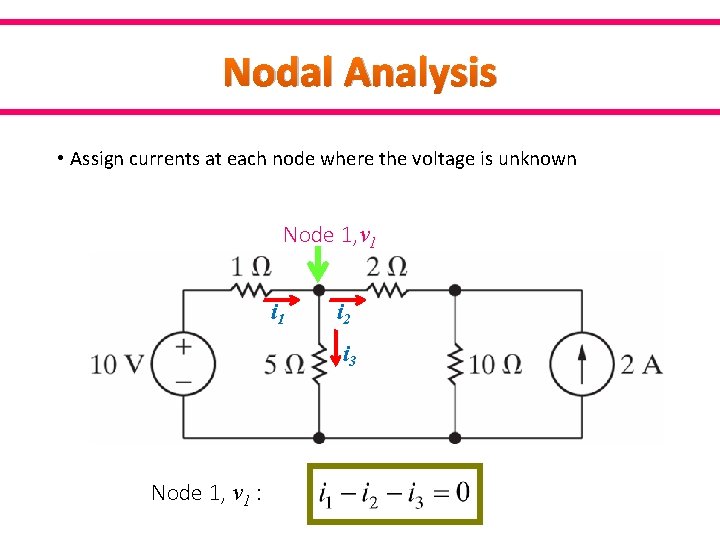

Nodal Analysis • Assign currents at each node where the voltage is unknown Node 1, v 1 i 2 i 3 Node 1, v 1 :

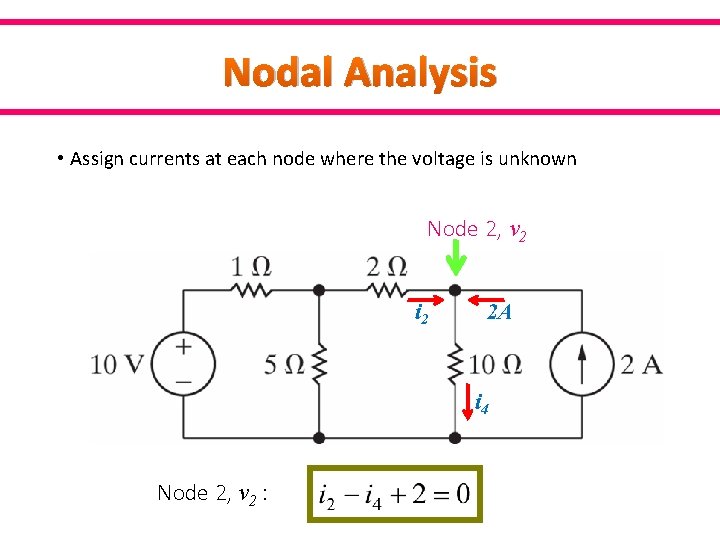

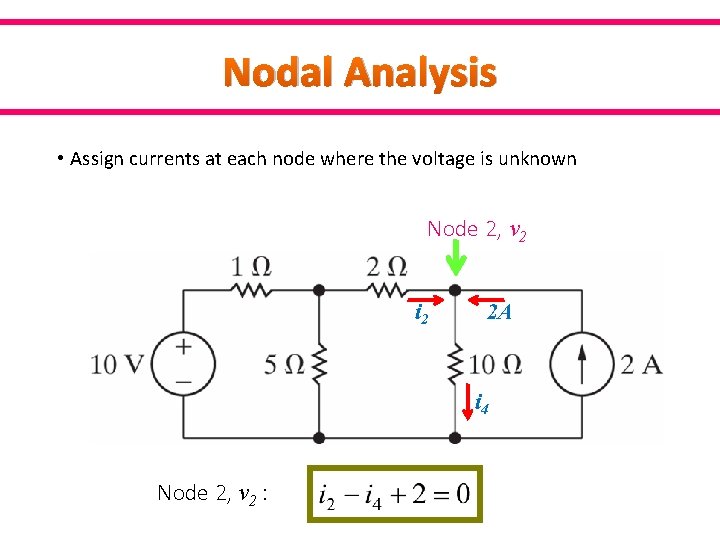

Nodal Analysis • Assign currents at each node where the voltage is unknown Node 2, v 2 i 2 2 A i 4 Node 2, v 2 :

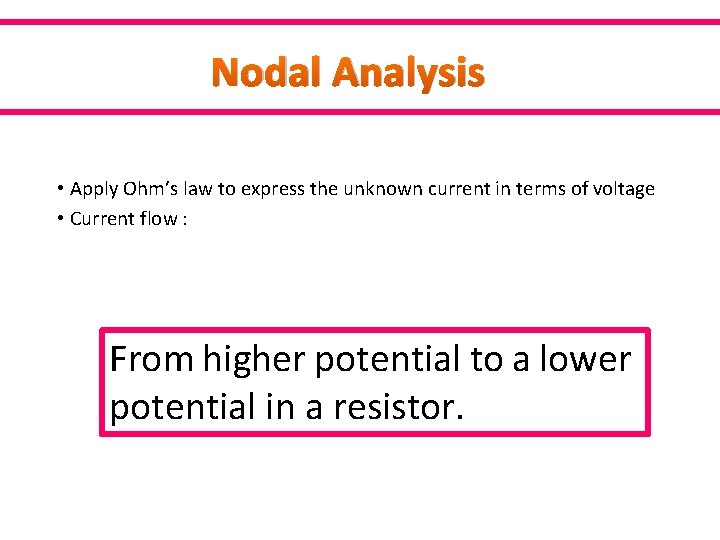

Nodal Analysis • Apply Ohm’s law to express the unknown current in terms of voltage • Current flow : From higher potential to a lower potential in a resistor.

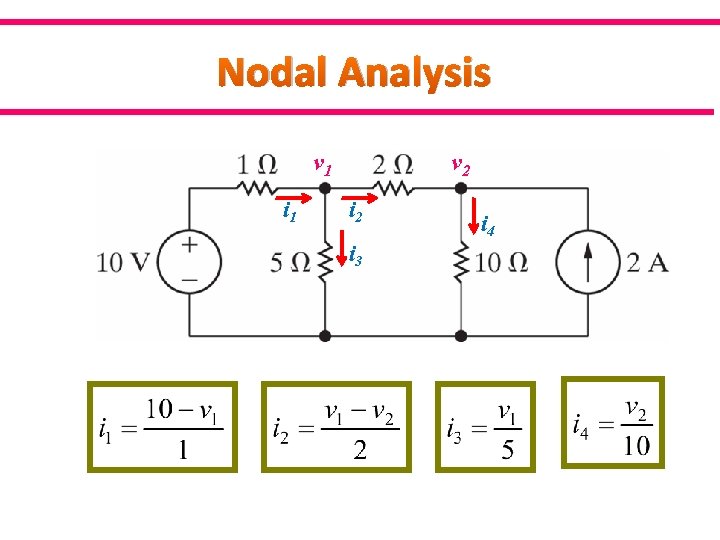

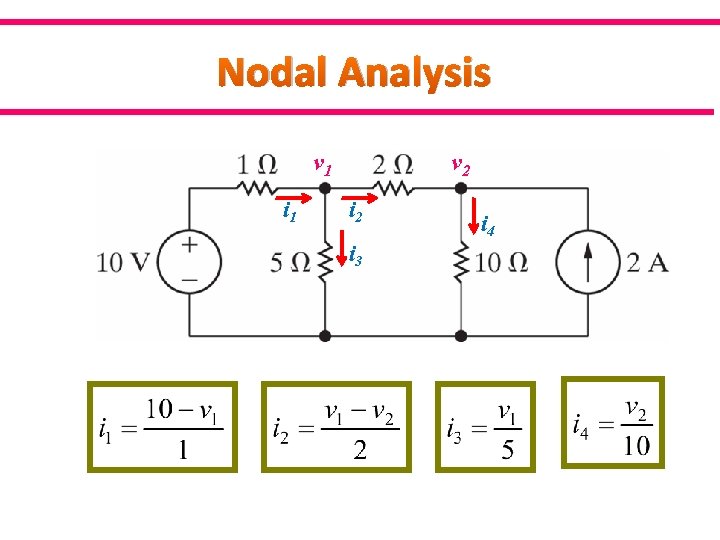

Nodal Analysis v 1 i 1 v 2 i 3 i 4

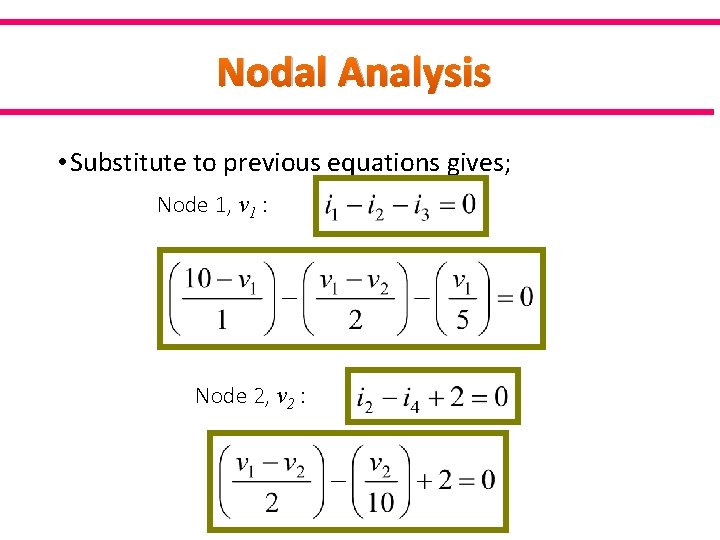

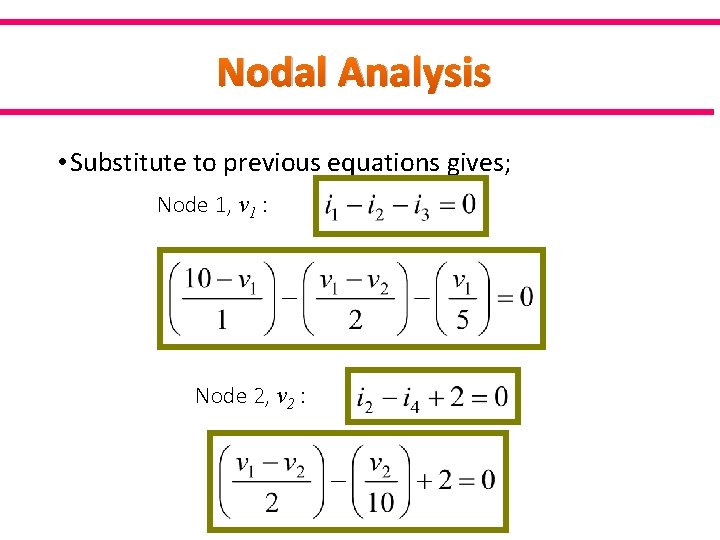

Nodal Analysis • Substitute to previous equations gives; Node 1, v 1 : Node 2, v 2 :

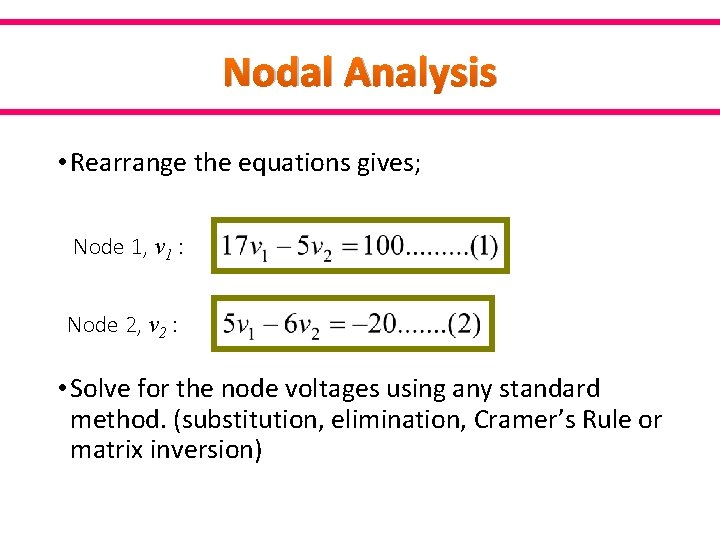

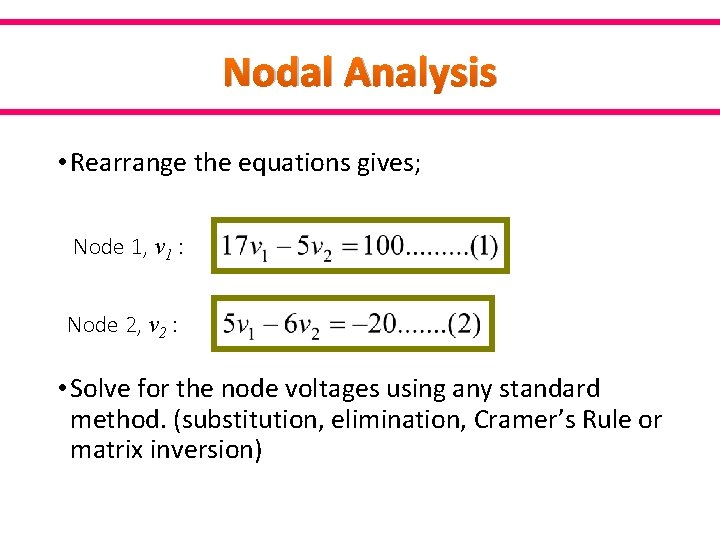

Nodal Analysis • Rearrange the equations gives; Node 1, v 1 : Node 2, v 2 : • Solve for the node voltages using any standard method. (substitution, elimination, Cramer’s Rule or matrix inversion)

Nodal Analysis : Substitution method • Based on the equation;

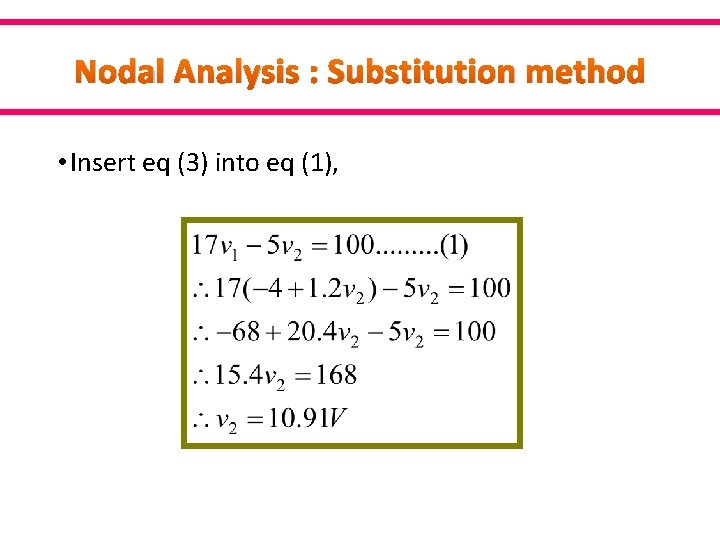

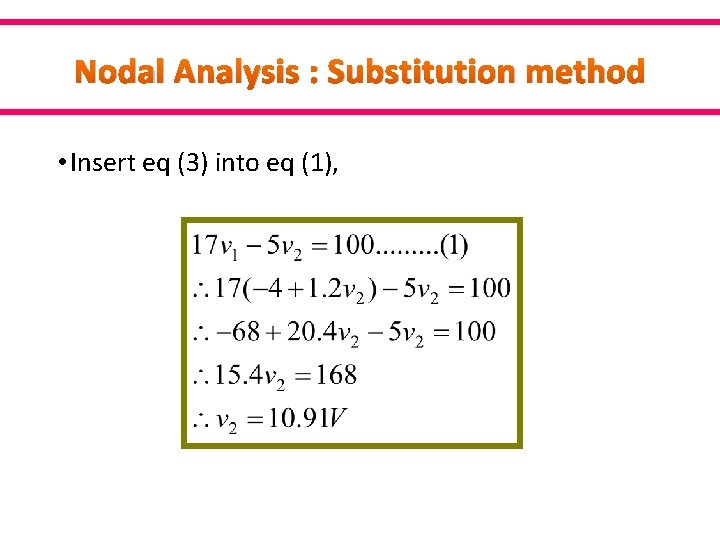

Nodal Analysis : Substitution method • Insert eq (3) into eq (1),

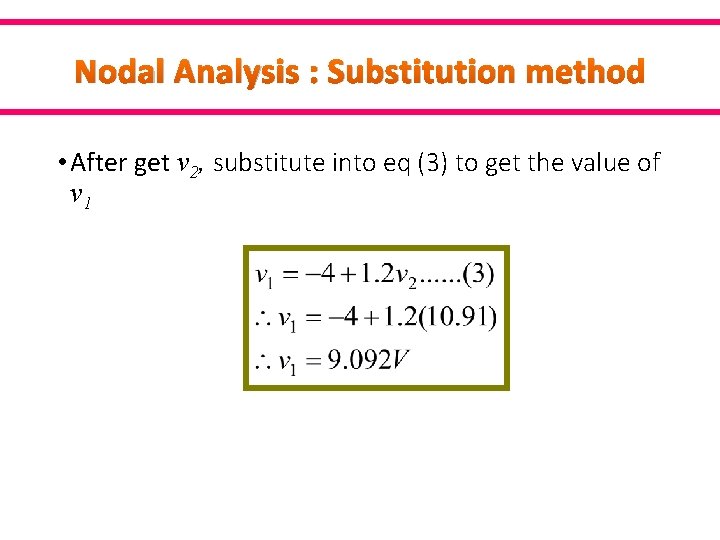

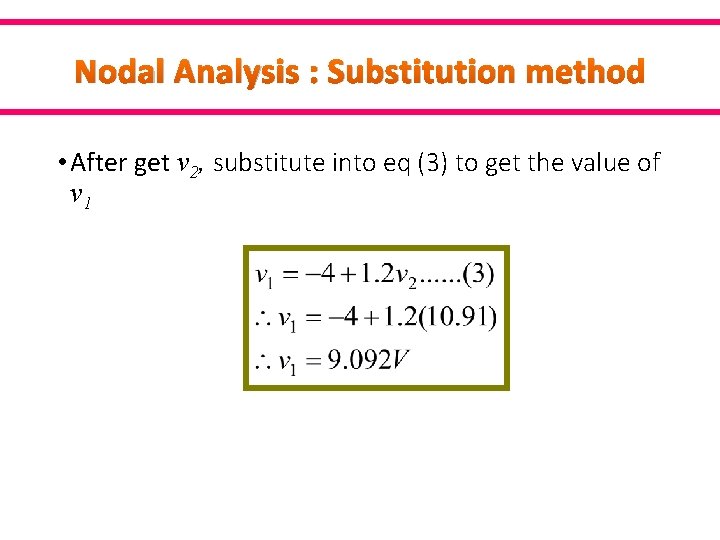

Nodal Analysis : Substitution method • After get v 2, substitute into eq (3) to get the value of v 1

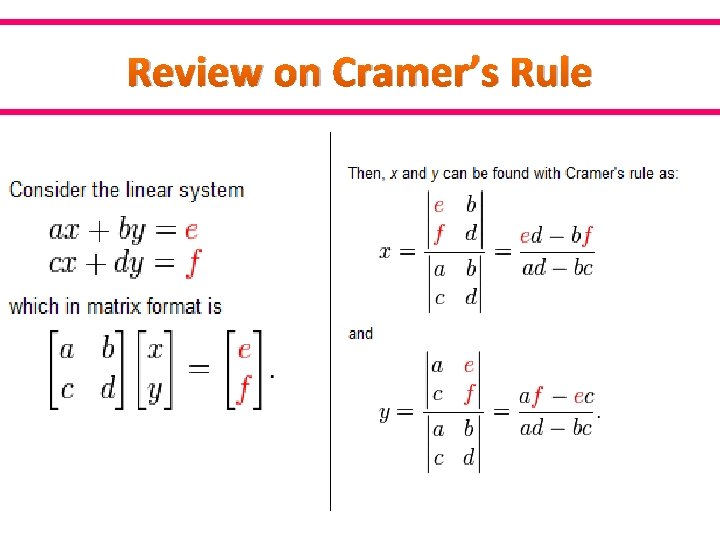

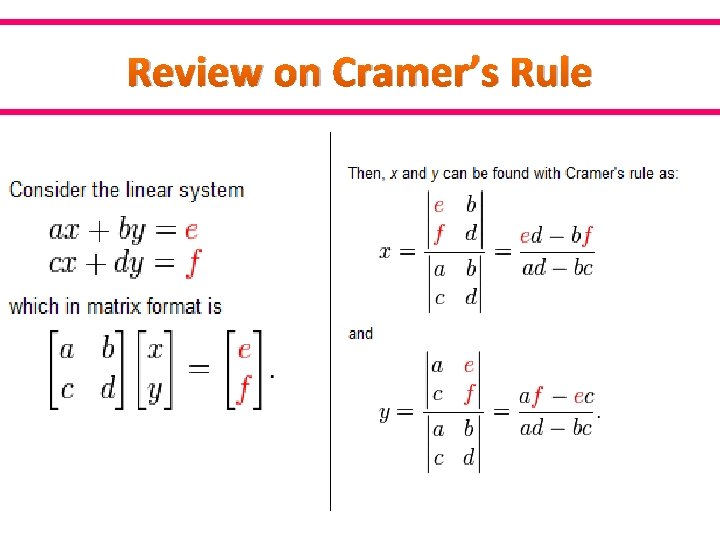

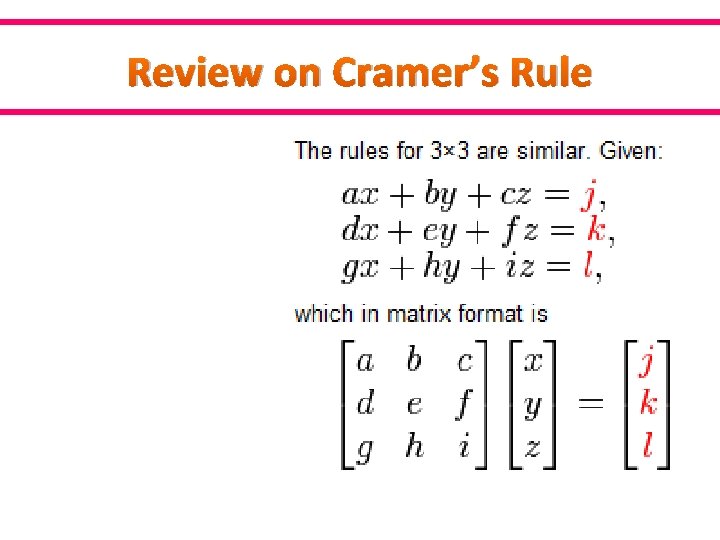

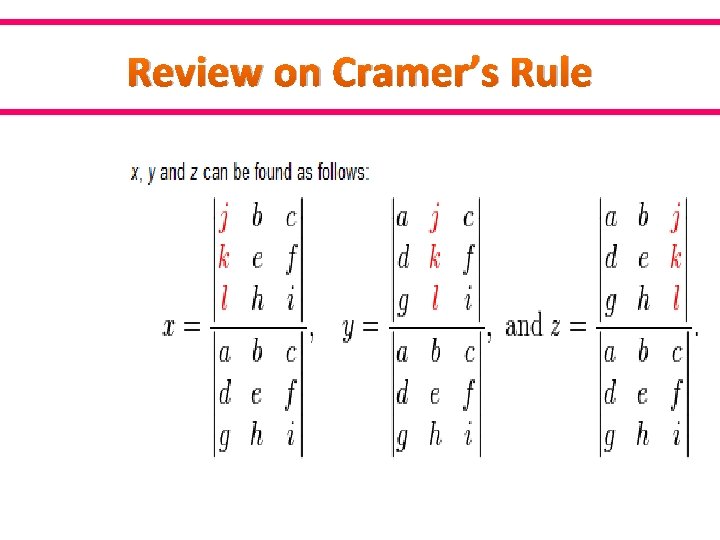

Review on Cramer’s Rule

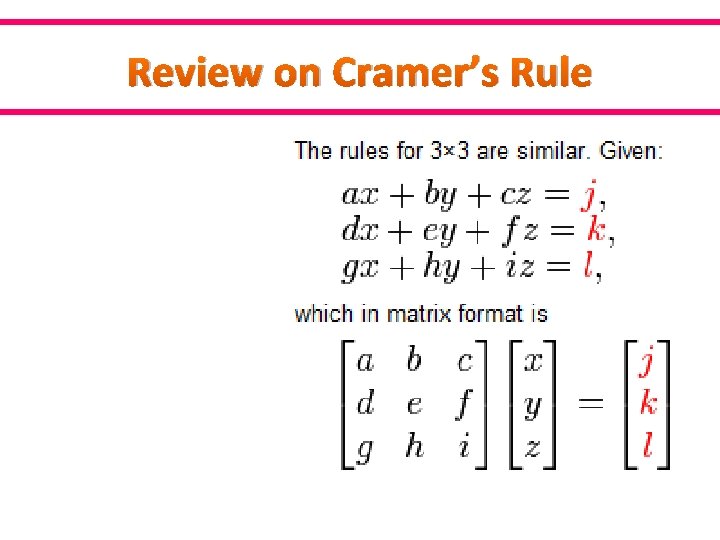

Review on Cramer’s Rule

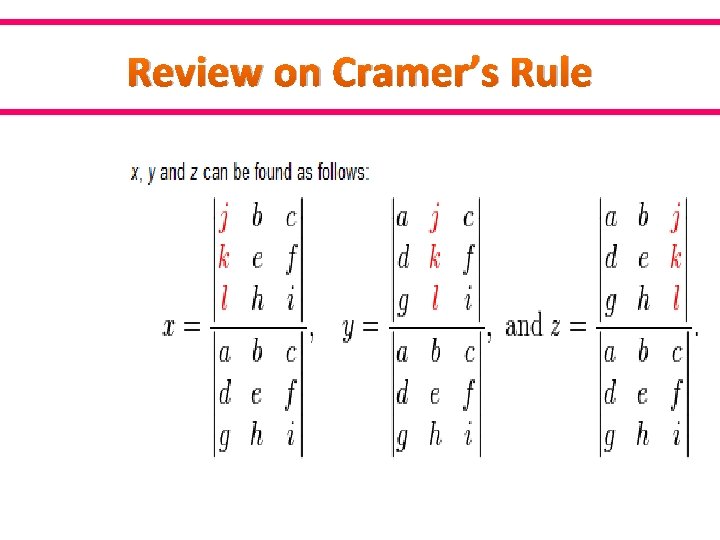

Review on Cramer’s Rule

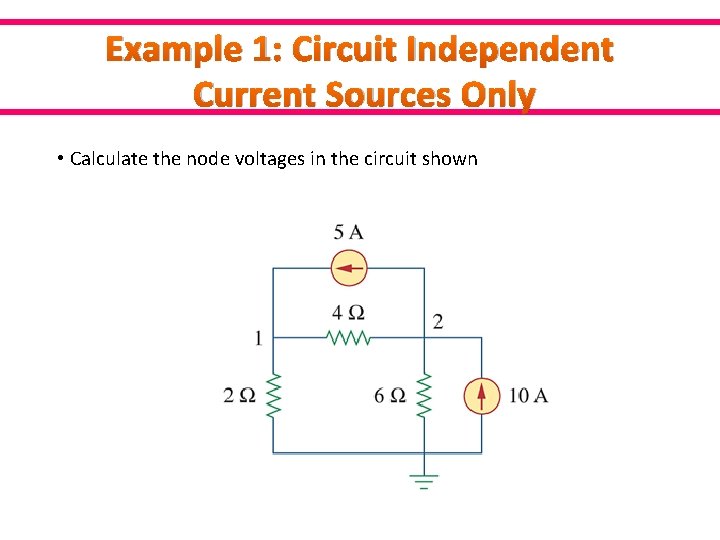

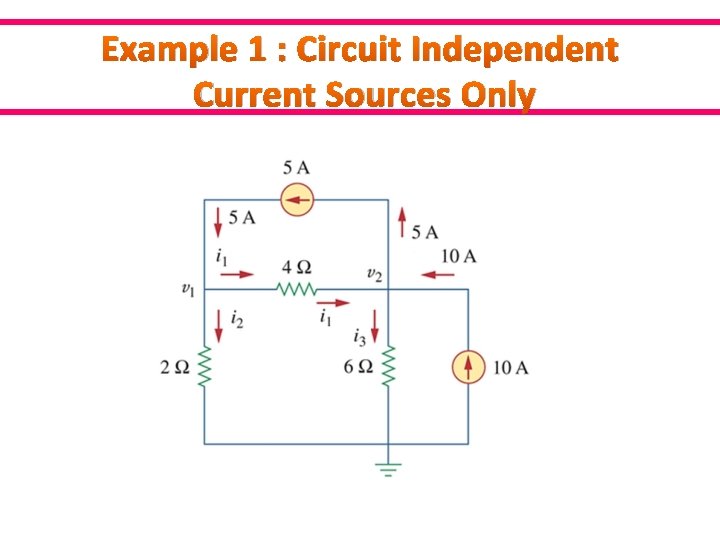

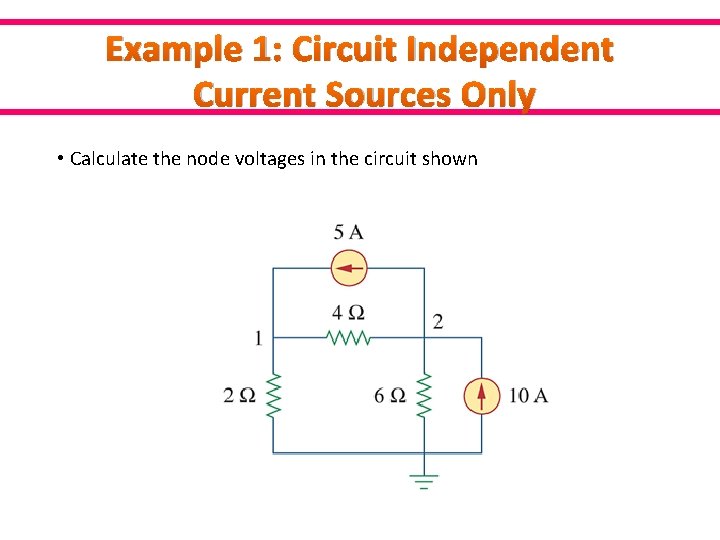

Example 1: Circuit Independent Current Sources Only • Calculate the node voltages in the circuit shown

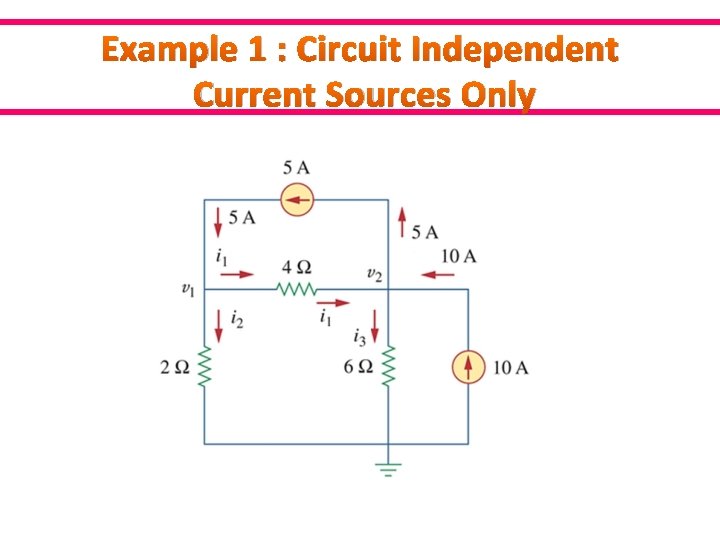

Example 1 : Circuit Independent Current Sources Only

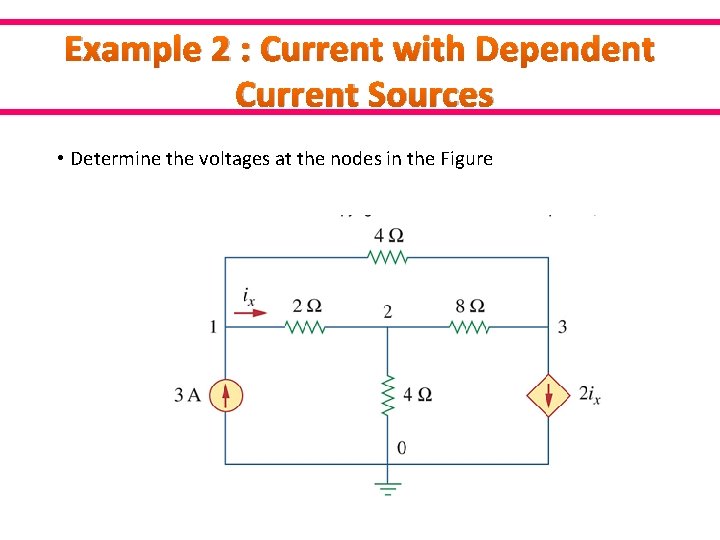

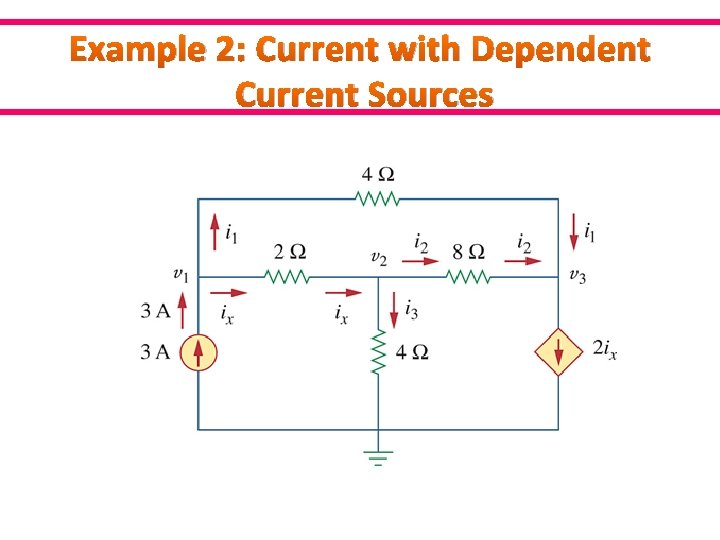

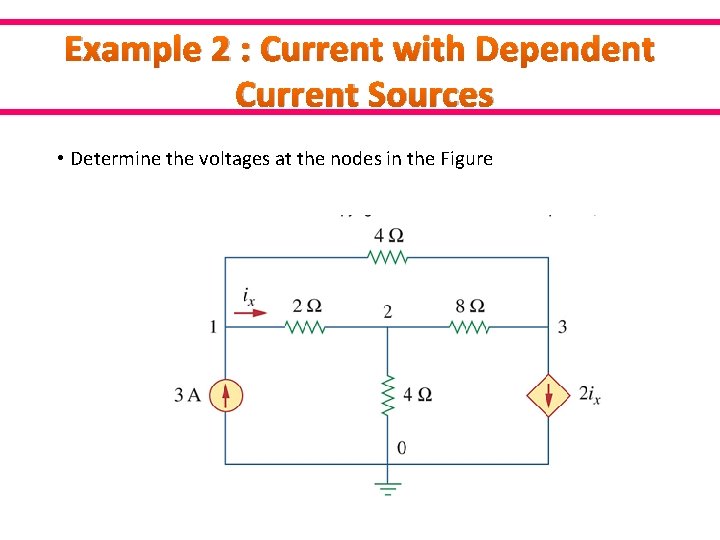

Example 2 : Current with Dependent Current Sources • Determine the voltages at the nodes in the Figure

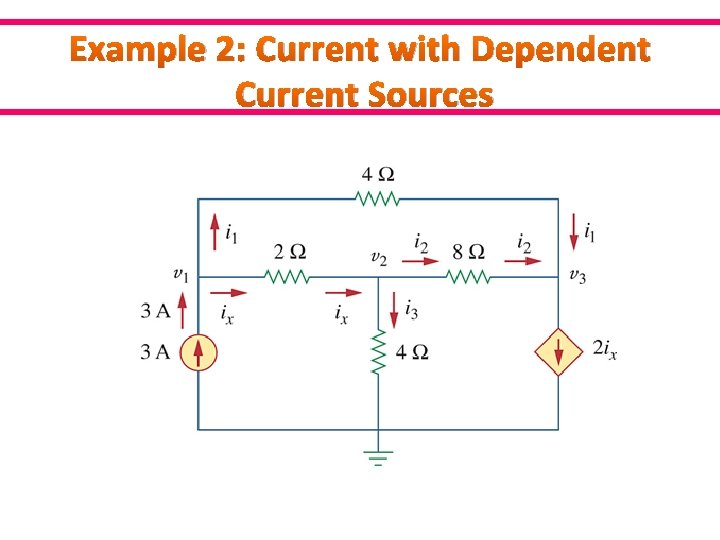

Example 2: Current with Dependent Current Sources

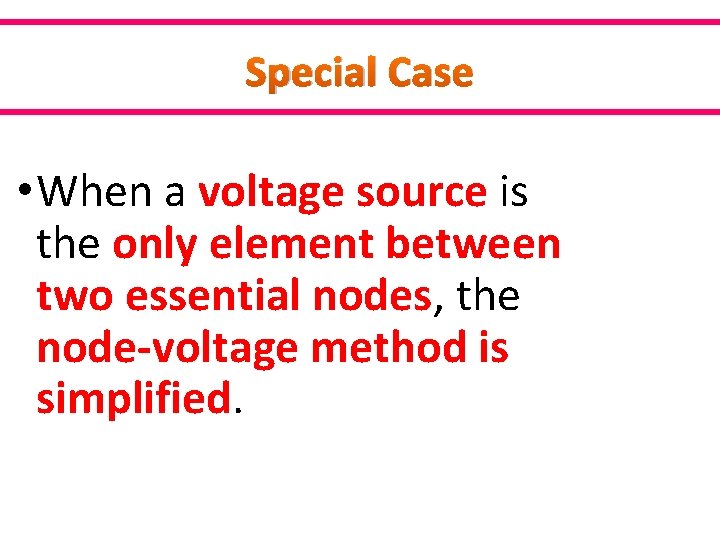

Special Case • When a voltage source is the only element between two essential nodes, the node-voltage method is simplified.

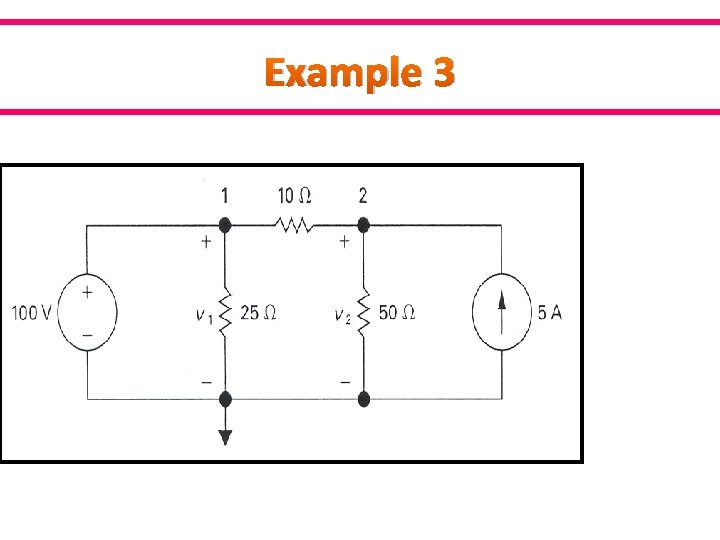

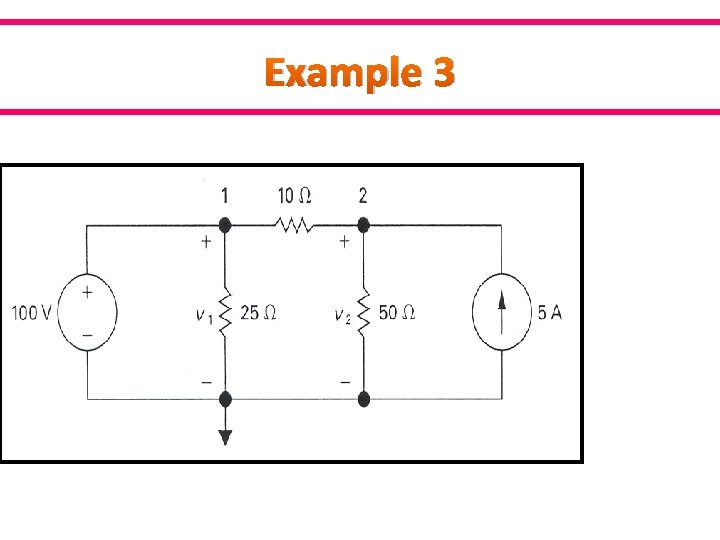

Example 3

Solution : Example 3 i. There is three essential nodes, so two simultaneous equation are needed. ii. Only one unknown node voltage, V 2 where as V 1=100 V. iii. Therefore, only a single node-voltage equation is needed which is at node 2.

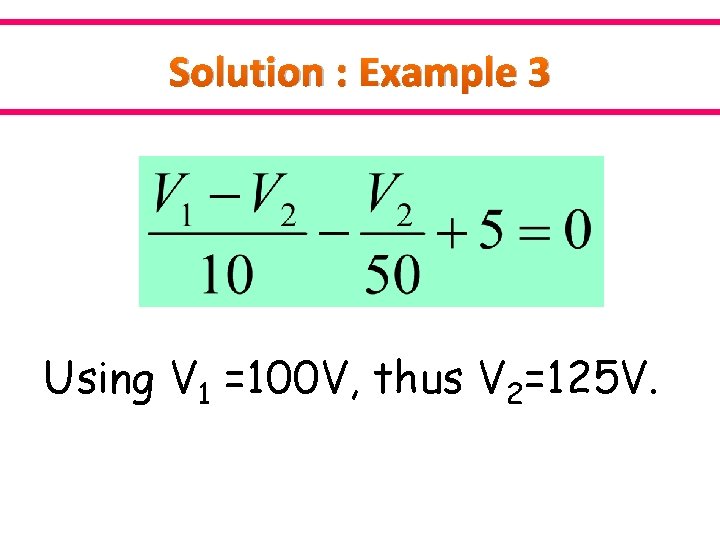

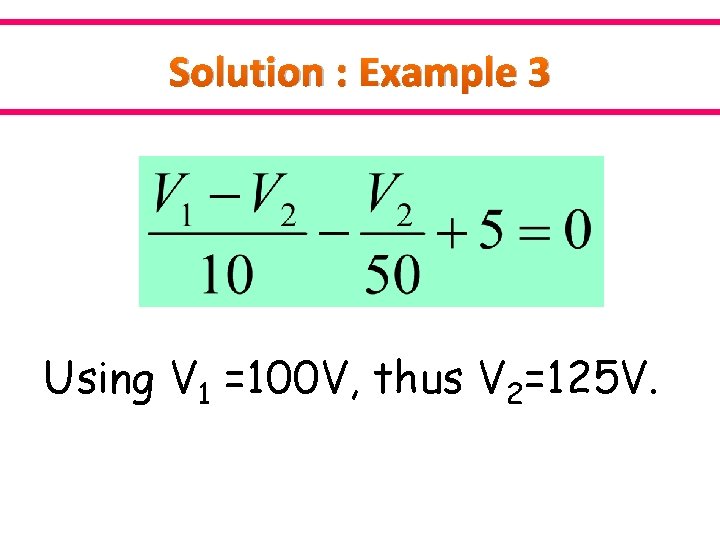

Solution : Example 3 Using V 1 =100 V, thus V 2=125 V.

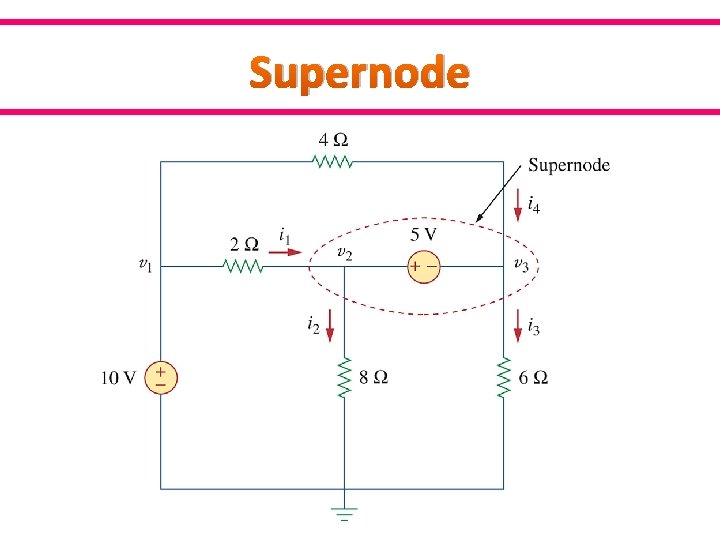

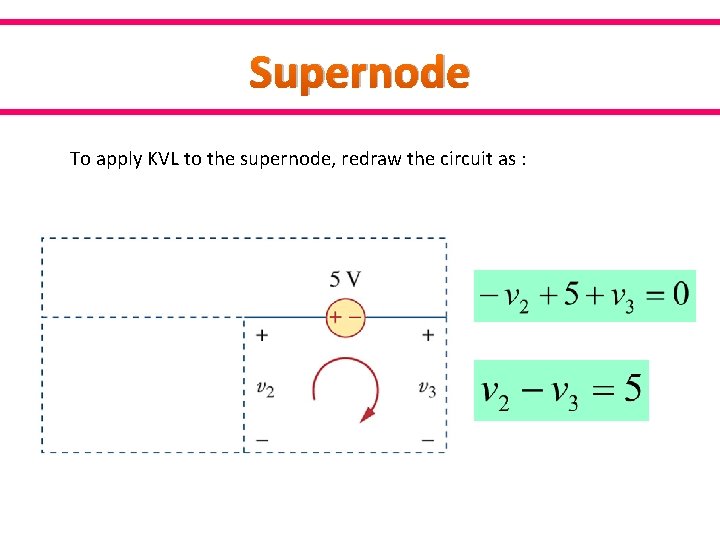

Supernode • When a voltage source is between two essential nodes, those nodes can be combine to form a supernode (voltage source is assume as open circuit). • We apply both KCL & KVL to determine the node voltages

Supernode • Properties of a supernode: 1. 2. 3. The voltage source inside the supernode provides a constraint equation needed to solve for the node voltages. Has no voltage of its own. Requires the application of both KCL & KVL

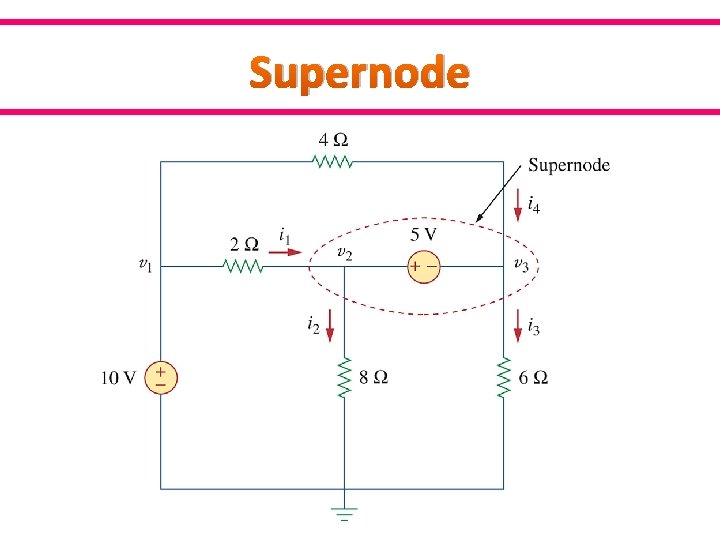

Supernode

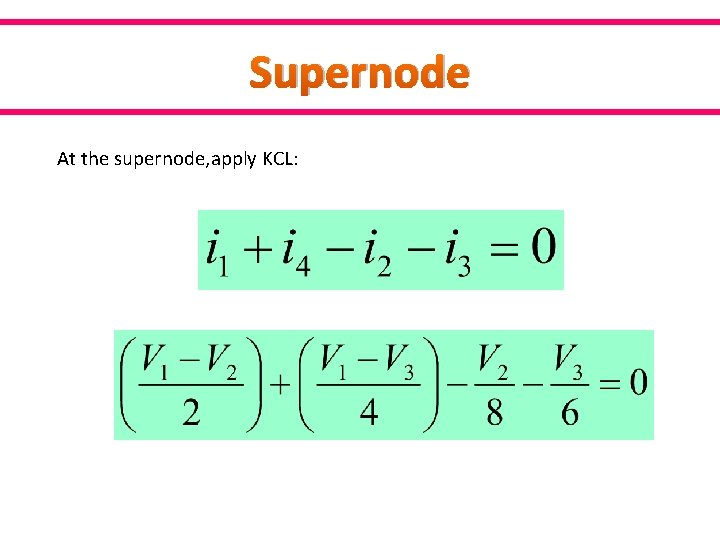

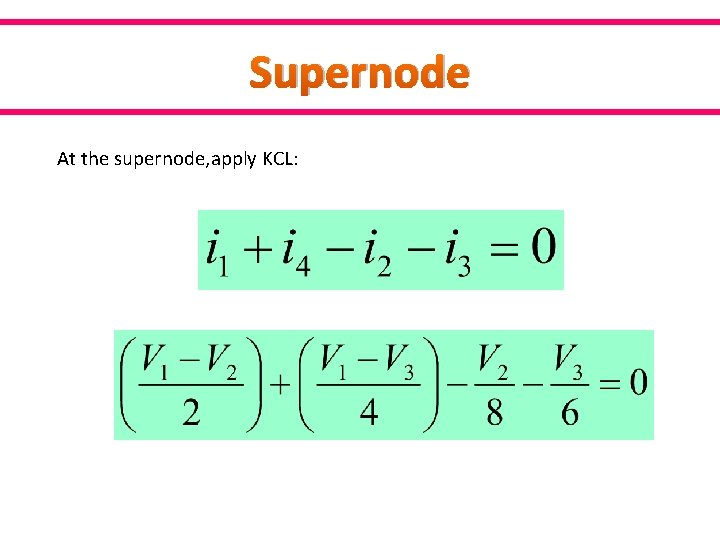

Supernode At the supernode, apply KCL:

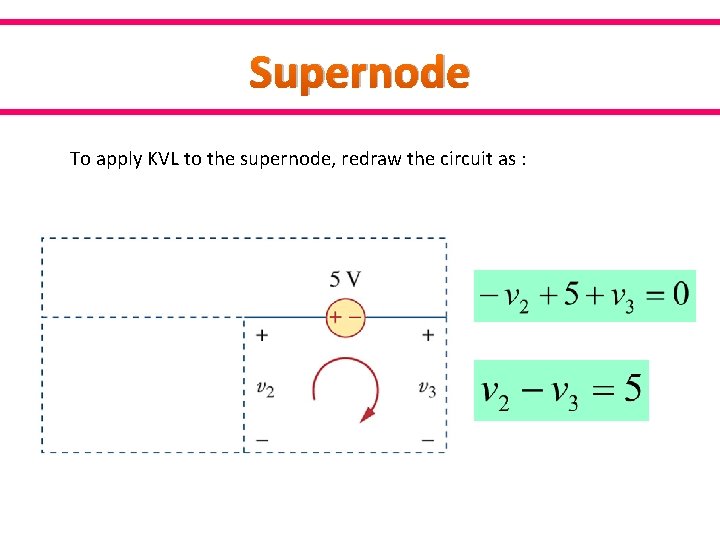

Supernode To apply KVL to the supernode, redraw the circuit as :

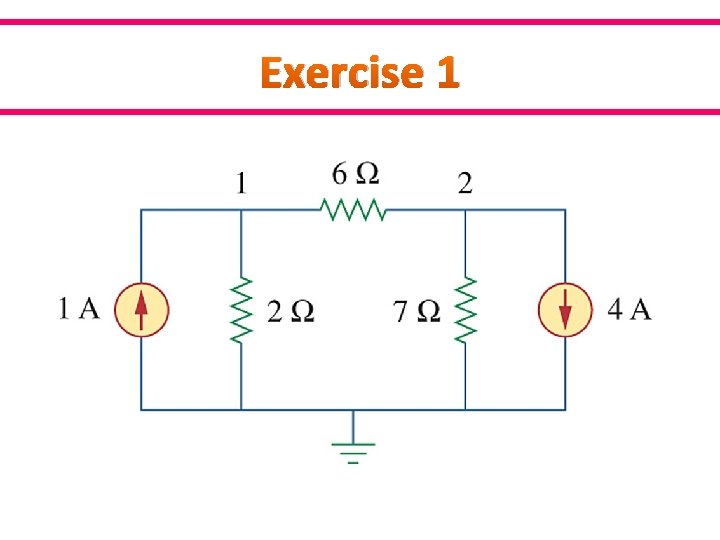

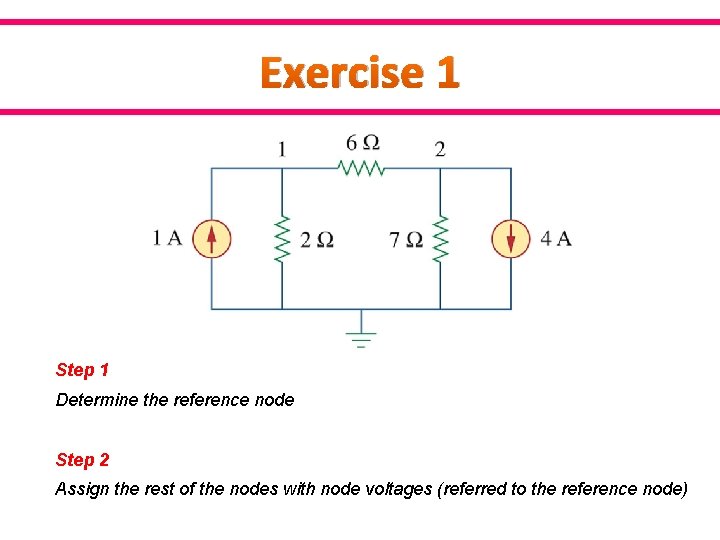

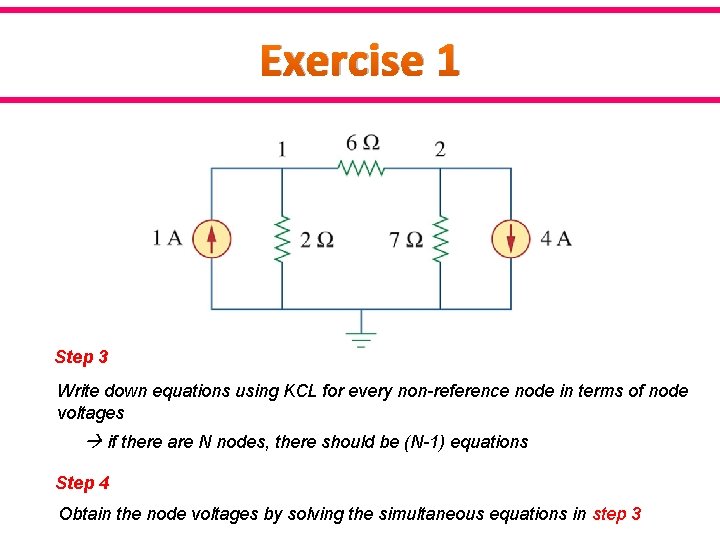

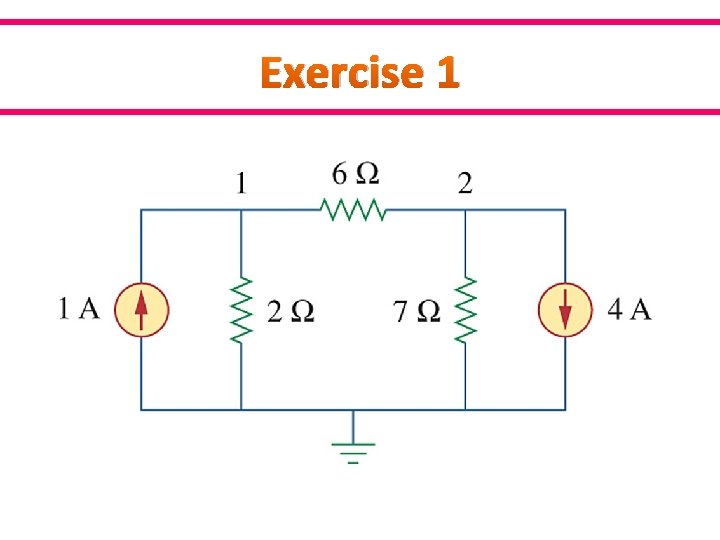

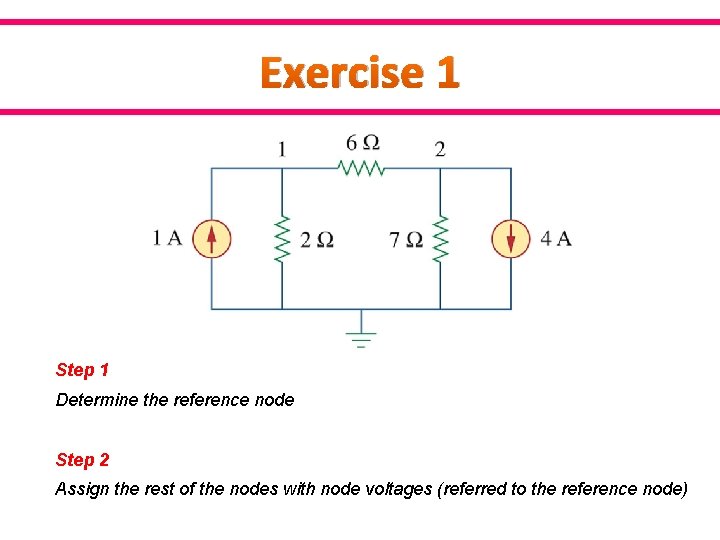

Exercise 1

Exercise 1 Step 1 Determine the reference node Step 2 Assign the rest of the nodes with node voltages (referred to the reference node)

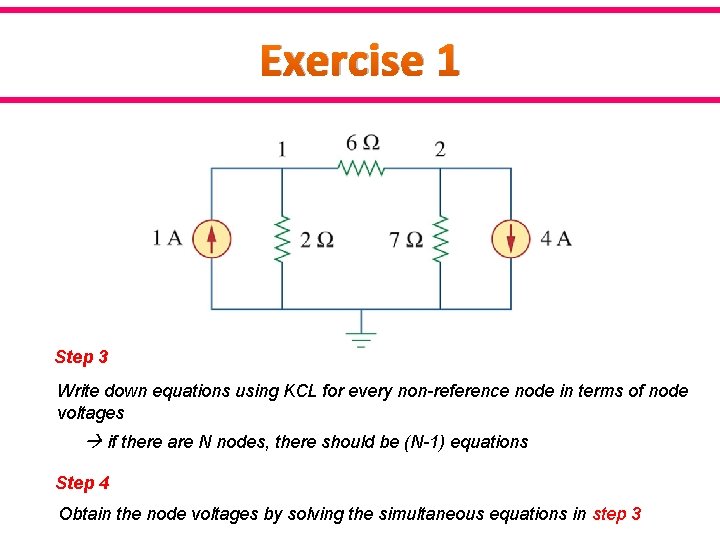

Exercise 1 Step 3 Write down equations using KCL for every non-reference node in terms of node voltages if there are N nodes, there should be (N-1) equations Step 4 Obtain the node voltages by solving the simultaneous equations in step 3

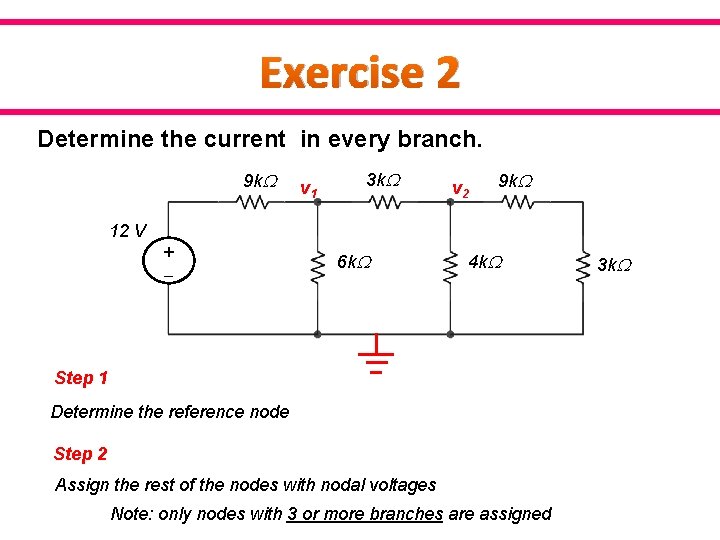

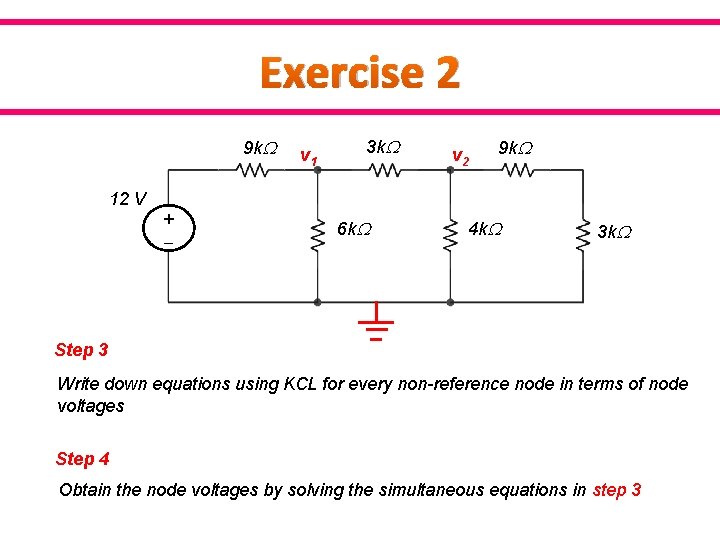

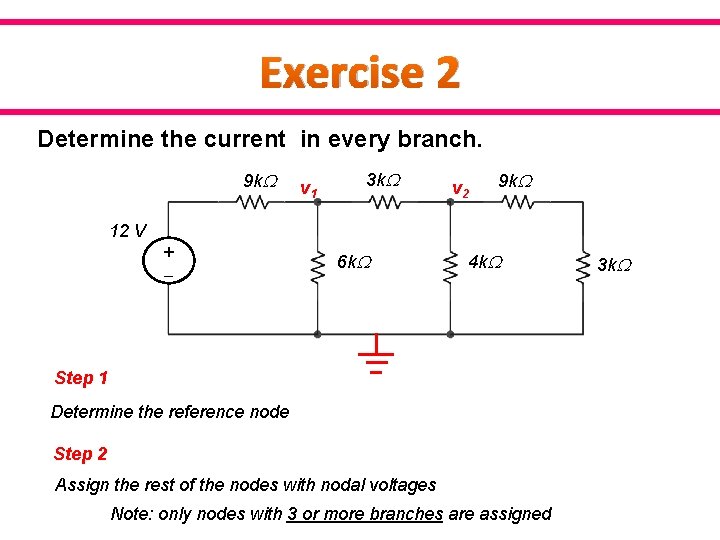

Exercise 2 Determine the current in every branch. 9 k v 1 3 k v 2 9 k 12 V + 6 k 4 k Step 1 Determine the reference node Step 2 Assign the rest of the nodes with nodal voltages Note: only nodes with 3 or more branches are assigned 3 k

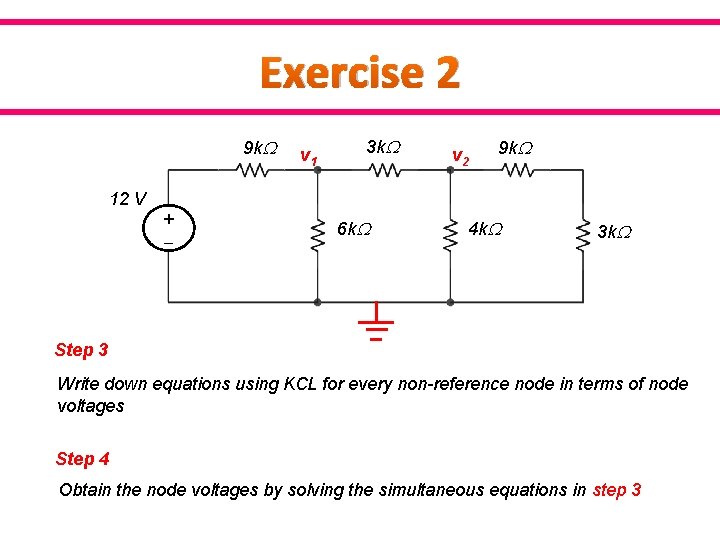

Exercise 2 9 k v 1 3 k v 2 9 k 12 V + 6 k 4 k 3 k Step 3 Write down equations using KCL for every non-reference node in terms of node voltages Step 4 Obtain the node voltages by solving the simultaneous equations in step 3

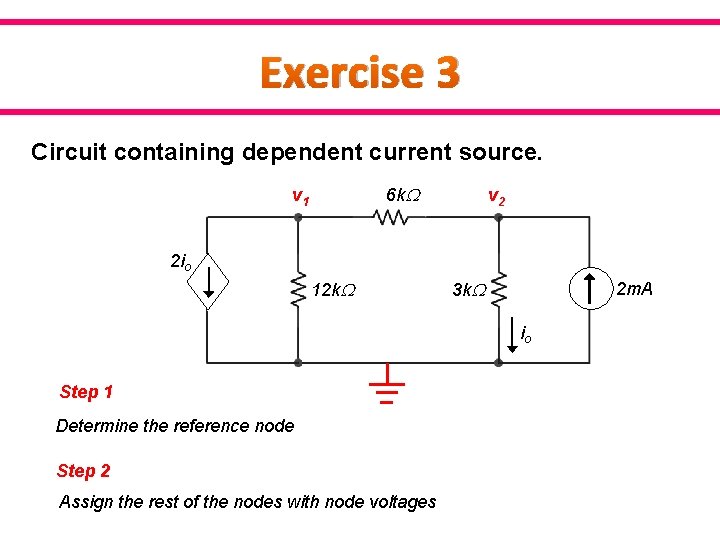

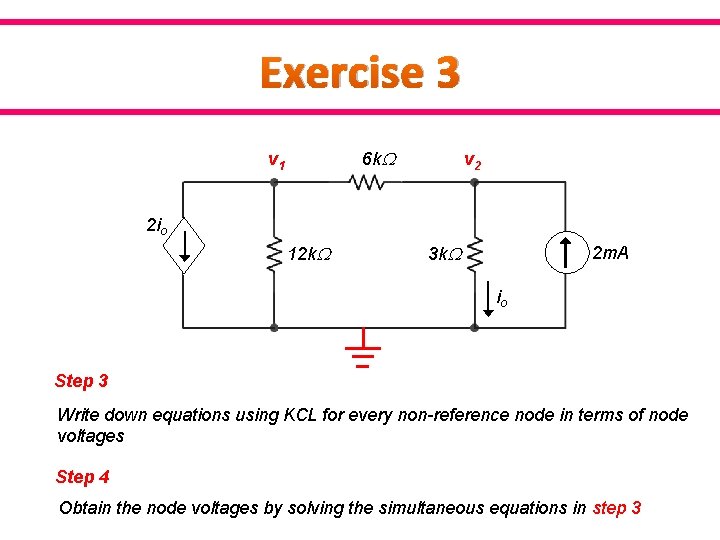

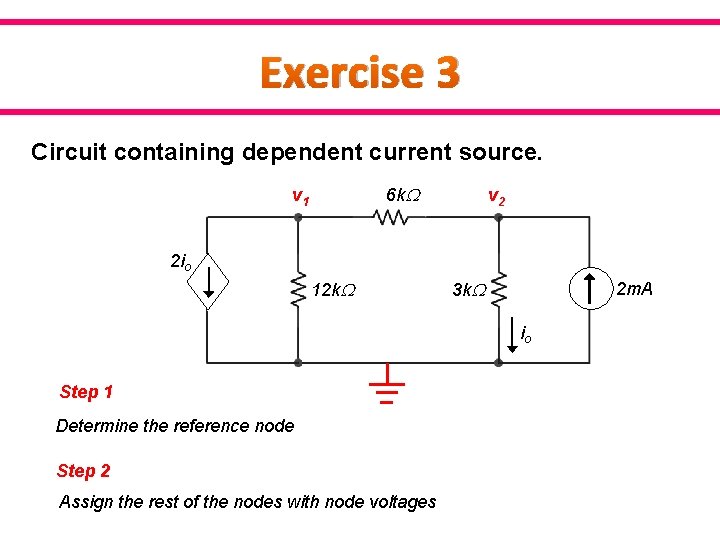

Exercise 3 Circuit containing dependent current source. 6 k v 1 v 2 2 io 12 k 3 k 2 m. A io Step 1 Determine the reference node Step 2 Assign the rest of the nodes with node voltages

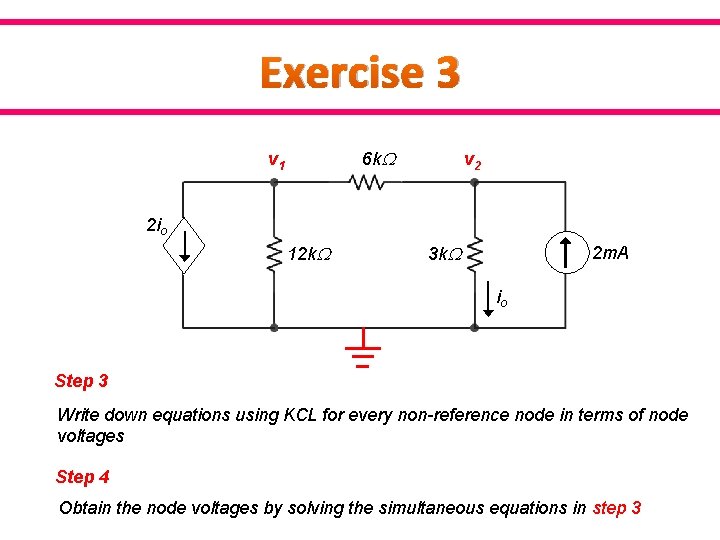

Exercise 3 6 k v 1 v 2 2 io 12 k 3 k 2 m. A io Step 3 Write down equations using KCL for every non-reference node in terms of node voltages Step 4 Obtain the node voltages by solving the simultaneous equations in step 3

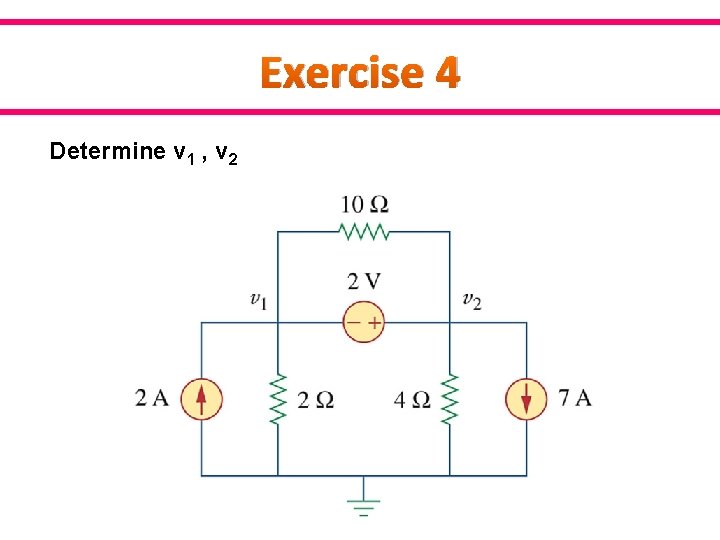

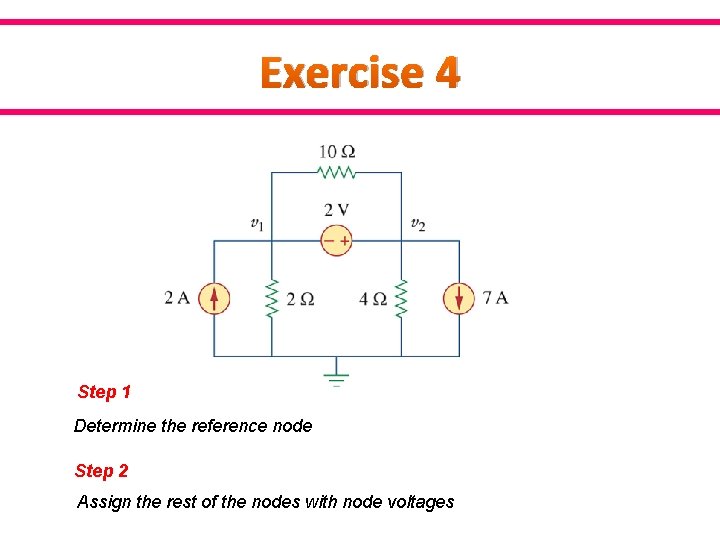

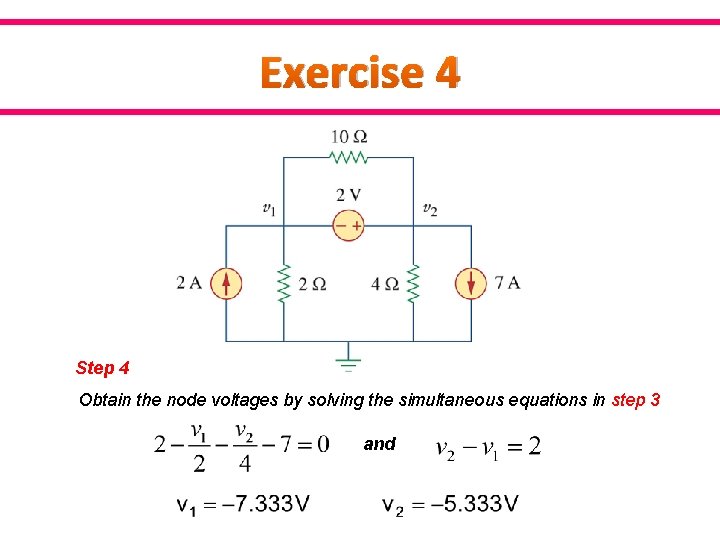

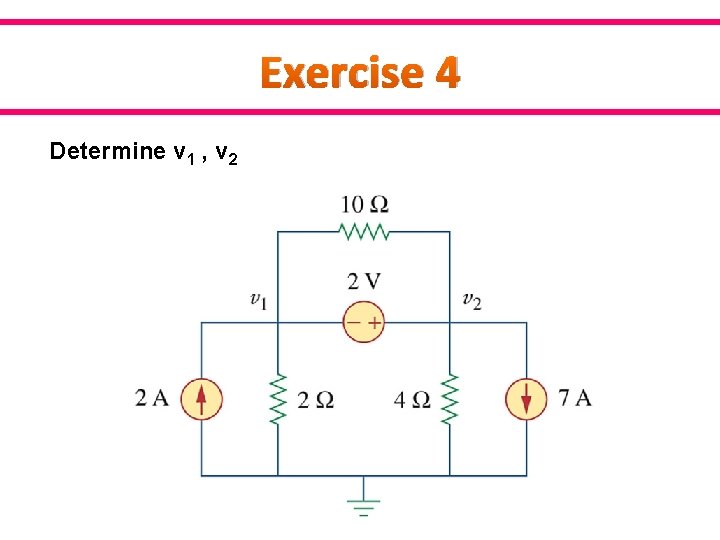

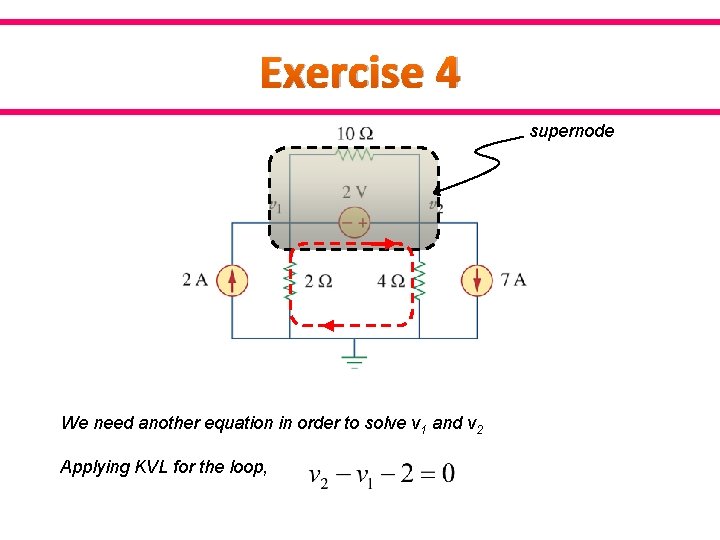

Exercise 4 Determine v 1 , v 2

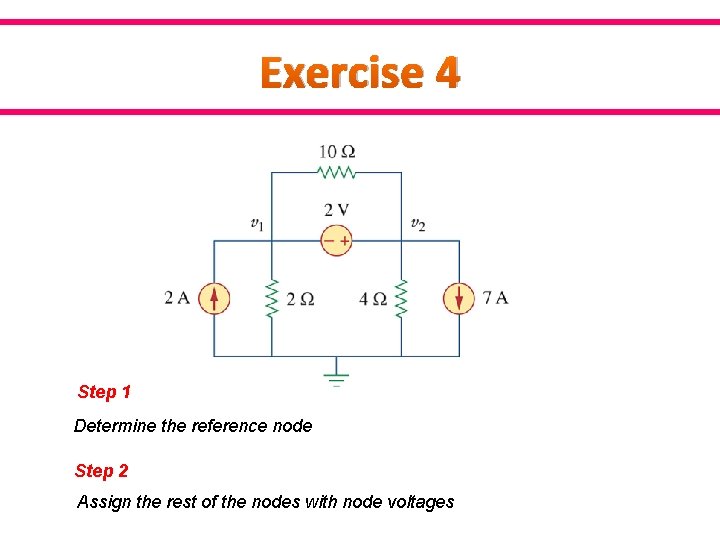

Exercise 4 Step 1 Determine the reference node Step 2 Assign the rest of the nodes with node voltages

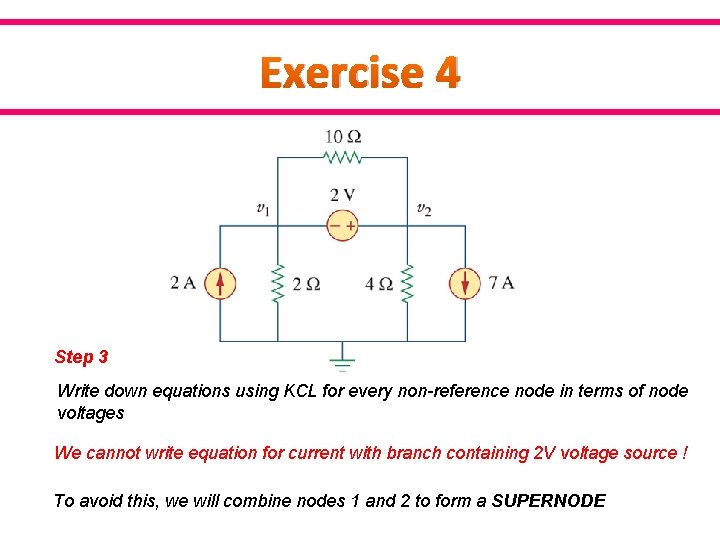

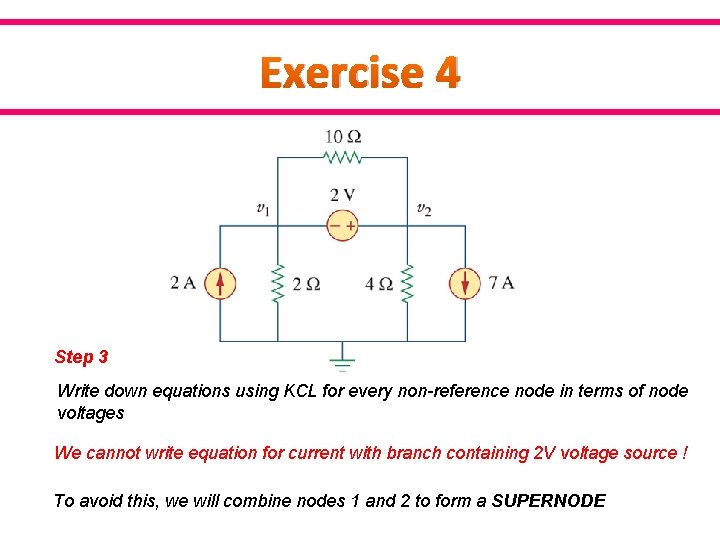

Exercise 4 Step 3 Write down equations using KCL for every non-reference node in terms of node voltages We cannot write equation for current with branch containing 2 V voltage source ! To avoid this, we will combine nodes 1 and 2 to form a SUPERNODE

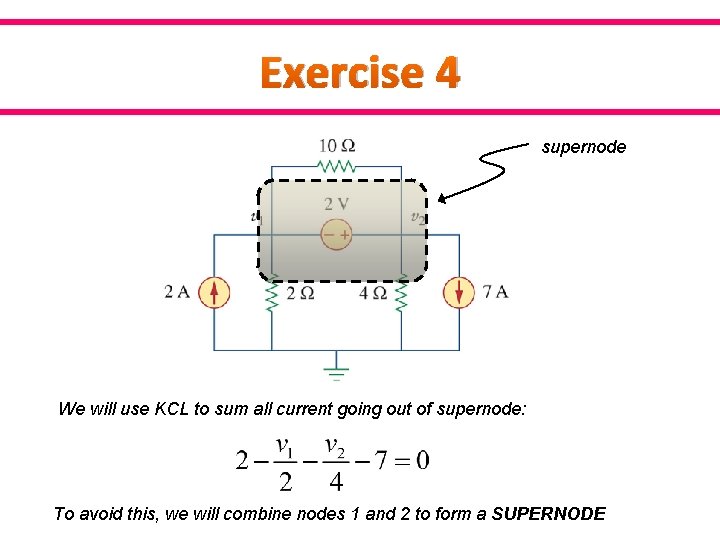

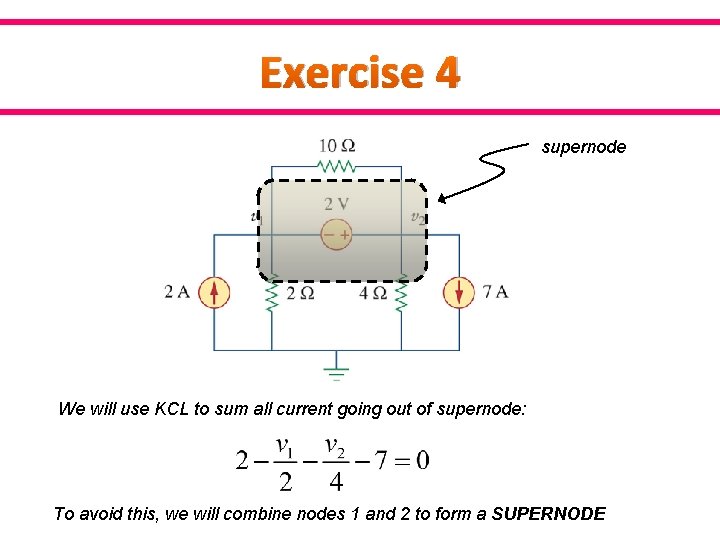

Exercise 4 supernode We will use KCL to sum all current going out of supernode: To avoid this, we will combine nodes 1 and 2 to form a SUPERNODE

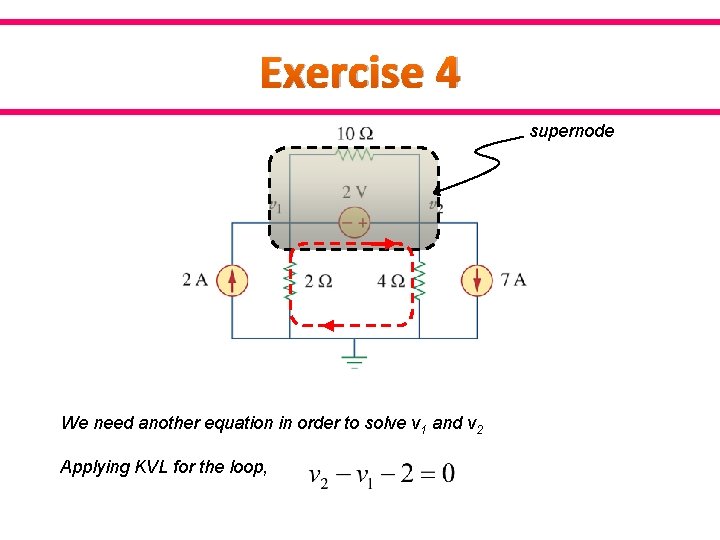

Exercise 4 supernode We need another equation in order to solve v 1 and v 2 Applying KVL for the loop,

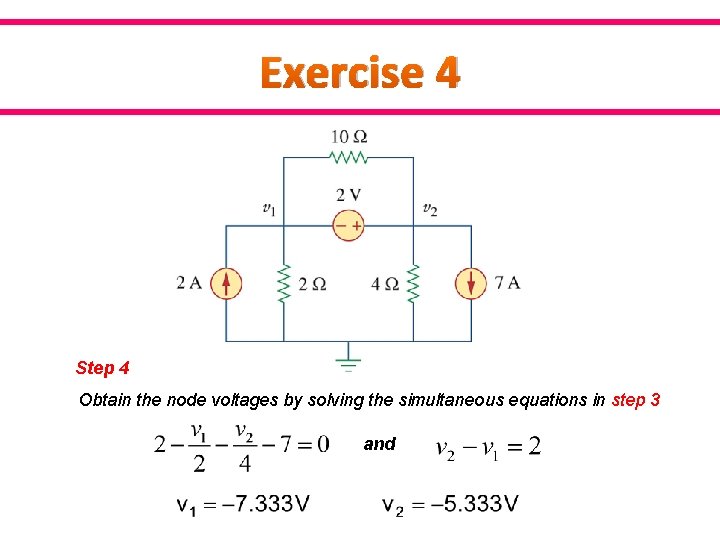

Exercise 4 Step 4 Obtain the node voltages by solving the simultaneous equations in step 3 and

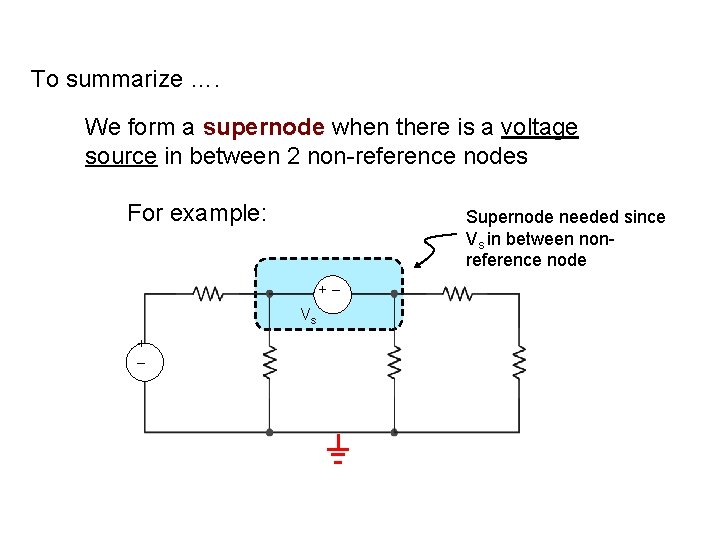

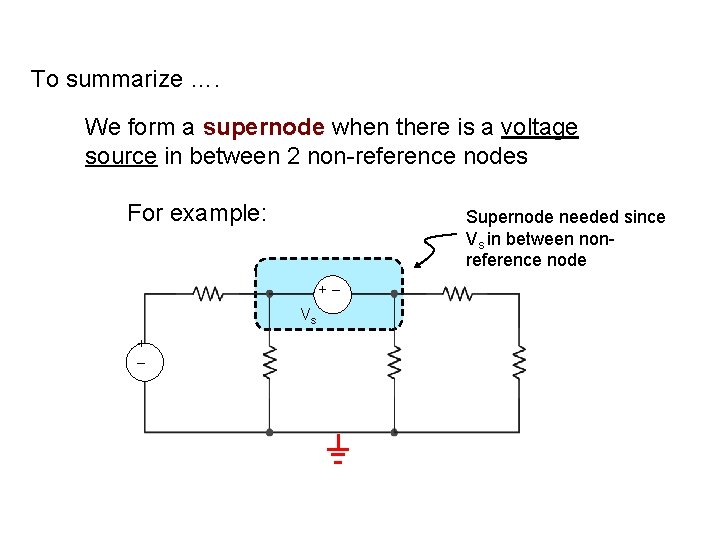

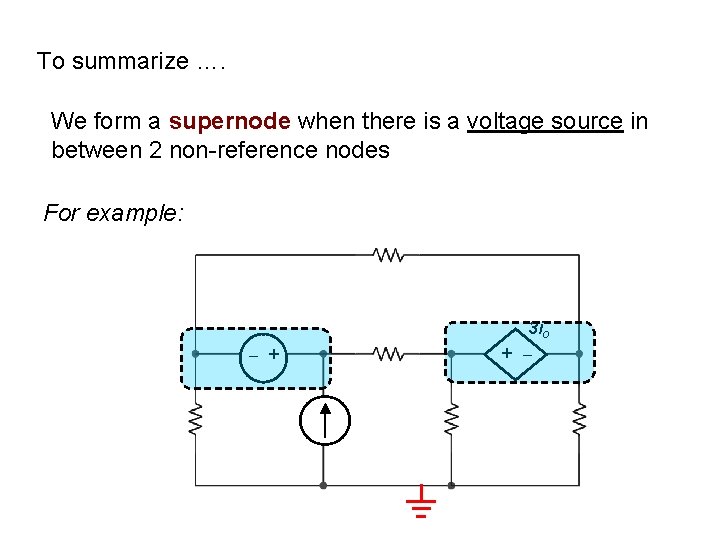

To summarize …. We form a supernode when there is a voltage source in between 2 non-reference nodes For example: Supernode needed since Vs in between nonreference node + Vs +

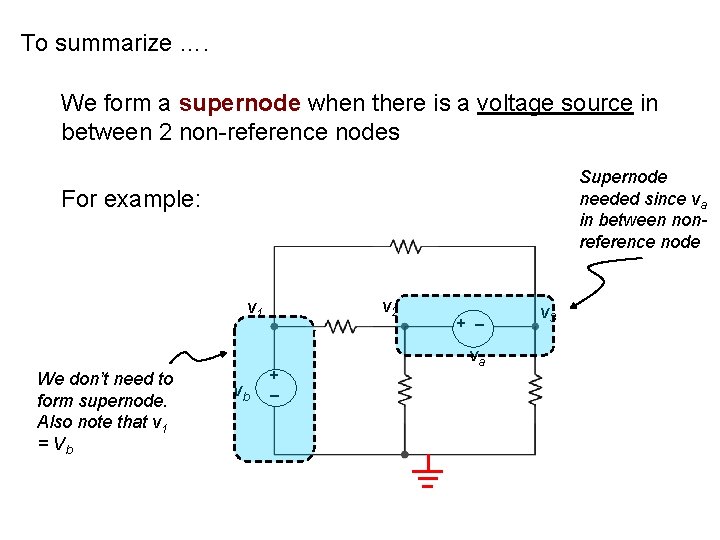

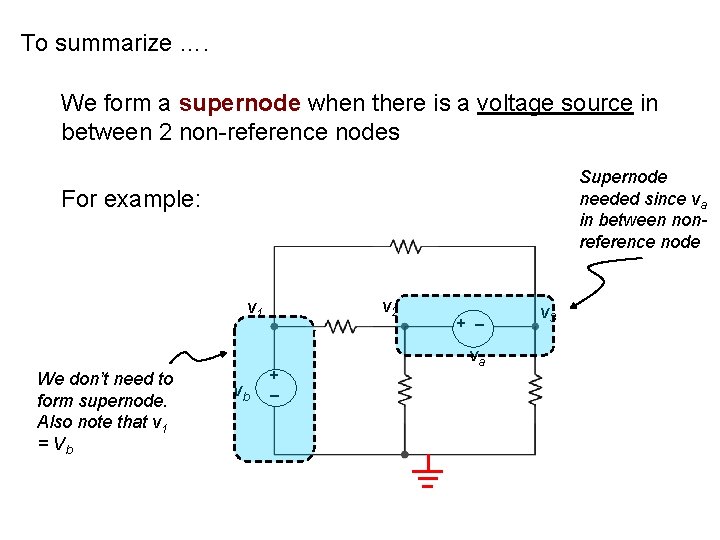

To summarize …. We form a supernode when there is a voltage source in between 2 non-reference nodes Supernode needed since va in between nonreference node For example: v 2 v 1 We don’t need to form supernode. Also note that v 1 = Vb vb + + va v 3

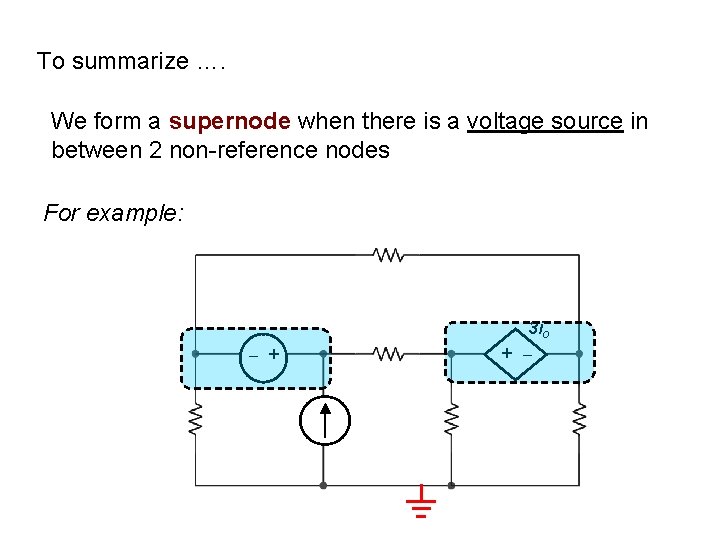

To summarize …. We form a supernode when there is a voltage source in between 2 non-reference nodes For example: 3 io + +

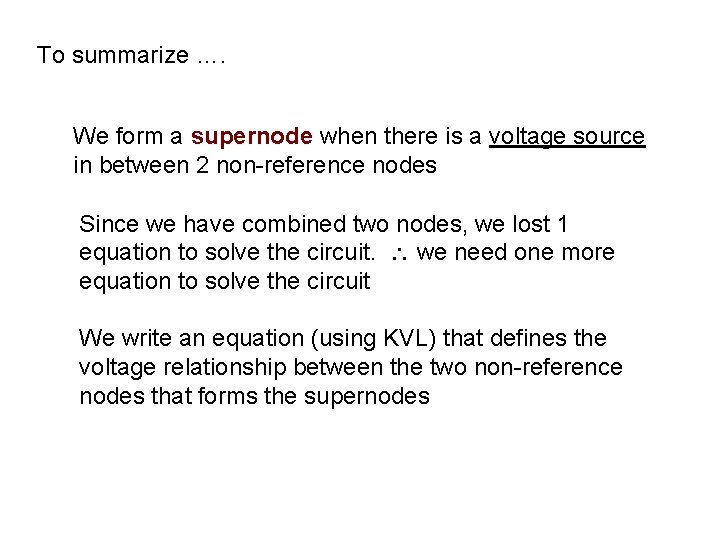

To summarize …. We form a supernode when there is a voltage source in between 2 non-reference nodes Since we have combined two nodes, we lost 1 equation to solve the circuit. we need one more equation to solve the circuit We write an equation (using KVL) that defines the voltage relationship between the two non-reference nodes that forms the supernodes