CHAPTER 3 MEMORY MANAGEMENT PART 2 by Uur

CHAPTER 3 MEMORY MANAGEMENT PART 2 by Uğur Halıcı

3. 3 Paging 1 Logical memorythe OS In paging, PAGE TABLE divide the physical page frame Attributes memory into 0 4 frames which are 3 blocks of small and 1 2 1 fixed size 3 5 Physical memory

3. 3 Paging 2 Logical memorythe OS In paging, PAGE TABLE divide the physical page frame Attributes P 0 memory into 0 4 frames. P 1 which are 3 P 2 small and 1 blocks of 2 1 fixed P 3 size 3 5 Physical memory f 0 f 1 f 2 f 3 f 4 f 5

3. 3 Paging 3 Logical memory OS divides also PAGE TABLE logical memory page the frame Attributes (program) into 0 4 pages which are 1 3 blocks of size 2 equal 1 to frame size. 3 5 Physical memory f 0 f 1 f 2 f 3 f 4 f 5

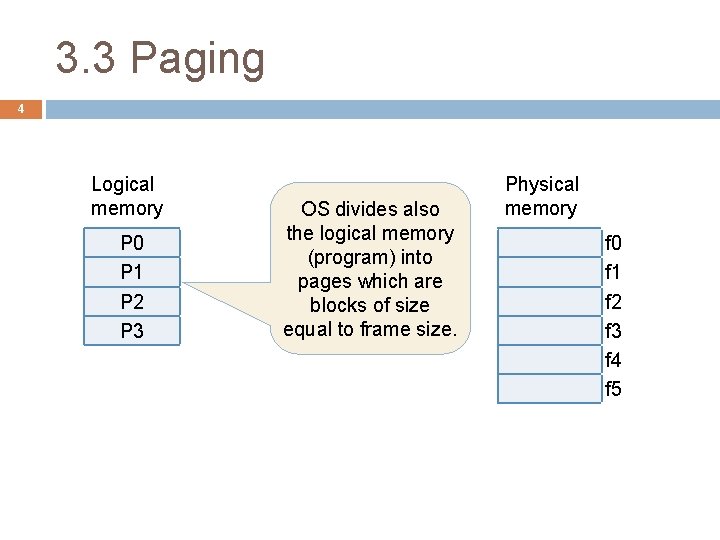

3. 3 Paging 4 Logical memory P 0 P 1 P 2 P 3 OS divides also PAGE TABLE logical memory page the frame Attributes (program) into 0 4 pages which are 1 3 blocks of size 2 equal 1 to frame size. 3 5 Physical memory f 0 f 1 f 2 f 3 f 4 f 5

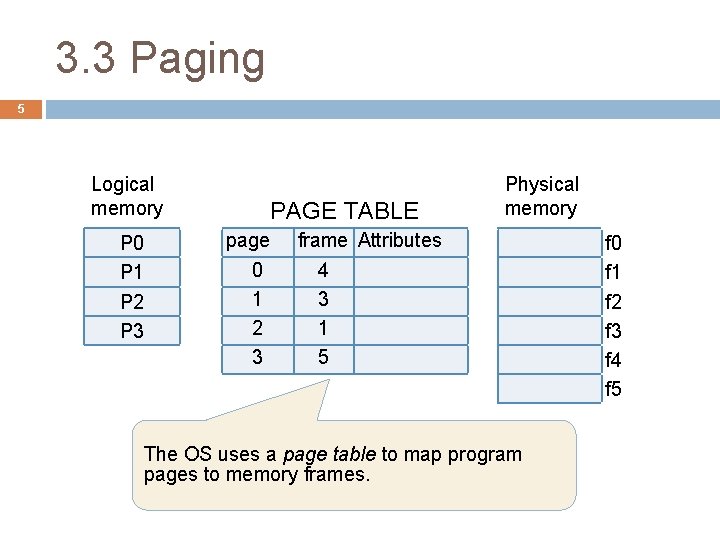

3. 3 Paging 5 Logical memory P 0 P 1 P 2 P 3 PAGE TABLE page 0 1 2 3 Physical memory frame Attributes 4 3 1 5 The OS uses a page table to map program pages to memory frames. f 0 f 1 f 2 f 3 f 4 f 5

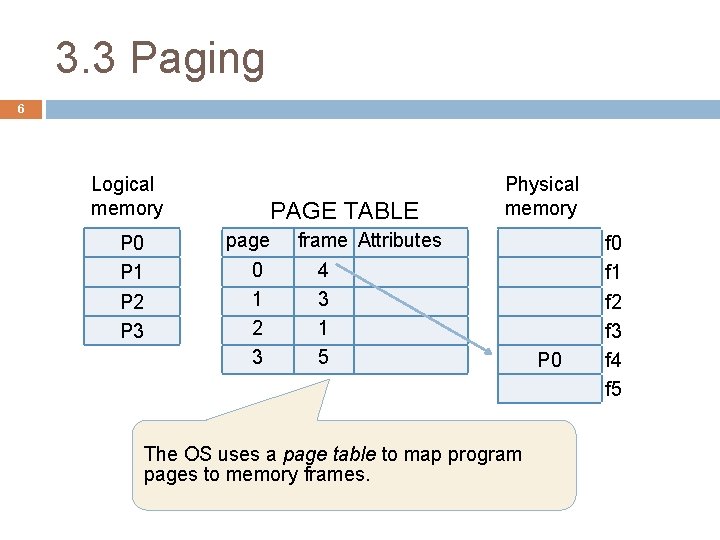

3. 3 Paging 6 Logical memory P 0 P 1 P 2 P 3 PAGE TABLE page 0 1 2 3 Physical memory frame Attributes 4 3 1 5 The OS uses a page table to map program pages to memory frames. P 0 f 1 f 2 f 3 f 4 f 5

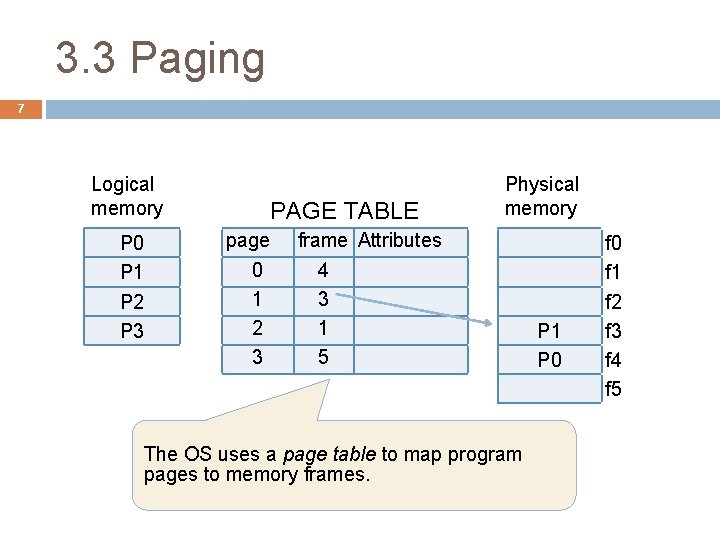

3. 3 Paging 7 Logical memory P 0 P 1 P 2 P 3 PAGE TABLE page 0 1 2 3 Physical memory frame Attributes 4 3 1 5 The OS uses a page table to map program pages to memory frames. P 1 P 0 f 1 f 2 f 3 f 4 f 5

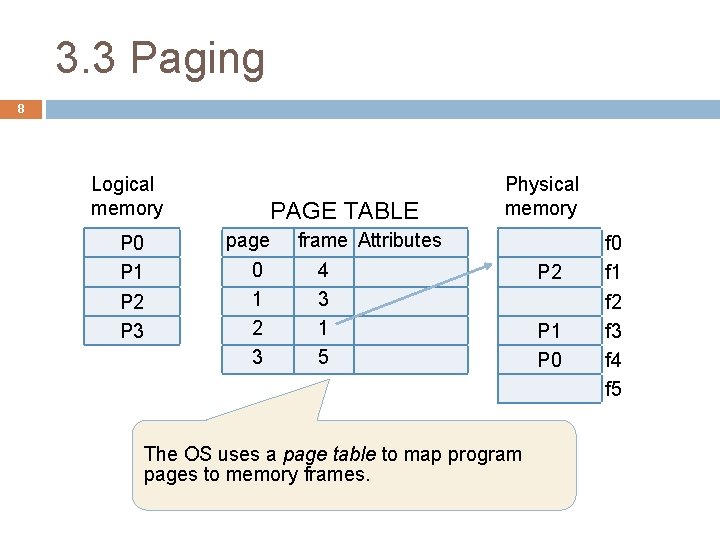

3. 3 Paging 8 Logical memory P 0 P 1 P 2 P 3 PAGE TABLE page 0 1 2 3 Physical memory frame Attributes 4 3 1 5 The OS uses a page table to map program pages to memory frames. P 2 P 1 P 0 f 1 f 2 f 3 f 4 f 5

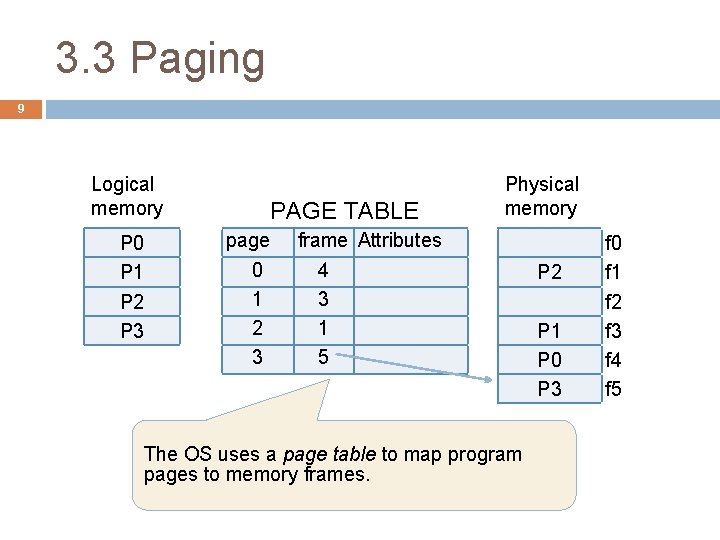

3. 3 Paging 9 Logical memory P 0 P 1 P 2 P 3 PAGE TABLE page 0 1 2 3 Physical memory frame Attributes 4 3 1 5 The OS uses a page table to map program pages to memory frames. P 2 P 1 P 0 P 3 f 0 f 1 f 2 f 3 f 4 f 5

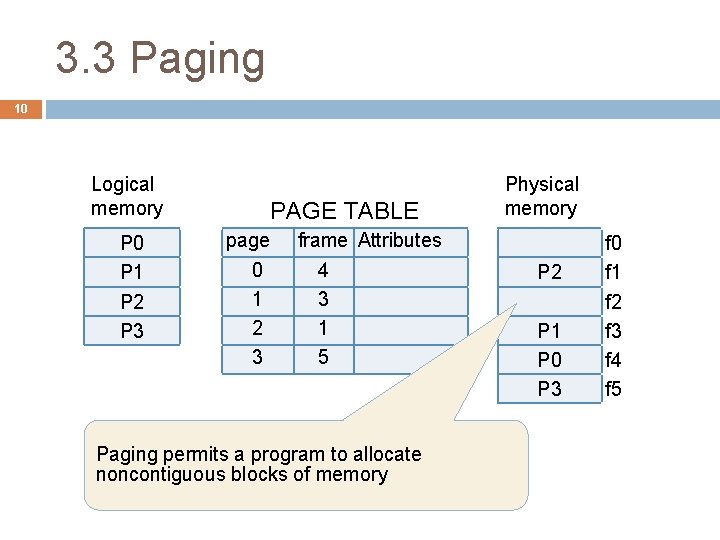

3. 3 Paging 10 Logical memory P 0 P 1 P 2 P 3 PAGE TABLE page 0 1 2 3 frame Attributes 4 3 1 5 Paging permits a program to allocate noncontiguous blocks of memory Physical memory P 2 P 1 P 0 P 3 f 0 f 1 f 2 f 3 f 4 f 5

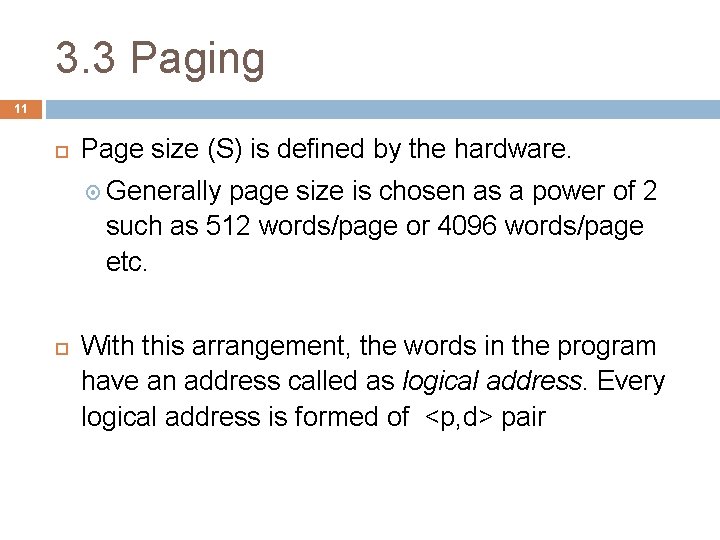

3. 3 Paging 11 Page size (S) is defined by the hardware. Generally page size is chosen as a power of 2 such as 512 words/page or 4096 words/page etc. With this arrangement, the words in the program have an address called as logical address. Every logical address is formed of <p, d> pair

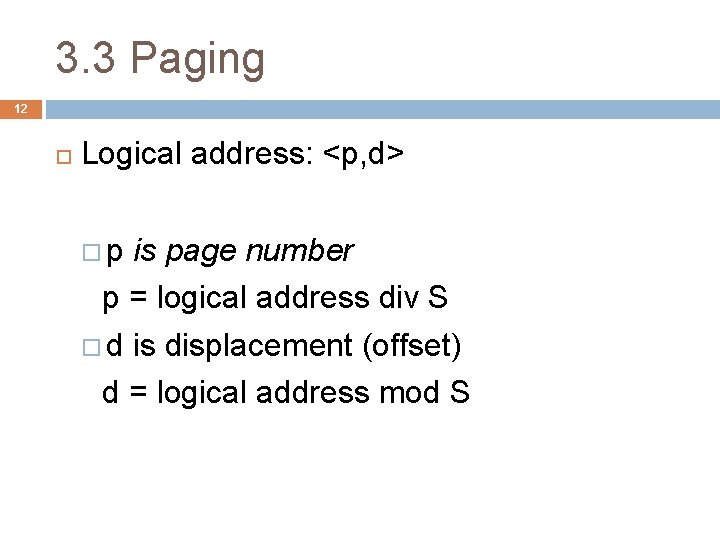

3. 3 Paging 12 Logical address: <p, d> p is page number p = logical address div S d is displacement (offset) d = logical address mod S

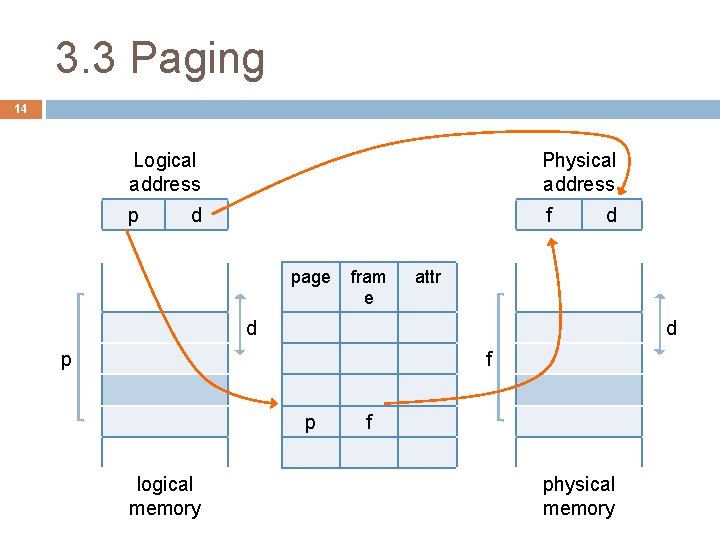

3. 3 Paging 13 When a logical address <p, d> is generated by the processor, first the frame number f corresponding to page p is determined by using the page table and then the physical address is calculated as (f*S+d) and the memory is accessed.

3. 3 Paging 14 Logical address Physical address p f d page fram e d attr d d p f p logical memory f physical memory

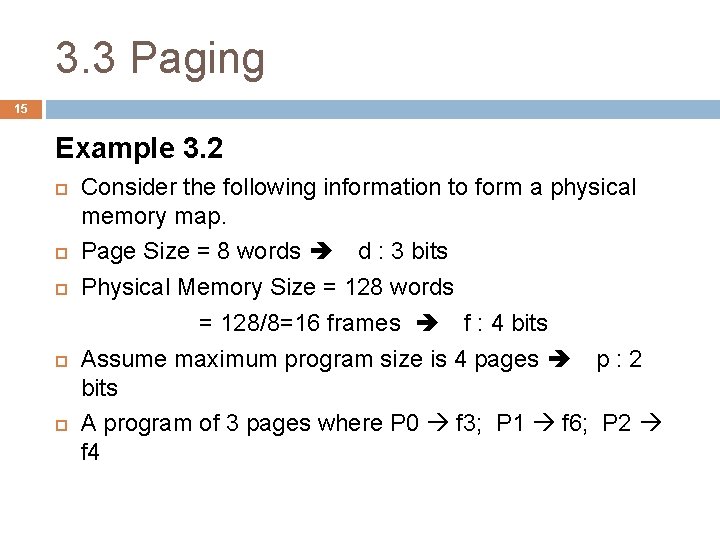

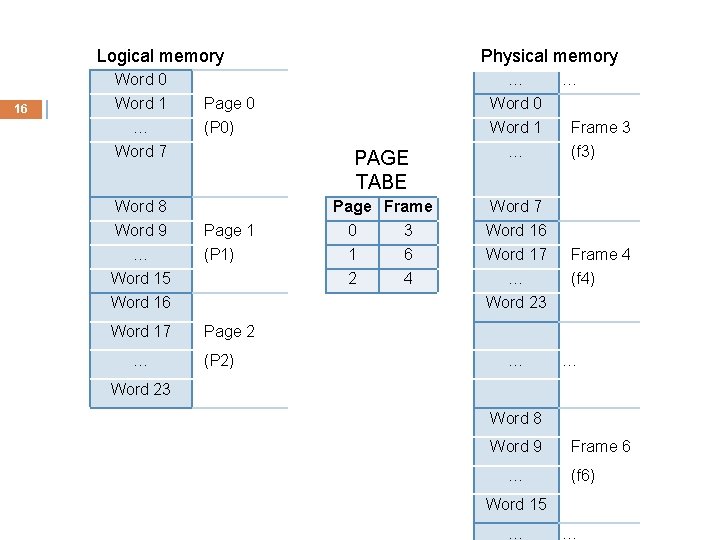

3. 3 Paging 15 Example 3. 2 Consider the following information to form a physical memory map. Page Size = 8 words d : 3 bits Physical Memory Size = 128 words = 128/8=16 frames f : 4 bits Assume maximum program size is 4 pages p : 2 bits A program of 3 pages where P 0 f 3; P 1 f 6; P 2 f 4

Logical memory Physical memory Word 0 16 Word 1 … Word 7 Word 8 Word 9 … Page 0 (P 0) PAGE TABE Page 1 … Word 15 Word 16 (P 1) Word 17 Page 2 … (P 2) Page Frame 0 3 1 2 6 4 Word 0 Word 1 … … Frame 3 (f 3) Word 7 Word 16 Word 17 … Word 23 … Frame 4 (f 4) … Word 23 Word 8 Word 9 … Frame 6 (f 6) Word 15 … …

3. 3 Paging 17 Program Line Word 0 Word 1 … Word 7 Word 8 Word 9 … Word 15 Word 16 Word 17 … Word 23

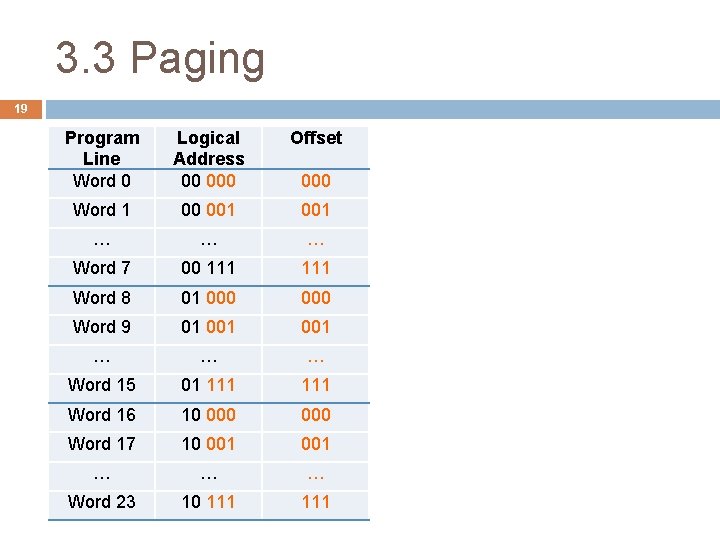

3. 3 Paging 18 Program Line Word 0 Logical Address 00 000 Word 1 00 001 … … Word 7 00 111 Word 8 01 000 Word 9 01 001 … … Word 15 01 111 Word 16 10 000 Word 17 10 001 … … Word 23 10 111

3. 3 Paging 19 Program Line Word 0 Logical Address 00 000 Offset Word 1 00 001 … … … Word 7 00 111 Word 8 01 000 Word 9 01 001 … … … Word 15 01 111 Word 16 10 000 Word 17 10 001 … … … Word 23 10 111 000

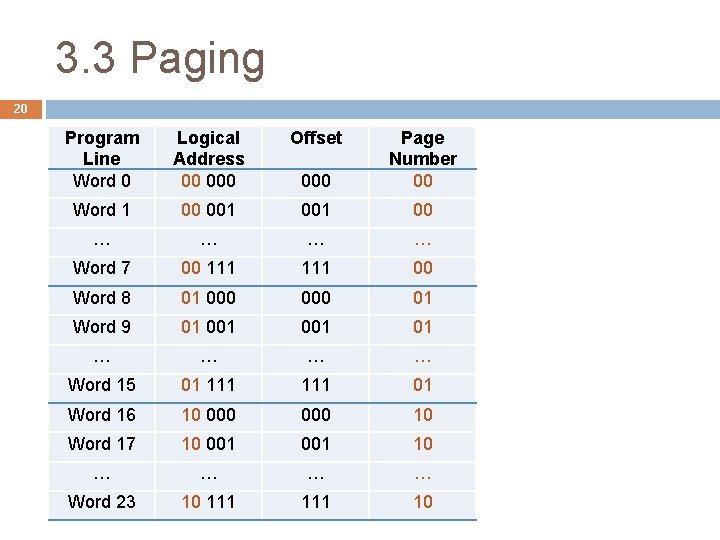

3. 3 Paging 20 Program Line Word 0 Logical Address 00 000 Offset 000 Page Number 00 Word 1 00 001 00 … … Word 7 00 111 00 Word 8 01 000 01 Word 9 01 001 01 … … Word 15 01 111 01 Word 16 10 000 10 Word 17 10 001 10 … … Word 23 10 111 10

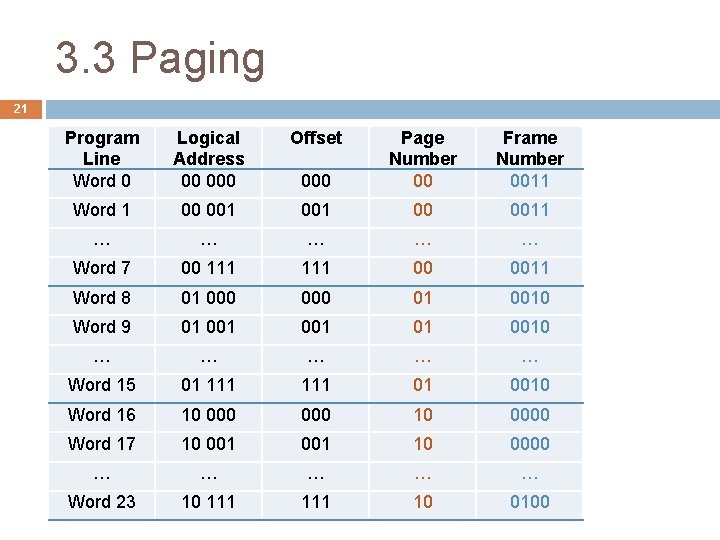

3. 3 Paging 21 Program Line Word 0 Logical Address 00 000 Offset 000 Page Number 00 Frame Number 0011 Word 1 00 0011 … … … Word 7 00 111 00 0011 Word 8 01 000 01 0010 Word 9 01 0010 … … … Word 15 01 111 01 0010 Word 16 10 0000 Word 17 10 001 10 0000 … … … Word 23 10 111 10 0100

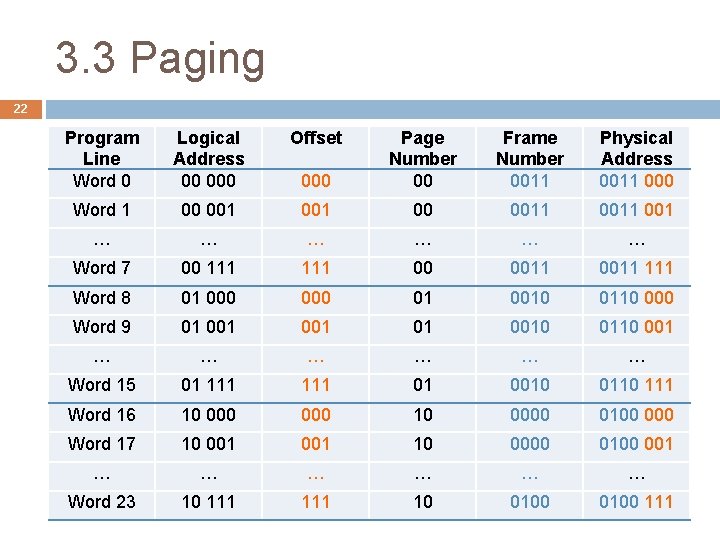

3. 3 Paging 22 Program Line Word 0 Logical Address 00 000 Offset 000 Page Number 00 Frame Number 0011 Physical Address 0011 000 Word 1 00 0011 001 … … … Word 7 00 111 00 0011 111 Word 8 01 000 01 0010 0110 000 Word 9 01 0010 0110 001 … … … Word 15 01 111 01 0010 0110 111 Word 16 10 0000 0100 000 Word 17 10 001 10 0000 0100 001 … … … Word 23 10 111 10 0100 111

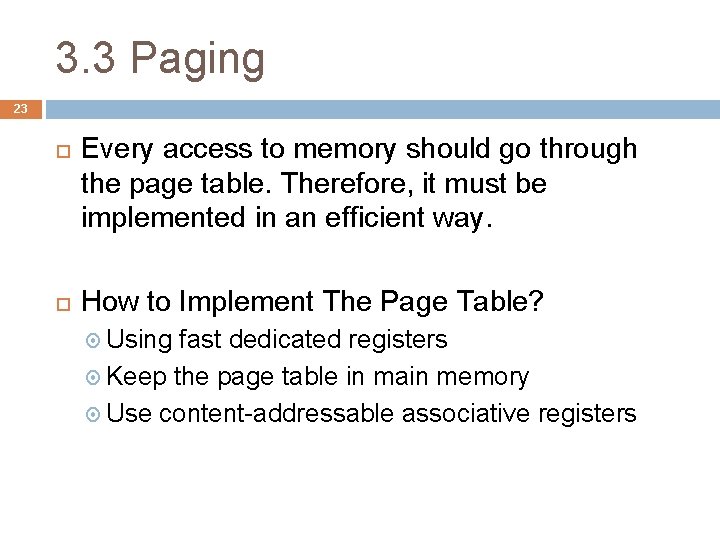

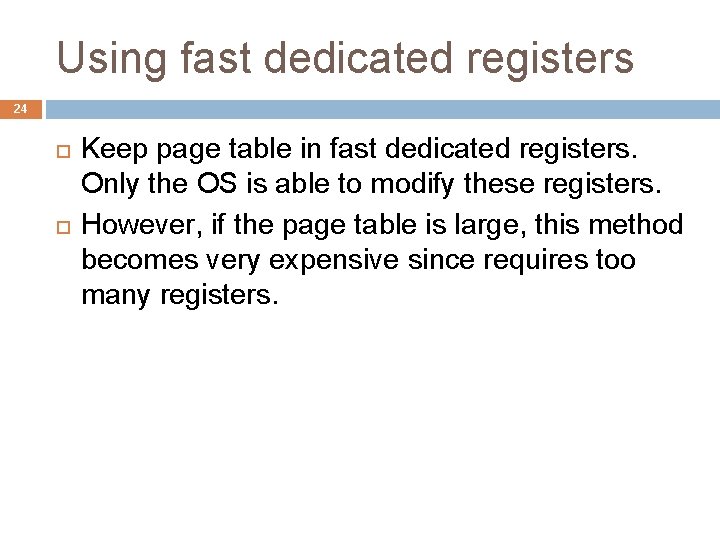

3. 3 Paging 23 Every access to memory should go through the page table. Therefore, it must be implemented in an efficient way. How to Implement The Page Table? Using fast dedicated registers Keep the page table in main memory Use content-addressable associative registers

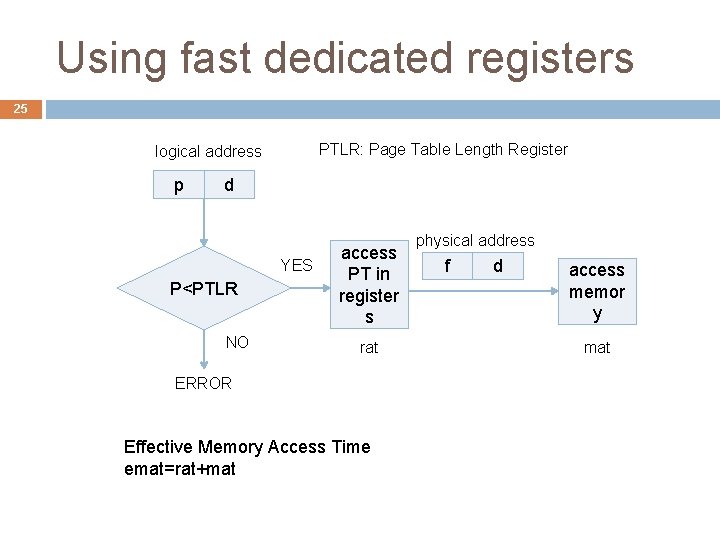

Using fast dedicated registers 24 Keep page table in fast dedicated registers. Only the OS is able to modify these registers. However, if the page table is large, this method becomes very expensive since requires too many registers.

Using fast dedicated registers 25 PTLR: Page Table Length Register logical address p d YES P<PTLR NO access PT in register s rat ERROR Effective Memory Access Time emat=rat+mat physical address f d access memor y mat

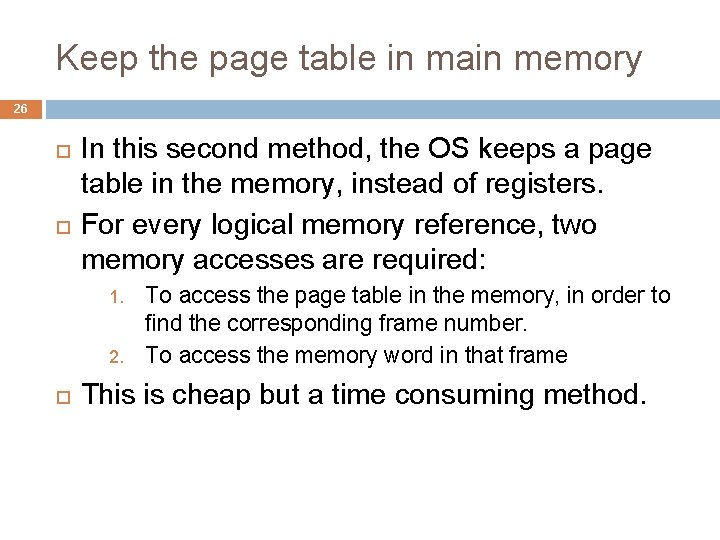

Keep the page table in main memory 26 In this second method, the OS keeps a page table in the memory, instead of registers. For every logical memory reference, two memory accesses are required: 1. 2. To access the page table in the memory, in order to find the corresponding frame number. To access the memory word in that frame This is cheap but a time consuming method.

Keep the page table in main memory 27 PTBR: Page Table Base Register PTLR: Page Table Length Register logical address p d P<PTLR Access PT entry YES in Memory at address PTBR + p NO mat ERROR Effective Memory Access Time: emat=mat+mat=2 mat physical address f d access memor y mat

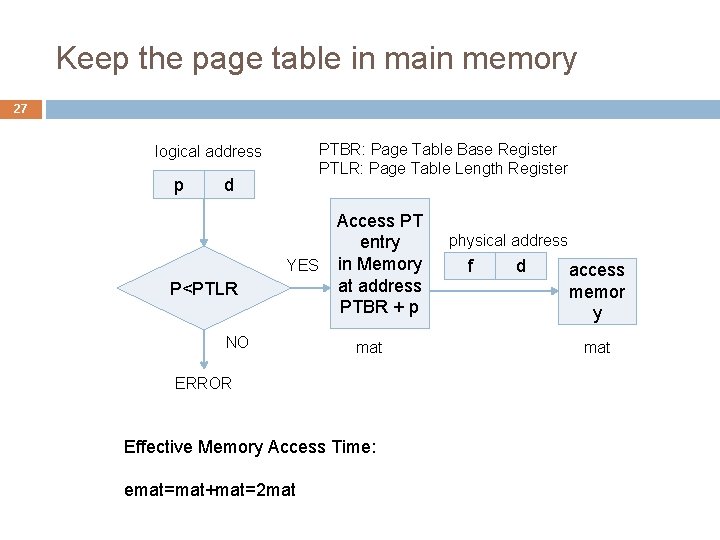

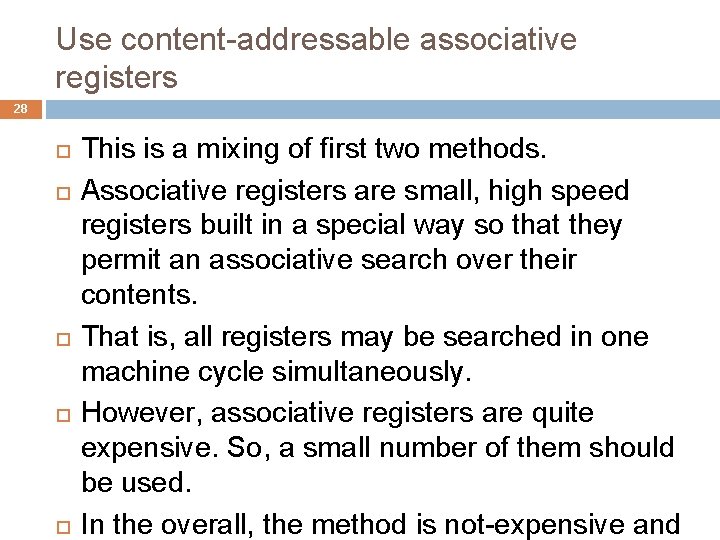

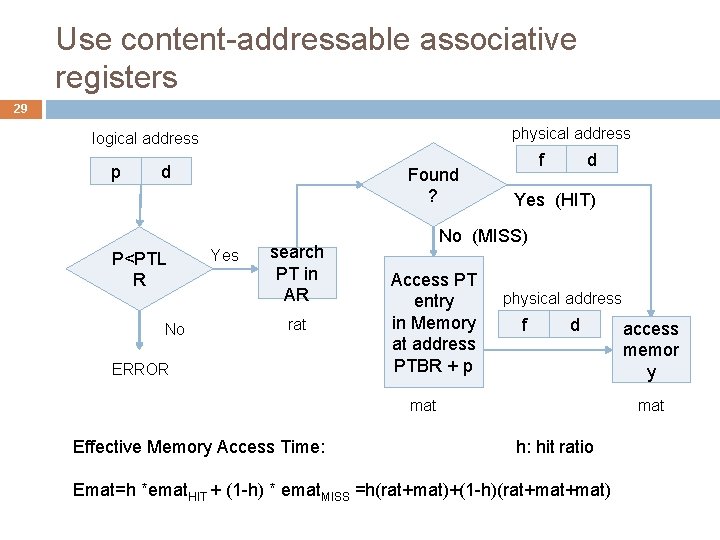

Use content-addressable associative registers 28 This is a mixing of first two methods. Associative registers are small, high speed registers built in a special way so that they permit an associative search over their contents. That is, all registers may be searched in one machine cycle simultaneously. However, associative registers are quite expensive. So, a small number of them should be used. In the overall, the method is not-expensive and

Use content-addressable associative registers 29 physical address logical address p d P<PTL R No Found ? Yes search PT in AR rat ERROR f d Yes (HIT) No (MISS) Access PT entry in Memory at address PTBR + p physical address f d mat Effective Memory Access Time: access memor y mat h: hit ratio Emat=h *emat. HIT + (1 -h) * emat. MISS =h(rat+mat)+(1 -h)(rat+mat)

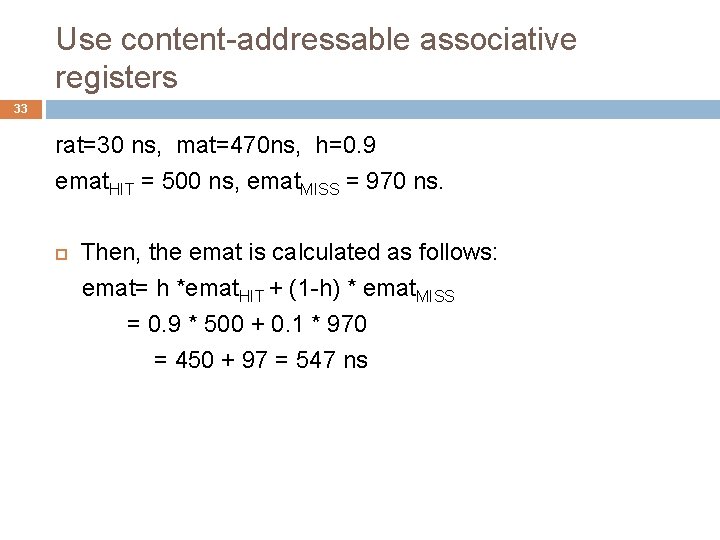

Use content-addressable associative registers 30 Assume we have a paging system which uses associative registers. These associative registers have an access time of 30 ns, and the memory access time is 470 ns. The system has a hit ratio of 90 %. rat=30 ns mat=470 ns h=0. 9

Use content-addressable associative registers 31 rat=30 ns, mat=470 ns, h=0. 9 Now, if the page number is found in one of the associative registers, then the effective access time: emat. HIT = 30 + 470 = 500 ns. Because one access to associative registers and one access to the main memory is sufficient.

Use content-addressable associative registers 32 rat=30 ns, mat=470 ns, h=0. 9 On the other hand, if the page number is not found in associative registers, then the effective access time: emat. MISS = 30 + (470+470) = 970 ns. Since one access to associative registers and two accesses to the main memory are required.

Use content-addressable associative registers 33 rat=30 ns, mat=470 ns, h=0. 9 emat. HIT = 500 ns, emat. MISS = 970 ns. Then, the emat is calculated as follows: emat= h *emat. HIT + (1 -h) * emat. MISS = 0. 9 * 500 + 0. 1 * 970 = 450 + 97 = 547 ns

Sharing Pages 34 Sharing pages is possible in a paging system, and is an important advantage of paging. It is possible to share system procedures or programs, user procedures or programs, and possibly data area. Sharing pages is especially advantageous in timesharing systems.

Sharing Pages 35 A reentrant program (non-self-modifying code = read only) never changes during execution. So, more than one process can execute the same code at the same time. Each process will have its own data storage and its own copy of registers to hold the data for its own execution of the shared program.

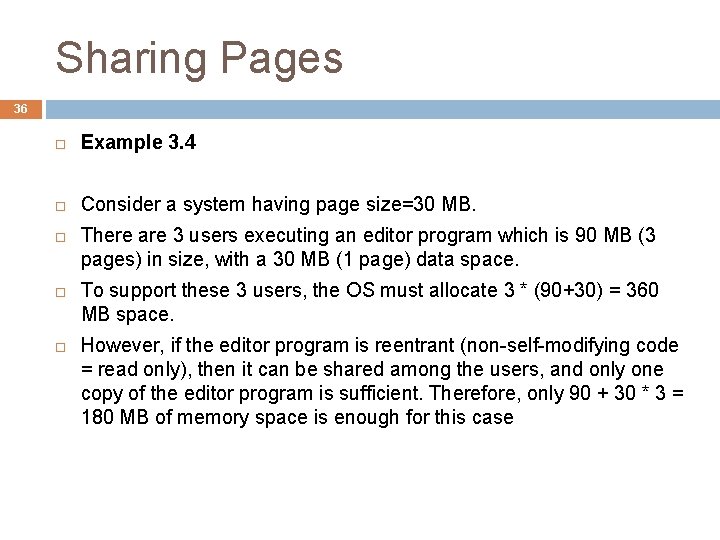

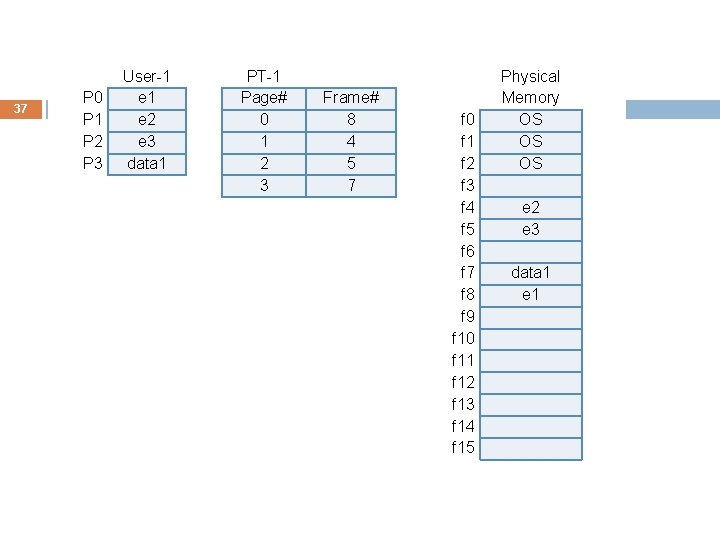

Sharing Pages 36 Example 3. 4 Consider a system having page size=30 MB. There are 3 users executing an editor program which is 90 MB (3 pages) in size, with a 30 MB (1 page) data space. To support these 3 users, the OS must allocate 3 * (90+30) = 360 MB space. However, if the editor program is reentrant (non-self-modifying code = read only), then it can be shared among the users, and only one copy of the editor program is sufficient. Therefore, only 90 + 30 * 3 = 180 MB of memory space is enough for this case

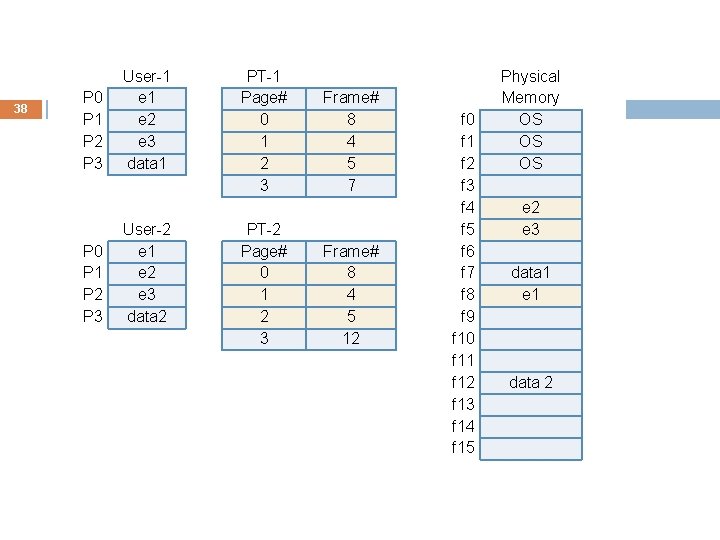

37 P 0 P 1 P 2 P 3 User-1 e 2 e 3 data 1 PT-1 Page# 0 1 2 3 Frame# 8 4 5 7 P 0 P 1 P 2 P 3 User-2 e 1 e 2 e 3 data 2 PT-2 Page# 0 1 2 3 Frame# 8 4 5 12 P 0 P 1 P 2 P 3 User-3 e 1 e 2 e 3 data 3 PT-3 Page# 0 1 2 3 Frame# 8 4 5 10 f 1 f 2 f 3 f 4 f 5 f 6 f 7 f 8 f 9 f 10 f 11 f 12 f 13 f 14 f 15 Physical Memory OS OS OS e 2 e 3 data 1 e 1

38 P 0 P 1 P 2 P 3 User-1 e 2 e 3 data 1 PT-1 Page# 0 1 2 3 P 0 P 1 P 2 P 3 User-2 e 1 e 2 e 3 data 2 PT-2 Page# 0 1 2 3 P 0 P 1 P 2 P 3 User-3 e 1 e 2 e 3 data 3 PT-3 Page# 0 1 2 3 Frame# 8 4 5 7 Frame# 8 4 5 12 Frame# 8 4 5 10 f 1 f 2 f 3 f 4 f 5 f 6 f 7 f 8 f 9 f 10 f 11 f 12 f 13 f 14 f 15 Physical Memory OS OS OS e 2 e 3 data 1 e 1 data 2

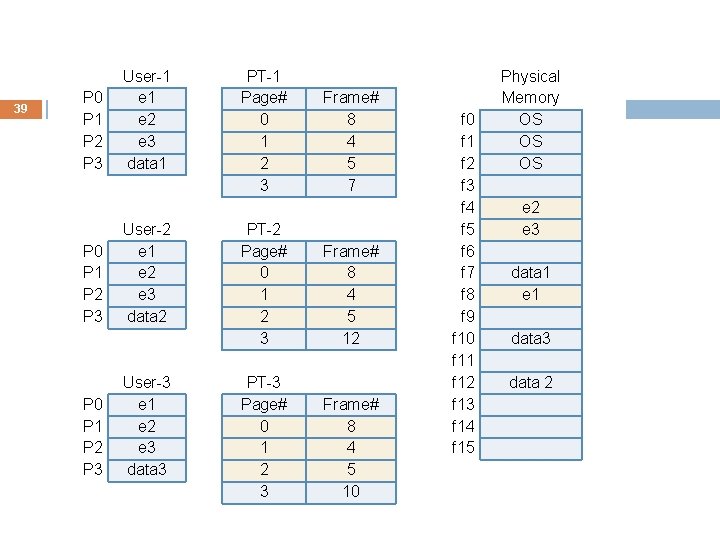

39 P 0 P 1 P 2 P 3 User-1 e 2 e 3 data 1 User-2 e 1 e 2 e 3 data 2 User-3 e 1 e 2 e 3 data 3 PT-1 Page# 0 1 2 3 PT-2 Page# 0 1 2 3 PT-3 Page# 0 1 2 3 Frame# 8 4 5 7 Frame# 8 4 5 12 Frame# 8 4 5 10 f 1 f 2 f 3 f 4 f 5 f 6 f 7 f 8 f 9 f 10 f 11 f 12 f 13 f 14 f 15 Physical Memory OS OS OS e 2 e 3 data 1 e 1 data 3 data 2

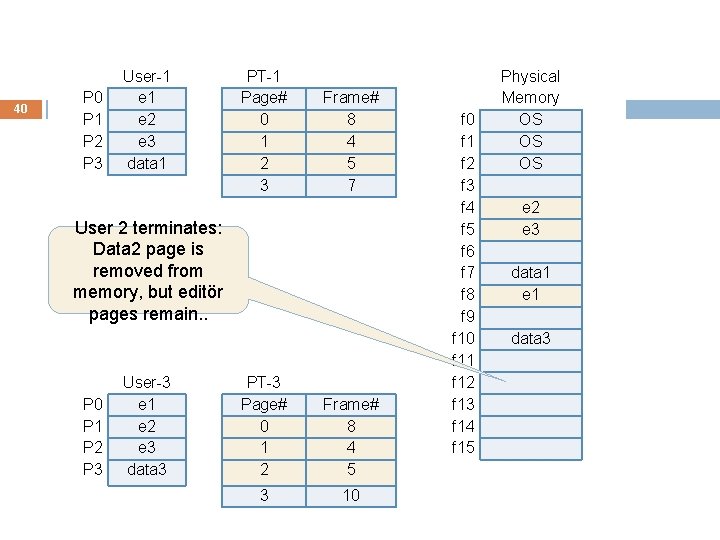

40 P 1 P 2 P 3 User-1 e 2 e 3 data 1 PT-1 Page# 0 1 2 3 User 2 User-2 terminates: PT-2 Data 2 e 1 page is P 0 Page# removed P 1 e 2 from 0 memory, P 2 e 3 but editör 1 pages remain. . P 3 data 2 2 P 0 P 1 P 2 P 3 User-3 e 1 e 2 e 3 data 3 Frame# 8 4 5 7 3 Frame# 8 4 5 12 PT-3 Page# 0 1 2 Frame# 8 4 5 3 10 f 1 f 2 f 3 f 4 f 5 f 6 f 7 f 8 f 9 f 10 f 11 f 12 f 13 f 14 f 15 Physical Memory OS OS OS e 2 e 3 data 1 e 1 data 3

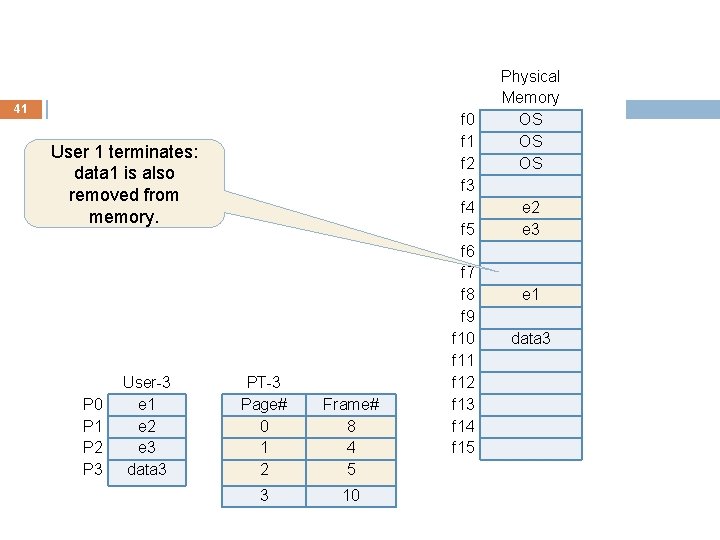

41 P 0 P 1 P 2 User 1 P 3 User-1 e 2 e 3 terminates: data 1 is also removed from memory. P 0 P 1 P 2 P 3 User-2 e 1 e 2 e 3 data 2 User-3 e 1 e 2 e 3 data 3 PT-1 Page# 0 1 2 3 Frame# 8 4 5 7 PT-2 Page# 0 1 2 3 Frame# 8 4 5 12 PT-3 Page# 0 1 2 Frame# 8 4 5 3 10 f 1 f 2 f 3 f 4 f 5 f 6 f 7 f 8 f 9 f 10 f 11 f 12 f 13 f 14 f 15 Physical Memory OS OS OS e 2 e 3 e 1 data 3

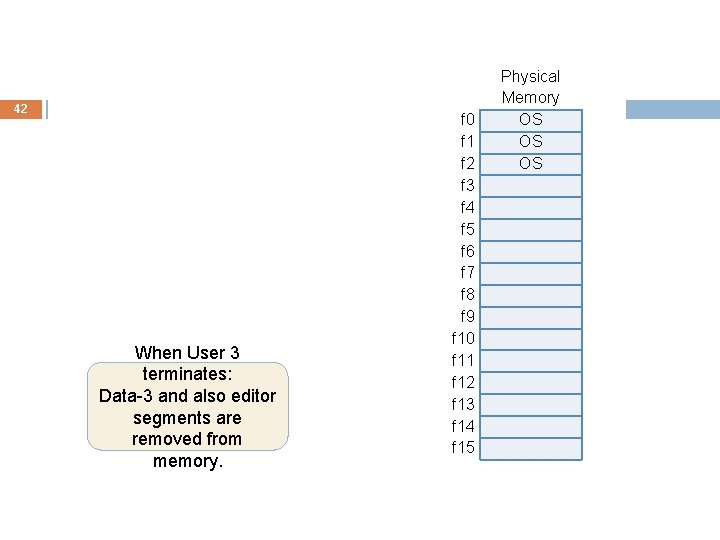

42 P 0 P 1 P 2 P 3 User-1 e 2 e 3 data 1 PT-1 Page# 0 1 2 3 Frame# 8 4 5 7 P 0 P 1 P 2 P 3 User-2 e 1 e 2 e 3 data 2 PT-2 Page# 0 1 2 3 Frame# 8 4 5 12 When User 3 terminates: PT-3 User-3 P 0 Data-3 e 1 and also editor Page# segments are P 1 e 2 0 removed from 1 P 2 e 3 memory. P 3 data 3 2 3 Frame# 8 4 5 10 f 1 f 2 f 3 f 4 f 5 f 6 f 7 f 8 f 9 f 10 f 11 f 12 f 13 f 14 f 15 Physical Memory OS OS OS

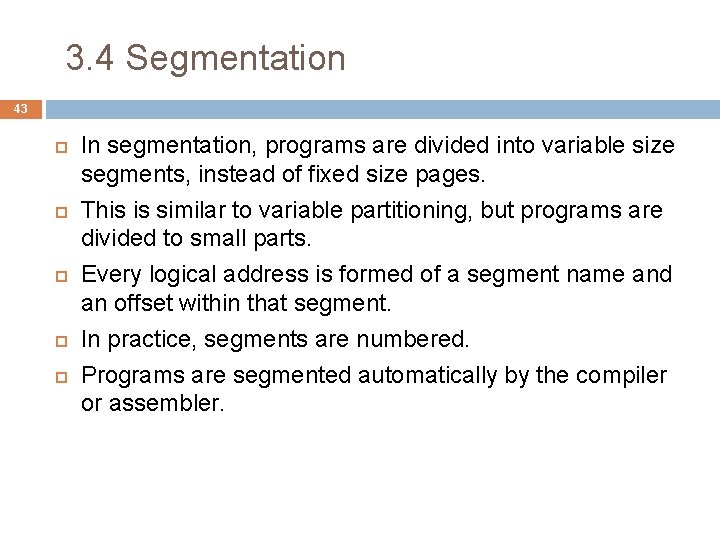

3. 4 Segmentation 43 In segmentation, programs are divided into variable size segments, instead of fixed size pages. This is similar to variable partitioning, but programs are divided to small parts. Every logical address is formed of a segment name and an offset within that segment. In practice, segments are numbered. Programs are segmented automatically by the compiler or assembler.

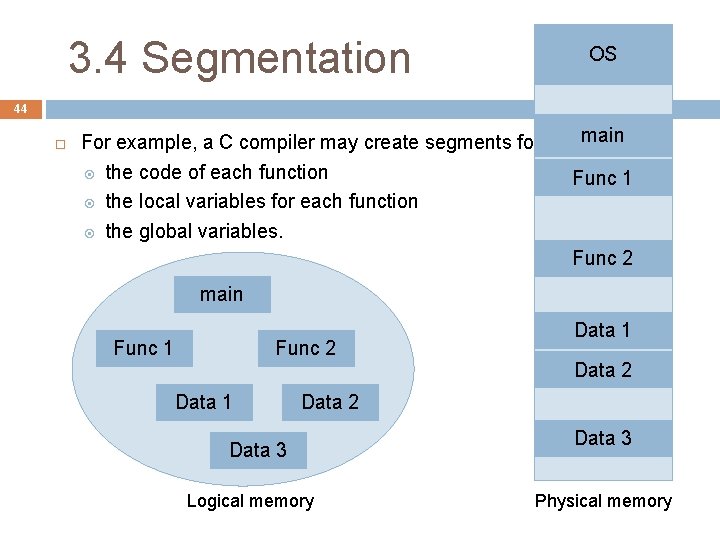

3. 4 Segmentation OS 44 For example, a C compiler may create segments for: the code of each function the local variables for each function the global variables. main Func 1 Func 2 Data 1 Data 2 Data 3 Logical memory Data 3 Physical memory

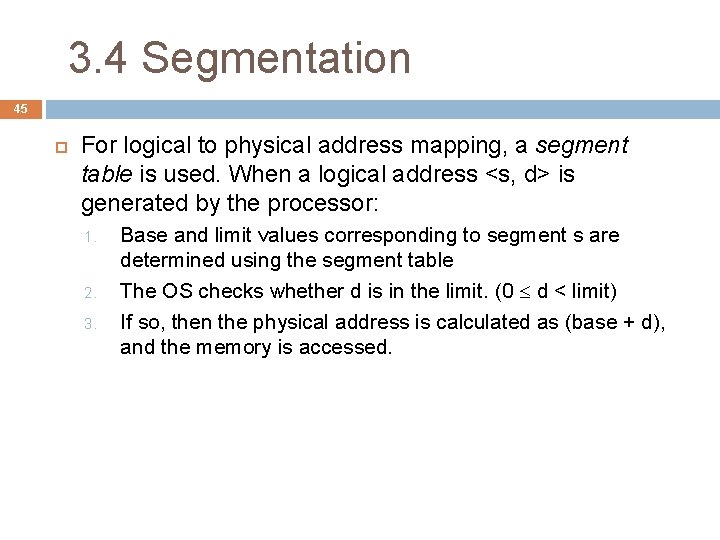

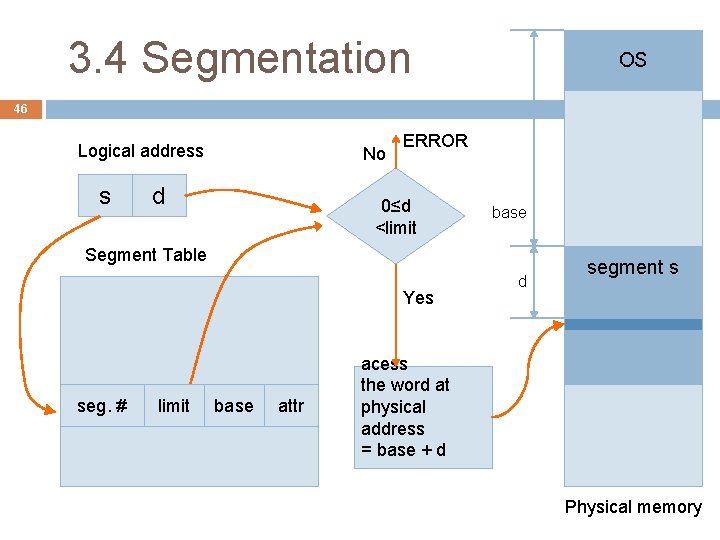

3. 4 Segmentation 45 For logical to physical address mapping, a segment table is used. When a logical address <s, d> is generated by the processor: 1. 2. 3. Base and limit values corresponding to segment s are determined using the segment table The OS checks whether d is in the limit. (0 d < limit) If so, then the physical address is calculated as (base + d), and the memory is accessed.

3. 4 Segmentation OS 46 Logical address s No d ERROR 0≤d <limit base Segment Table Yes seg. # limit base attr d segment s acess the word at physical address = base + d Physical memory

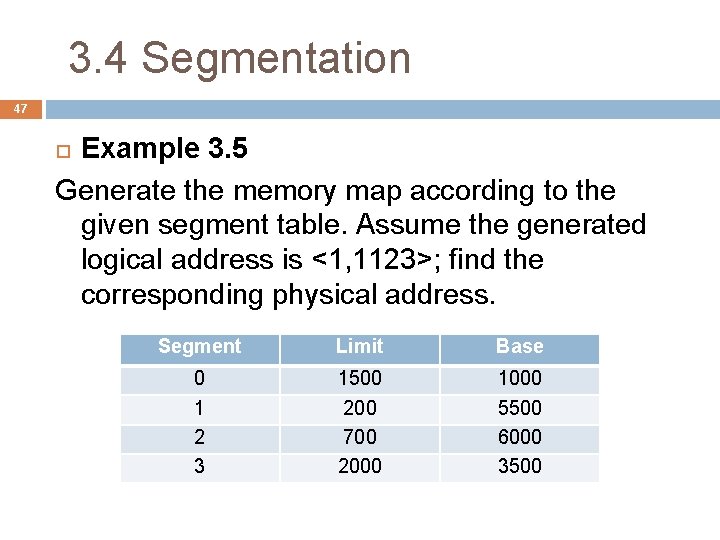

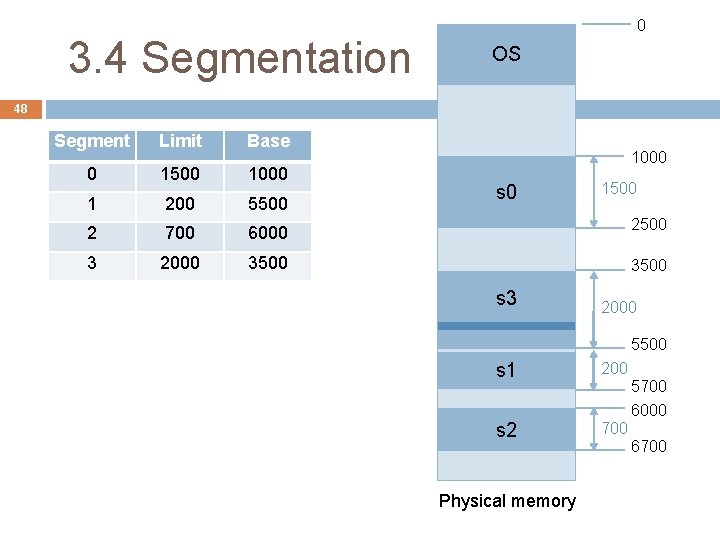

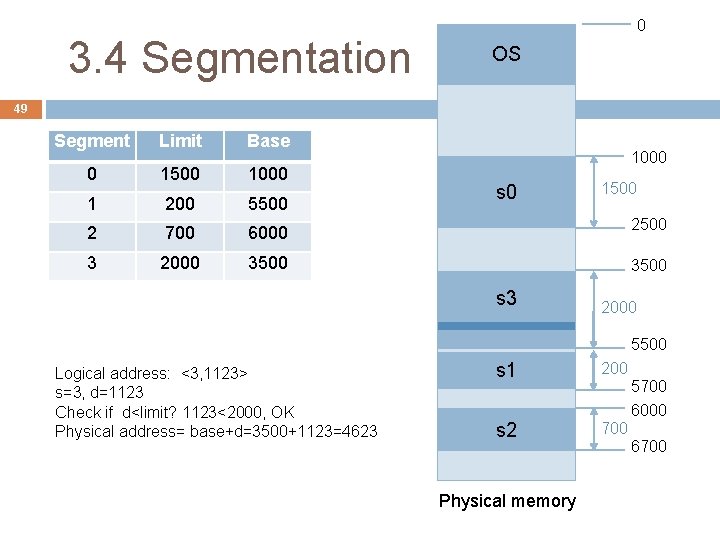

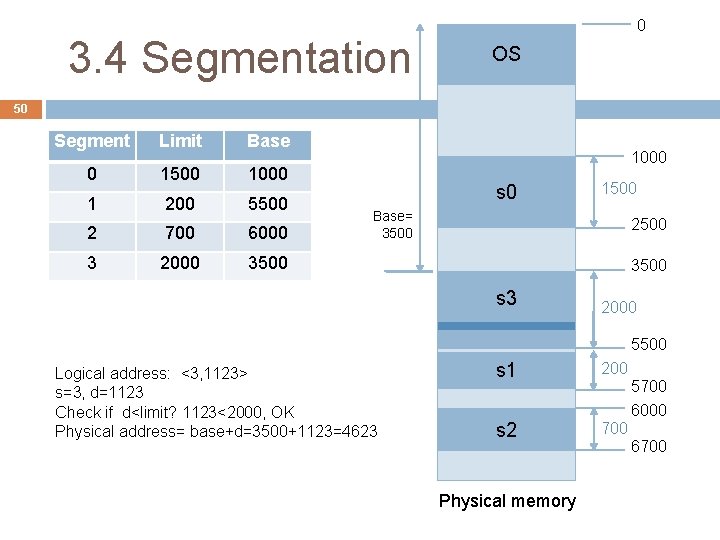

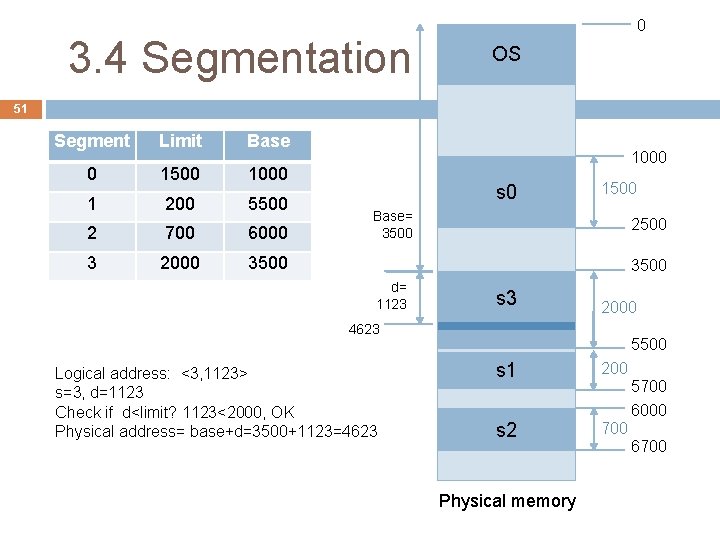

3. 4 Segmentation 47 Example 3. 5 Generate the memory map according to the given segment table. Assume the generated logical address is <1, 1123>; find the corresponding physical address. Segment Limit Base 0 1 2 3 1500 200 700 2000 1000 5500 6000 3500

3. 4 Segmentation 0 OS 48 Segment Limit Base 0 1500 1000 1 200 5500 2 700 6000 2500 3 2000 3500 1000 s 3 1500 2000 5500 s 1 200 s 2 700 Physical memory 5700 6000 6700

3. 4 Segmentation 0 OS 49 Segment Limit Base 0 1500 1000 1 200 5500 2 700 6000 2500 3 2000 3500 1000 s 3 1500 2000 5500 Logical address: <3, 1123> s=3, d=1123 Check if d<limit? 1123<2000, OK Physical address= base+d=3500+1123=4623 s 1 200 s 2 700 Physical memory 5700 6000 6700

3. 4 Segmentation 0 OS 50 Segment Limit Base 0 1500 1000 1 200 5500 2 700 6000 3 2000 3500 1000 s 0 1500 Base= 3500 2500 3500 s 3 2000 5500 Logical address: <3, 1123> s=3, d=1123 Check if d<limit? 1123<2000, OK Physical address= base+d=3500+1123=4623 s 1 200 s 2 700 Physical memory 5700 6000 6700

3. 4 Segmentation 0 OS 51 Segment Limit Base 0 1500 1000 1 200 5500 2 700 6000 3 2000 3500 1000 s 0 1500 Base= 3500 2500 3500 d= 1123 s 3 2000 4623 Logical address: <3, 1123> s=3, d=1123 Check if d<limit? 1123<2000, OK Physical address= base+d=3500+1123=4623 5500 s 1 200 s 2 700 Physical memory 5700 6000 6700

3. 4 Segmentation 52 Segment tables may be implemented in the main memory or in associative registers, in the same way it is done for page tables. Also sharing of segments is applicable as in paging. Shared segments should be read only and should be assigned the same segment number.

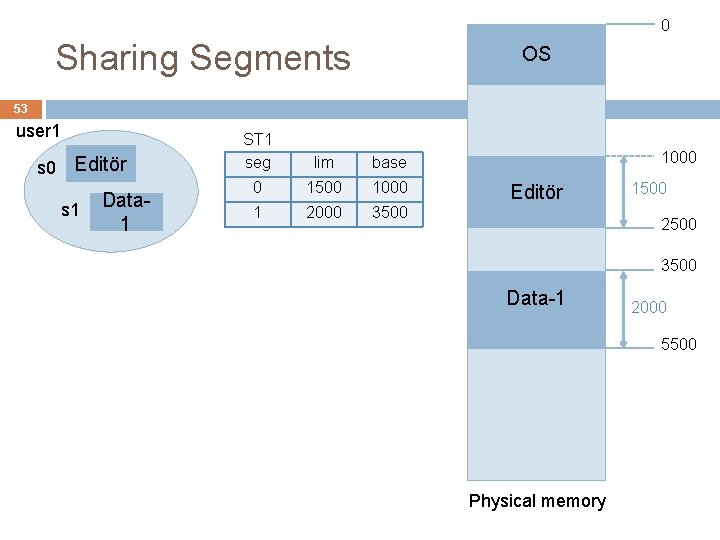

0 Sharing Segments OS 53 user 1 s 0 Editör s 1 Data 1 ST 1 seg lim base 0 1500 1000 1 2000 3500 1000 Editör 1500 2500 3500 Data-1 2000 5500 Physical memory

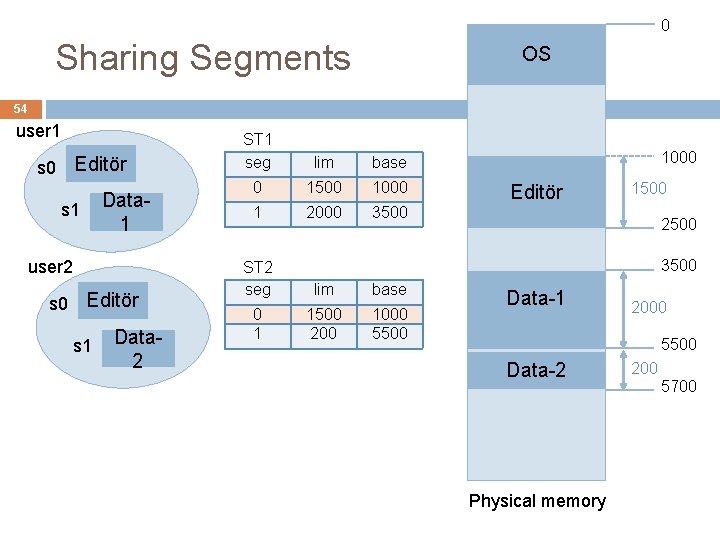

0 Sharing Segments OS 54 user 1 Editör s 0 s 1 Data 1 user 2 s 0 Editör s 1 Data 2 ST 1 seg lim base 0 1500 1000 1 2000 3500 1000 Editör 1500 2500 3500 ST 2 seg lim base 0 1 1500 200 1000 5500 Data-1 2000 5500 Data-2 Physical memory 200 5700

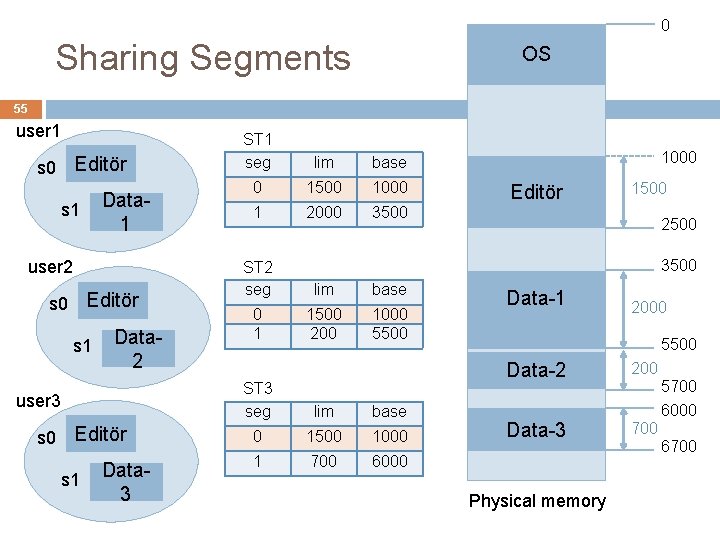

0 Sharing Segments OS 55 user 1 Editör s 0 s 1 Data 1 user 2 s 0 Editör s 1 Data 2 user 3 s 0 Editör s 1 Data 3 ST 1 seg lim base 0 1500 1000 1 2000 3500 1000 Editör 1500 2500 3500 ST 2 seg lim base 0 1 1500 200 1000 5500 ST 3 seg lim base 0 1500 1000 1 700 6000 Data-1 2000 5500 Data-2 200 Data-3 700 Physical memory 5700 6000 6700

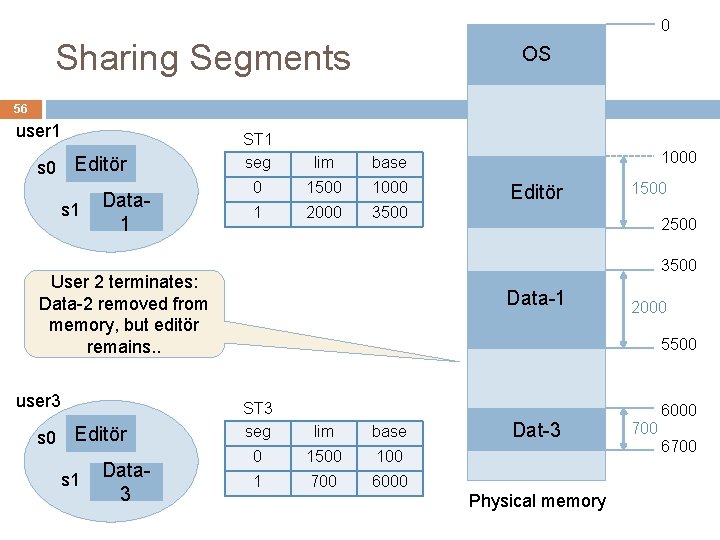

0 Sharing Segments OS 56 user 1 Editör s 0 s 1 Data 1 ST 1 seg lim base 0 1500 1000 1 2000 3500 s 0 Editör s 1 Data 3 Editör 1500 2500 3500 User 2 terminates: Data-2 removed from memory, but editör remains. . user 3 1000 Data-1 2000 5500 ST 3 seg lim base 0 1500 1 700 6000 Dat-3 Physical memory 6000 700 6700

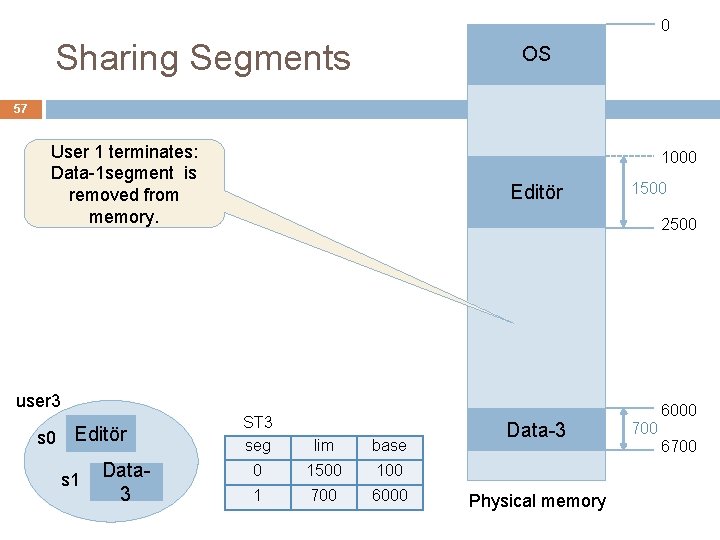

0 Sharing Segments OS 57 User 1 terminates: Data-1 segment is removed from memory. 1000 Editör 1500 2500 user 3 s 0 Editör s 1 Data 3 ST 3 seg lim base 0 1500 1 700 6000 Data-3 Physical memory 6000 700 6700

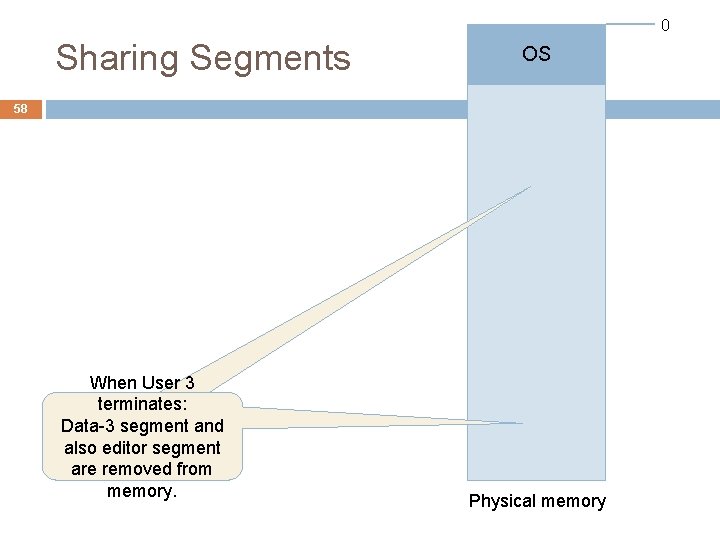

0 Sharing Segments OS 58 When User 3 terminates: Data-1 Data-3 and segment also editor and alsosegments editor segment are removed from memory. Physical memory

- Slides: 59