Chapter 3 Data Representation Http sslab cnu ac

Chapter 3 Data Representation 충남대학교 컴퓨터전공 Http: //sslab. cnu. ac. kr 이철훈 1

Chapter 3 Data Types n Number Systems - Decimal number system (radix 10) (724. 5)10 = 7× 102 + 2× 101 + 4× 100 + 5× 10 -1 - Binary number system (radix 2) (101101)2 = 1× 25 + 0× 24 + 1 × 23 + 1 × 22 + 0 × 21 + 1× 20 = (45)10 - Octal number system (radix 8) (736. 4)8 = 7× 82+ 3× 81 + 6× 80 + 4× 8 -1 = 7× 64 + 3× 8 + 6× 1 + 4/8 = (478. 5)10 - Hexadecimal system (radix 16) (F 3)16 = F × 16 + 3 = 15 × 16 + 3 = (243)10 Computer System Architecture 1 2

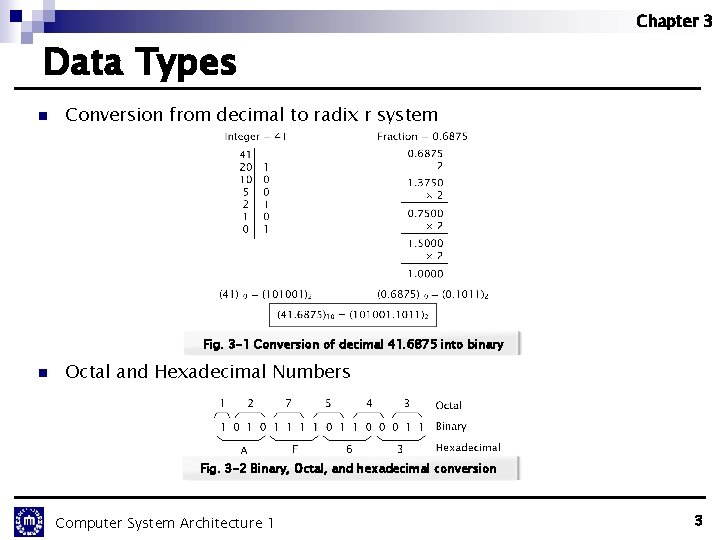

Chapter 3 Data Types n Conversion from decimal to radix r system Fig. 3 -1 Conversion of decimal 41. 6875 into binary n Octal and Hexadecimal Numbers Fig. 3 -2 Binary, Octal, and hexadecimal conversion Computer System Architecture 1 3

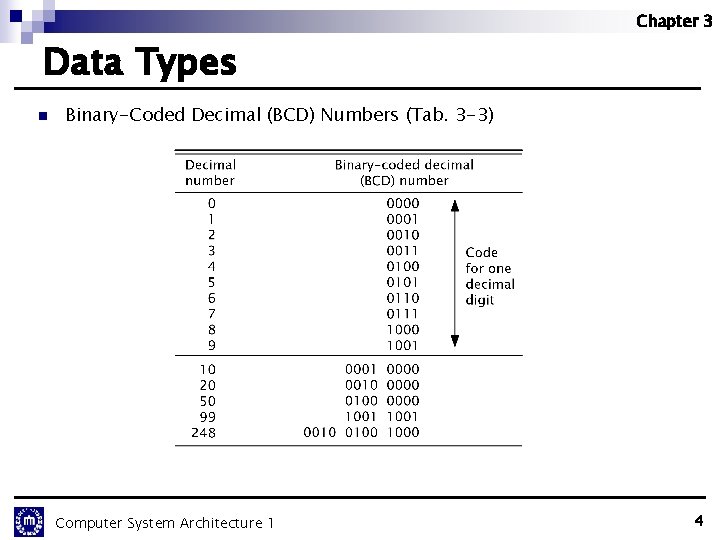

Chapter 3 Data Types n Binary-Coded Decimal (BCD) Numbers (Tab. 3 -3) Computer System Architecture 1 4

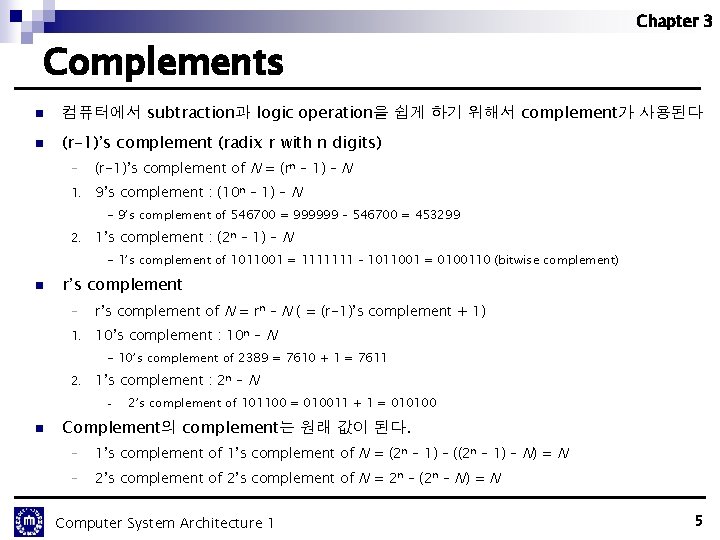

Chapter 3 Complements n 컴퓨터에서 subtraction과 logic operation을 쉽게 하기 위해서 complement가 사용된다 n (r-1)’s complement (radix r with n digits) - (r-1)’s complement of N = (rn – 1) – N 1. 9’s complement : (10 n – 1) – N - 9’s complement of 546700 = 999999 – 546700 = 453299 2. 1’s complement : (2 n – 1) – N - 1’s complement of 1011001 = 1111111 – 1011001 = 0100110 (bitwise complement) n r’s complement - r’s complement of N = rn – N ( = (r-1)’s complement + 1) 1. 10’s complement : 10 n – N - 10’s complement of 2389 = 7610 + 1 = 7611 2. 1’s complement : 2 n – N - n 2’s complement of 101100 = 010011 + 1 = 010100 Complement의 complement는 원래 값이 된다. - 1’s complement of N = (2 n – 1) – ((2 n – 1) – N) = N - 2’s complement of N = 2 n – (2 n – N) = N Computer System Architecture 1 5

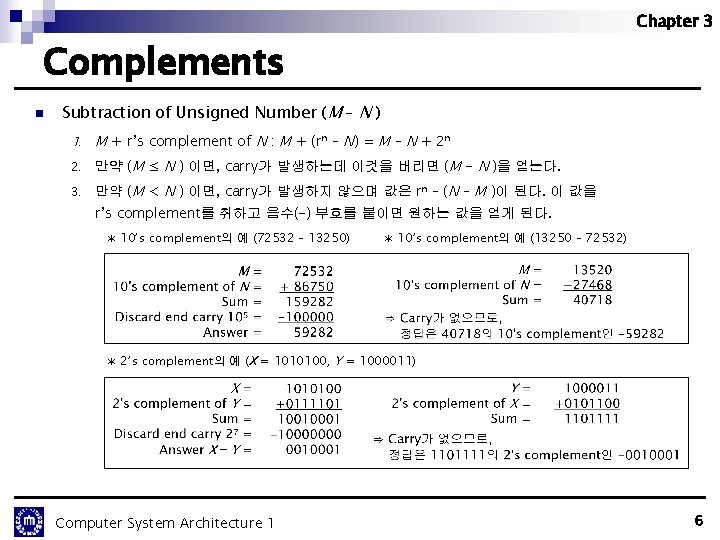

Chapter 3 Complements n Subtraction of Unsigned Number (M – N ) 1. M + r’s complement of N : M + (rn – N) = M – N + 2 n 2. 만약 (M ≤ N ) 이면, carry가 발생하는데 이것을 버리면 (M - N )을 얻는다. 3. 만약 (M < N ) 이면, carry가 발생하지 않으며 값은 rn – (N – M )이 된다. 이 값을 r’s complement를 취하고 음수(-) 부호를 붙이면 원하는 값을 얻게 된다. ∗ 10’s complement의 예 (72532 – 13250) ∗ 10’s complement의 예 (13250 – 72532) ∗ 2’s complement의 예 (X = 1010100, Y = 1000011) Computer System Architecture 1 6

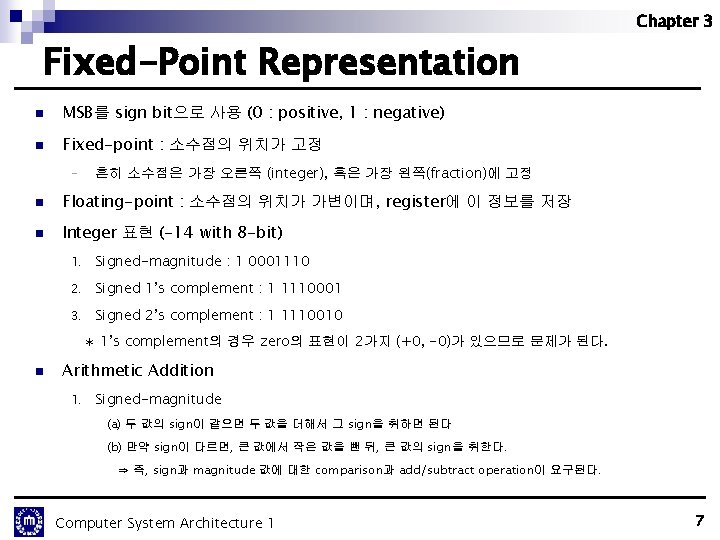

Chapter 3 Fixed-Point Representation n MSB를 sign bit으로 사용 (0 : positive, 1 : negative) n Fixed-point : 소수점의 위치가 고정 - 흔히 소수점은 가장 오른쪽 (integer), 혹은 가장 왼쪽(fraction)에 고정 n Floating-point : 소수점의 위치가 가변이며, register에 이 정보를 저장 n Integer 표현 (-14 with 8 -bit) 1. Signed-magnitude : 1 0001110 2. Signed 1’s complement : 1 1110001 3. Signed 2’s complement : 1 1110010 ∗ 1’s complement의 경우 zero의 표현이 2가지 (+0, -0)가 있으므로 문제가 된다. n Arithmetic Addition 1. Signed-magnitude (a) 두 값의 sign이 같으면 두 값을 더해서 그 sign을 취하면 된다 (b) 만약 sign이 다르면, 큰 값에서 작은 값을 뺀 뒤, 큰 값의 sign을 취한다. ⇒ 즉, sign과 magnitude 값에 대한 comparison과 add/subtract operation이 요구된다. Computer System Architecture 1 7

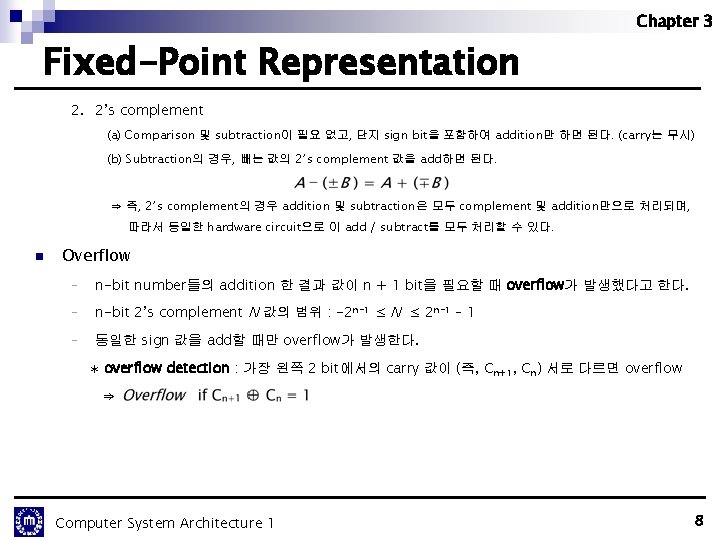

Chapter 3 Fixed-Point Representation 2. 2’s complement (a) Comparison 및 subtraction이 필요 없고, 단지 sign bit을 포함하여 addition만 하면 된다. (carry는 무시) (b) Subtraction의 경우, 빼는 값의 2’s complement 값을 add하면 된다. ⇒ 즉, 2’s complement의 경우 addition 및 subtraction은 모두 complement 및 addition만으로 처리되며, 따라서 동일한 hardware circuit으로 이 add / subtract를 모두 처리할 수 있다. n Overflow - n-bit number들의 addition 한 결과 값이 n + 1 bit을 필요할 때 overflow가 발생했다고 한다. - n-bit 2’s complement N 값의 범위 : -2 n-1 ≤ N ≤ 2 n-1 – 1 - 동일한 sign 값을 add할 때만 overflow가 발생한다. ∗ overflow detection : 가장 왼쪽 2 bit에서의 carry 값이 (즉, Cn+1, Cn) 서로 다르면 overflow ⇒ Computer System Architecture 1 8

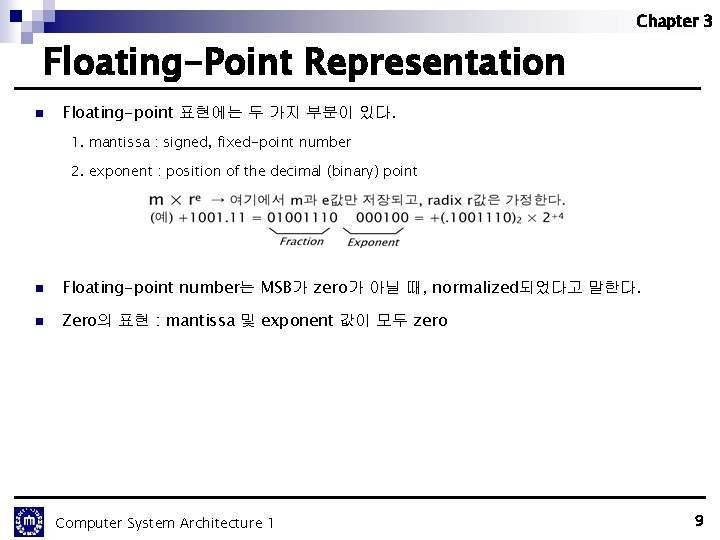

Chapter 3 Floating-Point Representation n Floating-point 표현에는 두 가지 부분이 있다. 1. mantissa : signed, fixed-point number 2. exponent : position of the decimal (binary) point n Floating-point number는 MSB가 zero가 아닐 때, normalized되었다고 말한다. n Zero의 표현 : mantissa 및 exponent 값이 모두 zero Computer System Architecture 1 9

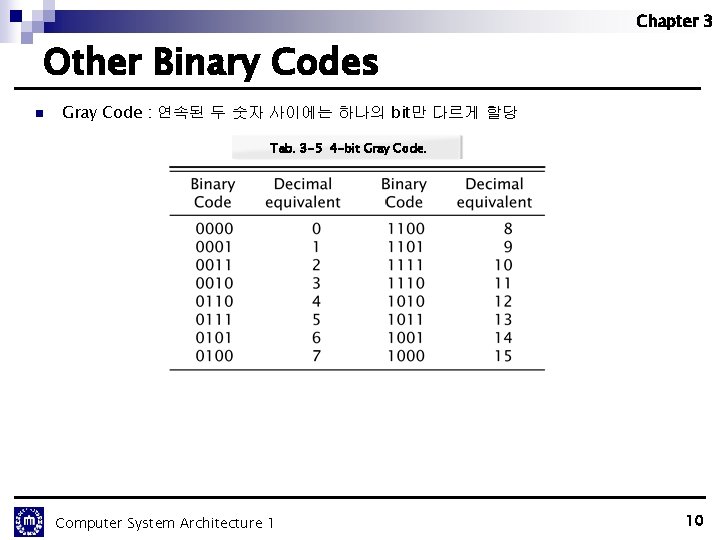

Chapter 3 Other Binary Codes n Gray Code : 연속된 두 숫자 사이에는 하나의 bit만 다르게 할당 Tab. 3 -5 4 -bit Gray Code. Computer System Architecture 1 10

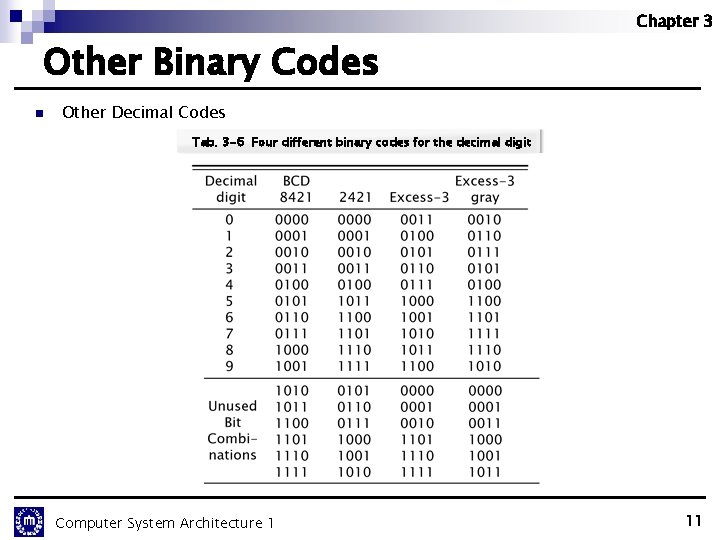

Chapter 3 Other Binary Codes n Other Decimal Codes Tab. 3 -6 Four different binary codes for the decimal digit Computer System Architecture 1 11

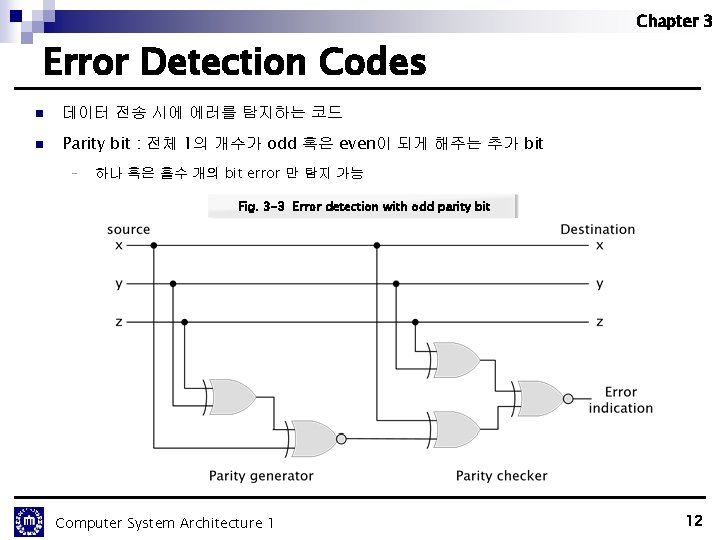

Chapter 3 Error Detection Codes n 데이터 전송 시에 에러를 탐지하는 코드 n Parity bit : 전체 1의 개수가 odd 혹은 even이 되게 해주는 추가 bit - 하나 혹은 홀수 개의 bit error 만 탐지 가능 Fig. 3 -3 Error detection with odd parity bit Computer System Architecture 1 12

- Slides: 12