Chapter 3 Boolean Algebra and Digital Logic 3

Chapter 3 Boolean Algebra and Digital Logic

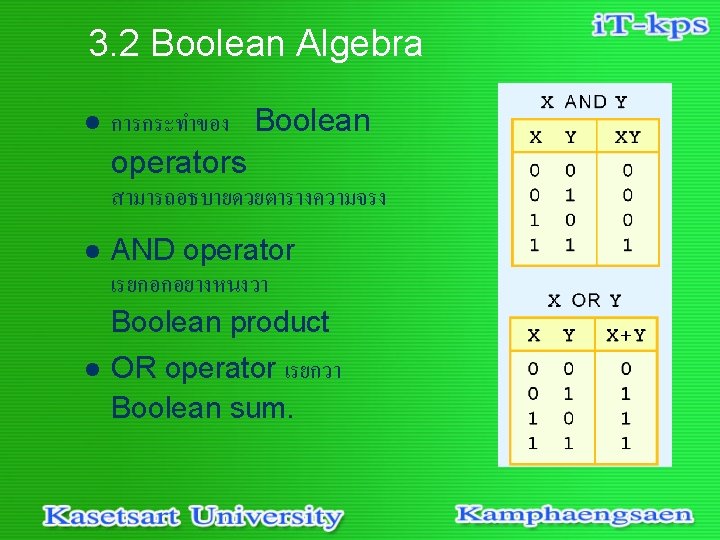

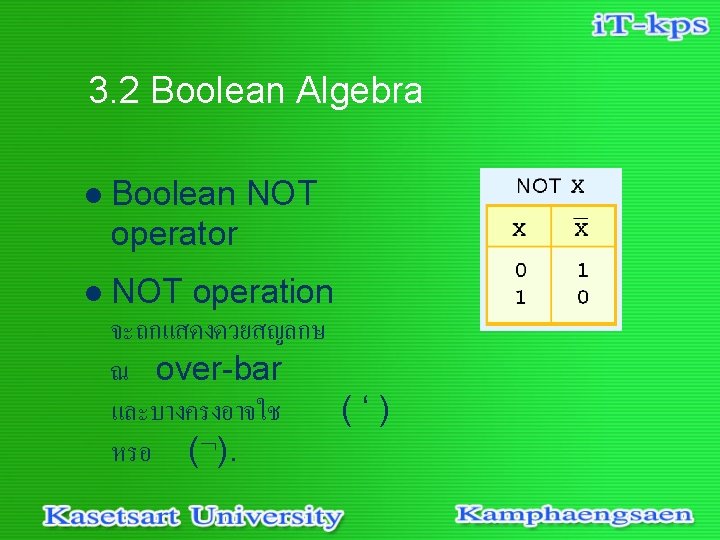

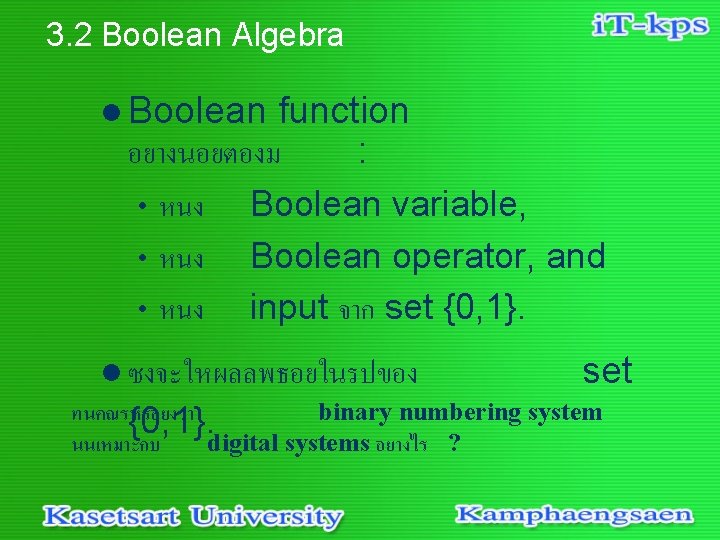

3. 2 Boolean Algebra l Boolean function อยางนอยตองม : หนง • Boolean variable, Boolean operator, and input จาก set {0, 1}. l ซงจะใหผลลพธอยในรปของ set ทนคณรหรอยงวา binary numbering system {0, 1}. นนเหมาะกบ digital systems อยางไร ?

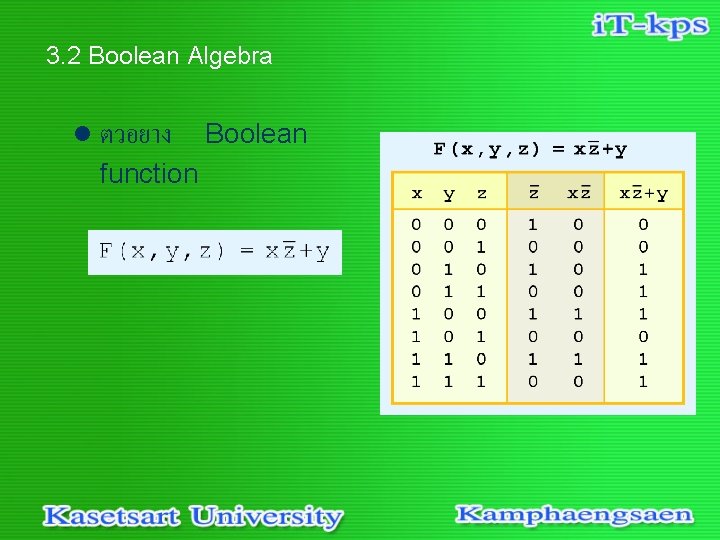

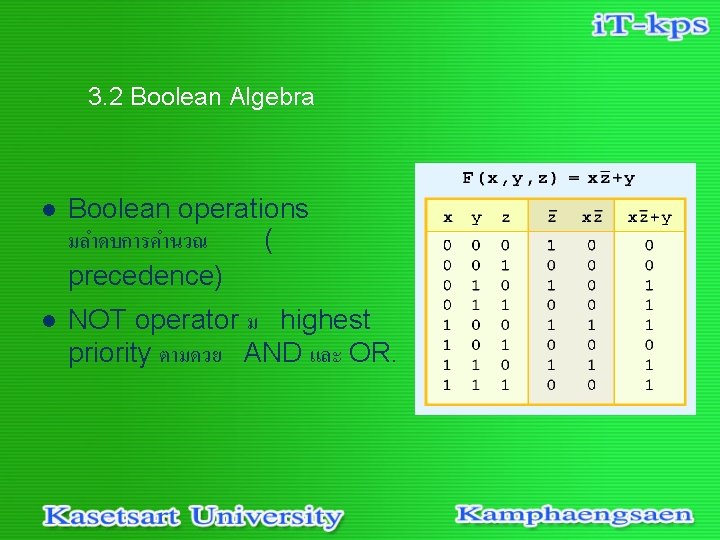

3. 2 Boolean Algebra l ตวอยาง function Boolean

3. 2 Boolean Algebra l Boolean operations มลำดบการคำนวณ ( precedence) l NOT operator ม highest priority ตามดวย AND และ OR.

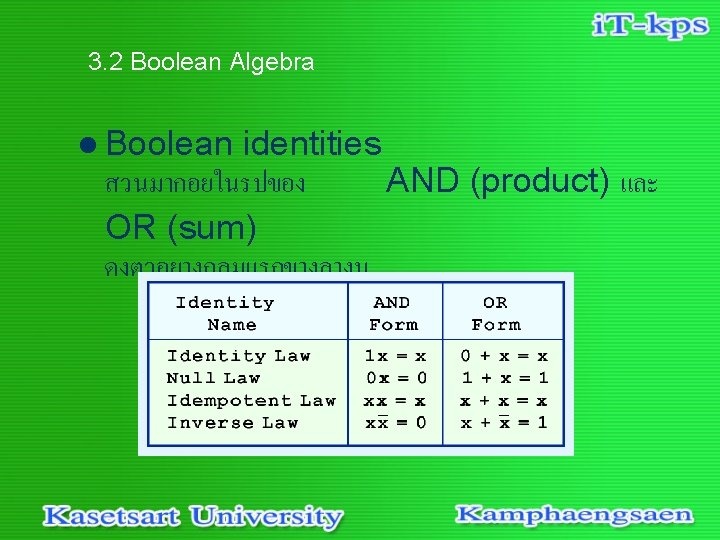

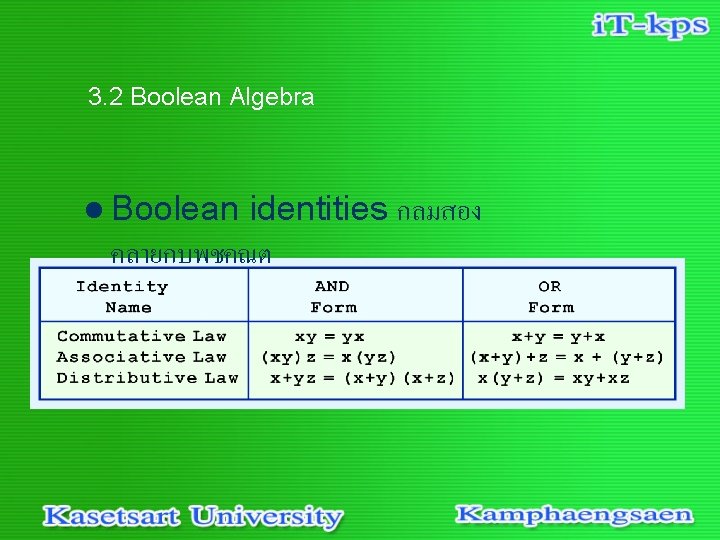

3. 2 Boolean Algebra identities กลมสอง คลายกบพชคณต l Boolean

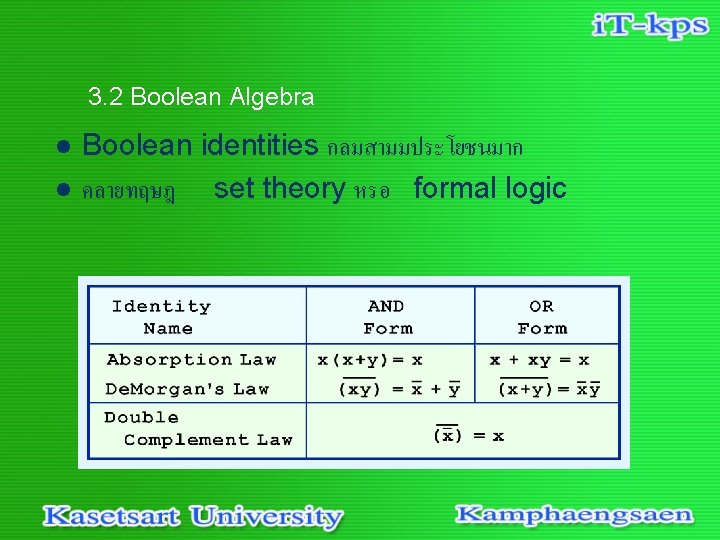

3. 2 Boolean Algebra l l Boolean identities กลมสามมประโยชนมาก คลายทฤษฎ set theory หรอ formal logic

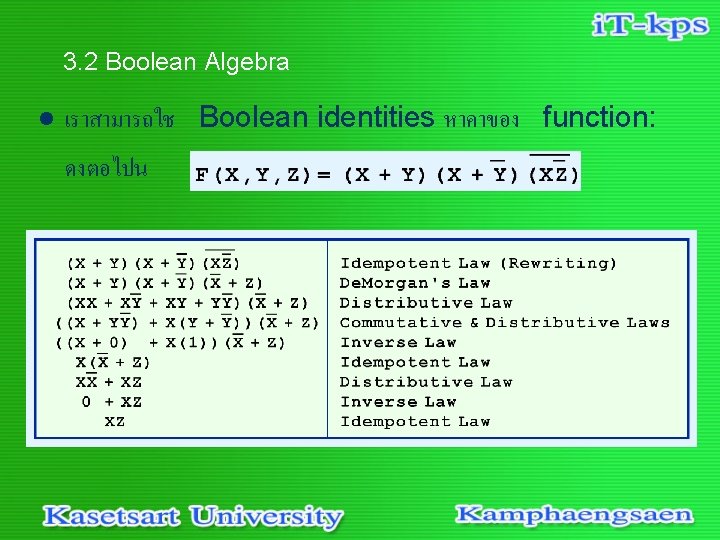

3. 2 Boolean Algebra l เราสามารถใช Boolean identities หาคาของ function: ดงตอไปน :

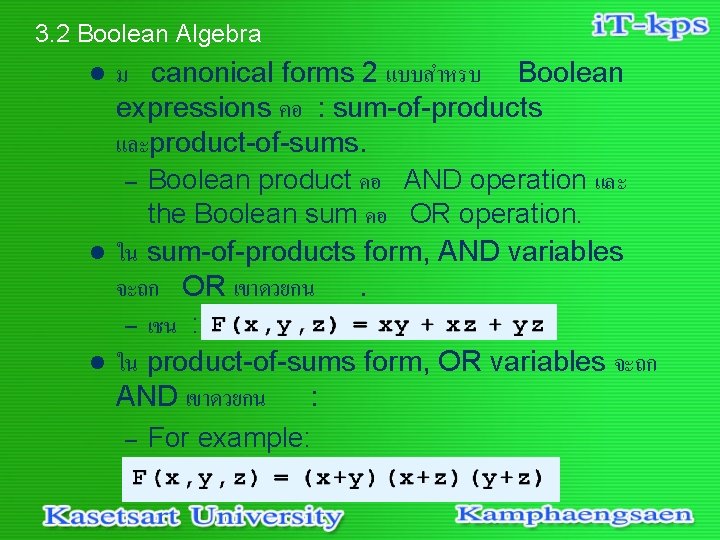

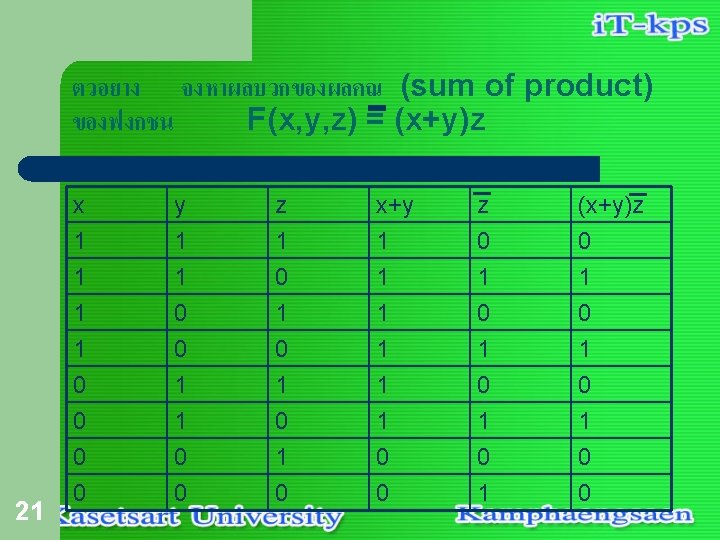

3. 2 Boolean Algebra l l l ม canonical forms 2 แบบสำหรบ Boolean expressions คอ : sum-of-products และproduct-of-sums. – Boolean product คอ AND operation และ the Boolean sum คอ OR operation. ใน sum-of-products form, AND variables จะถก OR เขาดวยกน. – เชน : ใน product-of-sums form, OR variables จะถก AND เขาดวยกน : – For example:

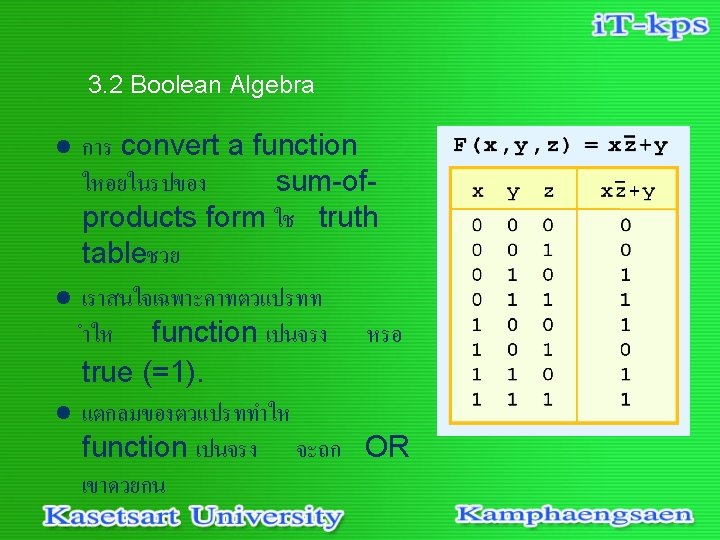

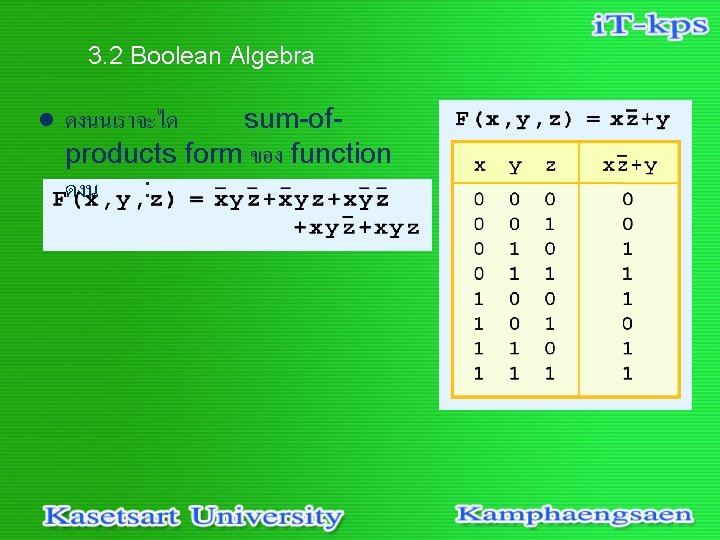

3. 2 Boolean Algebra l ดงนนเราจะได sum-ofproducts form ของ function ดงน :

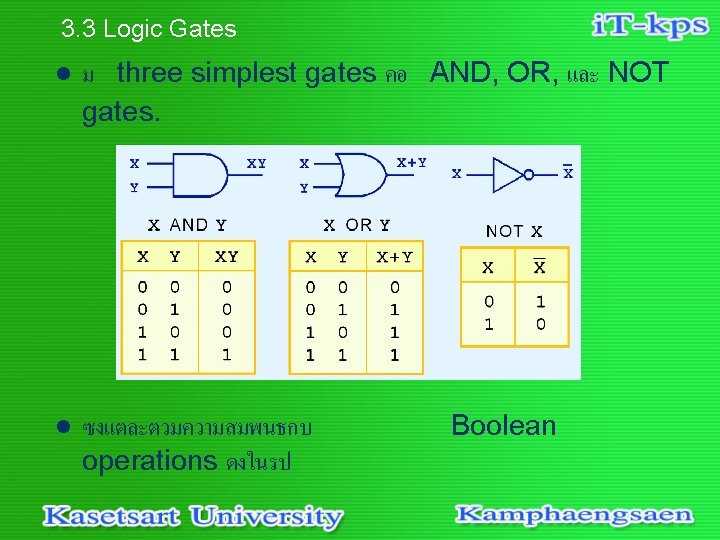

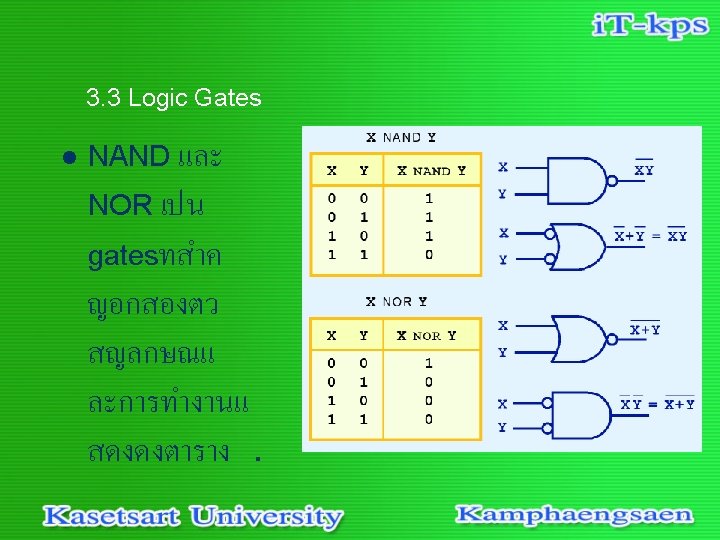

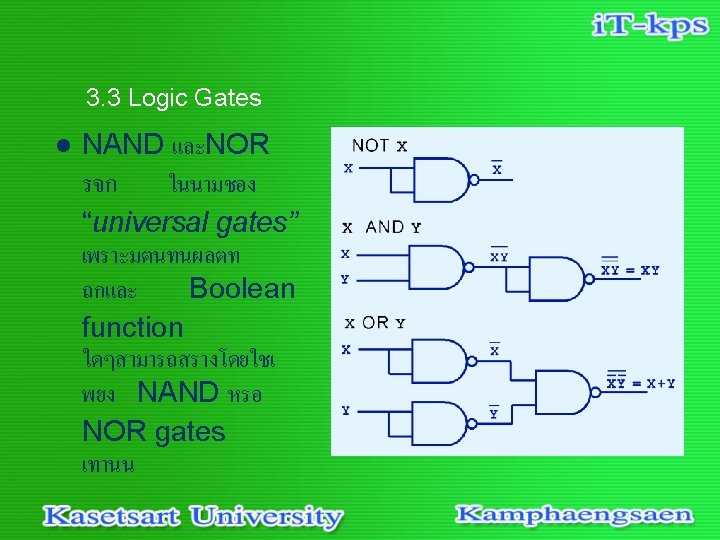

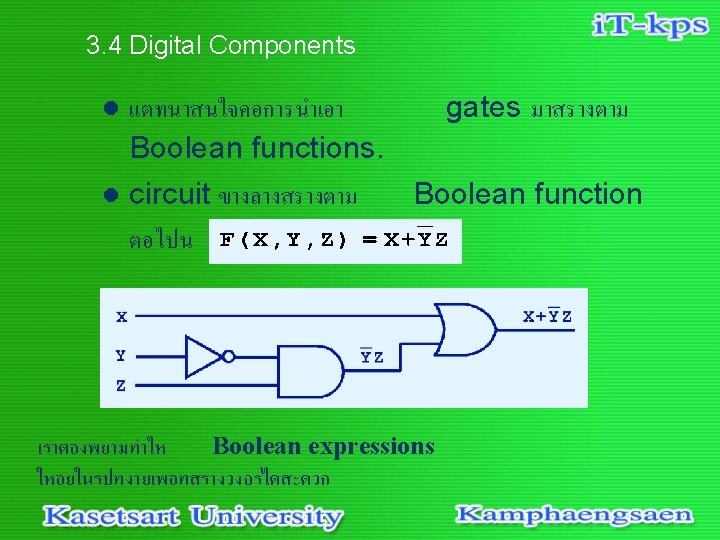

3. 3 Logic Gates l ม three simplest gates คอ AND, OR, และ NOT gates. l ซงแตละตวมความสมพนธกบ operations ดงในรป Boolean

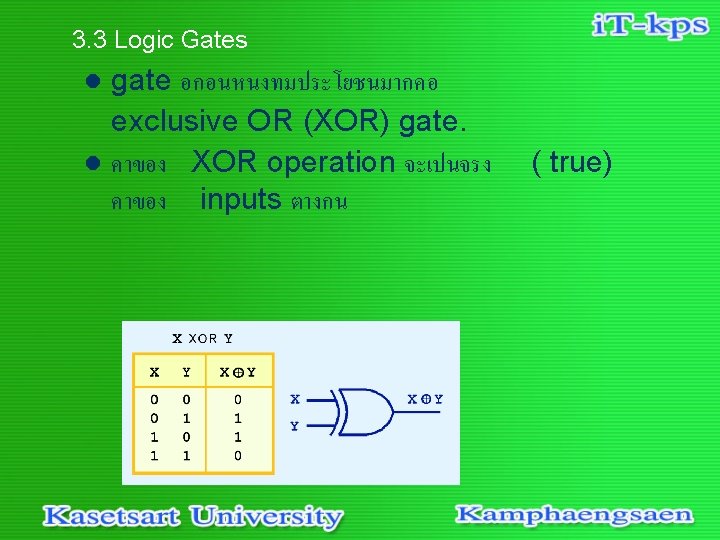

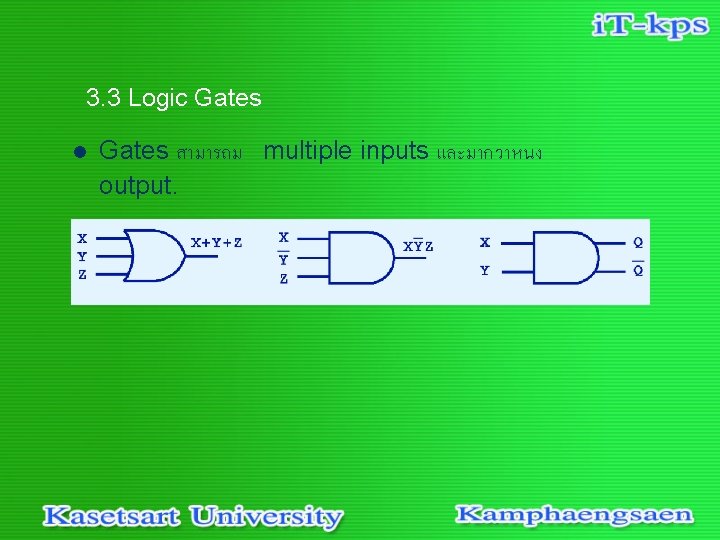

3. 3 Logic Gates l Gates สามารถม multiple inputs และมากวาหนง output.

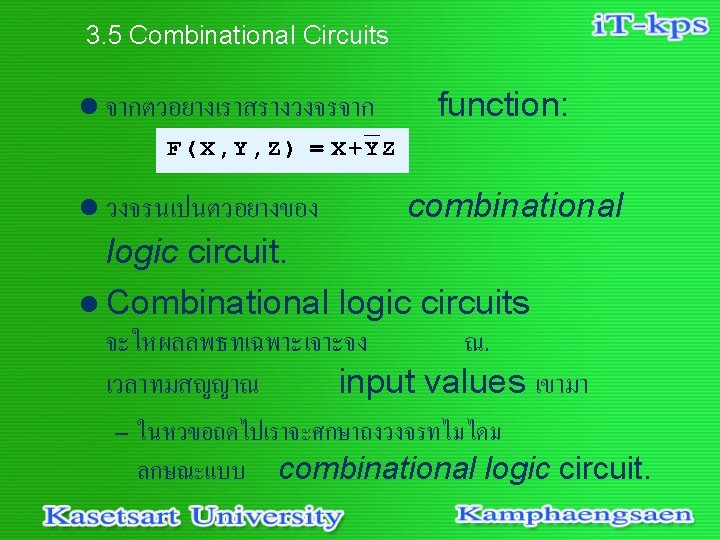

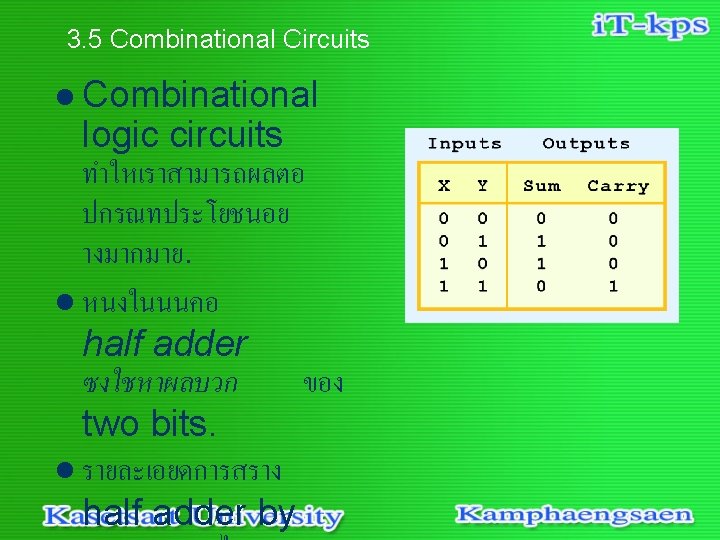

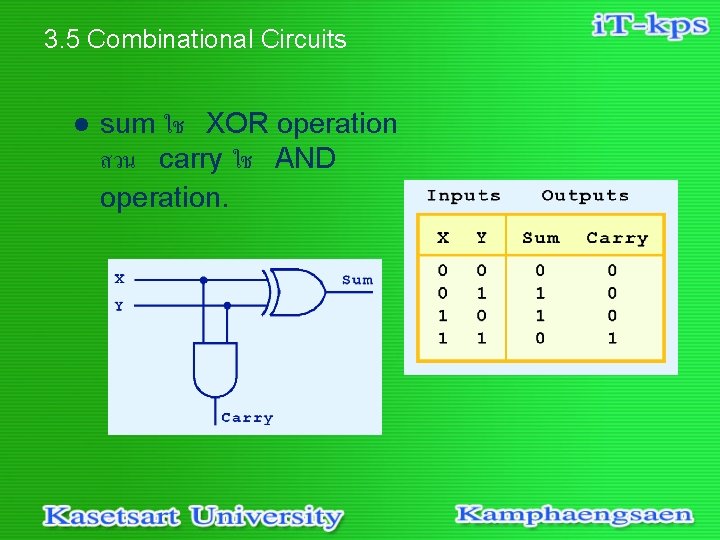

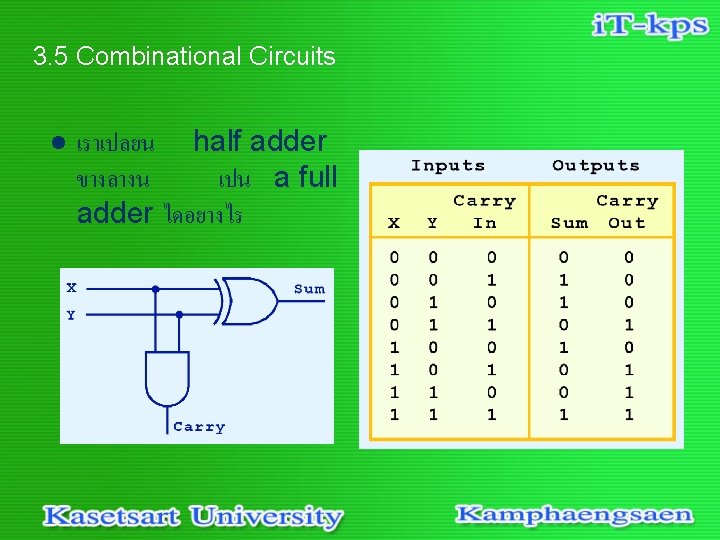

3. 5 Combinational Circuits l sum ใช XOR operation สวน carry ใช AND operation.

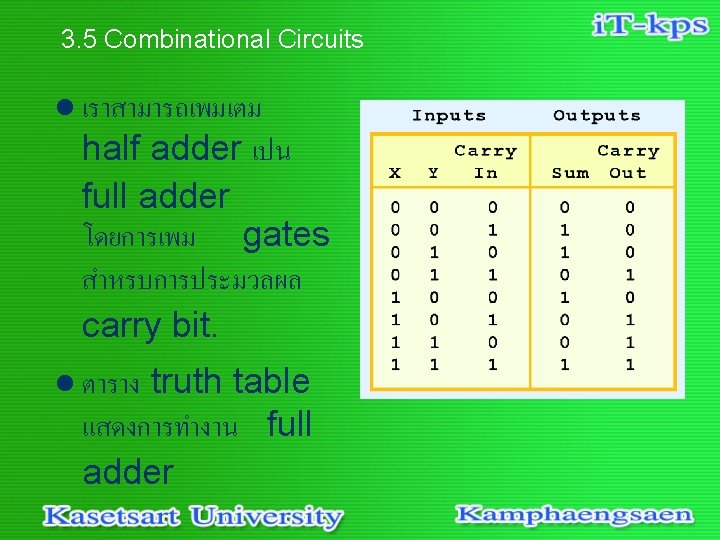

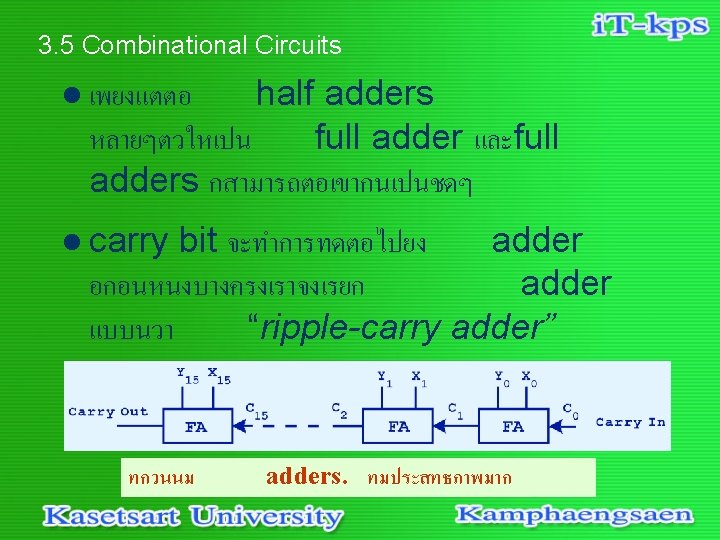

3. 5 Combinational Circuits l เราเปลยน half adder ขางลางน เปน a full adder ไดอยางไร

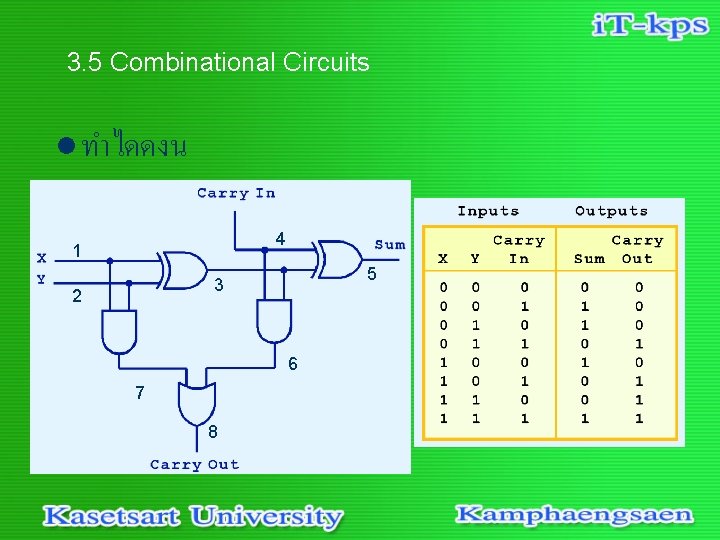

3. 5 Combinational Circuits l ทำไดดงน 4 1 5 3 2 6 7 8

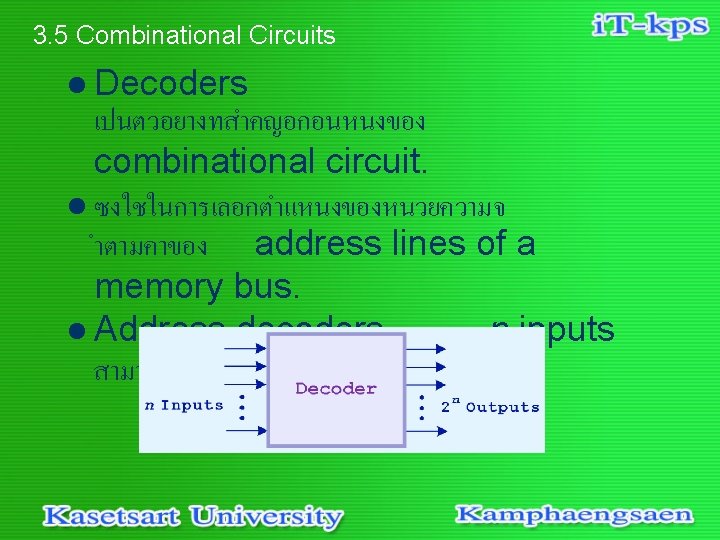

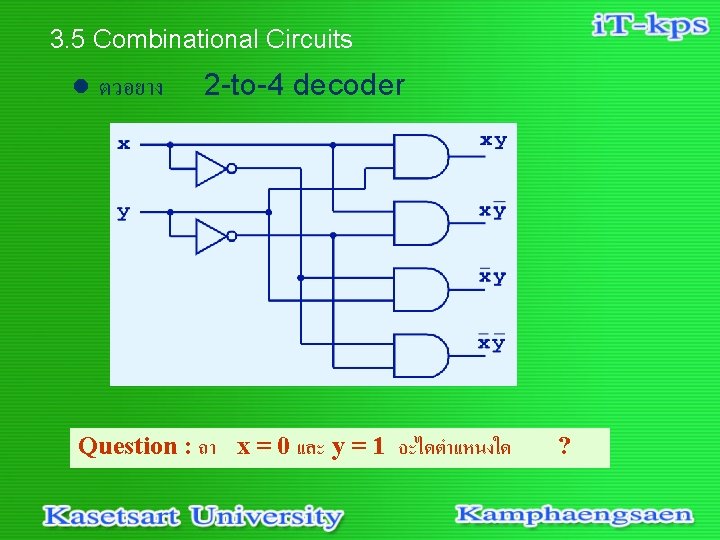

3. 5 Combinational Circuits l ตวอยาง 2 -to-4 decoder Question : ถา x = 0 และ y = 1 จะไดตำแหนงใด ?

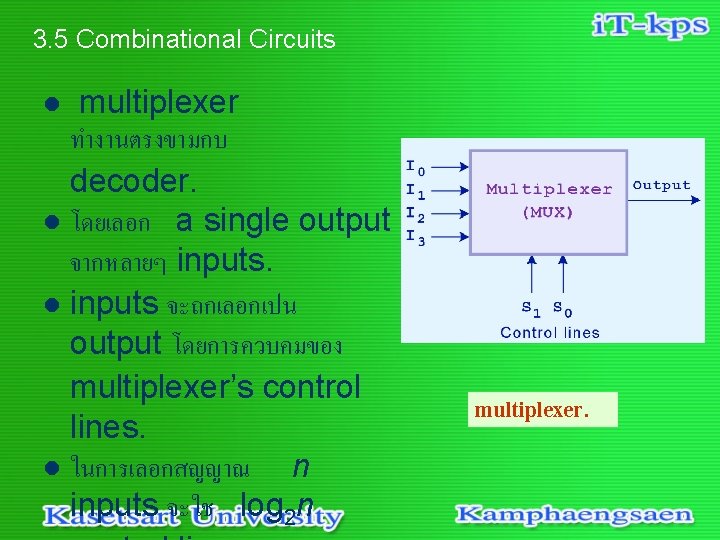

3. 5 Combinational Circuits multiplexer ทำงานตรงขามกบ decoder. l โดยเลอก a single output จากหลายๆ inputs. l inputs จะถกเลอกเปน output โดยการควบคมของ multiplexer’s control lines. l ในการเลอกสญญาณ n inputs จะใช log 2 n l multiplexer.

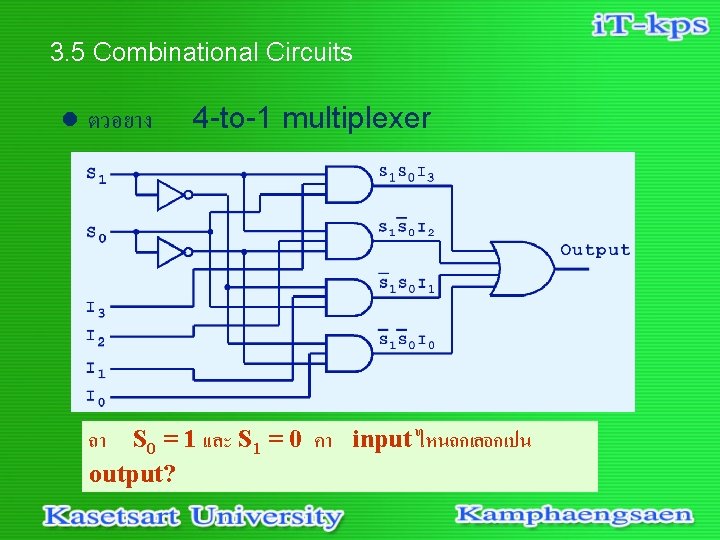

3. 5 Combinational Circuits l ตวอยาง 4 -to-1 multiplexer ถา S 0 = 1 และ S 1 = 0 คา input ไหนถกเลอกเปน output?

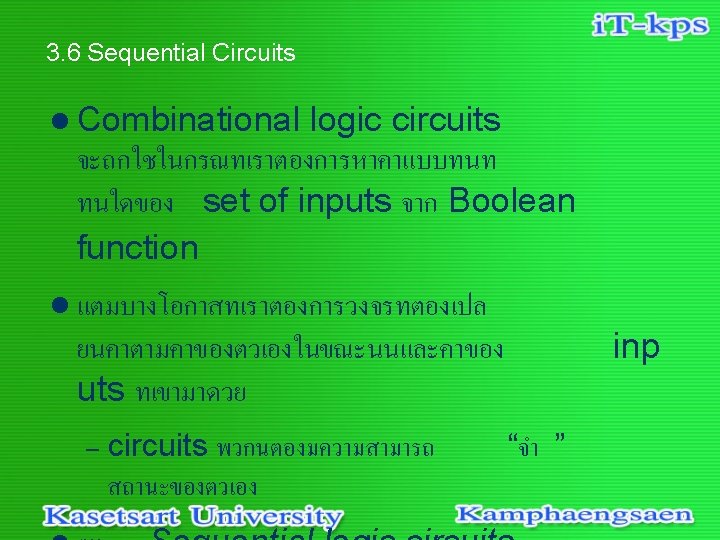

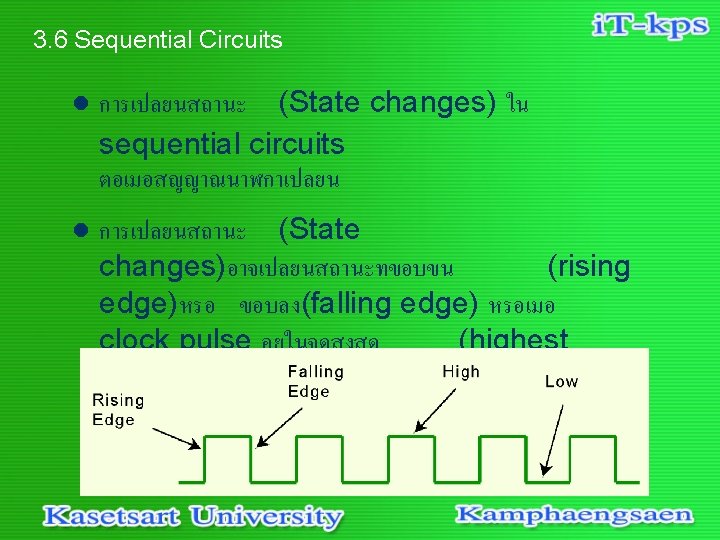

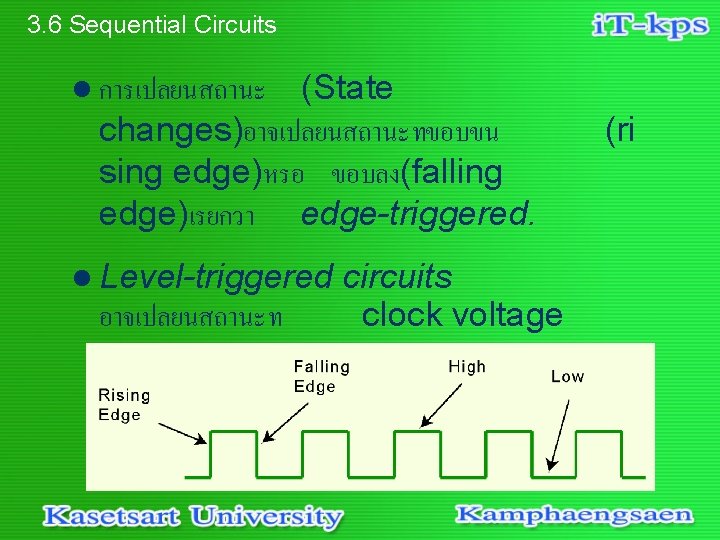

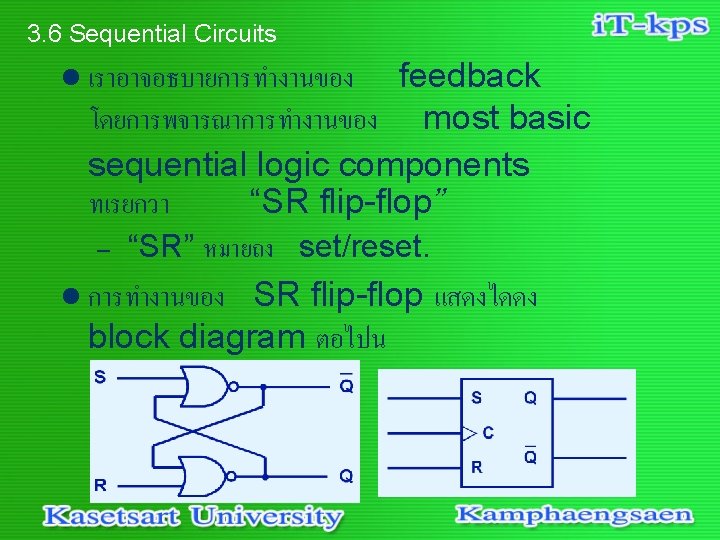

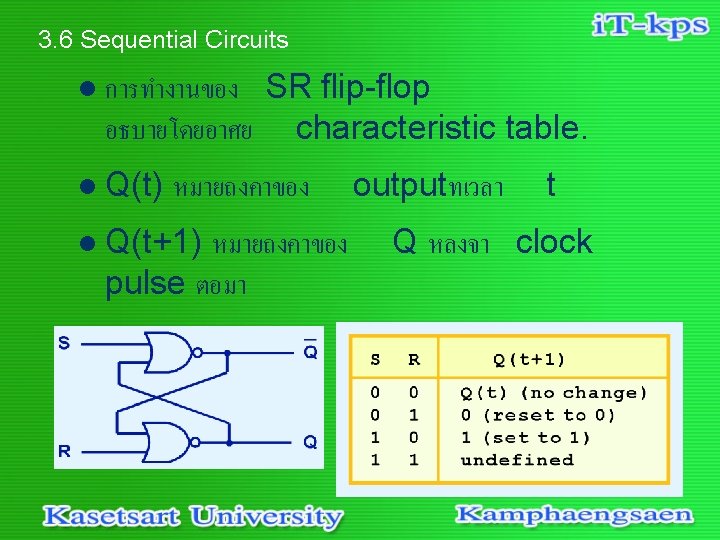

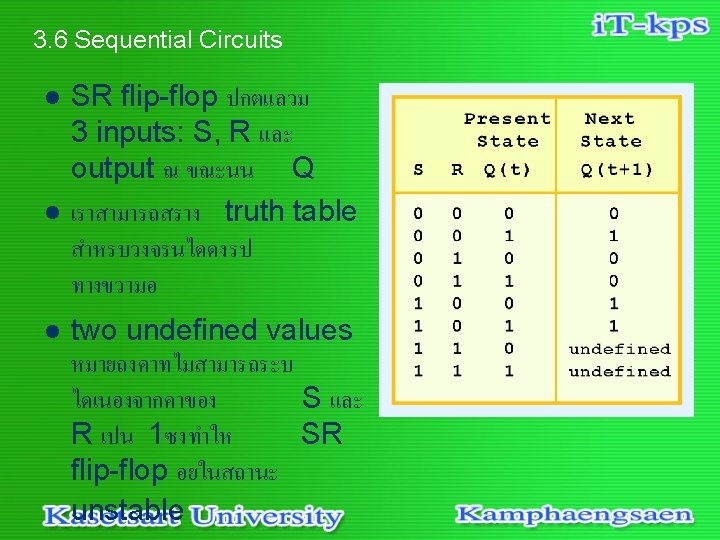

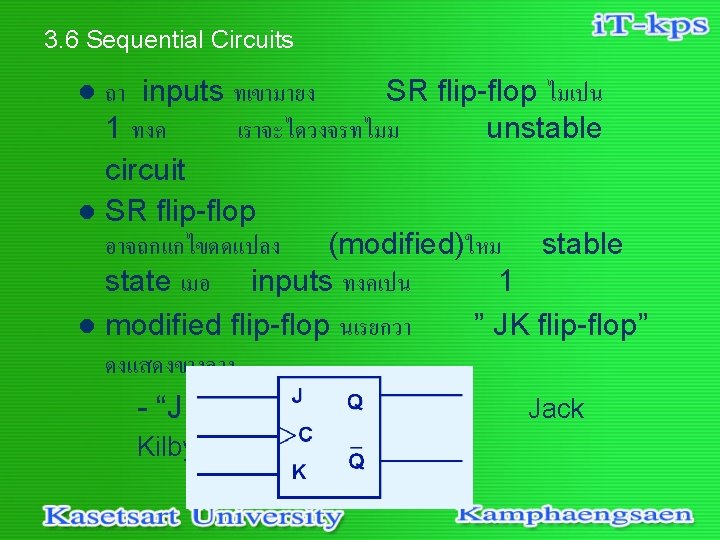

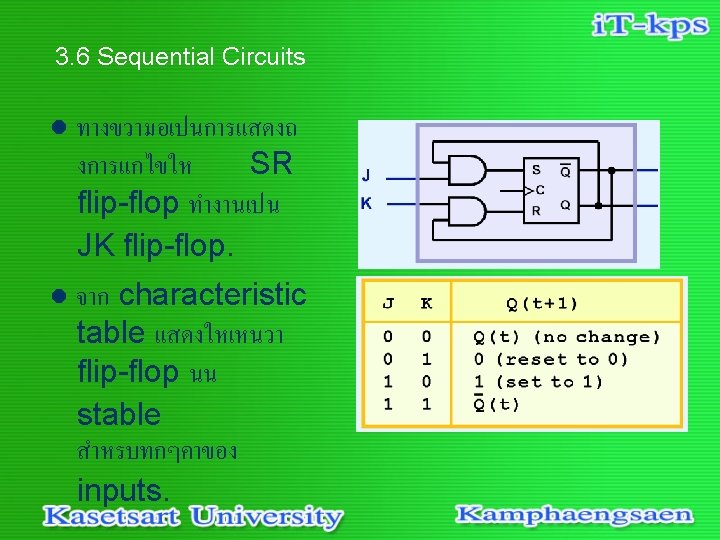

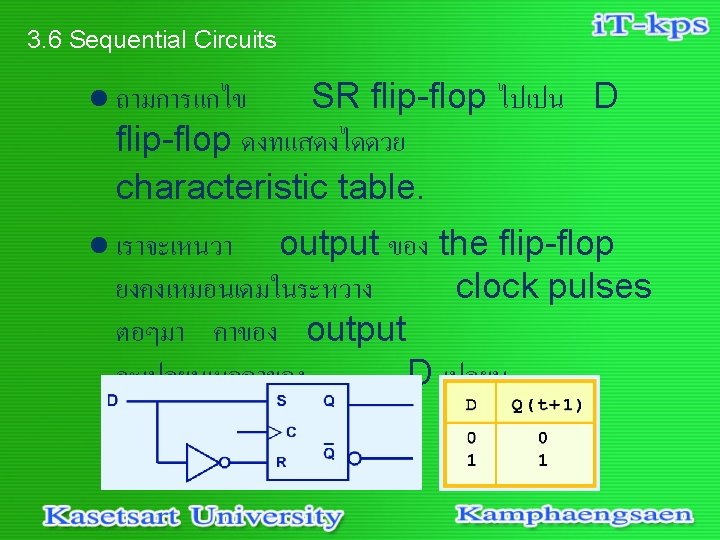

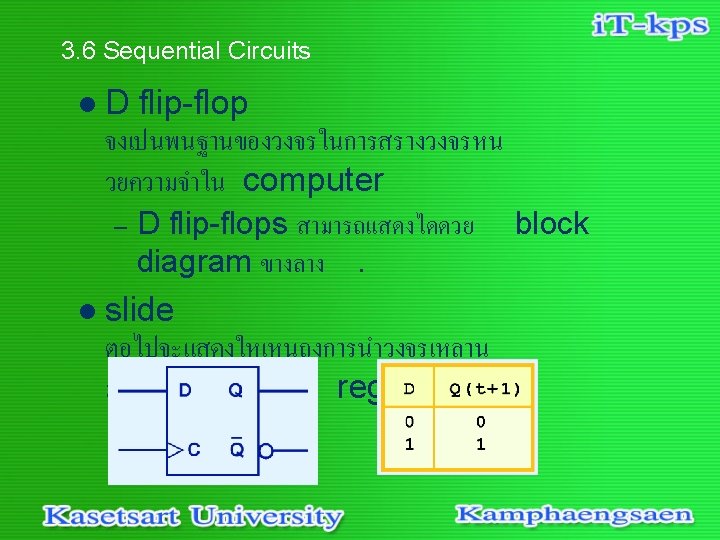

3. 6 Sequential Circuits l การเปลยนสถานะ (State changes)อาจเปลยนสถานะทขอบขน sing edge)หรอ ขอบลง(falling edge)เรยกวา edge-triggered. l Level-triggered circuits อาจเปลยนสถานะท clock voltage ถงจด highest หรอ lowest level. (ri

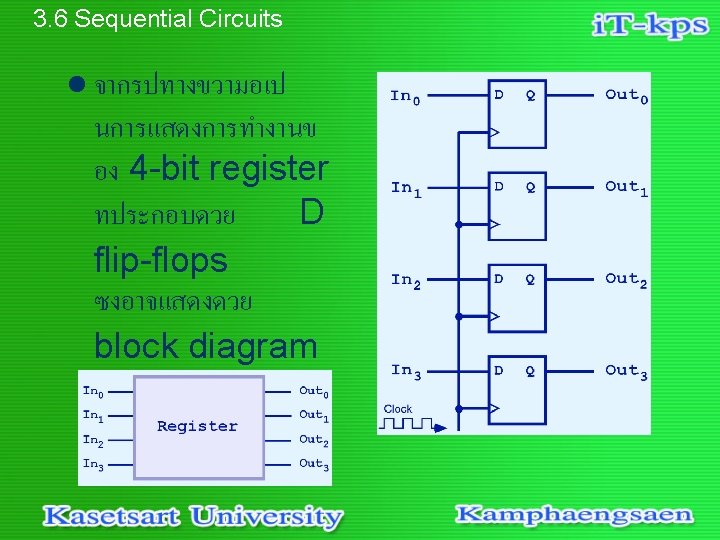

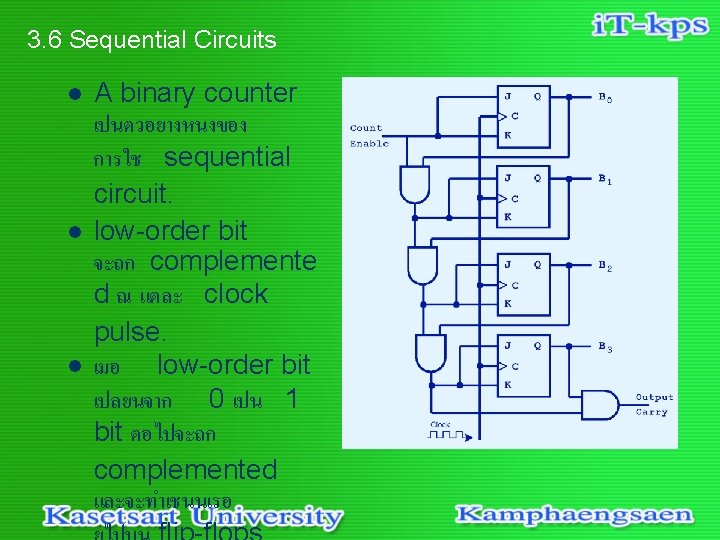

3. 6 Sequential Circuits l l l A binary counter เปนตวอยางหนงของ การใช sequential circuit. low-order bit จะถก complemente d ณ แตละ clock pulse. เมอ low-order bit เปลยนจาก 0 เปน 1 bit ตอไปจะถก complemented และจะทำเชนนเรอ

- Slides: 53