Chapter 3 ASIC Library Design ApplicationSpecific Integrated Circuits

Chapter 3 ASIC Library Design Application-Specific Integrated Circuits Michael John Sebastian Smith Addison Wesley, 1997 EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

ASIC Library Design l ASIC design is usually performed using a predefined and precharacterized library of cells l In designing this library, the original designer had to optimize speed and area without knowing the actual application that the cells will be used for - i. e. , how large a load they will be driving n n l wire load fanout load Being aware of the source and effect of these trade-offs will make it easier to understand how to optimally design using the library cells EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

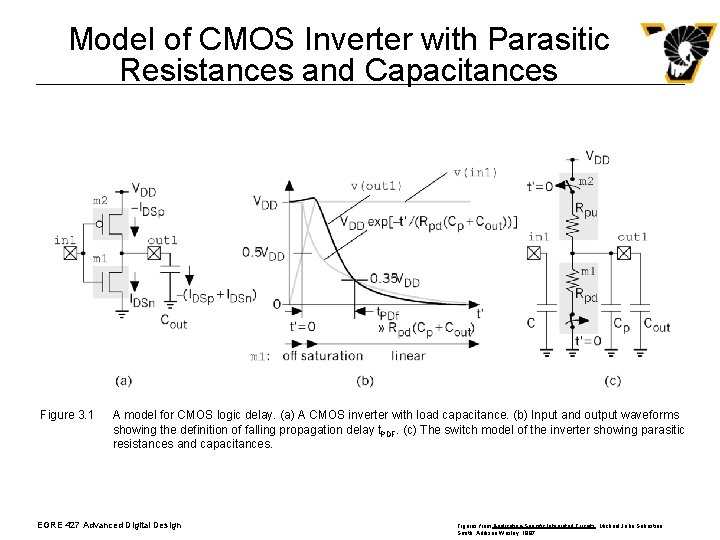

Model of CMOS Inverter with Parasitic Resistances and Capacitances Figure 3. 1 A model for CMOS logic delay. (a) A CMOS inverter with load capacitance. (b) Input and output waveforms showing the definition of falling propagation delay t. PDF. (c) The switch model of the inverter showing parasitic resistances and capacitances. EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

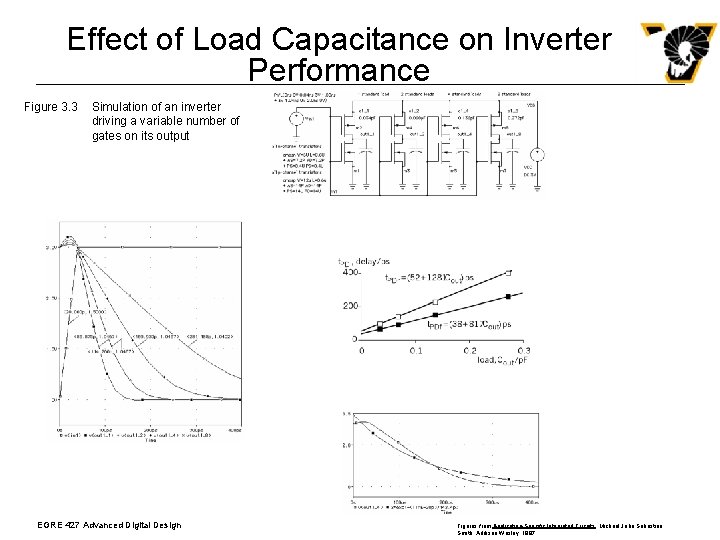

Effect of Load Capacitance on Inverter Performance Figure 3. 3 Simulation of an inverter driving a variable number of gates on its output EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

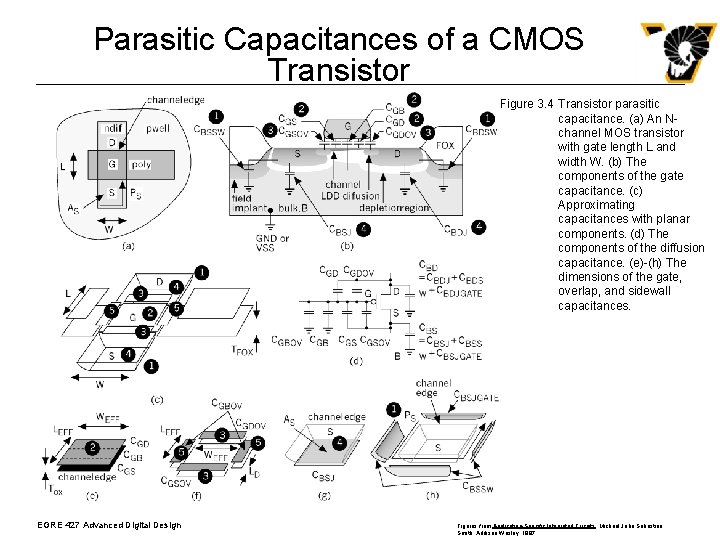

Parasitic Capacitances of a CMOS Transistor Figure 3. 4 Transistor parasitic capacitance. (a) An Nchannel MOS transistor with gate length L and width W. (b) The components of the gate capacitance. (c) Approximating capacitances with planar components. (d) The components of the diffusion capacitance. (e)-(h) The dimensions of the gate, overlap, and sidewall capacitances. EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

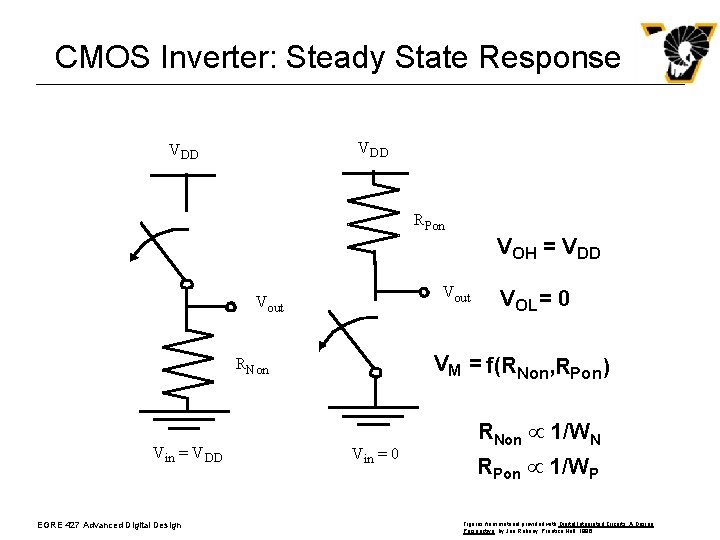

CMOS Inverter: Steady State Response VDD RPon VOH = VDD Vout VM = f(RNon, RPon ) RNon Vin = V DD EGRE 427 Advanced Digital Design VOL = 0 Vin = 0 RNon µ 1/WN RPon µ 1/WP Figures from material provided with Digital. Circuits Integrated Circuits, A Design Figures from Application-Specific Integrated , Michael John Sebastian Perspective, Jan Rabaey, Smith, Addison by Wesley, 1997 Prentice Hall, 1996

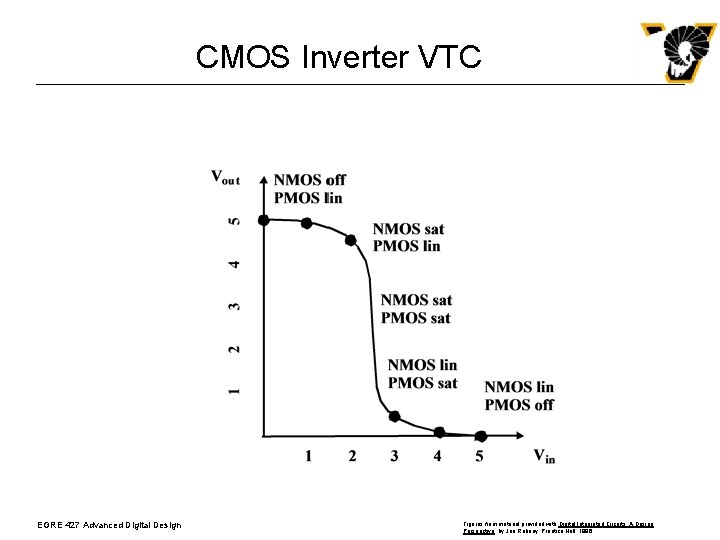

CMOS Inverter VTC EGRE 427 Advanced Digital Design Figures from material provided with Digital. Circuits Integrated Circuits, A Design Figures from Application-Specific Integrated , Michael John Sebastian Perspective, Jan Rabaey, Smith, Addison by Wesley, 1997 Prentice Hall, 1996

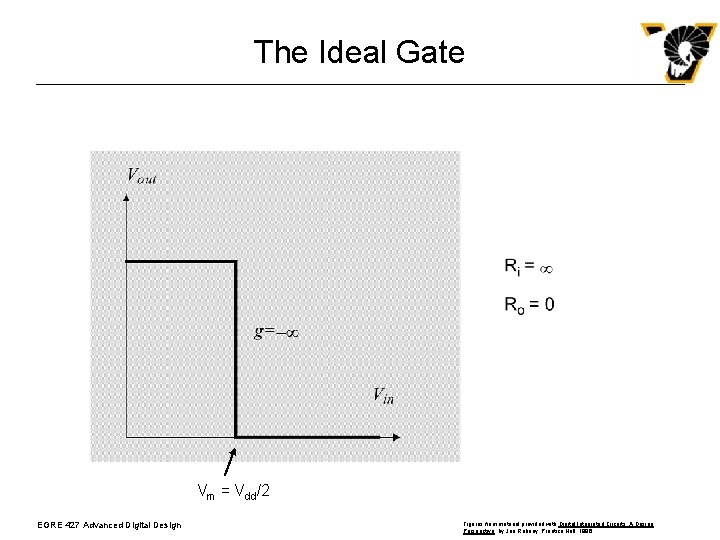

The Ideal Gate Vm = Vdd/2 EGRE 427 Advanced Digital Design Figures from material provided with Digital. Circuits Integrated Circuits, A Design Figures from Application-Specific Integrated , Michael John Sebastian Perspective, Jan Rabaey, Smith, Addison by Wesley, 1997 Prentice Hall, 1996

Balanced CMOS Inverter Assume that due to differences in mp and mn, for a minimum sized transistor, Rp = 2 Rn For a balanced inverter we want RP = RN, so in this case, WP must be 2 WN WP/LP = 2/1 WN/LN = 2/1 EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

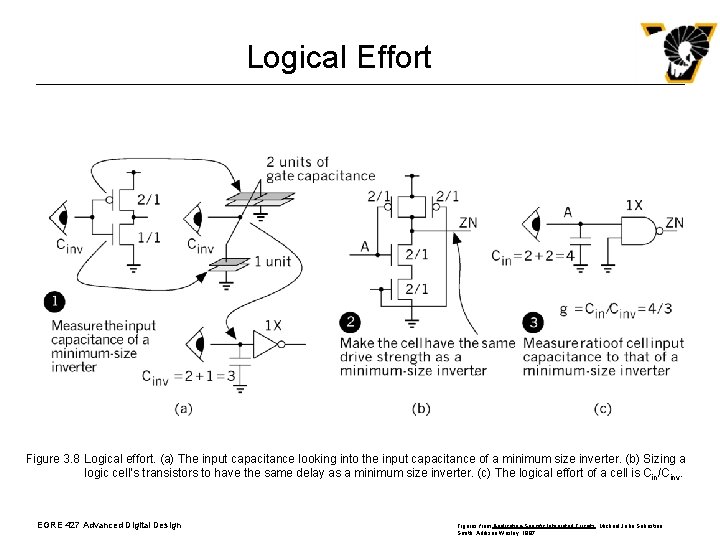

Logical Effort Figure 3. 8 Logical effort. (a) The input capacitance looking into the input capacitance of a minimum size inverter. (b) Sizing a logic cell’s transistors to have the same delay as a minimum size inverter. (c) The logical effort of a cell is Cin/Cinv. EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

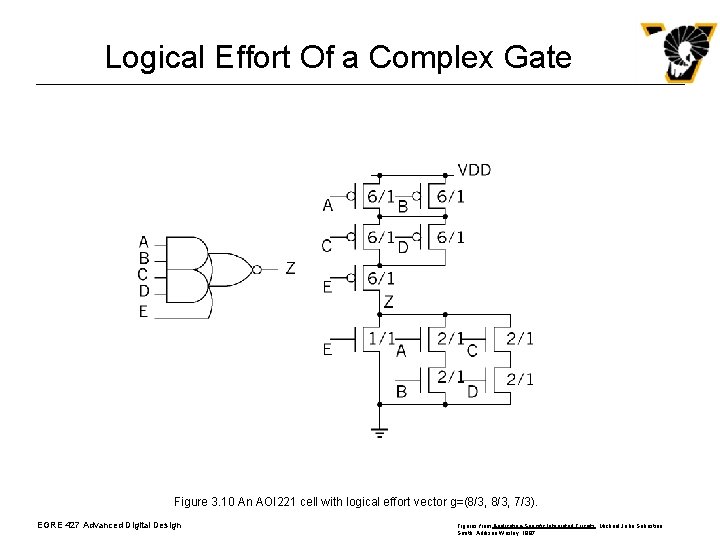

Logical Effort Of a Complex Gate Figure 3. 10 An AOI 221 cell with logical effort vector g=(8/3, 7/3). EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

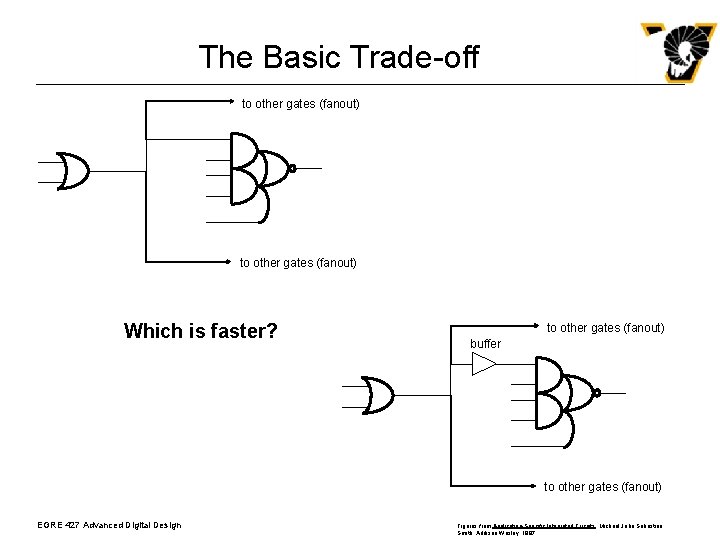

The Basic Trade-off to other gates (fanout) Which is faster? to other gates (fanout) buffer to other gates (fanout) EGRE 427 Advanced Digital Design Figures from Application-Specific Integrated Circuits , Michael John Sebastian Smith, Addison Wesley, 1997

- Slides: 12