Chapter 2 Microcontroller Architecture PIC 18 F Family

- Slides: 41

Chapter 2 Microcontroller Architecture— PIC 18 F Family

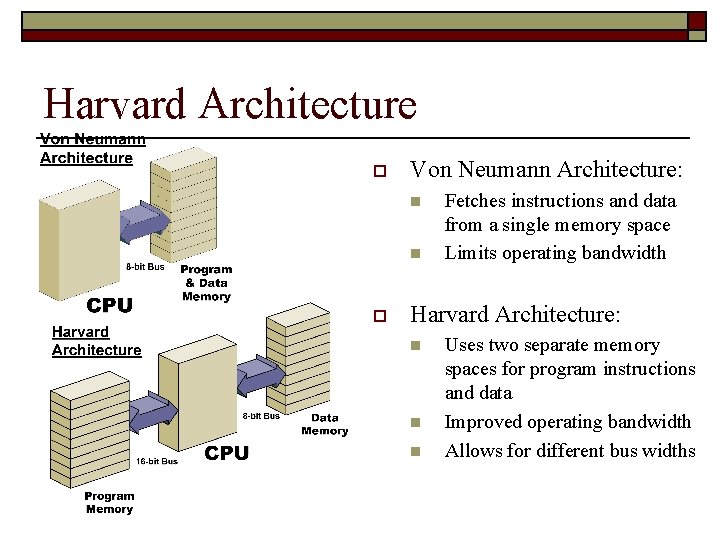

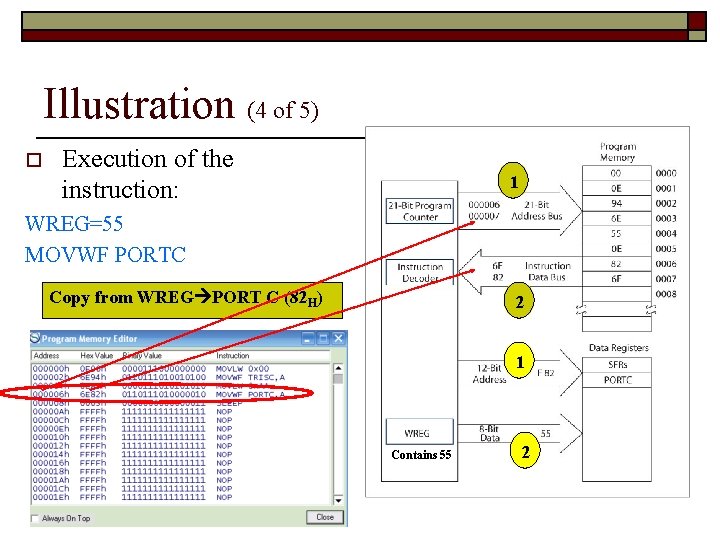

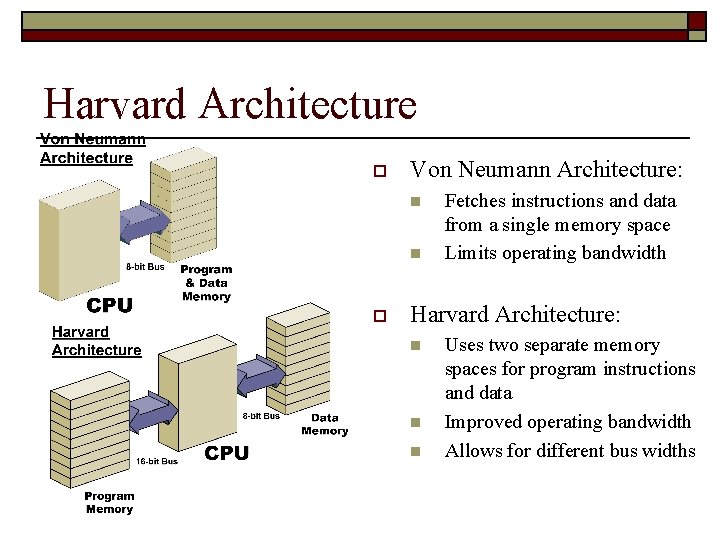

Harvard Architecture o Von Neumann Architecture: n n o Fetches instructions and data from a single memory space Limits operating bandwidth Harvard Architecture: n n n Uses two separate memory spaces for program instructions and data Improved operating bandwidth Allows for different bus widths

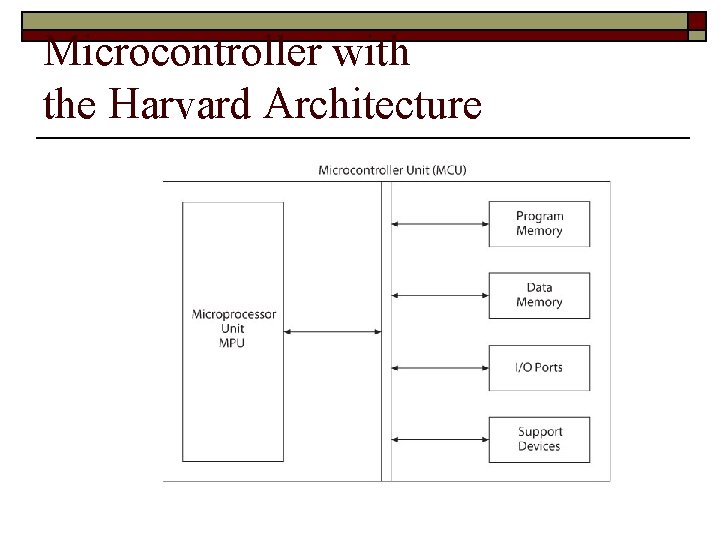

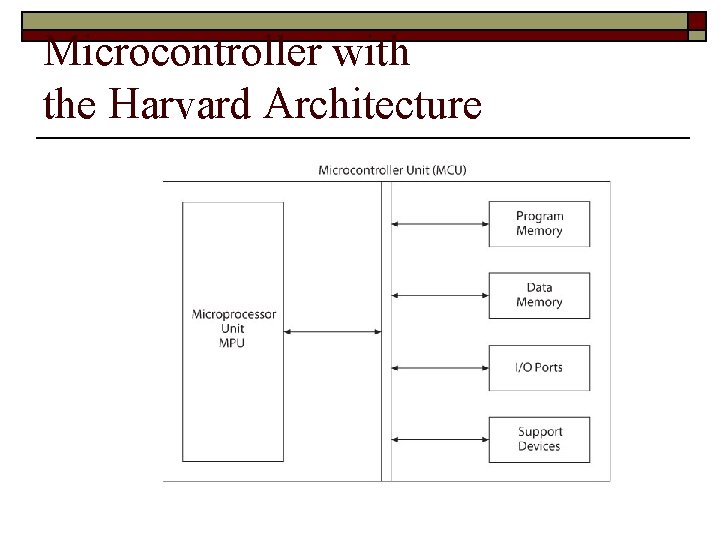

PIC 18 F Microcontroller Families o PIC microcontrollers are designed using the Harvard Architecture which includes: n n n Microprocessor unit (MPU) Program memory for instructions Data memory for data I/O ports Support devices such as timers

Microcontroller with the Harvard Architecture

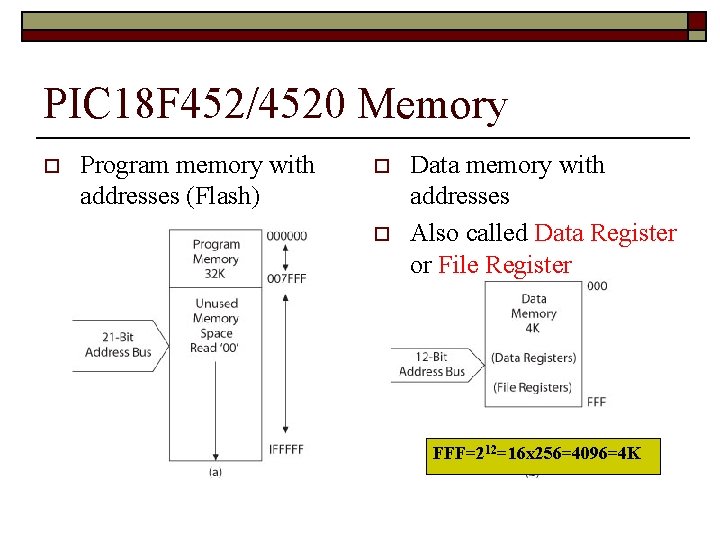

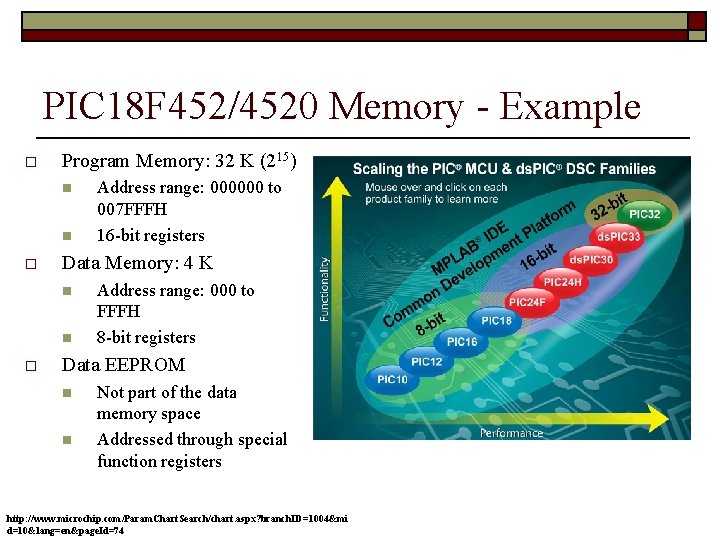

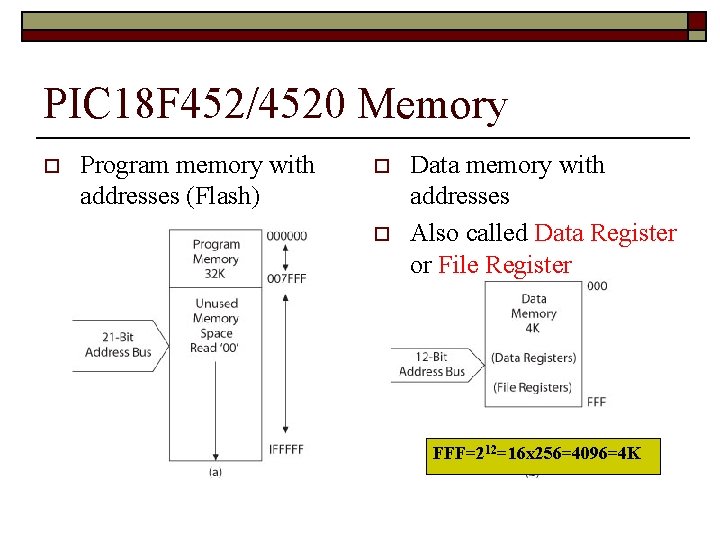

PIC 18 F 452/4520 Memory - Example o Program Memory: 32 K (215) n n o Data Memory: 4 K n n o Address range: 000000 to 007 FFFH 16 -bit registers Address range: 000 to FFFH 8 -bit registers Data EEPROM n n Not part of the data memory space Addressed through special function registers http: //www. microchip. com/Param. Chart. Search/chart. aspx? branch. ID=1004&mi d=10&lang=en&page. Id=74

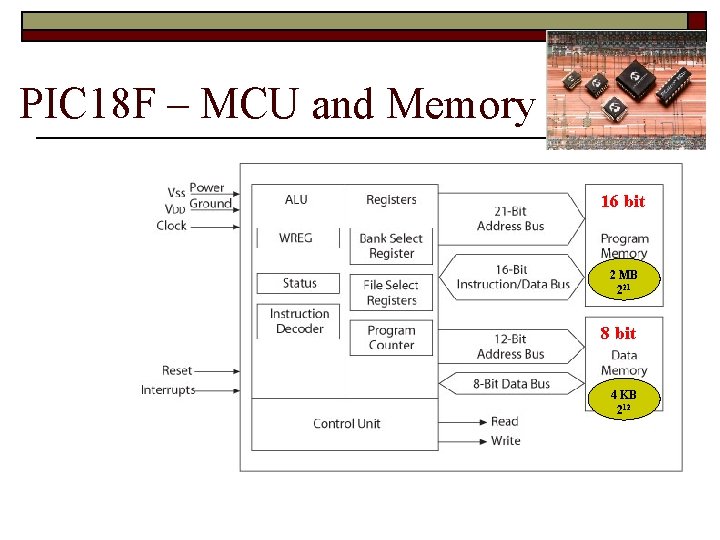

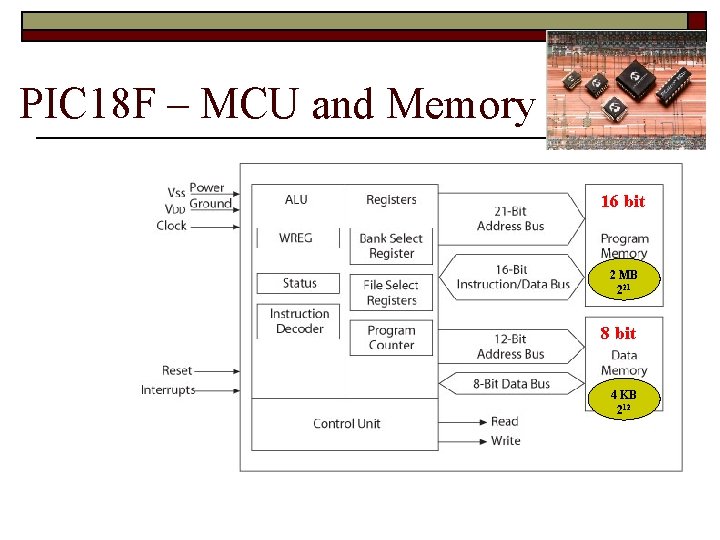

PIC 18 F – MCU and Memory 16 bit 2 MB 221 8 bit 4 KB 212

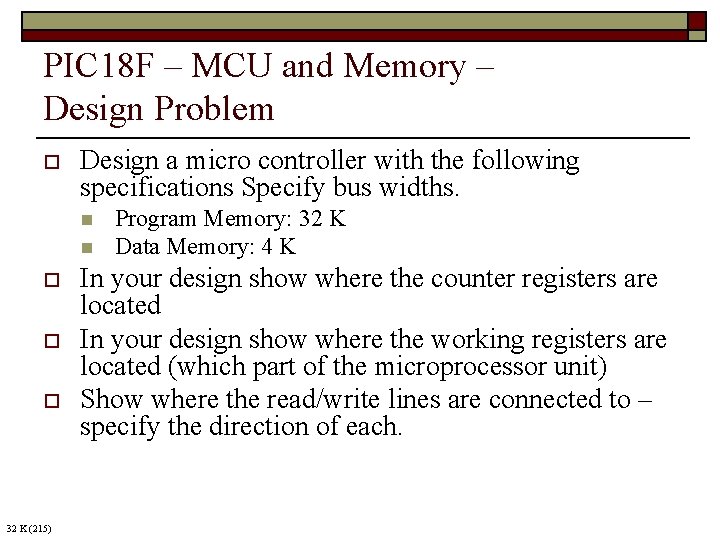

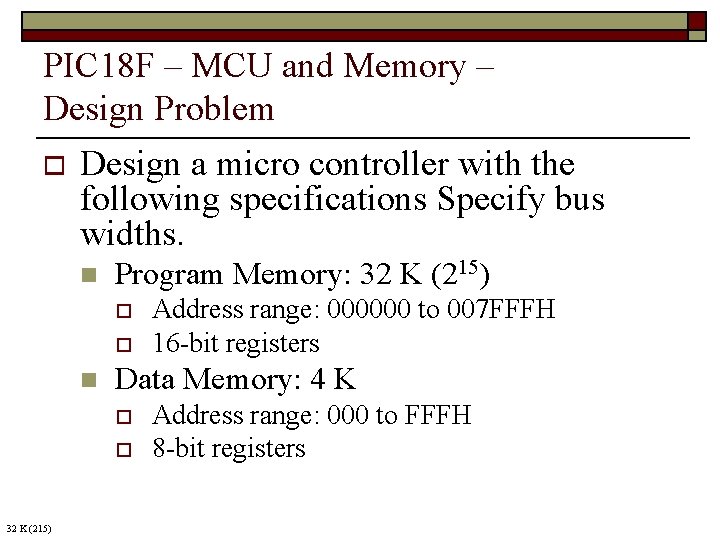

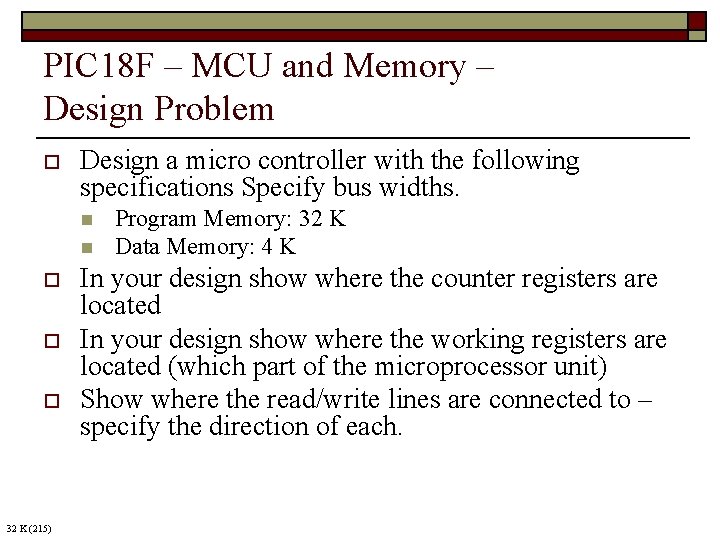

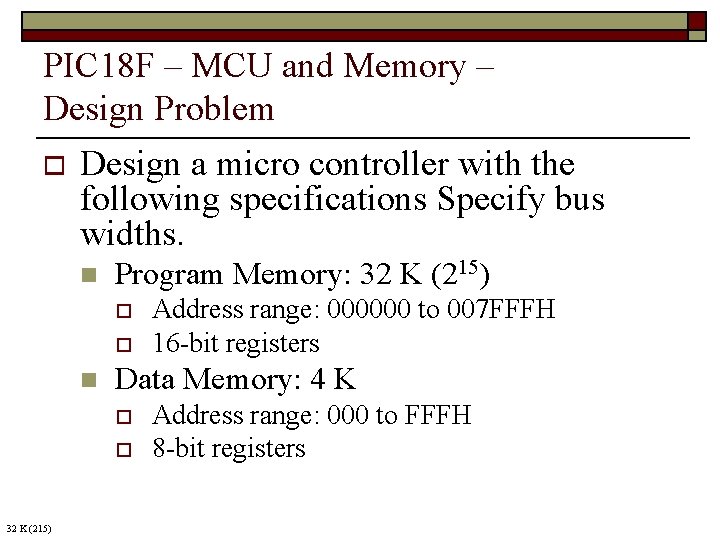

PIC 18 F – MCU and Memory – Design Problem o Design a micro controller with the following specifications Specify bus widths. n n o o o 32 K (215) Program Memory: 32 K Data Memory: 4 K In your design show where the counter registers are located In your design show where the working registers are located (which part of the microprocessor unit) Show where the read/write lines are connected to – specify the direction of each.

PIC 18 F – MCU and Memory – Design Problem o Design a micro controller with the following specifications Specify bus widths. n Program Memory: 32 K (215) o o n Data Memory: 4 K o o 32 K (215) Address range: 000000 to 007 FFFH 16 -bit registers Address range: 000 to FFFH 8 -bit registers

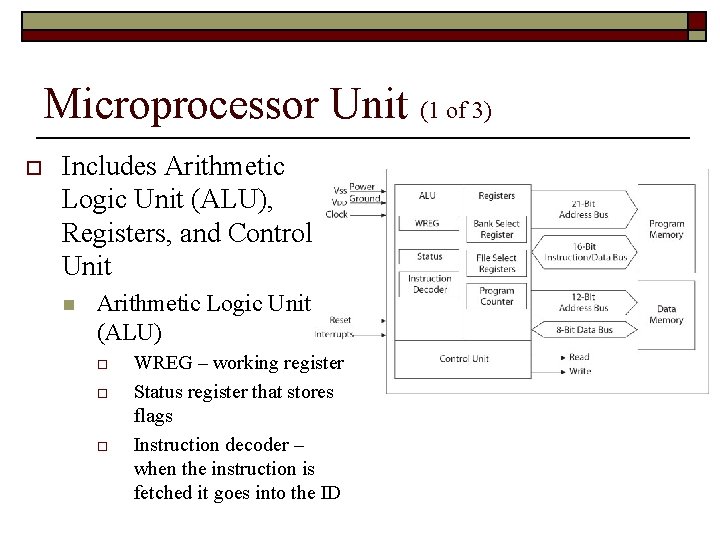

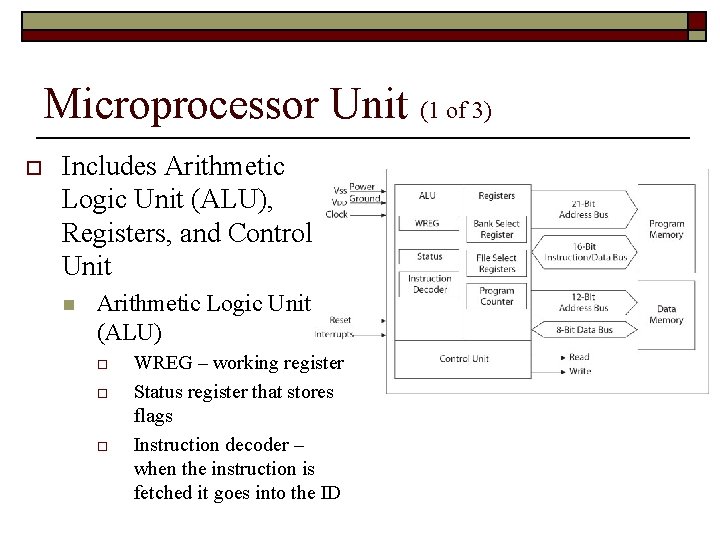

Microprocessor Unit (1 of 3) o Includes Arithmetic Logic Unit (ALU), Registers, and Control Unit n Arithmetic Logic Unit (ALU) o o o WREG – working register Status register that stores flags Instruction decoder – when the instruction is fetched it goes into the ID

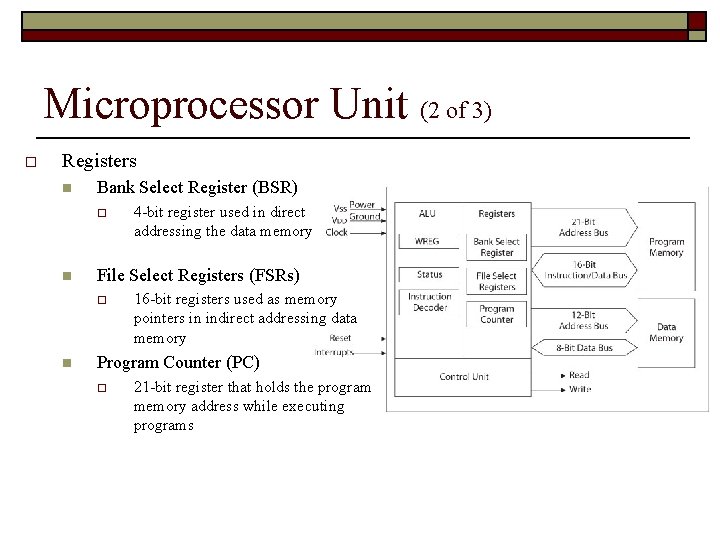

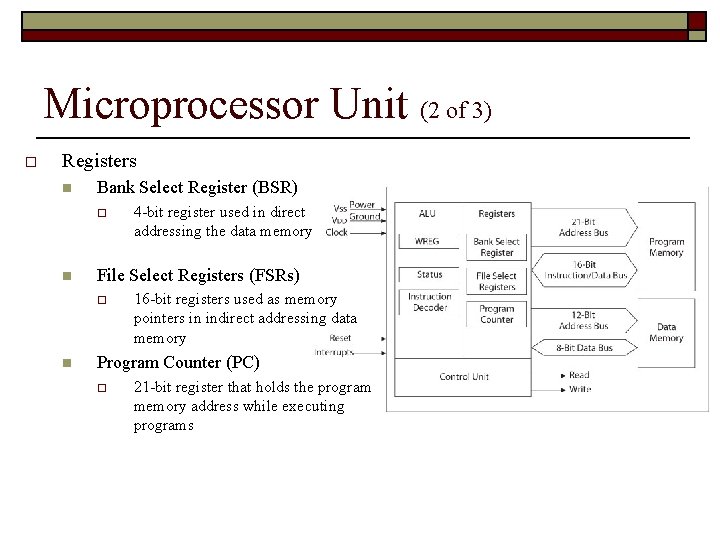

Microprocessor Unit (2 of 3) o Registers n Bank Select Register (BSR) o n File Select Registers (FSRs) o n 4 -bit register used in direct addressing the data memory 16 -bit registers used as memory pointers in indirect addressing data memory Program Counter (PC) o 21 -bit register that holds the program memory address while executing programs

Microprocessor Unit (3 of 3) o Control unit n Provides timing and control signals to various Read and Write operations

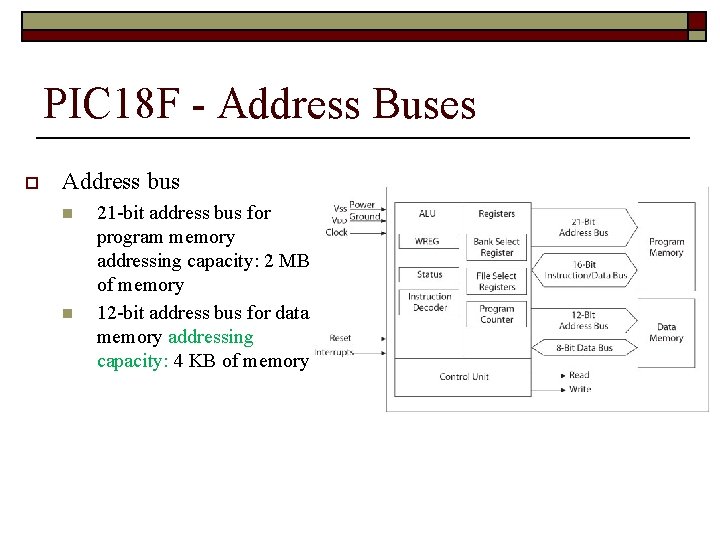

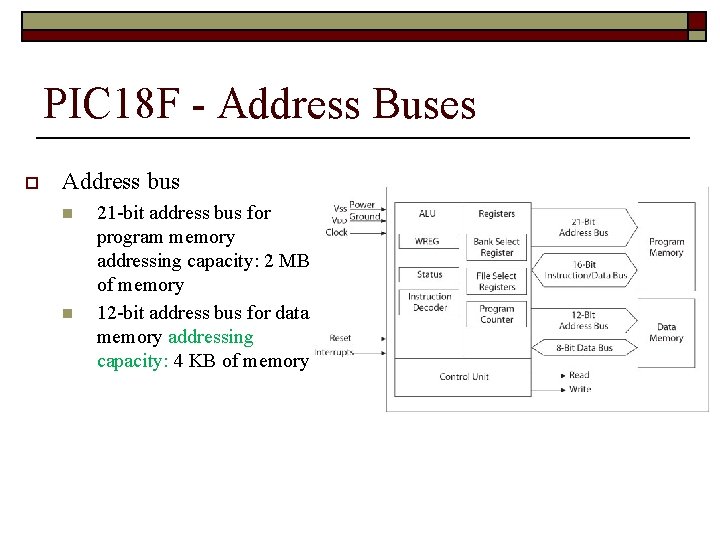

PIC 18 F - Address Buses o Address bus n n 21 -bit address bus for program memory addressing capacity: 2 MB of memory 12 -bit address bus for data memory addressing capacity: 4 KB of memory

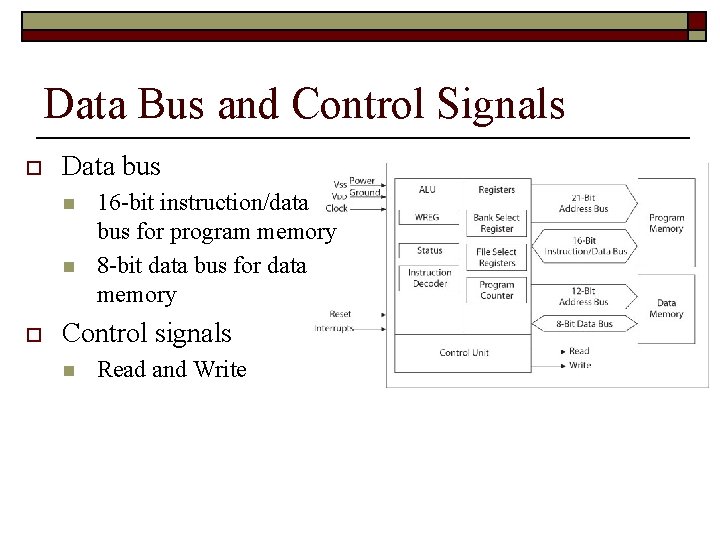

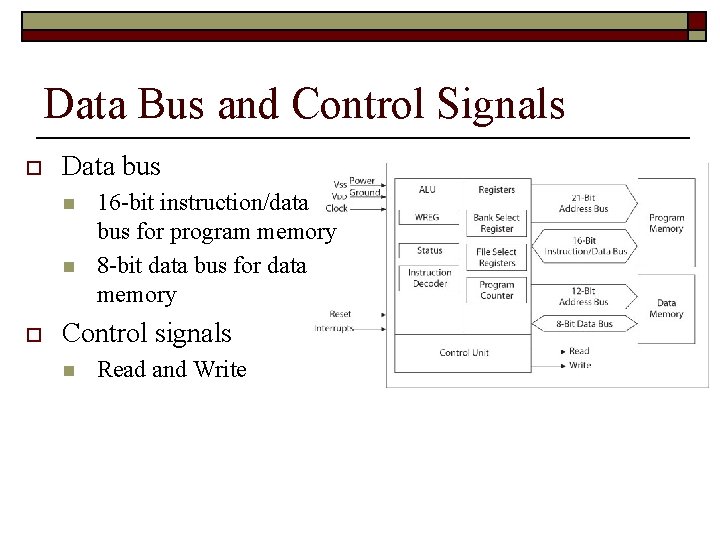

Data Bus and Control Signals o Data bus n n o 16 -bit instruction/data bus for program memory 8 -bit data bus for data memory Control signals n Read and Write

Examples o Refer to your notes!

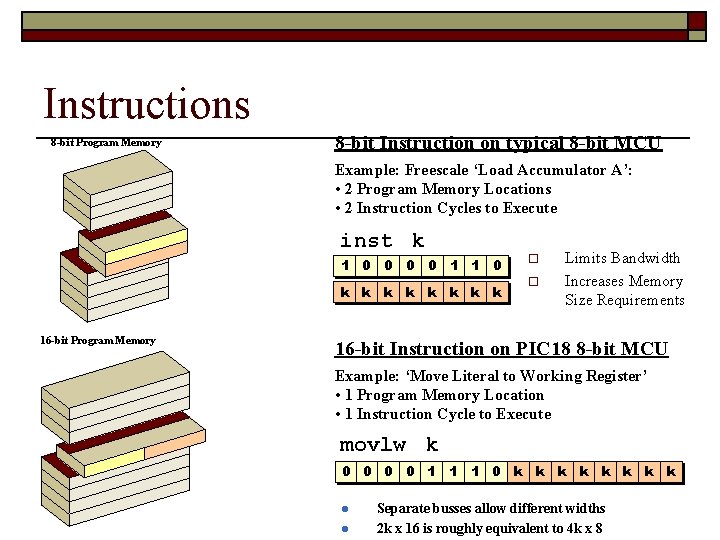

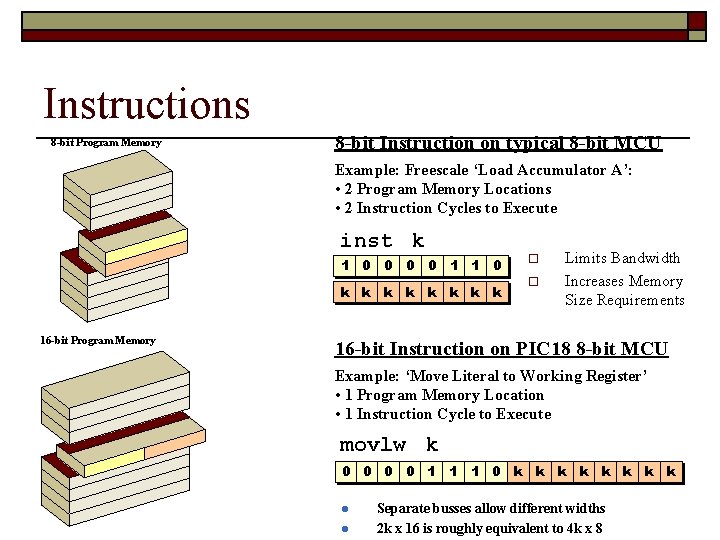

Instructions 8 -bit Program Memory 8 -bit Instruction on typical 8 -bit MCU Example: Freescale ‘Load Accumulator A’: • 2 Program Memory Locations • 2 Instruction Cycles to Execute inst k 16 -bit Program Memory 1 0 0 1 1 0 k k k k o o Limits Bandwidth Increases Memory Size Requirements 16 -bit Instruction on PIC 18 8 -bit MCU Example: ‘Move Literal to Working Register’ • 1 Program Memory Location • 1 Instruction Cycle to Execute movlw k 0 l l 0 0 0 1 1 1 0 k k k Separate busses allow different widths 2 k x 16 is roughly equivalent to 4 k x 8 k k k

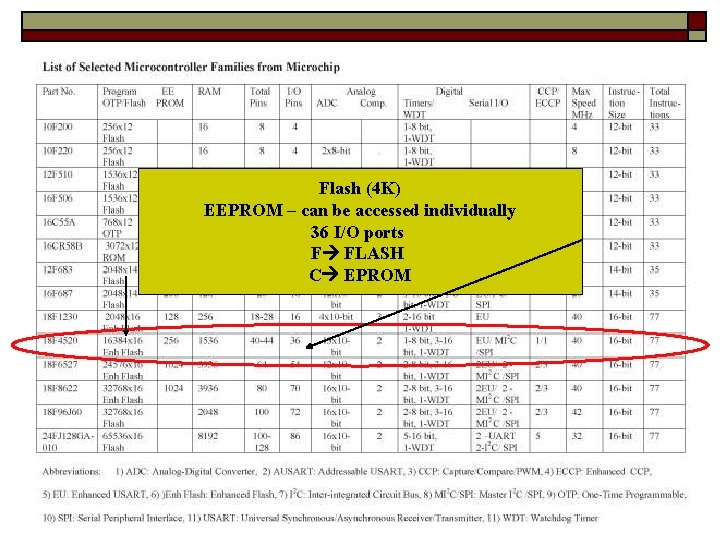

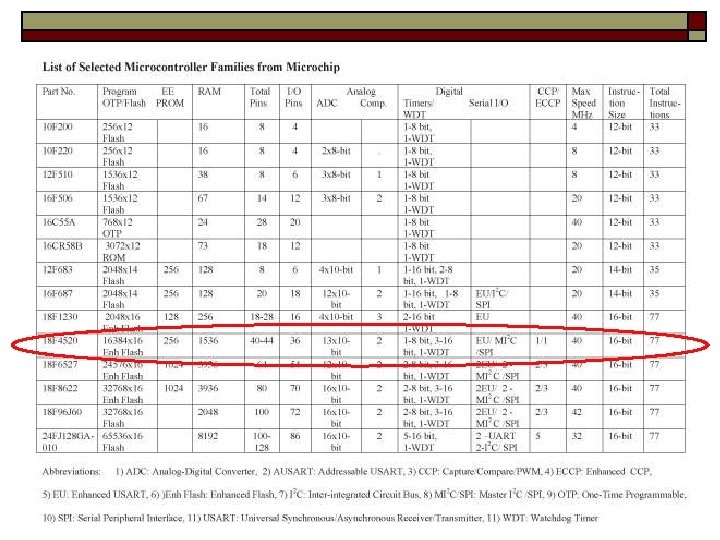

Flash (4 K) EEPROM – can be accessed individually 36 I/O ports F FLASH C EPROM

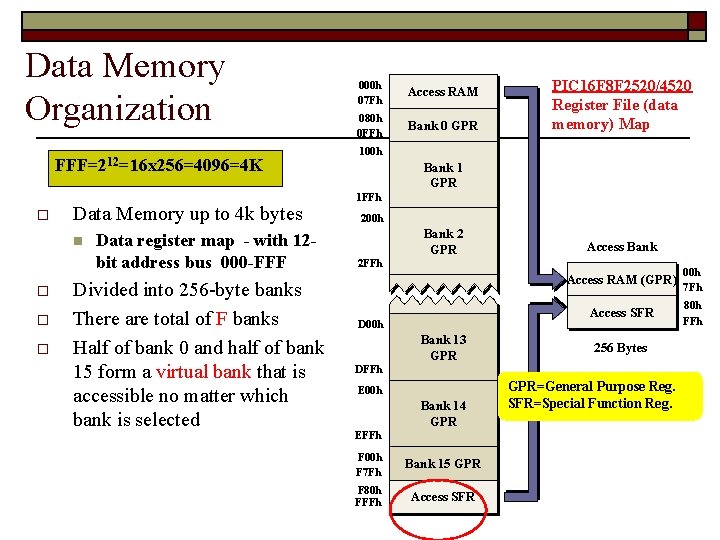

PIC 18 F 452/4520 Memory o Program memory with addresses (Flash) o o Data memory with addresses Also called Data Register or File Register FFF=212=16 x 256=4096=4 K

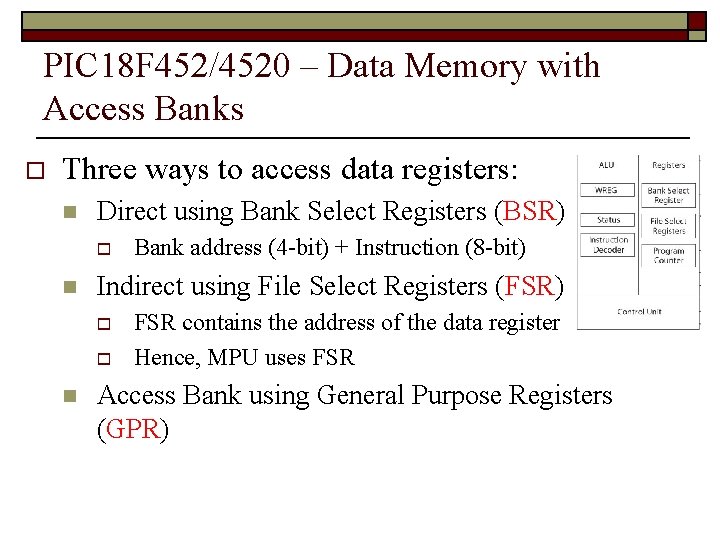

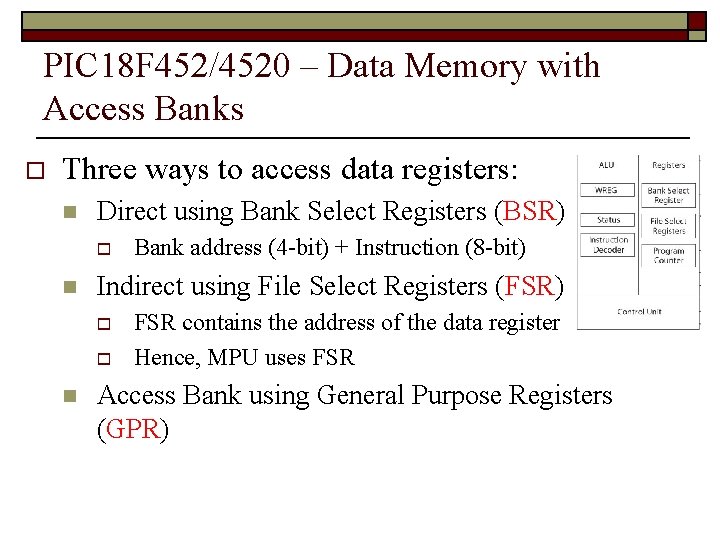

PIC 18 F 452/4520 – Data Memory with Access Banks o Three ways to access data registers: n Direct using Bank Select Registers (BSR) o n Indirect using File Select Registers (FSR) o o n Bank address (4 -bit) + Instruction (8 -bit) FSR contains the address of the data register Hence, MPU uses FSR Access Bank using General Purpose Registers (GPR)

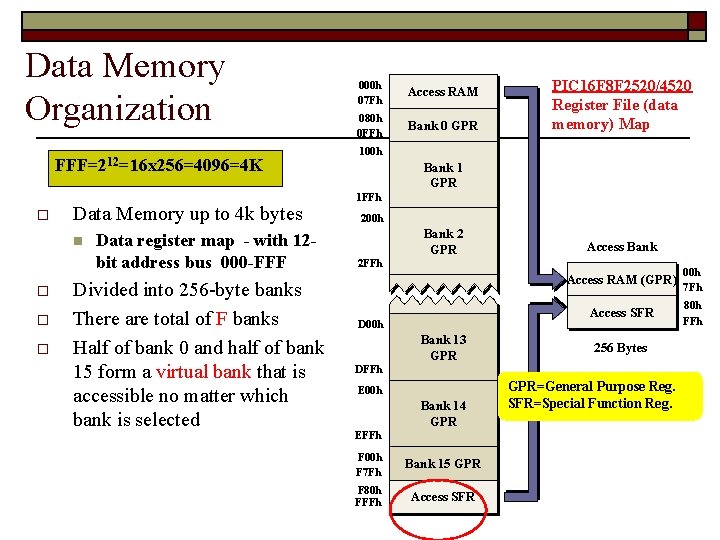

Data Memory Organization FFF=212=16 x 256=4096=4 K o Data Memory up to 4 k bytes n o o o Data register map - with 12 bit address bus 000 -FFF Divided into 256 -byte banks There are total of F banks Half of bank 0 and half of bank 15 form a virtual bank that is accessible no matter which bank is selected 000 h 07 Fh Access RAM 080 h 0 FFh Bank 0 GPR PIC 16 F 8 F 2520/4520 Register File (data memory) Map 100 h Bank 1 GPR 1 FFh 200 h Bank 2 GPR Access Bank 2 FFh D 00 h Bank 13 GPR Access RAM (GPR) 00 h 7 Fh Access SFR 80 h FFh 256 Bytes DFFh E 00 h Bank 14 GPR EFFh F 00 h F 7 Fh Bank 15 GPR F 80 h FFFh Access SFR GPR=General Purpose Reg. SFR=Special Function Reg.

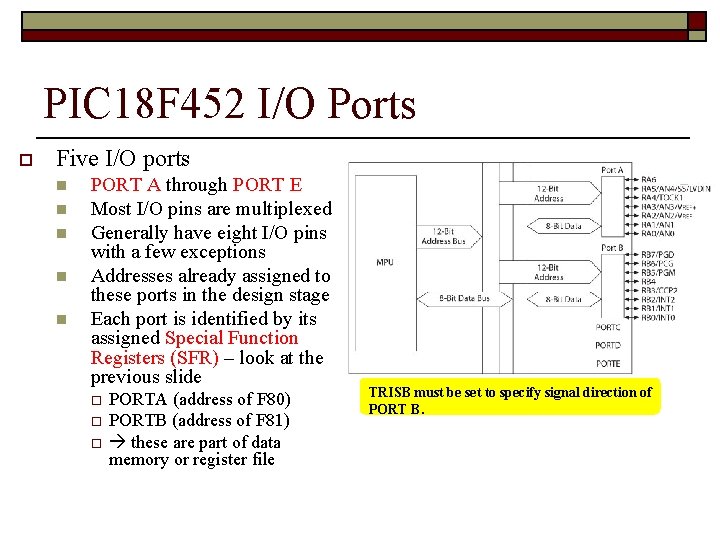

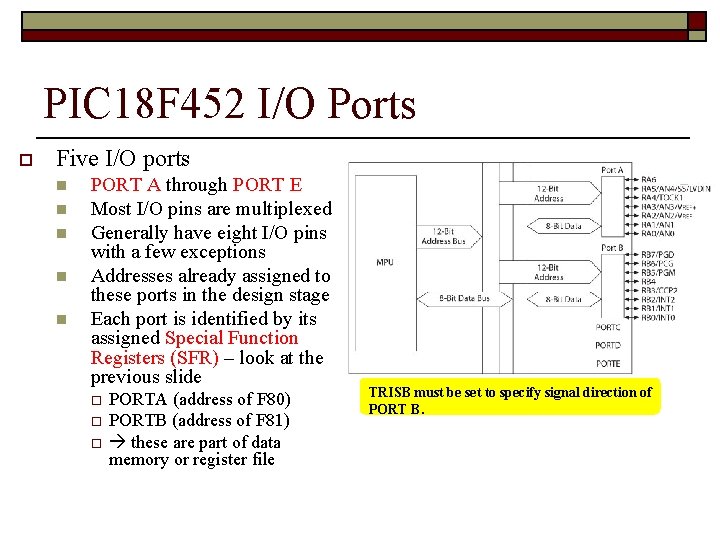

PIC 18 F 452 I/O Ports o Five I/O ports n n n PORT A through PORT E Most I/O pins are multiplexed Generally have eight I/O pins with a few exceptions Addresses already assigned to these ports in the design stage Each port is identified by its assigned Special Function Registers (SFR) – look at the previous slide o o o PORTA (address of F 80) PORTB (address of F 81) these are part of data memory or register file TRISB must be set to specify signal direction of PORT B.

Processes and Conditions of Data Transfer o Interrupt is a process of communication between two devices n n o If provides efficient communication between the two devices Examples: Sending a file to a printer, pressing a key on the key board External or Internal to the MPU

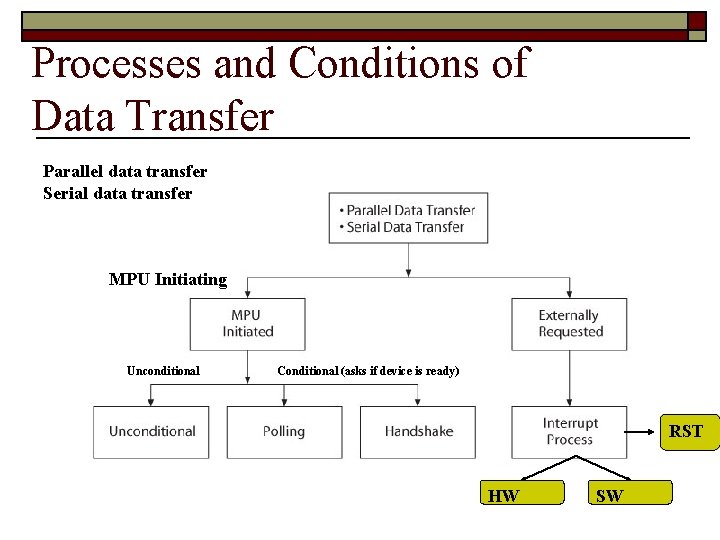

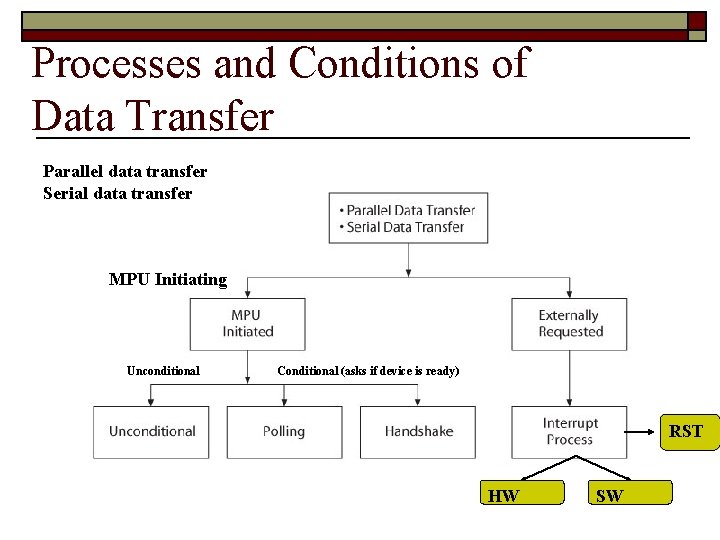

Processes and Conditions of Data Transfer Parallel data transfer Serial data transfer MPU Initiating Unconditional Conditional (asks if device is ready) RST HW SW

Processes and Conditions of Data Transfer o Reset n n Special type of external interrupt Examples: o o o Manual Reset Power-on Reset Brown-out Reset (power goes below a specifies value)

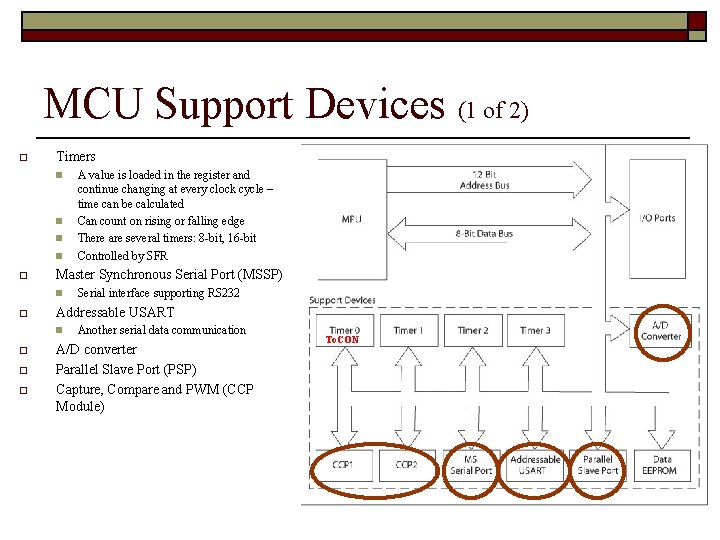

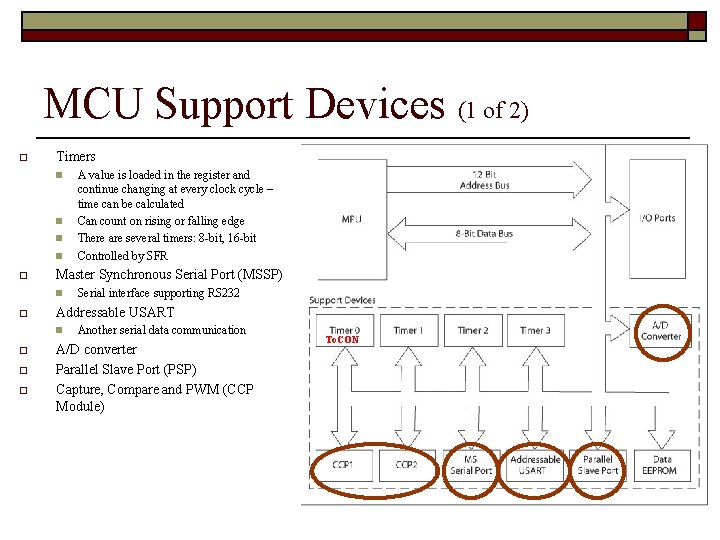

MCU Support Devices (1 of 2) o Timers n n o Master Synchronous Serial Port (MSSP) n o o o Serial interface supporting RS 232 Addressable USART n o A value is loaded in the register and continue changing at every clock cycle – time can be calculated Can count on rising or falling edge There are several timers: 8 -bit, 16 -bit Controlled by SFR Another serial data communication A/D converter Parallel Slave Port (PSP) Capture, Compare and PWM (CCP Module) To. CON

PIC 18 F Special Features o Sleep mode n o Watchdog timer (WDT) n o o Able to reset the processor if the program is caught in unknown state (e. g. , infinite loop) Code protection n o Power-down mode EEPROM can be protected through SFR In-circuit serial programming In-circuit debugger

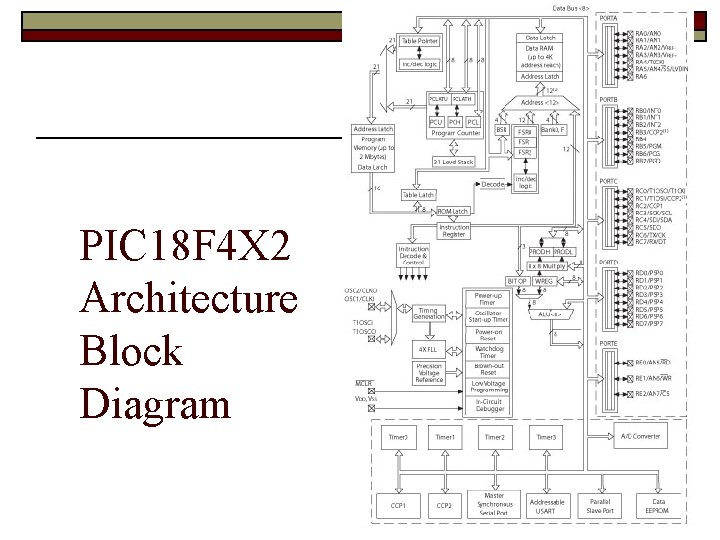

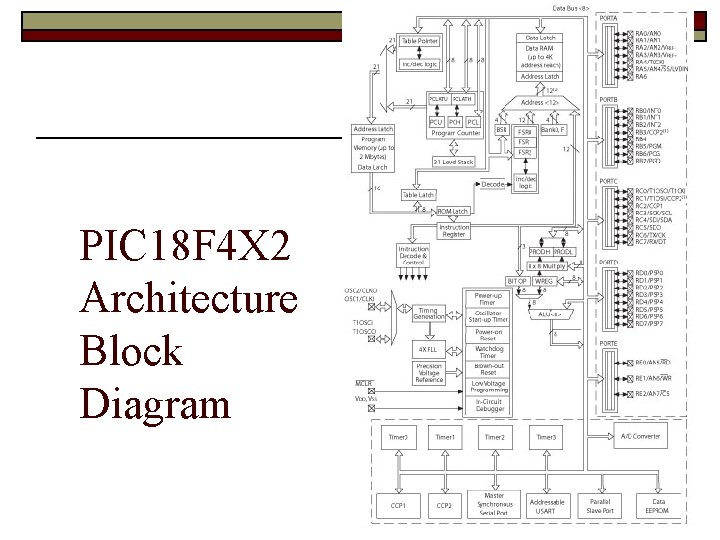

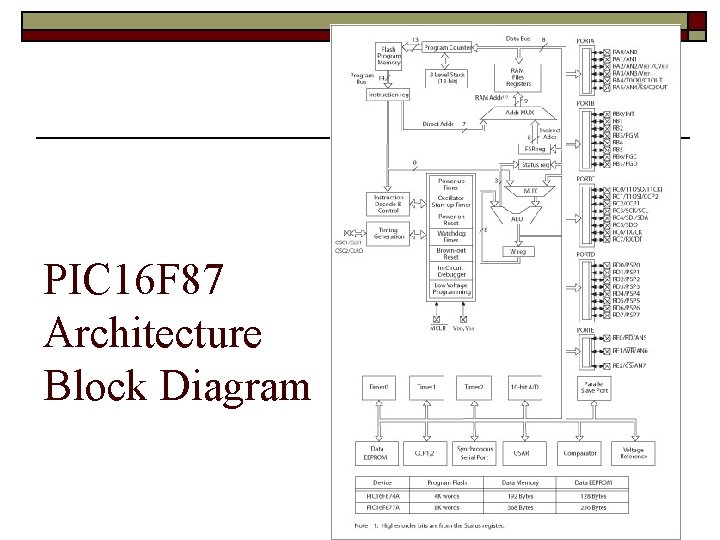

PIC 18 F 4 X 2 Architecture Block Diagram

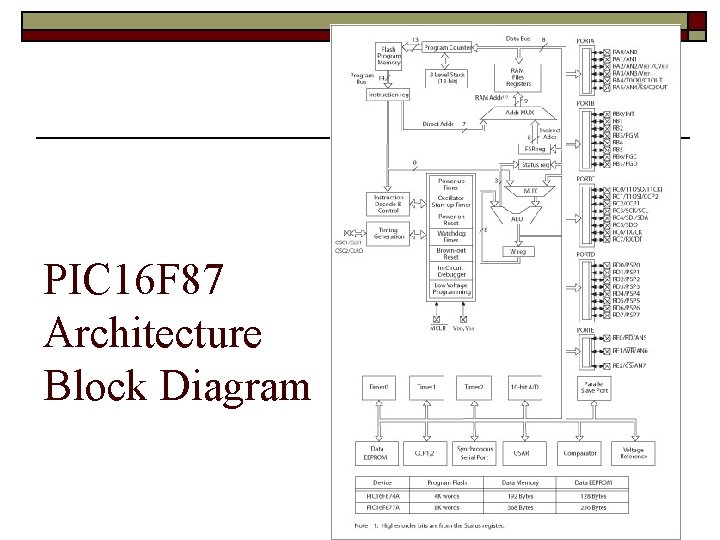

PIC 16 F 87 Architecture Block Diagram

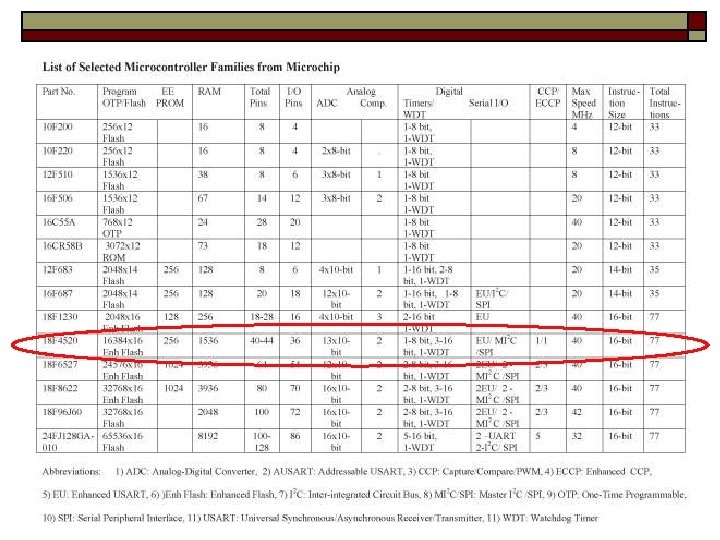

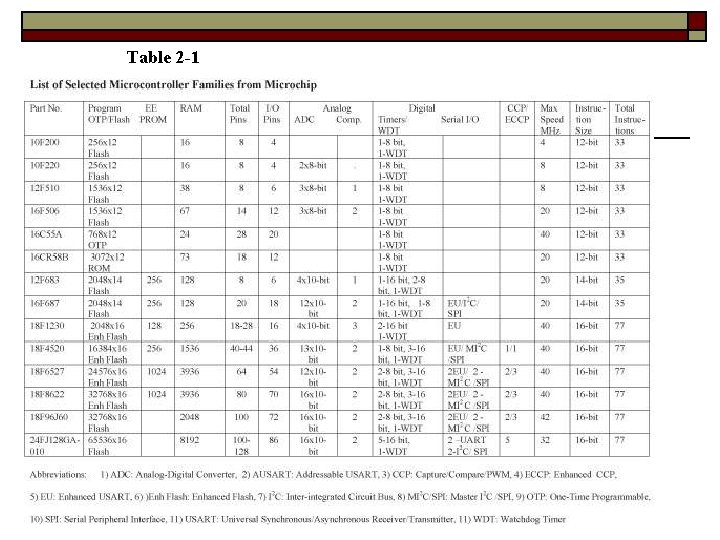

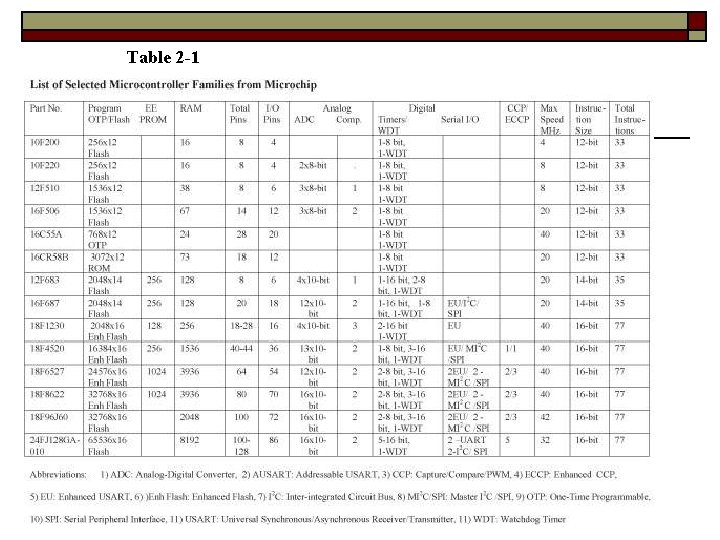

Table 2 -1

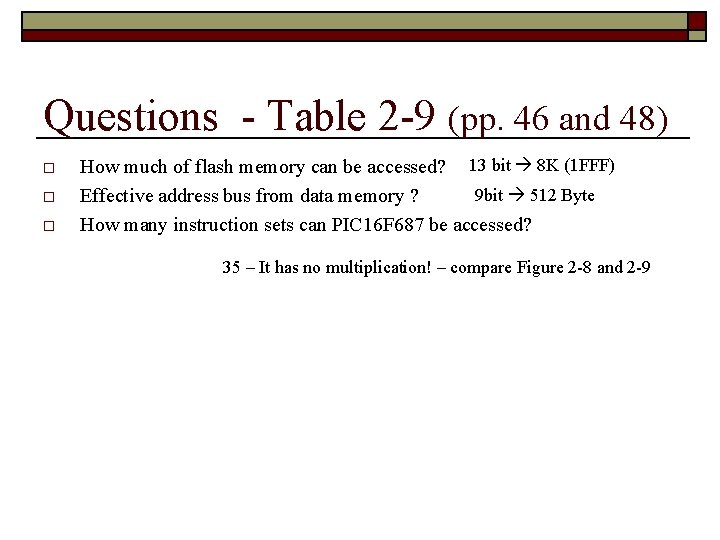

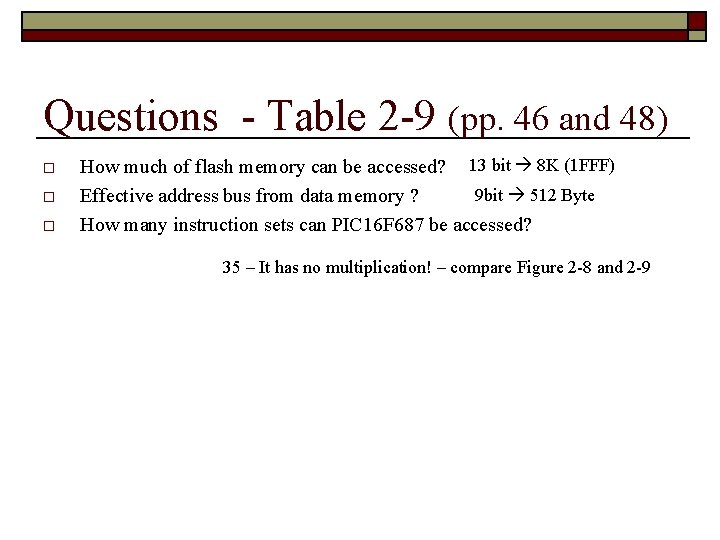

Questions - Table 2 -9 (pp. 46 and 48) o o o How much of flash memory can be accessed? 13 bit 8 K (1 FFF) 9 bit 512 Byte Effective address bus from data memory ? How many instruction sets can PIC 16 F 687 be accessed? 35 – It has no multiplication! – compare Figure 2 -8 and 2 -9

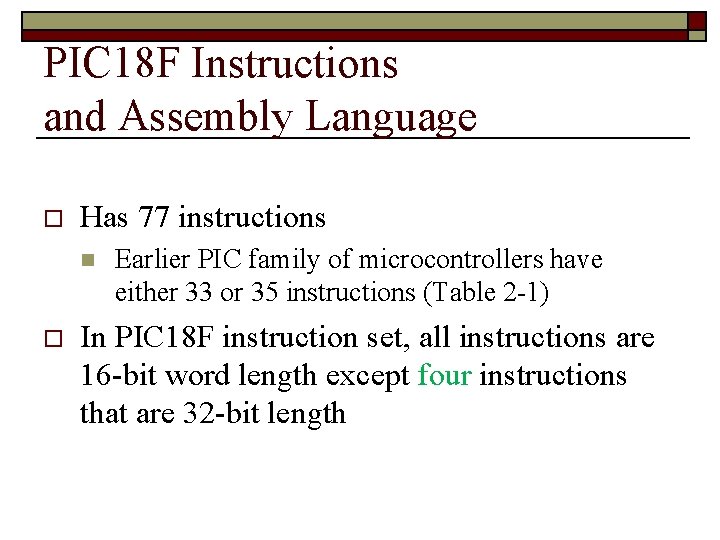

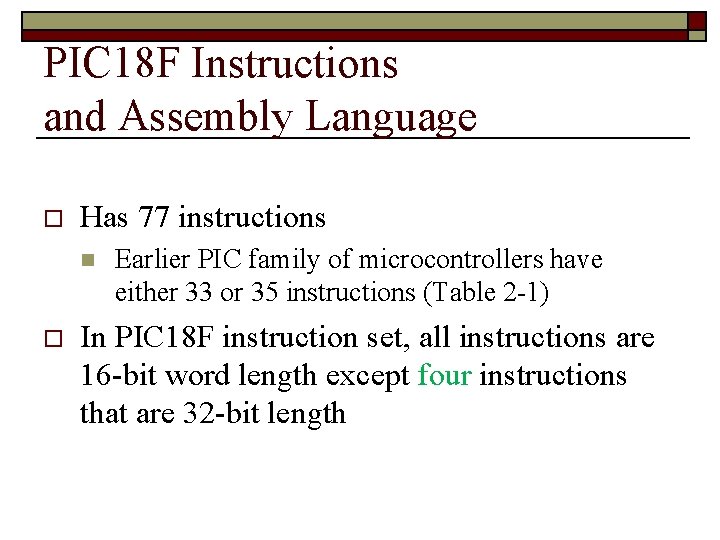

PIC 18 F Instructions and Assembly Language o Has 77 instructions n o Earlier PIC family of microcontrollers have either 33 or 35 instructions (Table 2 -1) In PIC 18 F instruction set, all instructions are 16 -bit word length except four instructions that are 32 -bit length

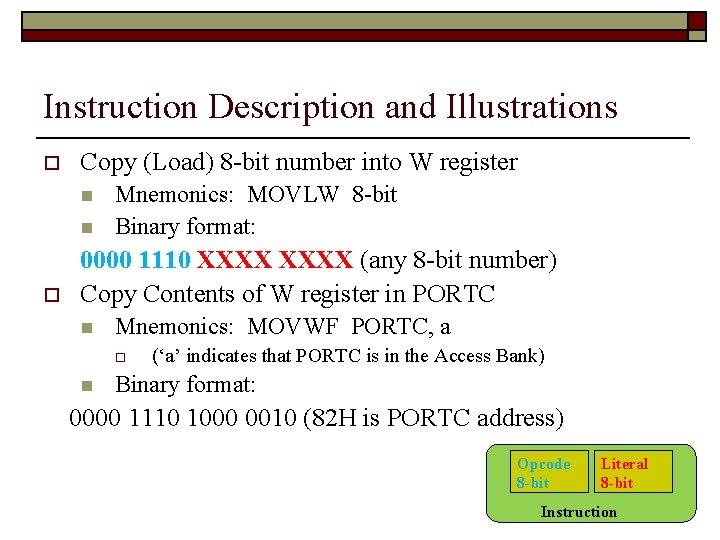

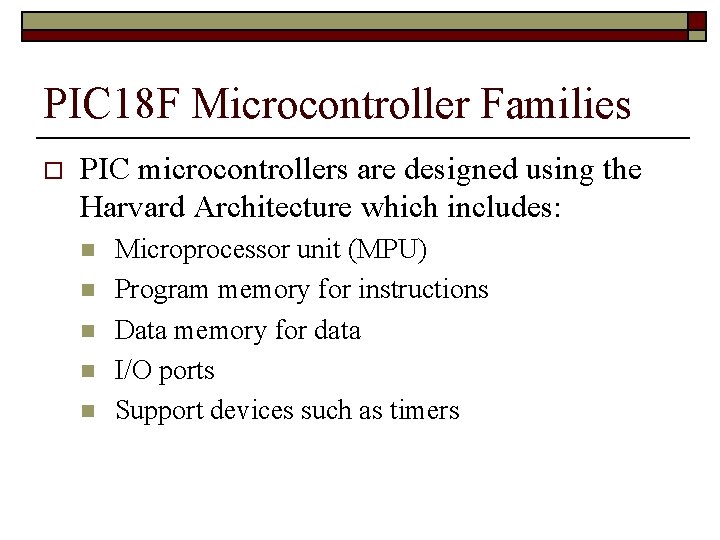

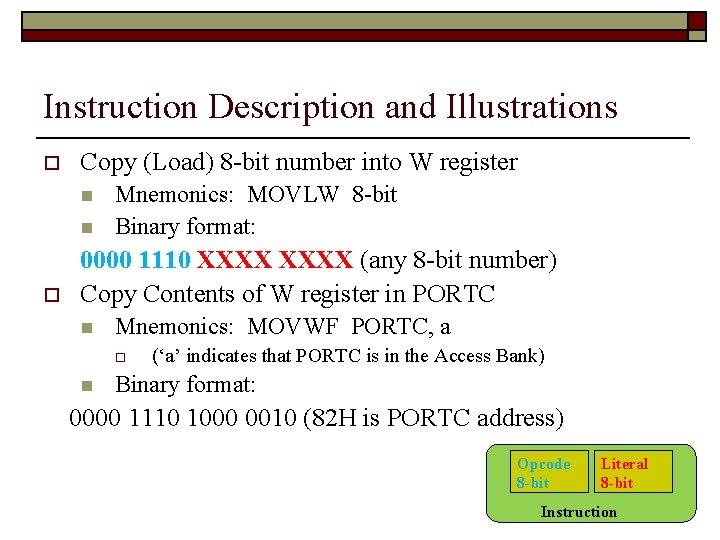

Instruction Description and Illustrations o Copy (Load) 8 -bit number into W register n n o Mnemonics: MOVLW 8 -bit Binary format: 0000 1110 XXXX (any 8 -bit number) Copy Contents of W register in PORTC n Mnemonics: MOVWF PORTC, a o n (‘a’ indicates that PORTC is in the Access Bank) Binary format: 0000 1110 1000 0010 (82 H is PORTC address) Opcode 8 -bit Literal 8 -bit Instruction

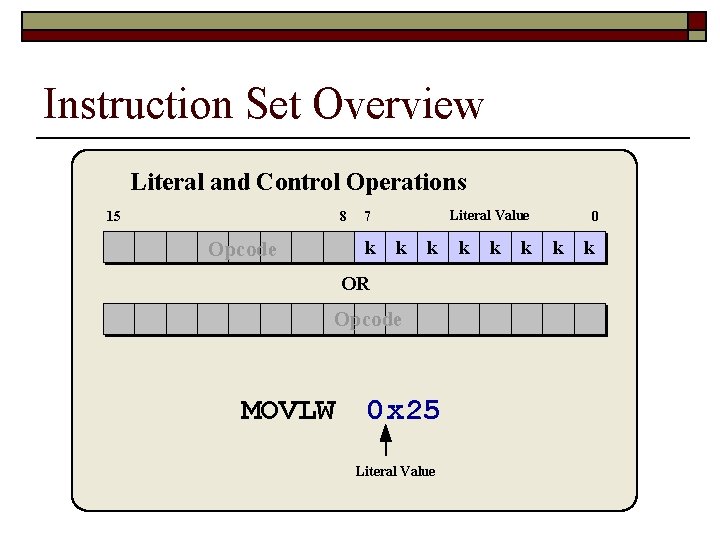

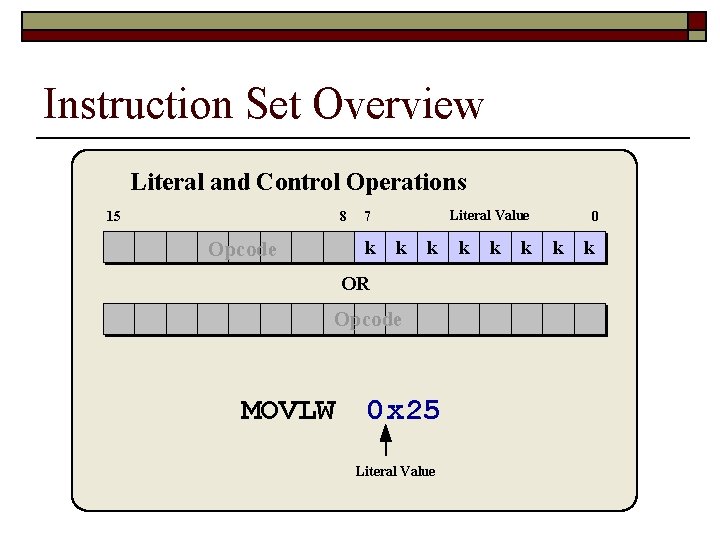

Instruction Set Overview Literal and Control Operations 15 8 k Opcode Literal Value 7 k k OR Opcode MOVLW 0 x 25 Literal Value k k k 0 k k

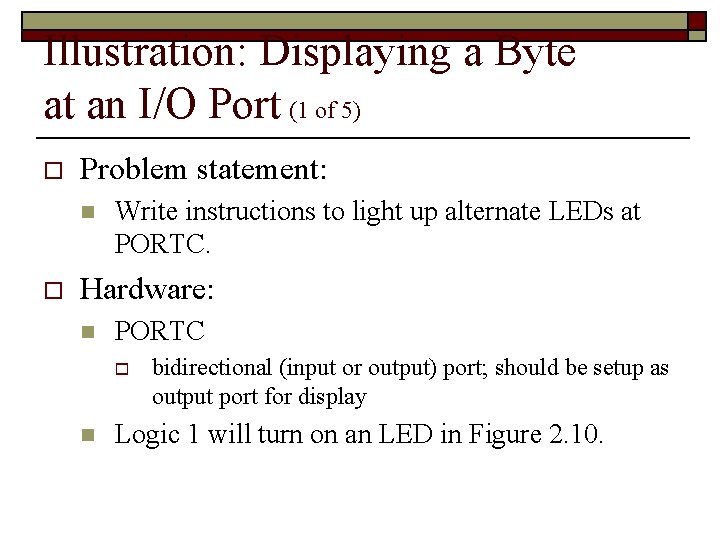

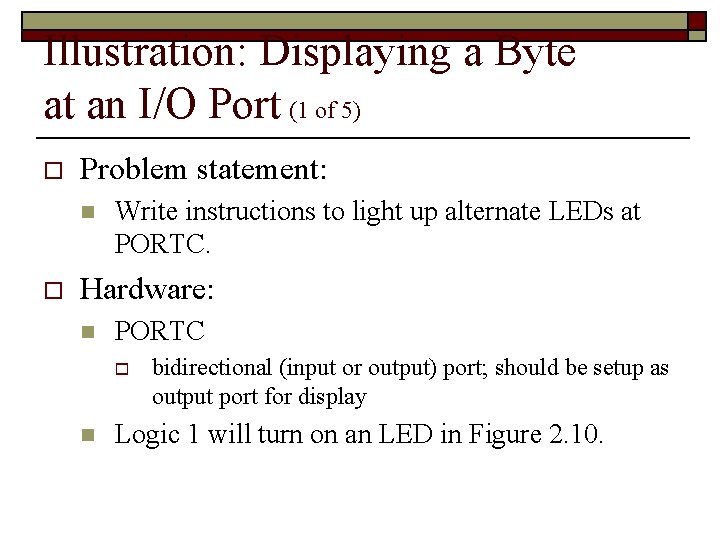

Illustration: Displaying a Byte at an I/O Port (1 of 5) o Problem statement: n o Write instructions to light up alternate LEDs at PORTC. Hardware: n PORTC o n bidirectional (input or output) port; should be setup as output port for display Logic 1 will turn on an LED in Figure 2. 10.

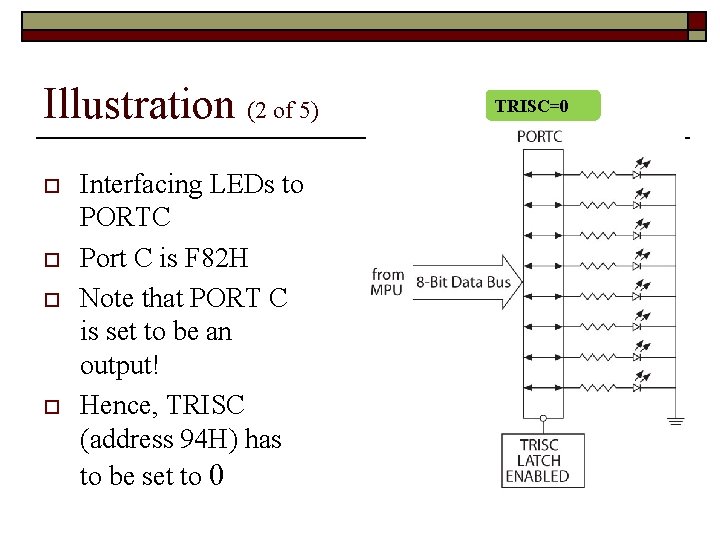

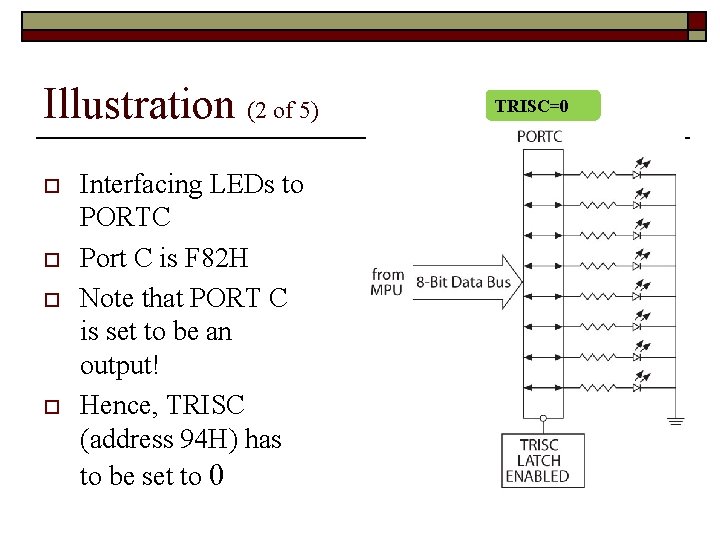

Illustration (2 of 5) o o Interfacing LEDs to PORTC Port C is F 82 H Note that PORT C is set to be an output! Hence, TRISC (address 94 H) has to be set to 0 TRISC=0

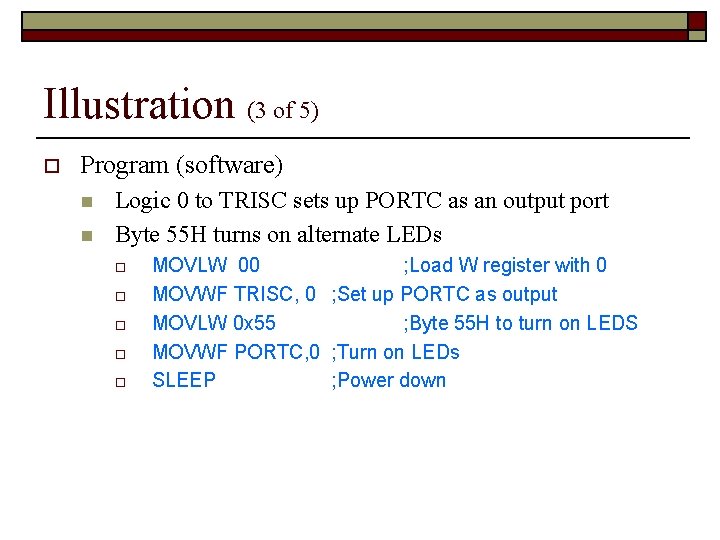

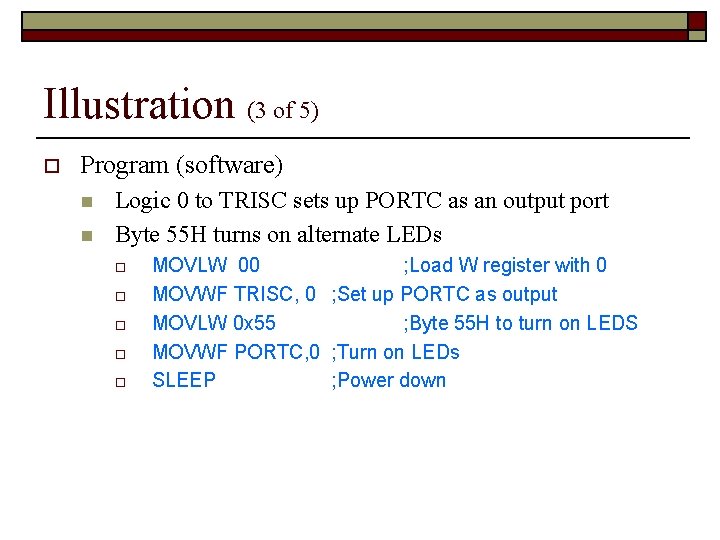

Illustration (3 of 5) o Program (software) n n Logic 0 to TRISC sets up PORTC as an output port Byte 55 H turns on alternate LEDs o o o MOVLW 00 ; Load W register with 0 MOVWF TRISC, 0 ; Set up PORTC as output MOVLW 0 x 55 ; Byte 55 H to turn on LEDS MOVWF PORTC, 0 ; Turn on LEDs SLEEP ; Power down

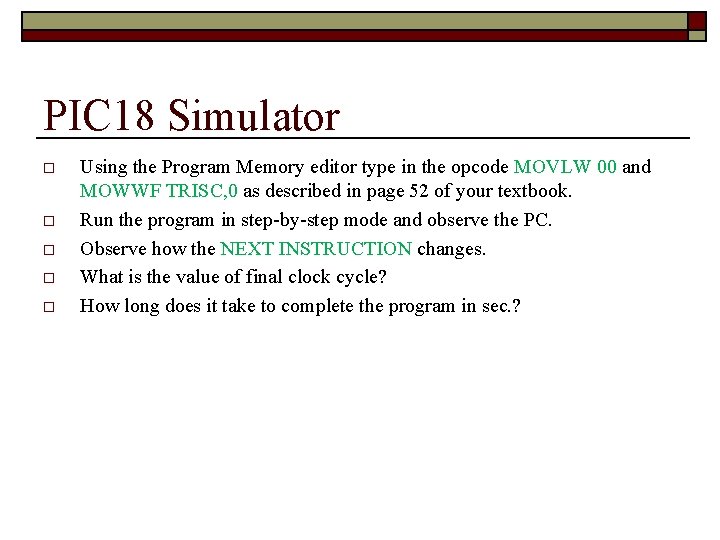

PIC 18 Simulator o o o Using the Program Memory editor type in the opcode MOVLW 00 and MOWWF TRISC, 0 as described in page 52 of your textbook. Run the program in step-by-step mode and observe the PC. Observe how the NEXT INSTRUCTION changes. What is the value of final clock cycle? How long does it take to complete the program in sec. ?

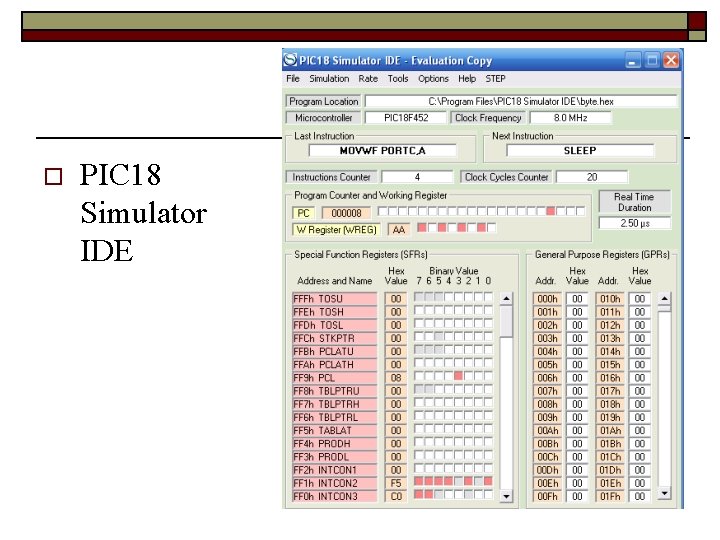

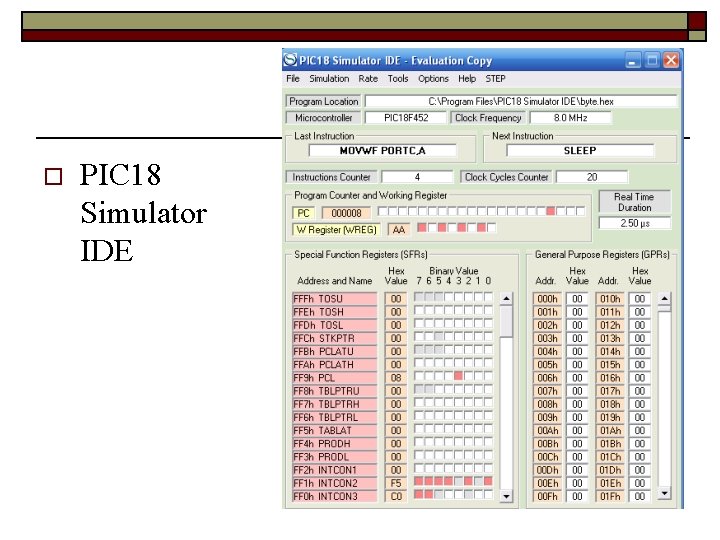

o PIC 18 Simulator IDE

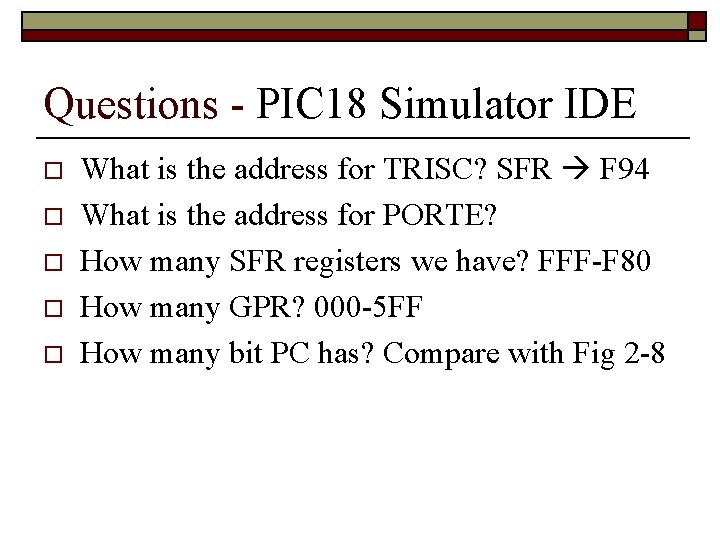

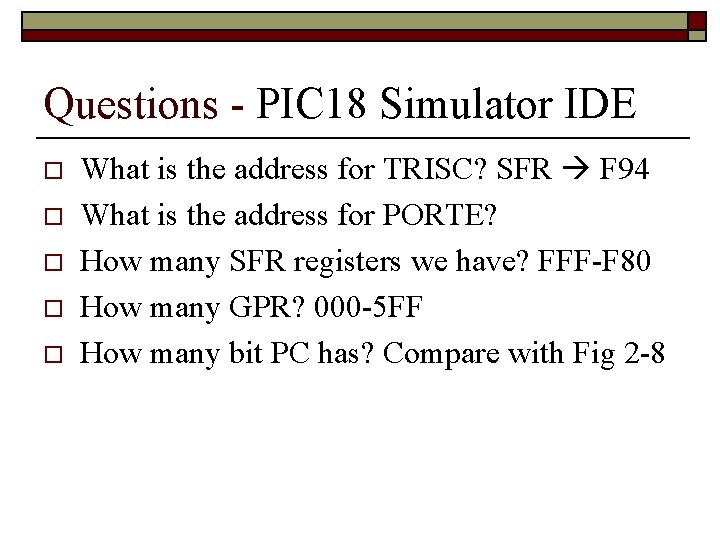

Questions - PIC 18 Simulator IDE o o o What is the address for TRISC? SFR F 94 What is the address for PORTE? How many SFR registers we have? FFF-F 80 How many GPR? 000 -5 FF How many bit PC has? Compare with Fig 2 -8

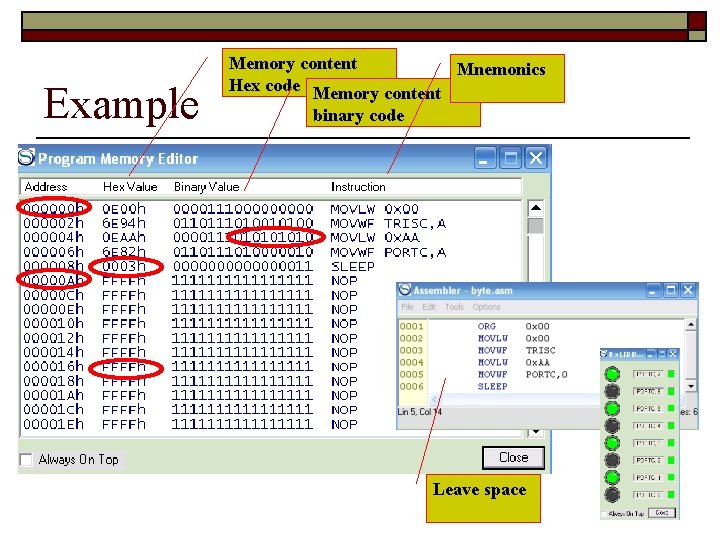

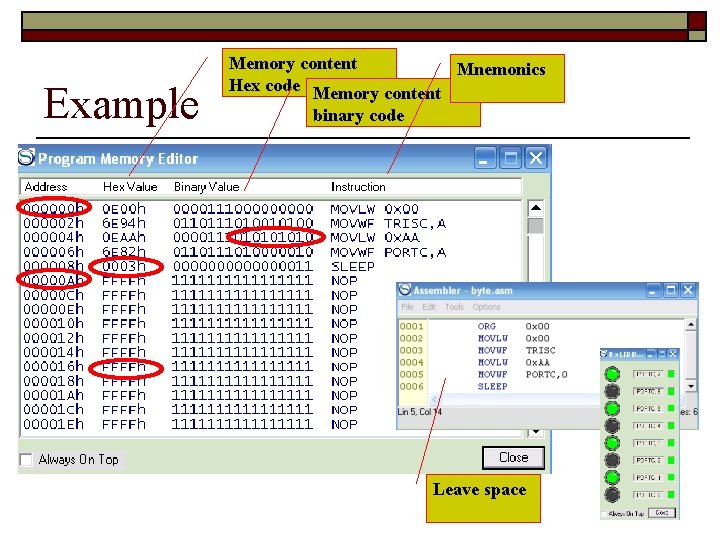

Example Memory content Mnemonics Hex code Memory content binary code Leave space

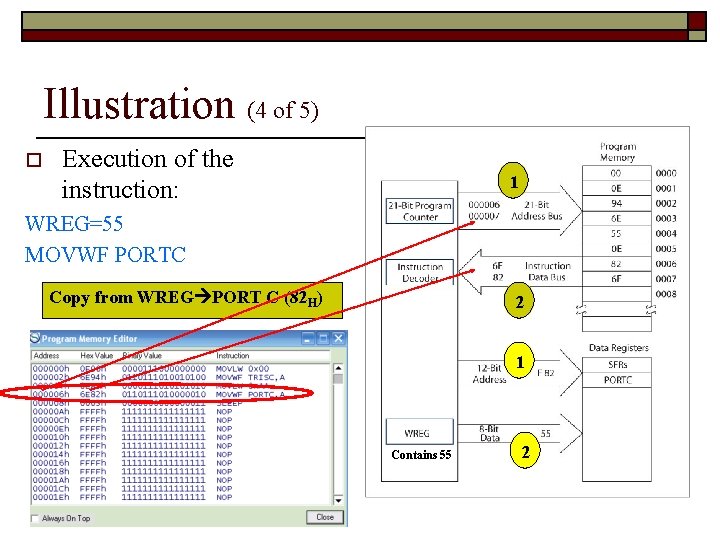

Illustration (4 of 5) o Execution of the instruction: 1 WREG=55 MOVWF PORTC Copy from WREG PORT C (82 H) 2 1 Contains 55 2