Chapter 2 Interconnect Analysis Delay Modeling Prof Lei

![Homework [1] Given the circuit as shown below and a unit step voltage source Homework [1] Given the circuit as shown below and a unit step voltage source](https://slidetodoc.com/presentation_image/2fda687b0af68e64c24edf706a5d900e/image-39.jpg)

![Homework [2] Give the circuit as shown below and a unit step voltage source Homework [2] Give the circuit as shown below and a unit step voltage source](https://slidetodoc.com/presentation_image/2fda687b0af68e64c24edf706a5d900e/image-40.jpg)

![Homework 2 [3] Modify the PRIMA code with single frequency expansion to multiple points Homework 2 [3] Modify the PRIMA code with single frequency expansion to multiple points](https://slidetodoc.com/presentation_image/2fda687b0af68e64c24edf706a5d900e/image-44.jpg)

- Slides: 56

Chapter 2 Interconnect Analysis Delay Modeling Prof. Lei He Electrical Engineering Department University of California, Los Angeles URL: eda. ee. ucla. edu Email: lhe@ee. ucla. edu 1

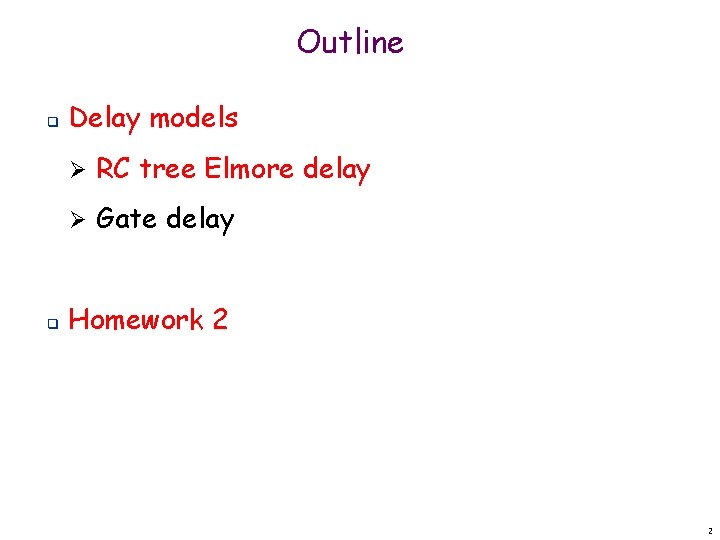

Outline q q Delay models Ø RC tree Elmore delay Ø Gate delay Homework 2 2

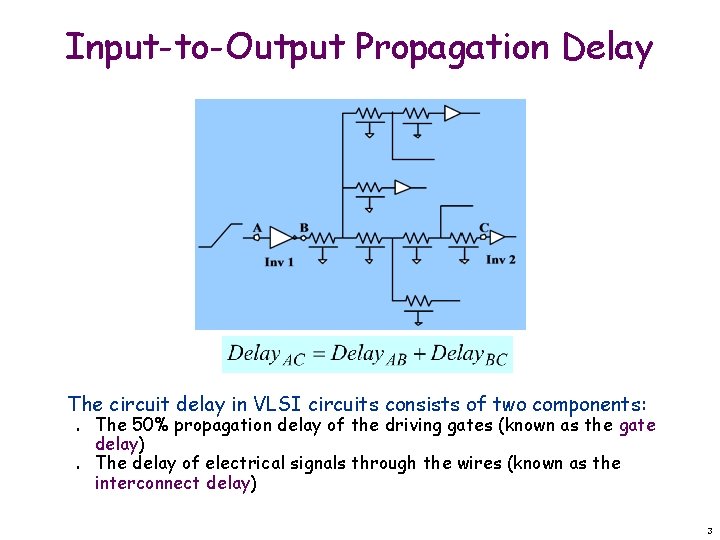

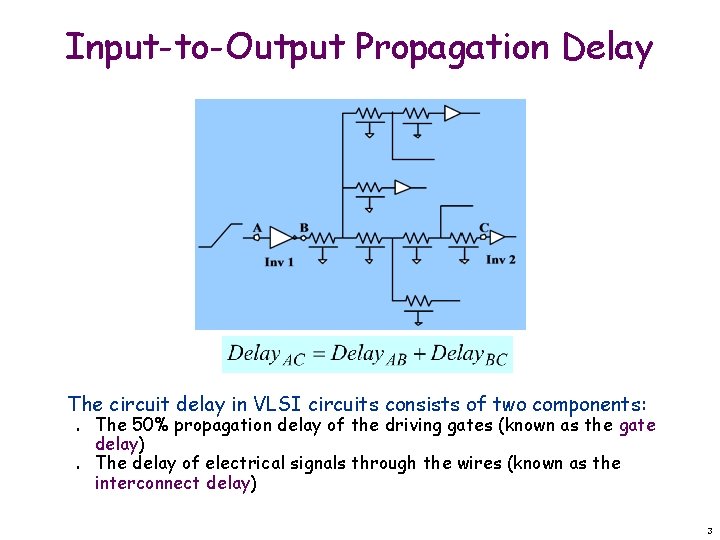

Input-to-Output Propagation Delay The circuit delay in VLSI circuits consists of two components: n n The 50% propagation delay of the driving gates (known as the gate delay) The delay of electrical signals through the wires (known as the interconnect delay) 3

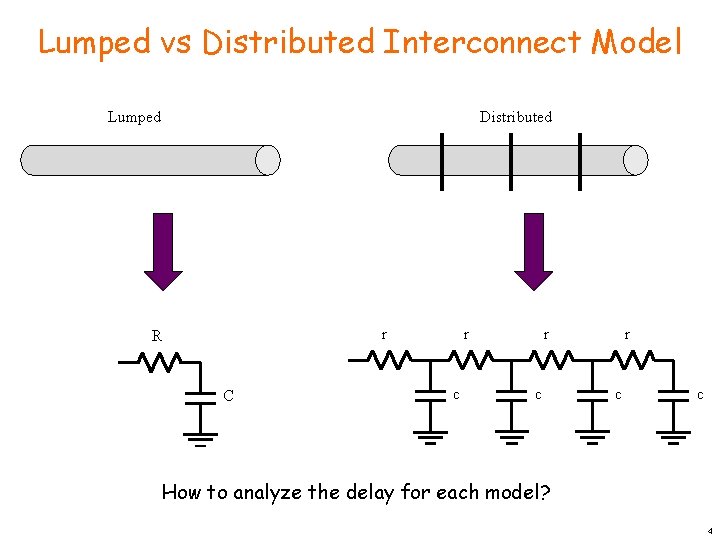

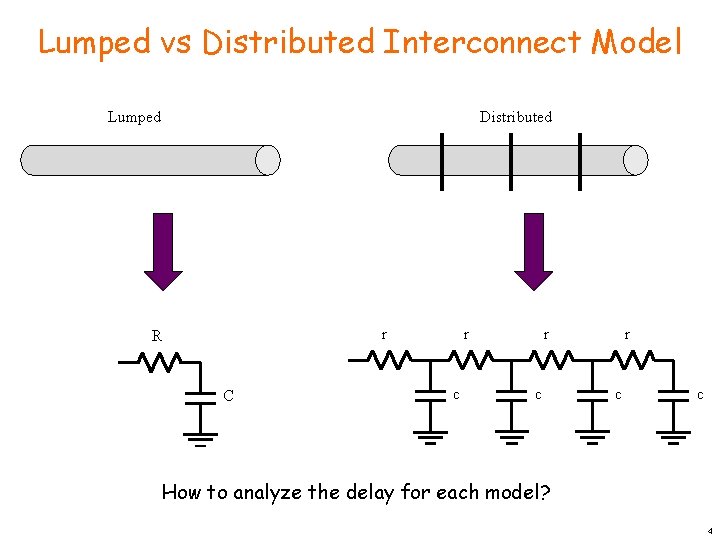

Lumped vs Distributed Interconnect Model Lumped Distributed r r R C c r c c How to analyze the delay for each model? 4

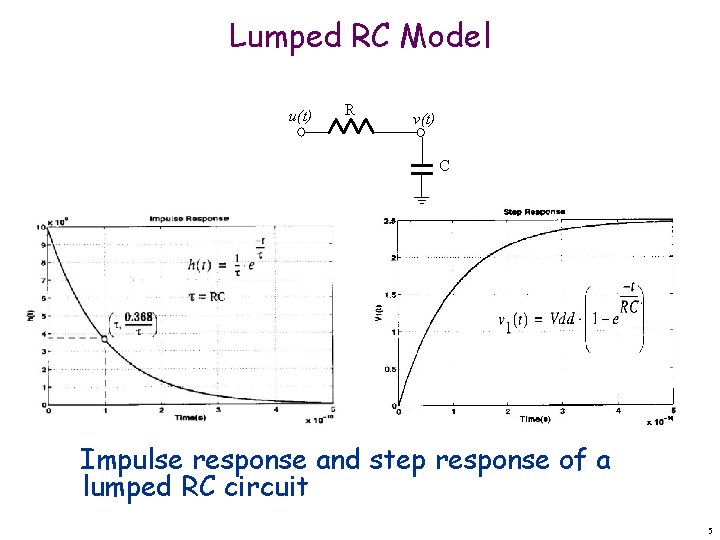

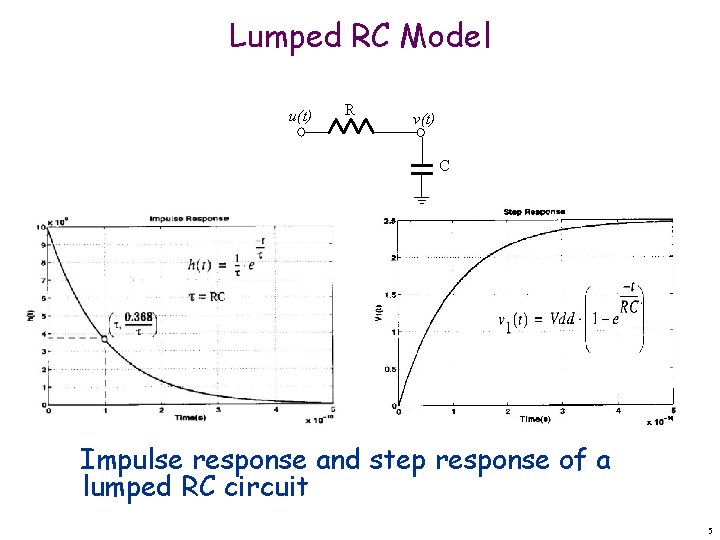

Lumped RC Model u(t) R v(t) C Impulse response and step response of a lumped RC circuit 5

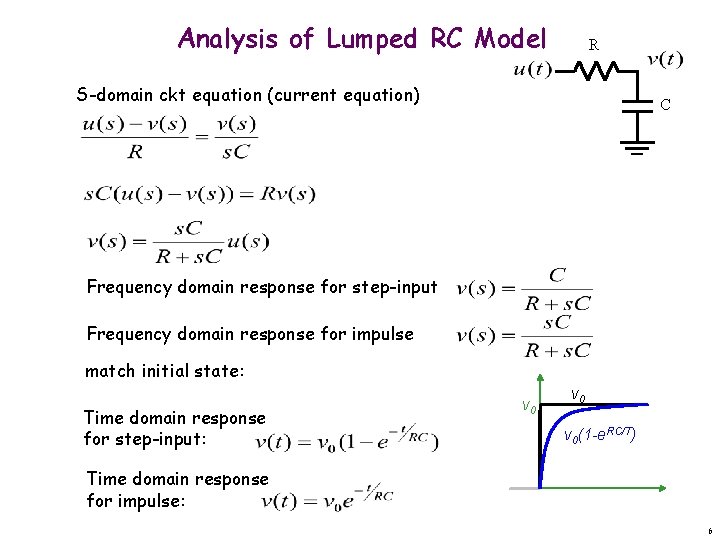

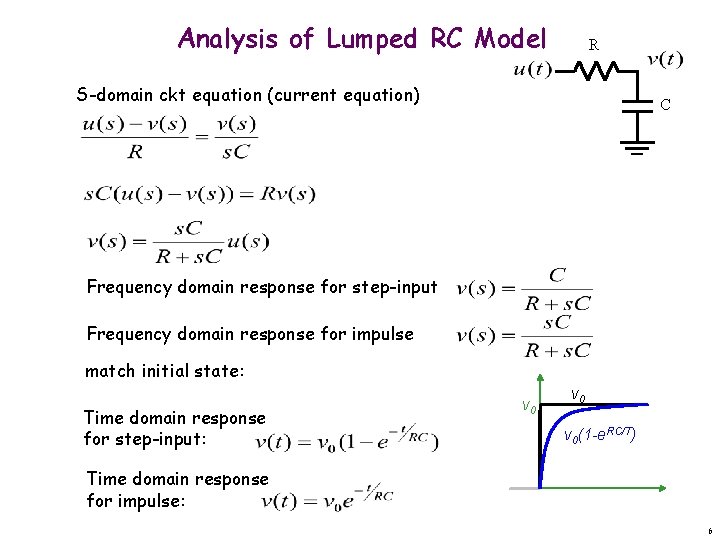

Analysis of Lumped RC Model R S-domain ckt equation (current equation) C Frequency domain response for step-input Frequency domain response for impulse match initial state: Time domain response for step-input: v 0 v 0(1 -e. RC/T) Time domain response for impulse: 6

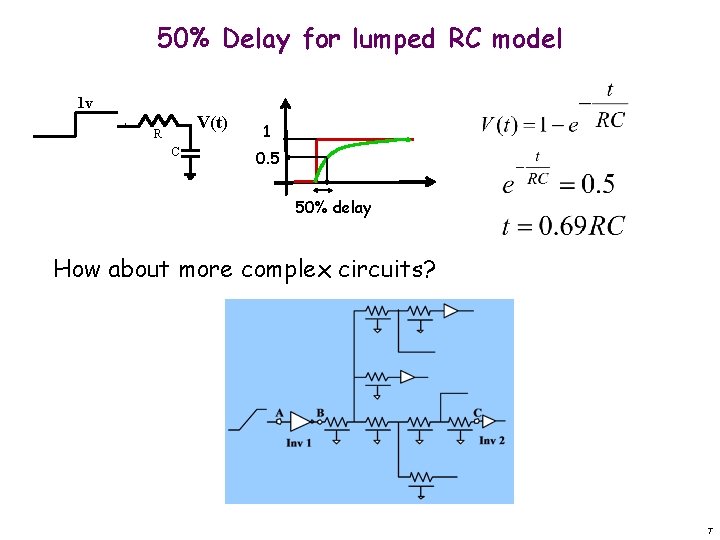

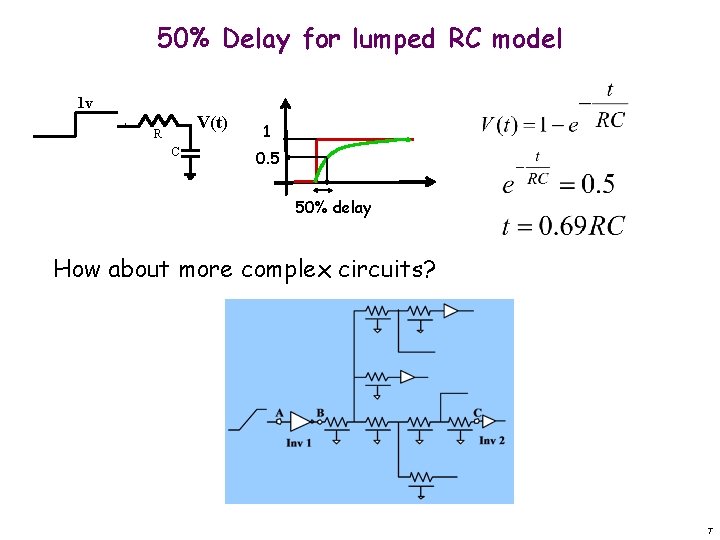

50% Delay for lumped RC model 1 v V(t) R C 1 0. 5 50% delay How about more complex circuits? 7

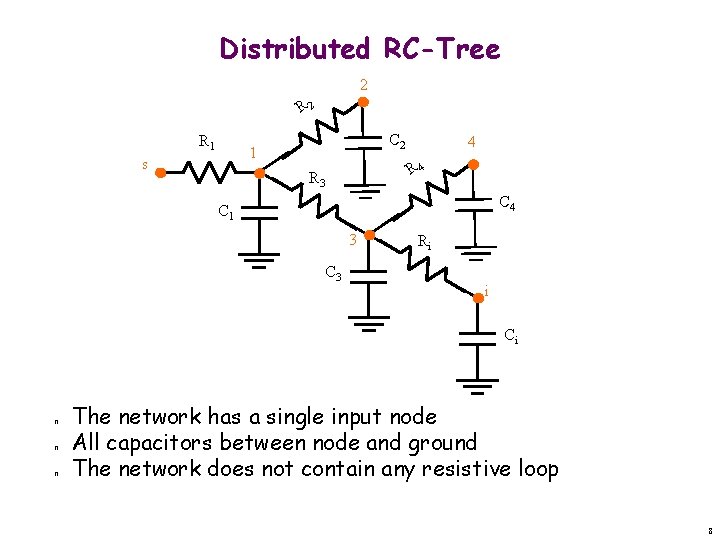

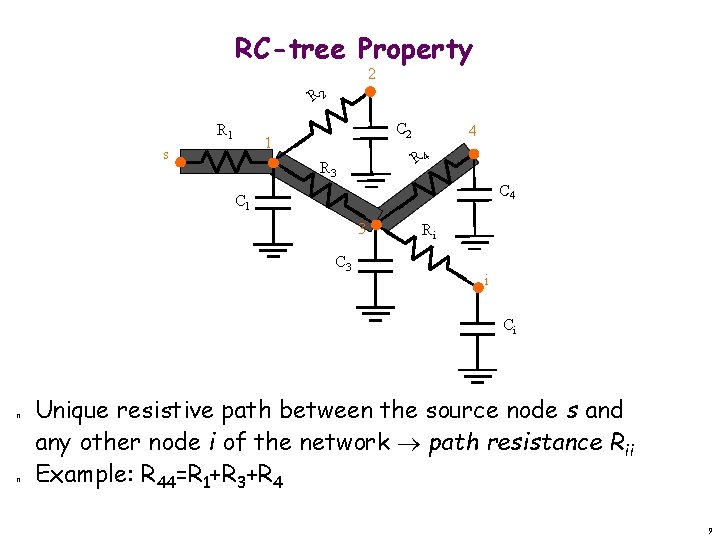

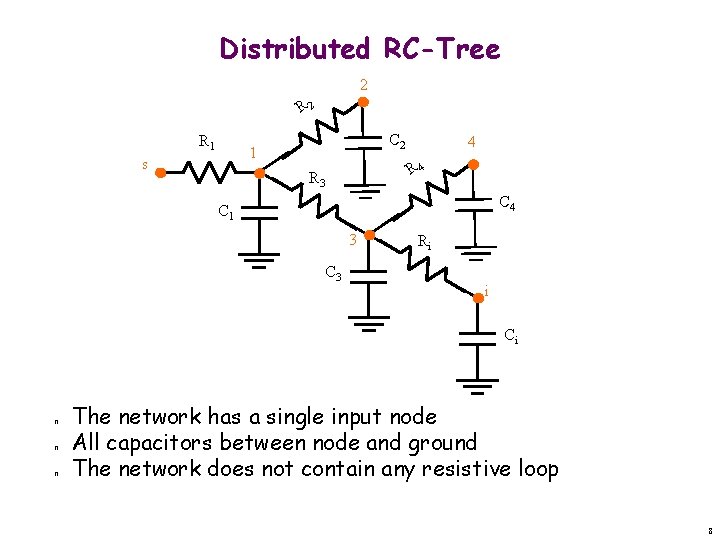

Distributed RC-Tree 2 R 1 C 2 1 s 4 R 3 C 4 C 1 3 C 3 Ri i Ci n n n The network has a single input node All capacitors between node and ground The network does not contain any resistive loop 8

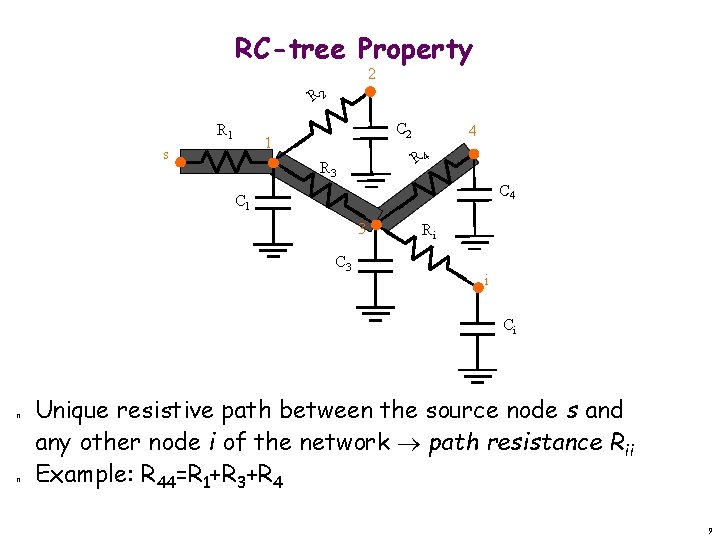

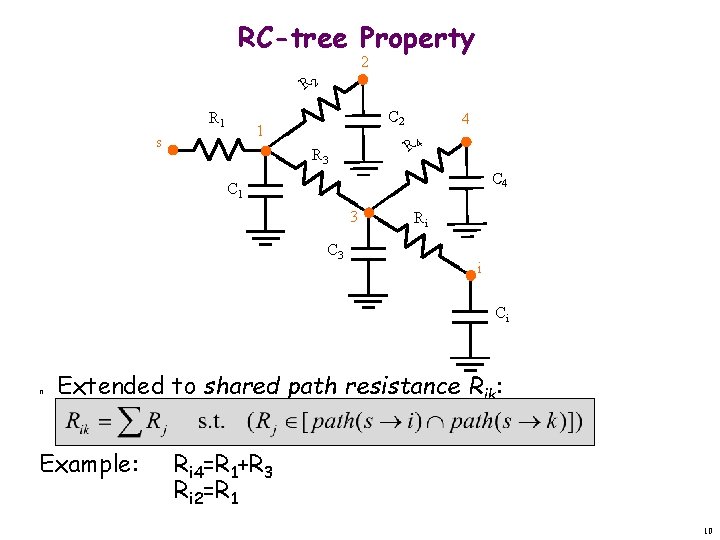

RC-tree Property 2 R 1 C 2 1 s 4 R 3 C 4 C 1 3 C 3 Ri i Ci n n Unique resistive path between the source node s and any other node i of the network path resistance Rii Example: R 44=R 1+R 3+R 4 9

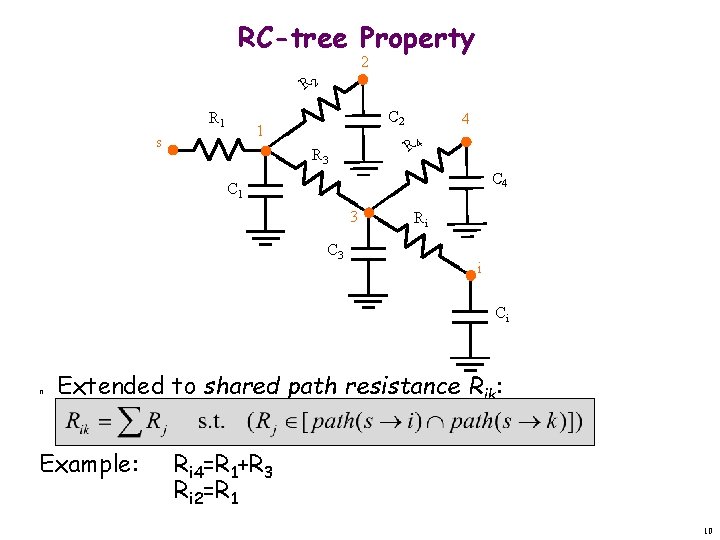

RC-tree Property 2 R 1 C 2 1 s 4 R 3 C 4 C 1 3 C 3 Ri i Ci n Extended to shared path resistance Rik: Example: Ri 4=R 1+R 3 Ri 2=R 1 10

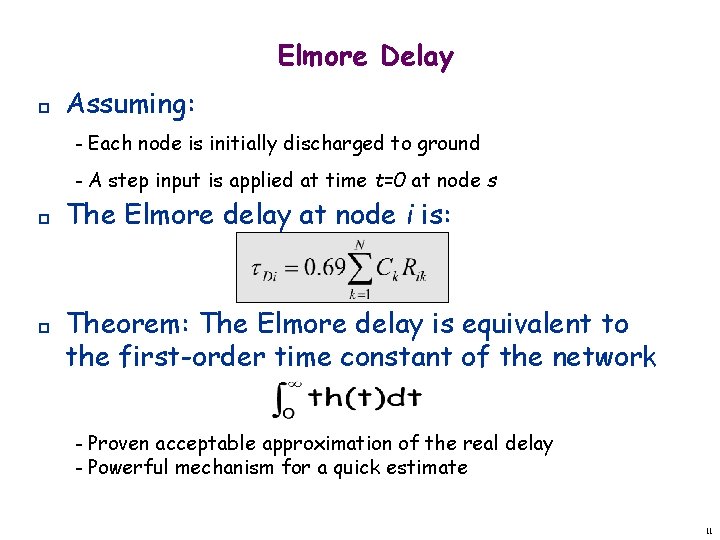

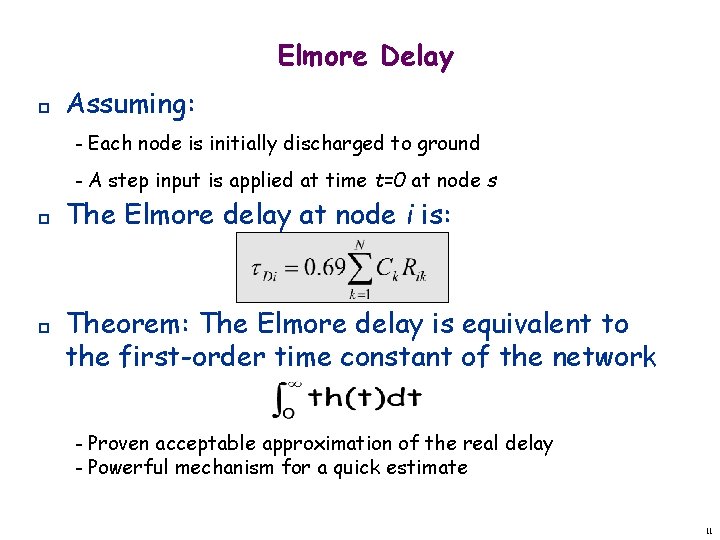

Elmore Delay p p p Assuming: – Each node is initially discharged to ground – A step input is applied at time t=0 at node s The Elmore delay at node i is: Theorem: The Elmore delay is equivalent to the first-order time constant of the network – – Proven acceptable approximation of the real delay Powerful mechanism for a quick estimate 11

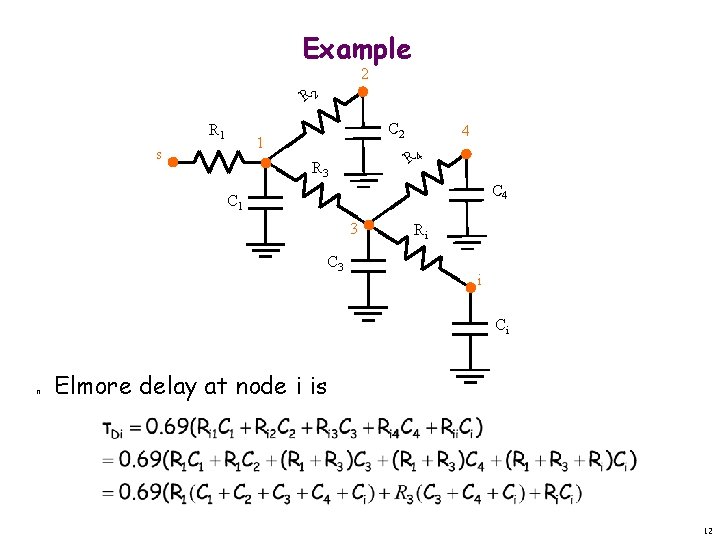

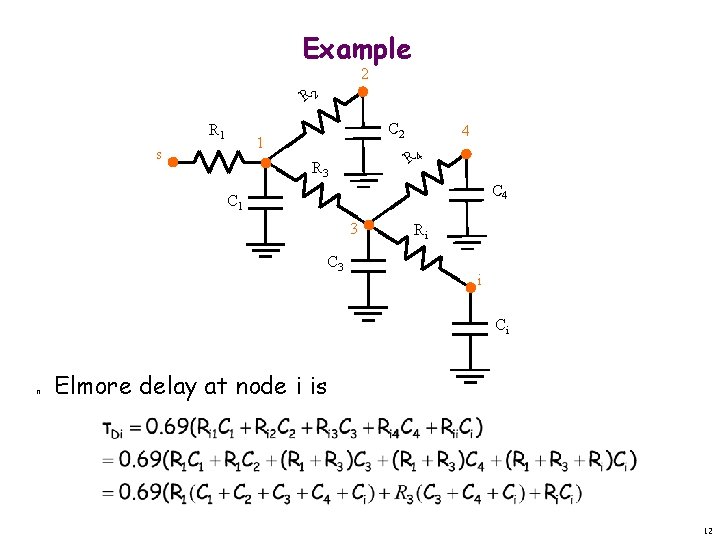

Example 2 R 1 C 2 1 s 4 R 3 C 4 C 1 3 C 3 Ri i Ci n Elmore delay at node i is 12

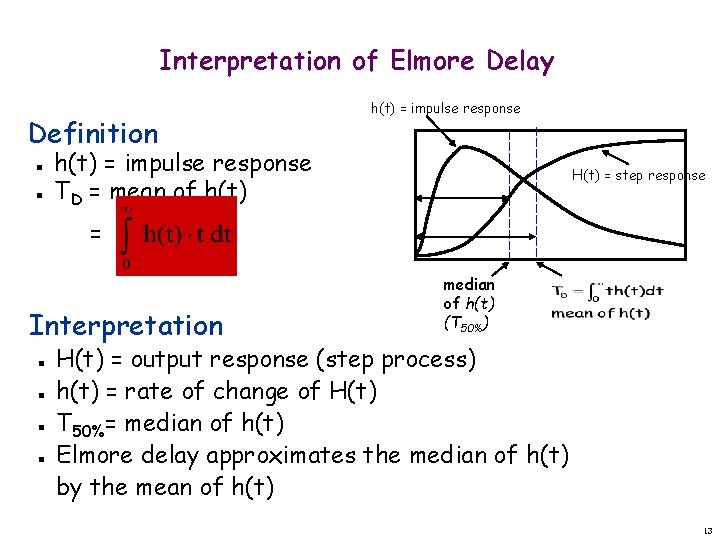

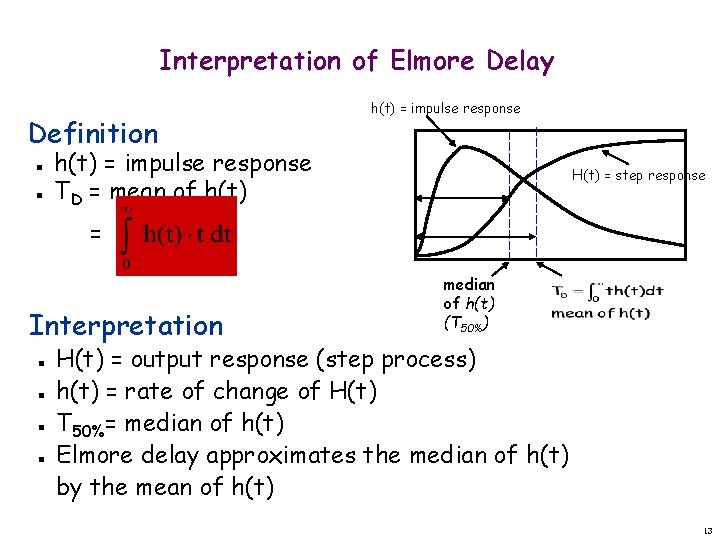

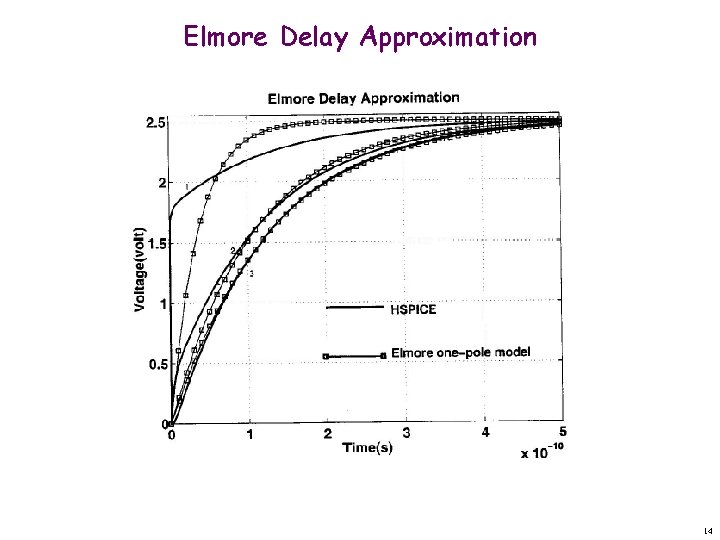

Interpretation of Elmore Delay Definition n n h(t) = impulse response TD = mean of h(t) H(t) = step response = Interpretation n n median of h(t) (T 50%) H(t) = output response (step process) h(t) = rate of change of H(t) T 50%= median of h(t) Elmore delay approximates the median of h(t) by the mean of h(t) 13

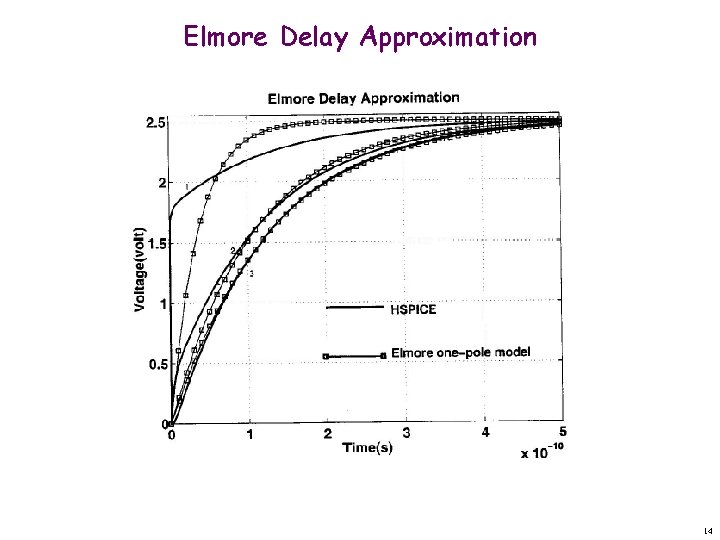

Elmore Delay Approximation 14

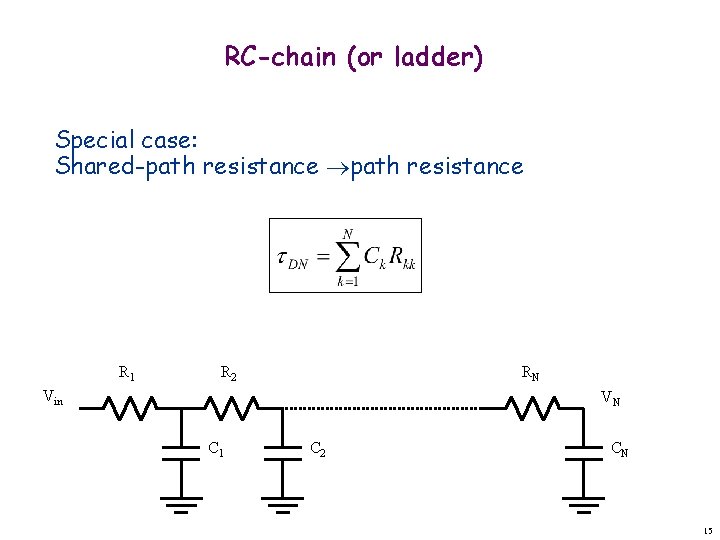

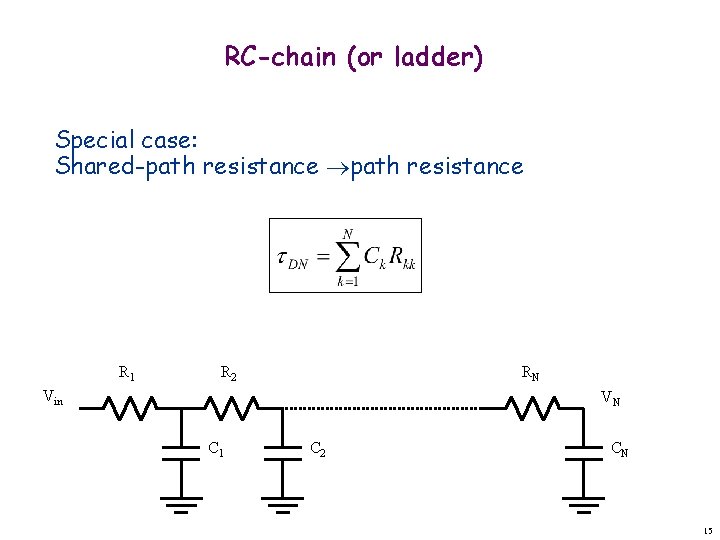

RC-chain (or ladder) Special case: Shared-path resistance R 1 R 2 RN Vin VN C 1 C 2 CN 15

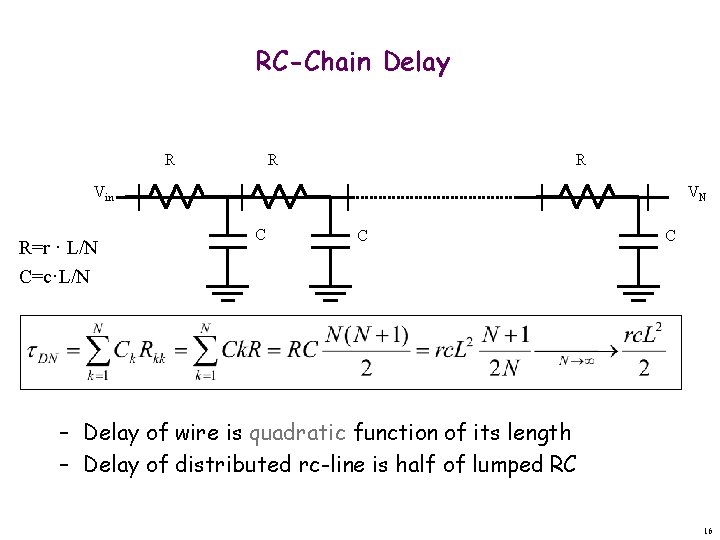

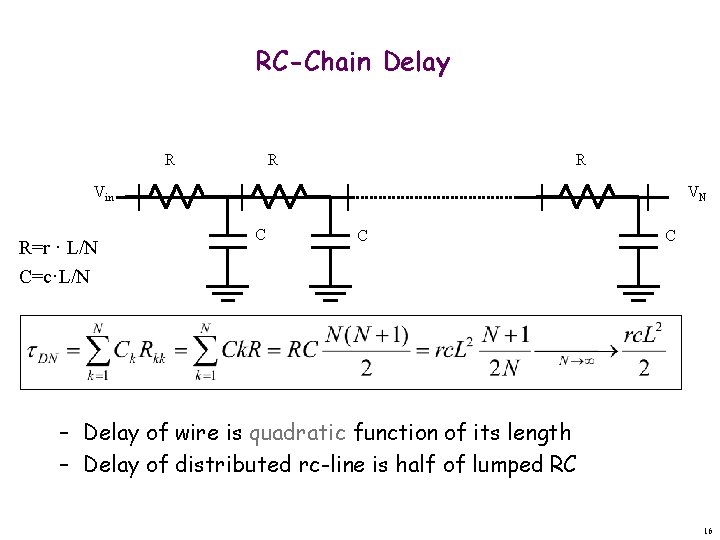

RC-Chain Delay R R R VN Vin R=r · L/N C=c·L/N C C C – Delay of wire is quadratic function of its length – Delay of distributed rc-line is half of lumped RC 16

Outline q Delay models Ø RC tree Elmore delay Ø Gate delay 17

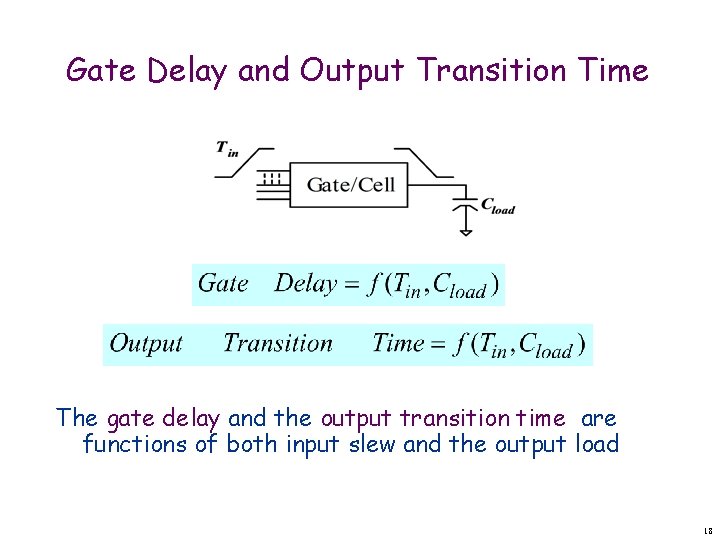

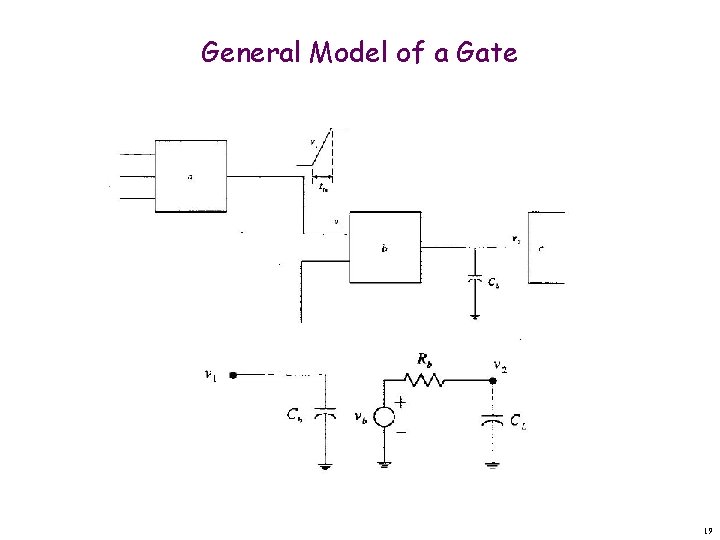

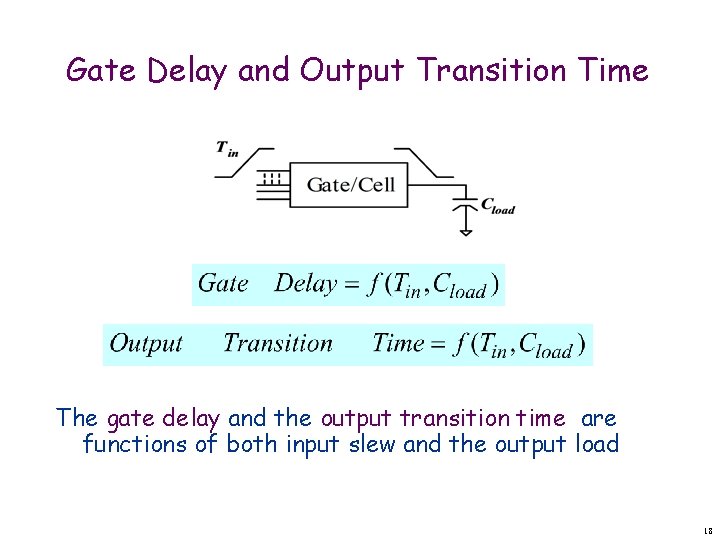

Gate Delay and Output Transition Time The gate delay and the output transition time are functions of both input slew and the output load 18

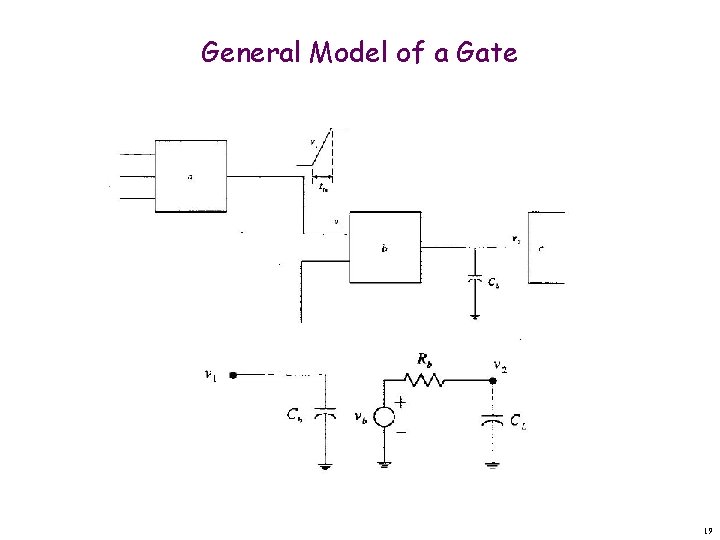

General Model of a Gate 19

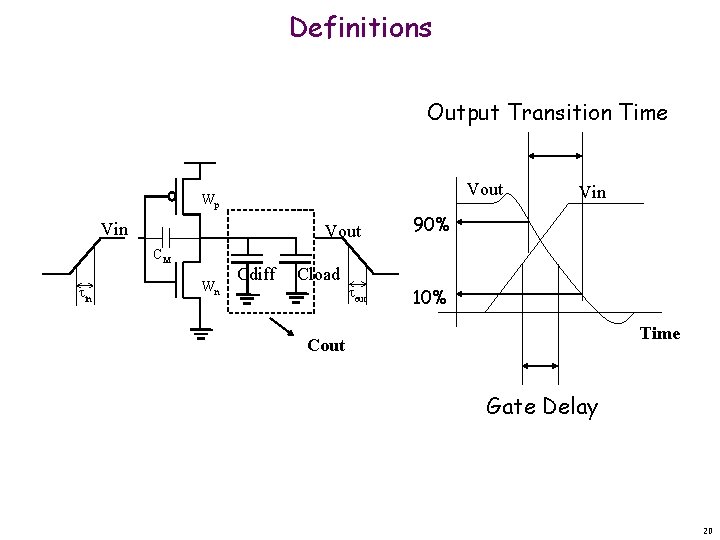

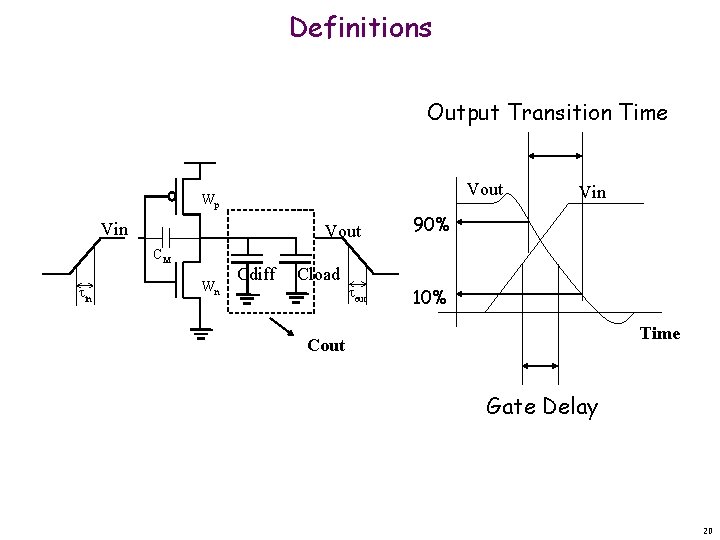

Definitions Output Transition Time Vout Wp Vin Vout CM tin Wn Cdiff Cload tout Vin 90% 10% Time Cout Gate Delay 20

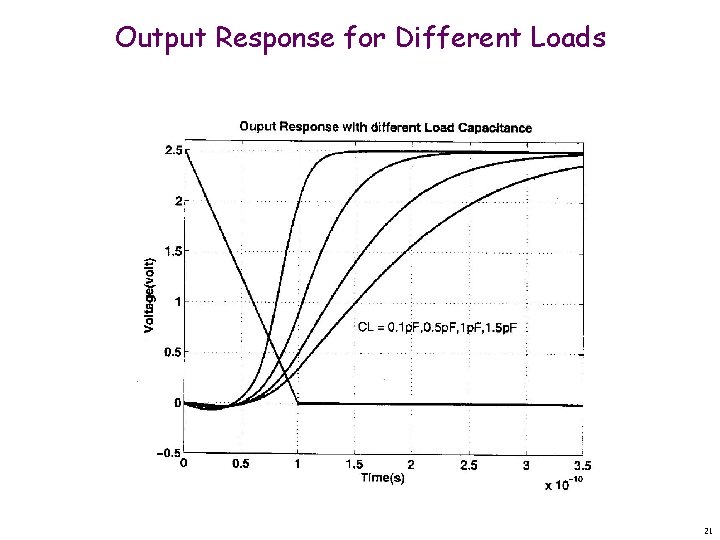

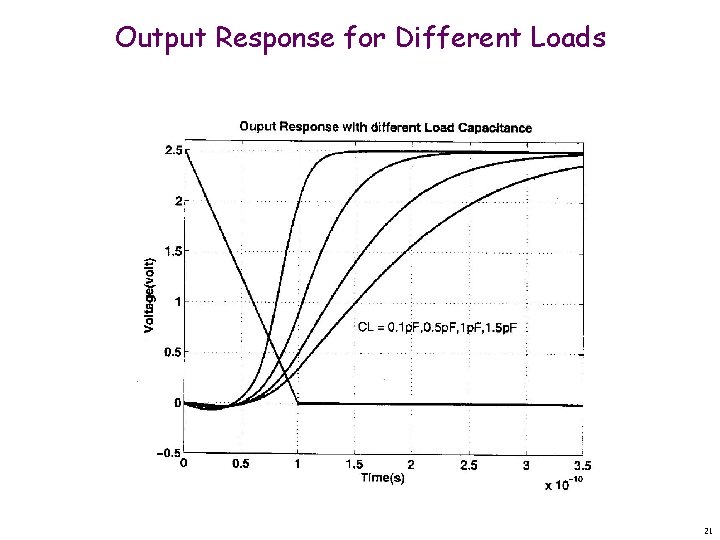

Output Response for Different Loads 21

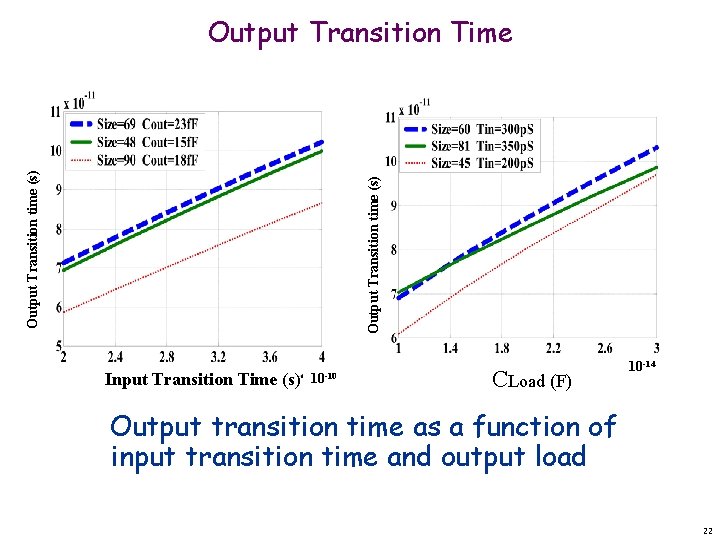

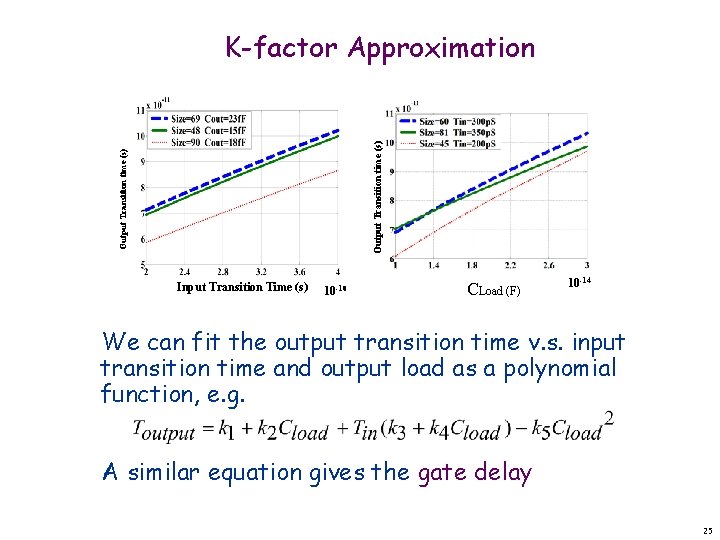

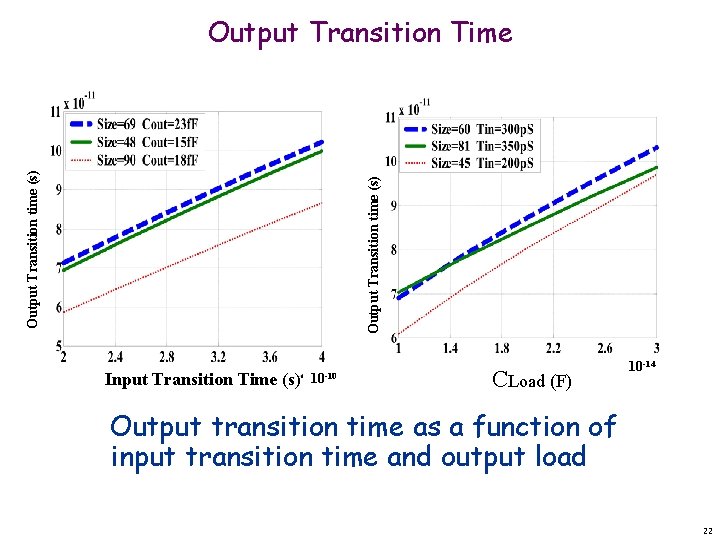

Output Transition time (s) Output Transition Time Input Transition Time (s) 10 -10 CLoad (F) 10 -14 Output transition time as a function of input transition time and output load 22

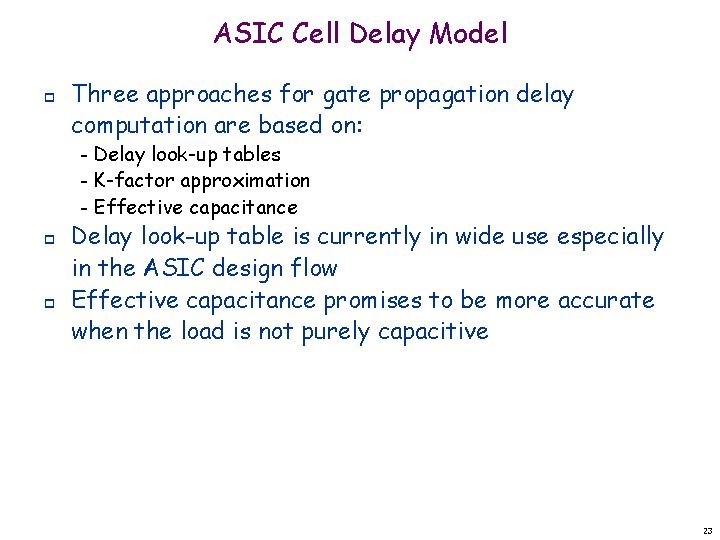

ASIC Cell Delay Model p Three approaches for gate propagation delay computation are based on: Delay look-up tables – K-factor approximation – Effective capacitance – p p Delay look-up table is currently in wide use especially in the ASIC design flow Effective capacitance promises to be more accurate when the load is not purely capacitive 23

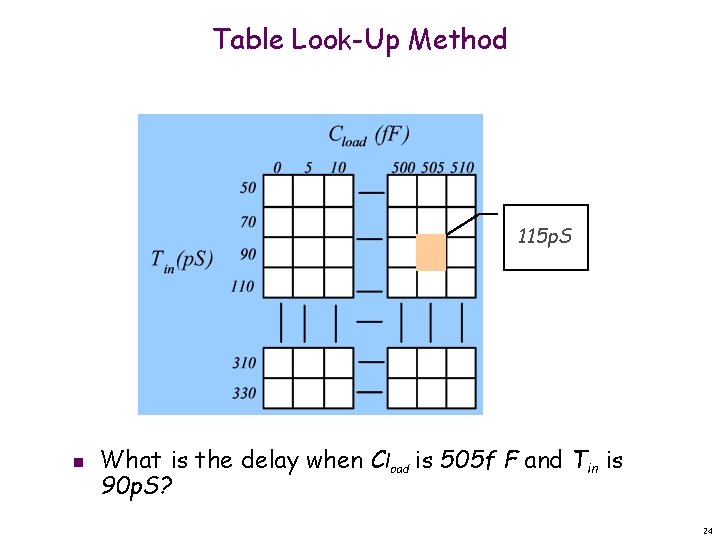

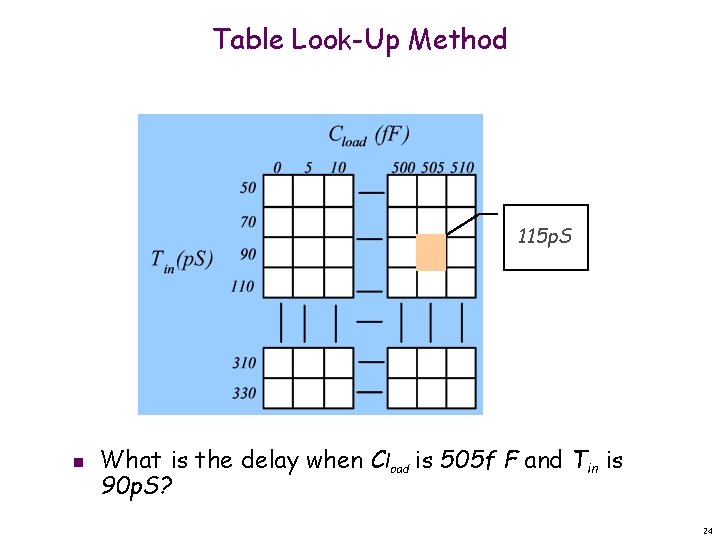

Table Look-Up Method 115 p. S n What is the delay when Cload is 505 f F and Tin is 90 p. S? 24

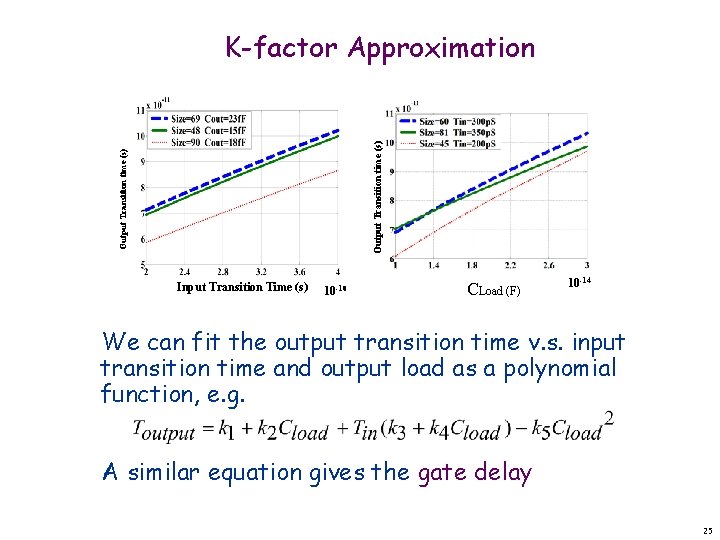

Output Transition time (s) K-factor Approximation Input Transition Time (s) 10 -10 CLoad (F) 10 -14 We can fit the output transition time v. s. input transition time and output load as a polynomial function, e. g. A similar equation gives the gate delay 25

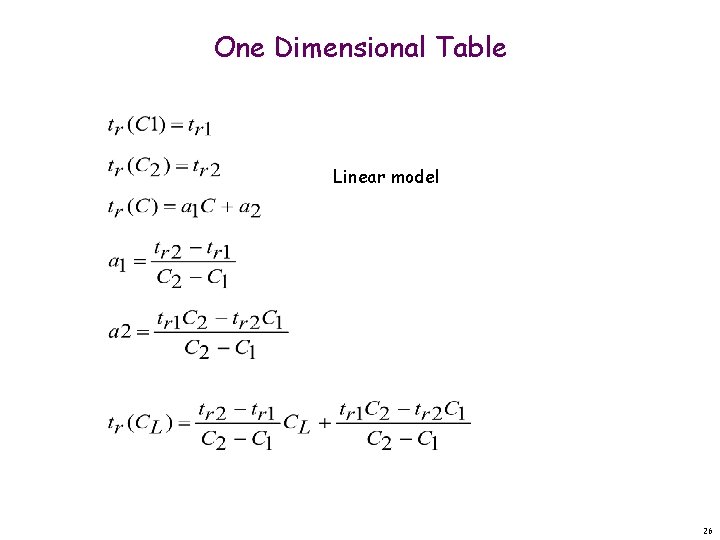

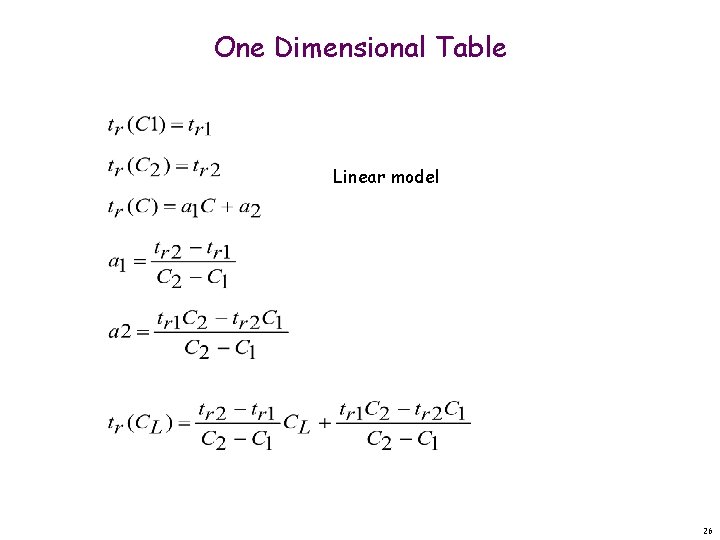

One Dimensional Table Linear model 26

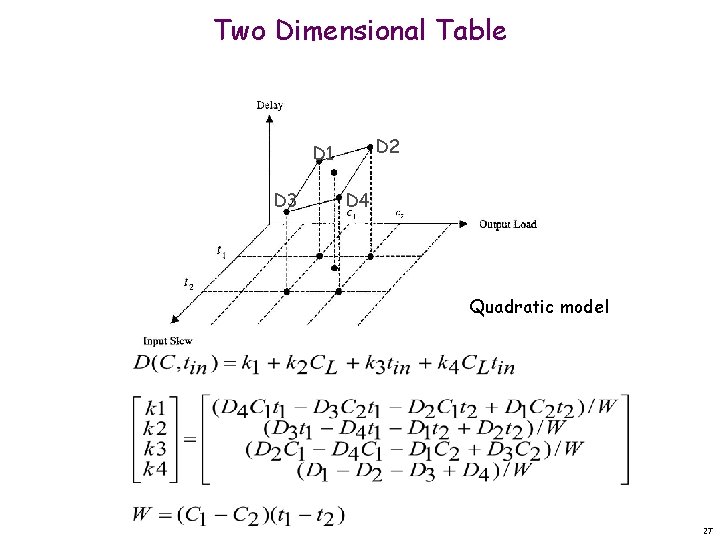

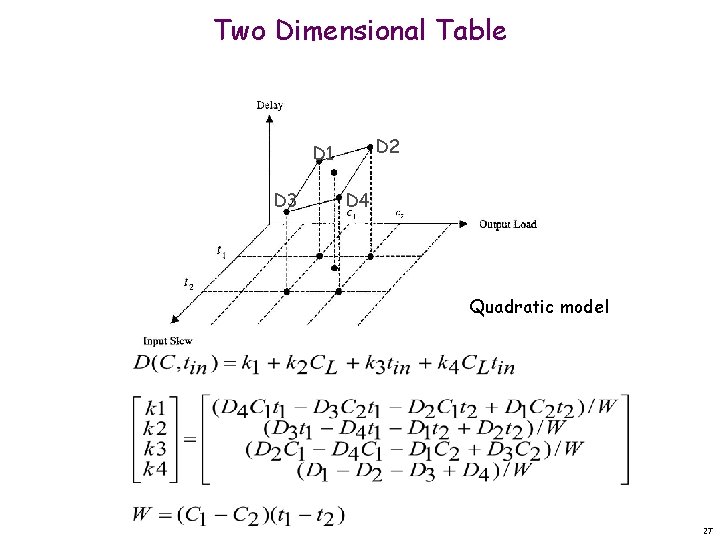

Two Dimensional Table D 2 D 1 D 3 D 4 Quadratic model 27

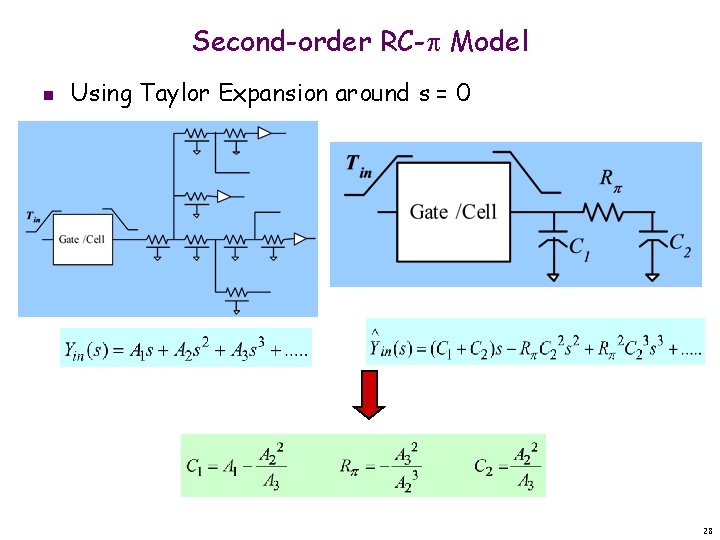

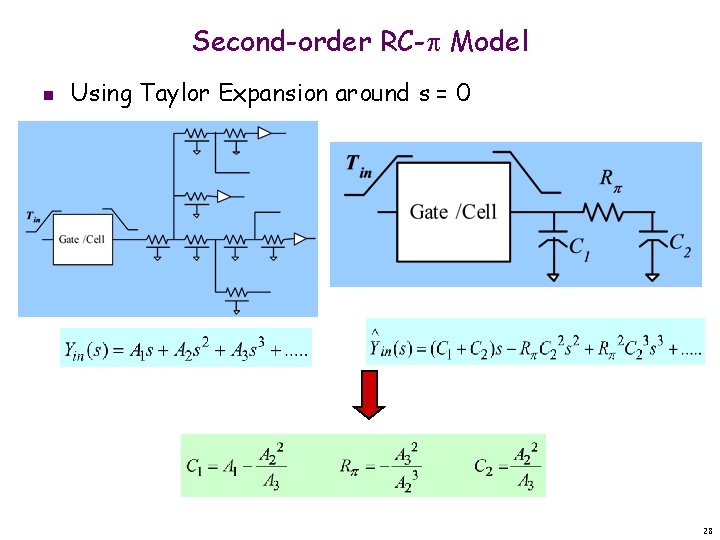

Second-order RC-p Model n Using Taylor Expansion around s = 0 28

Second-order RC-p Model (Cont’d) n n This equation requires creation of a fourdimensional table to achieve high accuracy This is however costly in terms of memory space and computational requirements 29

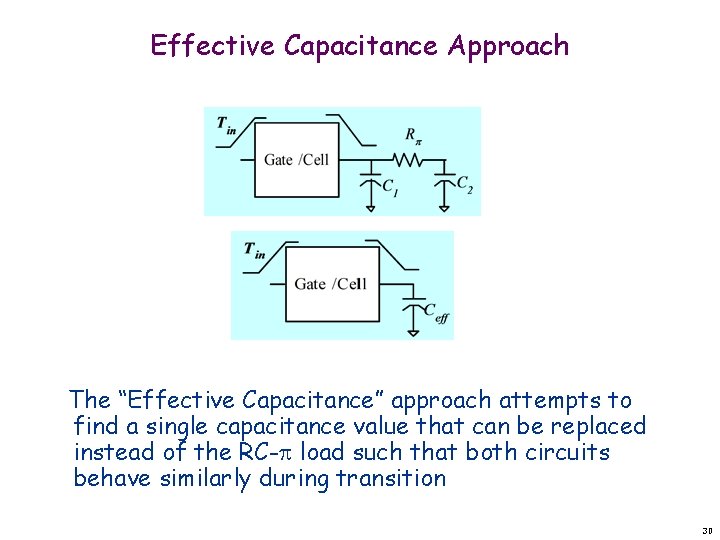

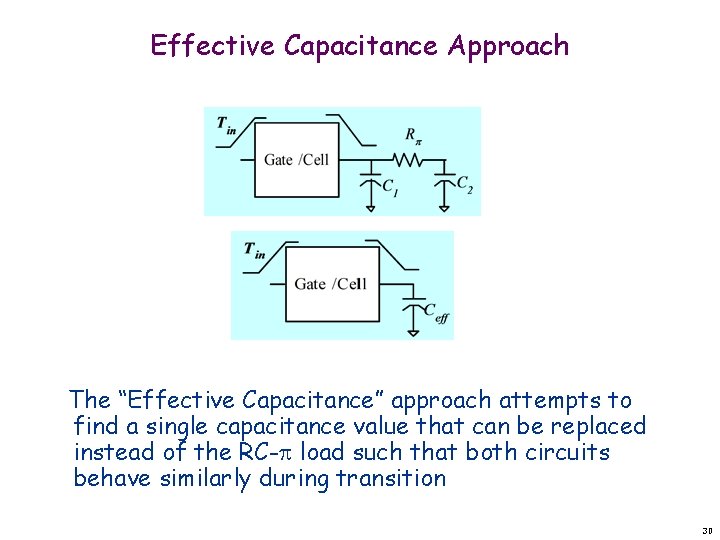

Effective Capacitance Approach The “Effective Capacitance” approach attempts to find a single capacitance value that can be replaced instead of the RC-p load such that both circuits behave similarly during transition 30

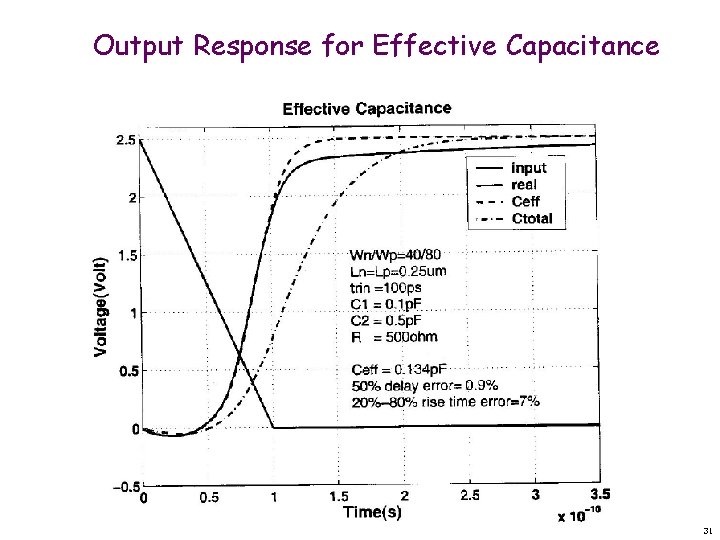

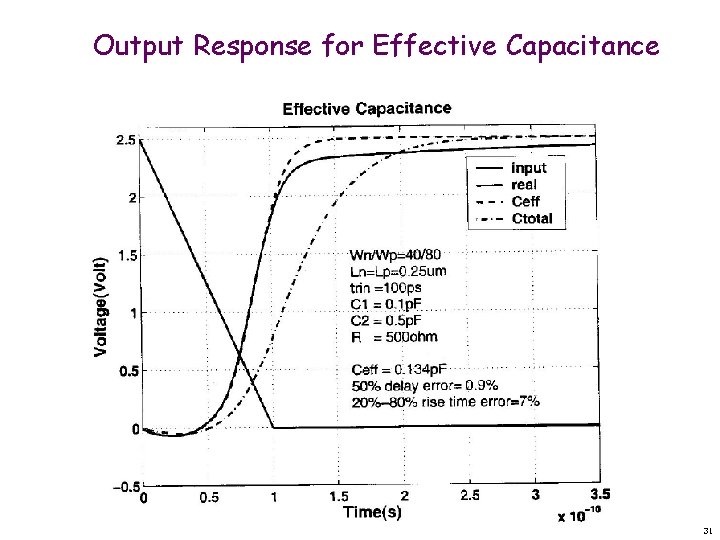

Output Response for Effective Capacitance 31

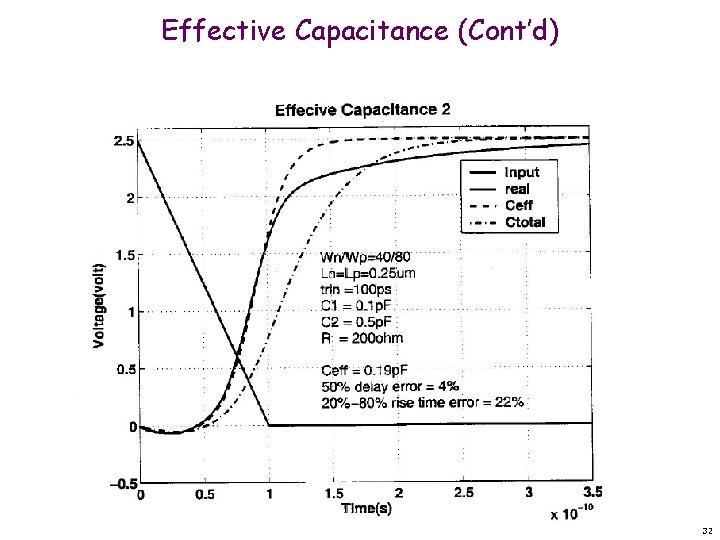

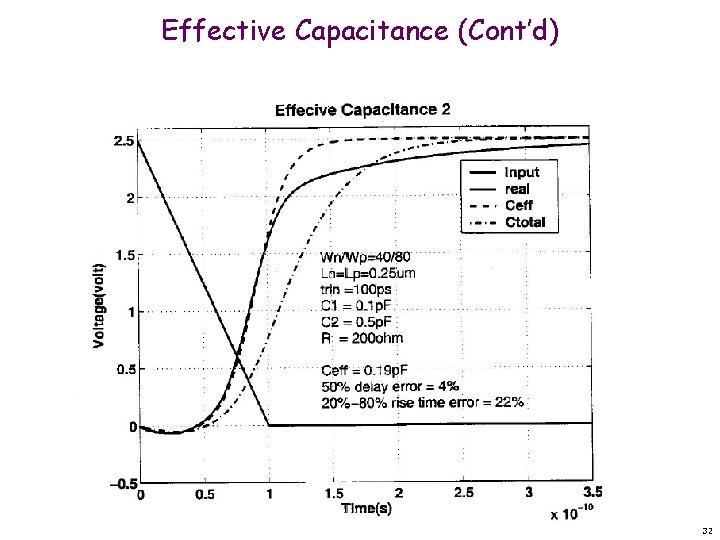

Effective Capacitance (Cont’d) 32

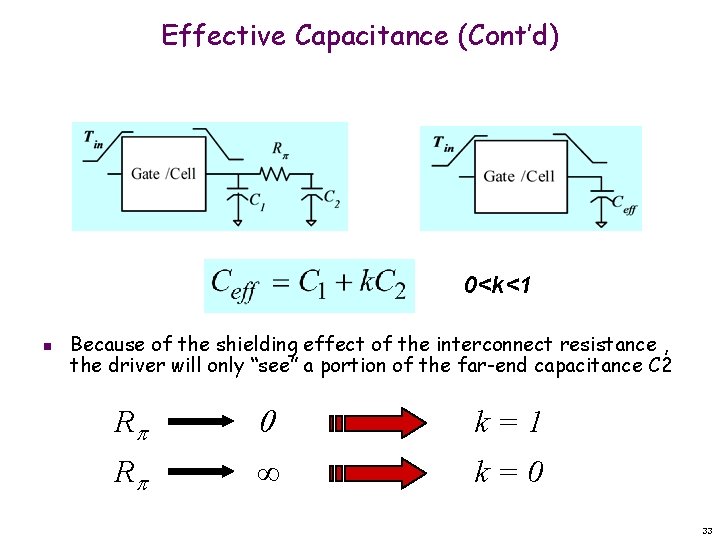

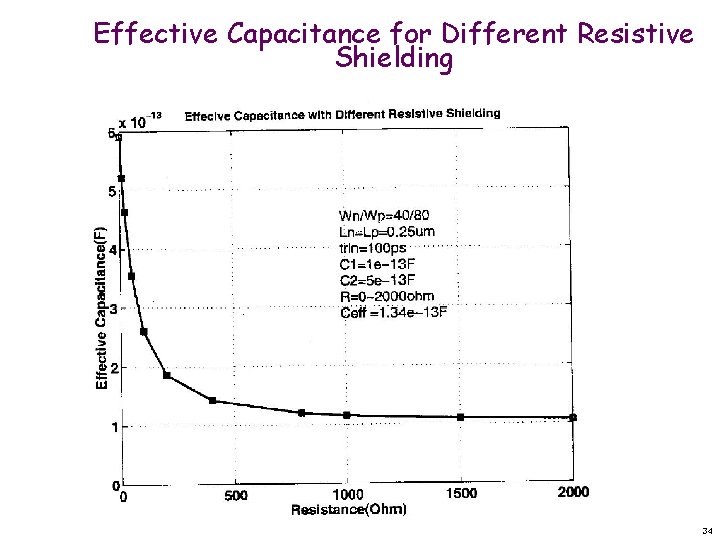

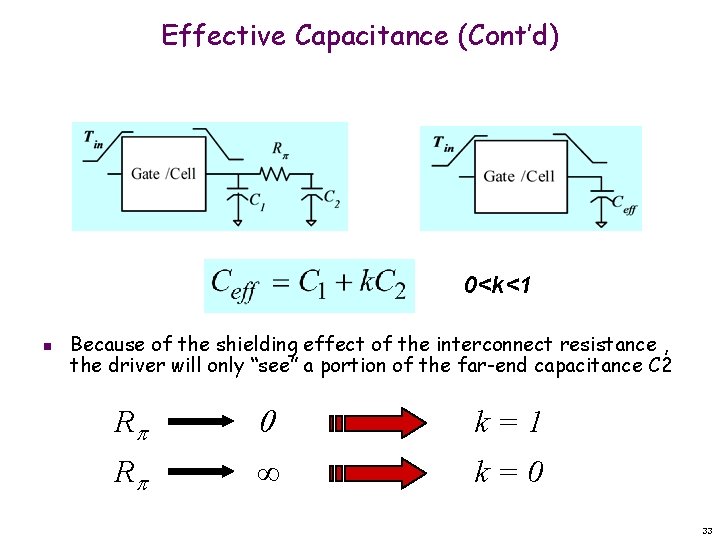

Effective Capacitance (Cont’d) 0<k<1 n Because of the shielding effect of the interconnect resistance , the driver will only “see” a portion of the far-end capacitance C 2 Rp 0 k=1 Rp ∞ k=0 33

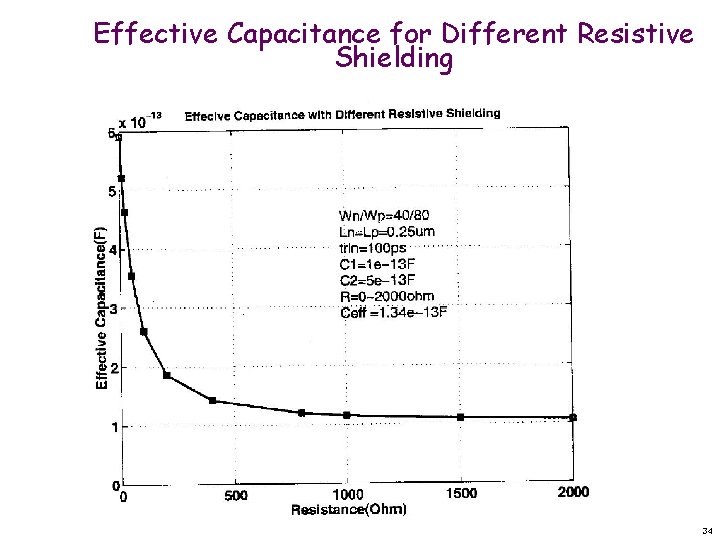

Effective Capacitance for Different Resistive Shielding 34

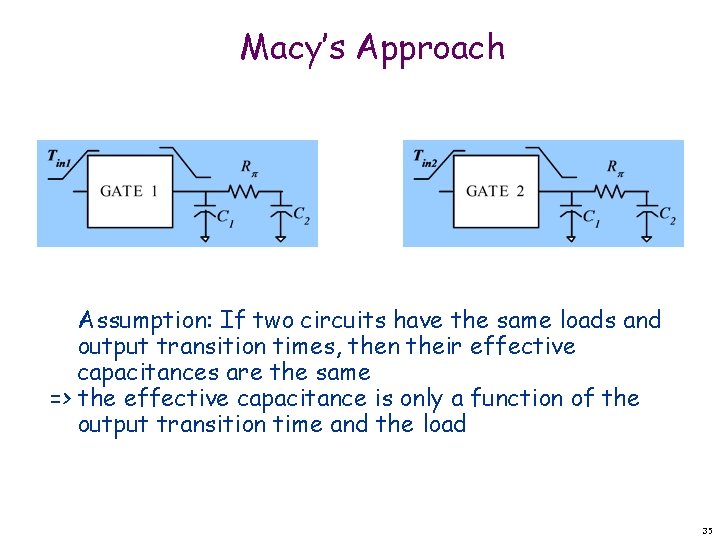

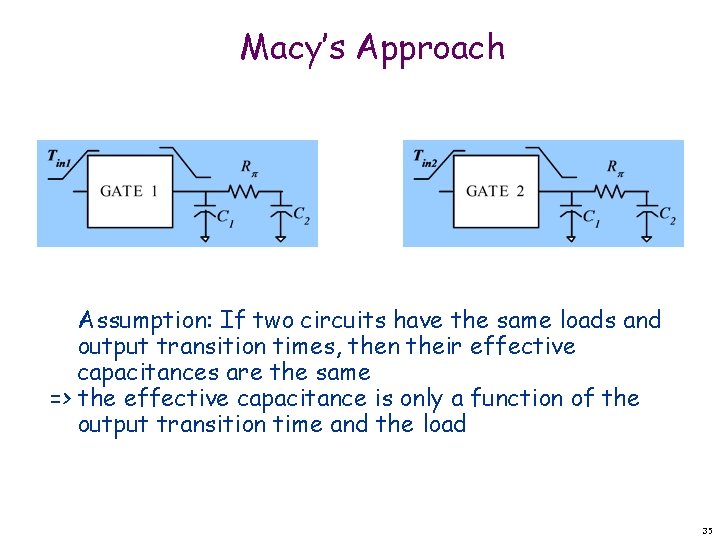

Macy’s Approach Assumption: If two circuits have the same loads and output transition times, then their effective capacitances are the same => the effective capacitance is only a function of the output transition time and the load 35

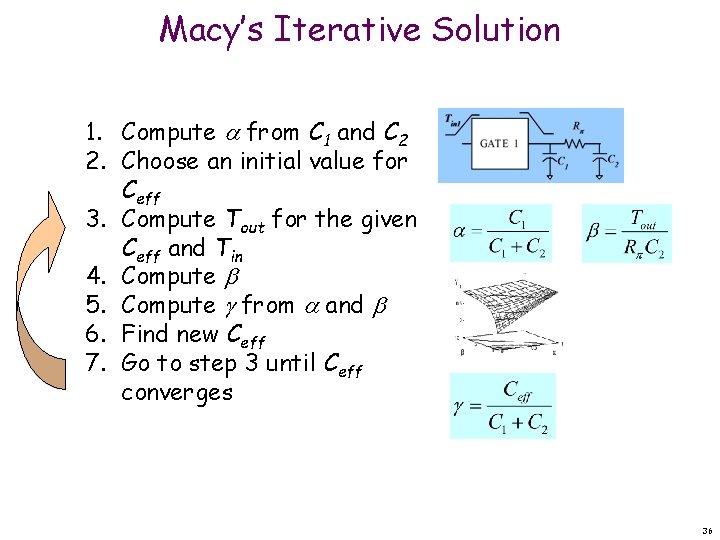

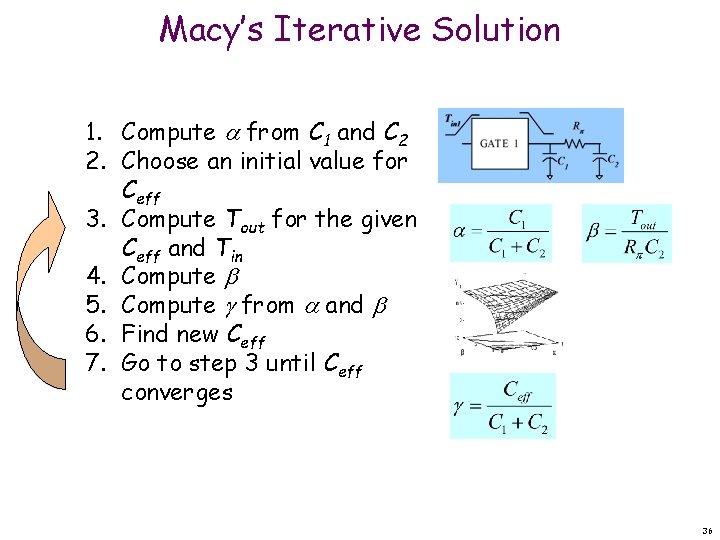

Macy’s Iterative Solution 1. Compute a from C 1 and C 2 2. Choose an initial value for Ceff 3. Compute Tout for the given Ceff and Tin 4. Compute b 5. Compute g from a and b 6. Find new Ceff 7. Go to step 3 until Ceff converges 36

Summary p Delay model – Elmore delay – Gate delay: look-up table, k-factor approximation, effective capacitance 37

References l R. Macys and S. Mc. Cormick, “A New Algorithm for Computing the “Effective Capacitance” in Deep Sub-micron Circuits” , Custom Integrated Circuits Conference 1998, pp. 313 -316 l J. Cong, Z. Pan and P. V. Srinivas, "Improved Crosstalk Modeling for Noise Constrained Interconnect Optimization", Asia and South Pacific Design Automation Conference 2001, pp. 373 -378 l L. H. Chen, M. M. -Sadowska, “Aggressor Alignment for Worst -case Coupling Noise”, International Symposium on Physical Design 2000, pp. 48 -54 38

![Homework 1 Given the circuit as shown below and a unit step voltage source Homework [1] Given the circuit as shown below and a unit step voltage source](https://slidetodoc.com/presentation_image/2fda687b0af68e64c24edf706a5d900e/image-39.jpg)

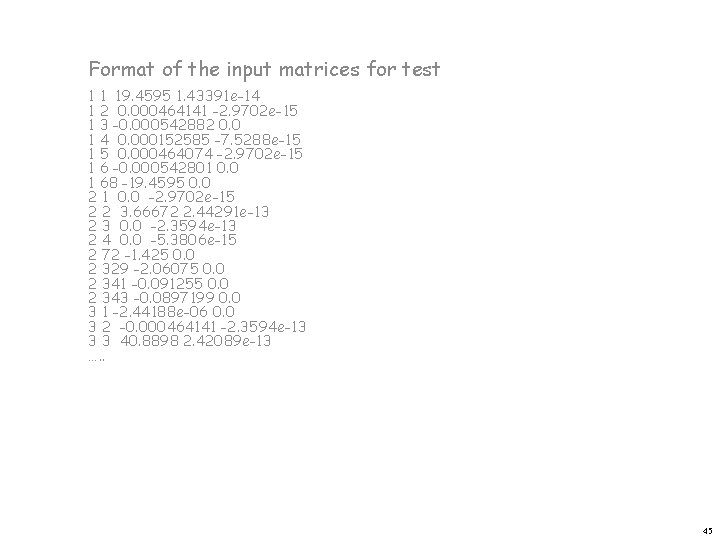

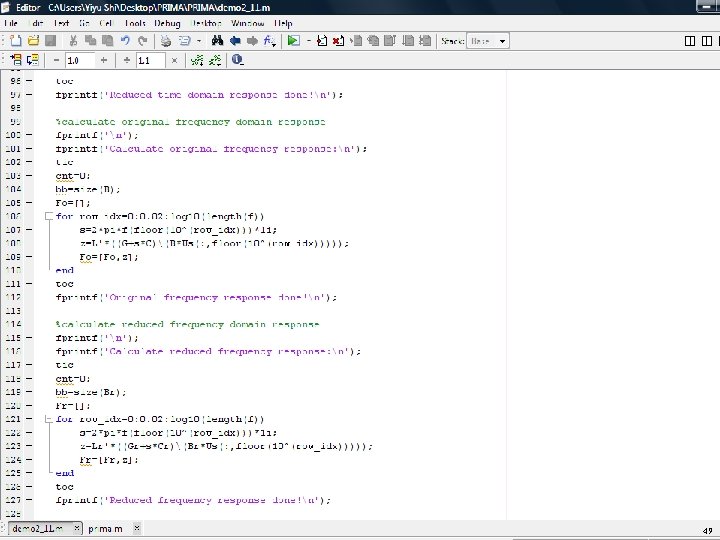

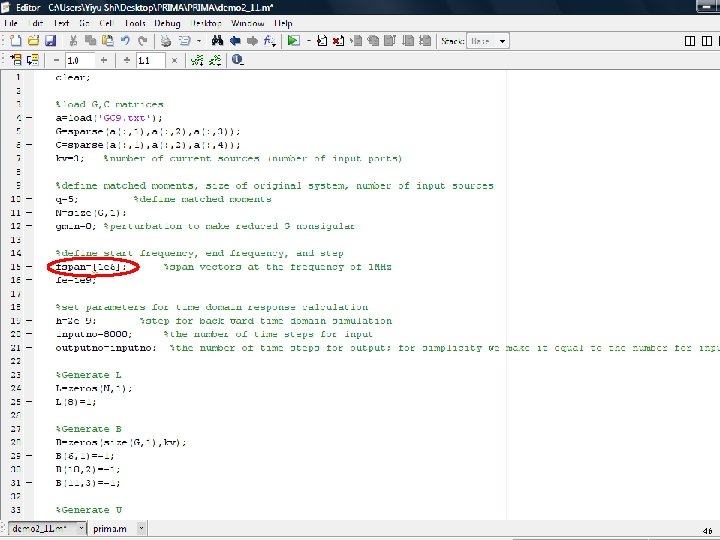

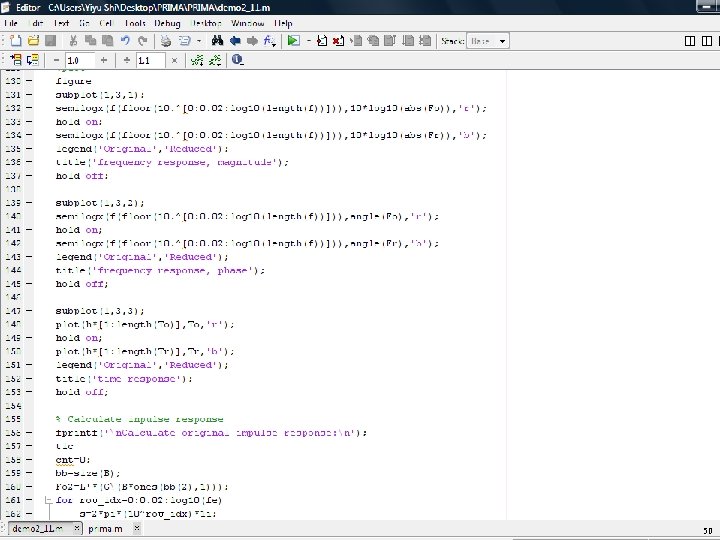

Homework [1] Given the circuit as shown below and a unit step voltage source at the input node s, use SPICE to simulate the circuit and obtain the accurate 50% delay at node n. Also analytically calculate the delay using Elmore method and S 2 P method. How do they compare with the result obtained by SPICE? R 2 C 2 R 1 s 1 v R 4 R 3 C 4 C 1 n R 5 C 3 C 5 R 1 = 1 mΩ R 2 = 2 mΩ R 3 = 2 mΩ R 4 = 1 mΩ R 5 = 4 mΩ C 1 = 1 n. F C 2 = 1 n. F C 3 = 4 n. F C 4 = 4 n. F C 5 = 2 n. F 39

![Homework 2 Give the circuit as shown below and a unit step voltage source Homework [2] Give the circuit as shown below and a unit step voltage source](https://slidetodoc.com/presentation_image/2fda687b0af68e64c24edf706a5d900e/image-40.jpg)

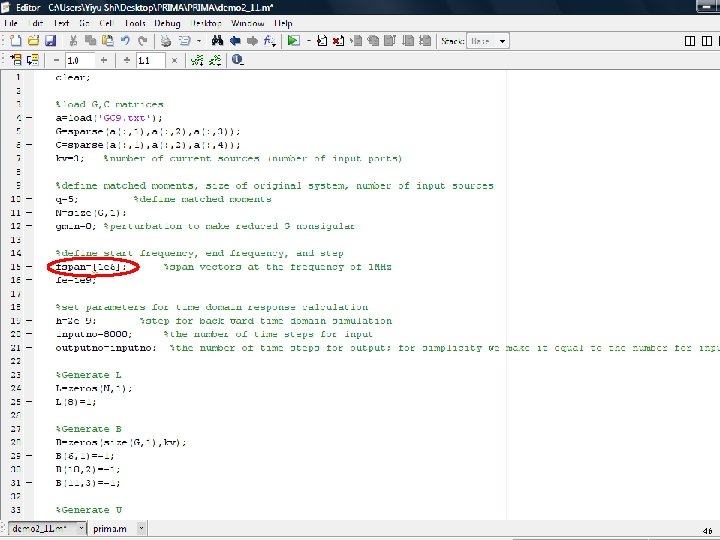

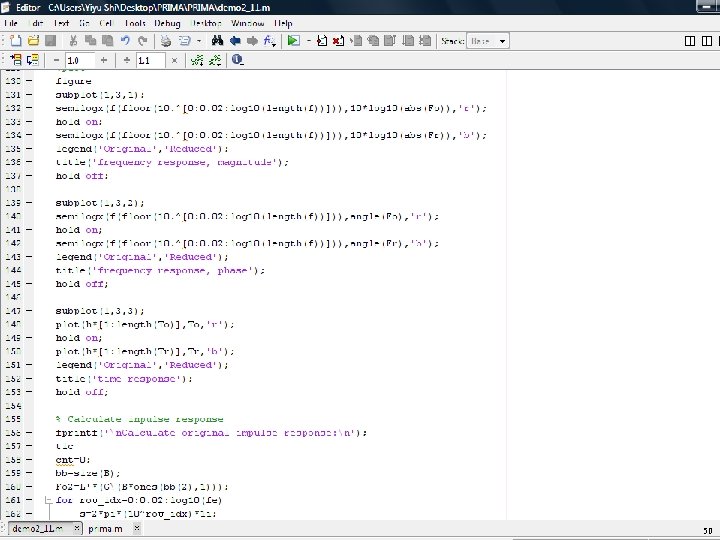

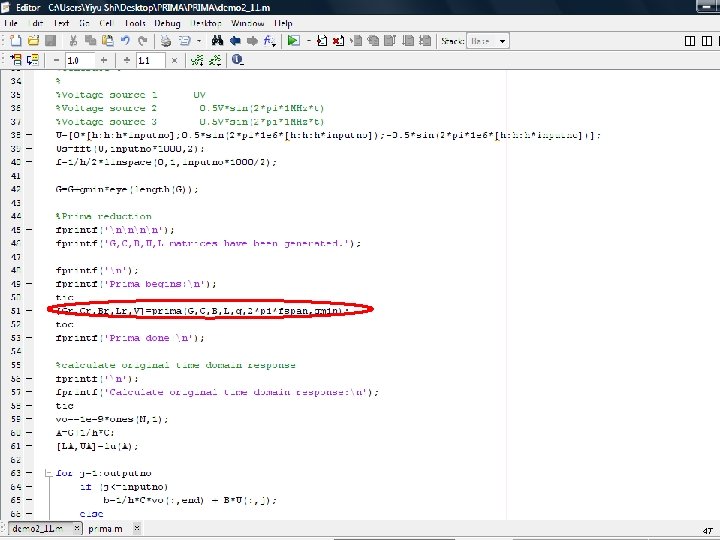

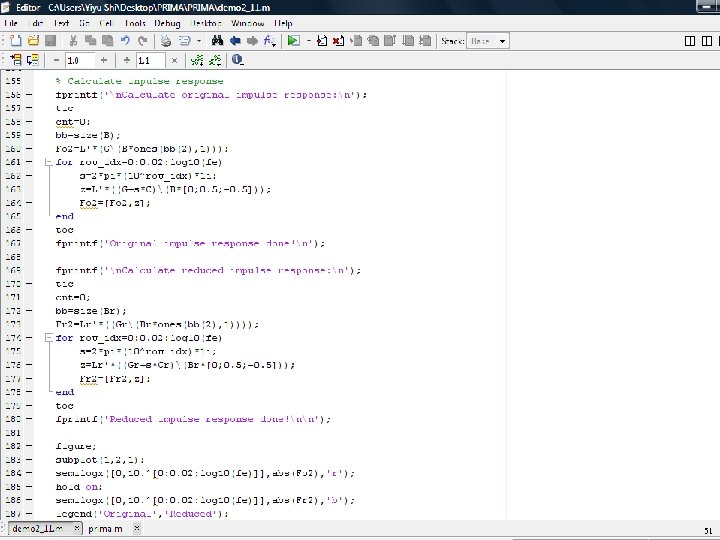

Homework [2] Give the circuit as shown below and a unit step voltage source at node s, can we still use the “shared-path” formula to calculate the Elmore delay? Explain why or why not. Use DC analysis method via MATLAB or SPICE to get the 0 th -3 rd moments of C 3 and C 5. R 2 C 2 R 1 s 1 v R 4 R 3 C 4 C 1 n C 6 C 3 C 5 R 1 = 1 mΩ R 2 = 2 mΩ R 3 = 2 mΩ R 4 = 1 mΩ C 1 = 1 n. F C 2 = 1 n. F C 3 = 4 n. F C 4 = 4 n. F C 5 = 2 n. F C 6 = 1 n. F 40

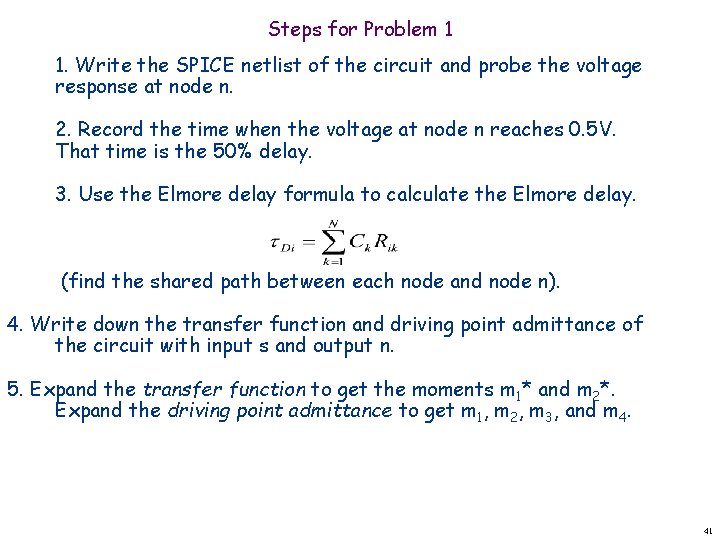

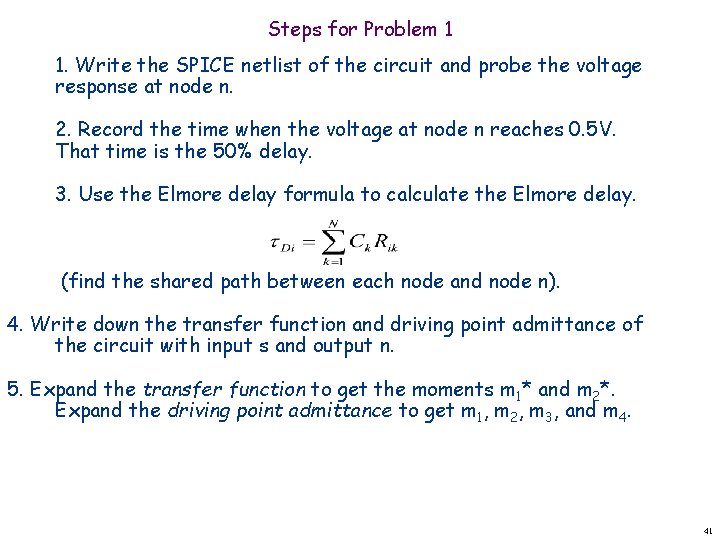

Steps for Problem 1 1. Write the SPICE netlist of the circuit and probe the voltage response at node n. 2. Record the time when the voltage at node n reaches 0. 5 V. That time is the 50% delay. 3. Use the Elmore delay formula to calculate the Elmore delay. (find the shared path between each node and node n). 4. Write down the transfer function and driving point admittance of the circuit with input s and output n. 5. Expand the transfer function to get the moments m 1* and m 2*. Expand the driving point admittance to get m 1, m 2, m 3, and m 4. 41

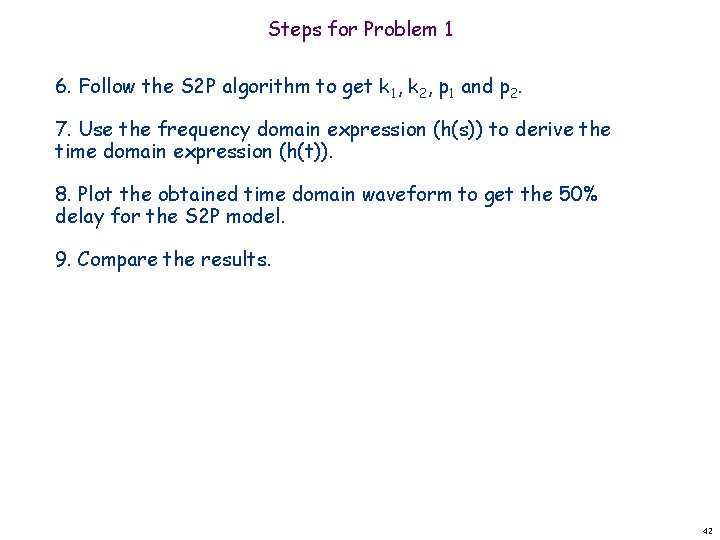

Steps for Problem 1 6. Follow the S 2 P algorithm to get k 1, k 2, p 1 and p 2. 7. Use the frequency domain expression (h(s)) to derive the time domain expression (h(t)). 8. Plot the obtained time domain waveform to get the 50% delay for the S 2 P model. 9. Compare the results. 42

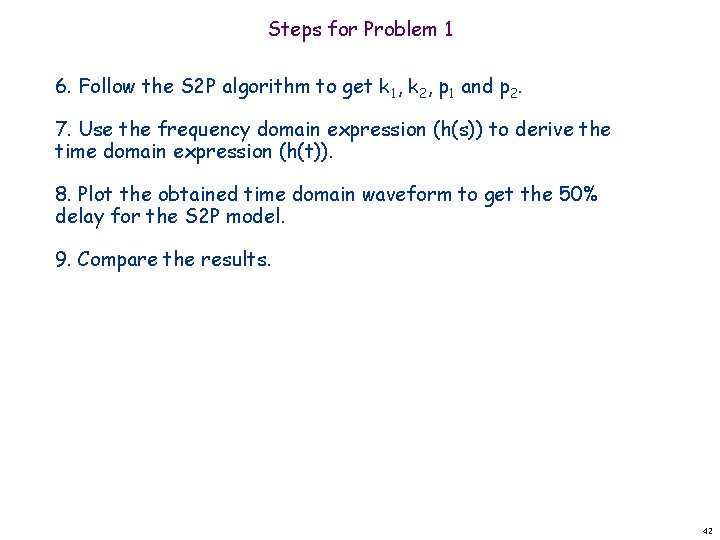

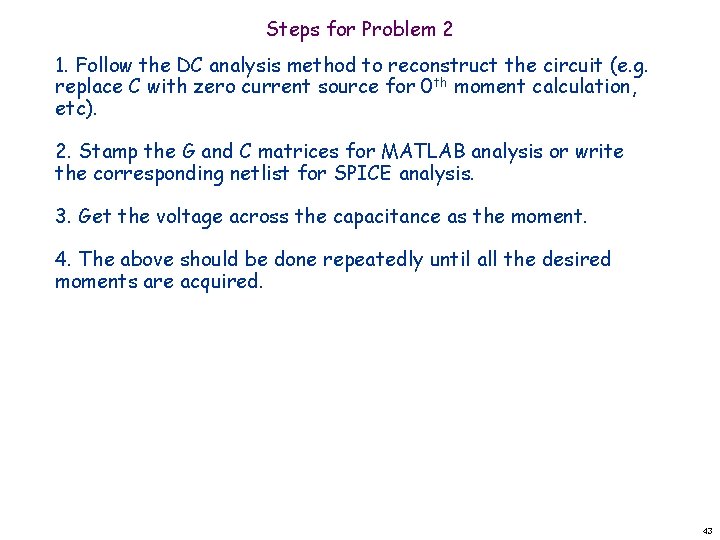

Steps for Problem 2 1. Follow the DC analysis method to reconstruct the circuit (e. g. replace C with zero current source for 0 th moment calculation, etc). 2. Stamp the G and C matrices for MATLAB analysis or write the corresponding netlist for SPICE analysis. 3. Get the voltage across the capacitance as the moment. 4. The above should be done repeatedly until all the desired moments are acquired. 43

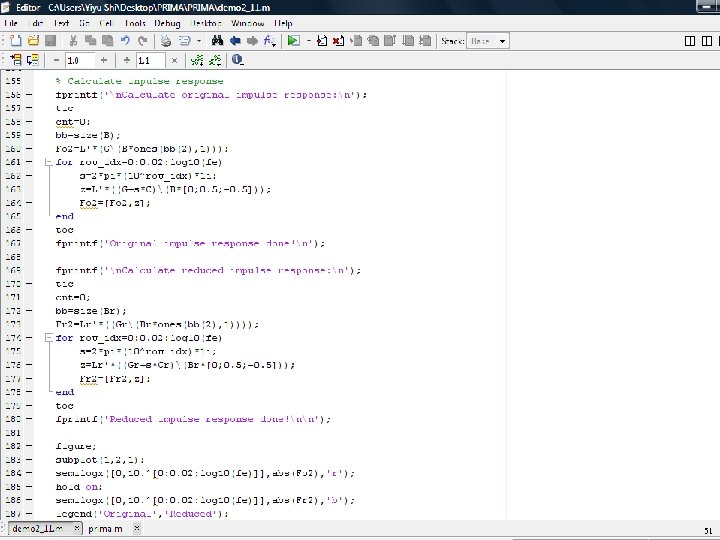

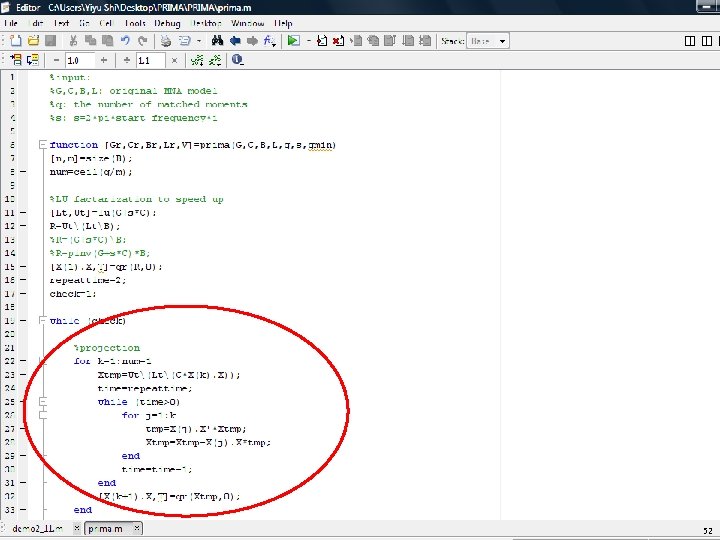

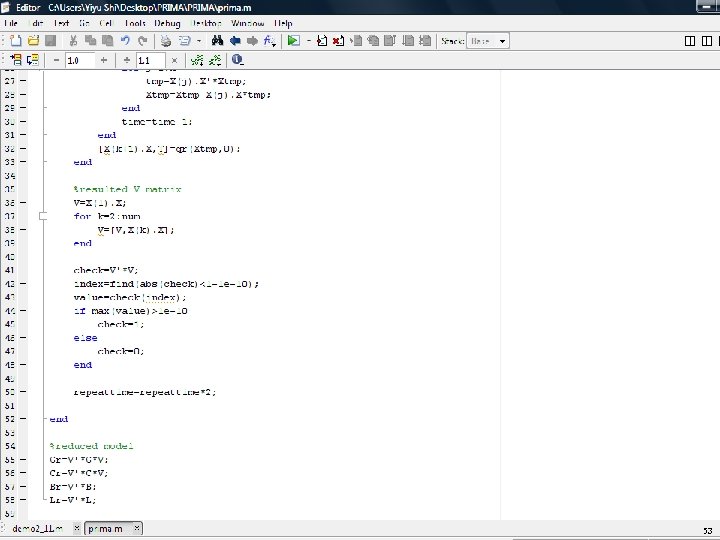

![Homework 2 3 Modify the PRIMA code with single frequency expansion to multiple points Homework 2 [3] Modify the PRIMA code with single frequency expansion to multiple points](https://slidetodoc.com/presentation_image/2fda687b0af68e64c24edf706a5d900e/image-44.jpg)

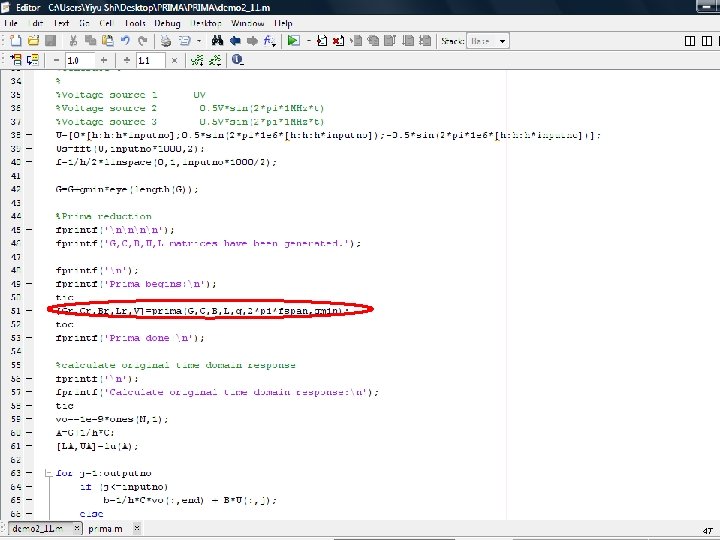

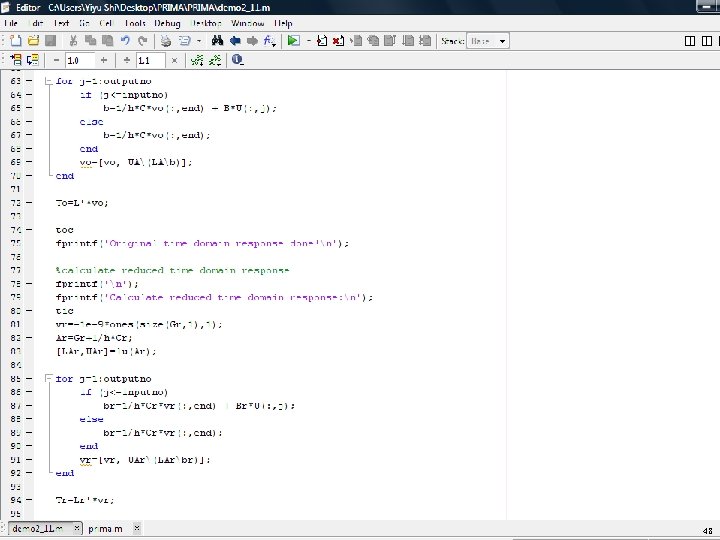

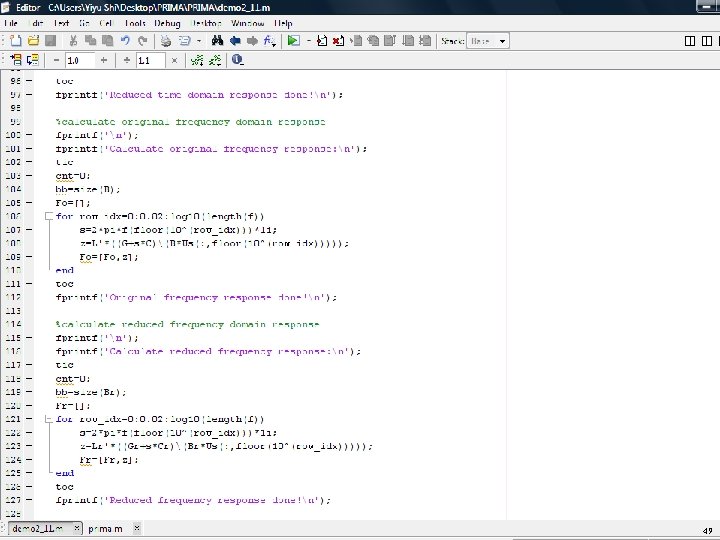

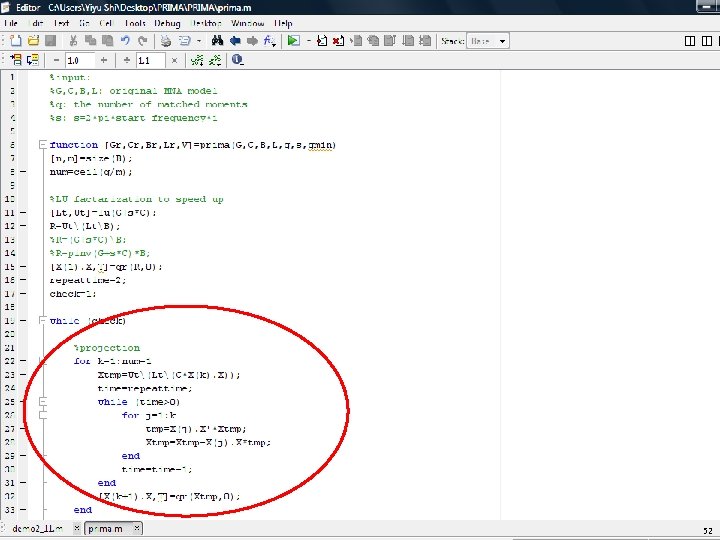

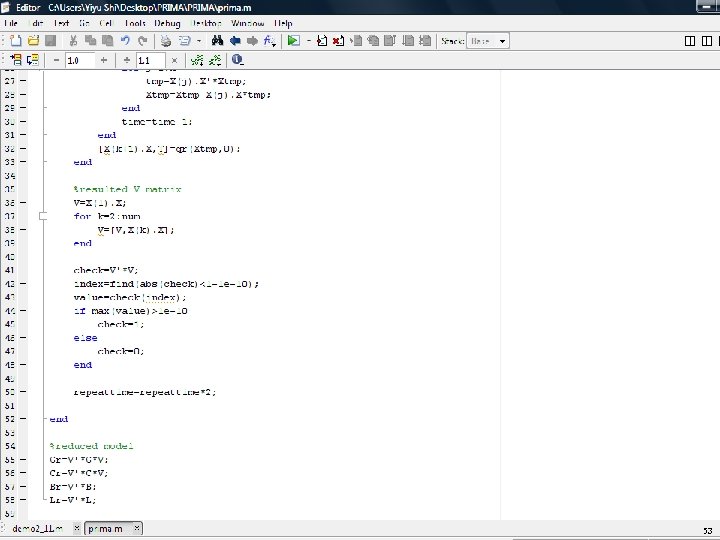

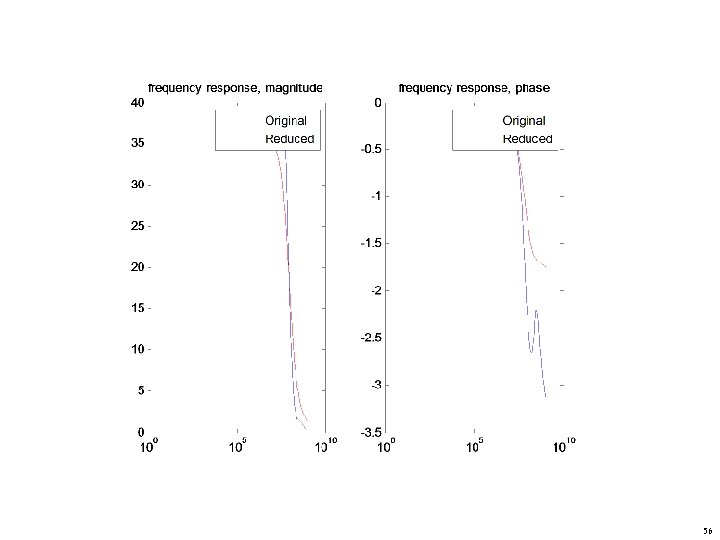

Homework 2 [3] Modify the PRIMA code with single frequency expansion to multiple points expansion. You should use a vector fspan to pass the frequency expansion points. Compare the waveforms of the reduced model between the following two cases: 1. Single point expansion at s=1 e 4. 2. Four-point expansion at s=1 e 3, 1 e 5, 1 e 7, 1 e 9. 44

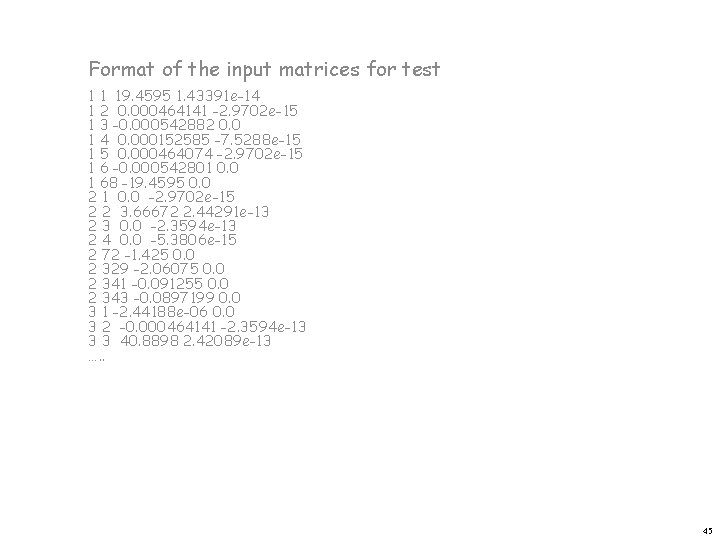

Format of the input matrices for test 1 1 19. 4595 1. 43391 e-14 1 2 0. 000464141 -2. 9702 e-15 1 3 -0. 000542882 0. 0 1 4 0. 000152585 -7. 5288 e-15 1 5 0. 000464074 -2. 9702 e-15 1 6 -0. 000542801 0. 0 1 68 -19. 4595 0. 0 2 1 0. 0 -2. 9702 e-15 2 2 3. 66672 2. 44291 e-13 2 3 0. 0 -2. 3594 e-13 2 4 0. 0 -5. 3806 e-15 2 72 -1. 425 0. 0 2 329 -2. 06075 0. 0 2 341 -0. 091255 0. 0 2 343 -0. 0897199 0. 0 3 1 -2. 44188 e-06 0. 0 3 2 -0. 000464141 -2. 3594 e-13 3 3 40. 8898 2. 42089 e-13 …. . 45

46

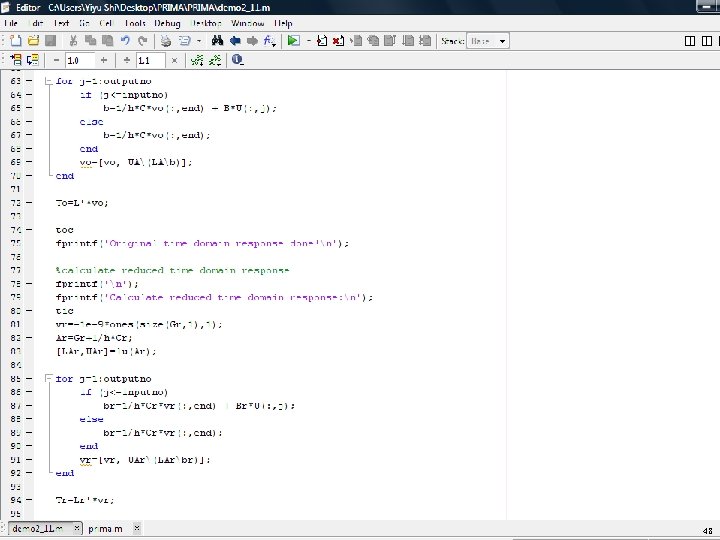

47

48

49

50

51

52

53

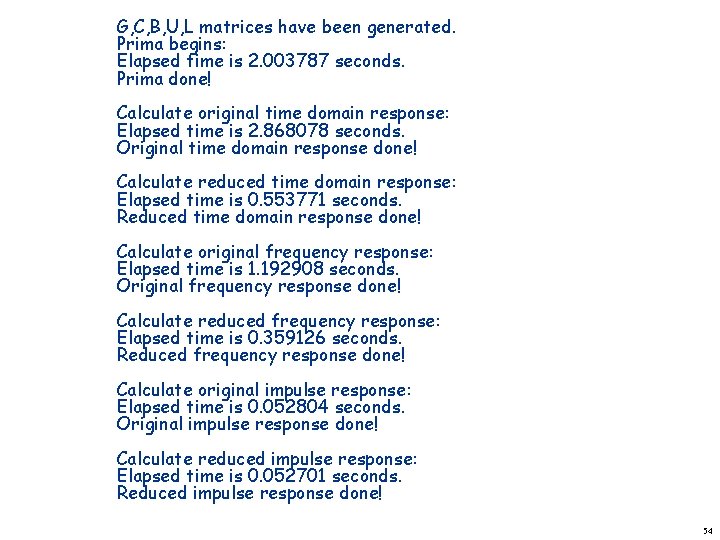

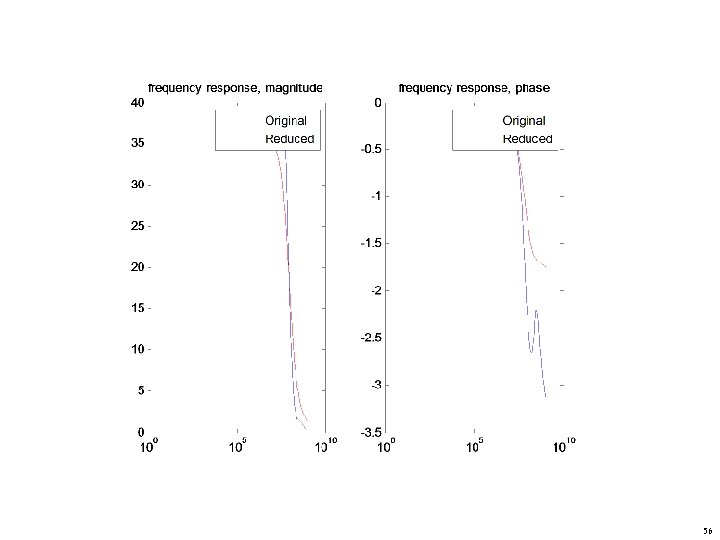

G, C, B, U, L matrices have been generated. Prima begins: Elapsed time is 2. 003787 seconds. Prima done! Calculate original time domain response: Elapsed time is 2. 868078 seconds. Original time domain response done! Calculate reduced time domain response: Elapsed time is 0. 553771 seconds. Reduced time domain response done! Calculate original frequency response: Elapsed time is 1. 192908 seconds. Original frequency response done! Calculate reduced frequency response: Elapsed time is 0. 359126 seconds. Reduced frequency response done! Calculate original impulse response: Elapsed time is 0. 052804 seconds. Original impulse response done! Calculate reduced impulse response: Elapsed time is 0. 052701 seconds. Reduced impulse response done! 54

55

56