Chapter 2 Instructions Language of the Computer Instructions

![Instructions l l Load and store instructions Example: C code: A[8] = h + Instructions l l Load and store instructions Example: C code: A[8] = h +](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-8.jpg)

![Another Example l What is the MIPS assembly code for A[12] = h + Another Example l What is the MIPS assembly code for A[12] = h +](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-9.jpg)

![Loops l while loop in C: while (save[i]==k) i+=1; l i $s 3, k Loops l while loop in C: while (save[i]==k) i+=1; l i $s 3, k](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-23.jpg)

![String Copy Procedure l C version void strcpy char x[], char y[] { int String Copy Procedure l C version void strcpy char x[], char y[] { int](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-33.jpg)

- Slides: 47

Chapter 2 Instructions: Language of the Computer

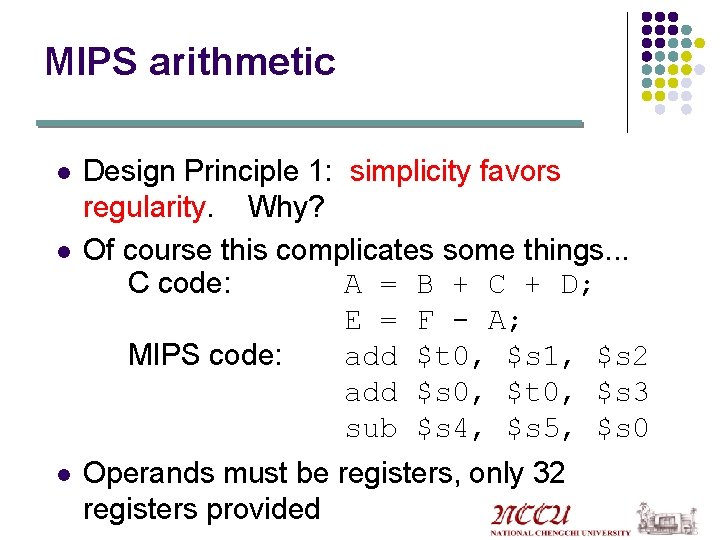

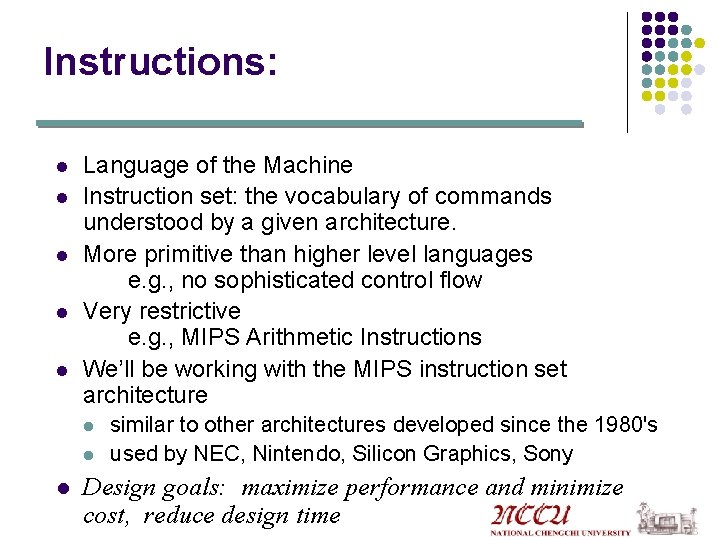

Instructions: l l l Language of the Machine Instruction set: the vocabulary of commands understood by a given architecture. More primitive than higher level languages e. g. , no sophisticated control flow Very restrictive e. g. , MIPS Arithmetic Instructions We’ll be working with the MIPS instruction set architecture l l l similar to other architectures developed since the 1980's used by NEC, Nintendo, Silicon Graphics, Sony Design goals: maximize performance and minimize cost, reduce design time

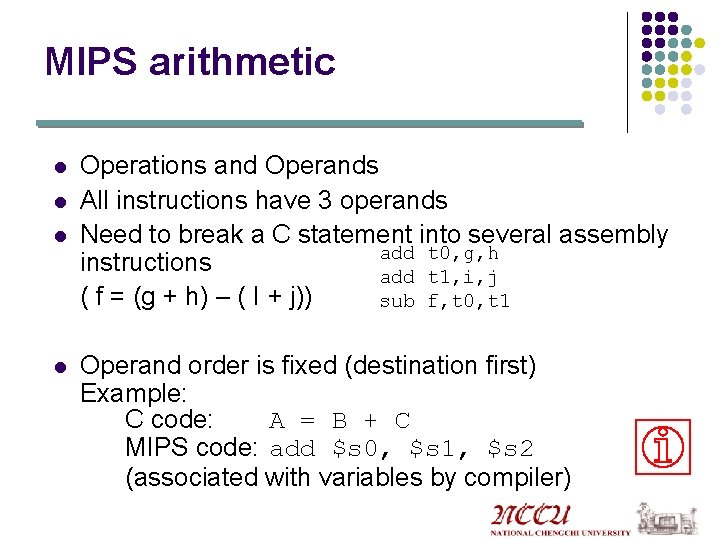

MIPS arithmetic l l Operations and Operands All instructions have 3 operands Need to break a C statement into several assembly add t 0, g, h instructions add t 1, i, j ( f = (g + h) – ( I + j)) sub f, t 0, t 1 Operand order is fixed (destination first) Example: C code: A = B + C MIPS code: add $s 0, $s 1, $s 2 (associated with variables by compiler)

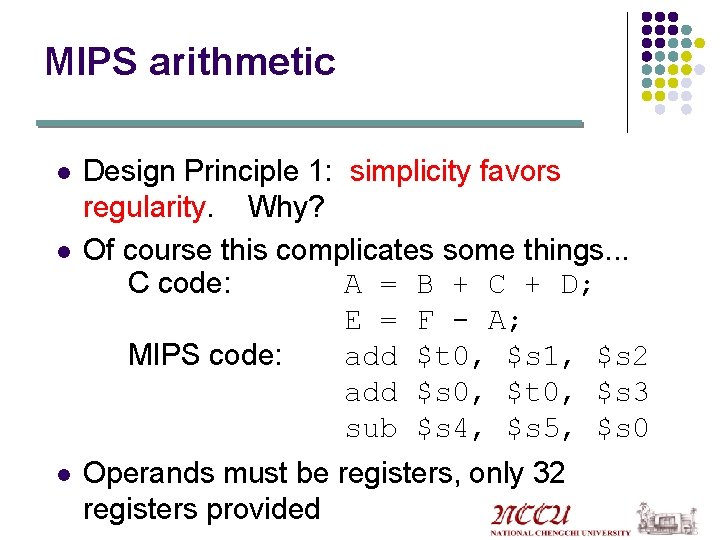

MIPS arithmetic l l l Design Principle 1: simplicity favors regularity. Why? Of course this complicates some things. . . C code: A = B + C + D; E = F - A; MIPS code: add $t 0, $s 1, $s 2 add $s 0, $t 0, $s 3 sub $s 4, $s 5, $s 0 Operands must be registers, only 32 registers provided

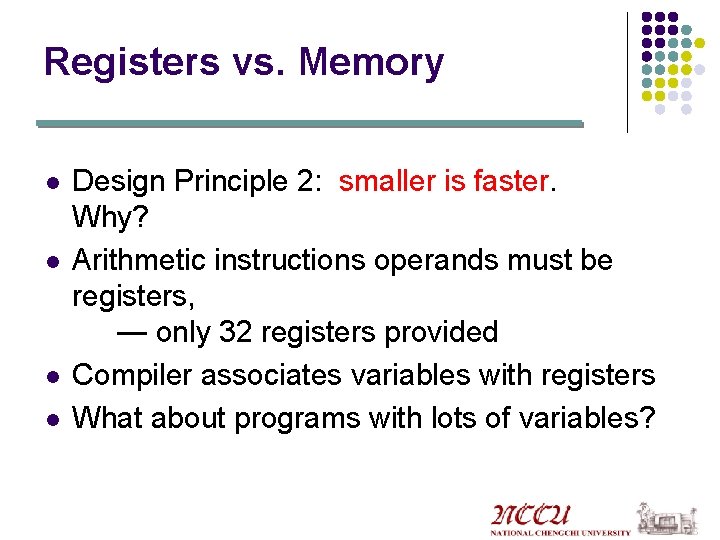

Registers vs. Memory l l Design Principle 2: smaller is faster. Why? Arithmetic instructions operands must be registers, — only 32 registers provided Compiler associates variables with registers What about programs with lots of variables?

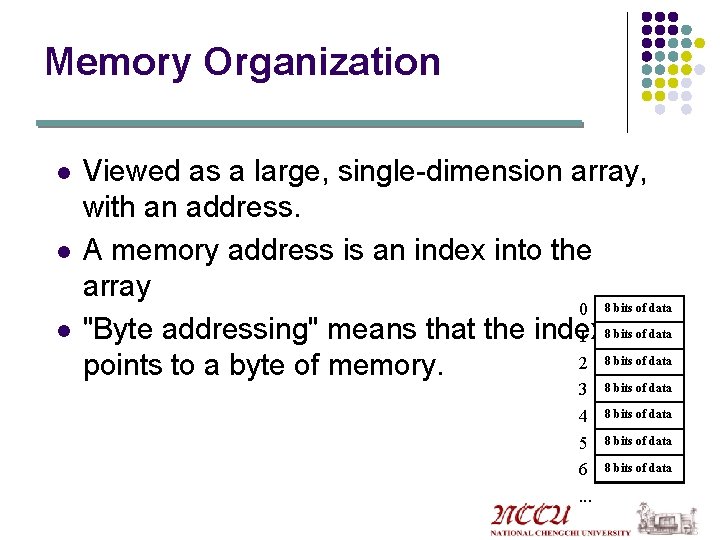

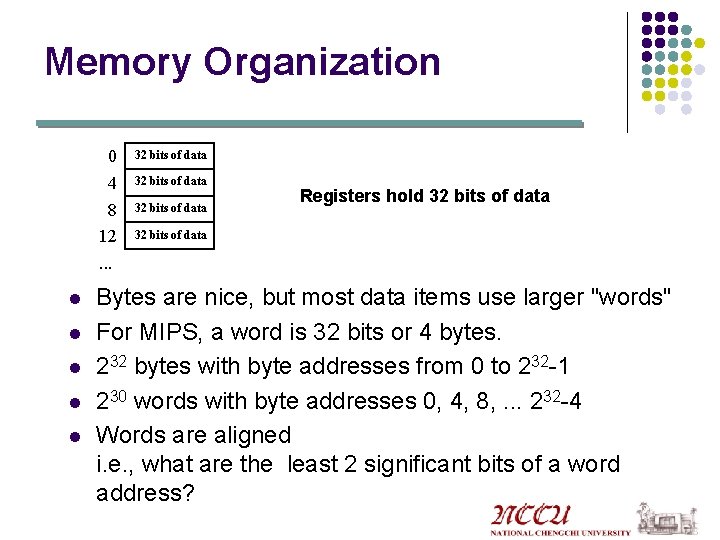

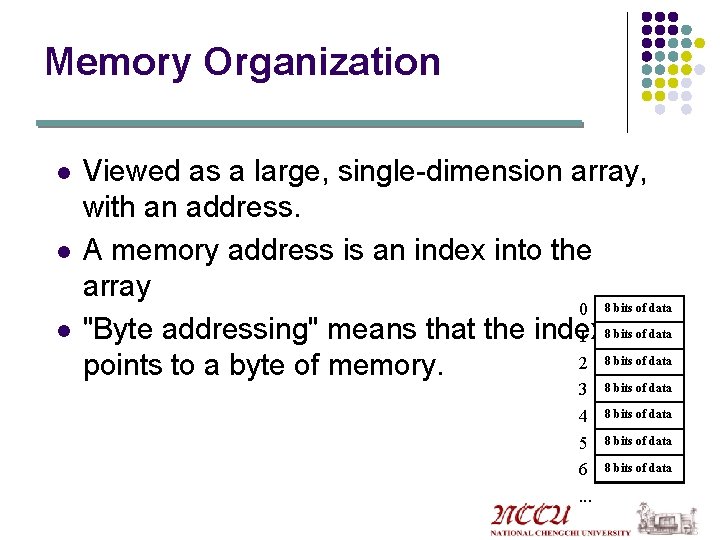

Memory Organization l l Viewed as a large, single-dimension array, with an address. A memory address is an index into the array 0 "Byte addressing" means that the index 1 2 points to a byte of memory. 8 bits of data l 8 bits of data 3 4 5 6. . . 8 bits of data

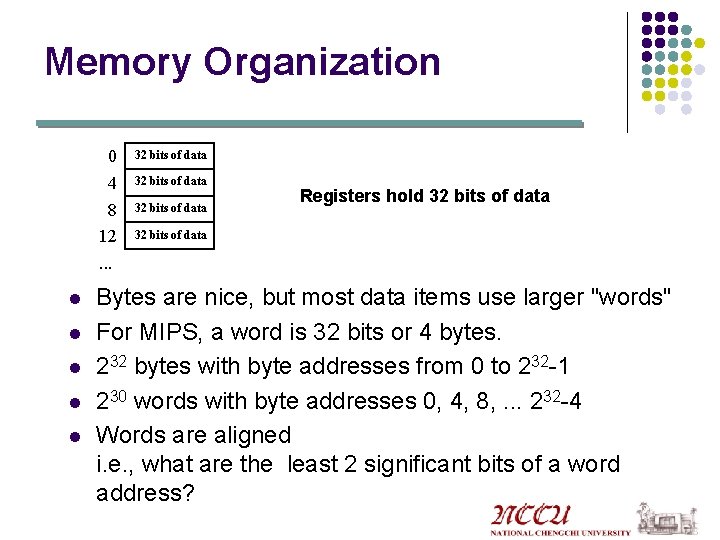

Memory Organization 0 4 8 12. . . l l l 32 bits of data Registers hold 32 bits of data Bytes are nice, but most data items use larger "words" For MIPS, a word is 32 bits or 4 bytes. 232 bytes with byte addresses from 0 to 232 -1 230 words with byte addresses 0, 4, 8, . . . 232 -4 Words are aligned i. e. , what are the least 2 significant bits of a word address?

![Instructions l l Load and store instructions Example C code A8 h Instructions l l Load and store instructions Example: C code: A[8] = h +](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-8.jpg)

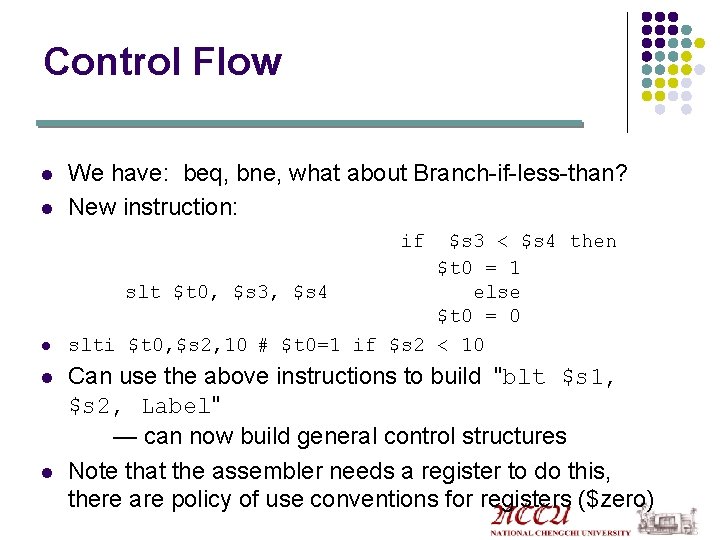

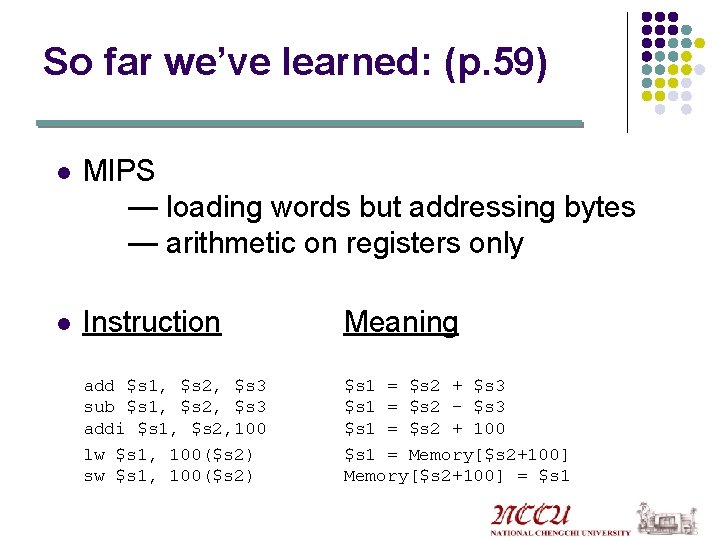

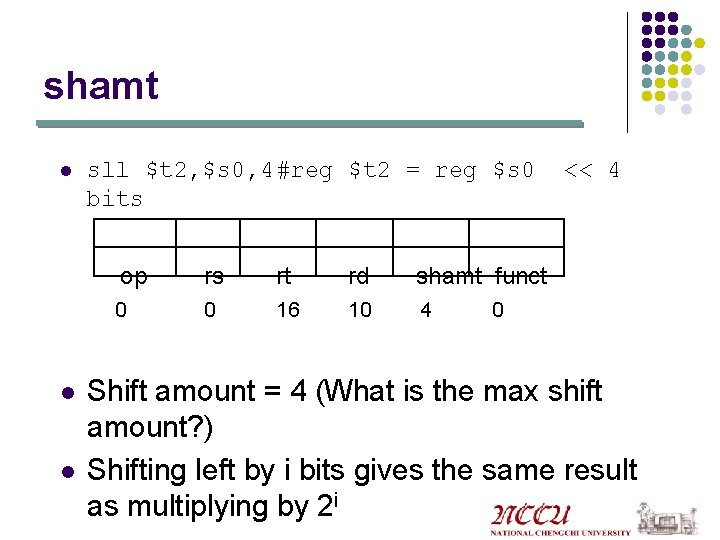

Instructions l l Load and store instructions Example: C code: A[8] = h + A[8]; MIPS code: l l lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0, 32($s 3) Store word has destination last Remember arithmetic operands are registers, not memory!

![Another Example l What is the MIPS assembly code for A12 h Another Example l What is the MIPS assembly code for A[12] = h +](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-9.jpg)

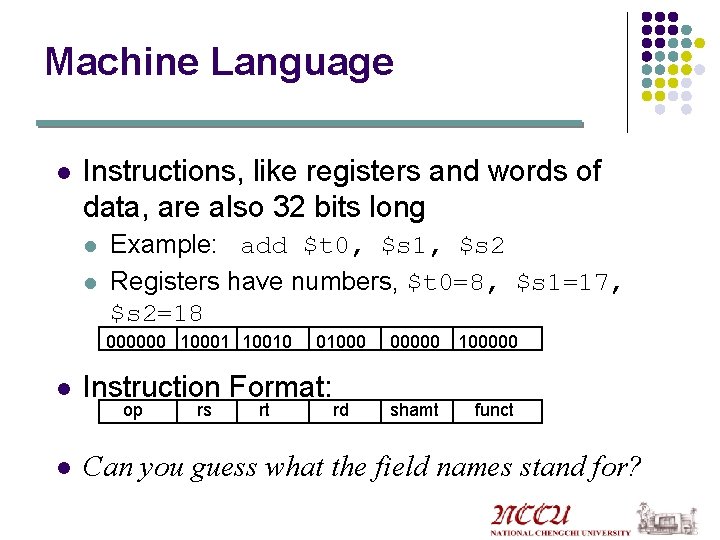

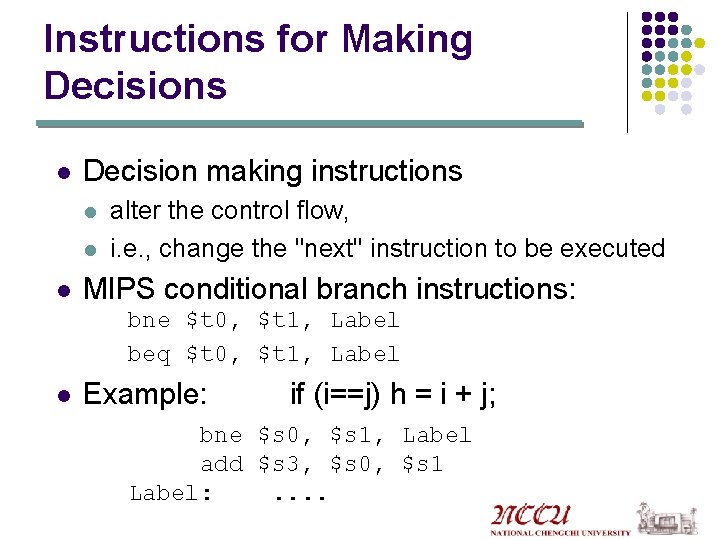

Another Example l What is the MIPS assembly code for A[12] = h + A[8] assuming that h is associated with register $s 2 and the base address of the array A is in $s 3? lw $t 0, 32($s 3) # temporary reg $t 0 gets A[8] add $t 0, $s 2, $t 0 # $t 0 gets h + A[8] sw $t 0, 48($s 3) # stores h + A[8] into A[12]

Constants l l Small constants are used quite frequently (50% of operands) e. g. , A = A + 5; B = B + 1; C = C - 18; Solutions? Why not? l l put 'typical constants' in memory and load them. create hard-wired registers (like $zero) for constants like one. 3

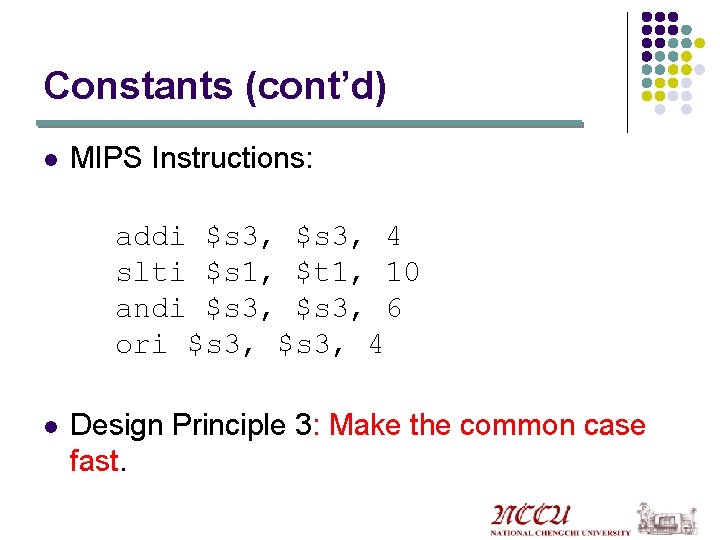

Constants (cont’d) l MIPS Instructions: addi $s 3, 4 slti $s 1, $t 1, 10 andi $s 3, 6 ori $s 3, 4 l Design Principle 3: Make the common case fast.

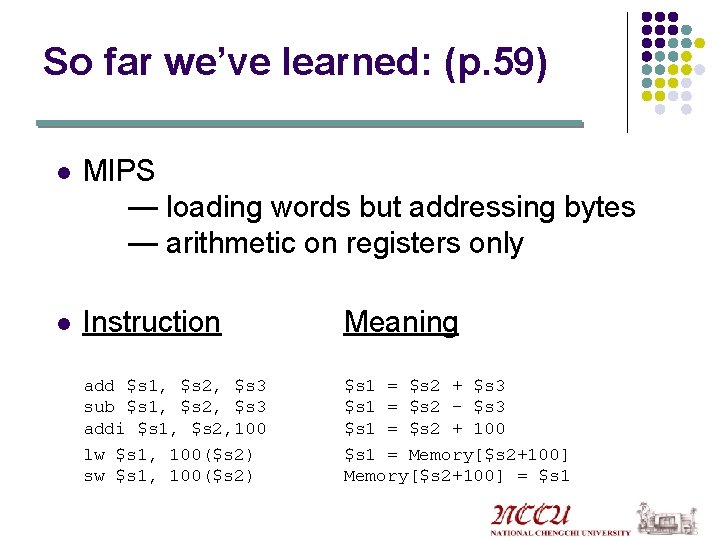

So far we’ve learned: (p. 59) l MIPS — loading words but addressing bytes — arithmetic on registers only l Instruction Meaning add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 addi $s 1, $s 2, 100 lw $s 1, 100($s 2) sw $s 1, 100($s 2) $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = $s 2 + 100 $s 1 = Memory[$s 2+100] = $s 1

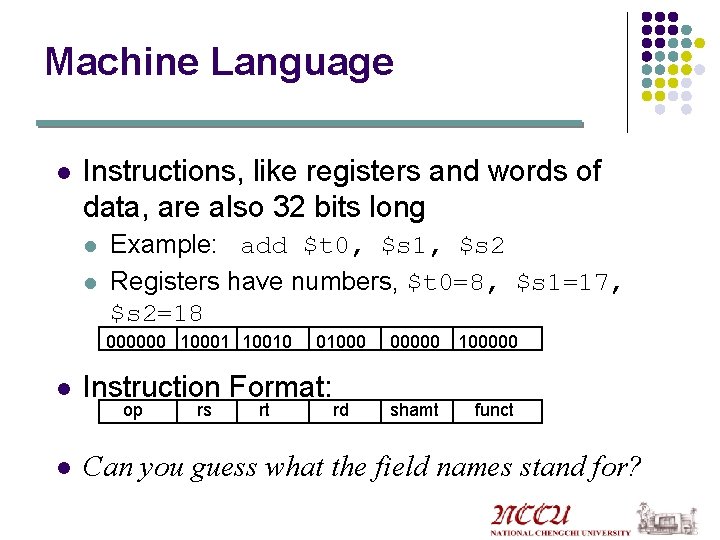

Machine Language l Instructions, like registers and words of data, are also 32 bits long l l Example: add $t 0, $s 1, $s 2 Registers have numbers, $t 0=8, $s 1=17, $s 2=18 000000 10001 10010 01000 00000 100000 shamt funct l Instruction Format: l Can you guess what the field names stand for? op rs rt rd

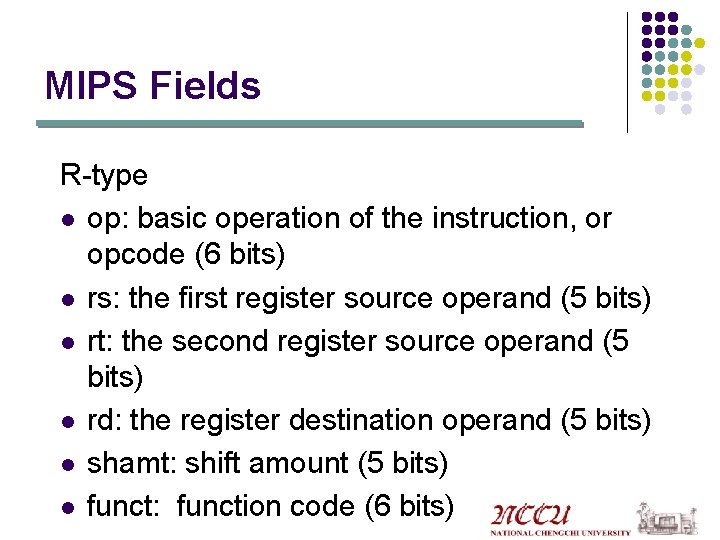

MIPS Fields R-type l op: basic operation of the instruction, or opcode (6 bits) l rs: the first register source operand (5 bits) l rt: the second register source operand (5 bits) l rd: the register destination operand (5 bits) l shamt: shift amount (5 bits) l funct: function code (6 bits)

Machine Language l Consider the load-word and store-word instructions, l l What would the regularity principle have us do? New principle: Good design demands good compromises.

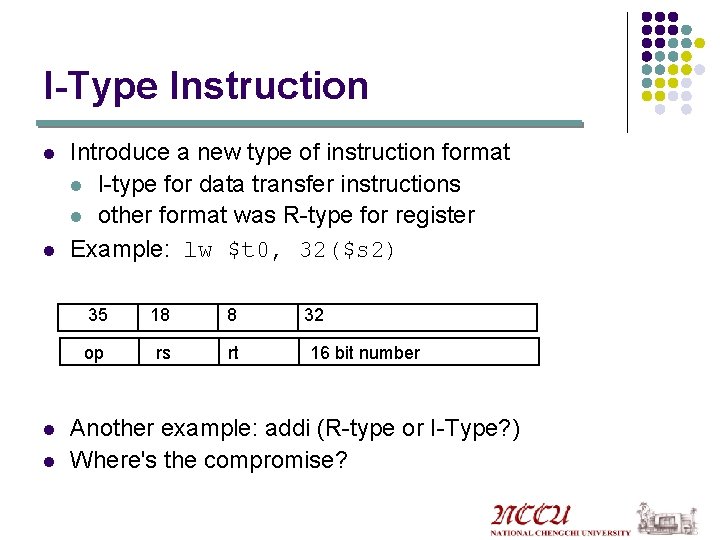

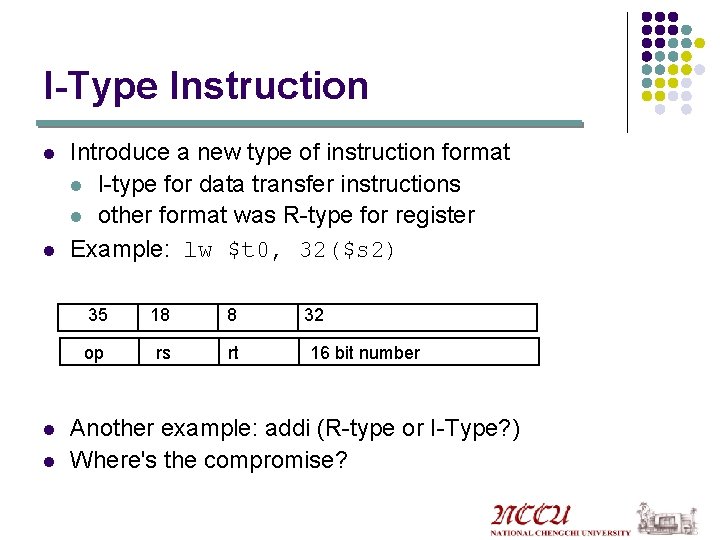

I-Type Instruction l l Introduce a new type of instruction format l I-type for data transfer instructions l other format was R-type for register Example: lw $t 0, 32($s 2) 35 18 8 op rs rt 32 16 bit number Another example: addi (R-type or I-Type? ) Where's the compromise?

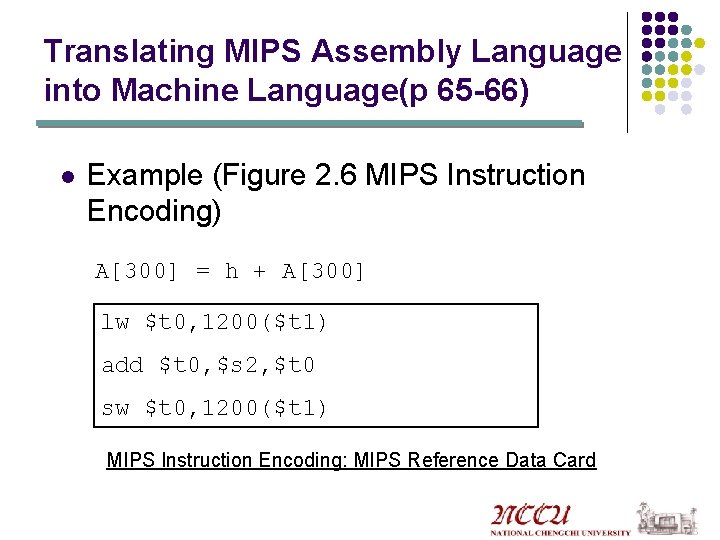

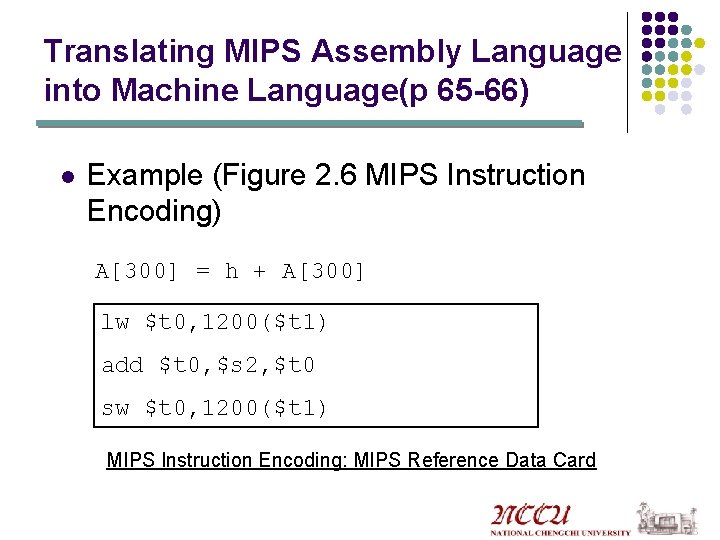

Translating MIPS Assembly Language into Machine Language(p 65 -66) l Example (Figure 2. 6 MIPS Instruction Encoding) A[300] = h + A[300] lw $t 0, 1200($t 1) add $t 0, $s 2, $t 0 sw $t 0, 1200($t 1) MIPS Instruction Encoding: MIPS Reference Data Card

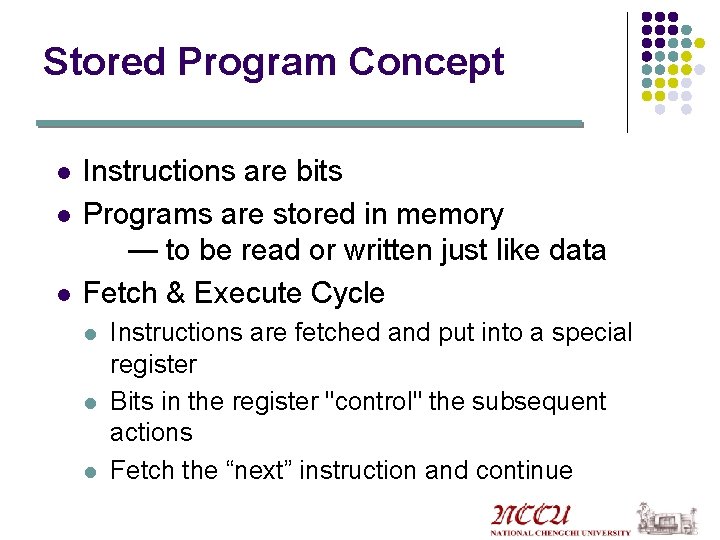

Stored Program Concept l l l Instructions are bits Programs are stored in memory — to be read or written just like data Fetch & Execute Cycle l l l Instructions are fetched and put into a special register Bits in the register "control" the subsequent actions Fetch the “next” instruction and continue

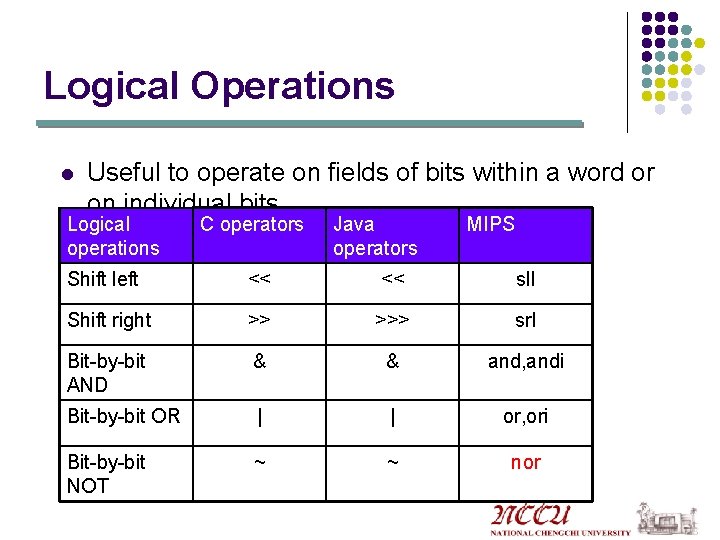

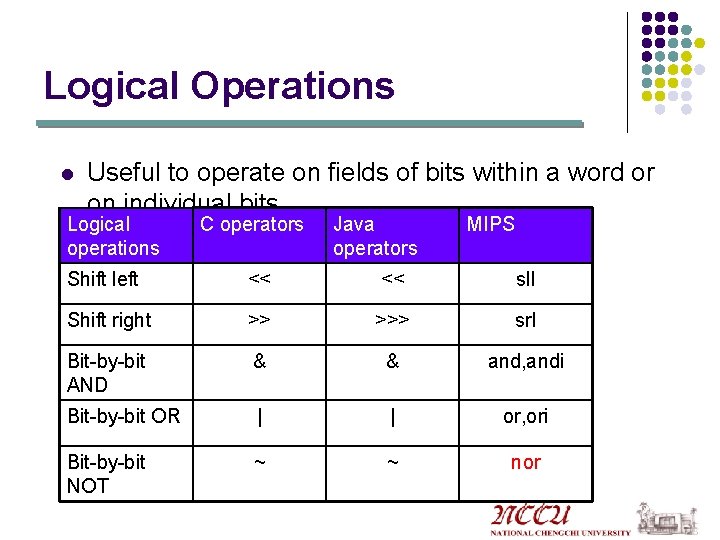

Logical Operations l Useful to operate on fields of bits within a word or on individual bits. Logical operations C operators Java operators MIPS Shift left << << sll Shift right >> >>> srl Bit-by-bit AND & & and, andi Bit-by-bit OR | | or, ori Bit-by-bit NOT ~ ~ nor

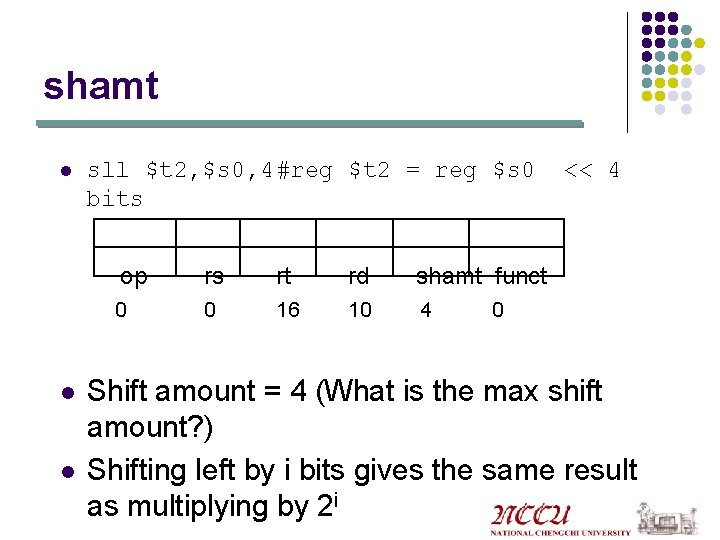

shamt l l l sll $t 2, $s 0, 4#reg $t 2 = reg $s 0 bits op rs rt rd shamt funct 0 0 16 10 4 << 4 0 Shift amount = 4 (What is the max shift amount? ) Shifting left by i bits gives the same result as multiplying by 2 i

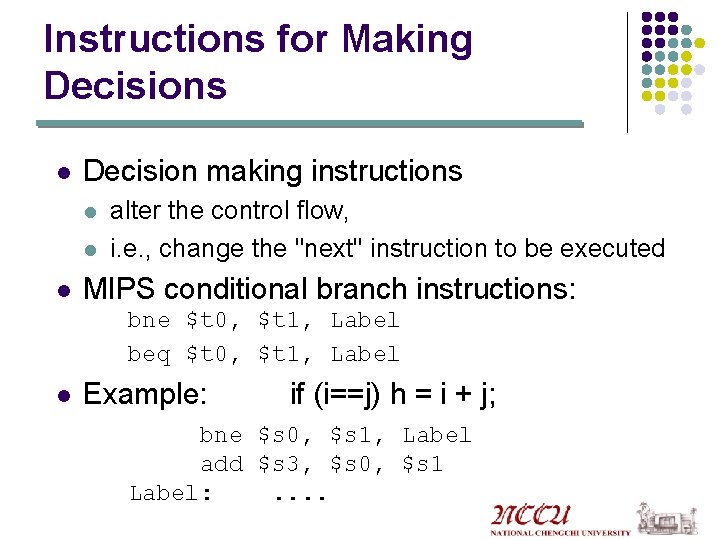

Instructions for Making Decisions l Decision making instructions l l l alter the control flow, i. e. , change the "next" instruction to be executed MIPS conditional branch instructions: bne $t 0, $t 1, Label beq $t 0, $t 1, Label l Example: if (i==j) h = i + j; bne $s 0, $s 1, Label add $s 3, $s 0, $s 1 Label: . .

If-then-else conditional branches l MIPS unconditional branch instructions: j l label Example: if (i==j) Else h=g+h; else f=g-h; $s 0, $s 1, $s 2 bne $s 3, $s 4, add $s 0, $s 1, $s 2 j Exit Else: sub Exit:

![Loops l while loop in C while saveik i1 l i s 3 k Loops l while loop in C: while (save[i]==k) i+=1; l i $s 3, k](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-23.jpg)

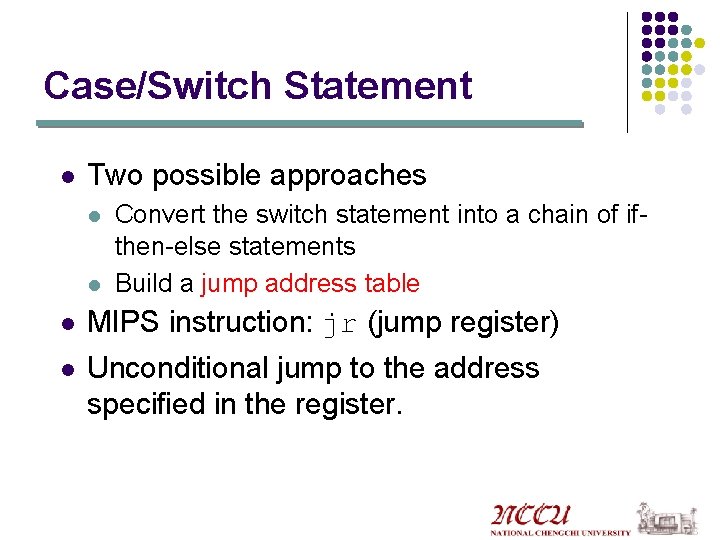

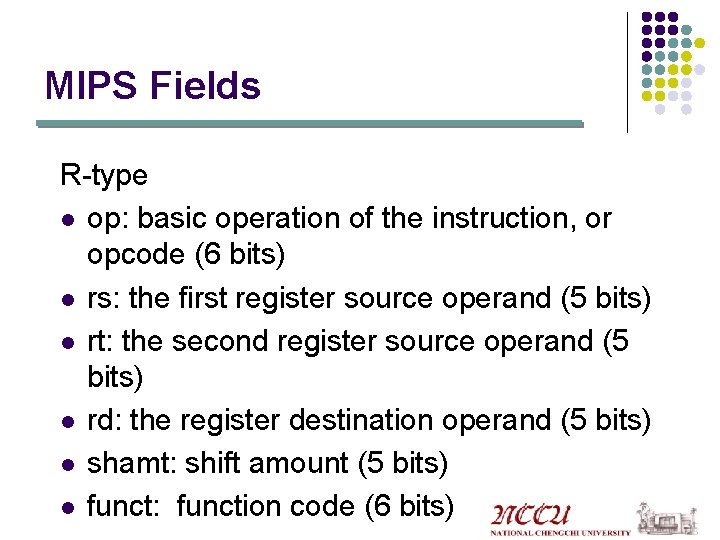

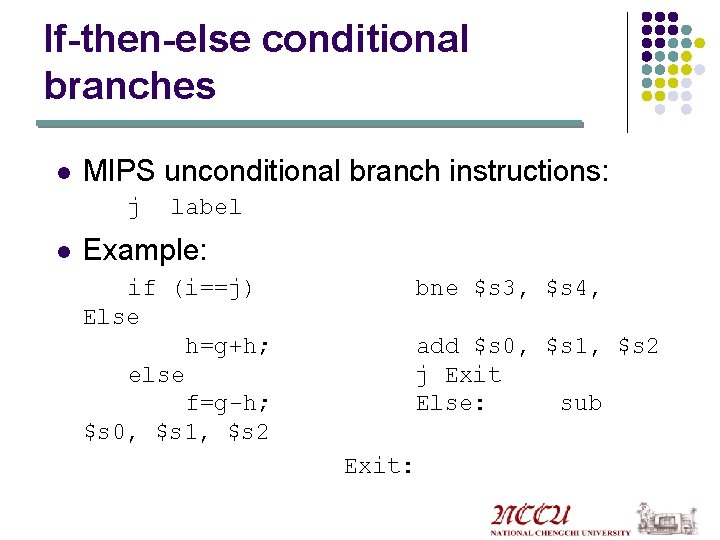

Loops l while loop in C: while (save[i]==k) i+=1; l i $s 3, k $s 5, base of the array save is in $s 6. Loop: sll Exit: $t 1, $s 3, 2 # reg $t 1=4*i add $t 1, $s 6 # $t 1= address of save[i] lw $t 0, 0($t 1) bne $t 0, $s 5, Exit # go to Exit if save[i]!=k addi $s 3, 1 # i=i+1 j Loop # go to Loop # reg t 0=save[i]

Control Flow l l We have: beq, bne, what about Branch-if-less-than? New instruction: if l l l $s 3 < $s 4 then $t 0 = 1 slt $t 0, $s 3, $s 4 else $t 0 = 0 slti $t 0, $s 2, 10 # $t 0=1 if $s 2 < 10 Can use the above instructions to build "blt $s 1, $s 2, Label" — can now build general control structures Note that the assembler needs a register to do this, there are policy of use conventions for registers ($zero)

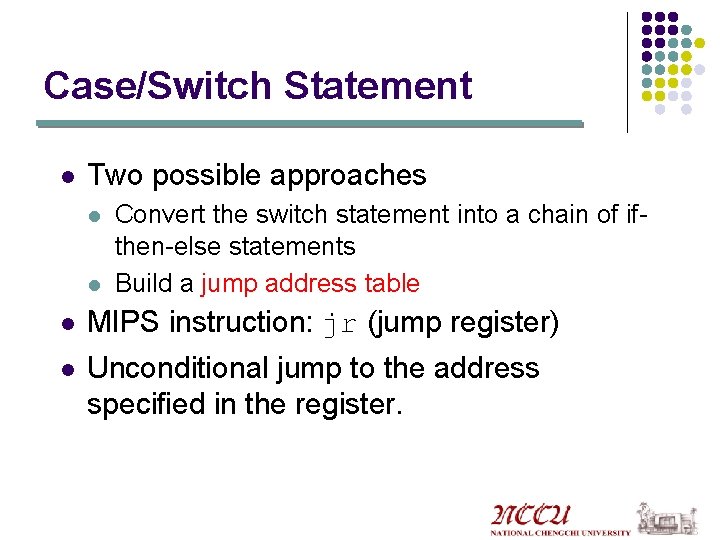

Case/Switch Statement l Two possible approaches l l Convert the switch statement into a chain of ifthen-else statements Build a jump address table l MIPS instruction: jr (jump register) l Unconditional jump to the address specified in the register.

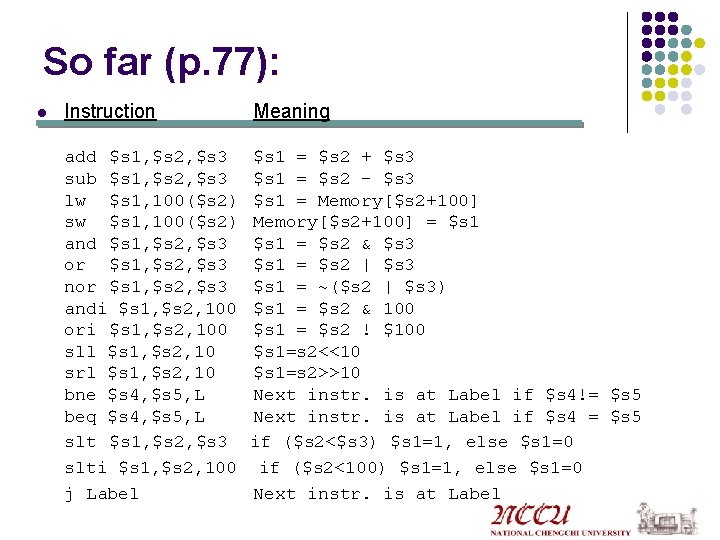

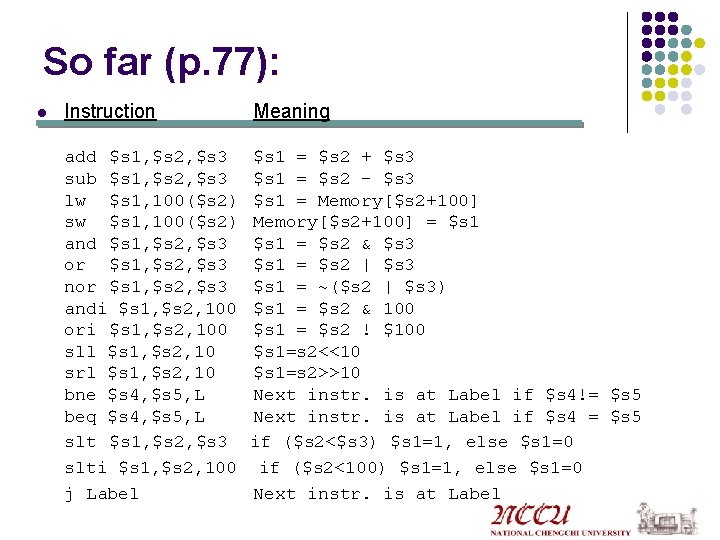

So far (p. 77): l Instruction Meaning add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) sw $s 1, 100($s 2) and $s 1, $s 2, $s 3 or $s 1, $s 2, $s 3 nor $s 1, $s 2, $s 3 andi $s 1, $s 2, 100 ori $s 1, $s 2, 100 sll $s 1, $s 2, 10 srl $s 1, $s 2, 10 bne $s 4, $s 5, L beq $s 4, $s 5, L slt $s 1, $s 2, $s 3 slti $s 1, $s 2, 100 j Label $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1 = $s 2 & $s 3 $s 1 = $s 2 | $s 3 $s 1 = ~($s 2 | $s 3) $s 1 = $s 2 & 100 $s 1 = $s 2 ! $100 $s 1=s 2<<10 $s 1=s 2>>10 Next instr. is at Label if $s 4!= $s 5 Next instr. is at Label if $s 4 = $s 5 if ($s 2<$s 3) $s 1=1, else $s 1=0 if ($s 2<100) $s 1=1, else $s 1=0 Next instr. is at Label

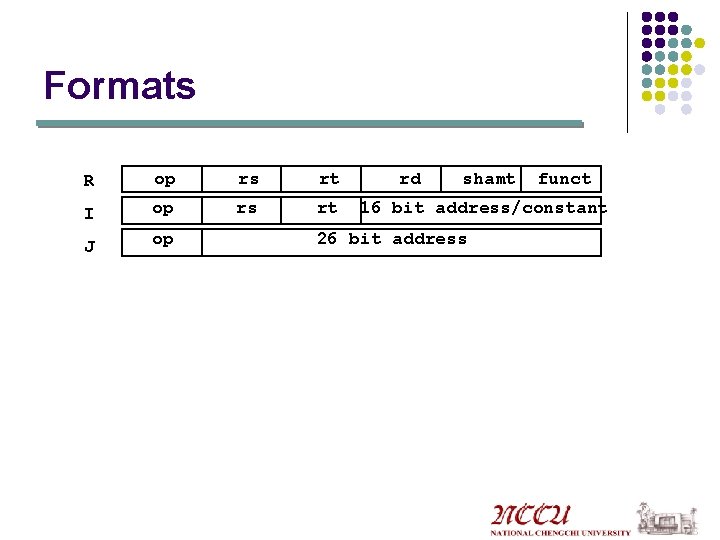

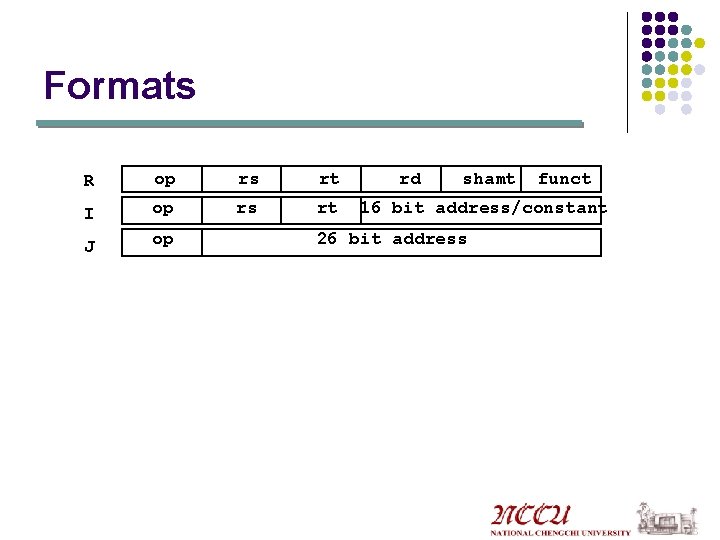

Formats R op rs rt I op rs rt J op rd shamt funct 16 bit address/constant 26 bit address

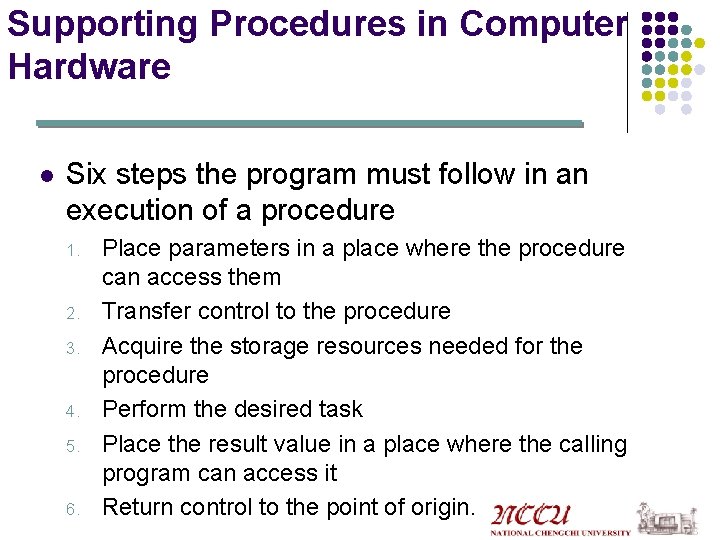

Supporting Procedures in Computer Hardware l Six steps the program must follow in an execution of a procedure 1. 2. 3. 4. 5. 6. Place parameters in a place where the procedure can access them Transfer control to the procedure Acquire the storage resources needed for the procedure Perform the desired task Place the result value in a place where the calling program can access it Return control to the point of origin.

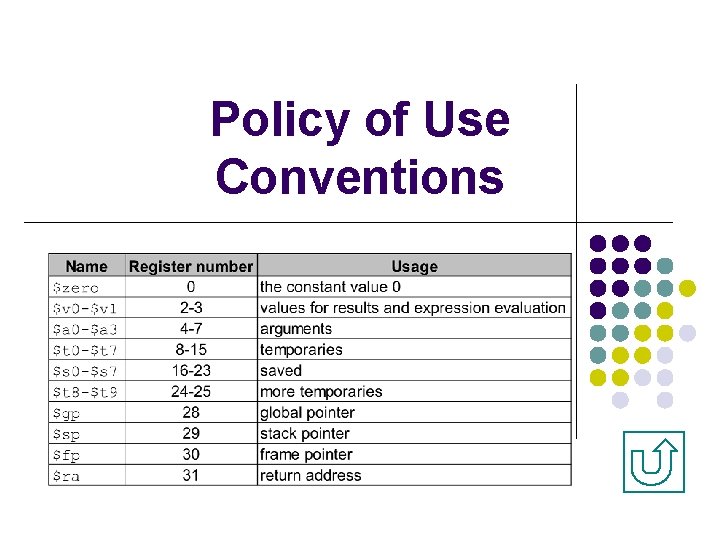

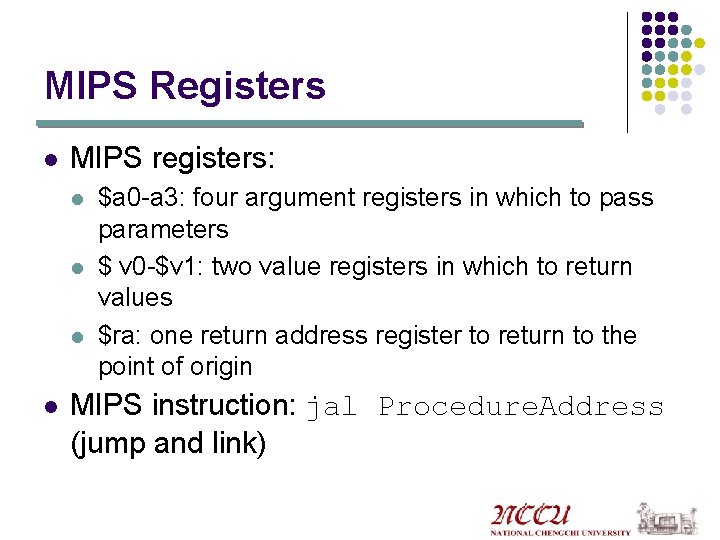

MIPS Registers l MIPS registers: l l $a 0 -a 3: four argument registers in which to pass parameters $ v 0 -$v 1: two value registers in which to return values $ra: one return address register to return to the point of origin MIPS instruction: jal Procedure. Address (jump and link)

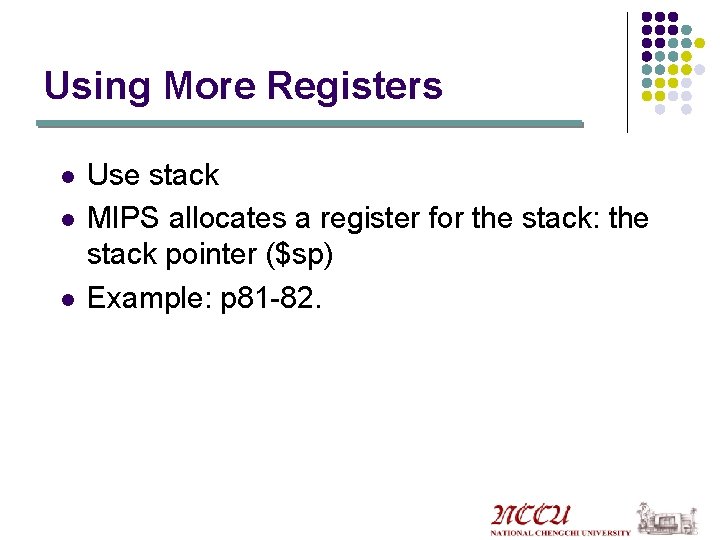

Using More Registers l l l Use stack MIPS allocates a register for the stack: the stack pointer ($sp) Example: p 81 -82.

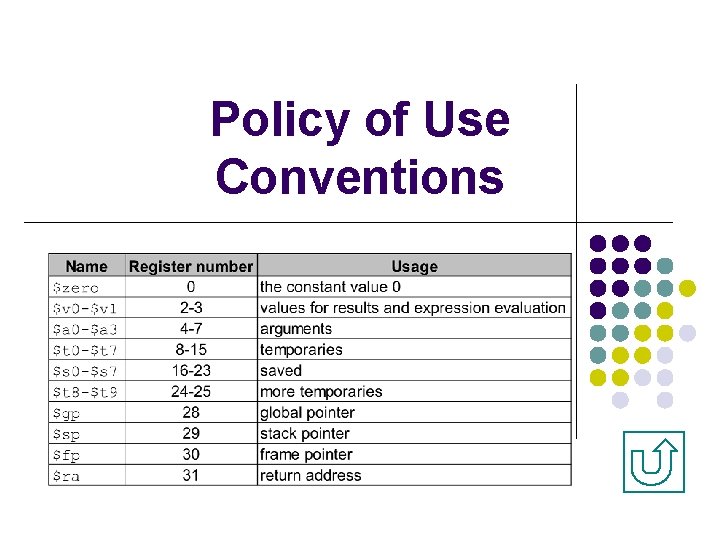

Policy of Use Conventions

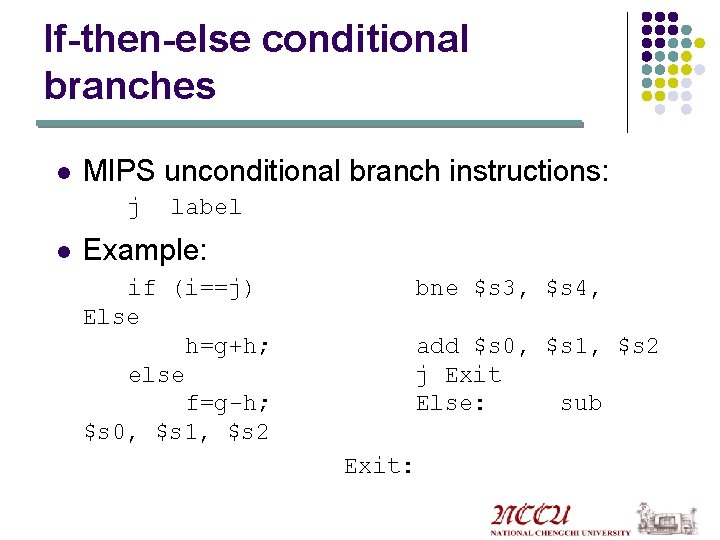

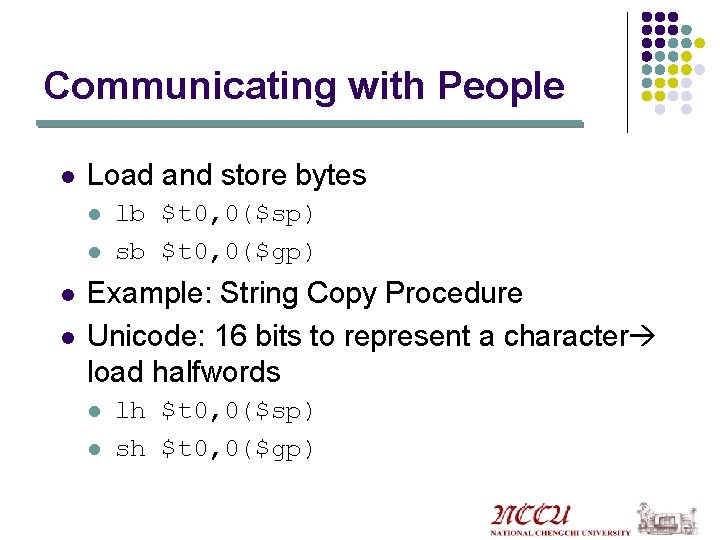

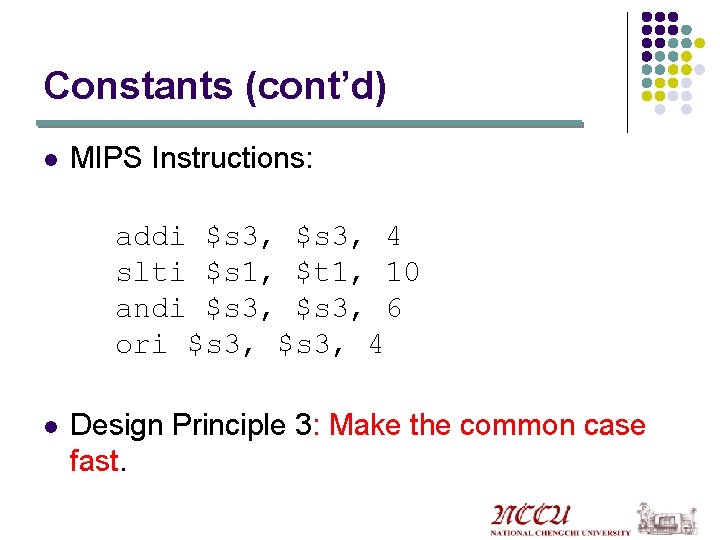

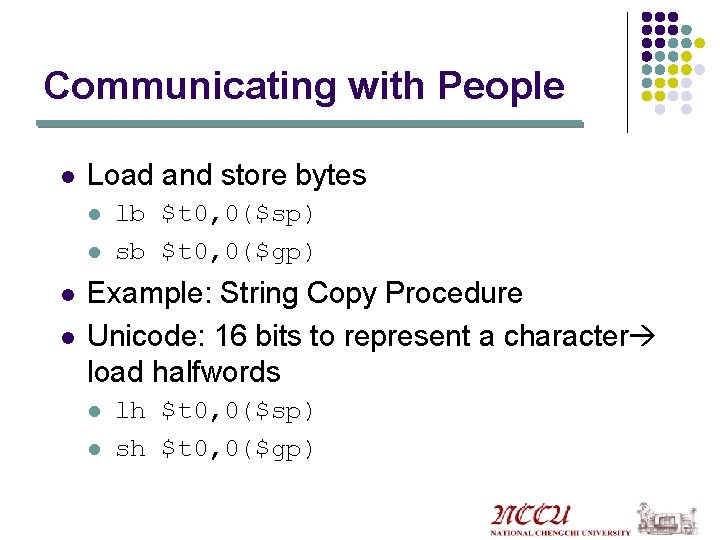

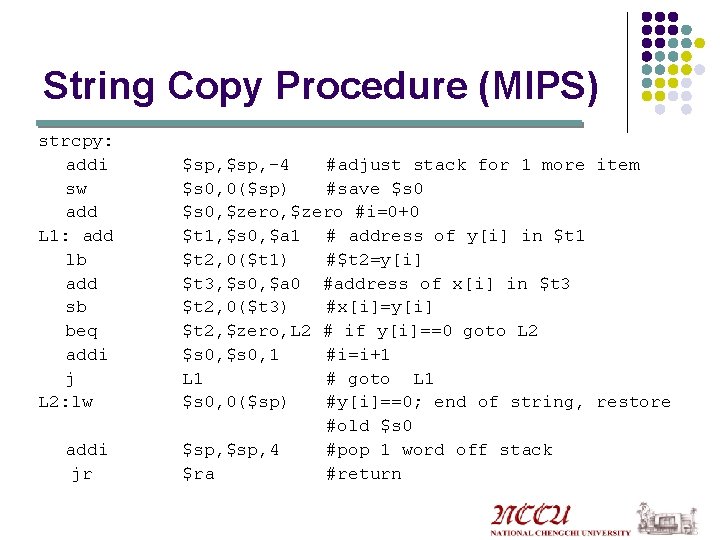

Communicating with People l Load and store bytes l l lb $t 0, 0($sp) sb $t 0, 0($gp) Example: String Copy Procedure Unicode: 16 bits to represent a character load halfwords l l lh $t 0, 0($sp) sh $t 0, 0($gp)

![String Copy Procedure l C version void strcpy char x char y int String Copy Procedure l C version void strcpy char x[], char y[] { int](https://slidetodoc.com/presentation_image_h/cab3face1cfd776755cec0656ac9d4d3/image-33.jpg)

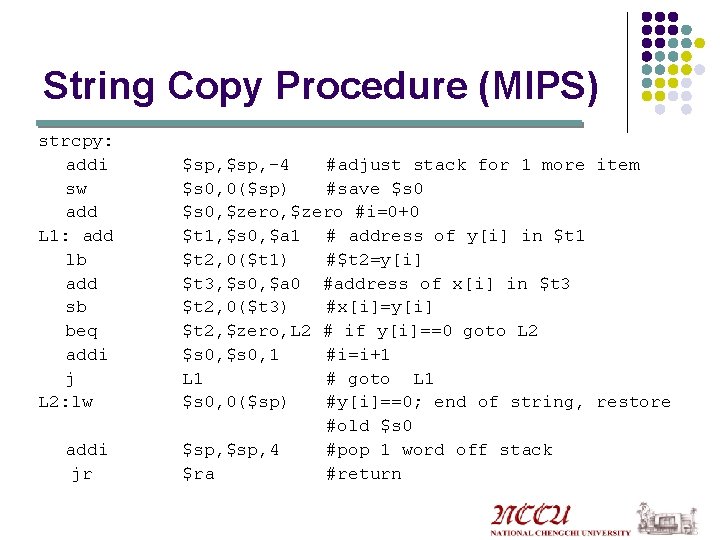

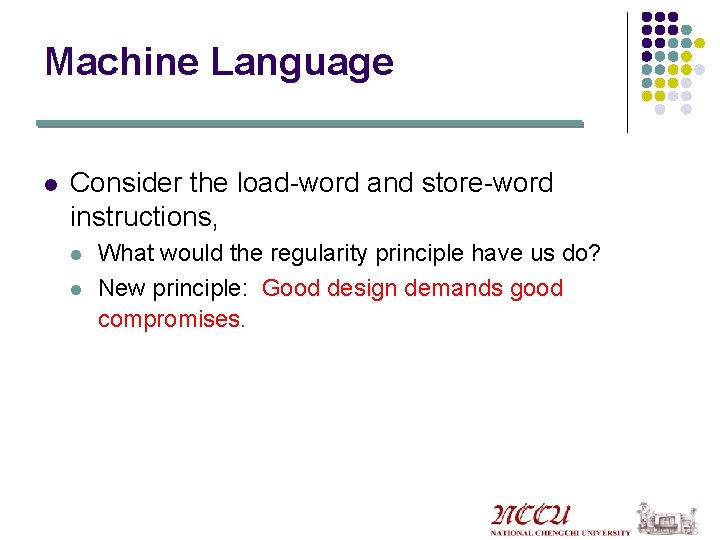

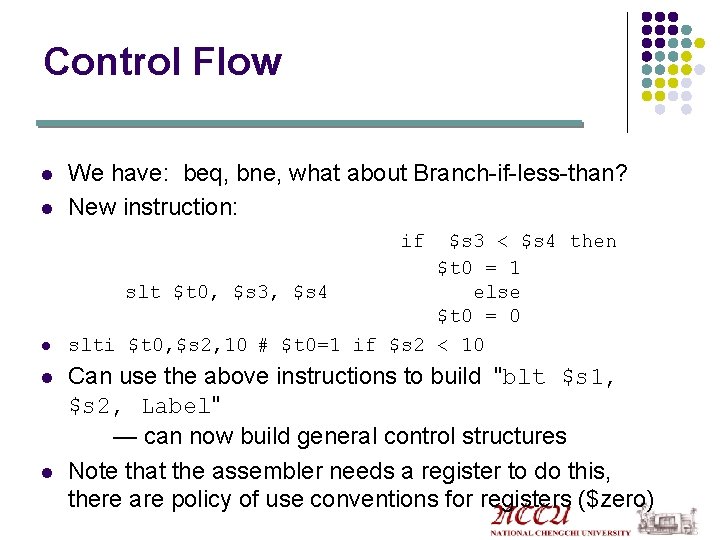

String Copy Procedure l C version void strcpy char x[], char y[] { int i; i=0; while ((x[i]=y[i])!=‘�’ i+=1; }

String Copy Procedure (MIPS) strcpy: addi sw add L 1: add lb add sb beq addi j L 2: lw addi jr $sp, -4 #adjust stack for 1 more item $s 0, 0($sp) #save $s 0, $zero #i=0+0 $t 1, $s 0, $a 1 # address of y[i] in $t 1 $t 2, 0($t 1) #$t 2=y[i] $t 3, $s 0, $a 0 #address of x[i] in $t 3 $t 2, 0($t 3) #x[i]=y[i] $t 2, $zero, L 2 # if y[i]==0 goto L 2 $s 0, 1 #i=i+1 L 1 # goto L 1 $s 0, 0($sp) #y[i]==0; end of string, restore #old $s 0 $sp, 4 #pop 1 word off stack $ra #return

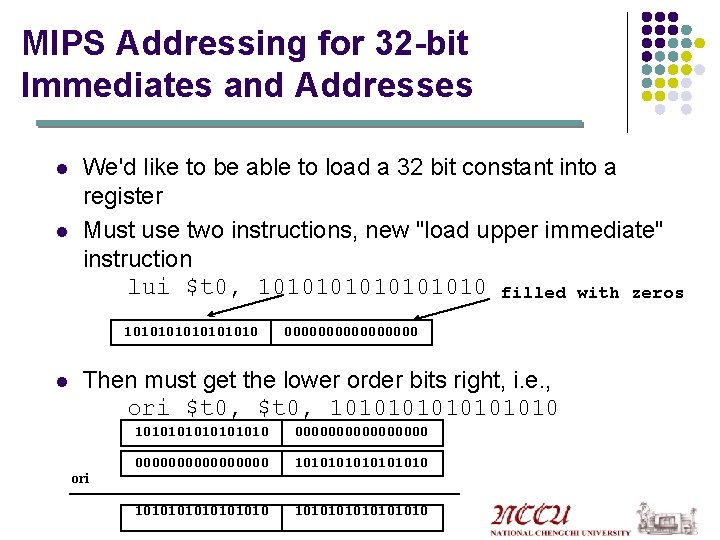

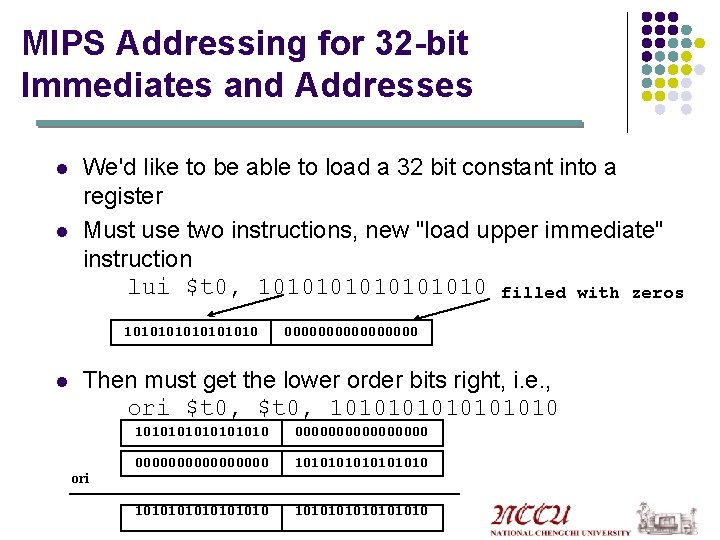

MIPS Addressing for 32 -bit Immediates and Addresses l l We'd like to be able to load a 32 bit constant into a register Must use two instructions, new "load upper immediate" instruction lui $t 0, 10101010 filled with zeros 10101010 l 00000000 Then must get the lower order bits right, i. e. , ori $t 0, 10101010 ori 10101010 0000000000000000 1010101010101010

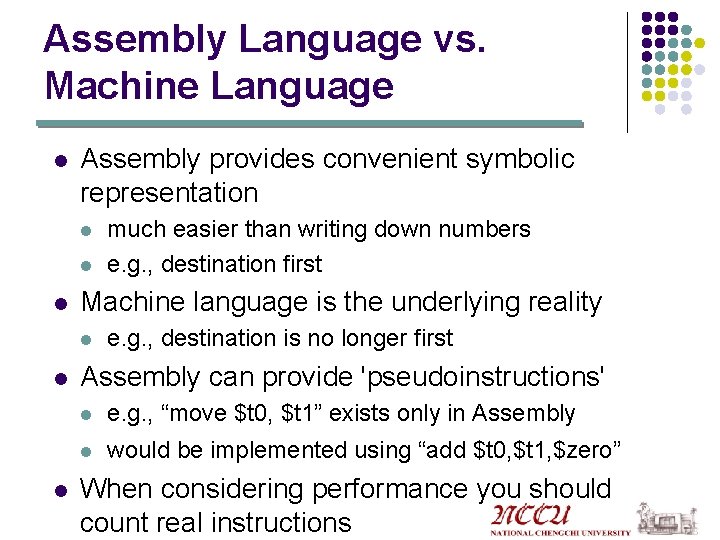

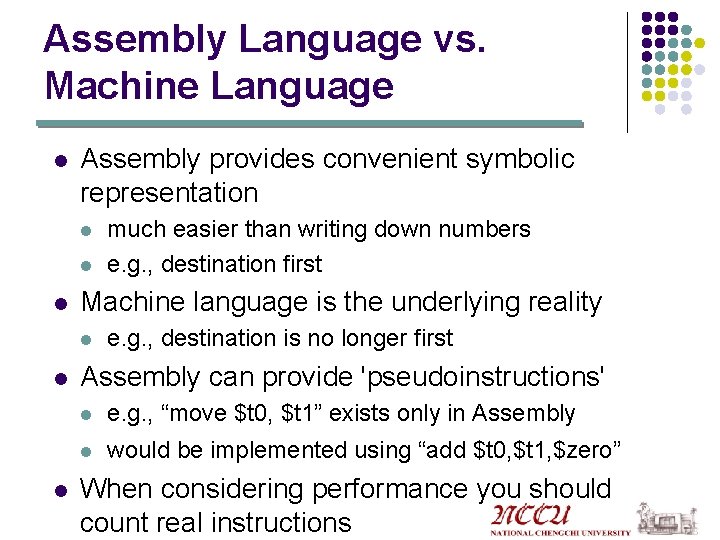

Assembly Language vs. Machine Language l Assembly provides convenient symbolic representation l l l Machine language is the underlying reality l l l much easier than writing down numbers e. g. , destination first e. g. , destination is no longer first Assembly can provide 'pseudoinstructions' l e. g. , “move $t 0, $t 1” exists only in Assembly l would be implemented using “add $t 0, $t 1, $zero” When considering performance you should count real instructions

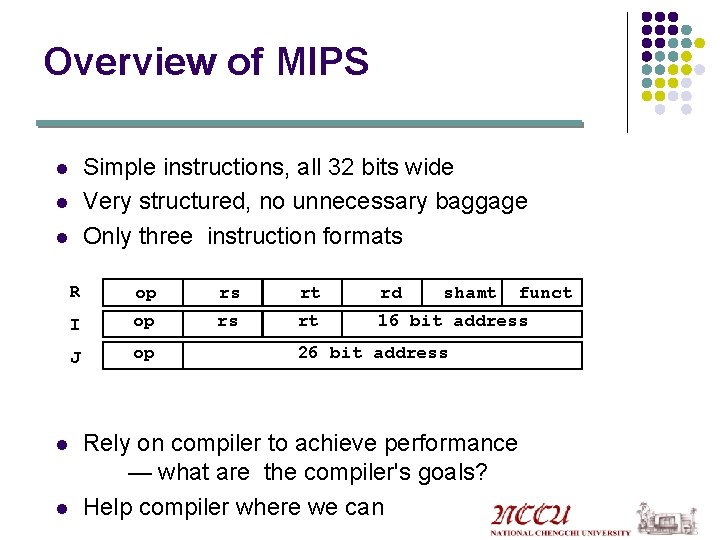

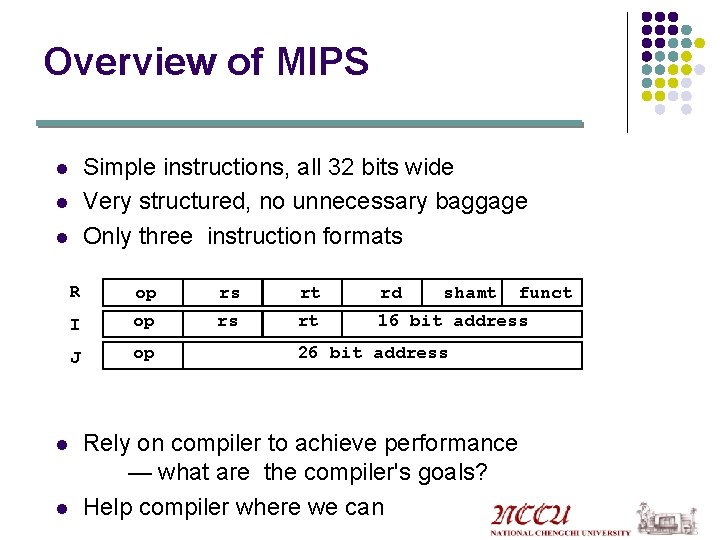

Overview of MIPS Simple instructions, all 32 bits wide Very structured, no unnecessary baggage Only three instruction formats l l l R op rs rt rd I op rs rt 16 bit address J op shamt funct 26 bit address Rely on compiler to achieve performance — what are the compiler's goals? Help compiler where we can

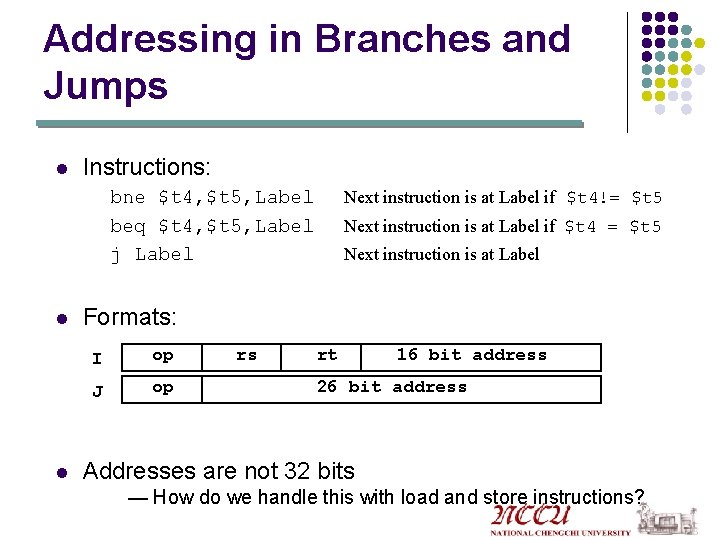

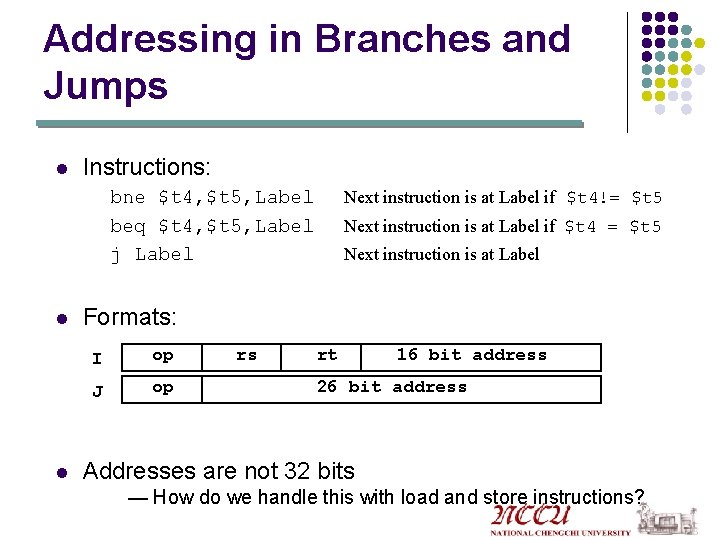

Addressing in Branches and Jumps l Instructions: bne $t 4, $t 5, Label beq $t 4, $t 5, Label j Label l l Next instruction is at Label if $t 4!= $t 5 Next instruction is at Label if $t 4 = $t 5 Next instruction is at Label Formats: I op J op rs rt 16 bit address 26 bit address Addresses are not 32 bits — How do we handle this with load and store instructions?

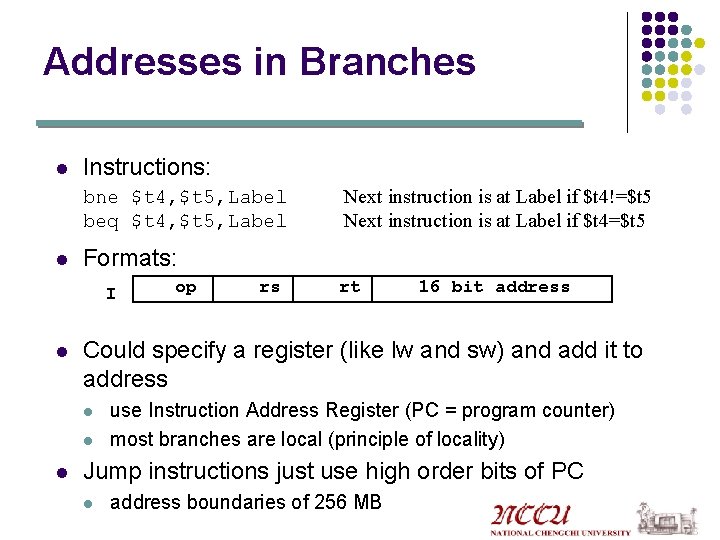

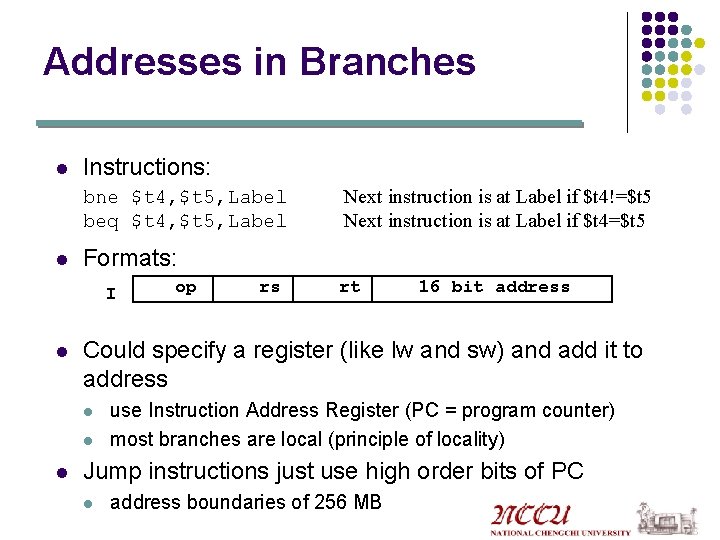

Addresses in Branches l Instructions: bne $t 4, $t 5, Label beq $t 4, $t 5, Label l Formats: I l op rs rt 16 bit address Could specify a register (like lw and sw) and add it to address l l l Next instruction is at Label if $t 4!=$t 5 Next instruction is at Label if $t 4=$t 5 use Instruction Address Register (PC = program counter) most branches are local (principle of locality) Jump instructions just use high order bits of PC l address boundaries of 256 MB

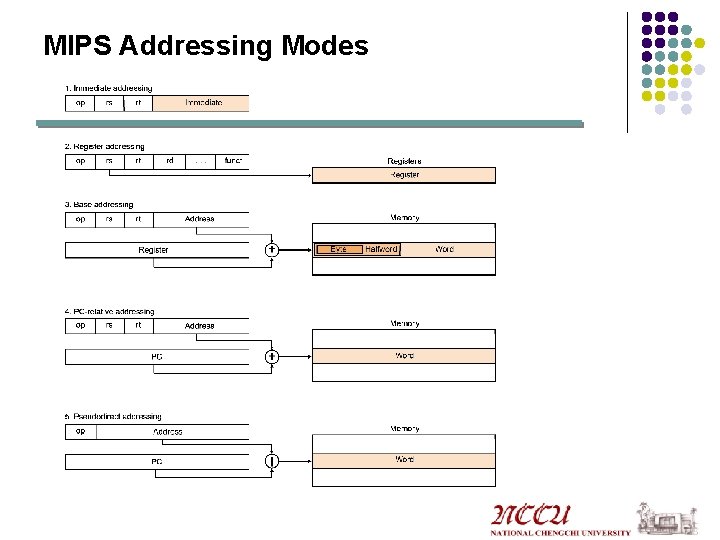

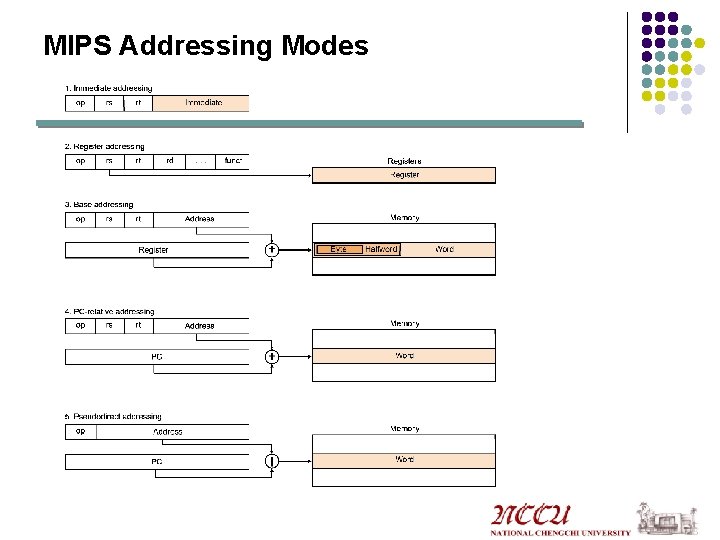

MIPS Addressing Modes

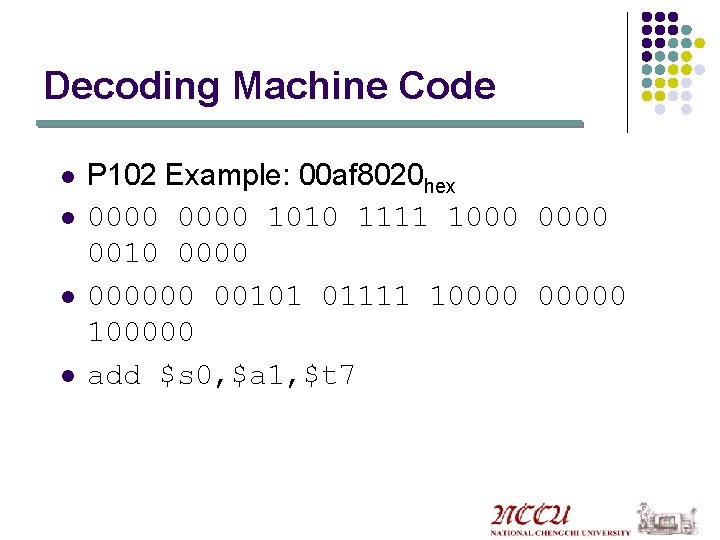

Decoding Machine Code l l P 102 Example: 00 af 8020 hex 0000 1010 1111 1000 0010 000000 00101 01111 100000 100000 add $s 0, $a 1, $t 7

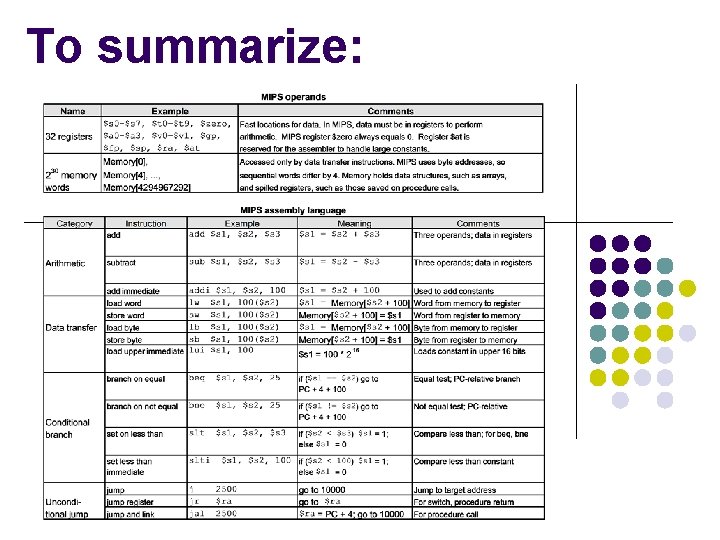

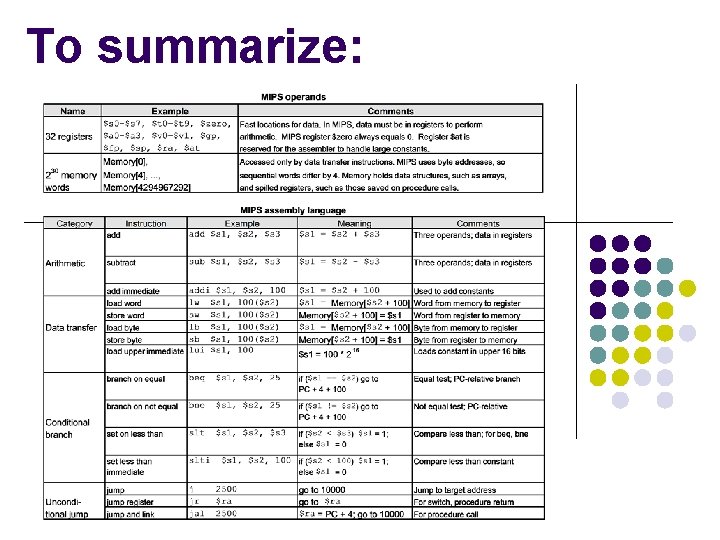

To summarize:

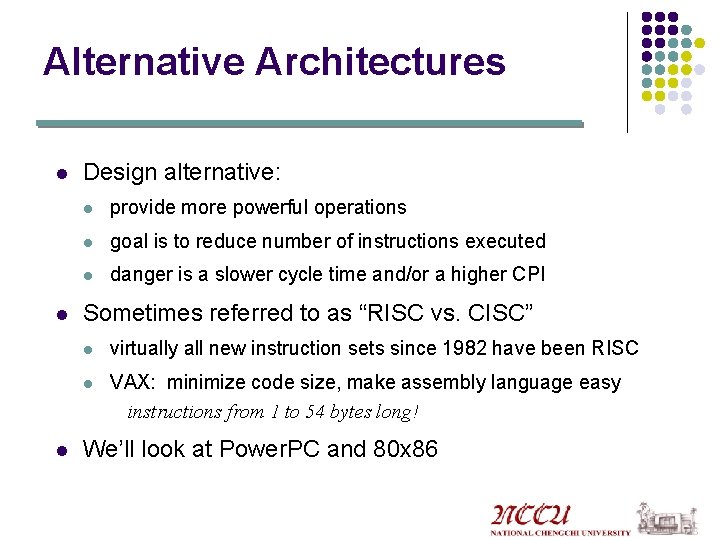

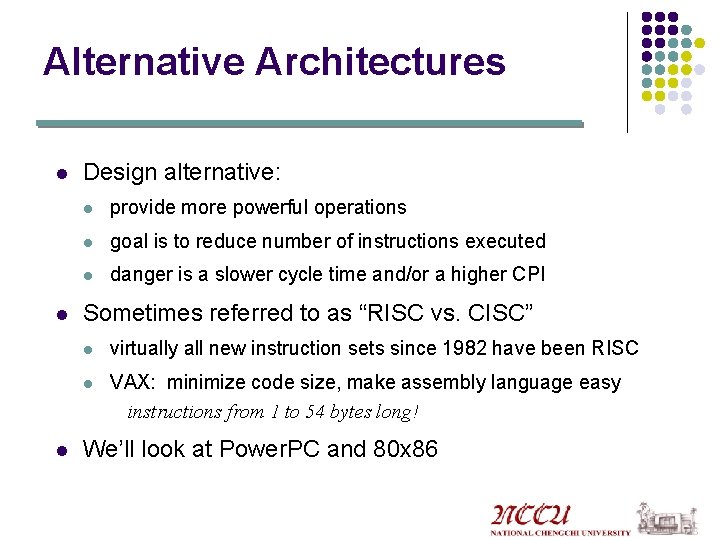

Alternative Architectures l l l Design alternative: l provide more powerful operations l goal is to reduce number of instructions executed l danger is a slower cycle time and/or a higher CPI Sometimes referred to as “RISC vs. CISC” l virtually all new instruction sets since 1982 have been RISC l VAX: minimize code size, make assembly language easy instructions from 1 to 54 bytes long! We’ll look at Power. PC and 80 x 86

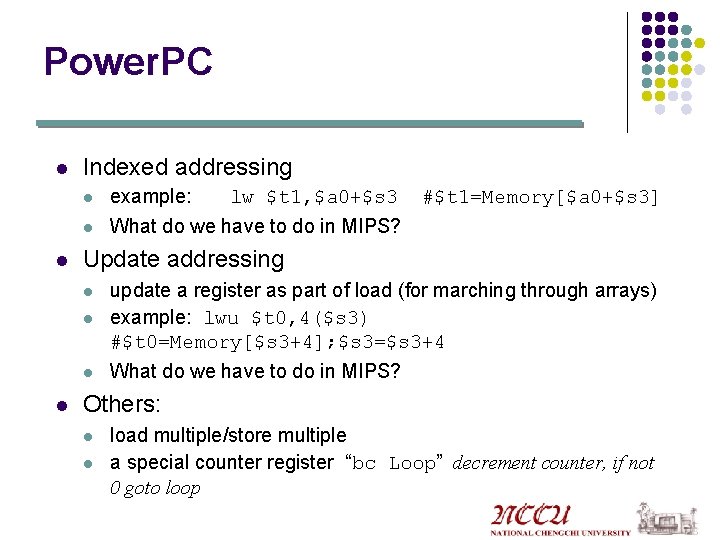

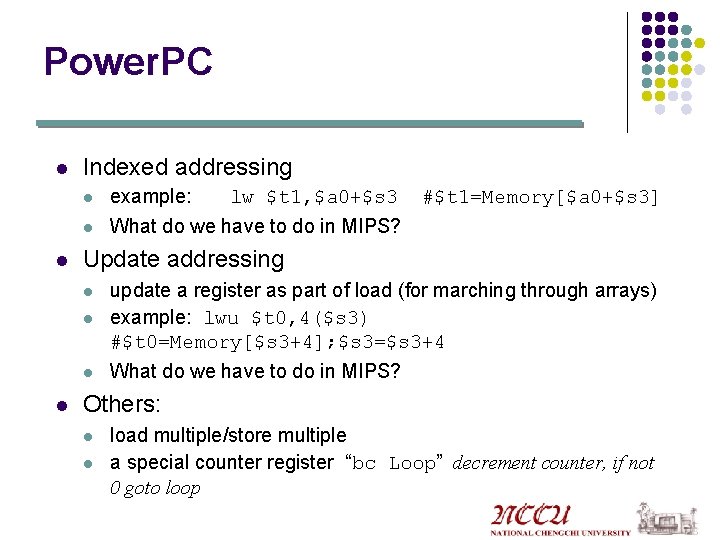

Power. PC l l Indexed addressing l example: l What do we have to do in MIPS? #$t 1=Memory[$a 0+$s 3] Update addressing l update a register as part of load (for marching through arrays) example: lwu $t 0, 4($s 3) #$t 0=Memory[$s 3+4]; $s 3=$s 3+4 l What do we have to do in MIPS? l l lw $t 1, $a 0+$s 3 Others: l l load multiple/store multiple a special counter register “bc Loop” decrement counter, if not 0 goto loop

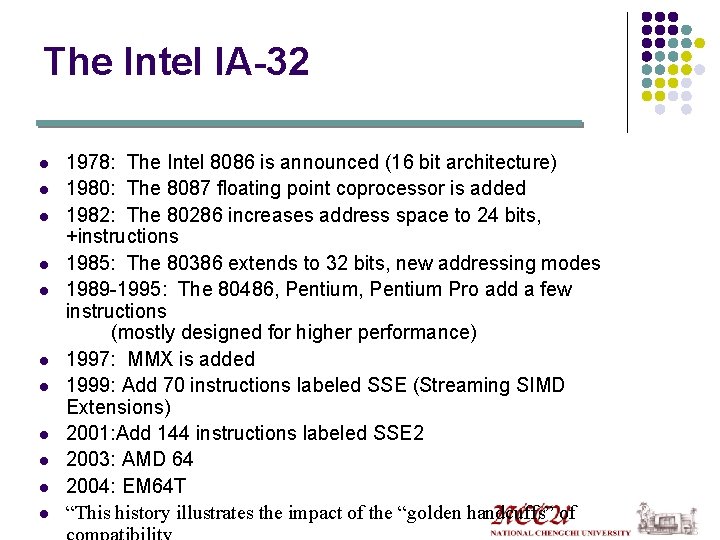

The Intel IA-32 l l l 1978: The Intel 8086 is announced (16 bit architecture) 1980: The 8087 floating point coprocessor is added 1982: The 80286 increases address space to 24 bits, +instructions 1985: The 80386 extends to 32 bits, new addressing modes 1989 -1995: The 80486, Pentium Pro add a few instructions (mostly designed for higher performance) 1997: MMX is added 1999: Add 70 instructions labeled SSE (Streaming SIMD Extensions) 2001: Add 144 instructions labeled SSE 2 2003: AMD 64 2004: EM 64 T “This history illustrates the impact of the “golden handcuffs” of

A dominant architecture: 80 x 86 l l See your textbook for a more detailed description Complexity: l l l Instructions from 1 to 17 bytes long one operand must act as both a source and destination one operand can come from memory complex addressing modes e. g. , “base or scaled index with 8 or 32 bit displacement” Saving grace: l l the most frequently used instructions are not too difficult to build compilers avoid the portions of the architecture that are slow “what the 80 x 86 lacks in style is made up in quantity,

Summary l Instruction complexity is only one variable l l Design Principles: l l lower instruction count vs. higher CPI / lower clock rate simplicity favors regularity smaller is faster good design demands compromise make the common case fast Instruction set architecture l a very important abstraction indeed!