CHAPTER 2 DIGITAL ELECTRONICS WITH MULTISIM Multi Sim

- Slides: 40

CHAPTER 2: DIGITAL ELECTRONICS WITH MULTISIM

Multi. Sim: Arithmetic Circuits, Flip-flops, Counters, Shift Registers and Multiplexers

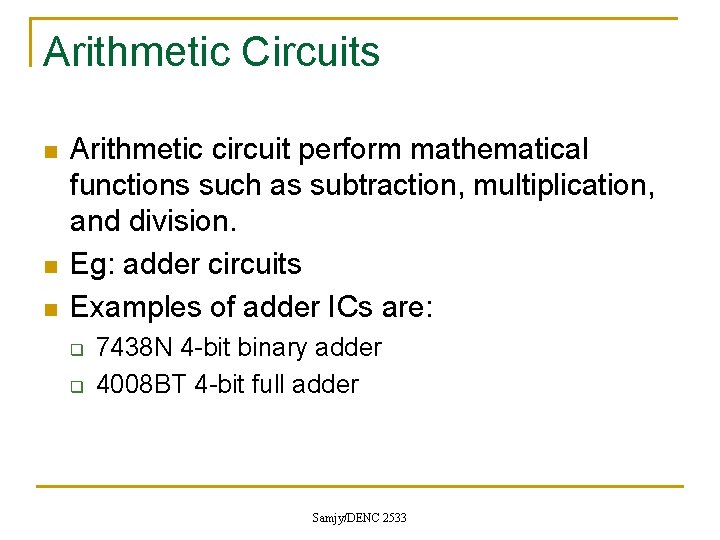

Arithmetic Circuits n n n Arithmetic circuit perform mathematical functions such as subtraction, multiplication, and division. Eg: adder circuits Examples of adder ICs are: q q 7438 N 4 -bit binary adder 4008 BT 4 -bit full adder Samjy/DENC 2533

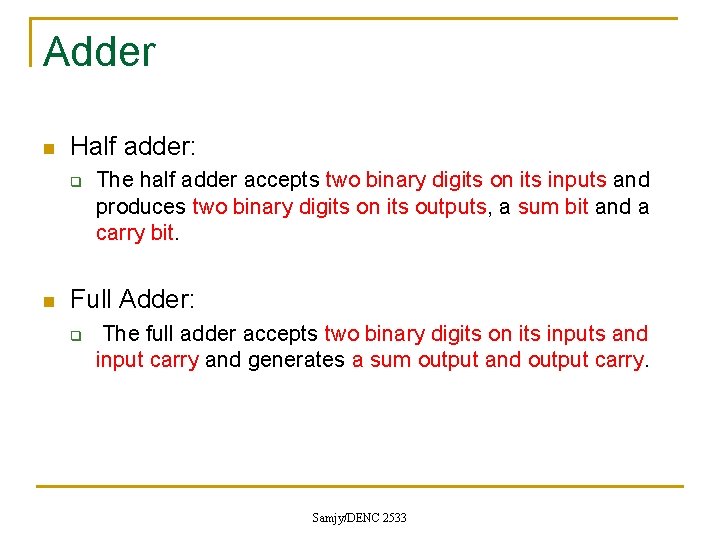

Adder n Half adder: q n The half adder accepts two binary digits on its inputs and produces two binary digits on its outputs, a sum bit and a carry bit. Full Adder: q The full adder accepts two binary digits on its inputs and input carry and generates a sum output and output carry. Samjy/DENC 2533

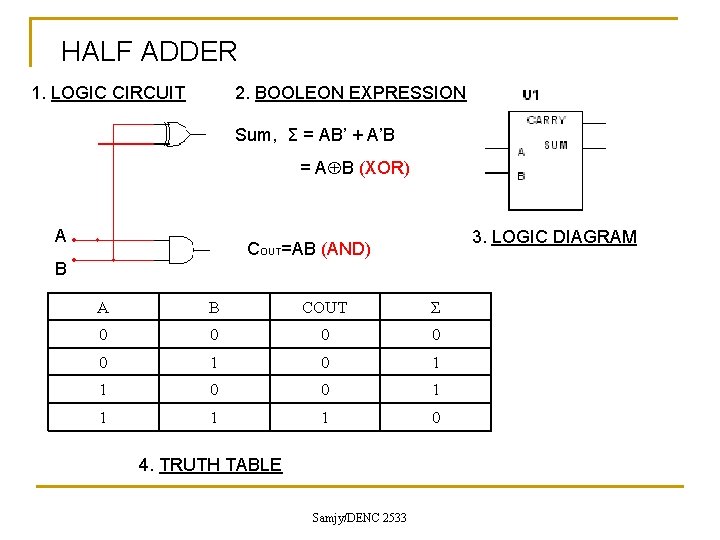

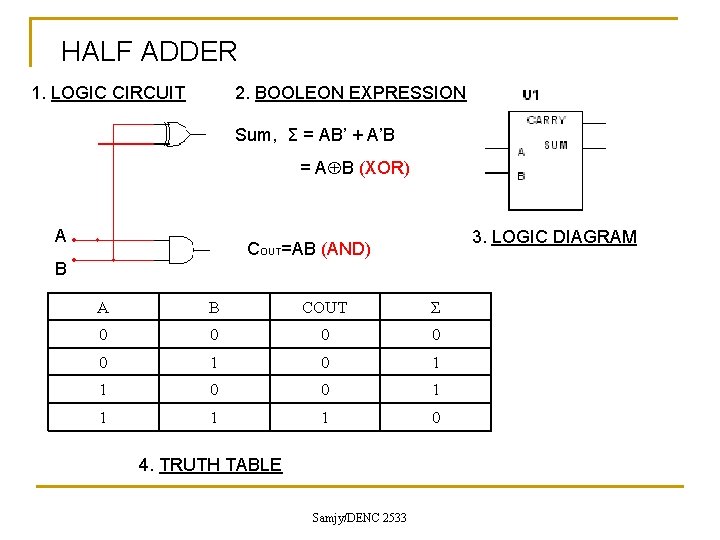

HALF ADDER 1. LOGIC CIRCUIT 2. BOOLEON EXPRESSION Sum, Σ = AB’ + A’B = A B (XOR) A 3. LOGIC DIAGRAM COUT=AB (AND) B A B COUT Σ 0 0 0 1 1 0 4. TRUTH TABLE Samjy/DENC 2533

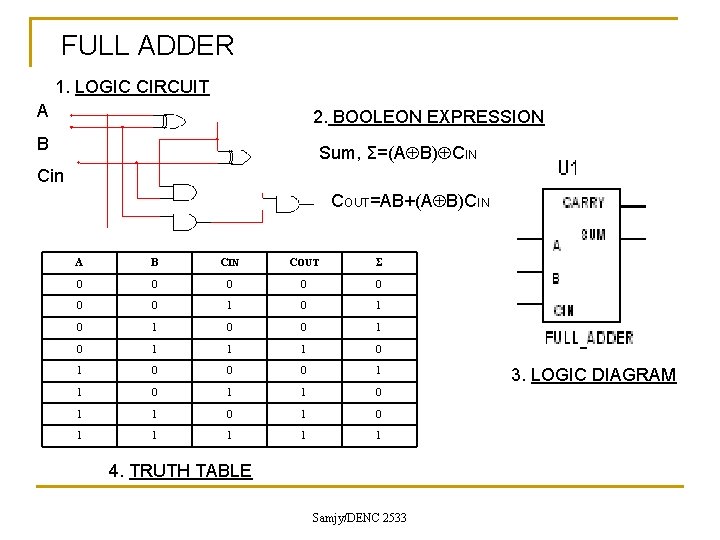

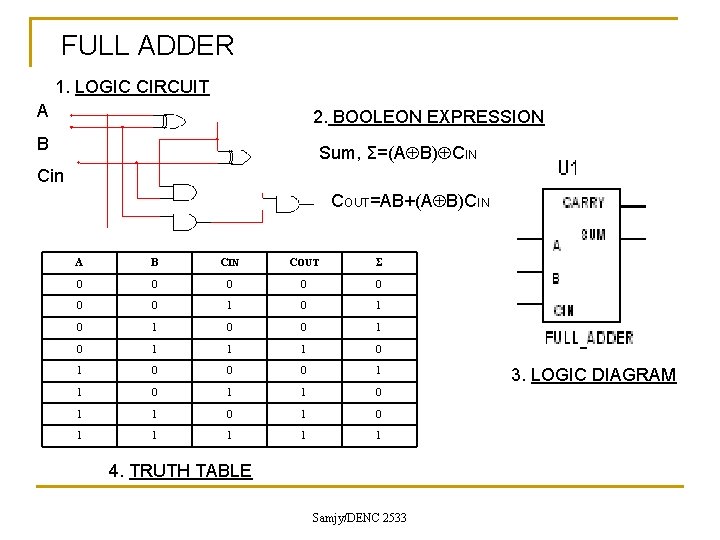

FULL ADDER 1. LOGIC CIRCUIT A 2. BOOLEON EXPRESSION B Sum, Σ=(A B) CIN Cin COUT=AB+(A B)CIN A B CIN COUT Σ 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 4. TRUTH TABLE Samjy/DENC 2533 3. LOGIC DIAGRAM

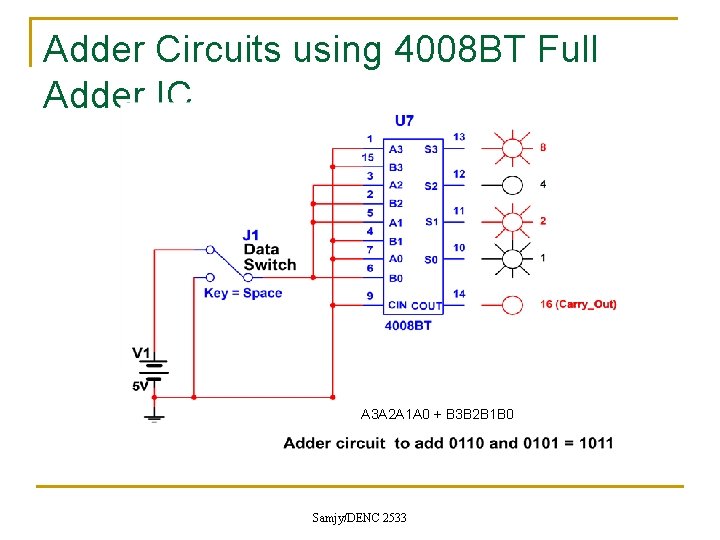

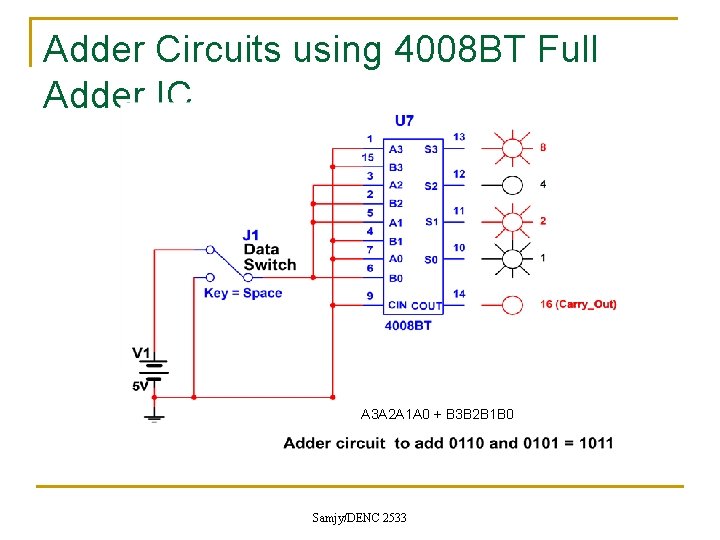

Adder Circuits using 4008 BT Full Adder IC A 3 A 2 A 1 A 0 + B 3 B 2 B 1 B 0 Samjy/DENC 2533

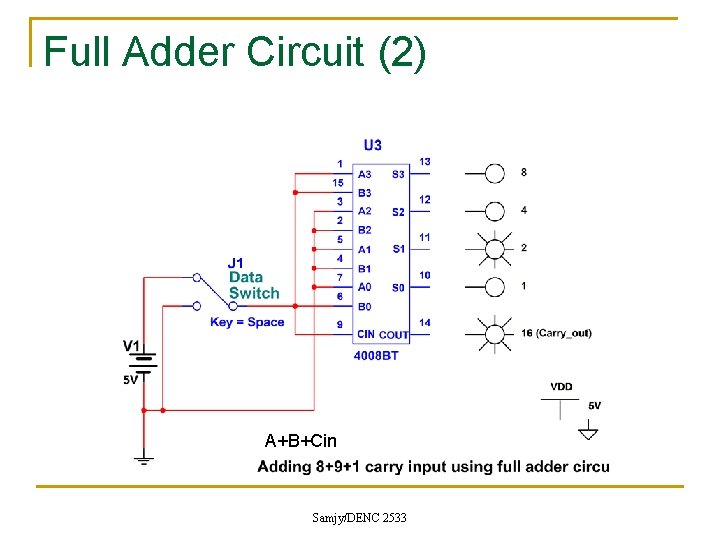

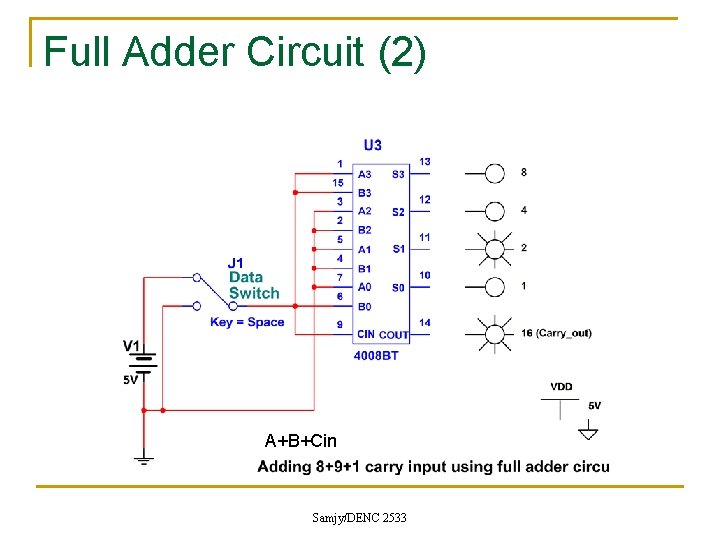

Full Adder Circuit (2) A+B+Cin Samjy/DENC 2533

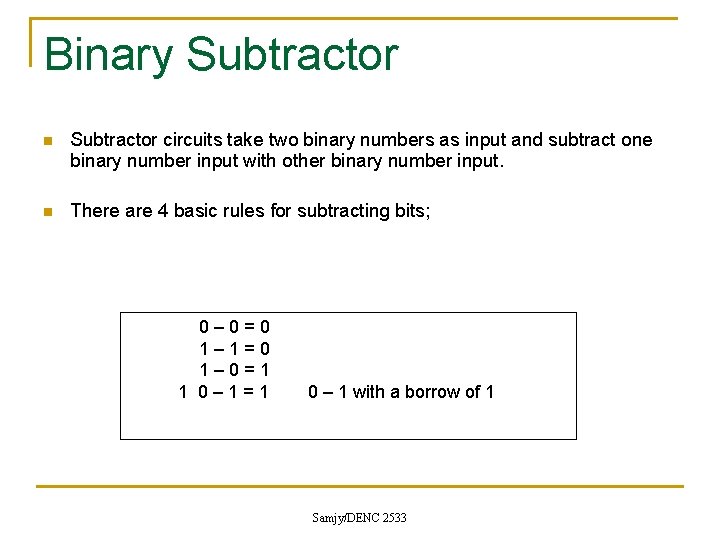

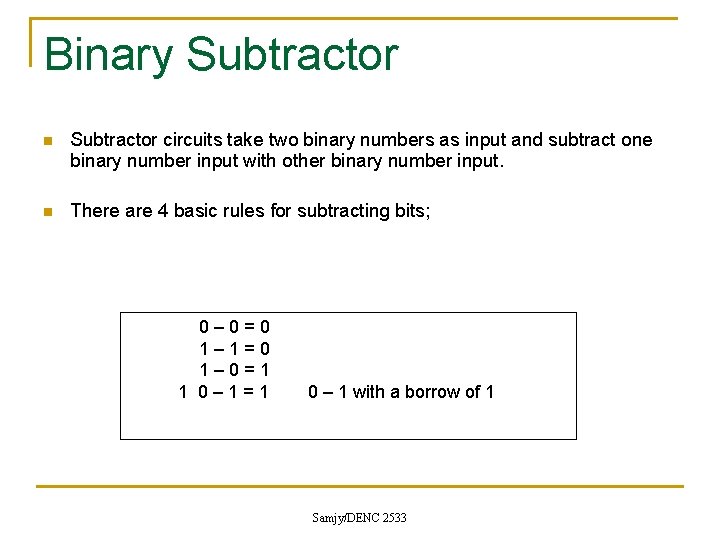

Binary Subtractor n Subtractor circuits take two binary numbers as input and subtract one binary number input with other binary number input. n There are 4 basic rules for subtracting bits; 0– 0=0 1– 1=0 1– 0=1 1 0– 1=1 0 – 1 with a borrow of 1 Samjy/DENC 2533

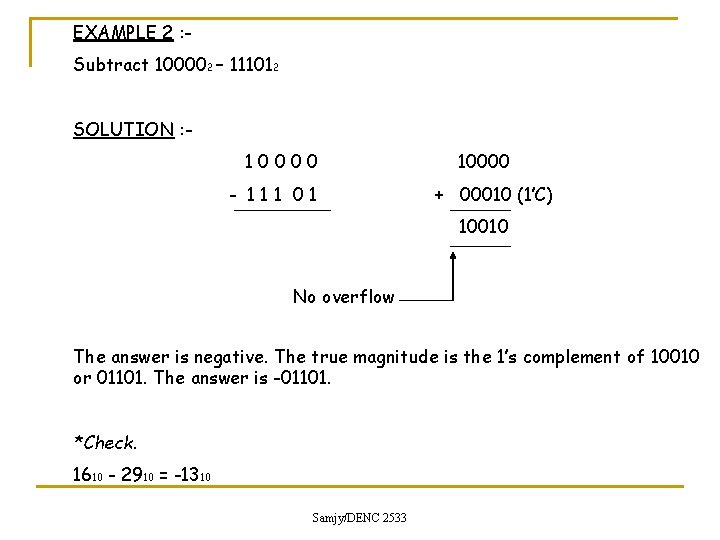

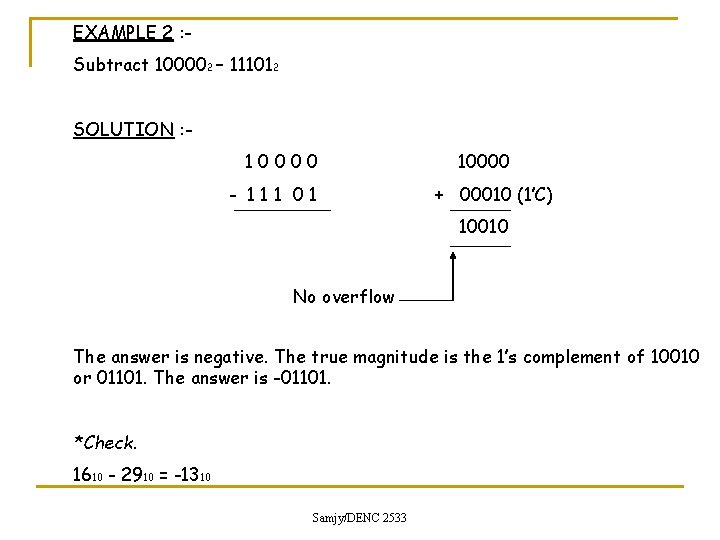

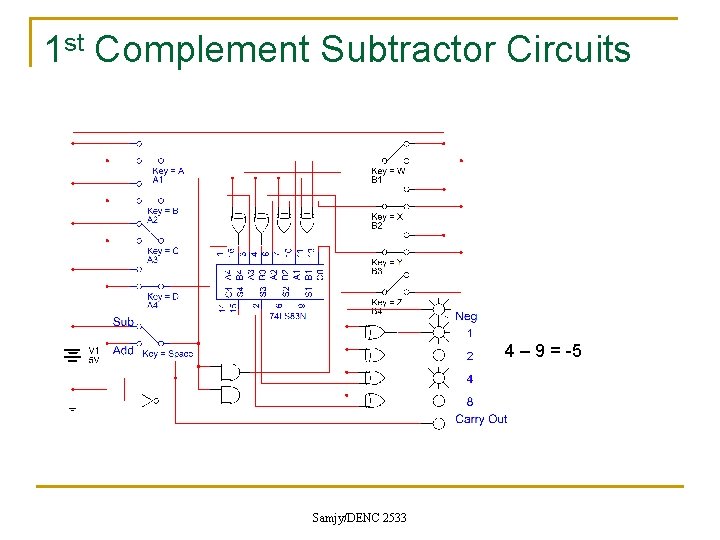

EXAMPLE 2 : Subtract 100002 – 111012 SOLUTION : 10000 - 111 01 10000 + 00010 (1’C) 10010 No overflow The answer is negative. The true magnitude is the 1’s complement of 10010 or 01101. The answer is -01101. *Check. 1610 - 2910 = -1310 Samjy/DENC 2533

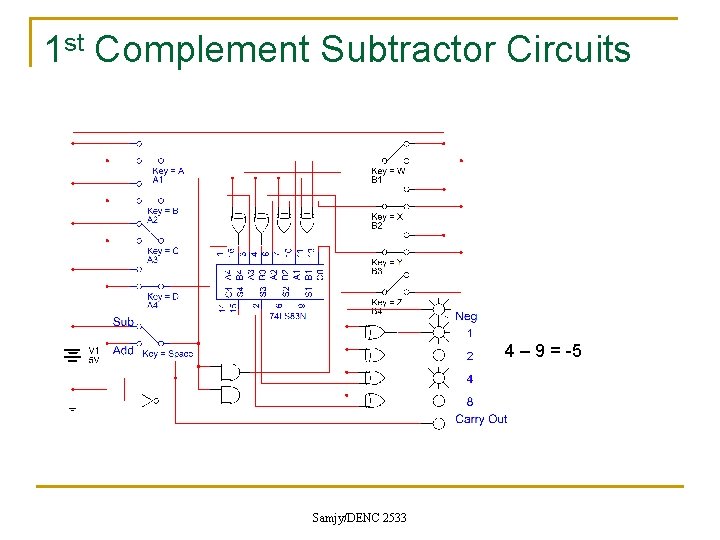

1 st Complement Subtractor Circuits 4 – 9 = -5 Samjy/DENC 2533

Sequential Circuit: Flip-Flops(ffs) n Is a logic circuit with a memory characteristics such that its output (Q) will go to a new stage in response to an input pulse, and will remain that new state after the input pulse is terminated. n Is a sequential circuit, whose output changes when its CLOCK input triggers. n Several types of edge-triggered ffs, such as D, JK, SC ff. n Synchronous control input – ffs is synchronous with PGT/NGT (positive/negative edge triggered) signal applied to CLOCK. n Asynchronous control input-set the ffs to ‘ 1’state or ‘ 0’ state by its 2 asynchronous inputs: PRESET and CLEAR. Samjy/DENC 2533

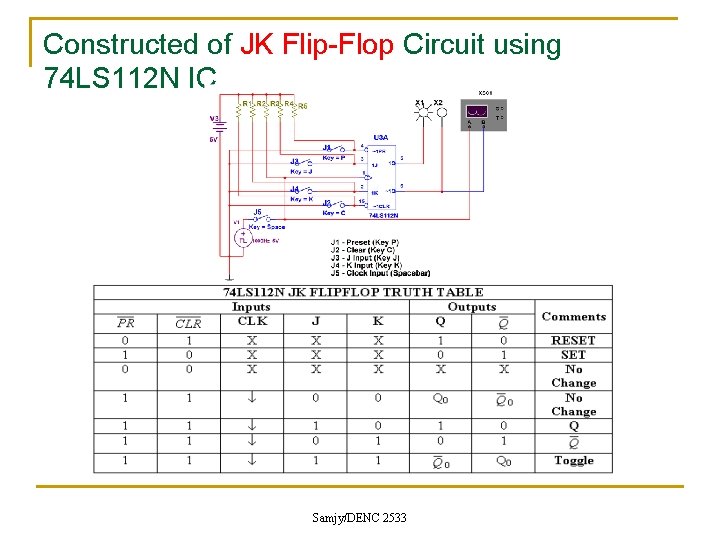

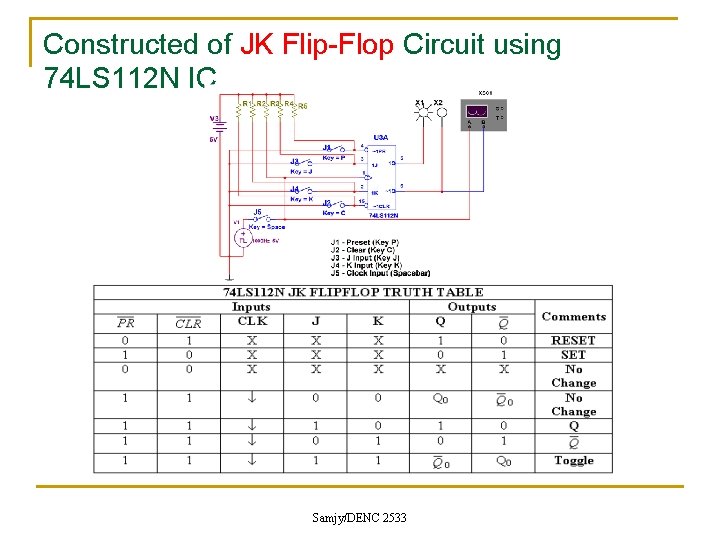

Constructed of JK Flip-Flop Circuit using 74 LS 112 N IC Samjy/DENC 2533

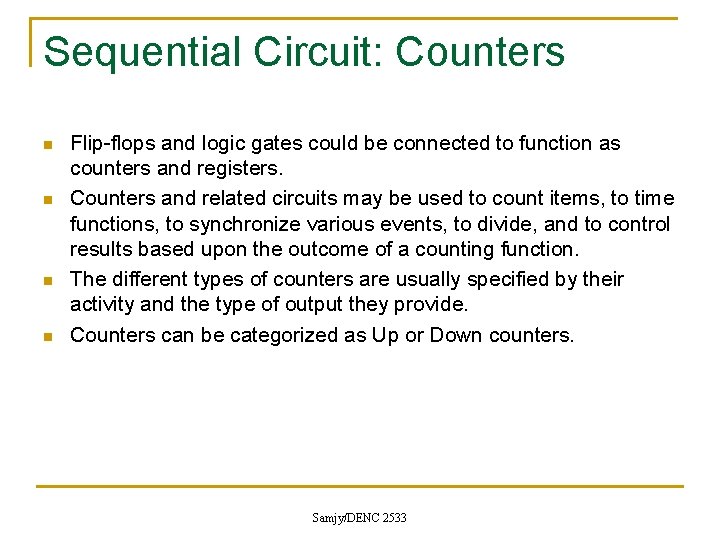

Sequential Circuit: Counters n n Flip-flops and logic gates could be connected to function as counters and registers. Counters and related circuits may be used to count items, to time functions, to synchronize various events, to divide, and to control results based upon the outcome of a counting function. The different types of counters are usually specified by their activity and the type of output they provide. Counters can be categorized as Up or Down counters. Samjy/DENC 2533

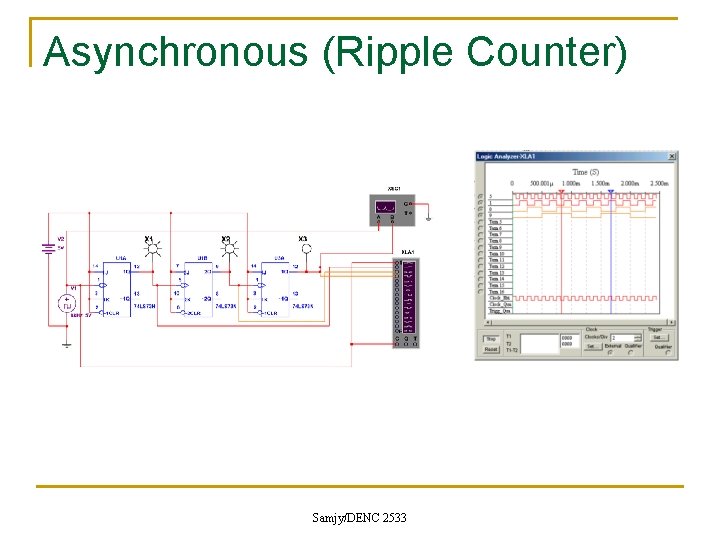

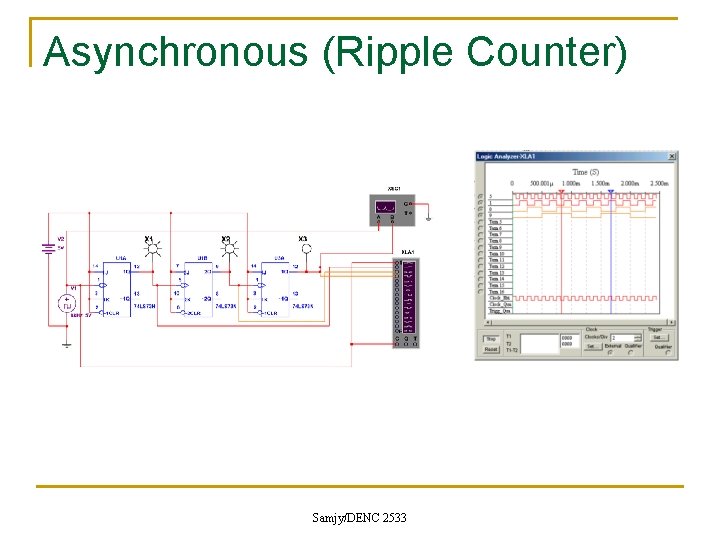

Asynchronous and Synchronous Counters n A synchronous counter circuit has the operation of flip-flops is synchronized by a common clock pulse so that when several flip flops must change state, the state changes occur simultaneously. n Asynchronous counters (Ripple counter) which the state change of one flip flop triggers the next flip flop in line. It uses the external event to directly SET or CLEAR a flip-flop when it occurs. Each flip-flop in the ripple counter is clocked by the output from the previous flip-flop. Only the first flip-flop is clocked by an external clock. Samjy/DENC 2533

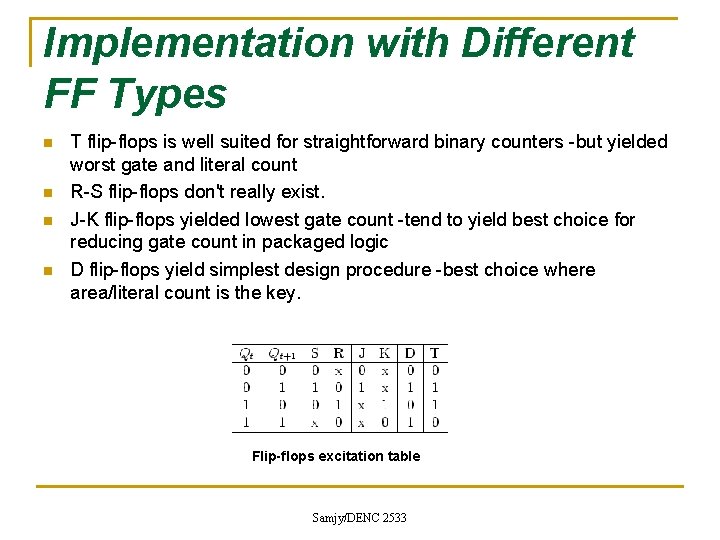

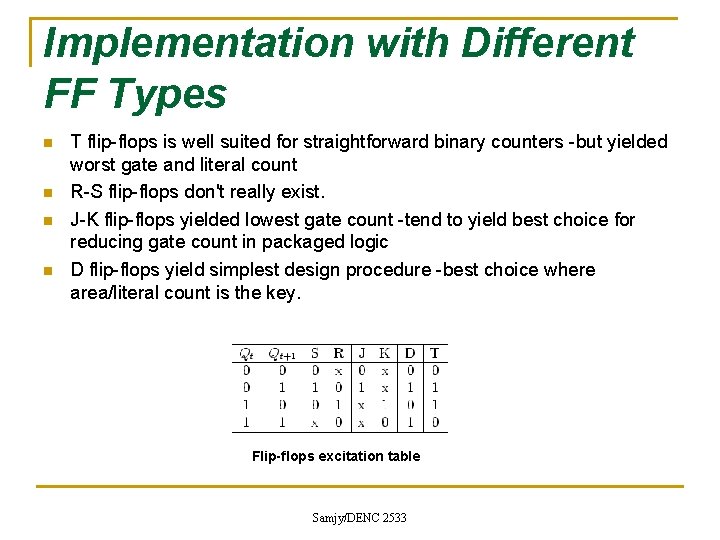

Implementation with Different FF Types n n T flip-flops is well suited for straightforward binary counters -but yielded worst gate and literal count R-S flip-flops don't really exist. J-K flip-flops yielded lowest gate count -tend to yield best choice for reducing gate count in packaged logic D flip-flops yield simplest design procedure -best choice where area/literal count is the key. Flip-flops excitation table Samjy/DENC 2533

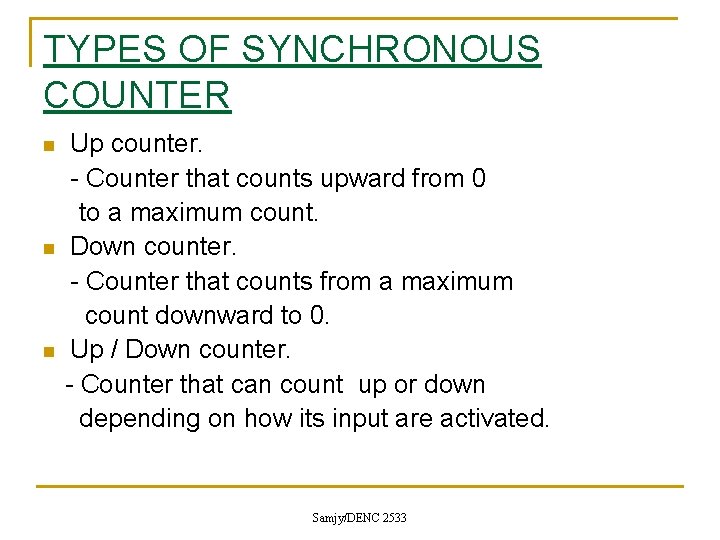

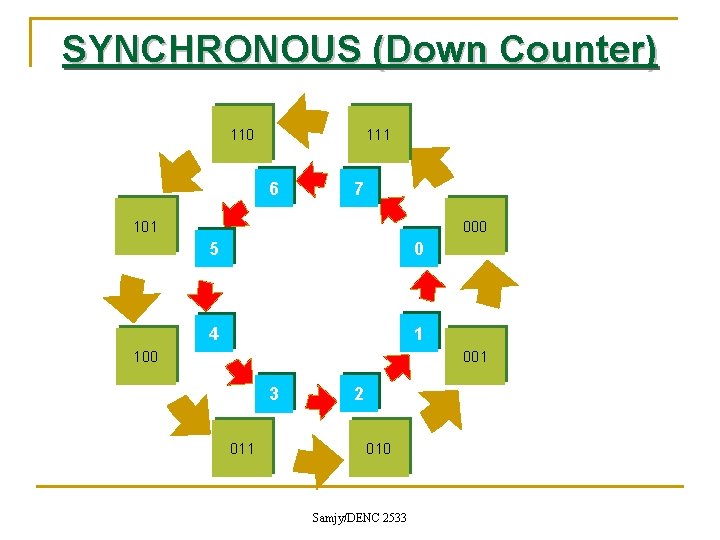

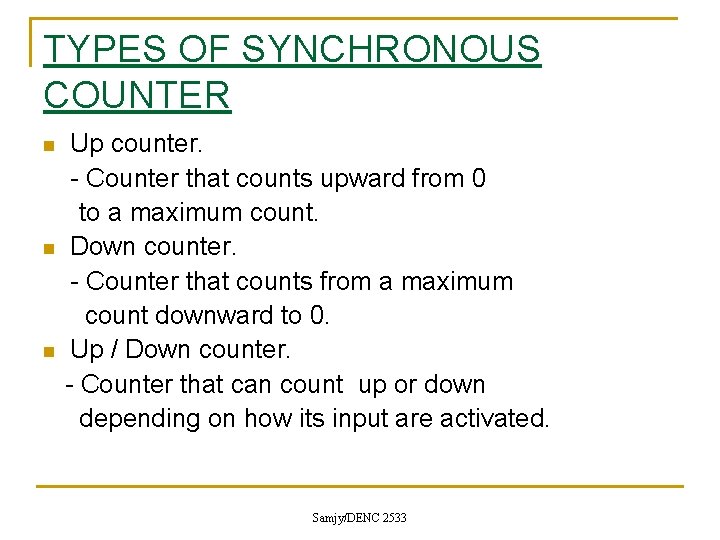

TYPES OF SYNCHRONOUS COUNTER n n n Up counter. - Counter that counts upward from 0 to a maximum count. Down counter. - Counter that counts from a maximum count downward to 0. Up / Down counter. - Counter that can count up or down depending on how its input are activated. Samjy/DENC 2533

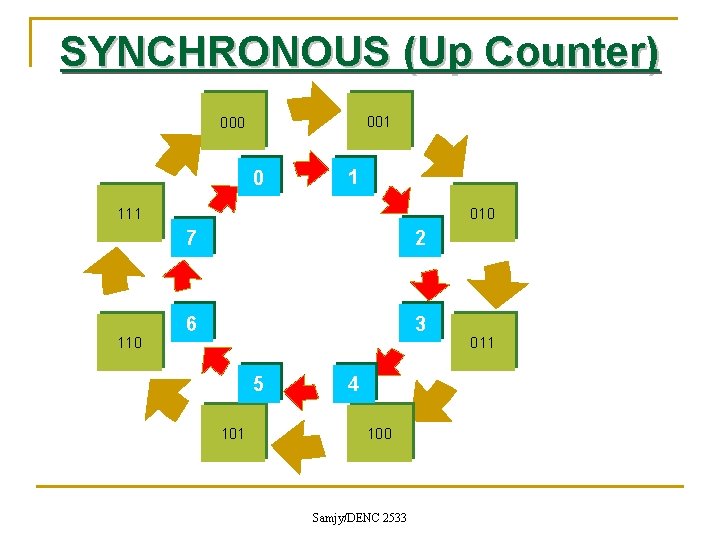

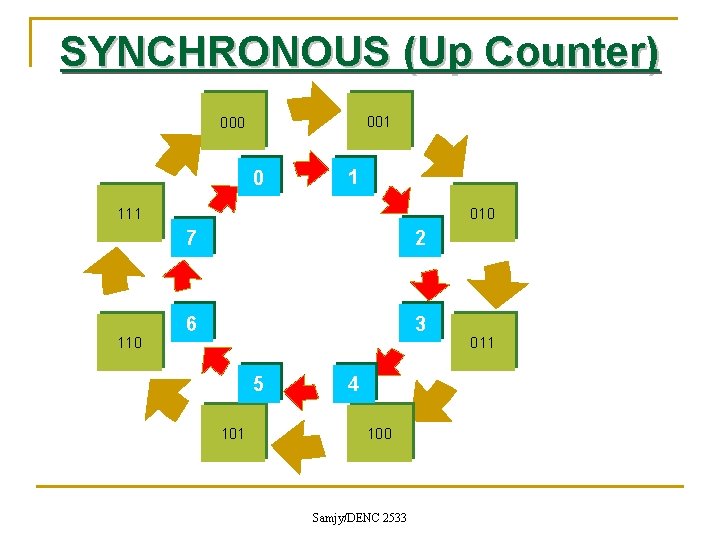

SYNCHRONOUS (Up Counter) 001 000 0 1 010 111 110 7 2 6 3 5 101 4 100 Samjy/DENC 2533 011

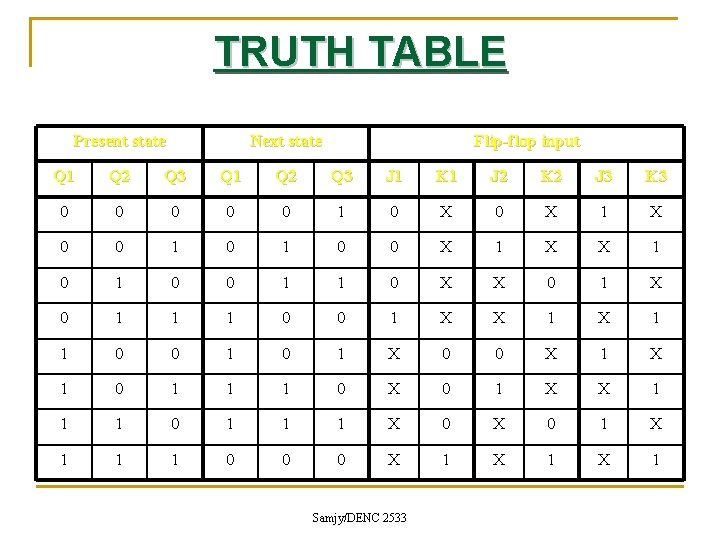

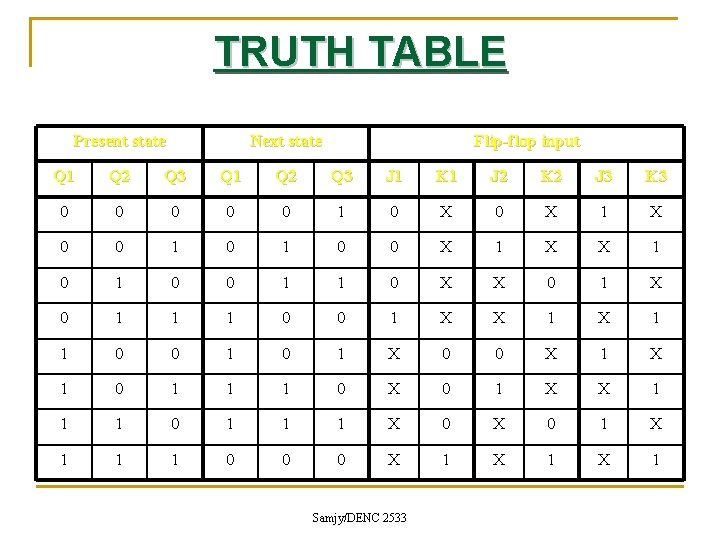

TRUTH TABLE Present state Next state Flip-flop input Q 1 Q 2 Q 3 J 1 K 1 J 2 K 2 J 3 K 3 0 0 0 1 0 X 1 X 0 0 1 0 0 X 1 X X 1 0 0 1 1 0 X X 0 1 1 1 0 0 1 X X 1 1 0 0 1 X 0 0 X 1 0 1 1 1 0 X 0 1 X X 1 1 1 0 1 1 1 X 0 1 X 1 1 1 0 0 0 X 1 X 1 Samjy/DENC 2533

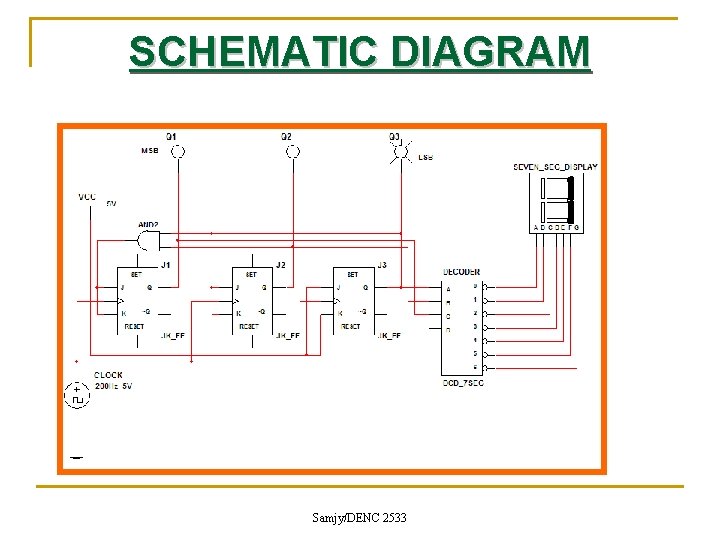

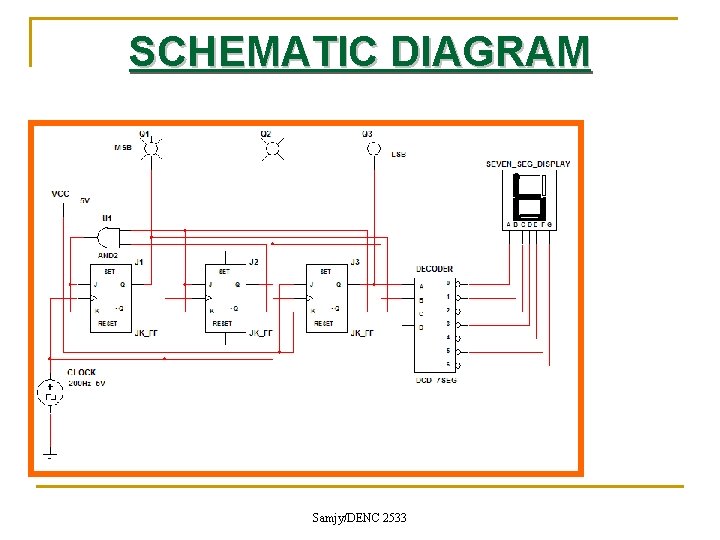

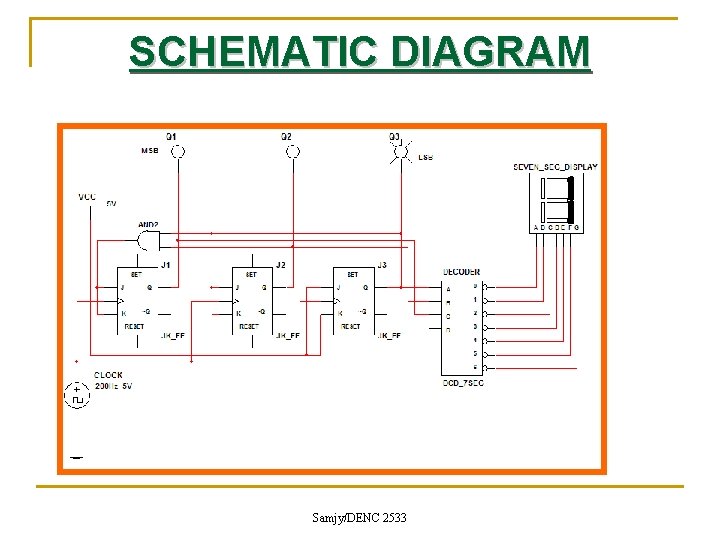

SCHEMATIC DIAGRAM Samjy/DENC 2533

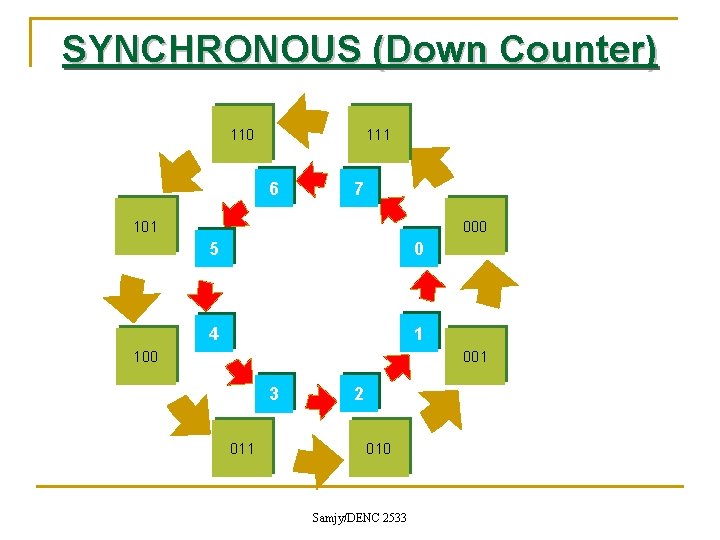

SYNCHRONOUS (Down Counter) 111 110 6 7 000 101 5 0 4 1 001 100 3 011 2 010 Samjy/DENC 2533

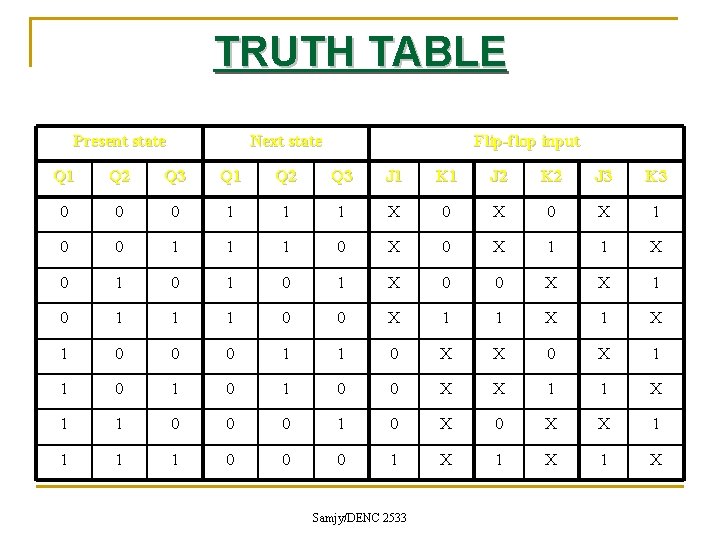

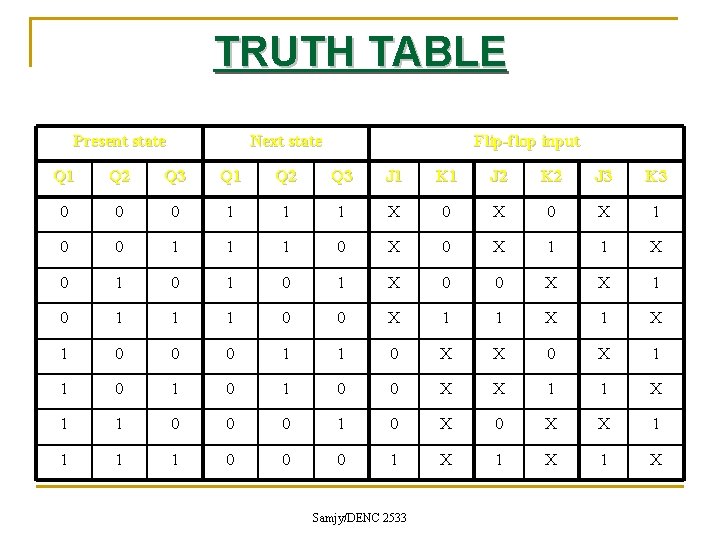

TRUTH TABLE Present state Next state Flip-flop input Q 1 Q 2 Q 3 J 1 K 1 J 2 K 2 J 3 K 3 0 0 0 1 1 1 X 0 X 1 0 0 1 1 1 0 X 1 1 X 0 1 0 1 X 0 0 X X 1 0 1 1 1 0 0 X 1 1 X 1 0 0 0 1 1 0 X X 0 X 1 1 0 1 0 0 X X 1 1 0 0 0 1 X 1 X Samjy/DENC 2533

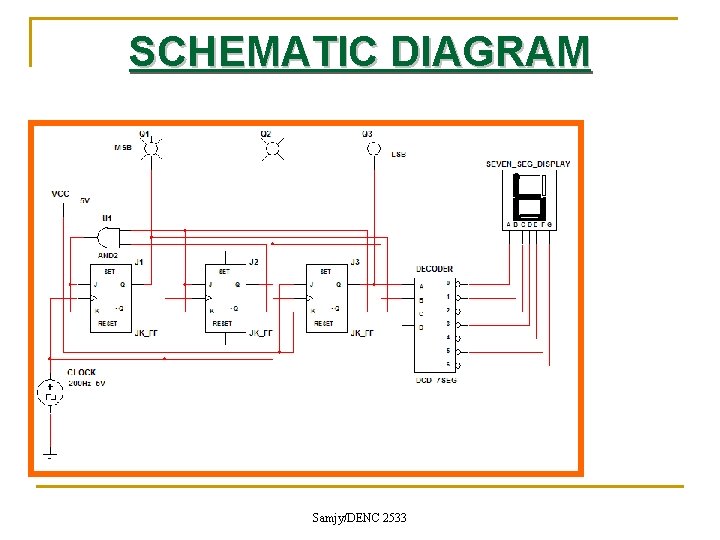

SCHEMATIC DIAGRAM Samjy/DENC 2533

Asynchronous (Ripple Counter) Samjy/DENC 2533

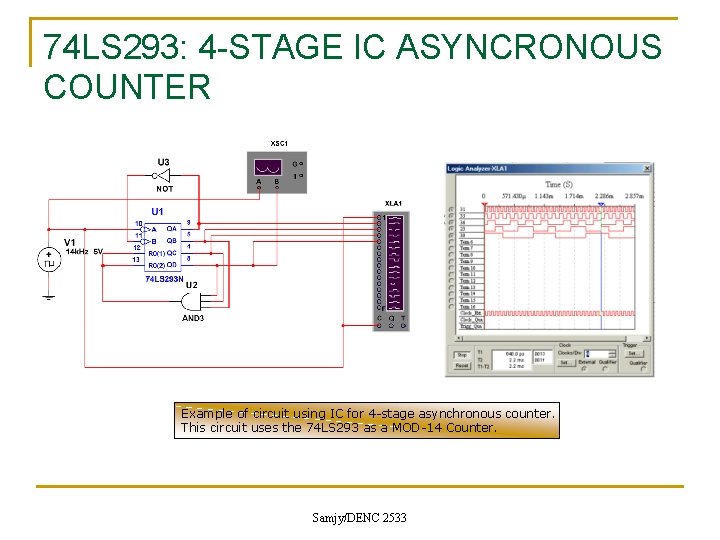

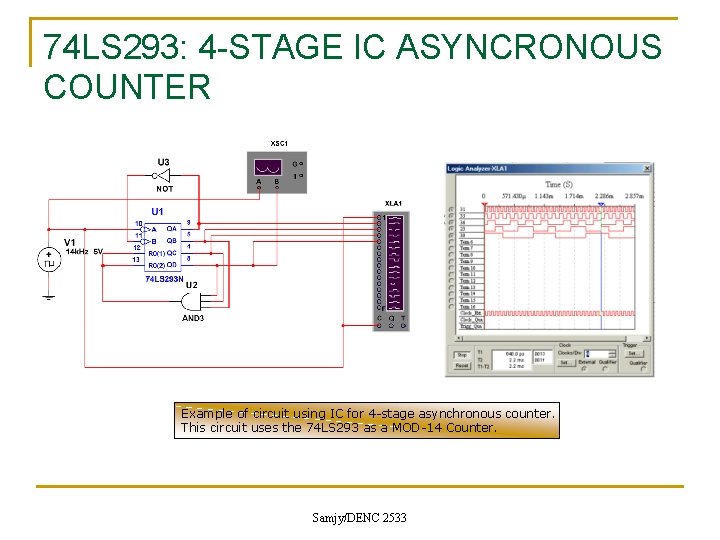

74 LS 293: 4 -STAGE IC ASYNCRONOUS COUNTER Example of circuit using IC for 4 -stage asynchronous counter. This circuit uses the 74 LS 293 as a MOD-14 Counter. Samjy/DENC 2533

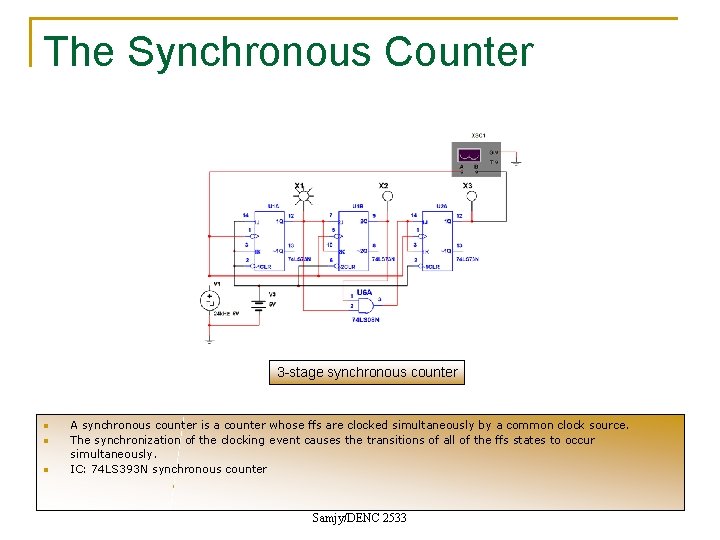

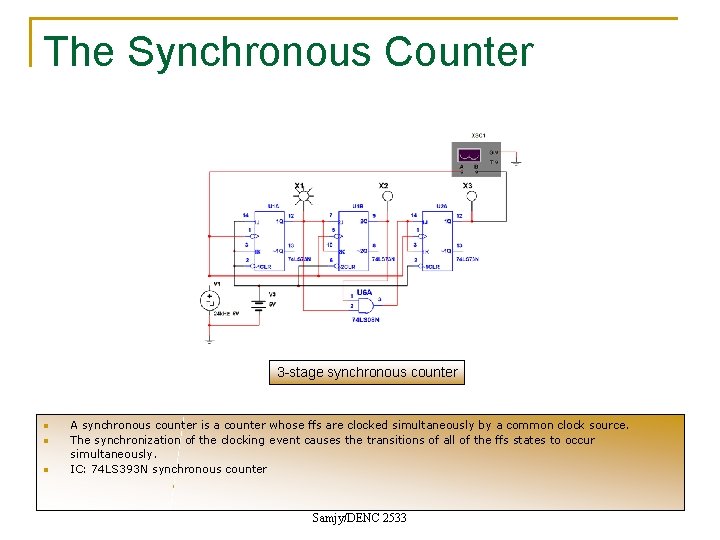

The Synchronous Counter 3 -stage synchronous counter n n n A synchronous counter is a counter whose ffs are clocked simultaneously by a common clock source. The synchronization of the clocking event causes the transitions of all of the ffs states to occur simultaneously. IC: 74 LS 393 N synchronous counter Samjy/DENC 2533

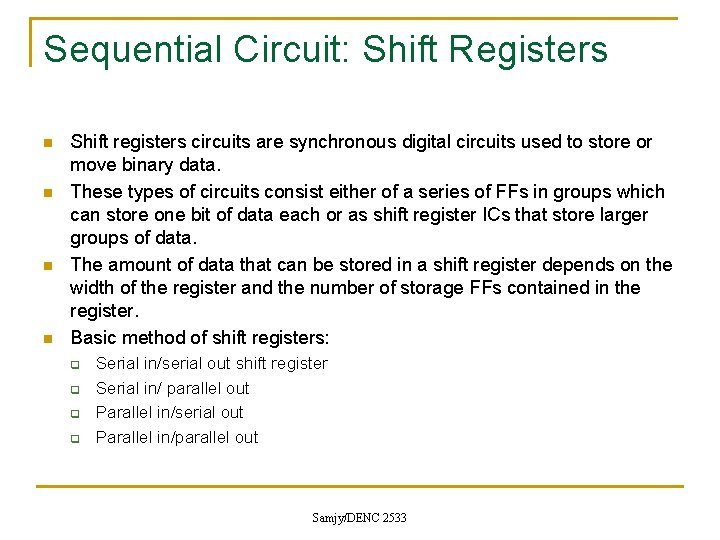

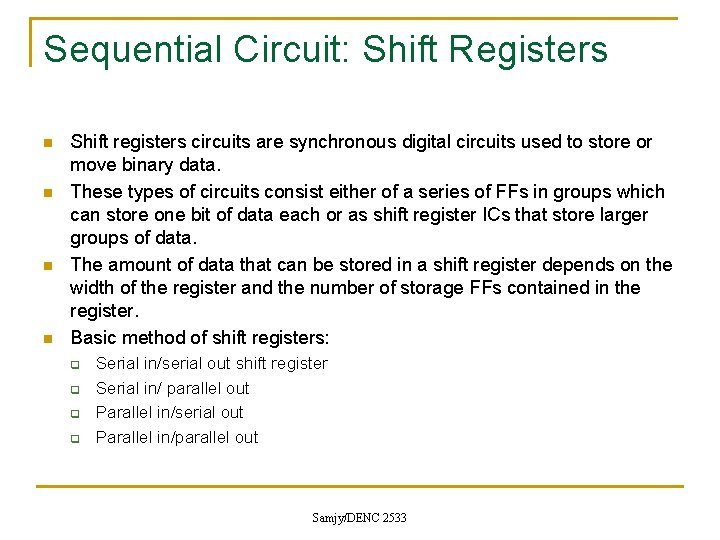

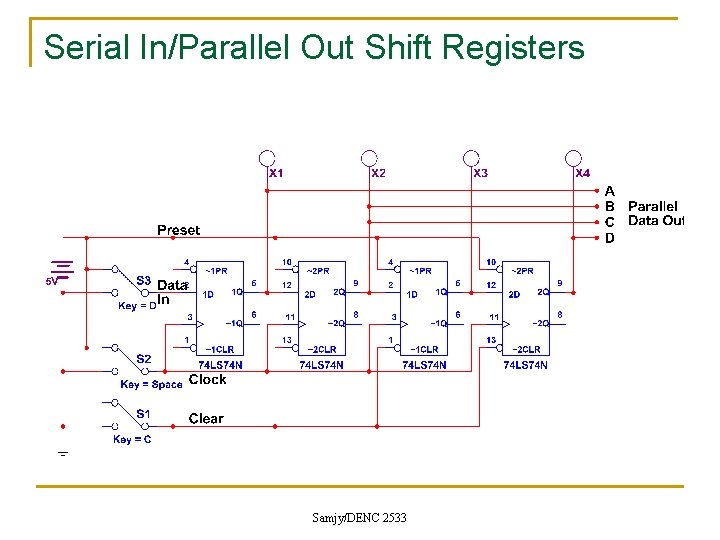

Sequential Circuit: Shift Registers n n Shift registers circuits are synchronous digital circuits used to store or move binary data. These types of circuits consist either of a series of FFs in groups which can store one bit of data each or as shift register ICs that store larger groups of data. The amount of data that can be stored in a shift register depends on the width of the register and the number of storage FFs contained in the register. Basic method of shift registers: q q Serial in/serial out shift register Serial in/ parallel out Parallel in/serial out Parallel in/parallel out Samjy/DENC 2533

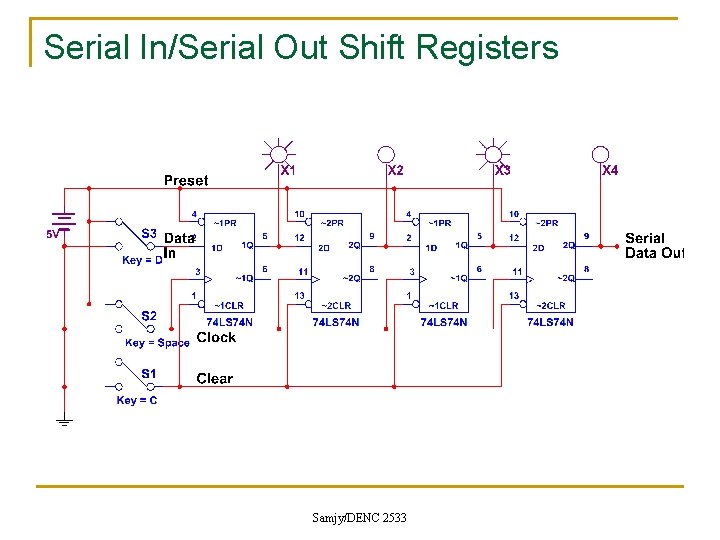

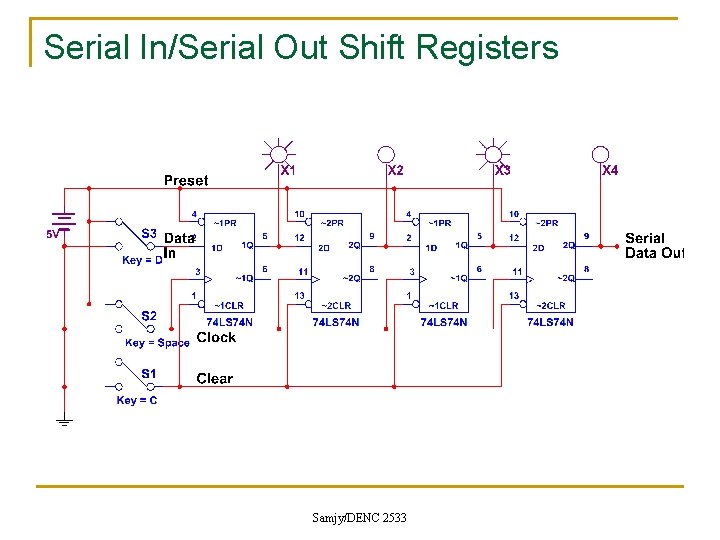

Serial In/Serial Out Shift Registers Samjy/DENC 2533

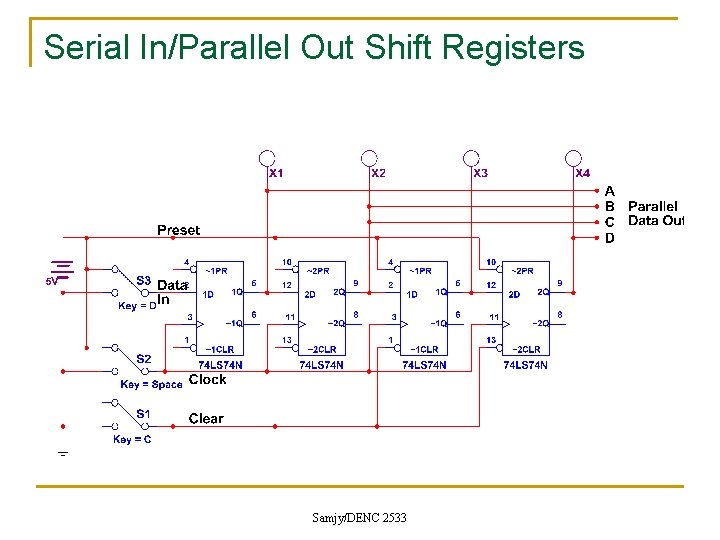

Serial In/Parallel Out Shift Registers Samjy/DENC 2533

Multiplexer

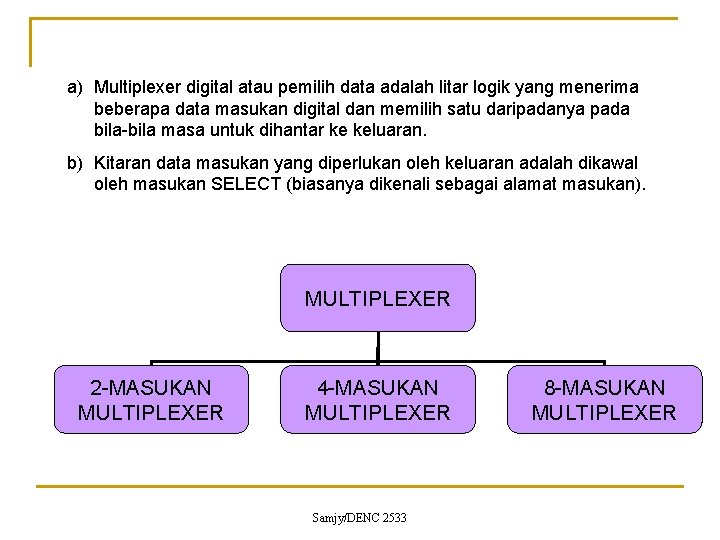

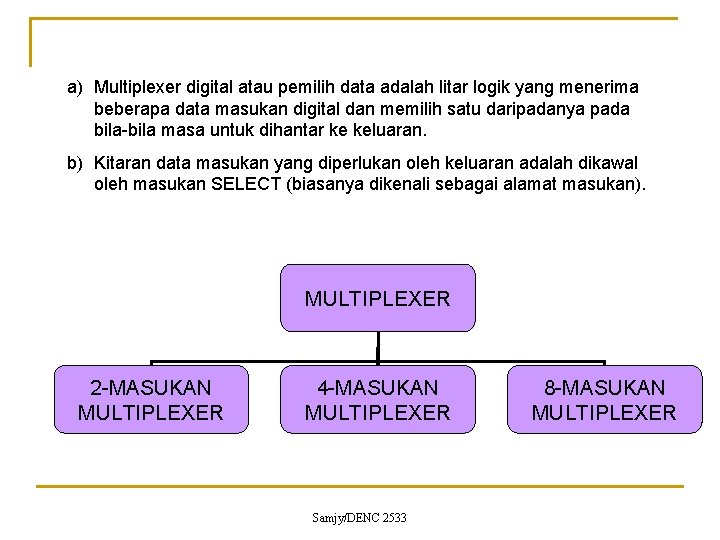

a) Multiplexer digital atau pemilih data adalah litar logik yang menerima beberapa data masukan digital dan memilih satu daripadanya pada bila-bila masa untuk dihantar ke keluaran. b) Kitaran data masukan yang diperlukan oleh keluaran adalah dikawal oleh masukan SELECT (biasanya dikenali sebagai alamat masukan). MULTIPLEXER 2 -MASUKAN MULTIPLEXER 4 -MASUKAN MULTIPLEXER Samjy/DENC 2533 8 -MASUKAN MULTIPLEXER

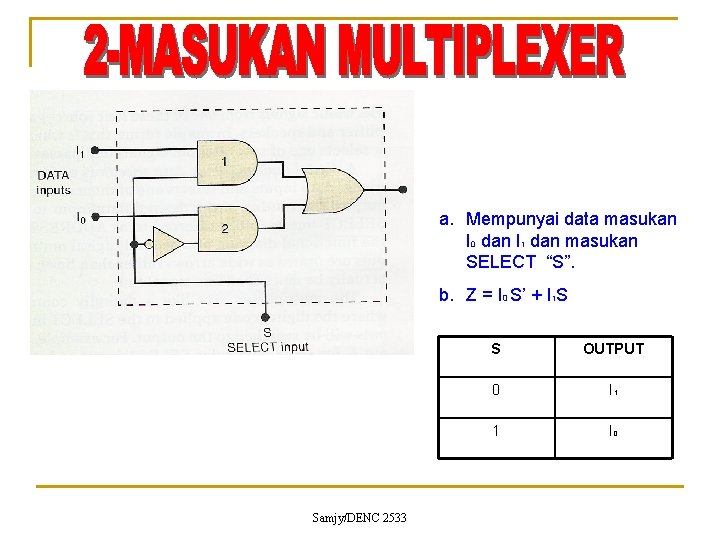

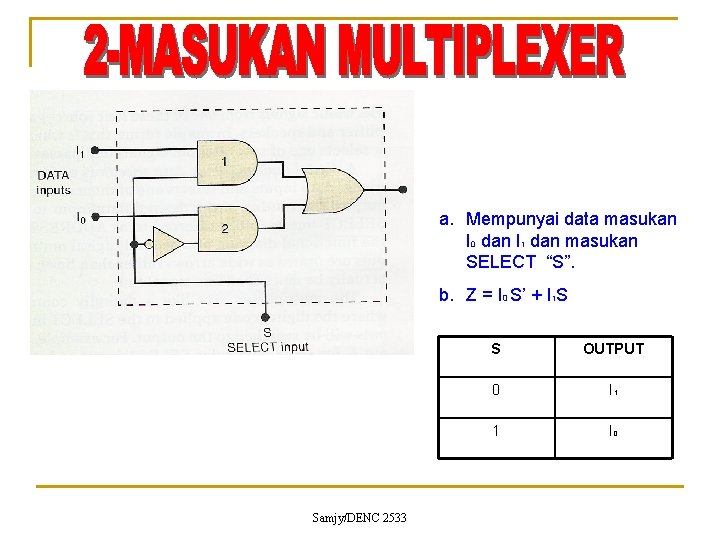

a. Mempunyai data masukan I 0 dan I 1 dan masukan SELECT “S”. b. Z = I 0 S’ + I 1 S Samjy/DENC 2533 S OUTPUT 0 I 1 1 I 0

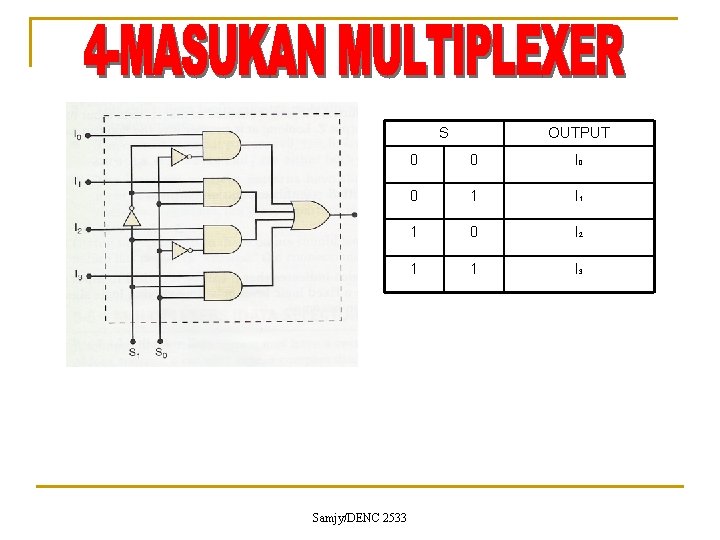

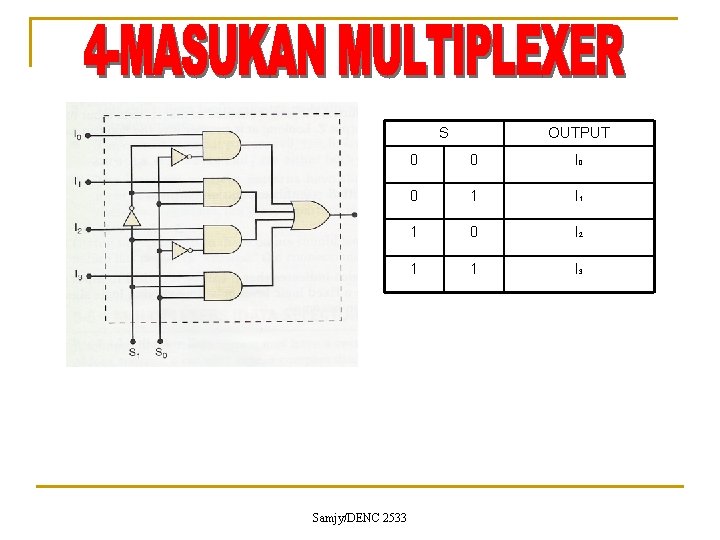

S Samjy/DENC 2533 OUTPUT 0 0 I 0 0 1 I 1 1 0 I 2 1 1 I 3

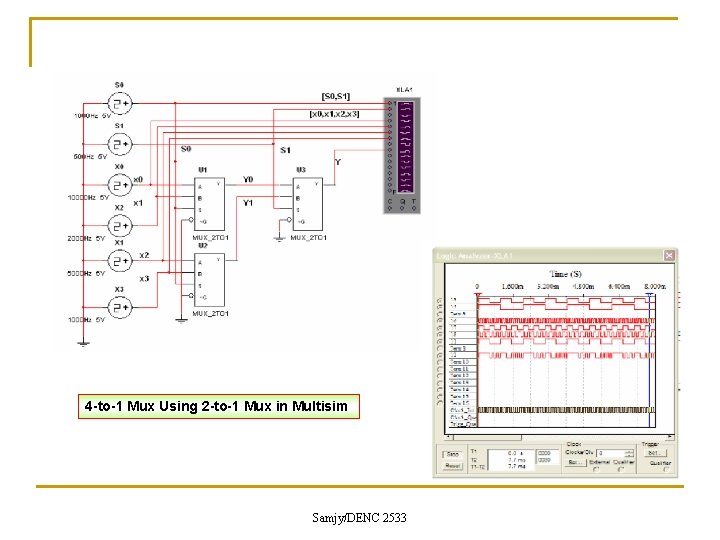

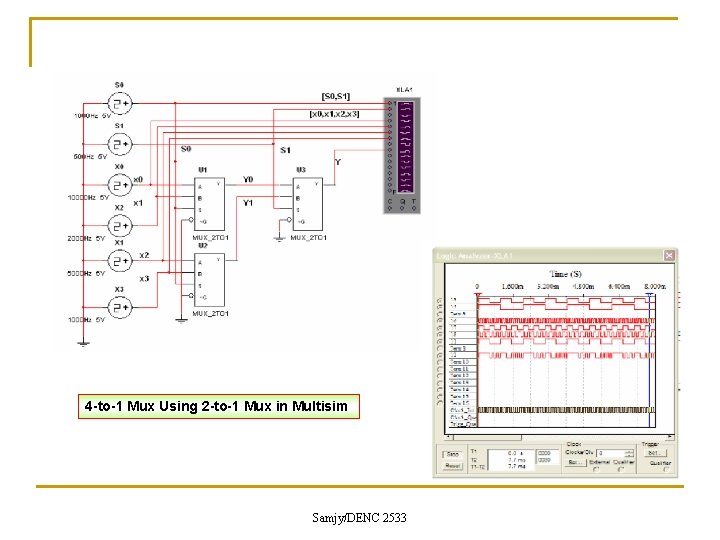

4 -to-1 Mux Using 2 -to-1 Mux in Multisim Samjy/DENC 2533

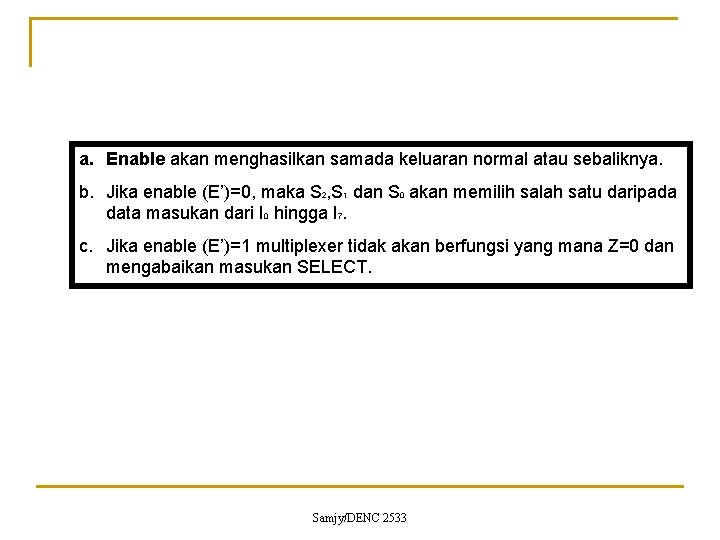

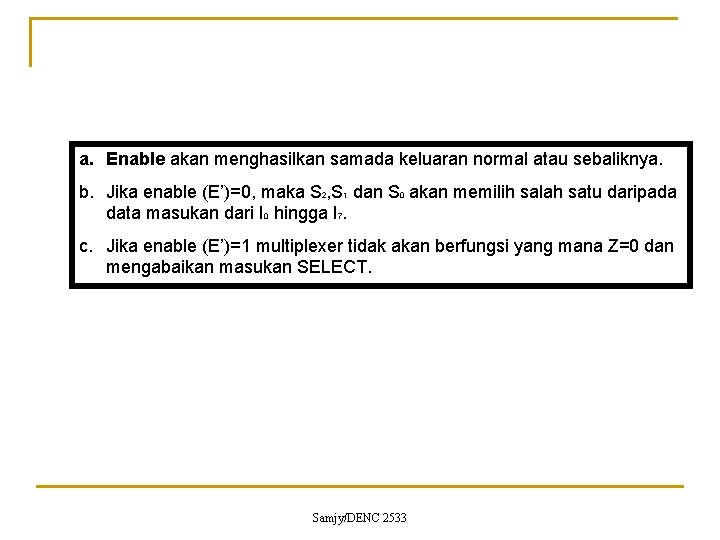

a. Enable akan menghasilkan samada keluaran normal atau sebaliknya. b. Jika enable (E’)=0, maka S 2, S 1 dan S 0 akan memilih salah satu daripada data masukan dari I 0 hingga I 7. c. Jika enable (E’)=1 multiplexer tidak akan berfungsi yang mana Z=0 dan mengabaikan masukan SELECT. Samjy/DENC 2533

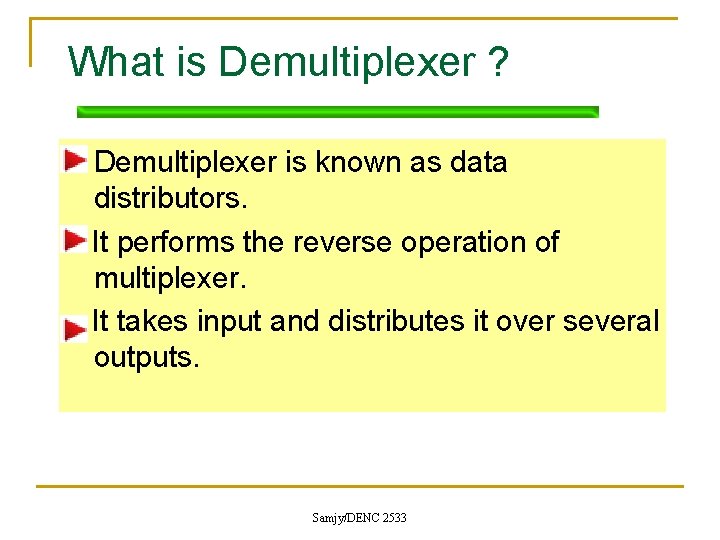

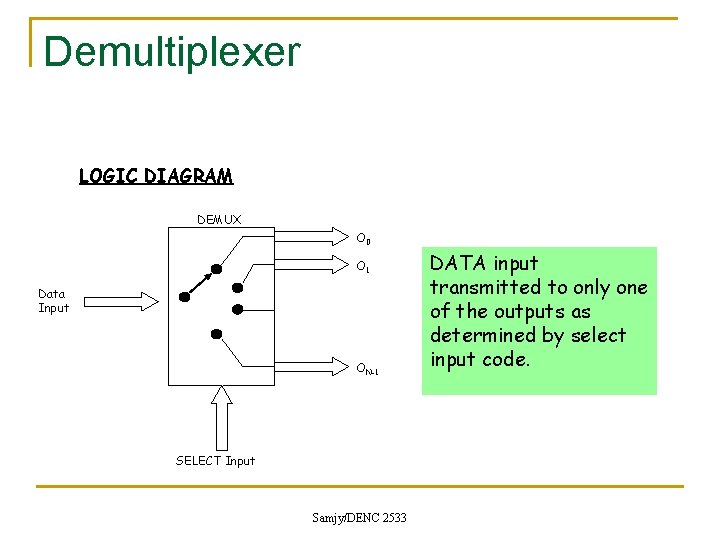

What is Demultiplexer ? Demultiplexer is known as data distributors. It performs the reverse operation of multiplexer. It takes input and distributes it over several outputs. Samjy/DENC 2533

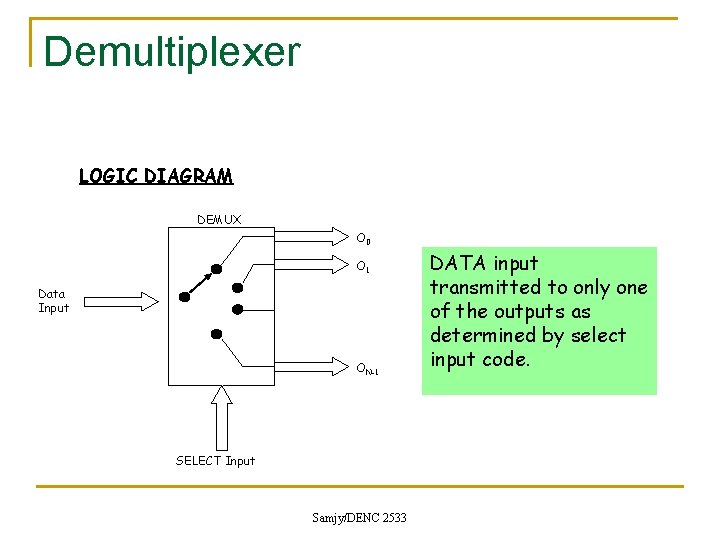

Demultiplexer LOGIC DIAGRAM DEMUX O 0 O 1 Data Input ON-1 SELECT Input Samjy/DENC 2533 DATA input transmitted to only one of the outputs as determined by select input code.

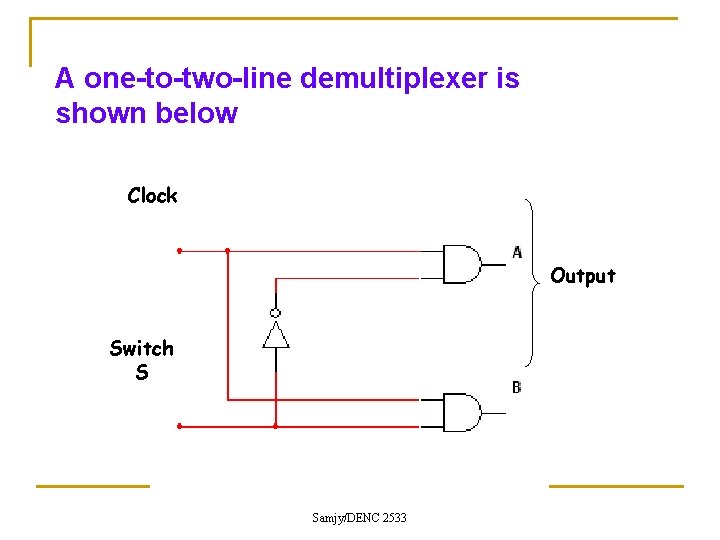

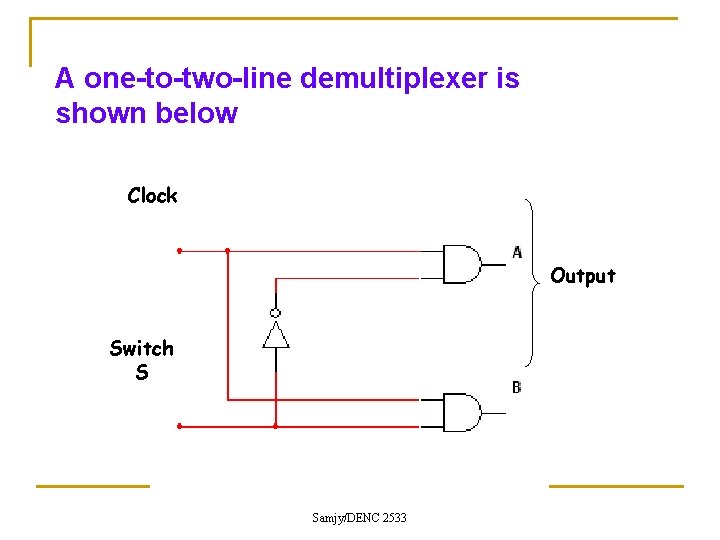

A one-to-two-line demultiplexer is shown below Clock Output Switch S Samjy/DENC 2533

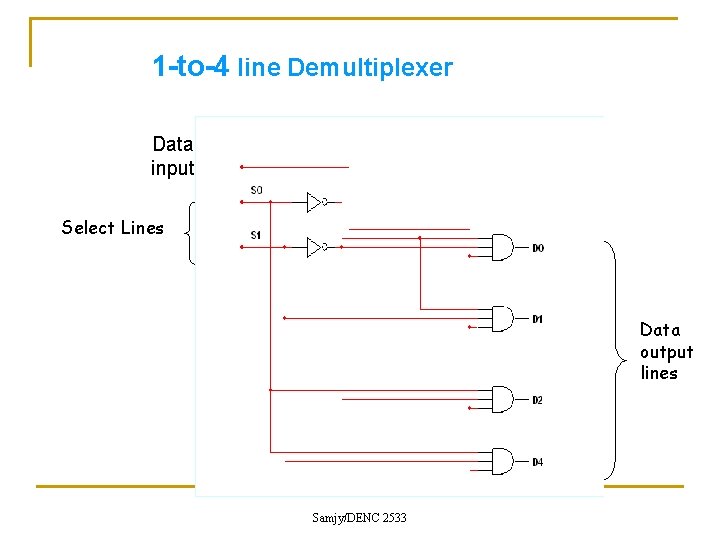

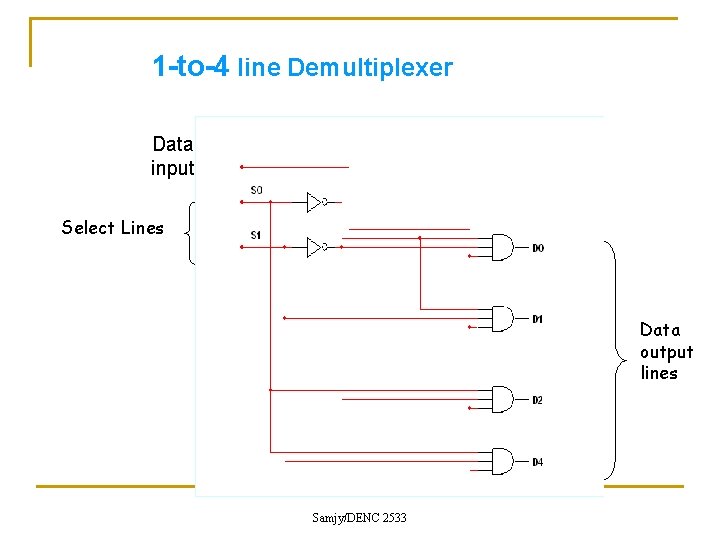

1 -to-4 line Demultiplexer Data input Select Lines Data output lines Samjy/DENC 2533

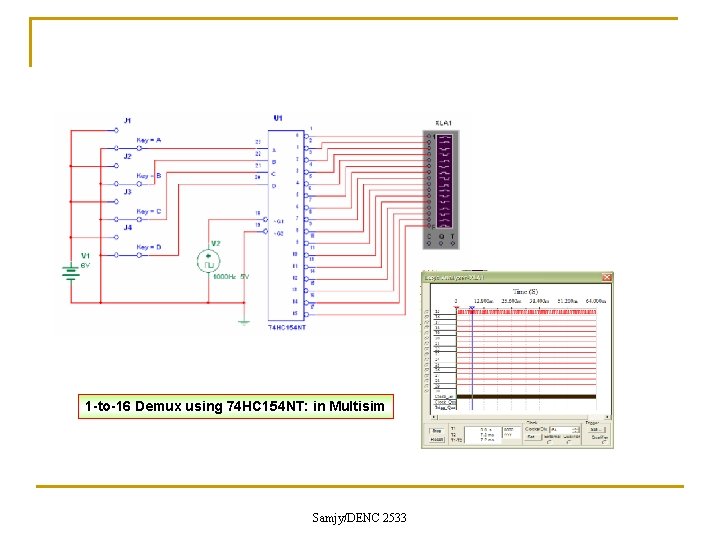

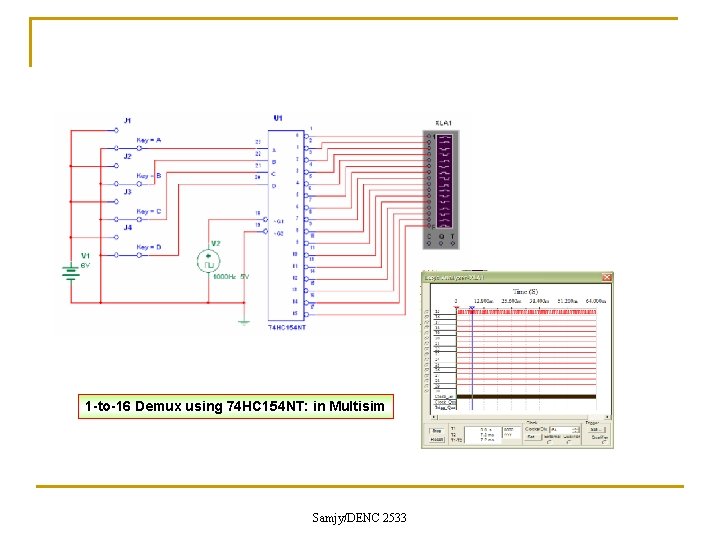

1 -to-16 Demux using 74 HC 154 NT: in Multisim Samjy/DENC 2533