Chapter 2 Data Manipulation Computer Architecture Machine Language

- Slides: 51

Chapter 2: Data Manipulation • • • Computer Architecture Machine Language Program Execution Arithmetic/Logic Instructions Communicating with Other Devices Other Architectures

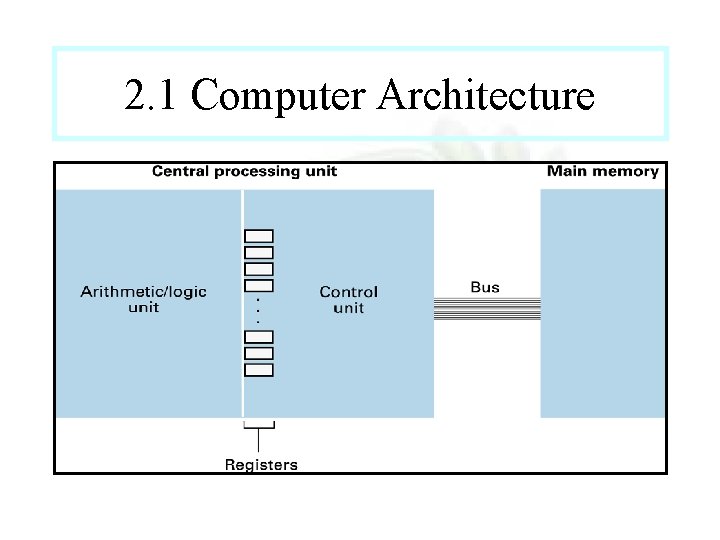

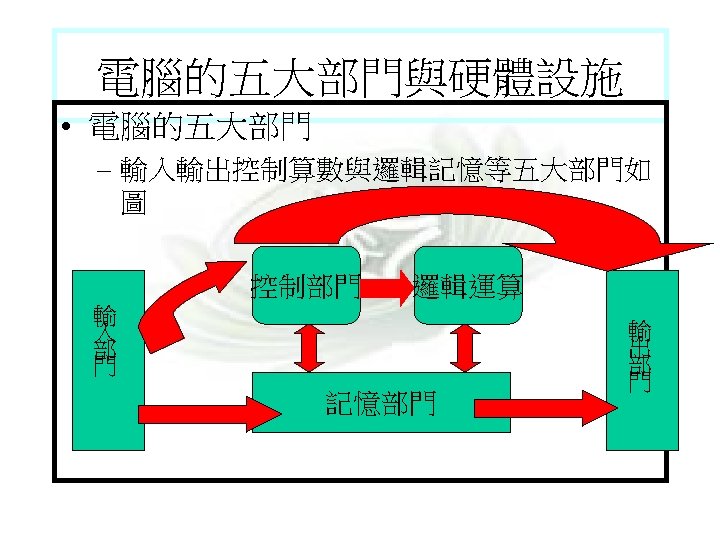

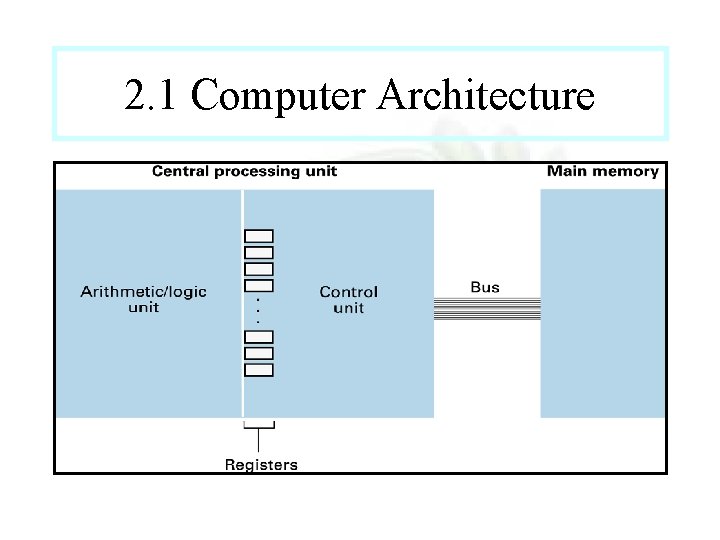

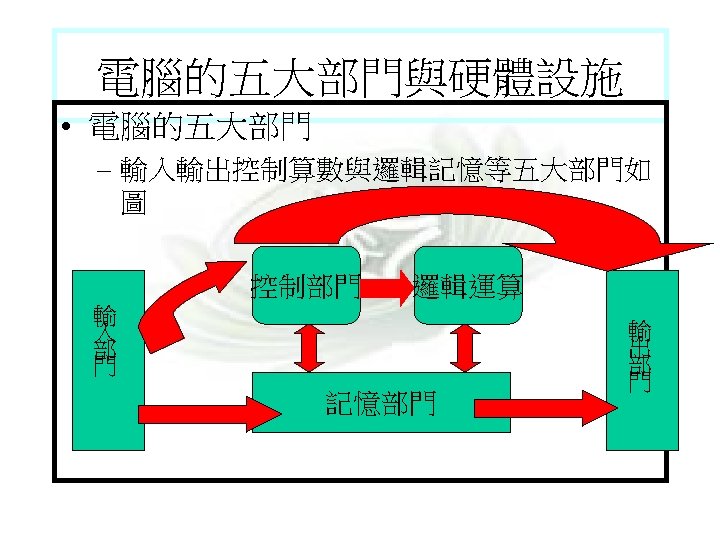

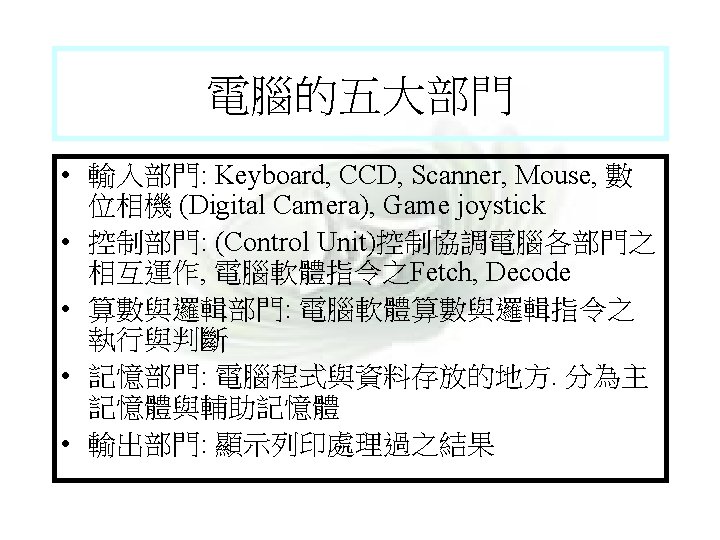

2. 1 Computer Architecture

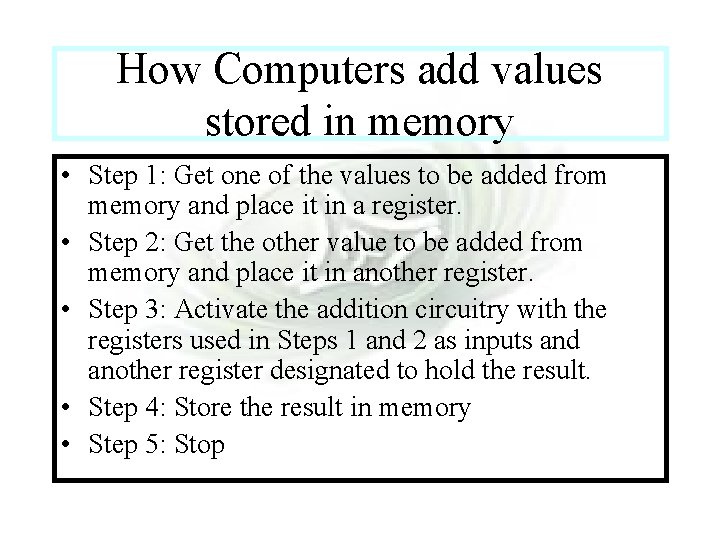

How Computers add values stored in memory • Step 1: Get one of the values to be added from memory and place it in a register. • Step 2: Get the other value to be added from memory and place it in another register. • Step 3: Activate the addition circuitry with the registers used in Steps 1 and 2 as inputs and another register designated to hold the result. • Step 4: Store the result in memory • Step 5: Stop

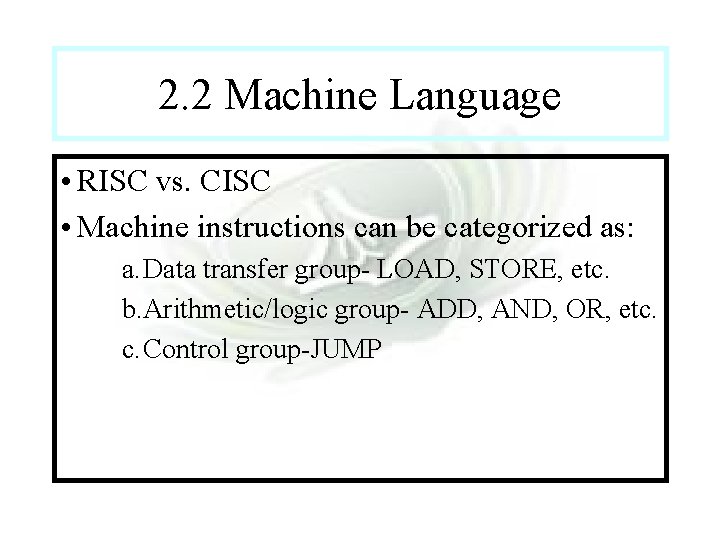

2. 2 Machine Language • RISC vs. CISC • Machine instructions can be categorized as: a. Data transfer group- LOAD, STORE, etc. b. Arithmetic/logic group- ADD, AND, OR, etc. c. Control group-JUMP

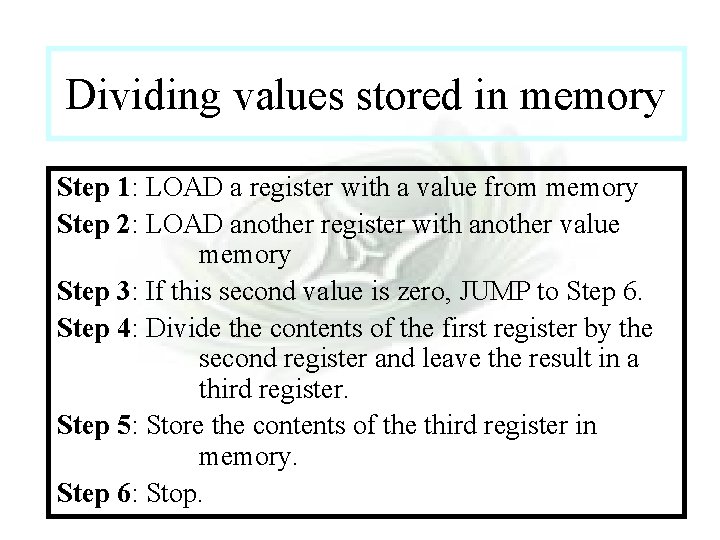

Dividing values stored in memory Step 1: LOAD a register with a value from memory Step 2: LOAD another register with another value memory Step 3: If this second value is zero, JUMP to Step 6. Step 4: Divide the contents of the first register by the second register and leave the result in a third register. Step 5: Store the contents of the third register in memory. Step 6: Stop.

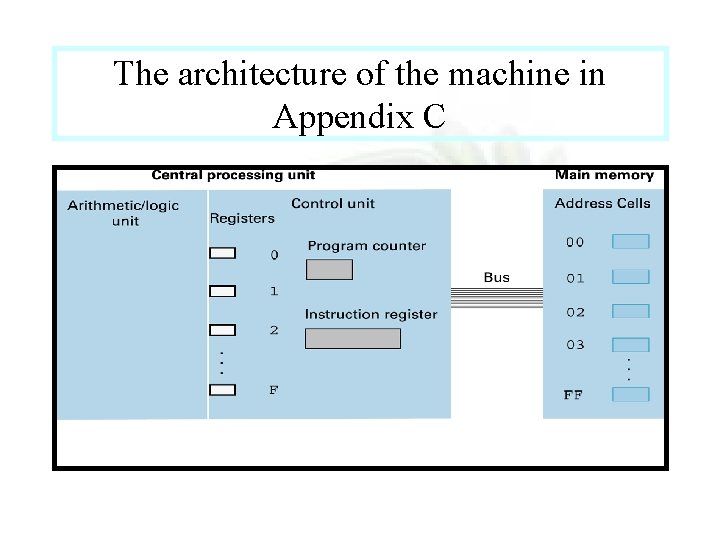

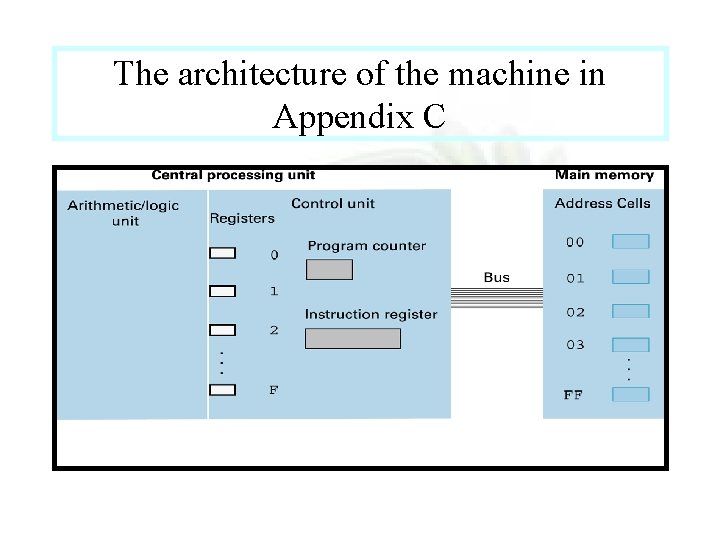

The architecture of the machine in Appendix C

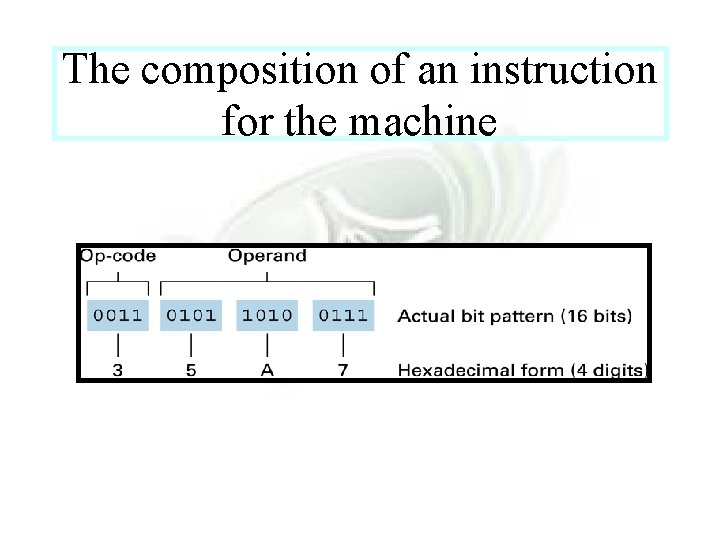

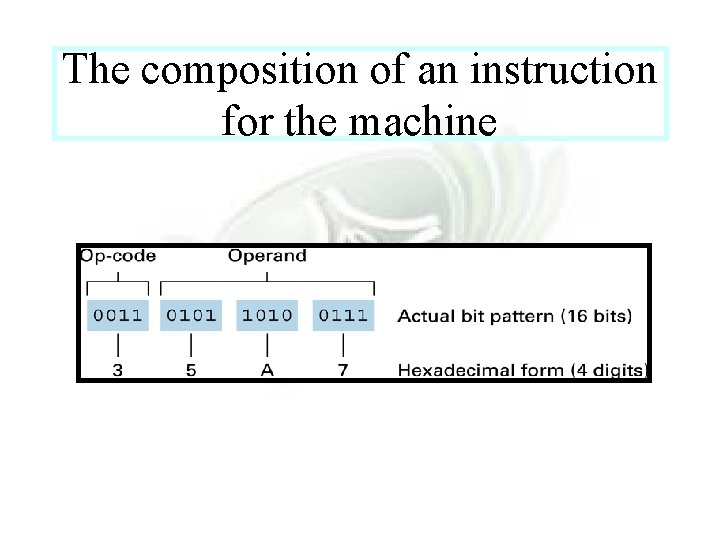

The composition of an instruction for the machine

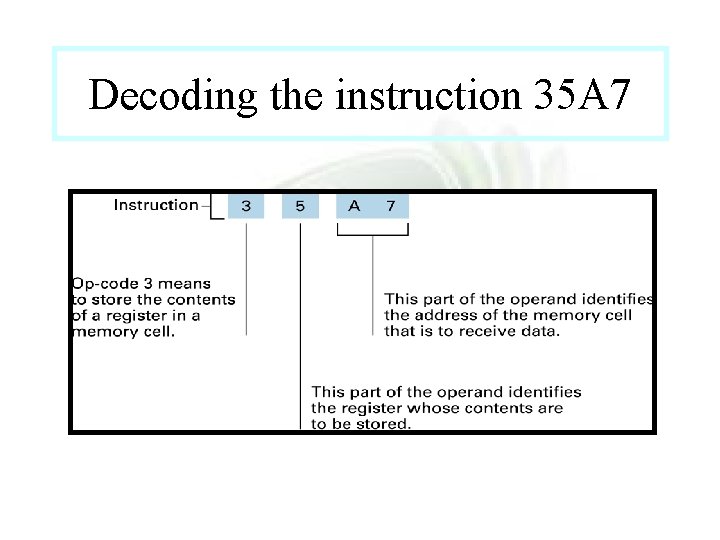

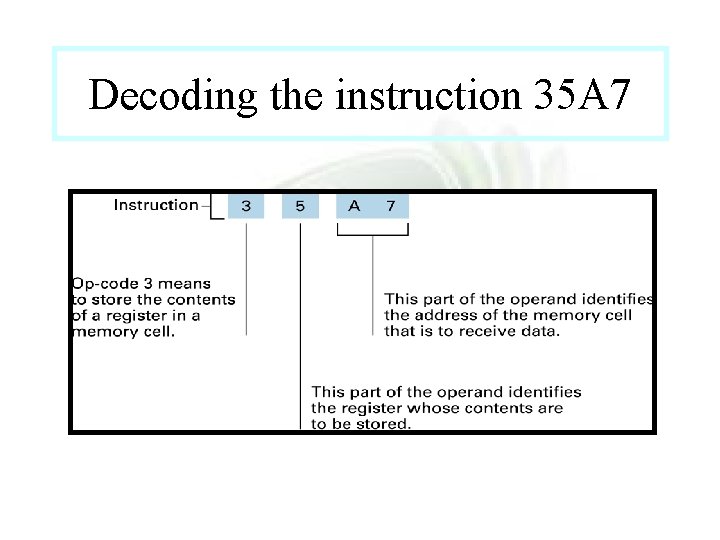

Decoding the instruction 35 A 7

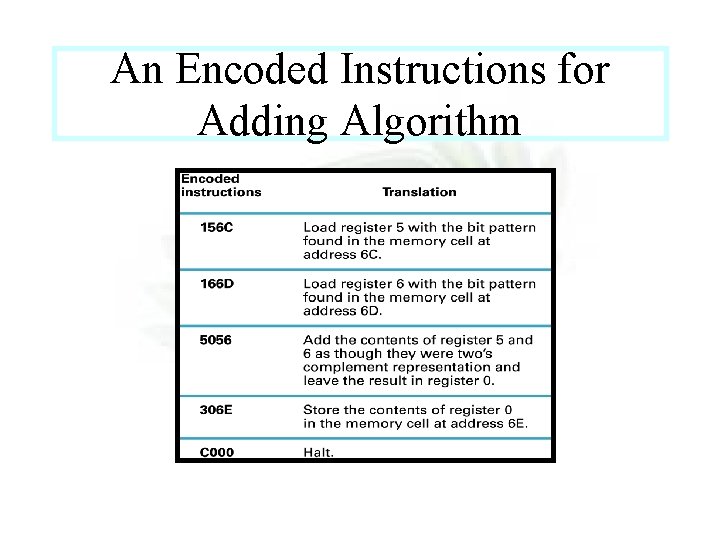

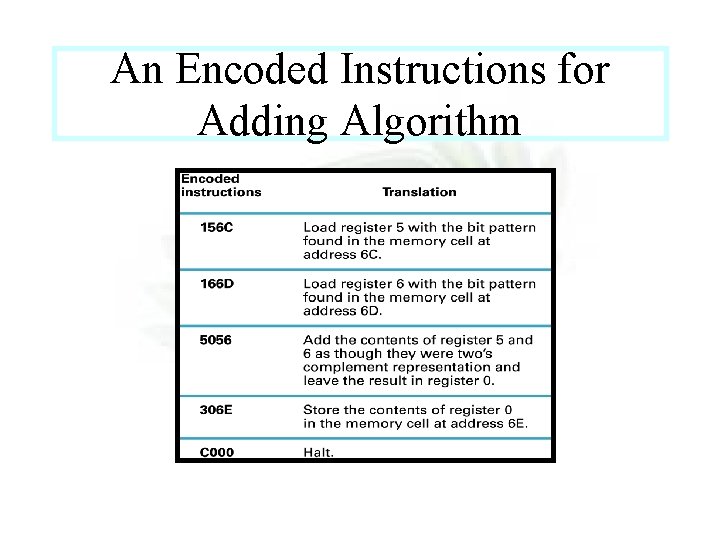

An Encoded Instructions for Adding Algorithm

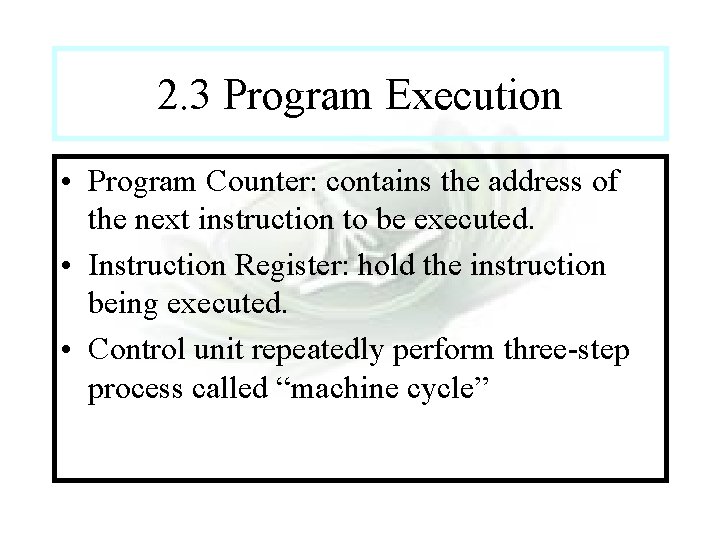

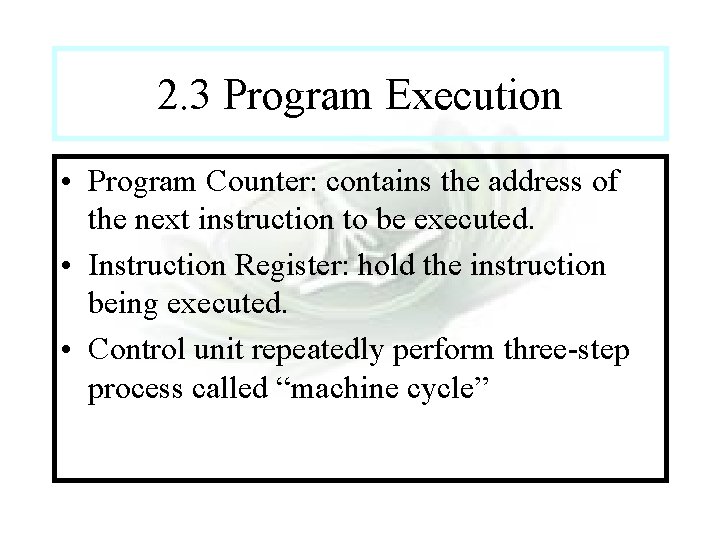

2. 3 Program Execution • Program Counter: contains the address of the next instruction to be executed. • Instruction Register: hold the instruction being executed. • Control unit repeatedly perform three-step process called “machine cycle”

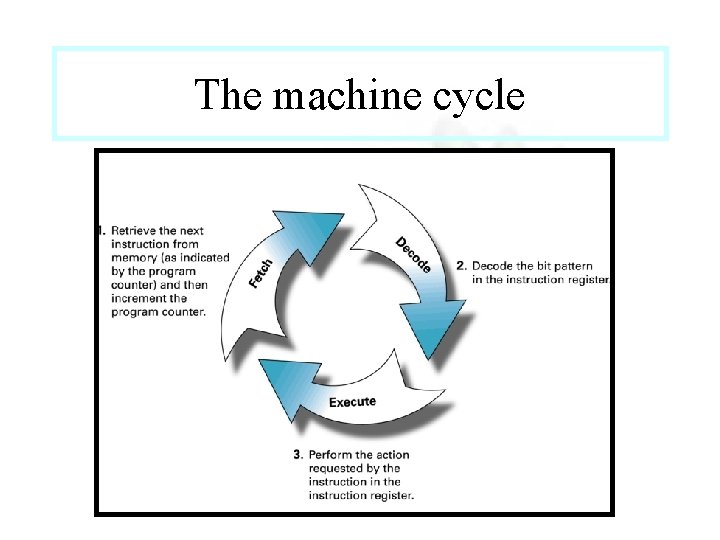

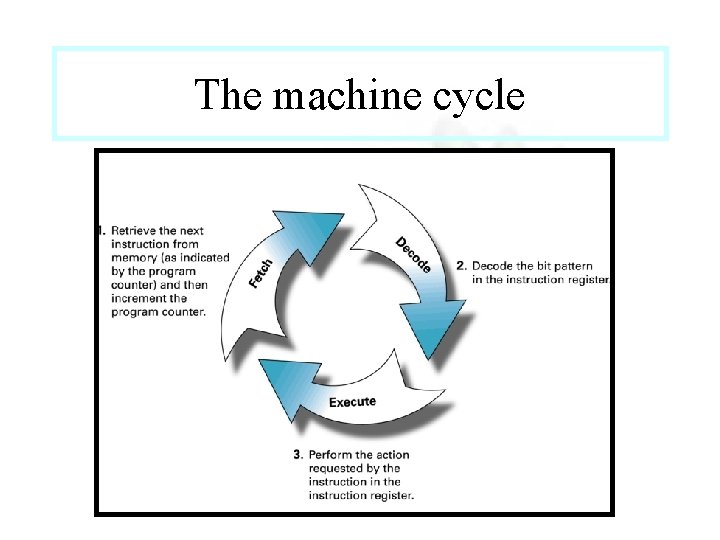

The machine cycle

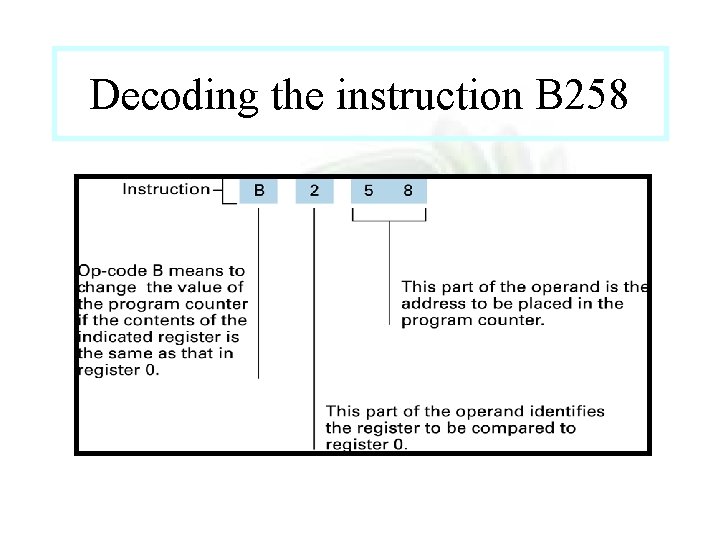

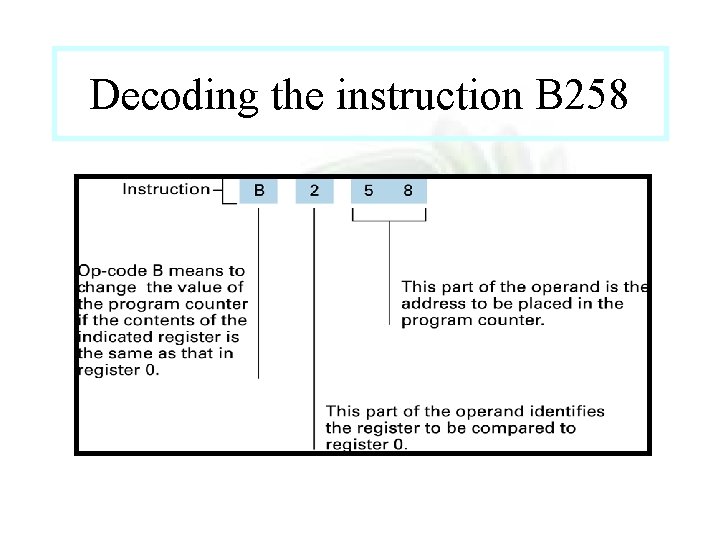

Decoding the instruction B 258

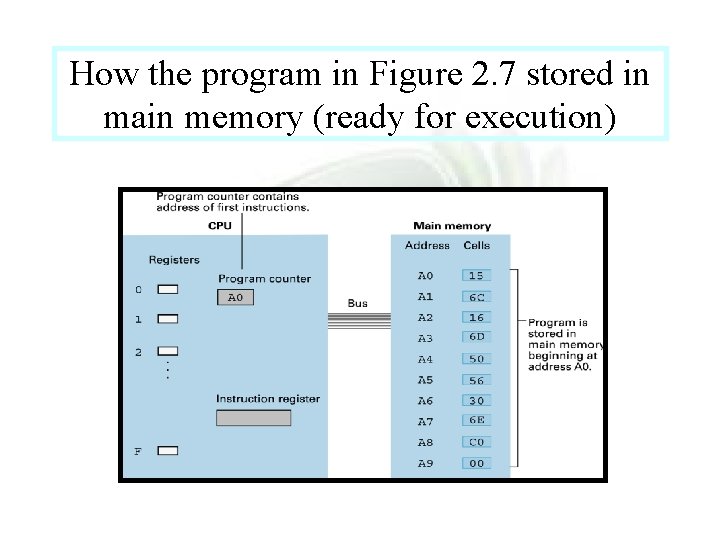

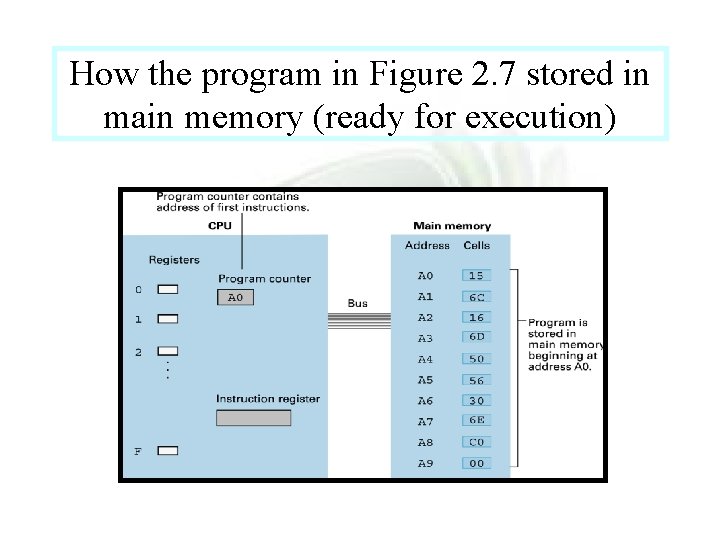

How the program in Figure 2. 7 stored in main memory (ready for execution)

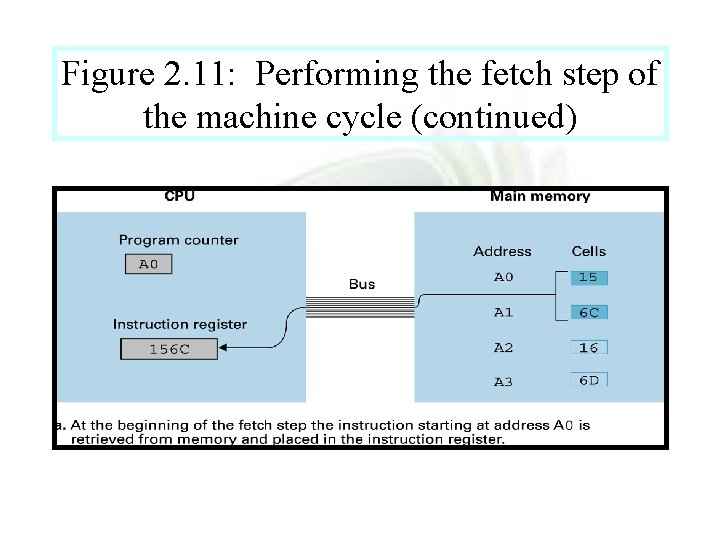

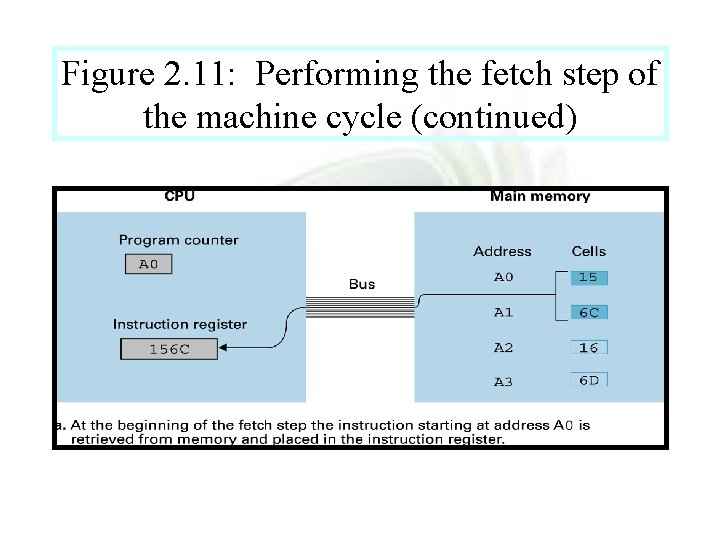

Figure 2. 11: Performing the fetch step of the machine cycle (continued)

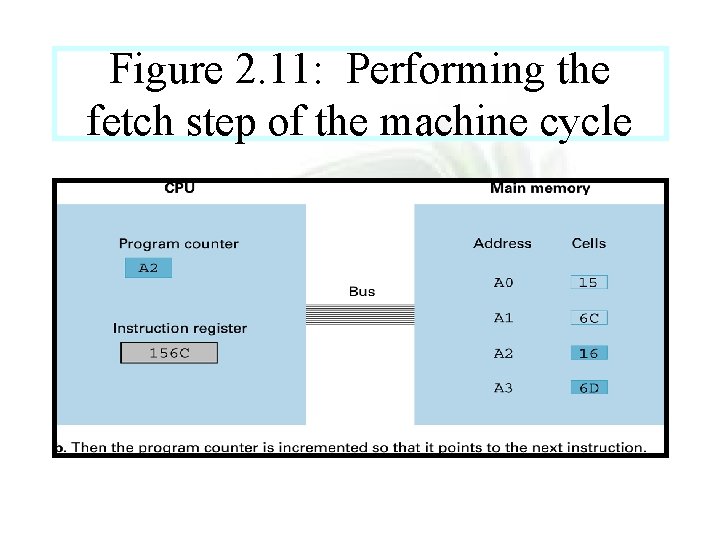

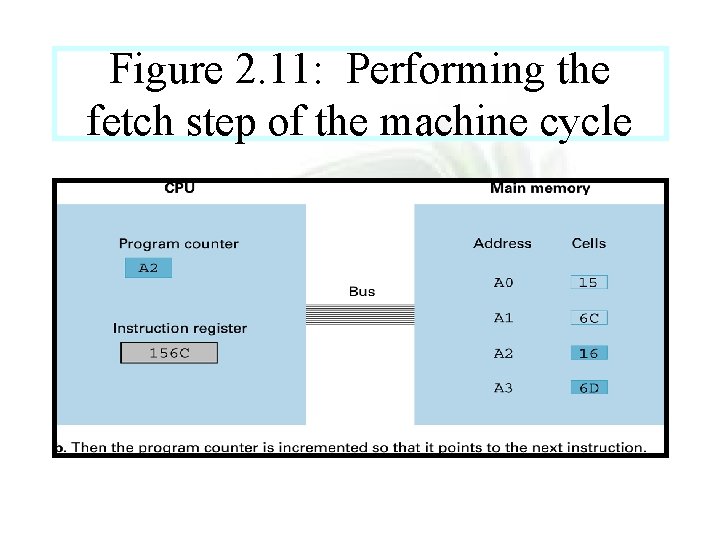

Figure 2. 11: Performing the fetch step of the machine cycle

2. 4 Arithmetic/Logic Instruction • Logic Operations – AND, OR, XOR – mask • Rotation and Shift Operations • Arithmetic Operations • ADD, SUBTRACT, MULTIPLY, DIVIDE • How floating point operands are added?

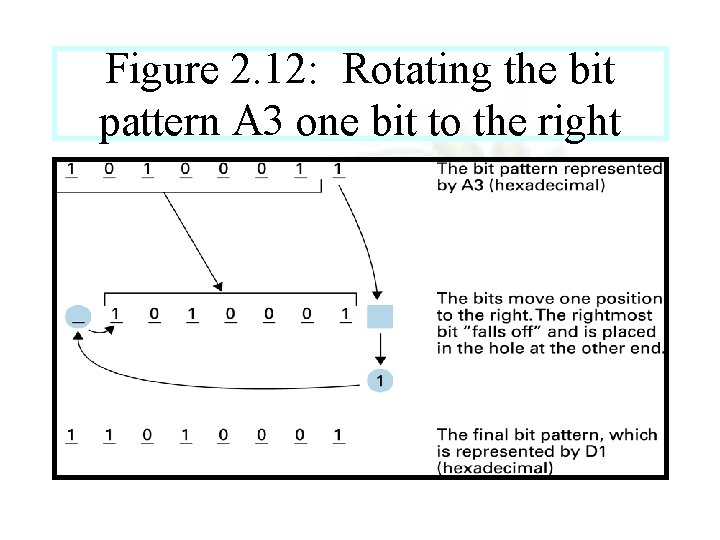

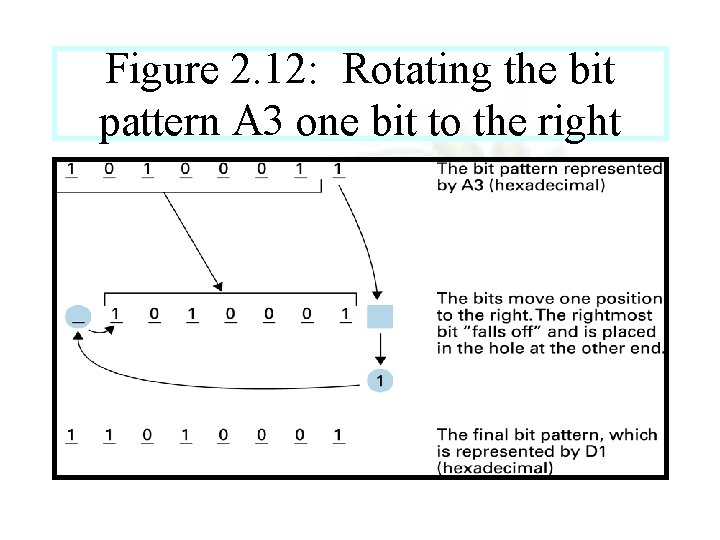

Figure 2. 12: Rotating the bit pattern A 3 one bit to the right

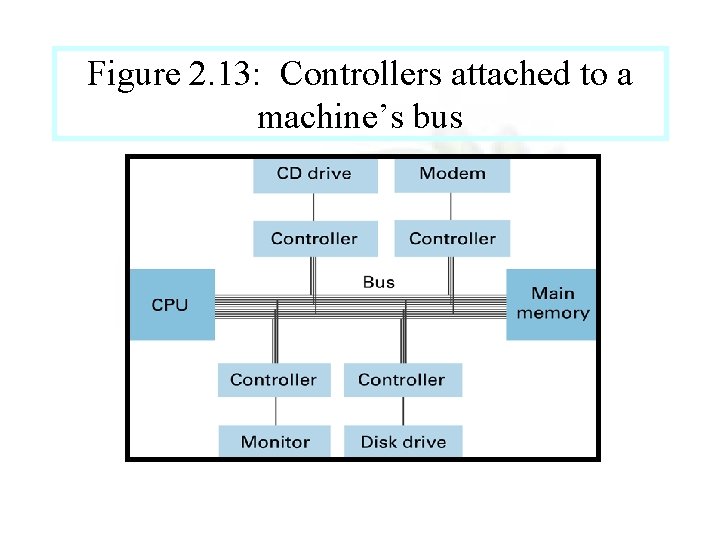

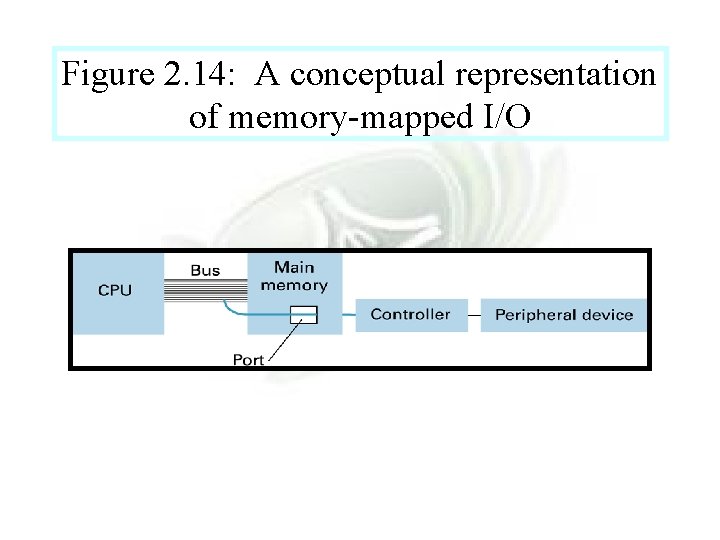

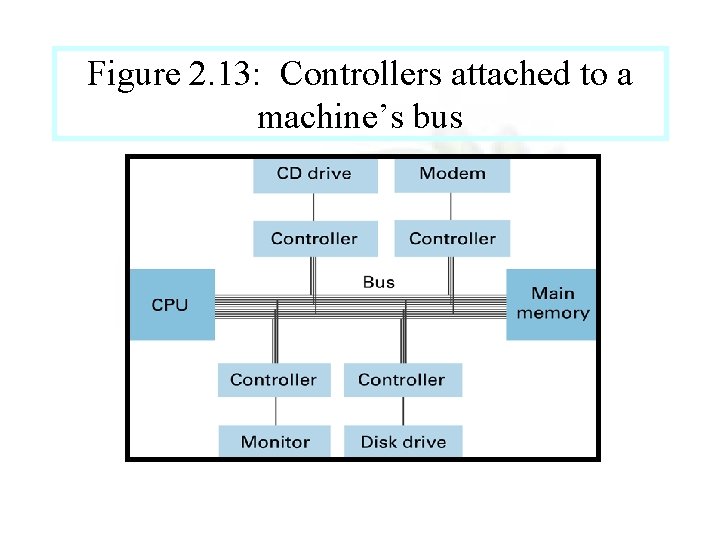

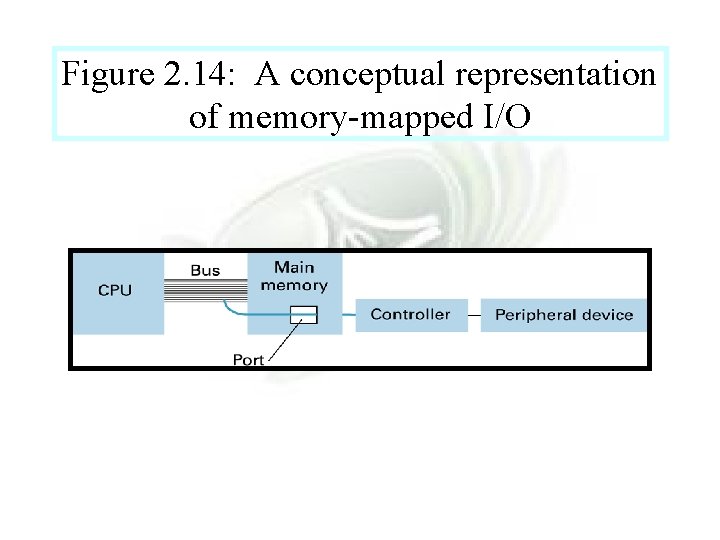

2. 5 Communicating with Other Devices • Communication via Controllers: direct memory access (DMA), memory-mapped I/O • Data Communication Rates: parallel communication, serial communication

Figure 2. 13: Controllers attached to a machine’s bus

Figure 2. 14: A conceptual representation of memory-mapped I/O

• Modem: – combine changes in a tone’s frequency, amplitude (volume), and phase (the degree to which the transmission of the tone is delayed) to achieve transfer rates of 9600 bps – To achieve still higher rates, data compression techniques are often applied, producing apparent transfer rates of up to 57. 6 Kbps.

ADSL (Asymmetric Digital Subscriber Line) • The ADSL solution takes advantage of advances in digital signal processing to eliminate echoes and other line noise electronically.

2. 6 Other Architectures. Pipelining • Electric pulses travel through a wire about 1 foot in a nanosecond, this is a limit. • Pipelining allowing the steps in machine cycle to overlap to increase throughput.

2. 6 Other Architecture Multiprocessor Machines • MIMD (Multiple-instruction stream, multiple-data stream) • SISD (Single-instruction stream, single-data stream) • SIMD (single-instruction stream, multiple-data stream) • Loading balancing • Scaling: dividing the present task into a number of subtasks compatible with the number of processors available

Intel Pentium 4 • • • 1. 4/1. 5 GHz System bus 400 MHz 42 M transistors 20 stage pipeline 144 new instructions for video and 3 D graphics processing • Intel 850 chip set provides 3. 2 GB/s transfer rate

• 0. 18 μm technology • Chip size 217 mm 2 • Package: flip-chip mount on Organic Land Grid (OLGA) and then on 423 -pin Pin Grid Array (PGA) • Advanced Transfer Cache • Execution Trace Cache: L 1 Cache (90 KB) for dynamic execution micro-operation sequence • Streaming SIMD Executions (128 b)

• ALU execution frequency 3 GHz • Advanced dynamic execution: pre-execution by branch prediction

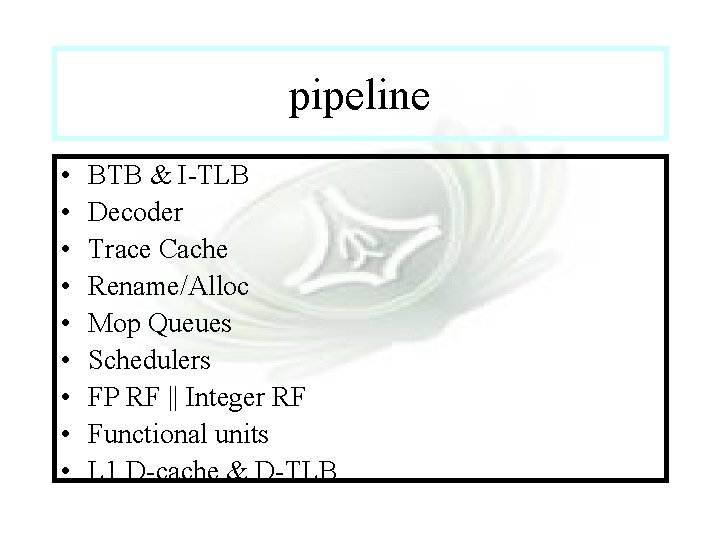

pipeline • • • BTB & I-TLB Decoder Trace Cache Rename/Alloc Μop Queues Schedulers FP RF || Integer RF Functional units L 1 D-cache & D-TLB

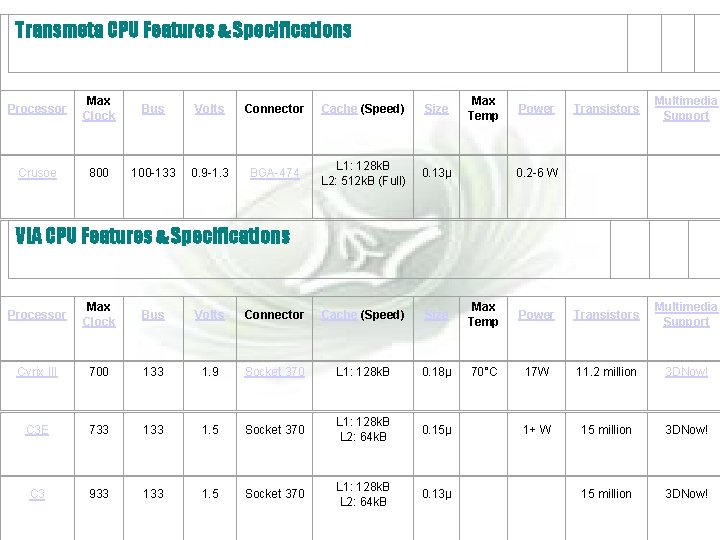

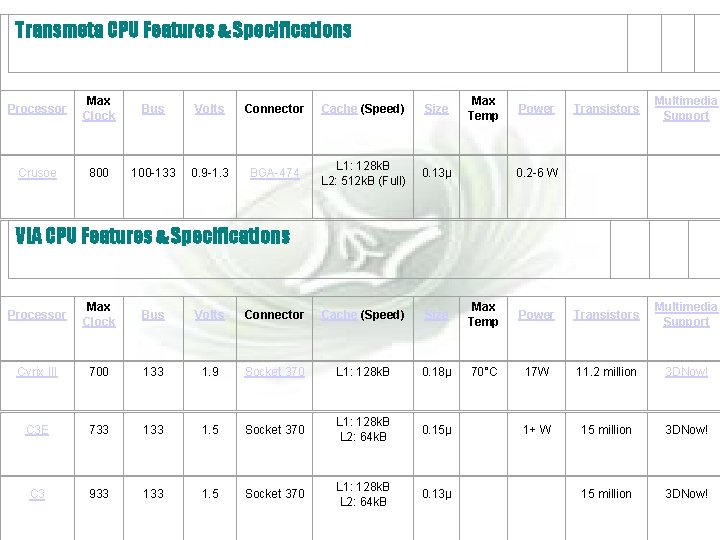

Transmeta CPU Features & Specifications Processor Max Clock Bus Volts Connector Cache (Speed) Size Crusoe 800 100 -133 0. 9 -1. 3 BGA-474 L 1: 128 k. B L 2: 512 k. B (Full) 0. 13µ Max Temp Power Transistors Multimedia Support 0. 2 -6 W VIA CPU Features & Specifications Processor Max Clock Bus Volts Connector Cache (Speed) Size Max Temp Power Transistors Multimedia Support Cyrix III 700 133 1. 9 Socket 370 L 1: 128 k. B 0. 18µ 70°C 17 W 11. 2 million 3 DNow! C 3 E 733 1. 5 Socket 370 L 1: 128 k. B L 2: 64 k. B 0. 15µ 1+ W 15 million 3 DNow! C 3 933 1. 5 Socket 370 L 1: 128 k. B L 2: 64 k. B 0. 13µ 15 million 3 DNow!

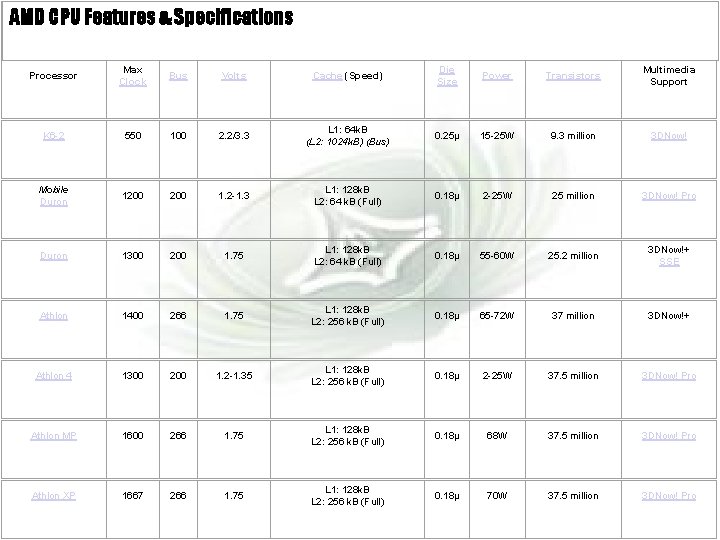

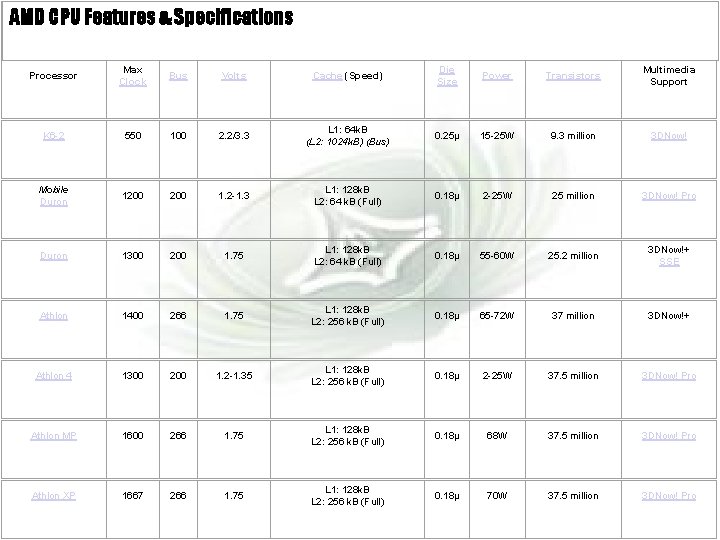

AMD CPU Features & Specifications Processor Max Clock Bus Volts Cache (Speed) Die Size Power Transistors Multimedia Support K 6 -2 550 100 2. 2/3. 3 L 1: 64 k. B (L 2: 1024 k. B) (Bus) 0. 25µ 15 -25 W 9. 3 million 3 DNow! Mobile Duron 1200 1. 2 -1. 3 L 1: 128 k. B L 2: 64 k. B (Full) 0. 18µ 2 -25 W 25 million 3 DNow! Pro Duron 1300 200 1. 75 L 1: 128 k. B L 2: 64 k. B (Full) 0. 18µ 55 -60 W 25. 2 million 3 DNow!+ SSE Athlon 1400 266 1. 75 L 1: 128 k. B L 2: 256 k. B (Full) 0. 18µ 65 -72 W 37 million 3 DNow!+ Athlon 4 1300 200 1. 2 -1. 35 L 1: 128 k. B L 2: 256 k. B (Full) 0. 18µ 2 -25 W 37. 5 million 3 DNow! Pro Athlon MP 1600 266 1. 75 L 1: 128 k. B L 2: 256 k. B (Full) 0. 18µ 68 W 37. 5 million 3 DNow! Pro Athlon XP 1667 266 1. 75 L 1: 128 k. B L 2: 256 k. B (Full) 0. 18µ 70 W 37. 5 million 3 DNow! Pro

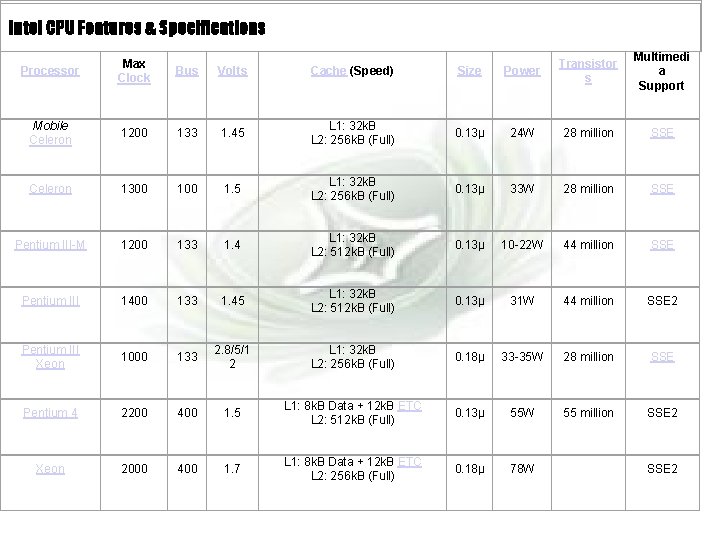

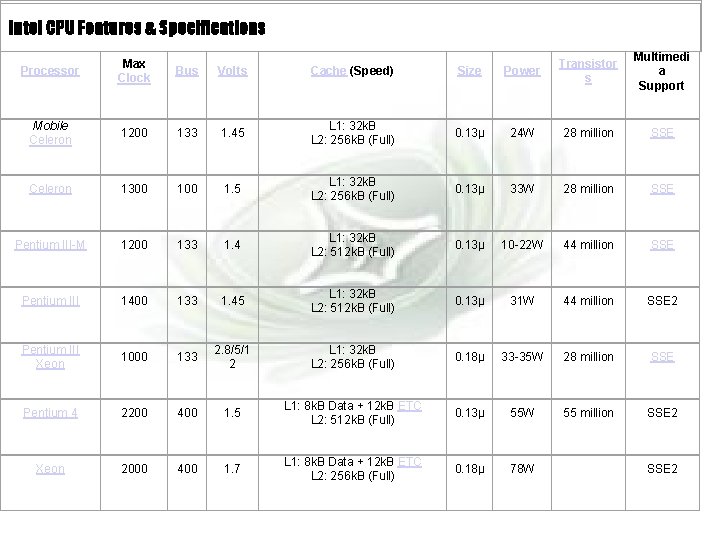

Intel CPU Features & Specifications Processor Max Clock Bus Volts Cache (Speed) Size Power Transistor s Multimedi a Support Mobile Celeron 1200 133 1. 45 L 1: 32 k. B L 2: 256 k. B (Full) 0. 13µ 24 W 28 million SSE Celeron 1300 1. 5 L 1: 32 k. B L 2: 256 k. B (Full) 0. 13µ 33 W 28 million SSE Pentium III-M 1200 133 1. 4 L 1: 32 k. B L 2: 512 k. B (Full) 0. 13µ 10 -22 W 44 million SSE Pentium III 1400 133 1. 45 L 1: 32 k. B L 2: 512 k. B (Full) 0. 13µ 31 W 44 million SSE 2 Pentium III Xeon 1000 133 2. 8/5/1 2 L 1: 32 k. B L 2: 256 k. B (Full) 0. 18µ 33 -35 W 28 million SSE Pentium 4 2200 400 1. 5 L 1: 8 k. B Data + 12 k. B ETC L 2: 512 k. B (Full) 0. 13µ 55 W 55 million SSE 2 Xeon 2000 400 1. 7 L 1: 8 k. B Data + 12 k. B ETC L 2: 256 k. B (Full) 0. 18µ 78 W SSE 2

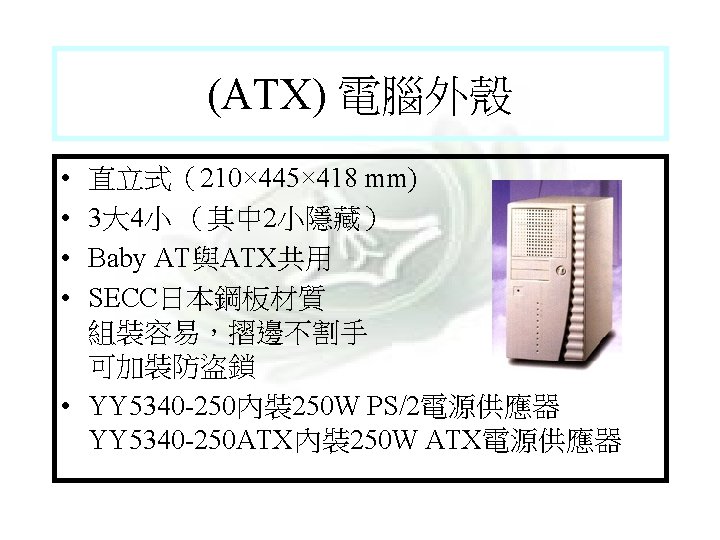

電腦主機內部元件 • CPU, RAM, Main board , Power Supply, Case, CD-ROM, 排線 • ROM, Floppy Disk, Hard Disk, 音效卡 • Display Card (顯示卡)

CPU: Central Processing Unit, 含 CU 與 ALU • 內含Primary Cache (快取記憶體) • Intel, AMD, Cyrix (PC 而言) • Intel Celeron, Intel Pentium III • AMD • Cyrix

• Pentium系列 133/150/166/200 MHz, 3. 3 V 適用Socket 7插座 內建L 1 16 KB Cache

• Pentium with MMX系列 66/200/233 MHz, 2. 8 V 133/150/166 MHz, 2. 5 V (Note. Book用) 適用Socket 7插座 整合MMX多媒體增強技術, 加強 3 D動態 影像, POTS視訊, MPEG, 語音辨視等處理能力 內建L 1 32 KB Cache

RAM (主記憶體) • 386時代 1 M , 486: 4 -8 M, 586: 16 -64 M, Pentium II, 64 M~256 M • 分為 30 Pine, 72 Pine EDO RAM, 168 Pine S-DRAM • 大小 512 K, 1 M, 4 M, 8 M, 16 M, 32 M, 64 M, 未來 128 M 一片 • 可分日系與台系與韓系等

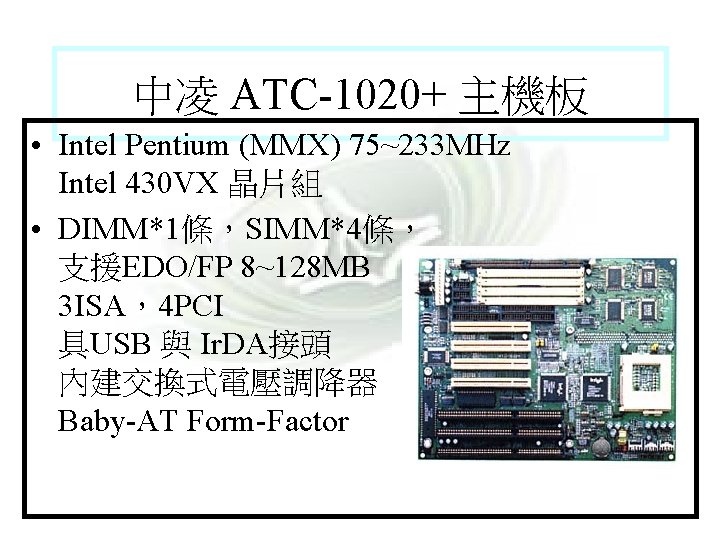

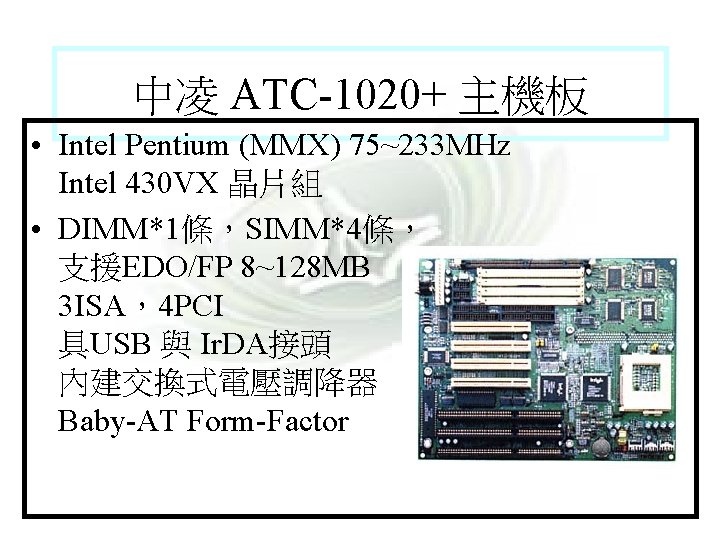

中凌 ATC-1020+ 主機板 • Intel Pentium (MMX) 75~233 MHz Intel 430 VX 晶片組 • DIMM*1條,SIMM*4條, 支援EDO/FP 8~128 MB 3 ISA,4 PCI 具USB 與 Ir. DA接頭 內建交換式電壓調降器 Baby-AT Form-Factor

Hard Disk • IDE & SCSI • IDE: 5400 RPM, 4 G, 6. 4 G, 8. 4 G, 9. 1 G, 10. 2 G, 13 G, 17. 2 G, 18. 2 G

CDR & CD-ROM • Philip MDC 3064 SS可讀寫光碟機 外接式 SCSI 介面 3600 rpm 2 MB ON BOARD • DYNA MO 640 AI 內接式可讀寫光碟機 – – 內接式 IDE 介面 3, 600 RPM 2 MB ON BOARD

Home. Work • Same as Chapter 1