Chapter 17 18 Hardwired vs Microprogrammed Control Multithreading

- Slides: 18

Chapter 17 - 18 • Hardwired vs Microprogrammed Control • Multithreading • Multicore Computers • Summary of Parallel Organizations • Recap of Course • Final Exam: Next Thursday- Same time / same place

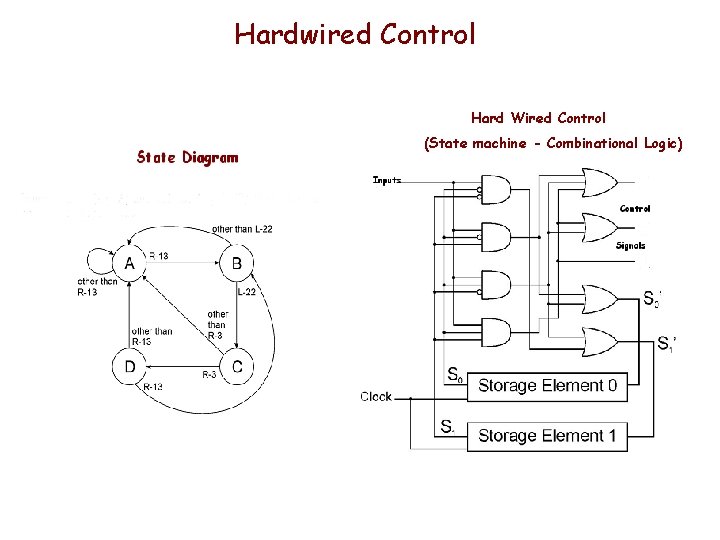

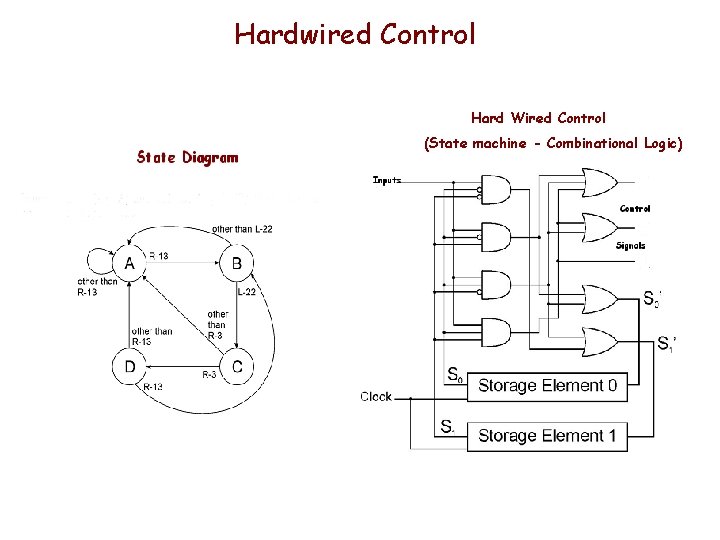

Hardwired Control Hard Wired Control (State machine - Combinational Logic)

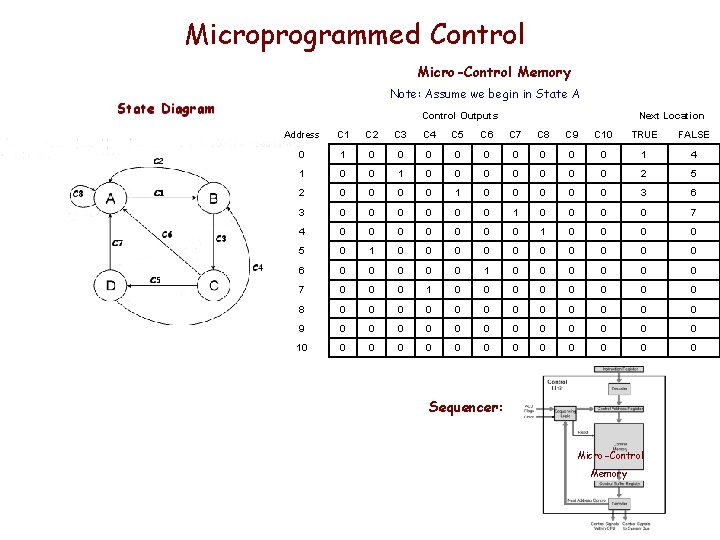

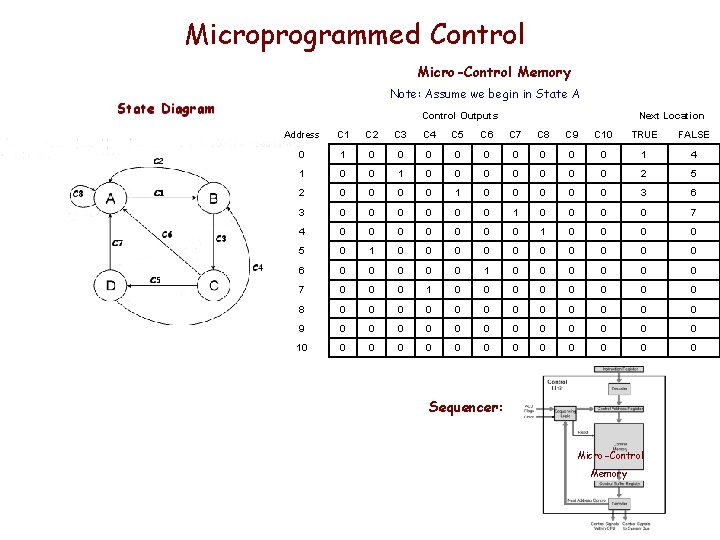

Microprogrammed Control Micro-Control Memory Note: Assume we begin in State A Control Outputs Next Location Address C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 9 C 10 TRUE FALSE 0 1 0 0 0 0 0 1 4 1 0 0 0 0 0 2 5 2 0 0 1 0 0 0 3 6 3 0 0 0 1 0 0 7 4 0 0 0 0 1 0 0 5 0 1 0 0 0 0 0 6 0 0 0 1 0 0 0 7 0 0 0 1 0 0 0 0 8 0 0 0 9 0 0 0 10 0 0 0 Sequencer: Micro-Control Memory

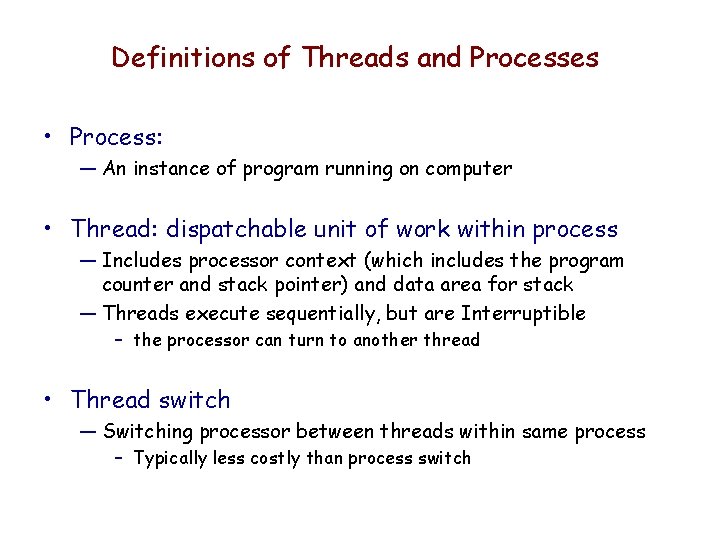

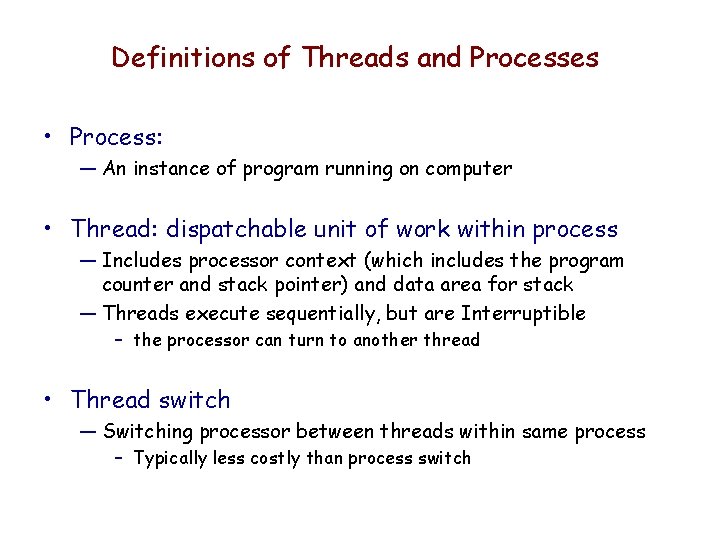

Definitions of Threads and Processes • Process: — An instance of program running on computer • Thread: dispatchable unit of work within process — Includes processor context (which includes the program counter and stack pointer) and data area for stack — Threads execute sequentially, but are Interruptible – the processor can turn to another thread • Thread switch — Switching processor between threads within same process – Typically less costly than process switch

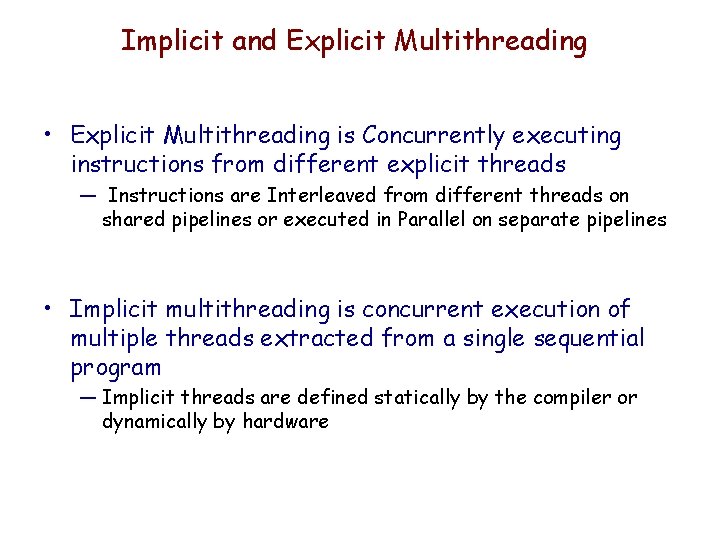

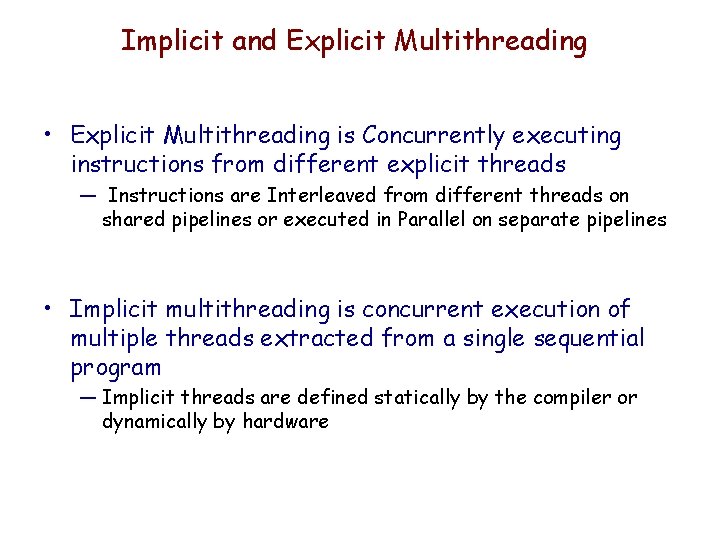

Implicit and Explicit Multithreading • Explicit Multithreading is Concurrently executing instructions from different explicit threads — Instructions are Interleaved from different threads on shared pipelines or executed in Parallel on separate pipelines • Implicit multithreading is concurrent execution of multiple threads extracted from a single sequential program — Implicit threads are defined statically by the compiler or dynamically by hardware

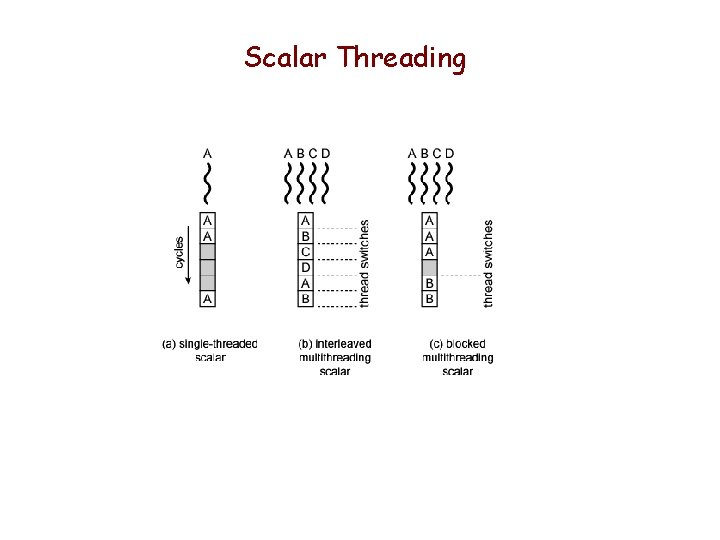

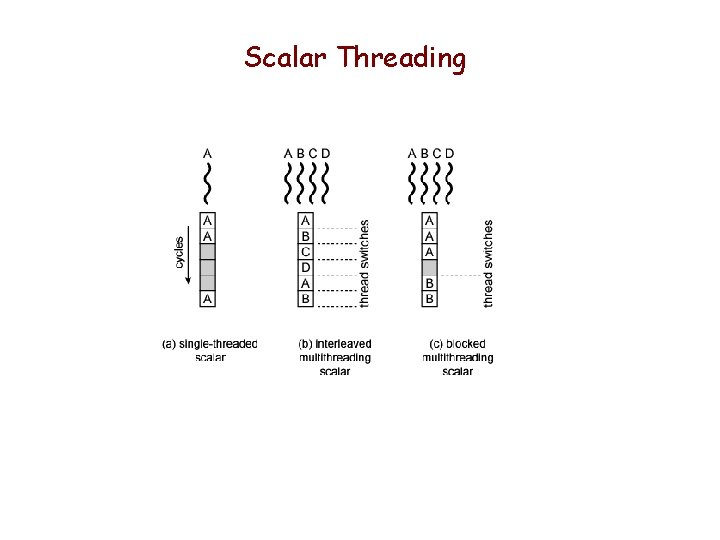

Scalar Threading

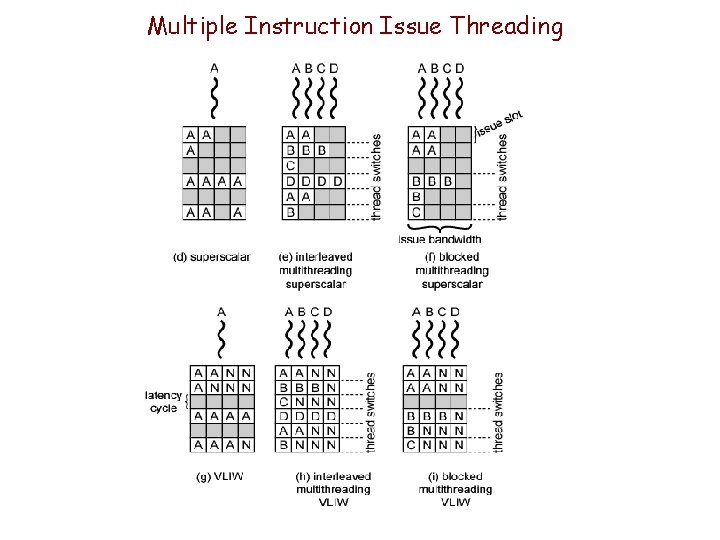

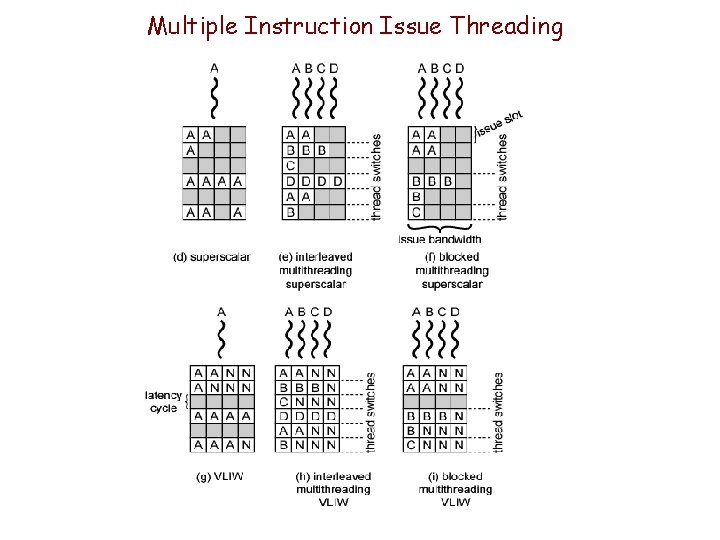

Multiple Instruction Issue Threading

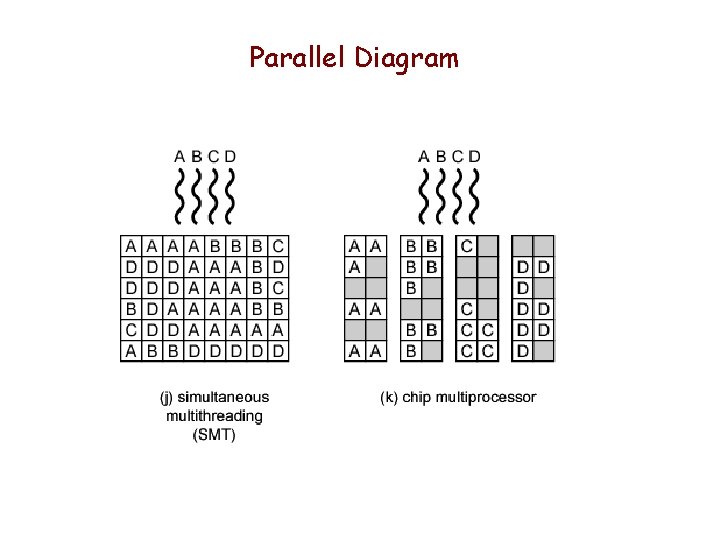

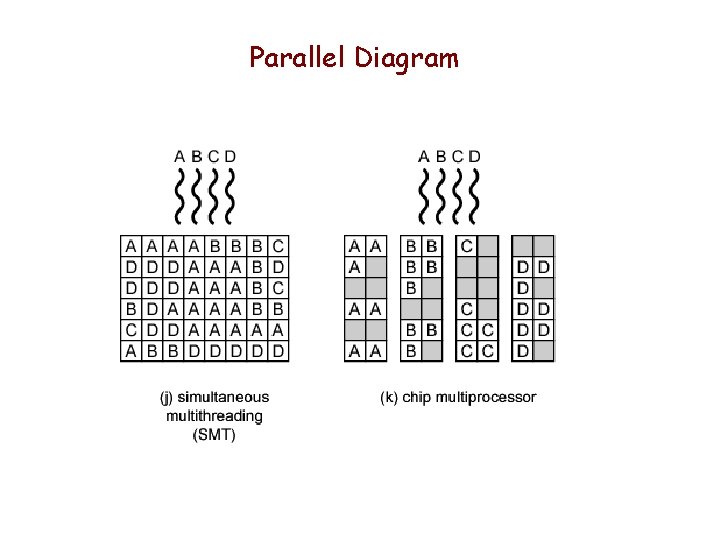

Parallel Diagram

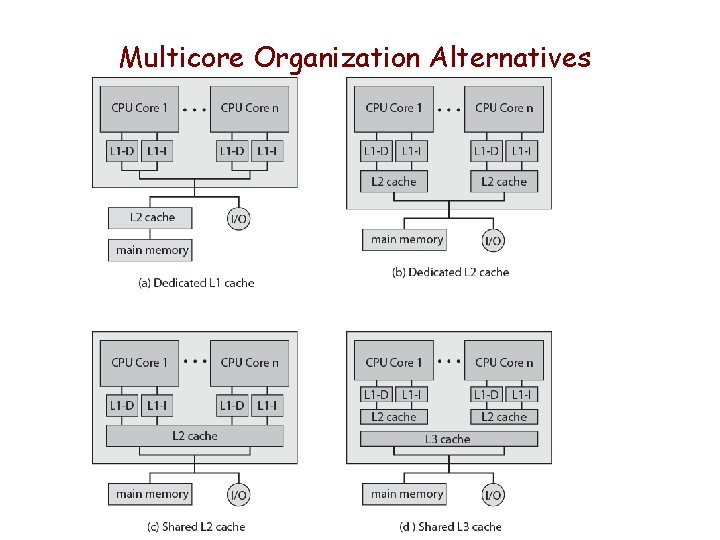

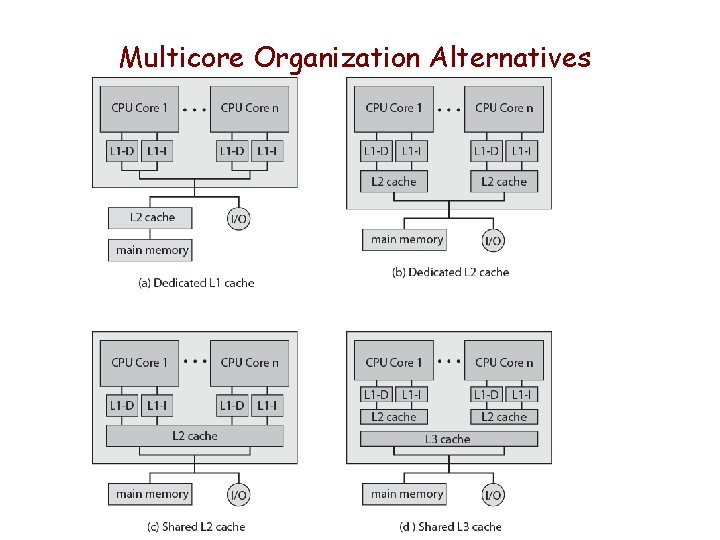

Multicore Organization Alternatives

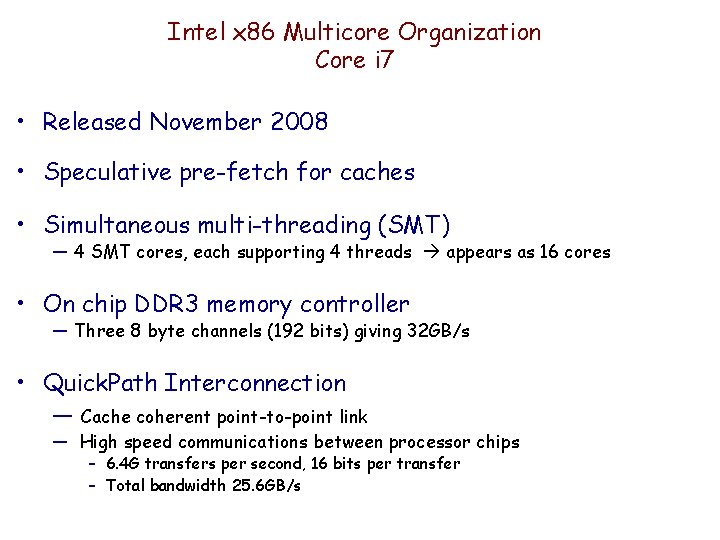

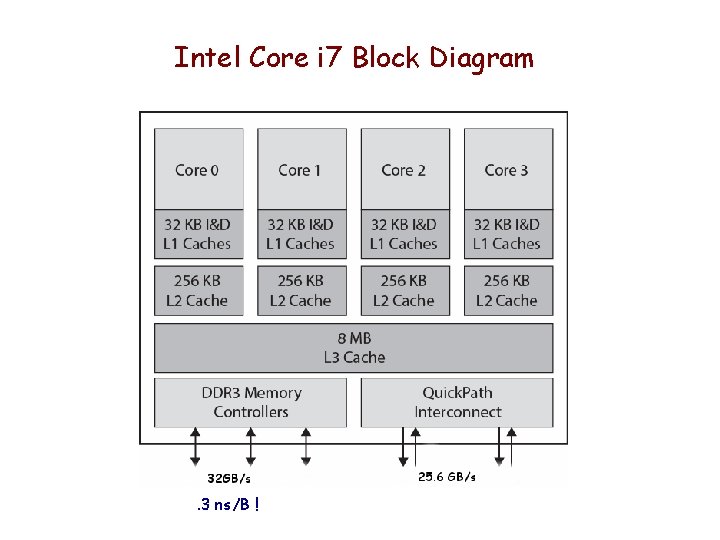

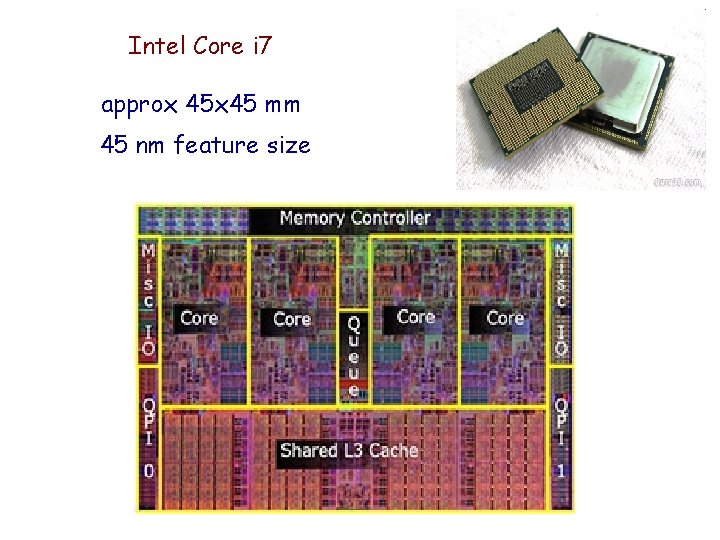

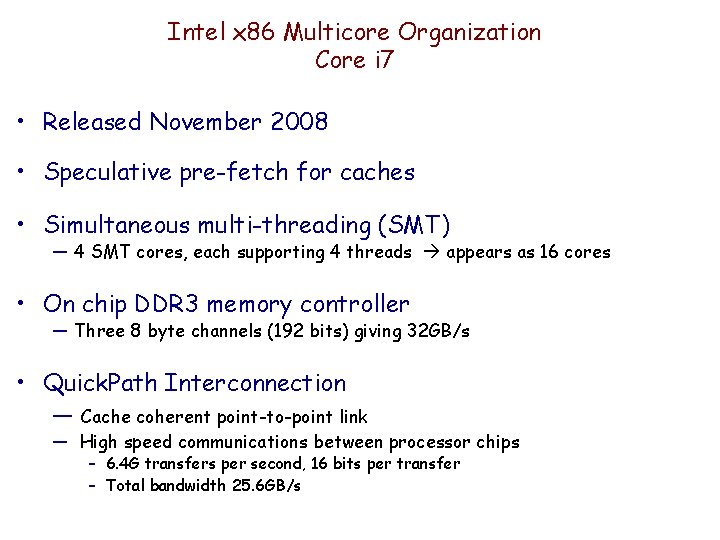

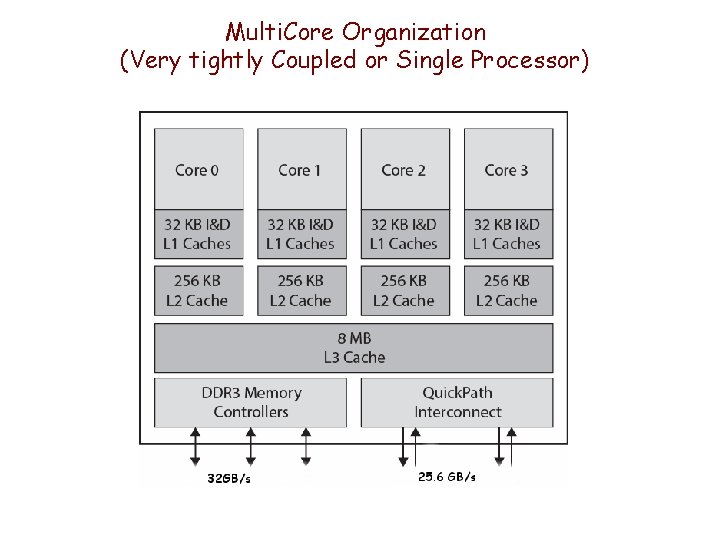

Intel x 86 Multicore Organization Core i 7 • Released November 2008 • Speculative pre-fetch for caches • Simultaneous multi-threading (SMT) — 4 SMT cores, each supporting 4 threads appears as 16 cores • On chip DDR 3 memory controller — Three 8 byte channels (192 bits) giving 32 GB/s • Quick. Path Interconnection — Cache coherent point-to-point link — High speed communications between processor chips – 6. 4 G transfers per second, 16 bits per transfer – Total bandwidth 25. 6 GB/s

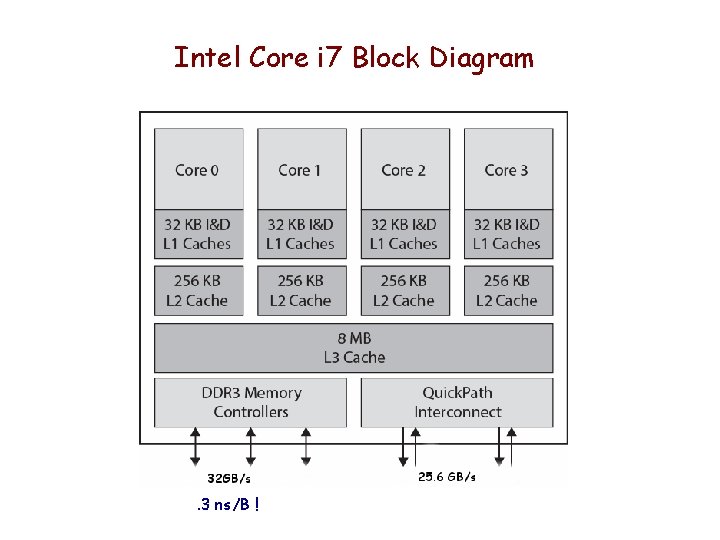

Intel Core i 7 Block Diagram . 3 ns/B !

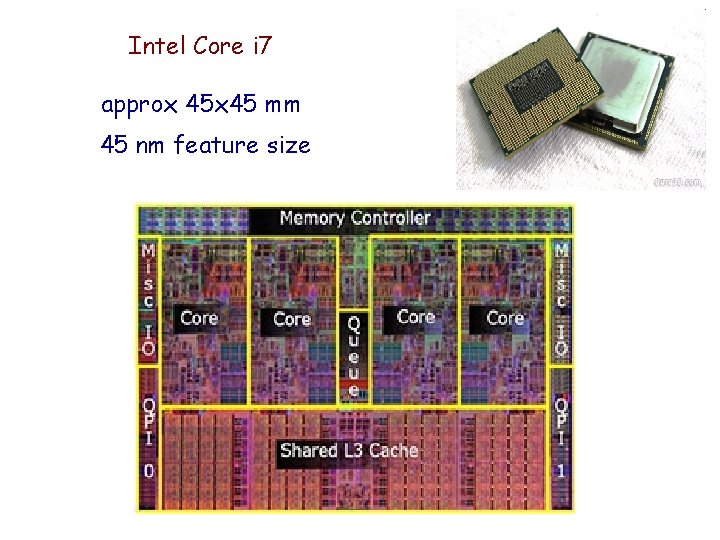

Intel Core i 7 approx 45 mm 45 nm feature size

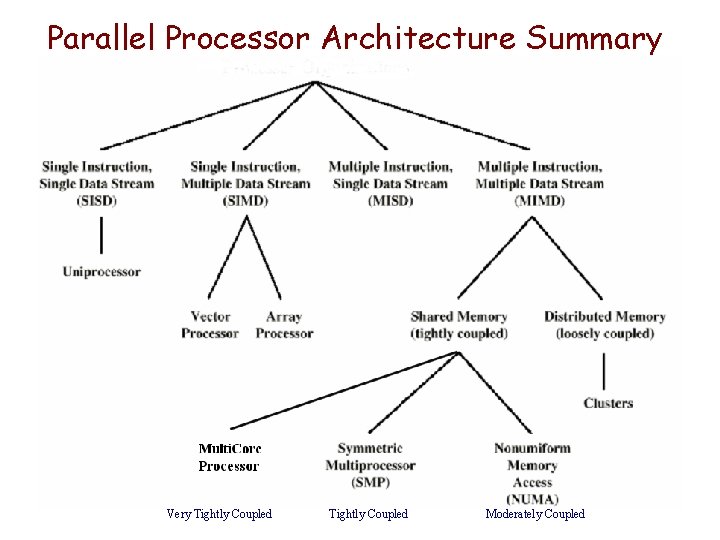

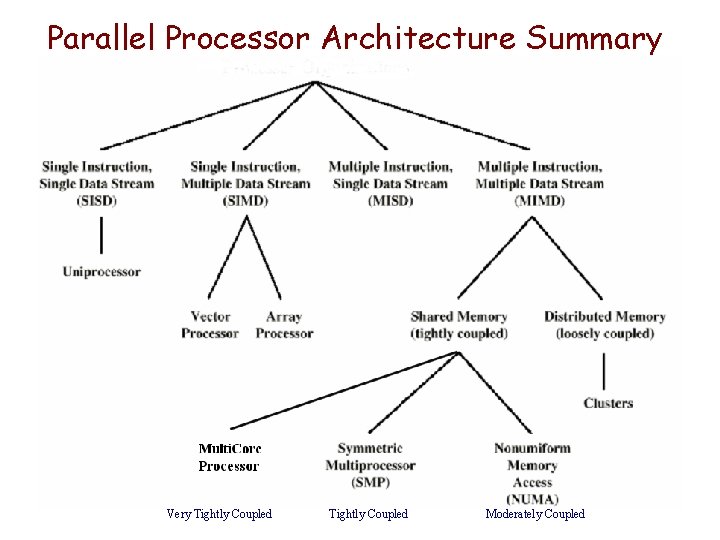

Parallel Processor Architecture Summary Very Tightly Coupled Moderately Coupled

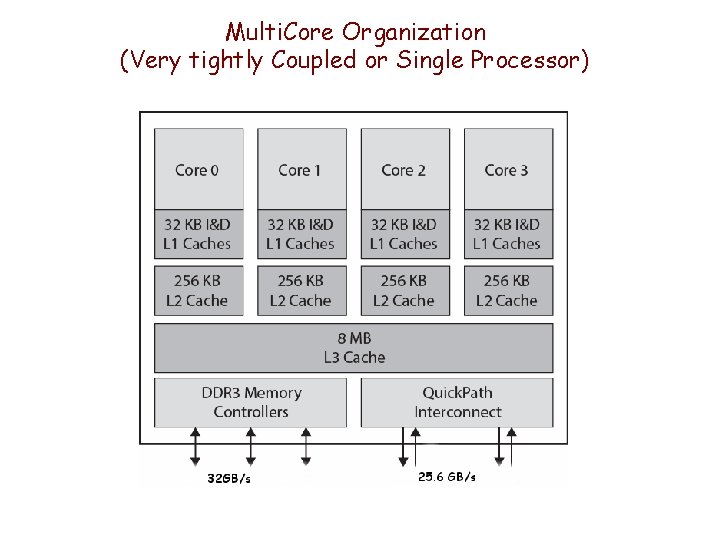

Multi. Core Organization (Very tightly Coupled or Single Processor)

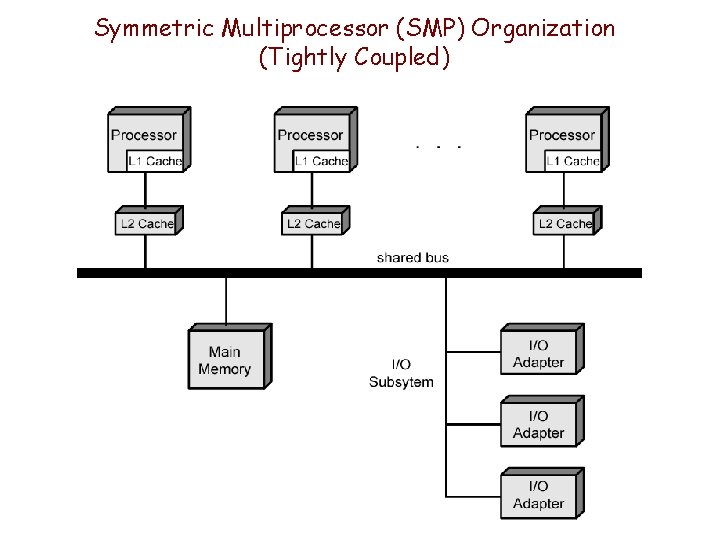

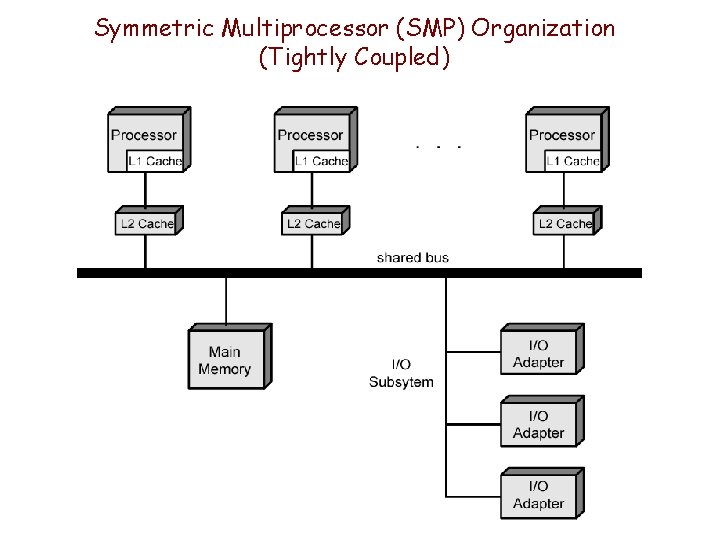

Symmetric Multiprocessor (SMP) Organization (Tightly Coupled)

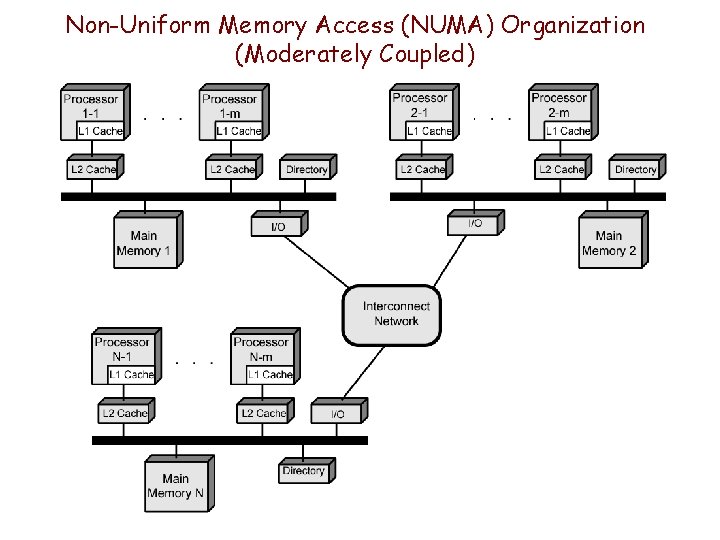

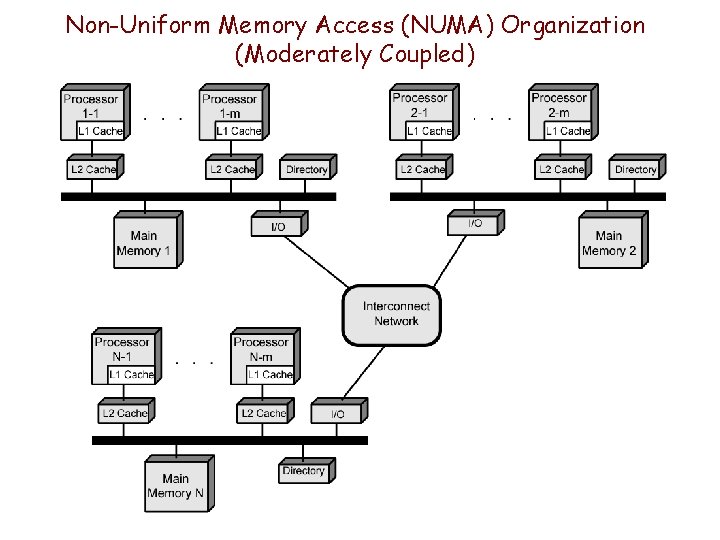

Non-Uniform Memory Access (NUMA) Organization (Moderately Coupled)

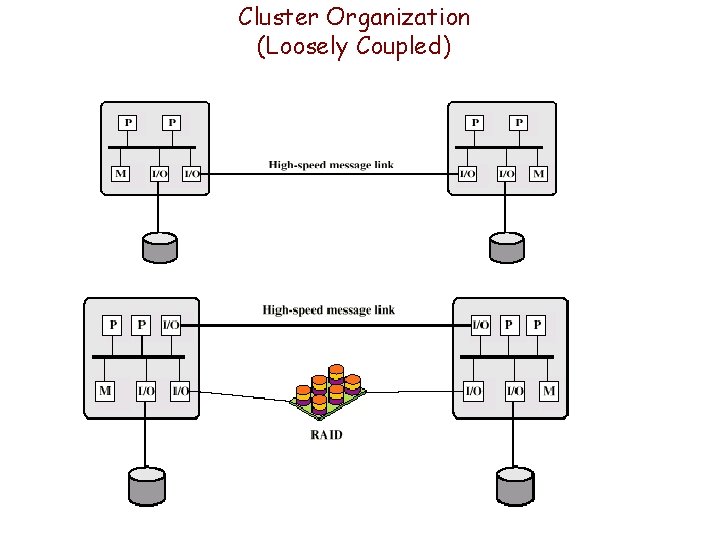

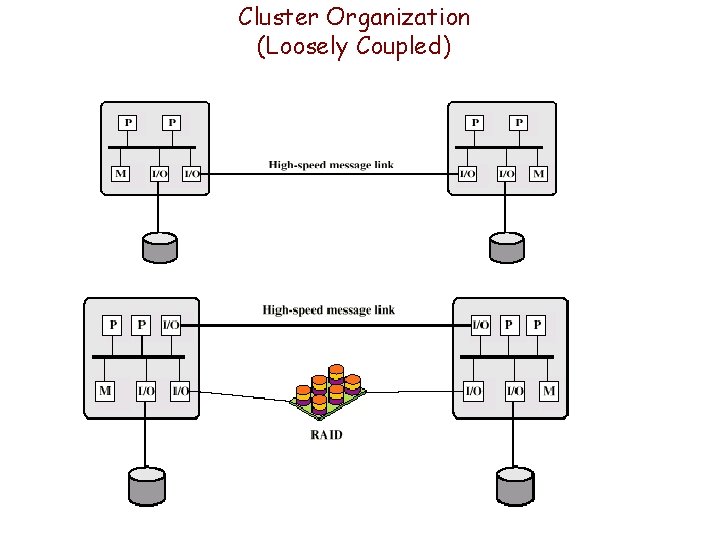

Cluster Organization (Loosely Coupled)