Chapter 13 ARM Exception Handling RealTime Embedded Multithreading

Chapter 13 ARM Exception Handling (Real-Time Embedded Multithreading : Using Thread. X® and ARM®) Department of Computer Science Hsu Hao Chen Professor Hsung-Pin Chang

Outline n n n n Exception Resulting for ARM Exception (Actions) Reset Vector Initialization Thread. X Initialization Thread Scheduling Thread. X Interrupt Handling Internal Interrupt Processing

Exception Resulting for ARM n n n Exceptions resulting for the direct effect of executing an instruction Exceptions resulting as a side effect of executing an instruction Exceptions resulting from external interrupts, unrelated to instruction execution

Exception (Actions) (1/2) n Step 1: n n Step 2: n n Modify the CPSR of the new operating mode Step 4: n n Change to the operating mode corresponding to the exception Step 3: n n Save CPSR -> SPSR Save r 15(PC) register -> r 14(LR) register Step 5: n Change the PC to the appropriate exception vector

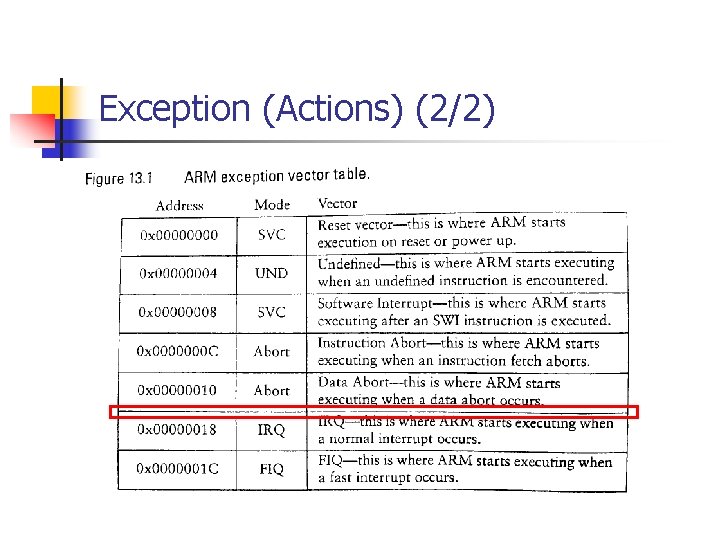

Exception (Actions) (2/2)

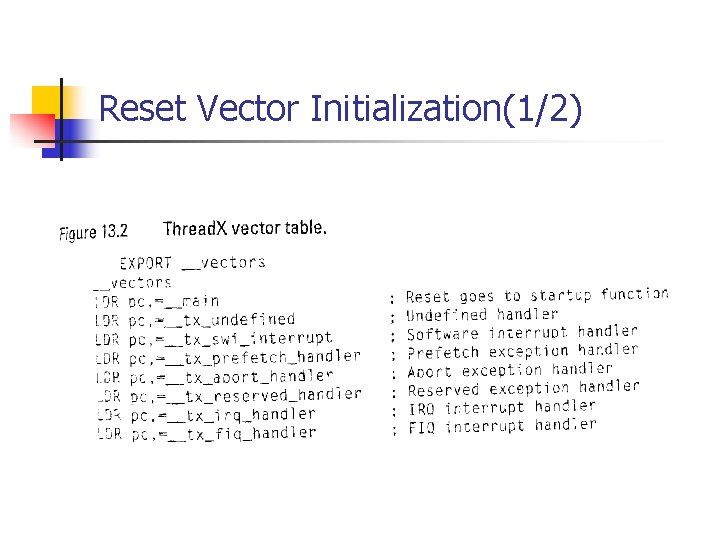

Reset Vector Initialization(1/2)

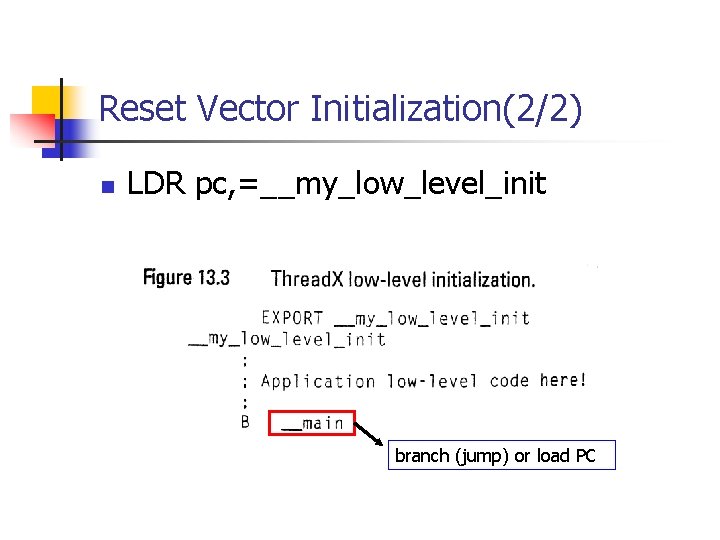

Reset Vector Initialization(2/2) n LDR pc, =__my_low_level_init branch (jump) or load PC

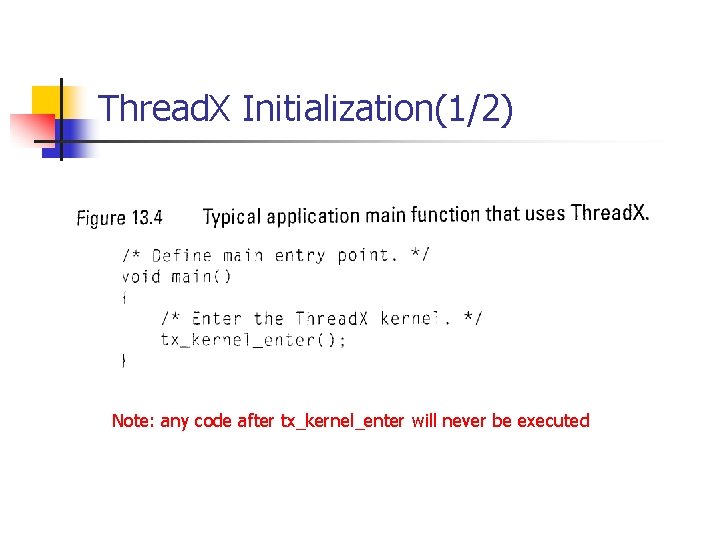

Thread. X Initialization(1/2) Note: any code after tx_kernel_enter will never be executed

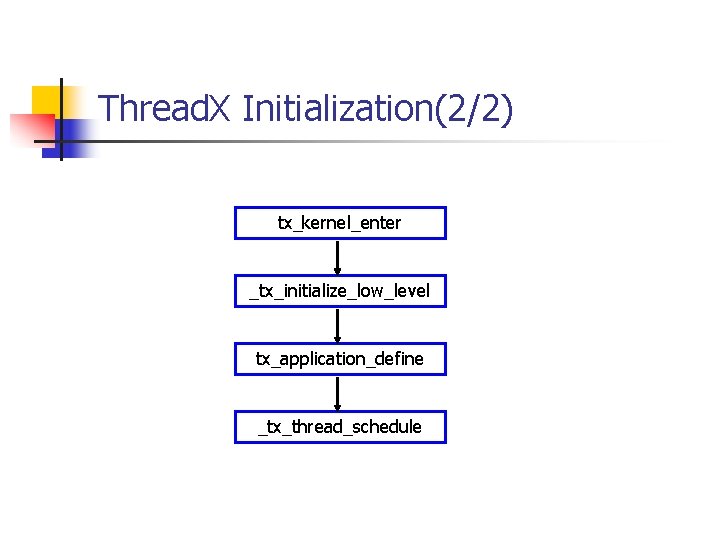

Thread. X Initialization(2/2) tx_kernel_enter _tx_initialize_low_level tx_application_define _tx_thread_schedule

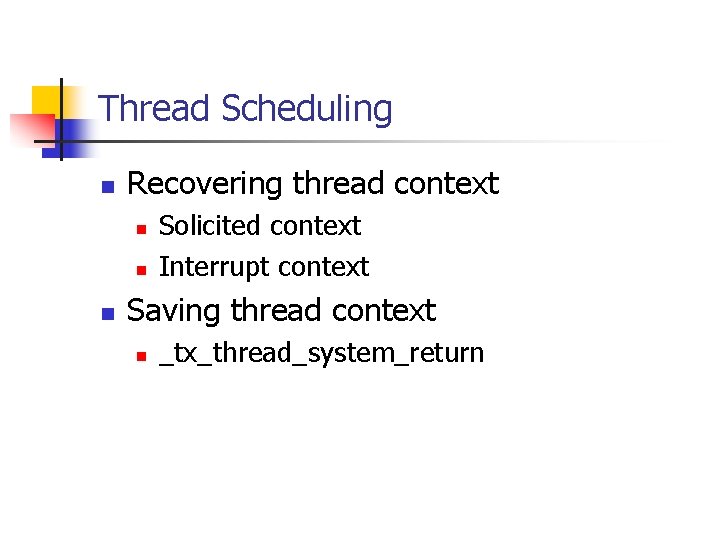

Thread Scheduling n Recovering thread context n n n Solicited context Interrupt context Saving thread context n _tx_thread_system_return

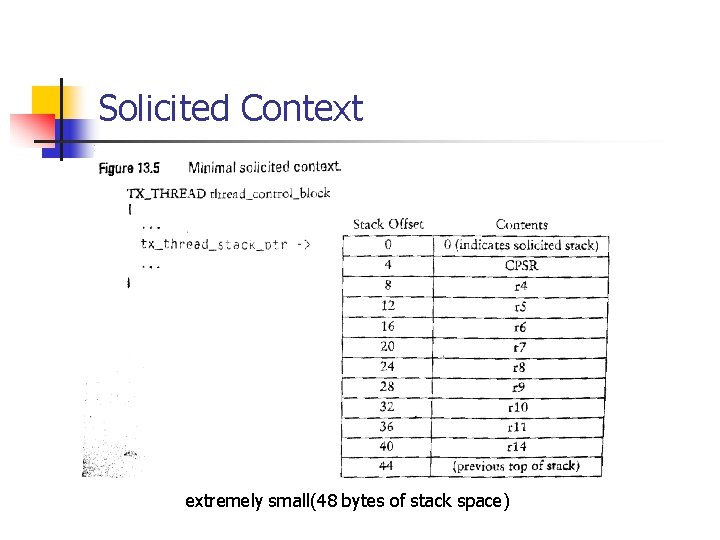

Solicited Context extremely small(48 bytes of stack space)

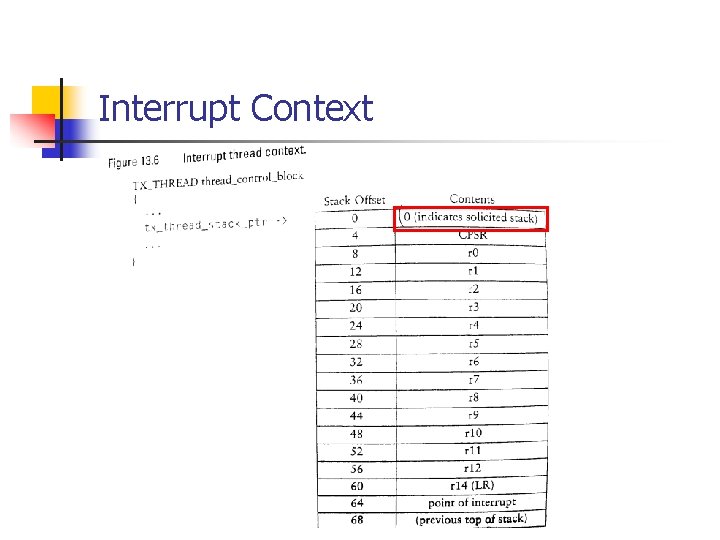

Interrupt Context

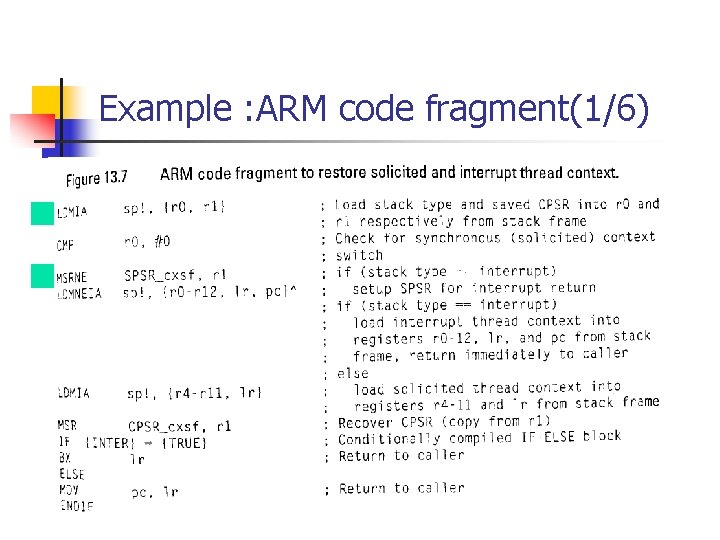

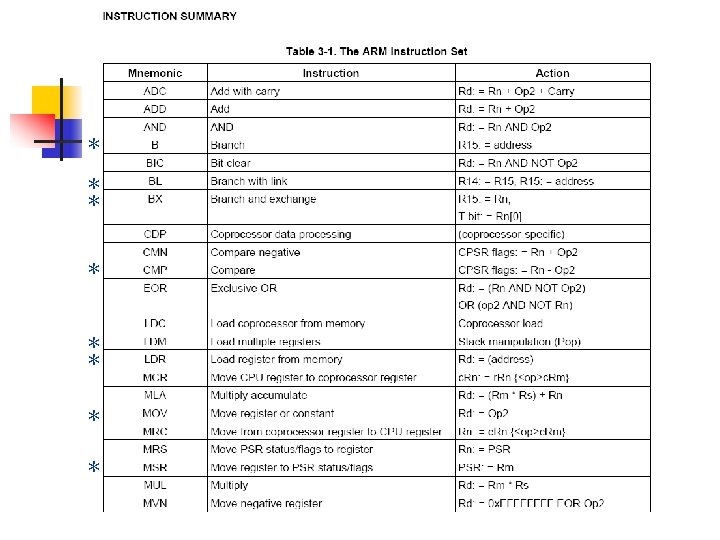

Example : ARM code fragment(1/6)

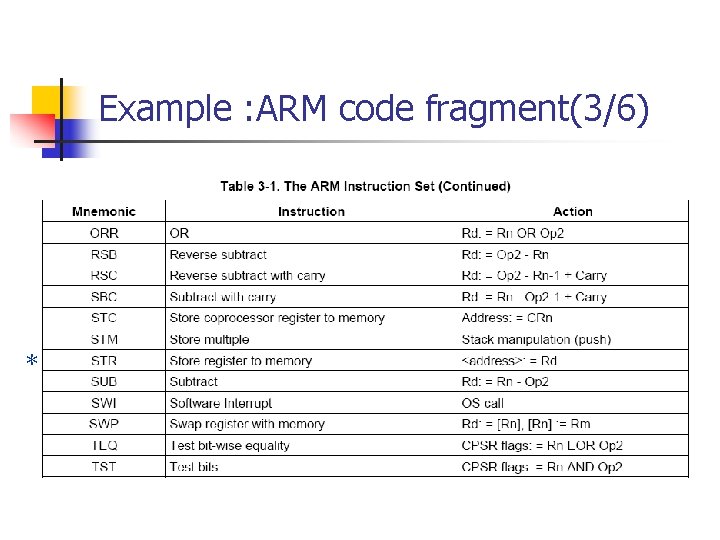

Example : ARM code fragment(3/6) *

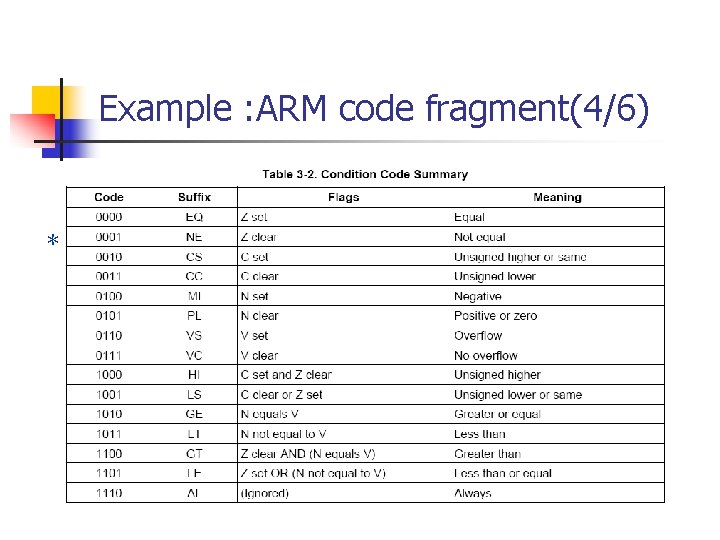

Example : ARM code fragment(4/6) *

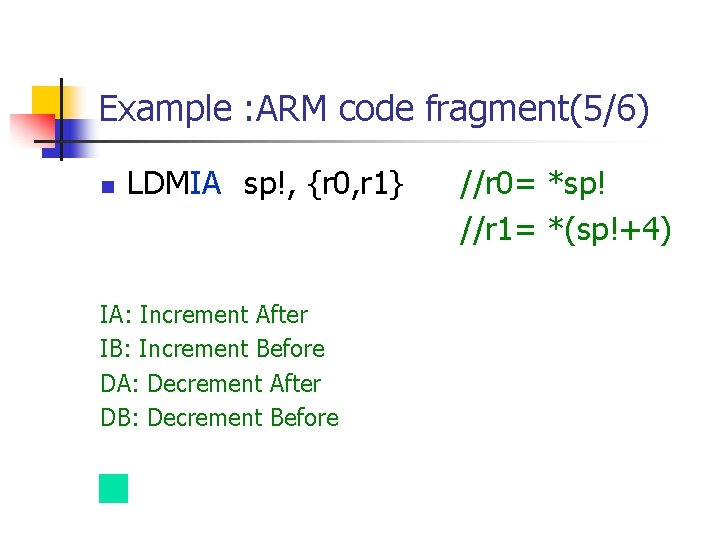

Example : ARM code fragment(5/6) n LDMIA sp!, {r 0, r 1} IA: Increment After IB: Increment Before DA: Decrement After DB: Decrement Before //r 0= *sp! //r 1= *(sp!+4)

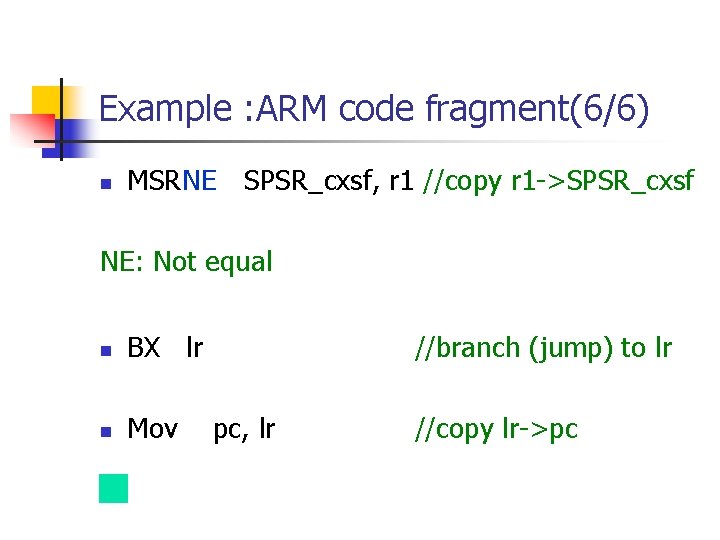

Example : ARM code fragment(6/6) n MSRNE SPSR_cxsf, r 1 //copy r 1 ->SPSR_cxsf NE: Not equal n BX lr n Mov //branch (jump) to lr pc, lr //copy lr->pc

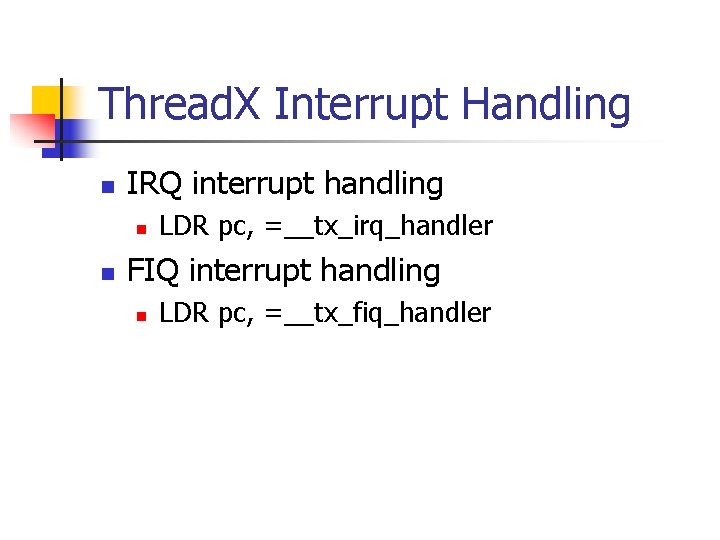

Thread. X Interrupt Handling n IRQ interrupt handling n n LDR pc, =__tx_irq_handler FIQ interrupt handling n LDR pc, =__tx_fiq_handler

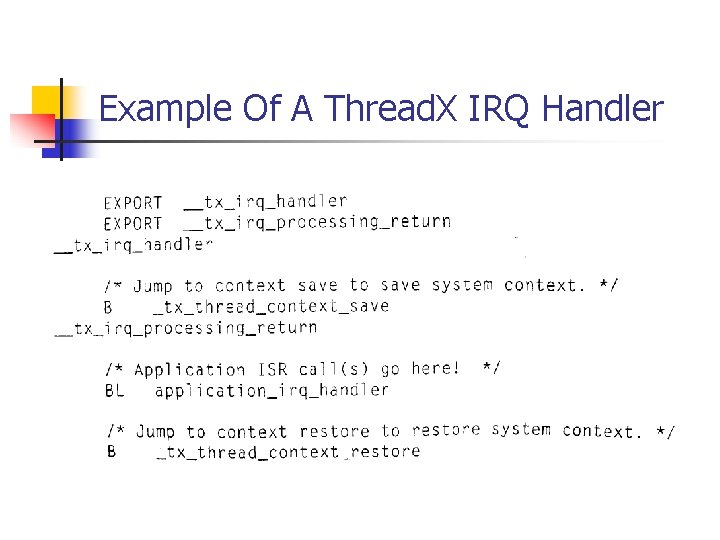

Example Of A Thread. X IRQ Handler

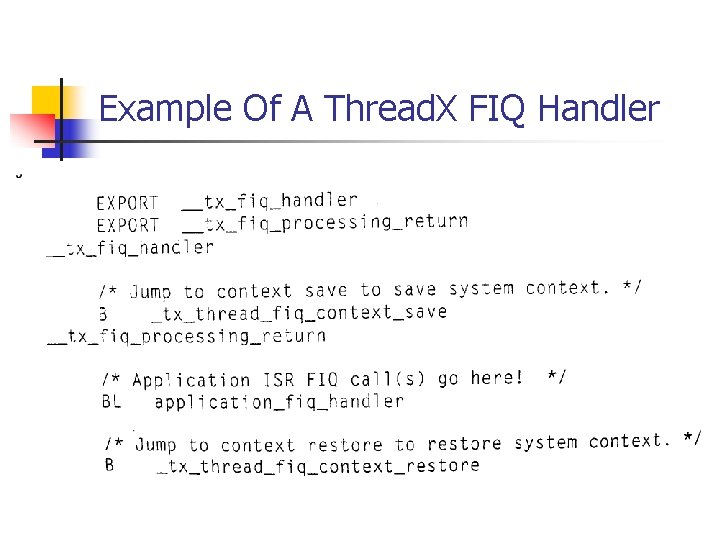

Example Of A Thread. X FIQ Handler

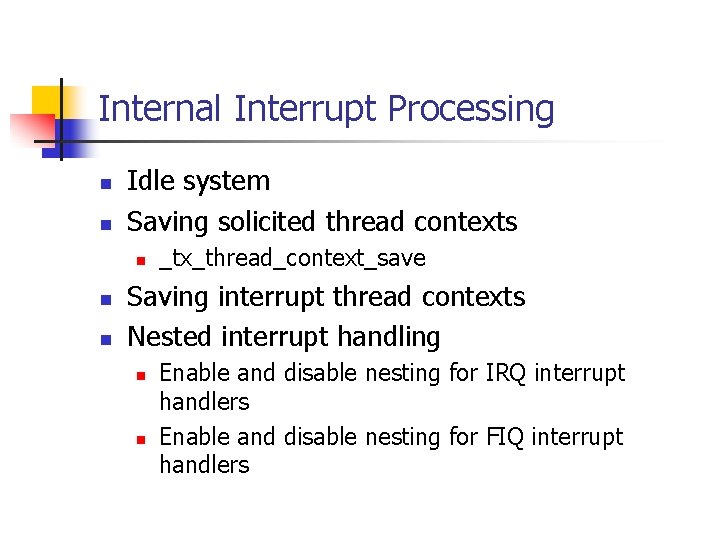

Internal Interrupt Processing n n Idle system Saving solicited thread contexts n n n _tx_thread_context_save Saving interrupt thread contexts Nested interrupt handling n n Enable and disable nesting for IRQ interrupt handlers Enable and disable nesting for FIQ interrupt handlers

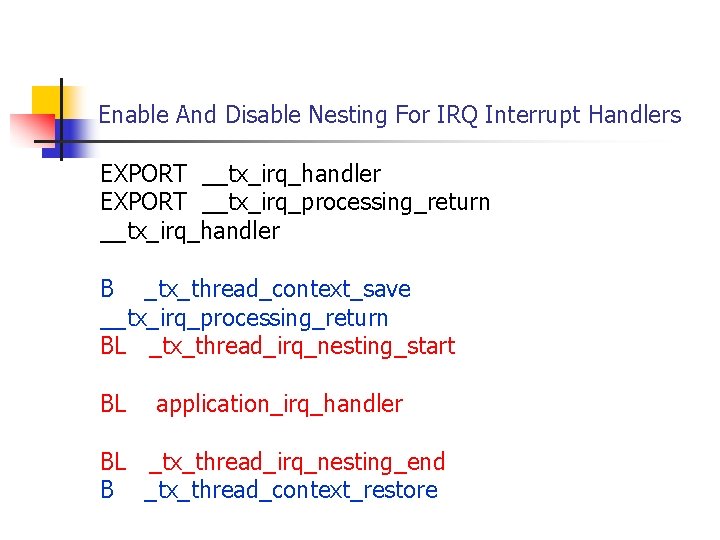

Enable And Disable Nesting For IRQ Interrupt Handlers EXPORT __tx_irq_handler EXPORT __tx_irq_processing_return __tx_irq_handler B _tx_thread_context_save __tx_irq_processing_return BL _tx_thread_irq_nesting_start BL application_irq_handler BL _tx_thread_irq_nesting_end B _tx_thread_context_restore

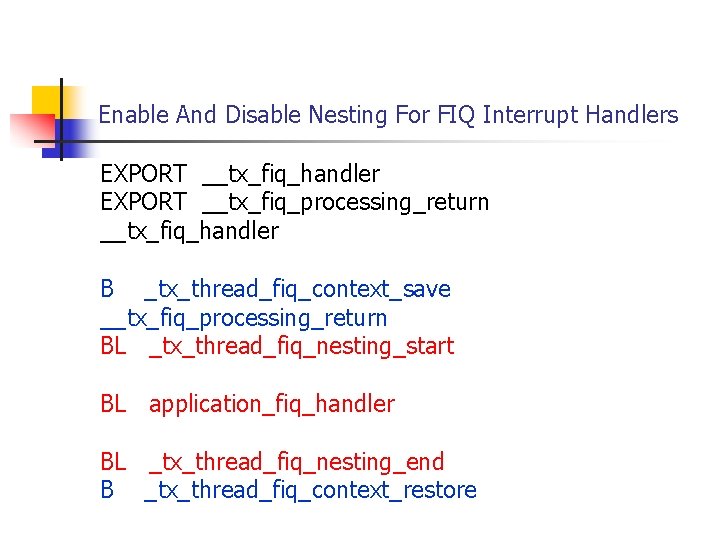

Enable And Disable Nesting For FIQ Interrupt Handlers EXPORT __tx_fiq_handler EXPORT __tx_fiq_processing_return __tx_fiq_handler B _tx_thread_fiq_context_save __tx_fiq_processing_return BL _tx_thread_fiq_nesting_start BL application_fiq_handler BL _tx_thread_fiq_nesting_end B _tx_thread_fiq_context_restore

- Slides: 24