Chapter 10 The Stack Stack An Abstract Data

Chapter 10 The Stack

Stack: An Abstract Data Type An important abstraction that you will encounter in many applications. We will describe two uses: Interrupt-Driven I/O • The rest of the story… Evaluating arithmetic expressions • Store intermediate results on stack instead of in registers 10 -2

Stacks A LIFO (last-in first-out) storage structure. • The first thing you put in is the last thing you take out. • The last thing you put in is the first thing you take out. Many different implementations satisfy the above definition. Two main operations: PUSH: add an item to the stack POP: remove an item from the stack 10 -3

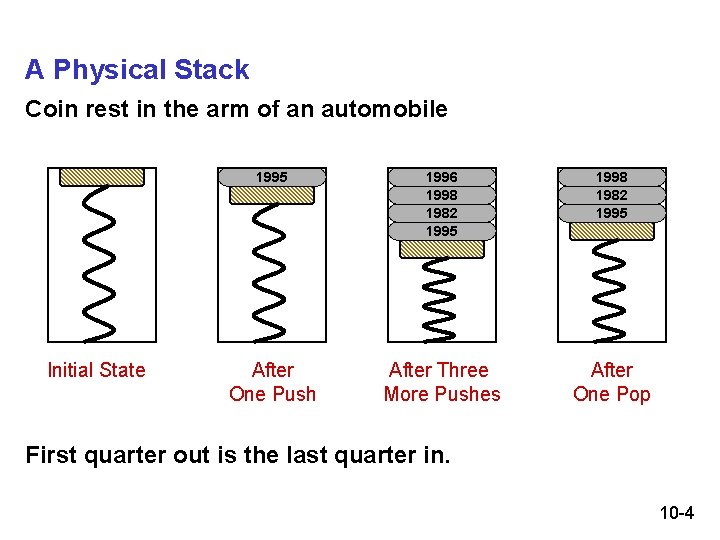

A Physical Stack Coin rest in the arm of an automobile Initial State 1995 1996 1998 1982 1995 After One Push After Three More Pushes After One Pop First quarter out is the last quarter in. 10 -4

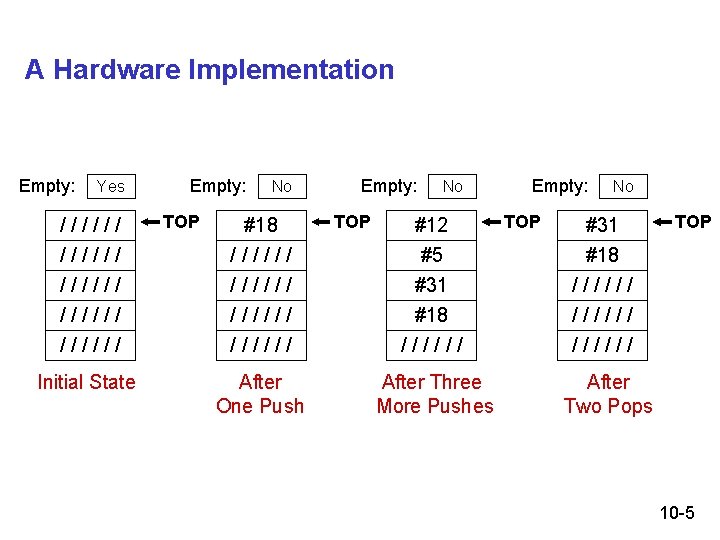

A Hardware Implementation Empty: Yes ////// Empty: TOP No #18 ////// Empty: TOP No #12 #5 ////// ////// #31 #18 ////// Initial State After One Push After Three More Pushes Empty: TOP No #31 #18 TOP ////// After Two Pops 10 -5

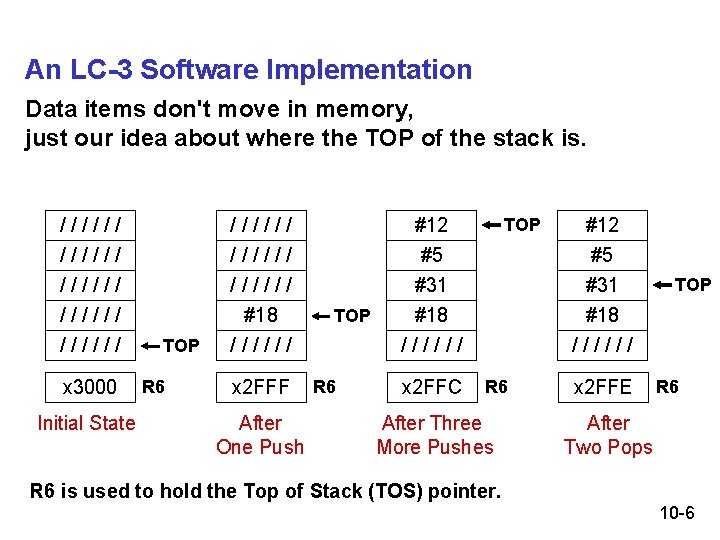

An LC-3 Software Implementation Data items don't move in memory, just our idea about where the TOP of the stack is. ////// #12 #5 ////// #18 ////// #31 #18 ////// x 3000 Initial State TOP R 6 x 2 FFF After One Push TOP R 6 x 2 FFC TOP #12 #5 #31 #18 ////// R 6 After Three More Pushes x 2 FFE TOP R 6 After Two Pops R 6 is used to hold the Top of Stack (TOS) pointer. 10 -6

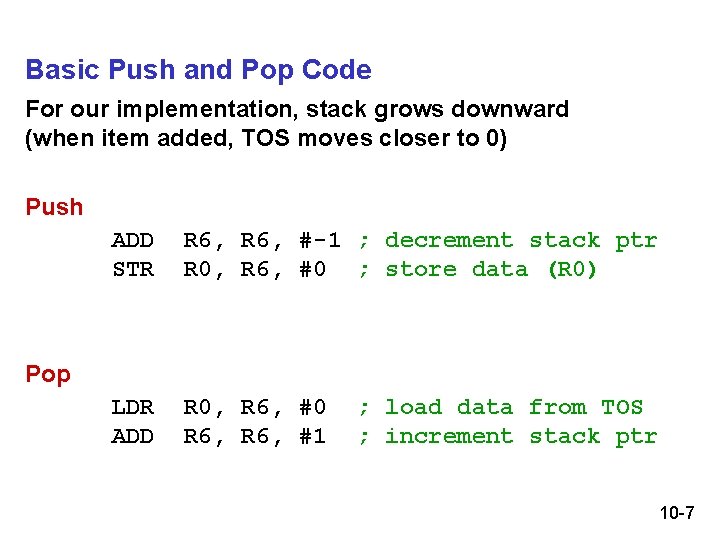

Basic Push and Pop Code For our implementation, stack grows downward (when item added, TOS moves closer to 0) Push ADD STR R 6, #-1 ; decrement stack ptr R 0, R 6, #0 ; store data (R 0) LDR ADD R 0, R 6, #0 R 6, #1 Pop ; load data from TOS ; increment stack ptr 10 -7

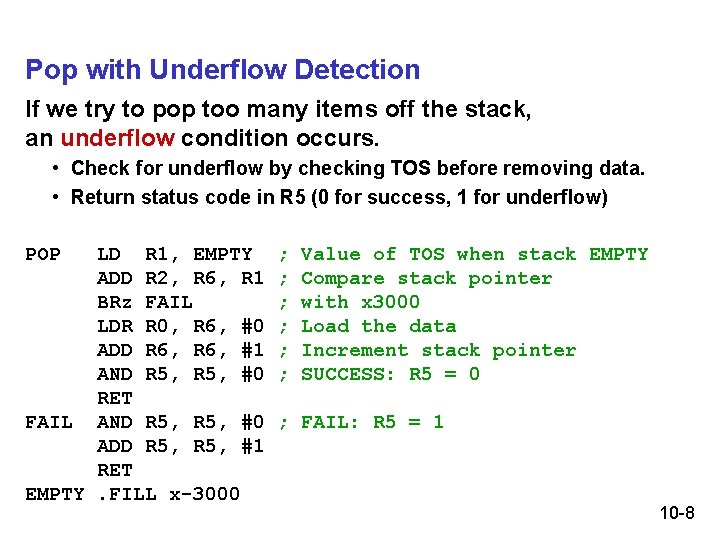

Pop with Underflow Detection If we try to pop too many items off the stack, an underflow condition occurs. • Check for underflow by checking TOS before removing data. • Return status code in R 5 (0 for success, 1 for underflow) POP LD R 1, EMPTY ADD R 2, R 6, R 1 BRz FAIL LDR R 0, R 6, #0 ADD R 6, #1 AND R 5, #0 RET FAIL AND R 5, #0 ADD R 5, #1 RET EMPTY. FILL x-3000 ; ; ; Value of TOS when stack EMPTY Compare stack pointer with x 3000 Load the data Increment stack pointer SUCCESS: R 5 = 0 ; FAIL: R 5 = 1 10 -8

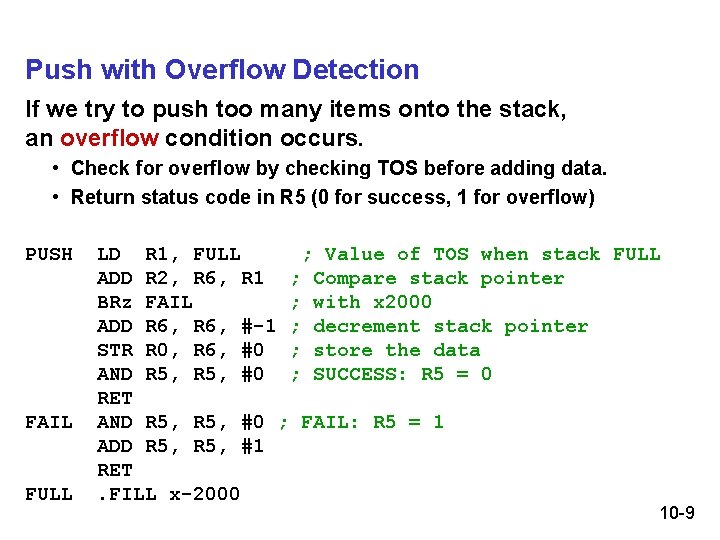

Push with Overflow Detection If we try to push too many items onto the stack, an overflow condition occurs. • Check for overflow by checking TOS before adding data. • Return status code in R 5 (0 for success, 1 for overflow) PUSH FAIL FULL LD R 1, FULL ; Value of TOS when stack FULL ADD R 2, R 6, R 1 ; Compare stack pointer BRz FAIL ; with x 2000 ADD R 6, #-1 ; decrement stack pointer STR R 0, R 6, #0 ; store the data AND R 5, #0 ; SUCCESS: R 5 = 0 RET AND R 5, #0 ; FAIL: R 5 = 1 ADD R 5, #1 RET. FILL x-2000 10 -9

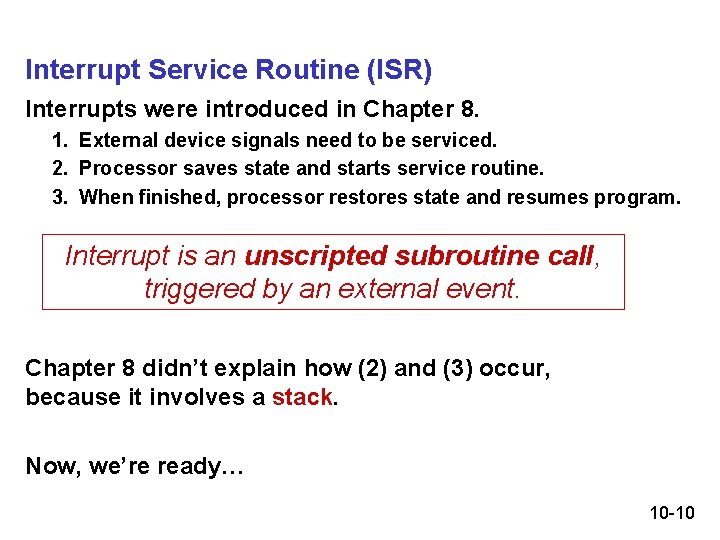

Interrupt Service Routine (ISR) Interrupts were introduced in Chapter 8. 1. External device signals need to be serviced. 2. Processor saves state and starts service routine. 3. When finished, processor restores state and resumes program. Interrupt is an unscripted subroutine call, triggered by an external event. Chapter 8 didn’t explain how (2) and (3) occur, because it involves a stack. Now, we’re ready… 10 -10

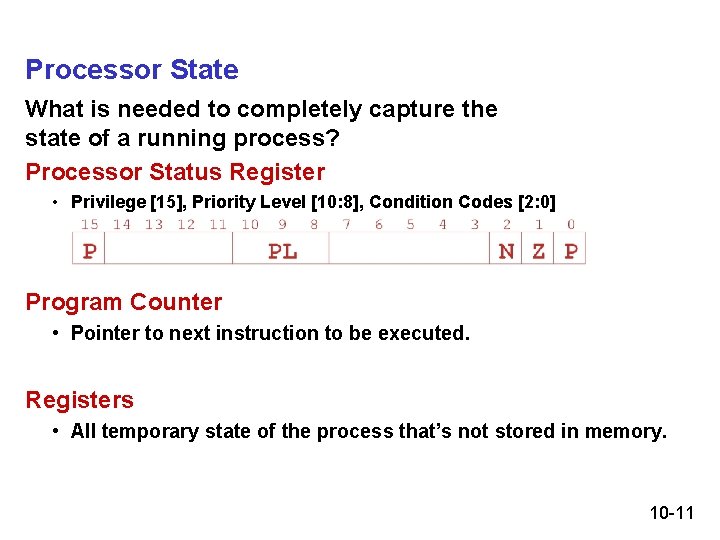

Processor State What is needed to completely capture the state of a running process? Processor Status Register • Privilege [15], Priority Level [10: 8], Condition Codes [2: 0] Program Counter • Pointer to next instruction to be executed. Registers • All temporary state of the process that’s not stored in memory. 10 -11

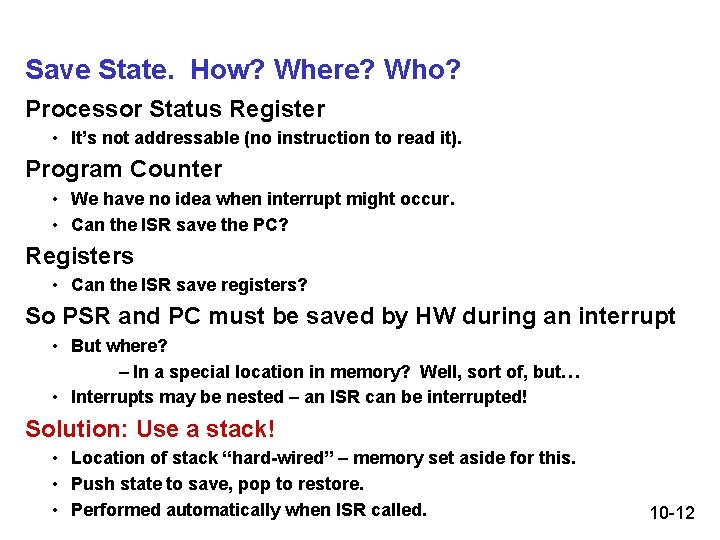

Save State. How? Where? Who? Processor Status Register • It’s not addressable (no instruction to read it). Program Counter • We have no idea when interrupt might occur. • Can the ISR save the PC? Registers • Can the ISR save registers? So PSR and PC must be saved by HW during an interrupt • But where? – In a special location in memory? Well, sort of, but… • Interrupts may be nested – an ISR can be interrupted! Solution: Use a stack! • Location of stack “hard-wired” – memory set aside for this. • Push state to save, pop to restore. • Performed automatically when ISR called. 10 -12

Supervisor Stack A special region of memory used as the stack for interrupt service routines. • Manually set this for the LC-3, using R 6 as stack pointer Use R 6 as stack pointer. • So that our PUSH/POP routines (from before) still work. 10 -13

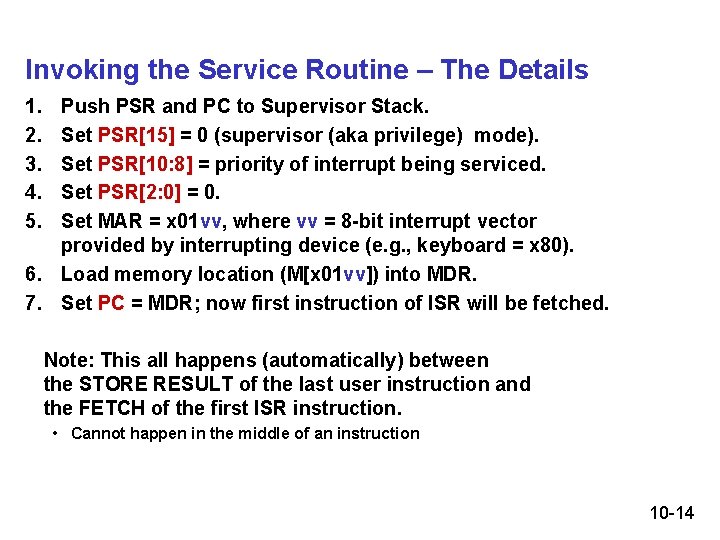

Invoking the Service Routine – The Details 1. 2. 3. 4. 5. Push PSR and PC to Supervisor Stack. Set PSR[15] = 0 (supervisor (aka privilege) mode). Set PSR[10: 8] = priority of interrupt being serviced. Set PSR[2: 0] = 0. Set MAR = x 01 vv, where vv = 8 -bit interrupt vector provided by interrupting device (e. g. , keyboard = x 80). 6. Load memory location (M[x 01 vv]) into MDR. 7. Set PC = MDR; now first instruction of ISR will be fetched. Note: This all happens (automatically) between the STORE RESULT of the last user instruction and the FETCH of the first ISR instruction. • Cannot happen in the middle of an instruction 10 -14

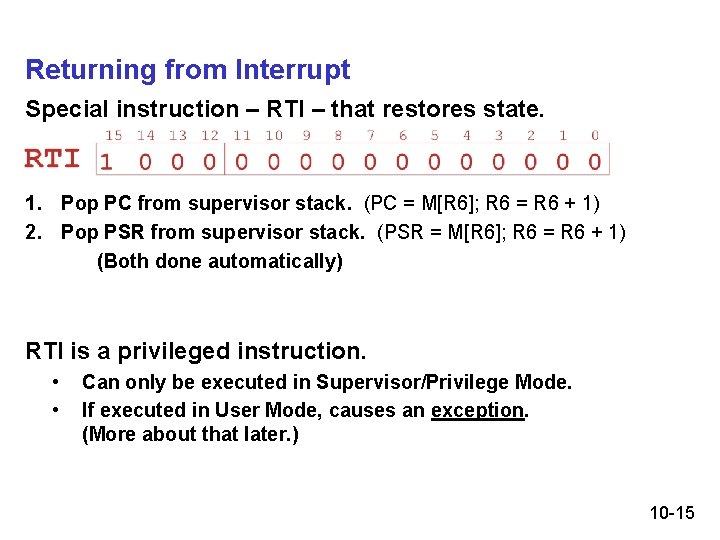

Returning from Interrupt Special instruction – RTI – that restores state. 1. Pop PC from supervisor stack. (PC = M[R 6]; R 6 = R 6 + 1) 2. Pop PSR from supervisor stack. (PSR = M[R 6]; R 6 = R 6 + 1) (Both done automatically) RTI is a privileged instruction. • • Can only be executed in Supervisor/Privilege Mode. If executed in User Mode, causes an exception. (More about that later. ) 10 -15

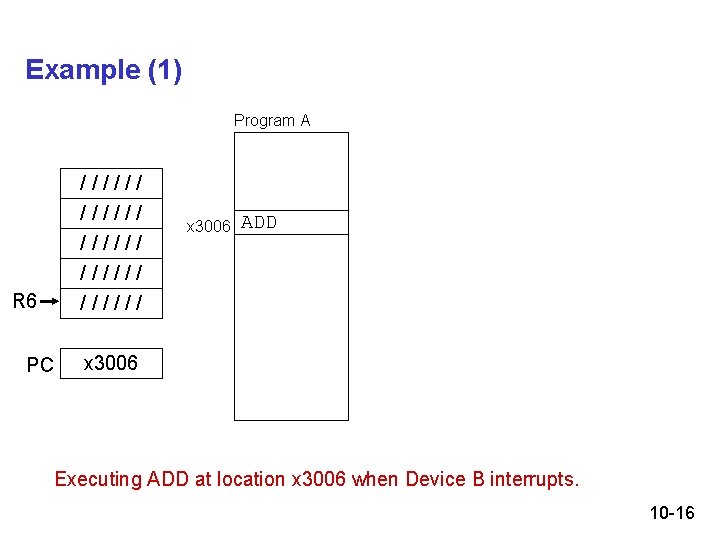

Example (1) Program A ////// x 3006 ADD ////// R 6 PC x 3006 Executing ADD at location x 3006 when Device B interrupts. 10 -16

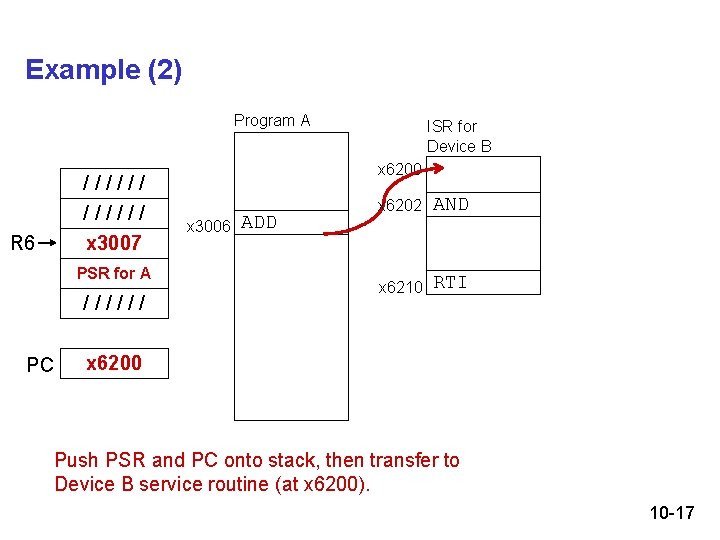

Example (2) Program A ////// x 3007 R 6 PSR for A ////// PC ISR for Device B x 6200 x 3006 ADD x 6202 AND x 6210 RTI x 6200 Push PSR and PC onto stack, then transfer to Device B service routine (at x 6200). 10 -17

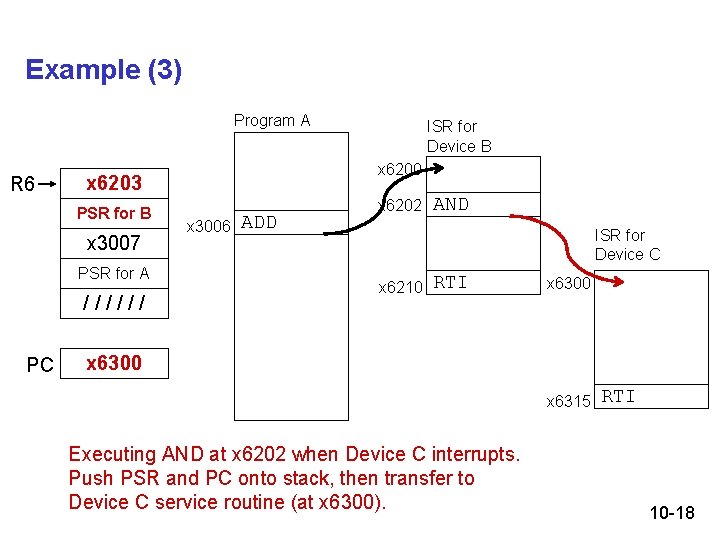

Example (3) Program A R 6 x 3007 PSR for A ////// PC x 6200 x 6203 PSR for B ISR for Device B x 3006 ADD x 6202 AND ISR for Device C x 6210 RTI x 6300 x 6315 Executing AND at x 6202 when Device C interrupts. Push PSR and PC onto stack, then transfer to Device C service routine (at x 6300). RTI 10 -18

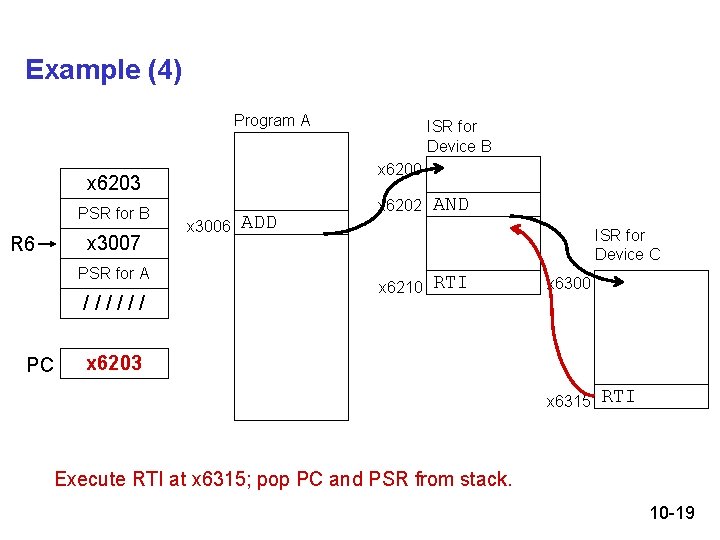

Example (4) Program A x 6200 x 6203 PSR for B x 3007 R 6 PSR for A ////// PC ISR for Device B x 3006 ADD x 6202 AND ISR for Device C x 6210 RTI x 6300 x 6203 x 6315 RTI Execute RTI at x 6315; pop PC and PSR from stack. 10 -19

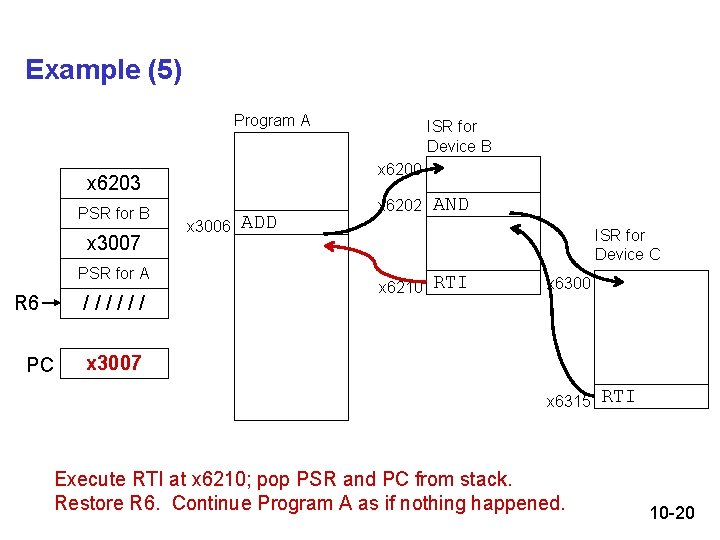

Example (5) Program A x 6200 x 6203 PSR for B x 3007 PSR for A R 6 ////// PC ISR for Device B x 3006 ADD x 6202 AND ISR for Device C x 6210 RTI x 6300 x 3007 x 6315 Execute RTI at x 6210; pop PSR and PC from stack. Restore R 6. Continue Program A as if nothing happened. RTI 10 -20

Exception: Internal Interrupt When something unexpected happens inside the processor, it may cause an exception. Examples: • • Privileged operation (e. g. , RTI in user mode) Executing an illegal opcode Divide by zero Accessing an illegal address (e. g. , protected system memory) Handled just like an interrupt • Vector is determined internally by type of exception • Priority is the same as running program 10 -21

Another use for a stack: Arithmetic Reverse Polish Notation (RPN) Calculators Instead of registers, some ISA's use a stack for source and destination operations: a zero-address machine. Operations: Push – place something on the top of the stack Pop – remove item on the top of the stack Arithmetic Operations – • pop two items from the stack • perform operation with those two items • push result onto stack 10 -22

Comparison – Registers vs. Stack-Based Write E = (A+B)*(C+D) using General Purpose Registers (Assume A, B, C, D, and E are labels for a memory location. ) 10 -23

Comparison – Registers vs. Stack-Based Write E = (A+B)*(C+D) using a stack: 10 -24

Comparison – Registers vs. Stack-Based Which instructions are larger? Which requires more instructions? Which requires more memory operations? Why use a stack? • • Computer has few registers (registers were once expensive) Simple programming model and ISA Java’s machine model is a stack. Reality: stack is stored on-chip in cache 10 -25

- Slides: 25