Chapter 10 InputOutput Organization Images courtesy of Addison

- Slides: 74

Chapter 10 Input/Output Organization Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Chapter Outline • • Asynchronous data transfers Programmed I/O Interrupts Direct Memory Access I/O Processors Serial Communication Standards Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

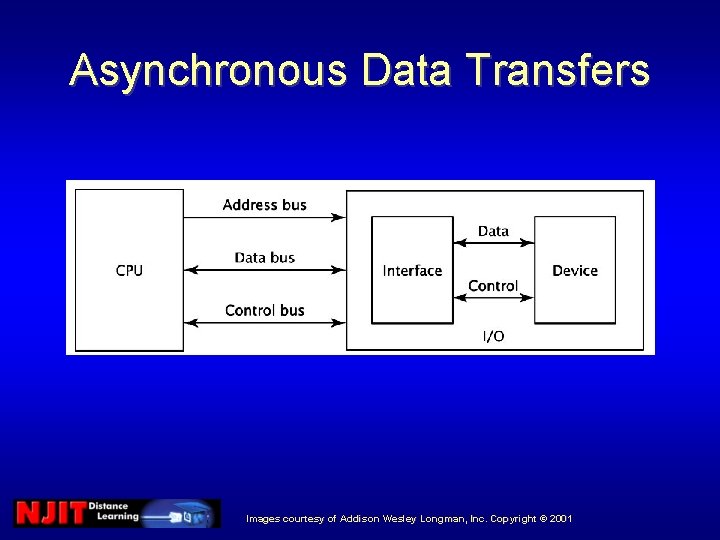

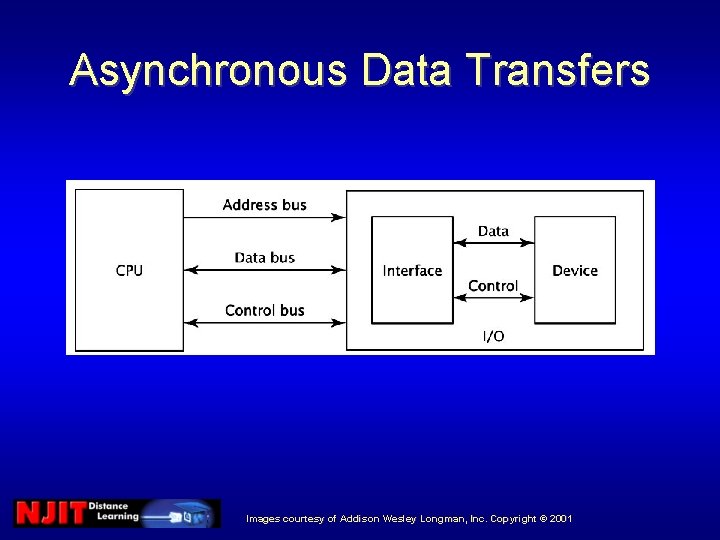

Asynchronous Data Transfers Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

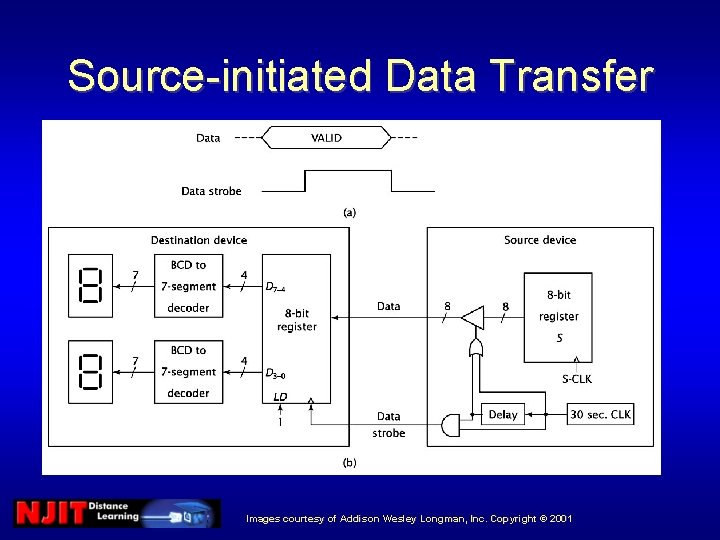

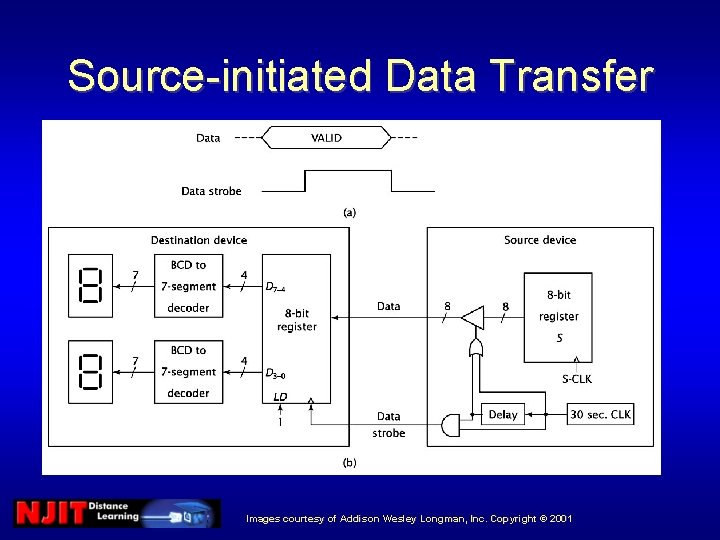

Source-initiated Data Transfer Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

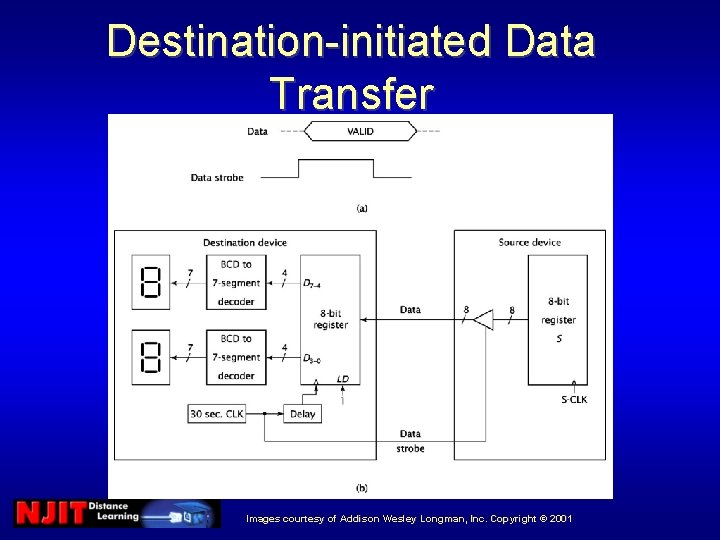

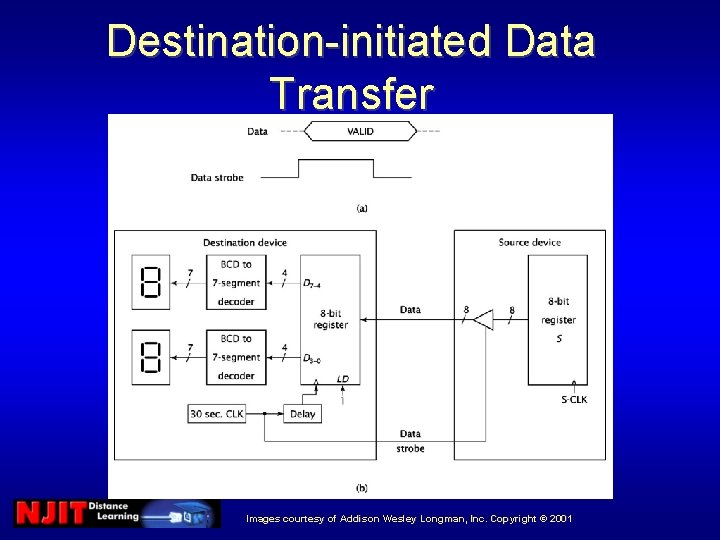

Destination-initiated Data Transfer Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

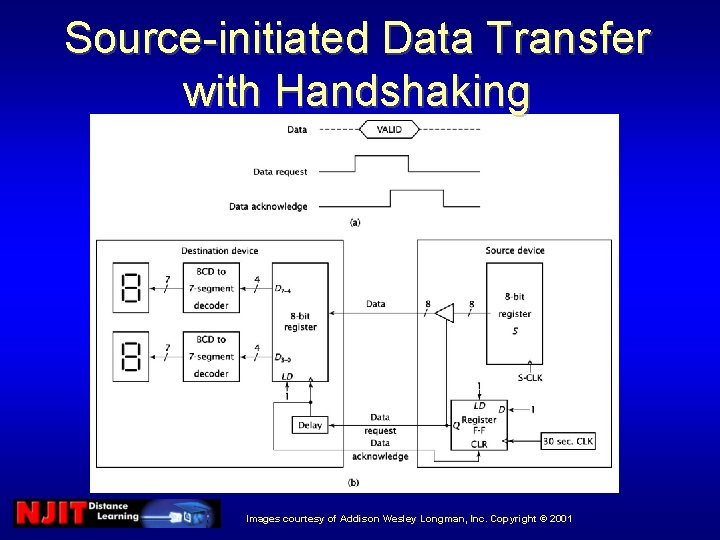

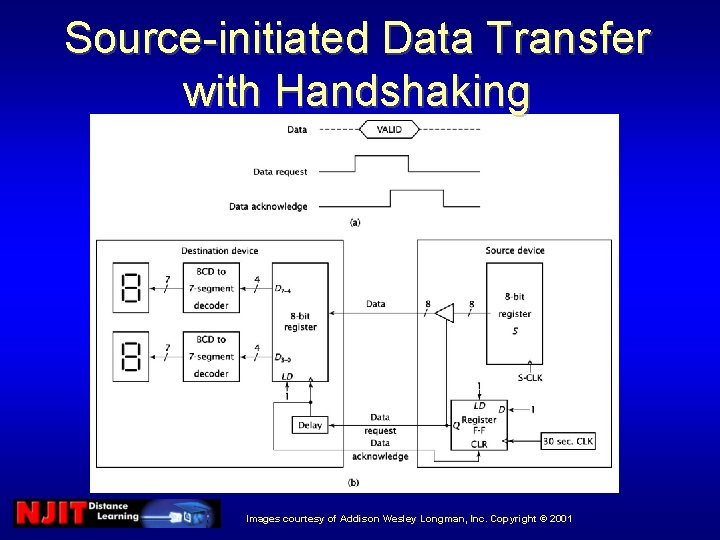

Source-initiated Data Transfer with Handshaking Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

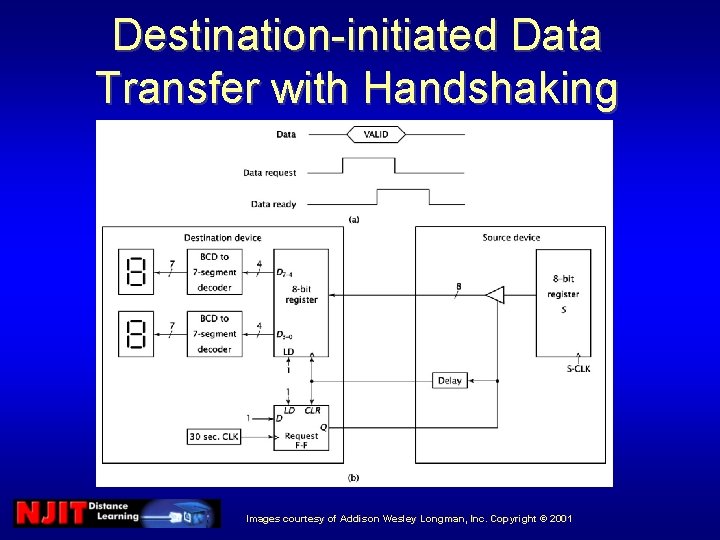

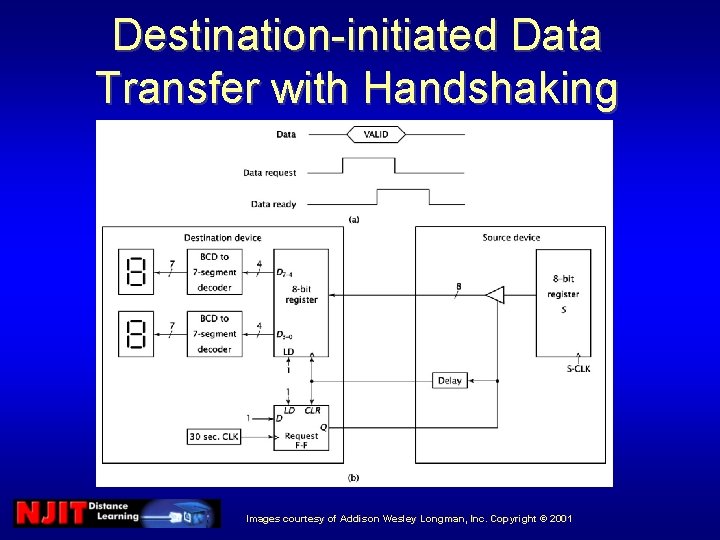

Destination-initiated Data Transfer with Handshaking Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

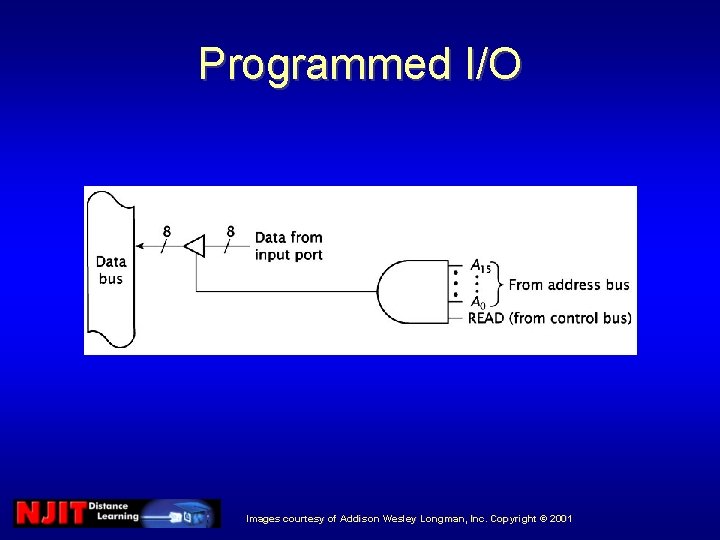

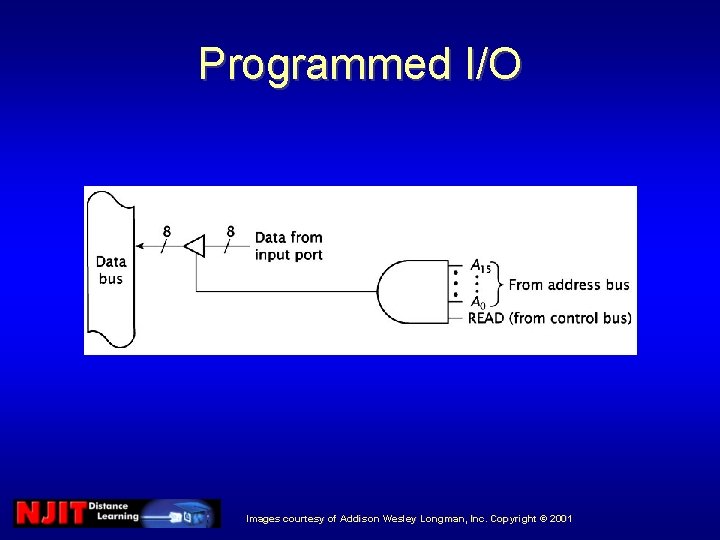

Programmed I/O Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

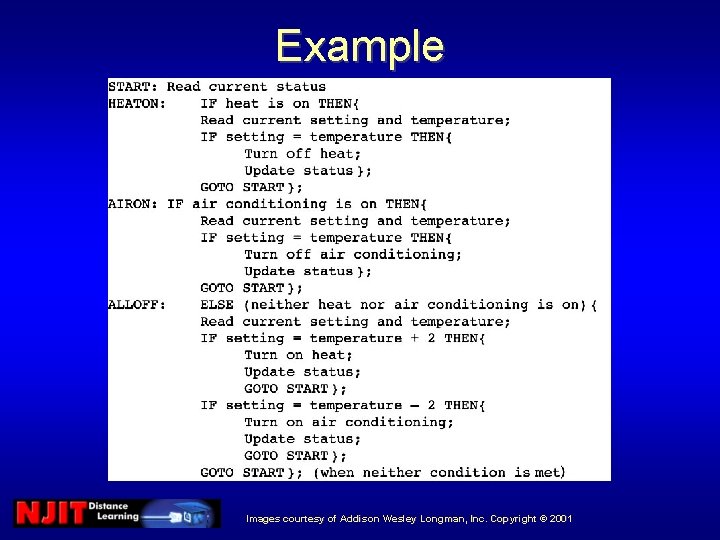

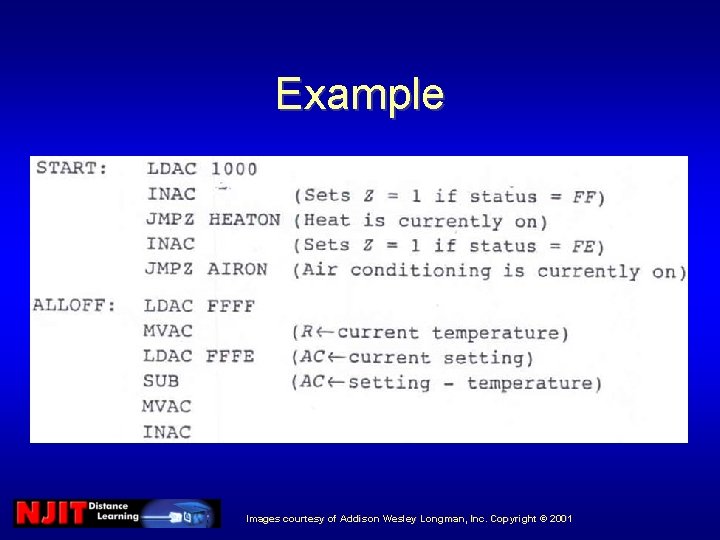

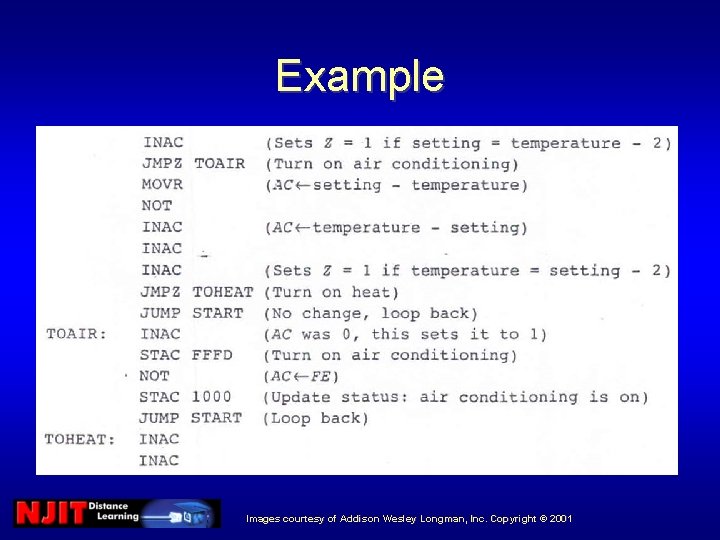

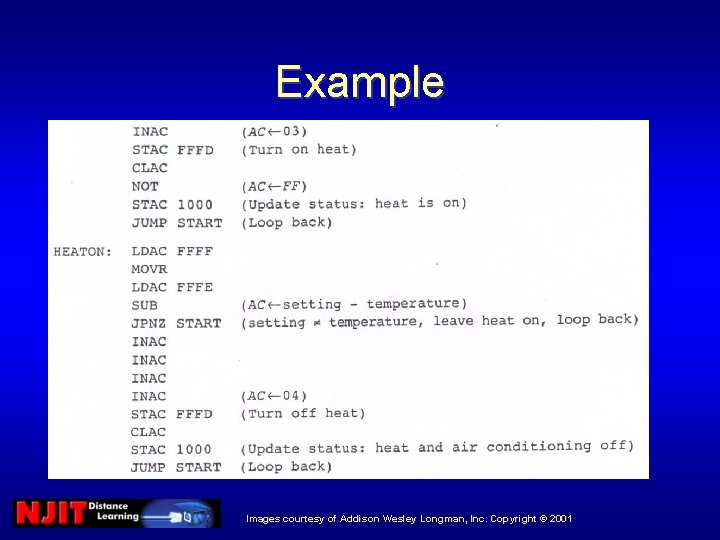

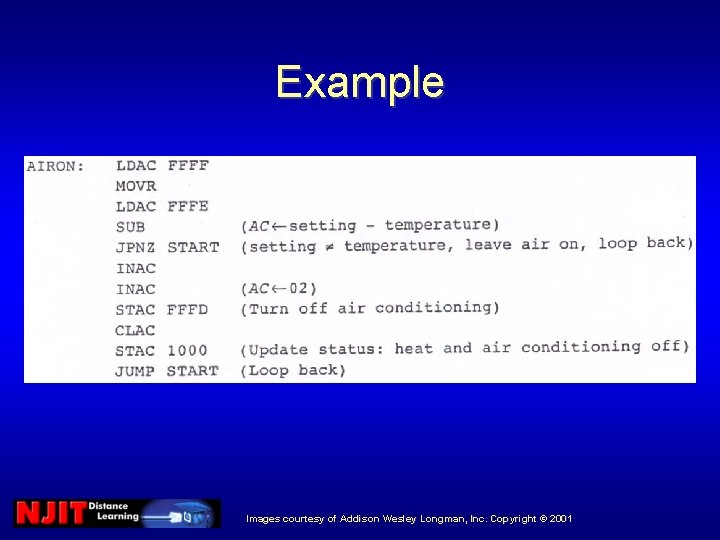

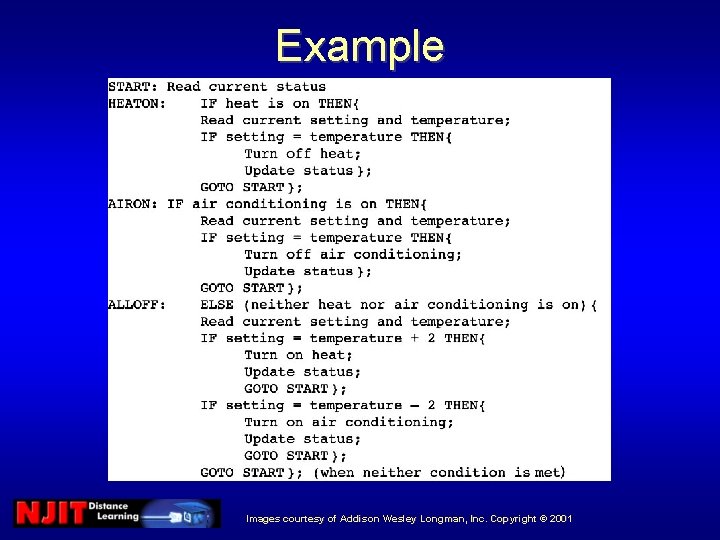

Example Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

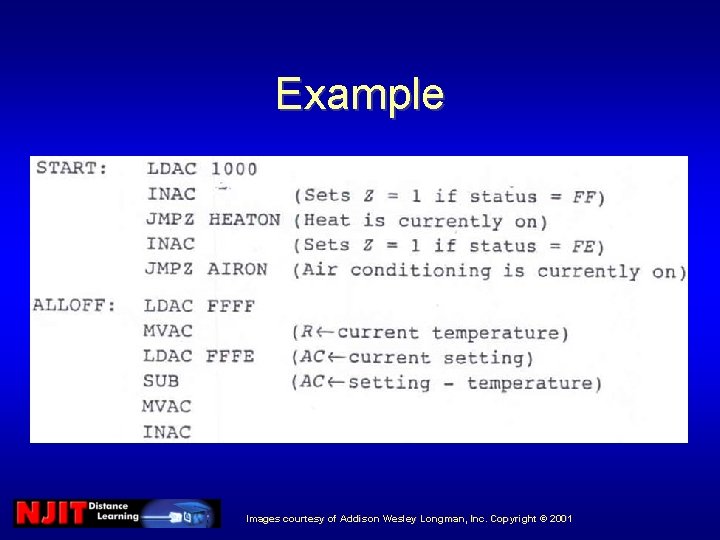

Example Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

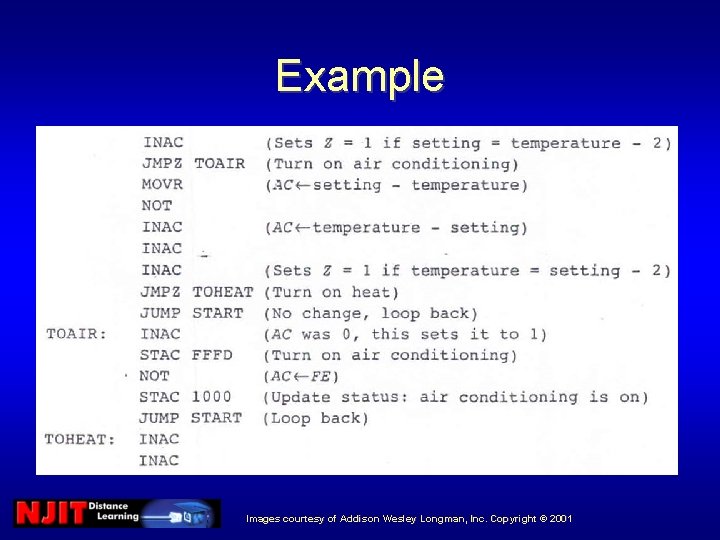

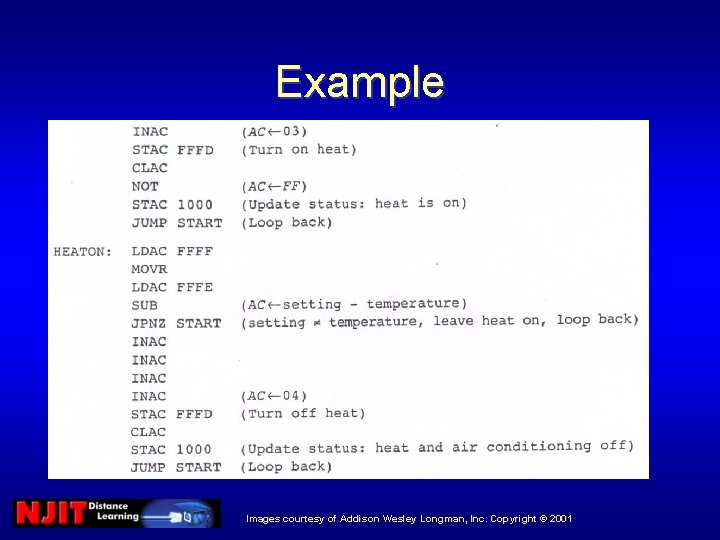

Example Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

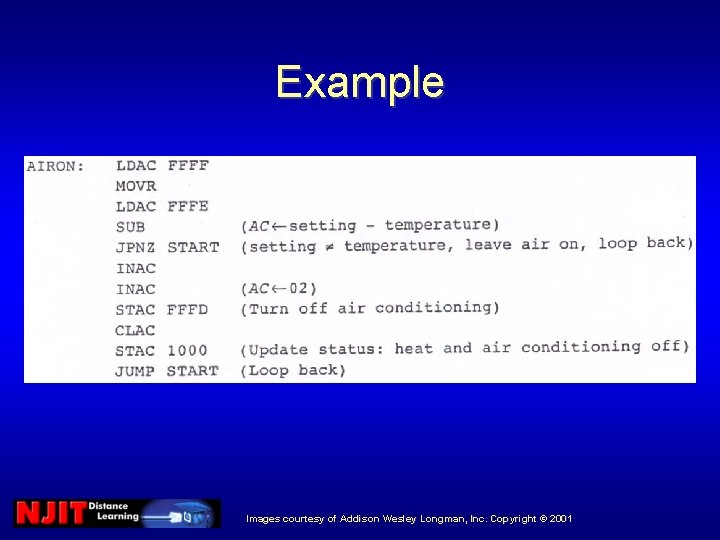

Example Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Example Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

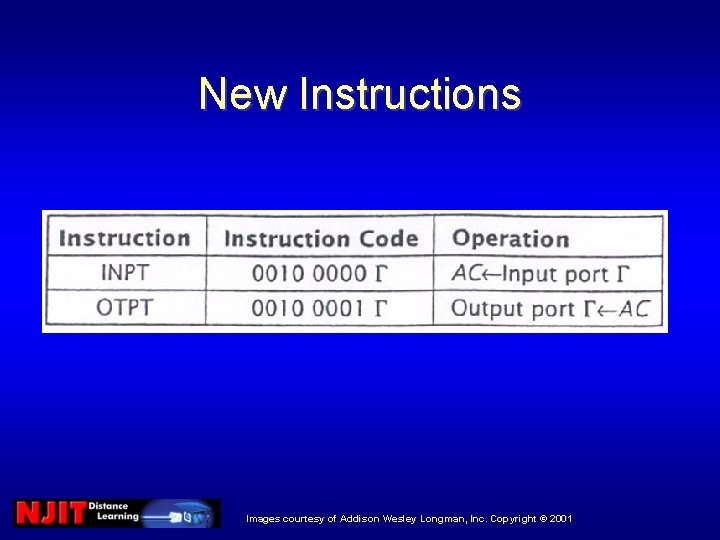

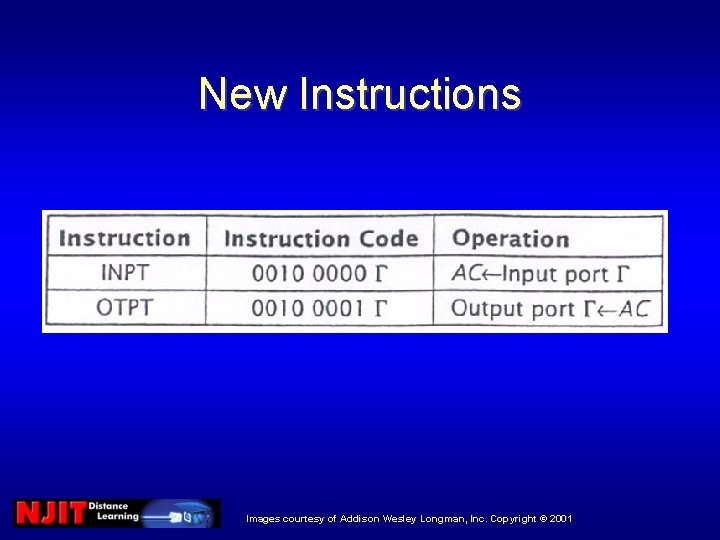

New Instructions Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

New Control Signals • IO differentiates I/O and memory accesses – IO = 1 for I/O access – IO = 0 for memory access Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

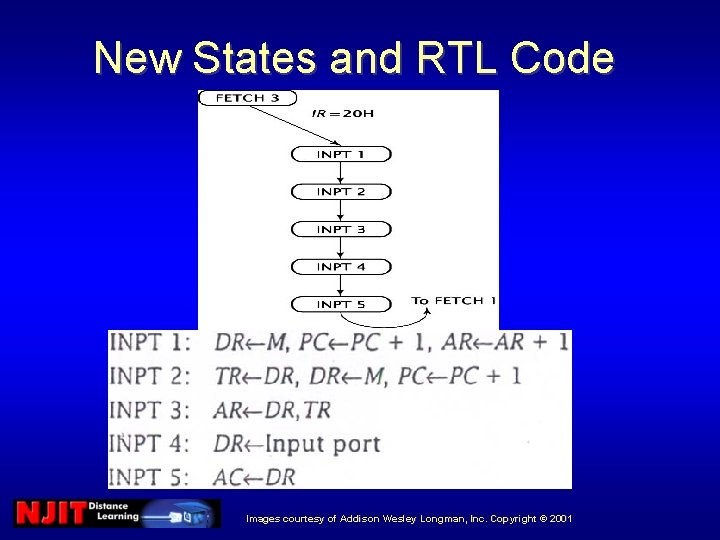

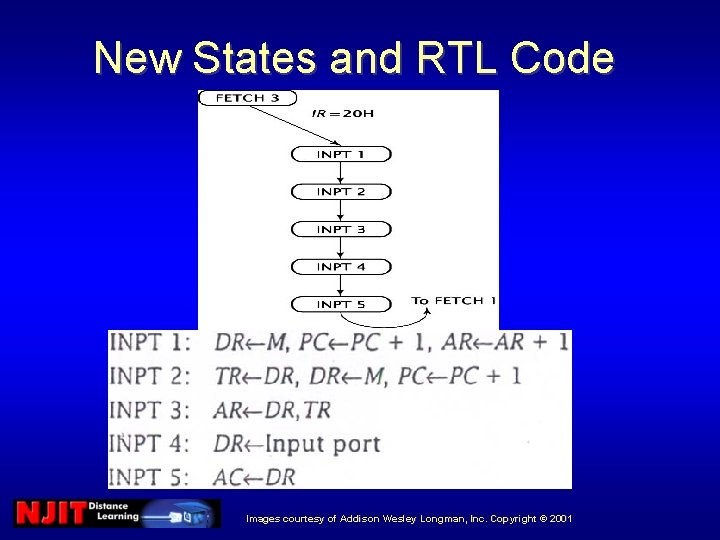

New States and RTL Code Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

CPU Modifications • Modify register section Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

CPU Modifications • Modify register section • Modify ALU Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

CPU Modifications • • • Modify register section Modify ALU Modify control unit (hard-wired) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

CPU Modifications • • Modify register section Modify ALU Modify control unit (hard-wired) Register and ALU sections unchanged Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

CPU Modifications • • • Modify register section Modify ALU Modify control unit (hard-wired) Register and ALU sections unchanged One new micro-operation: DR Input Port Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

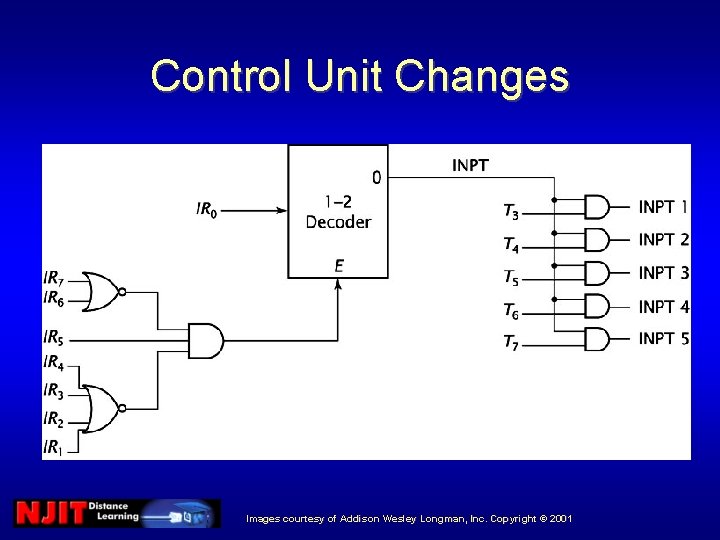

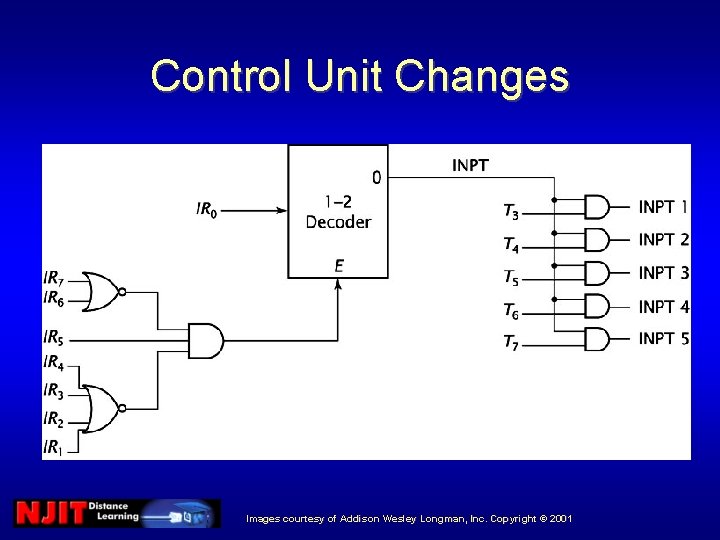

Control Unit Changes Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

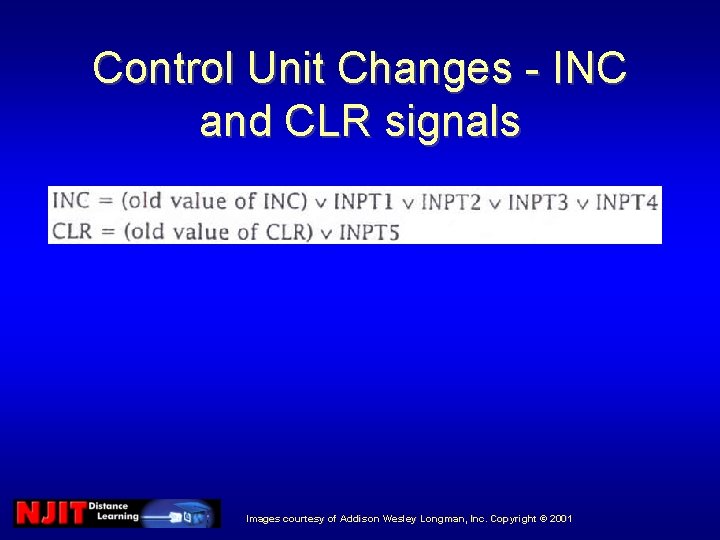

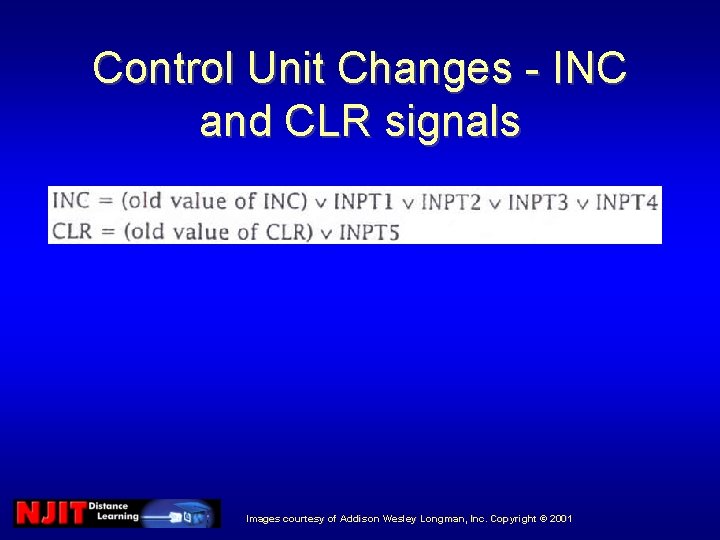

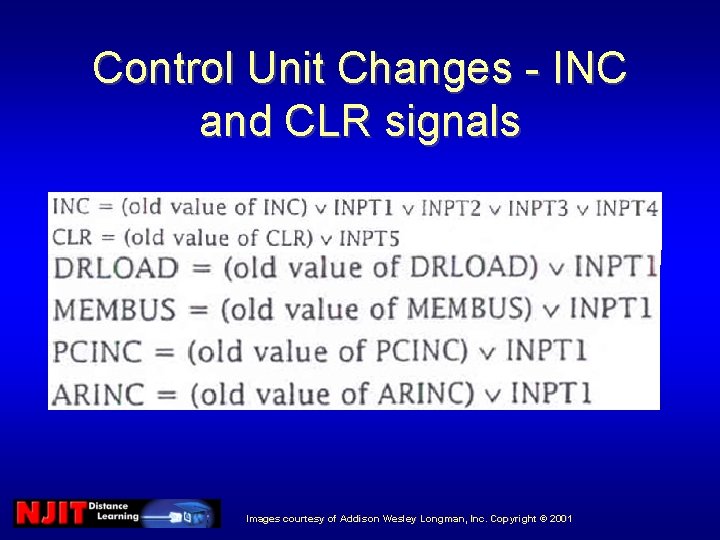

Control Unit Changes - INC and CLR signals Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

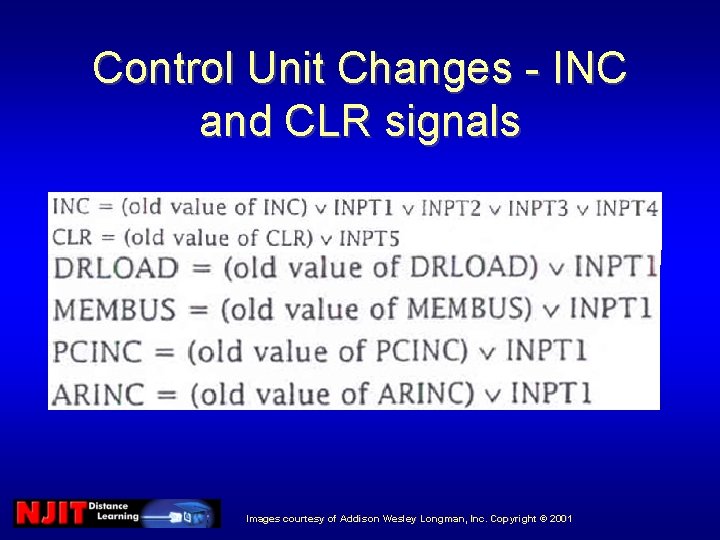

Control Unit Changes - INC and CLR signals Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Control Unit Changes Memory Read Signal • Memory Read = READ ^ IO’ Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

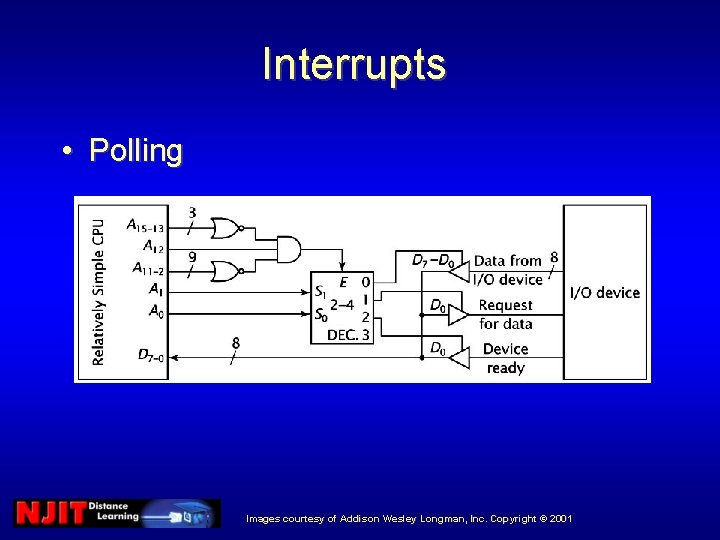

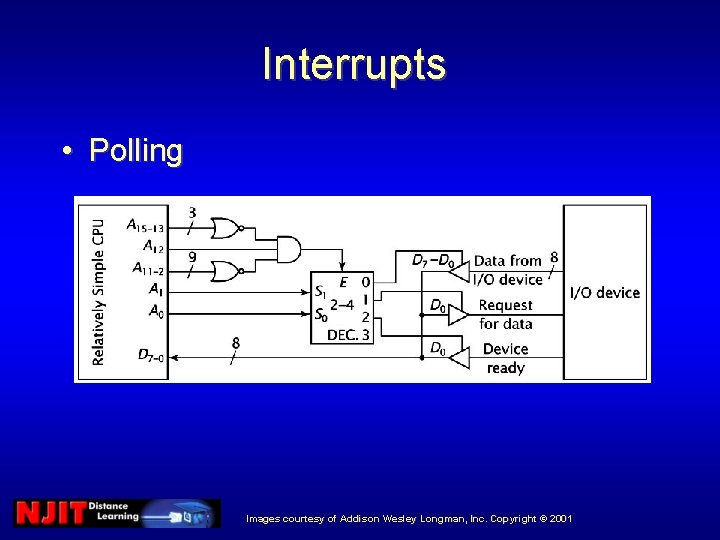

Interrupts • Polling Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

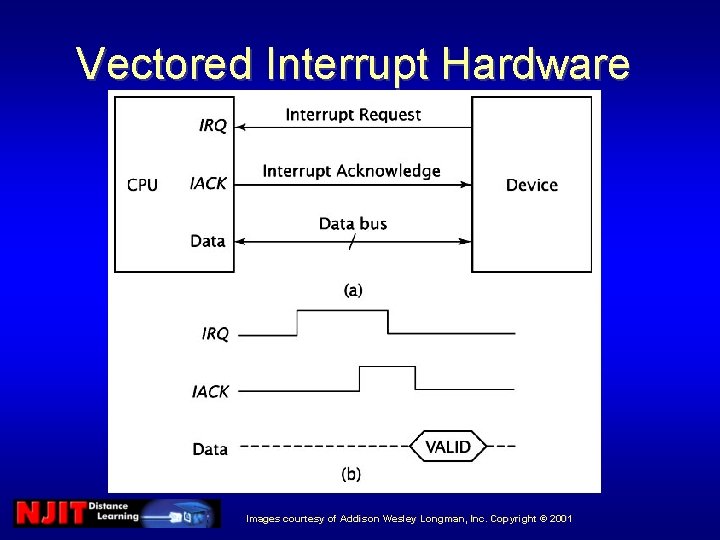

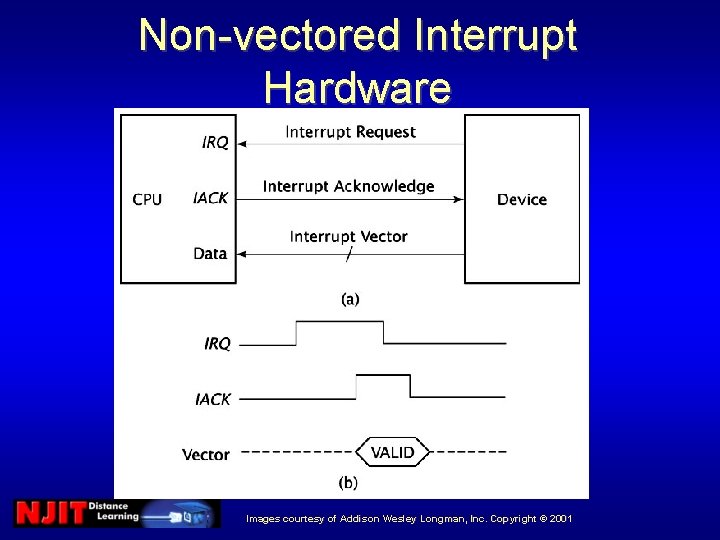

Interrupts • IRQ - Interrupt Request • IACK - Interrupt Acknowledge Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Types of Interrupts • External Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Types of Interrupts • External • Internal Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Types of Interrupts • • • External Internal Software Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Processing Interrupts • Do nothing (until the current instruction has been executed) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Processing Interrupts • Do nothing (until the current instruction has been executed) • Get handler address (vectored) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Processing Interrupts • Do nothing (until the current instruction has been executed) • Get handler address (vectored) • Invoke handler routine Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

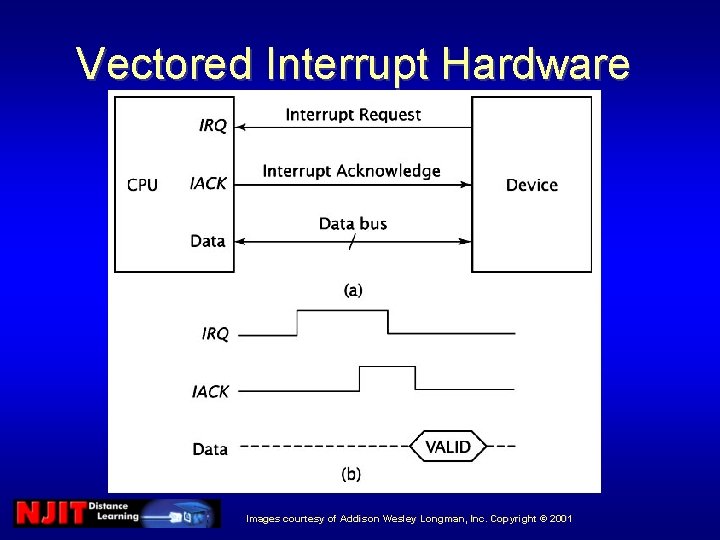

Vectored Interrupt Hardware Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

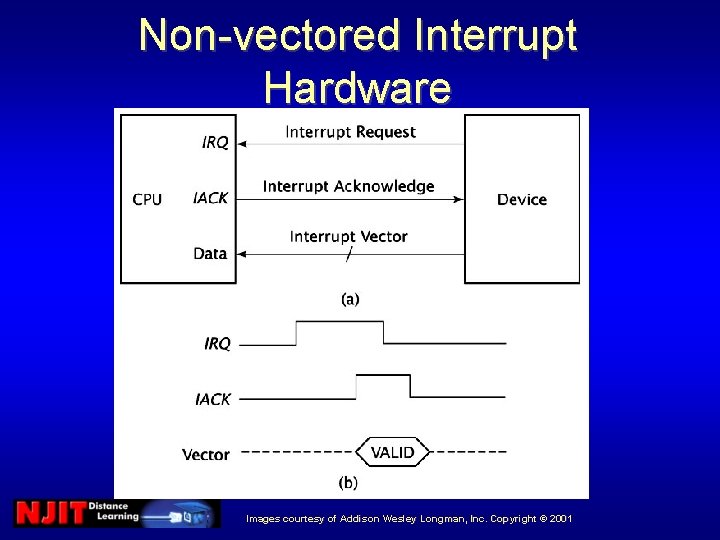

Non-vectored Interrupt Hardware Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

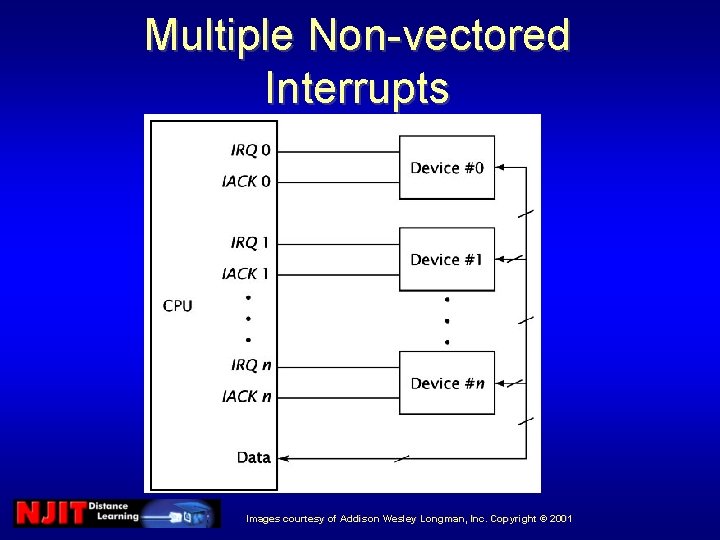

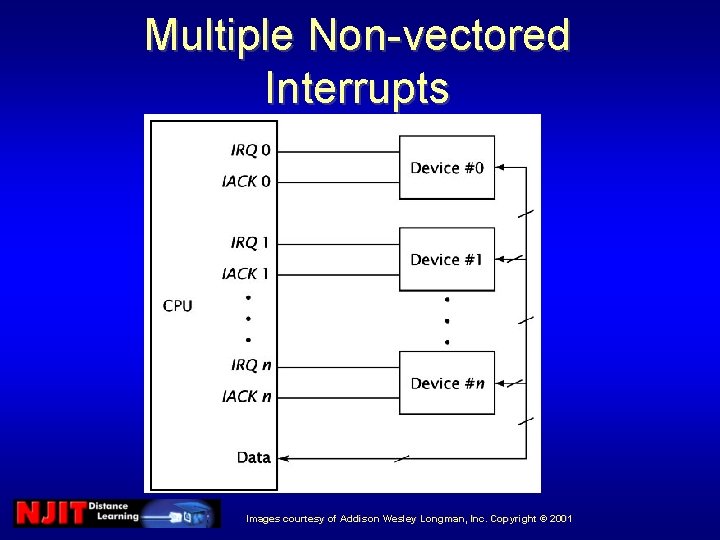

Multiple Non-vectored Interrupts Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

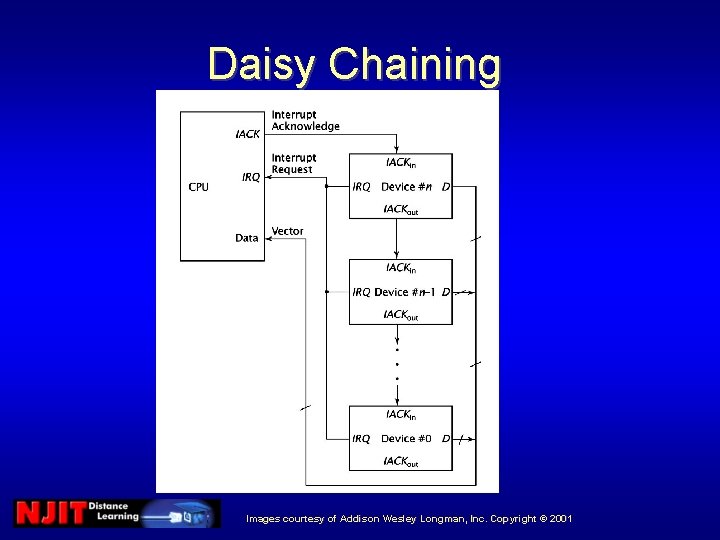

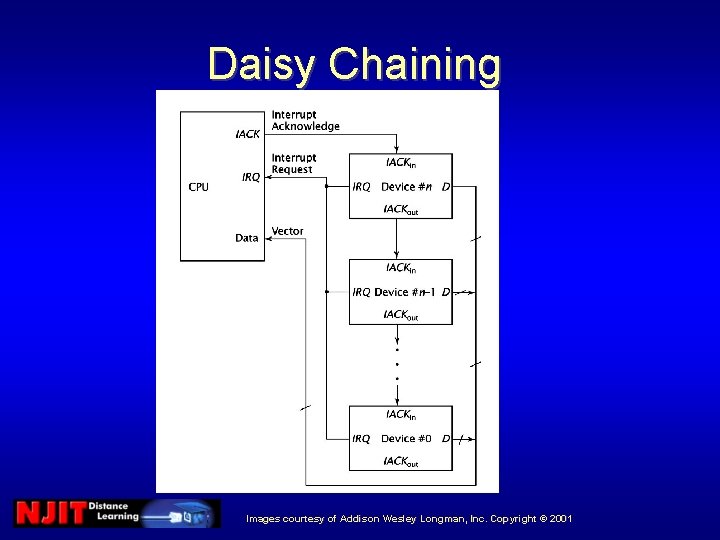

Daisy Chaining Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

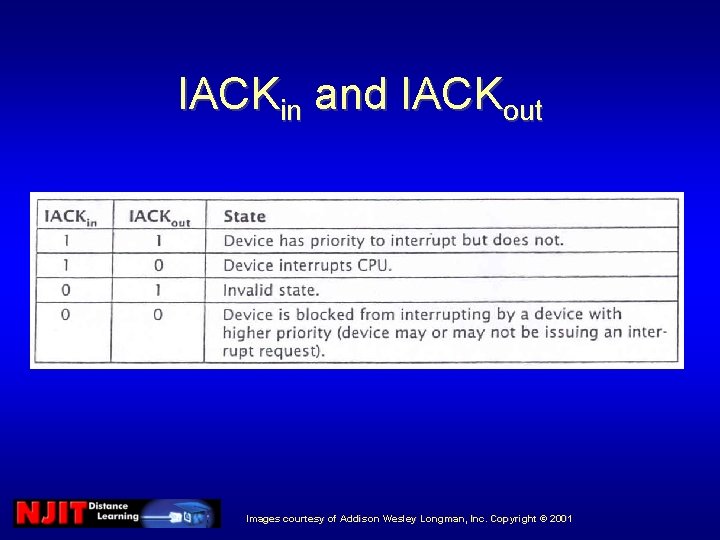

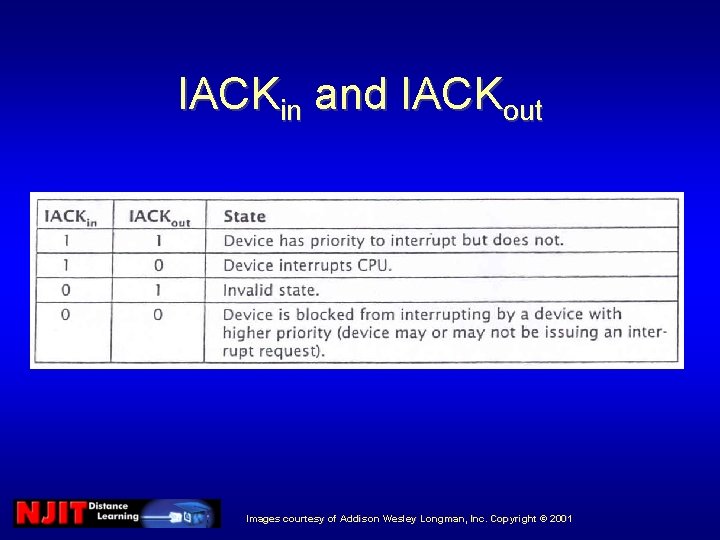

IACKin and IACKout Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

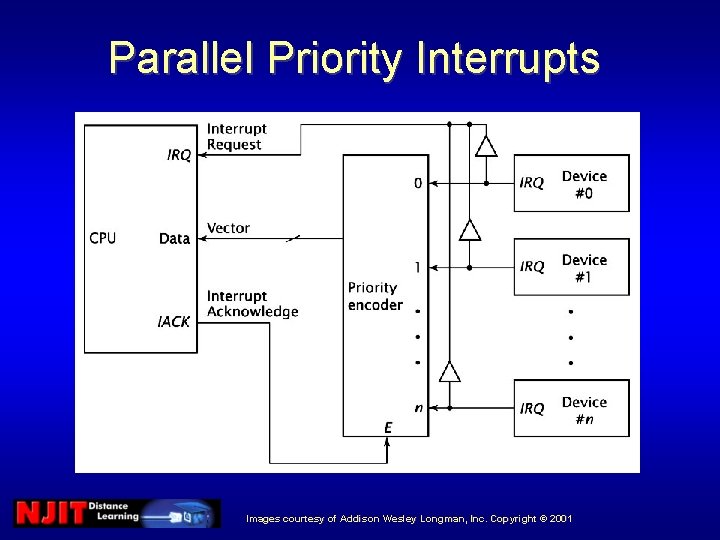

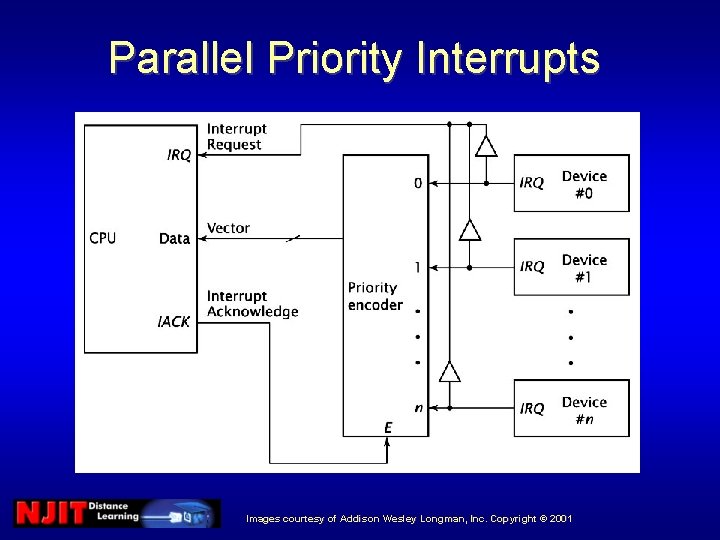

Parallel Priority Interrupts Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

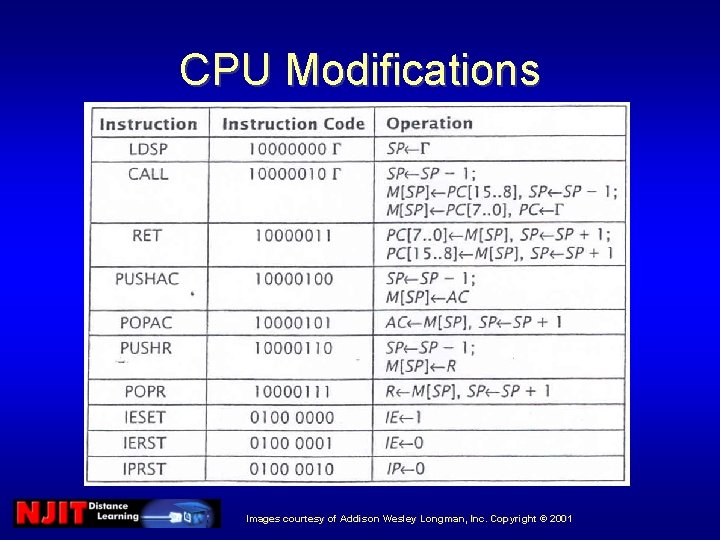

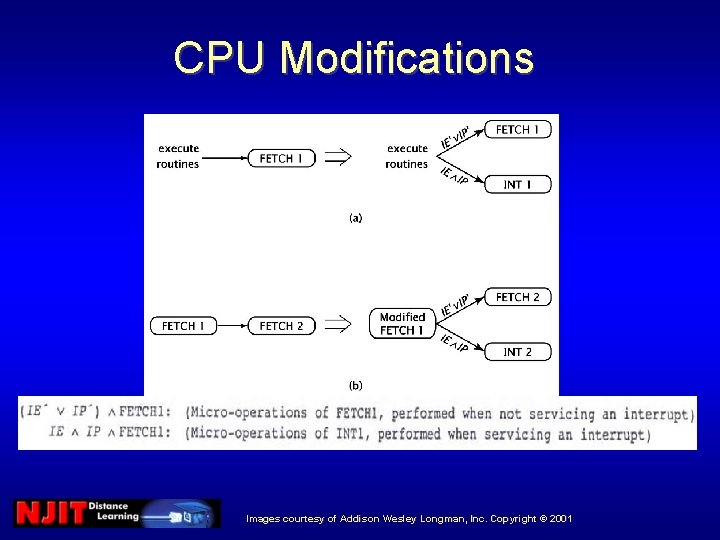

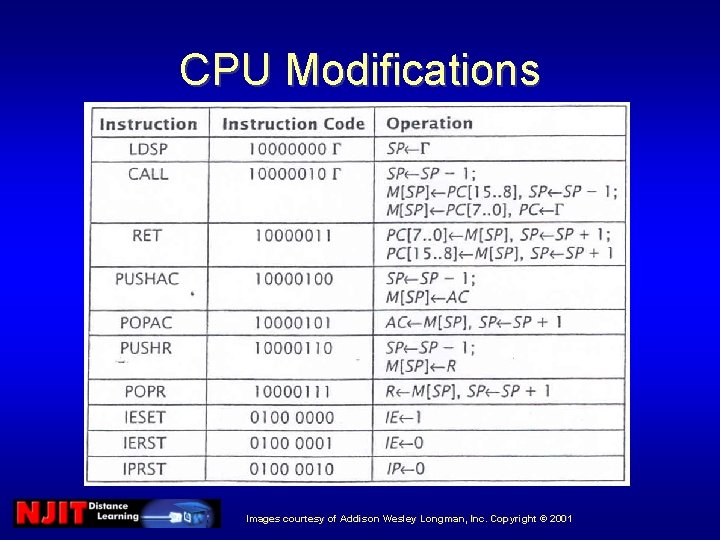

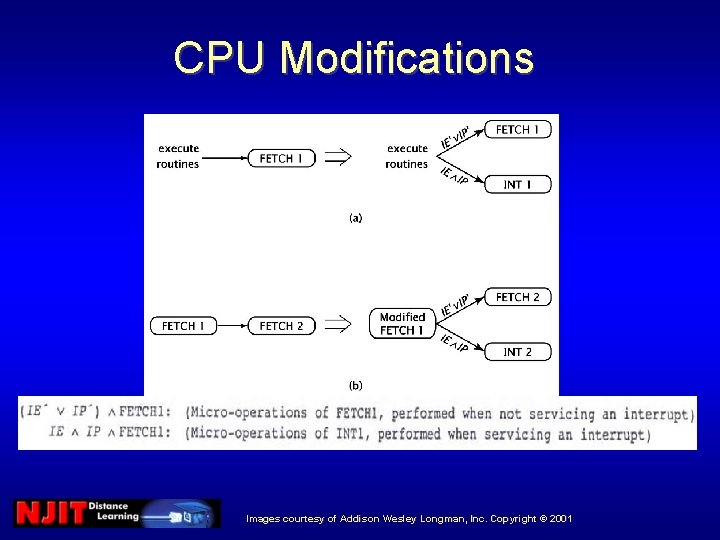

CPU Modifications Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

CPU Modifications Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

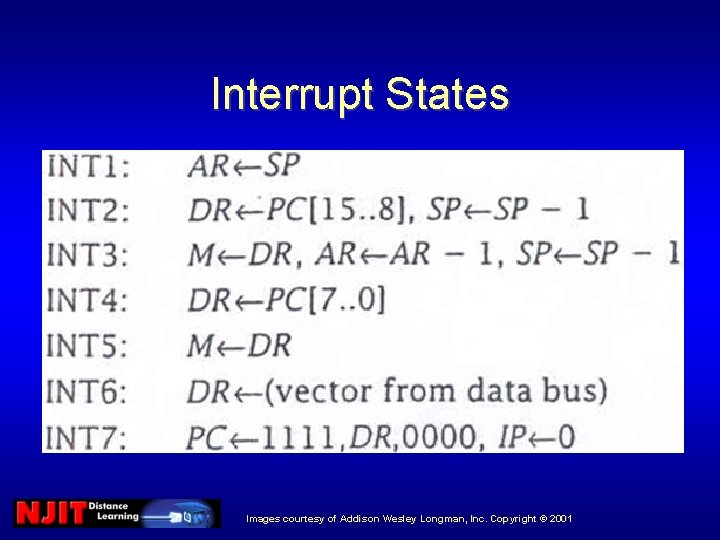

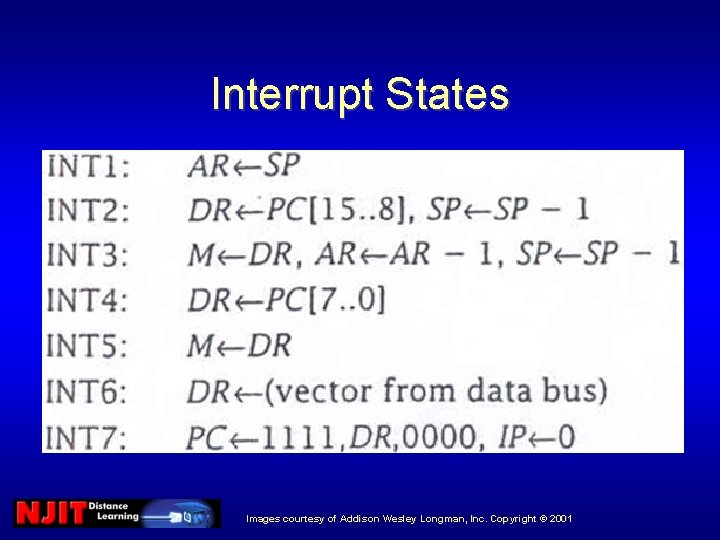

Interrupt States Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

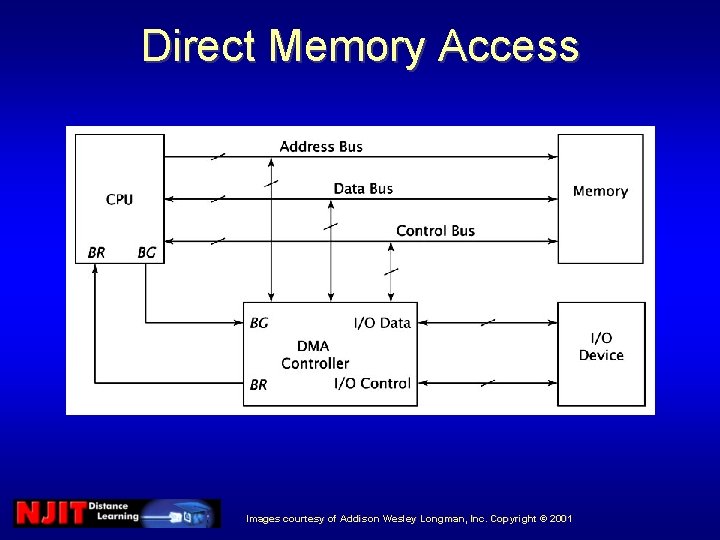

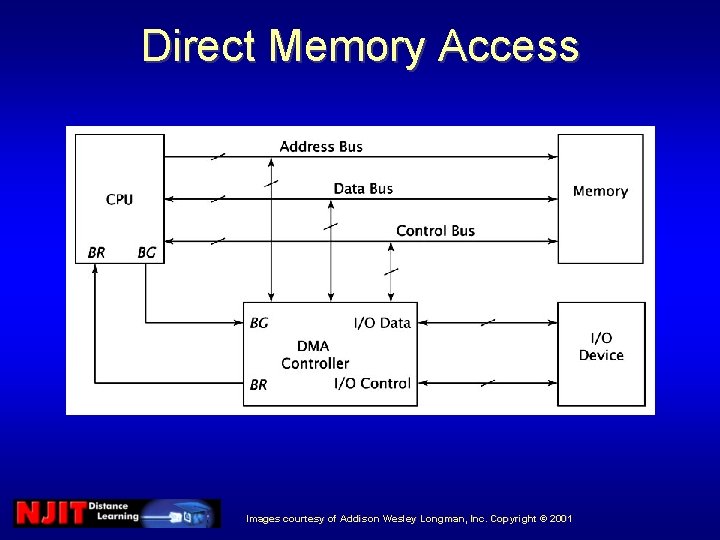

Direct Memory Access Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

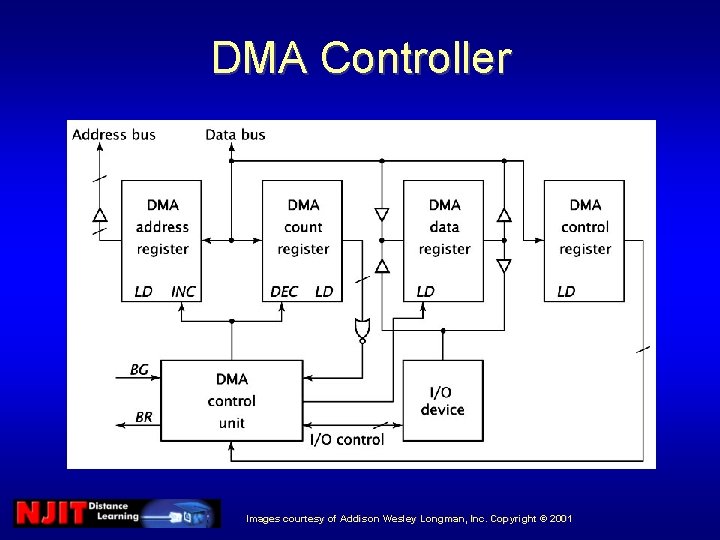

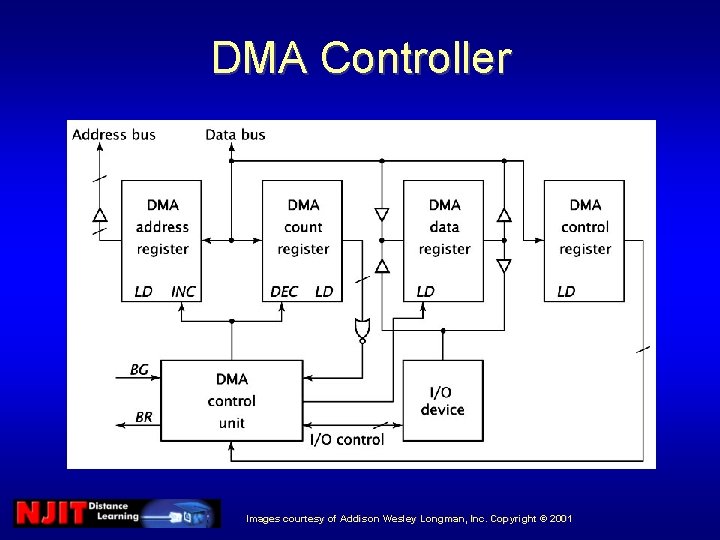

DMA Controller Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

DMA Transfer Modes • Block/Burst Mode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

DMA Transfer Modes • Block/Burst Mode • Cycle Stealing Mode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

DMA Transfer Modes • • • Block/Burst Mode Cycle Stealing Mode Transparent Mode Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

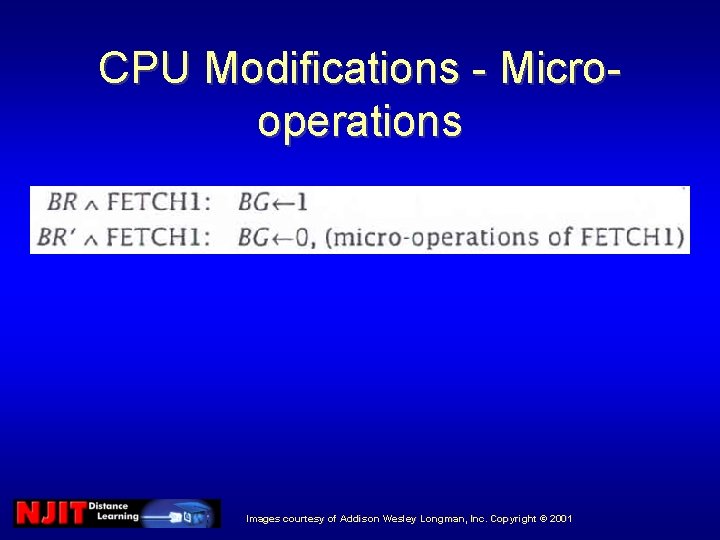

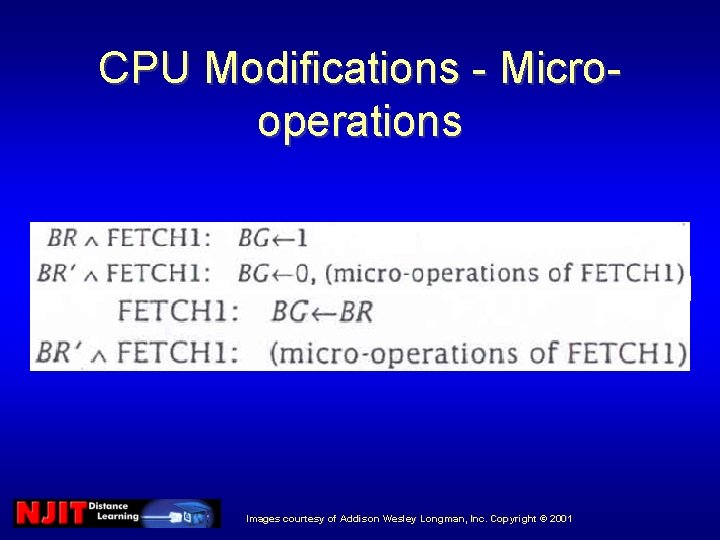

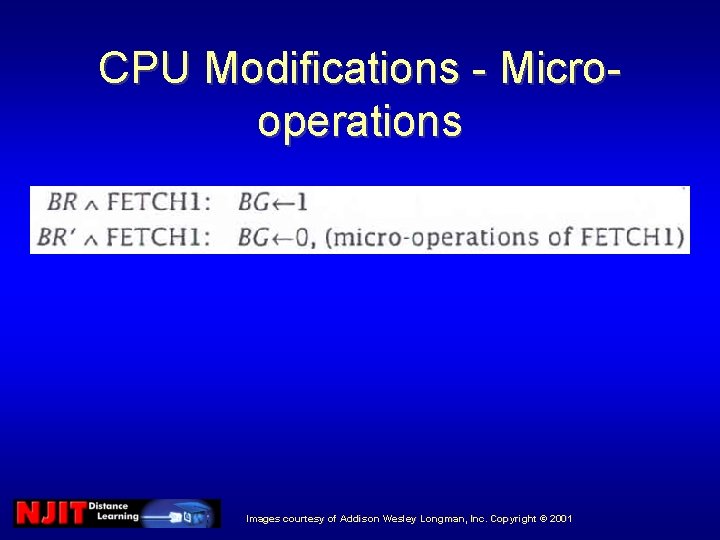

CPU Modifications - Microoperations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

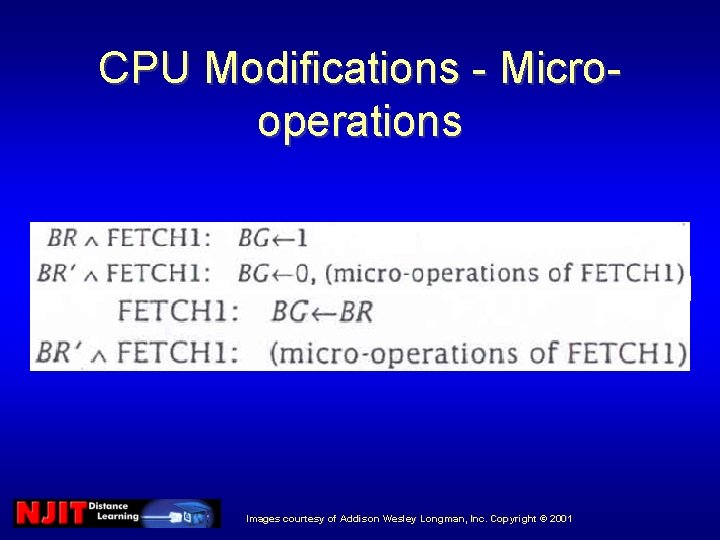

CPU Modifications - Microoperations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

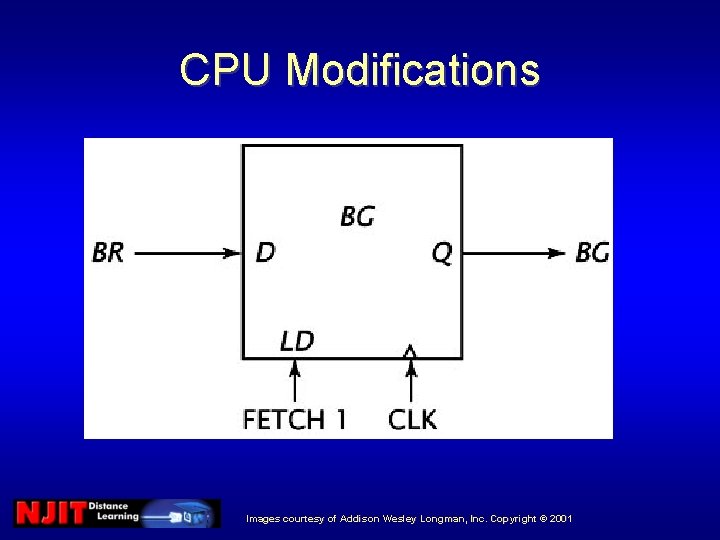

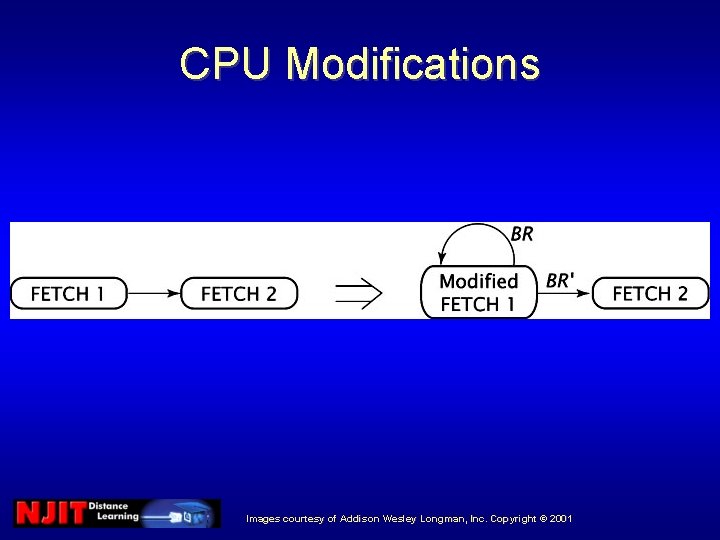

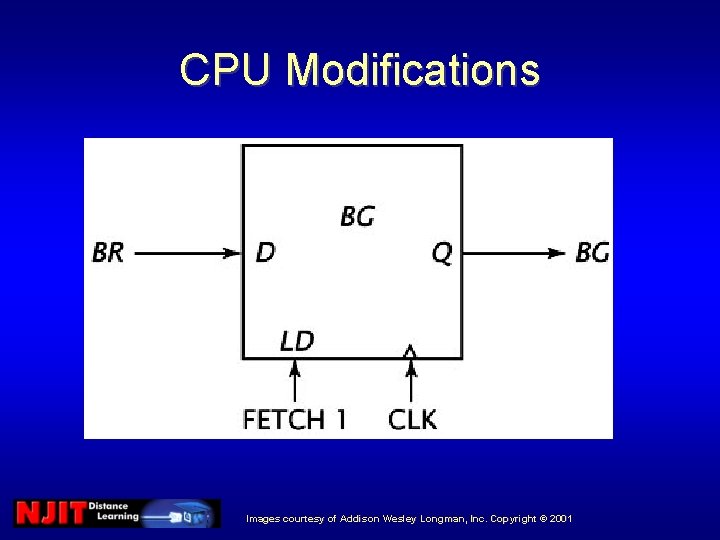

CPU Modifications Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

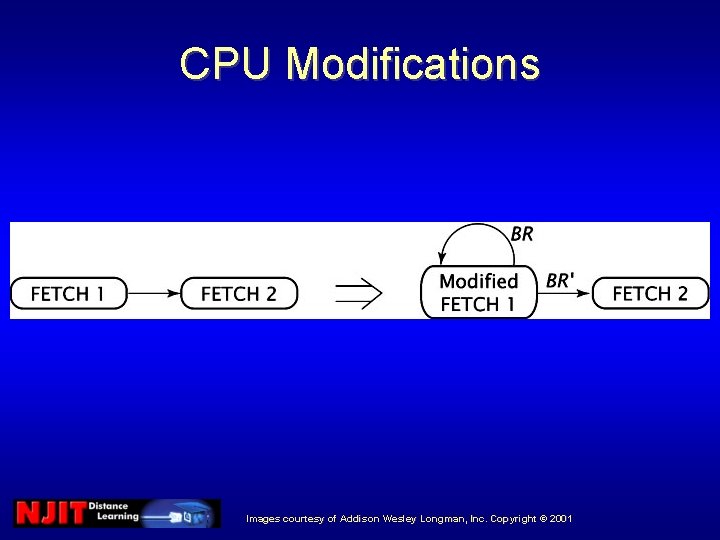

CPU Modifications Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

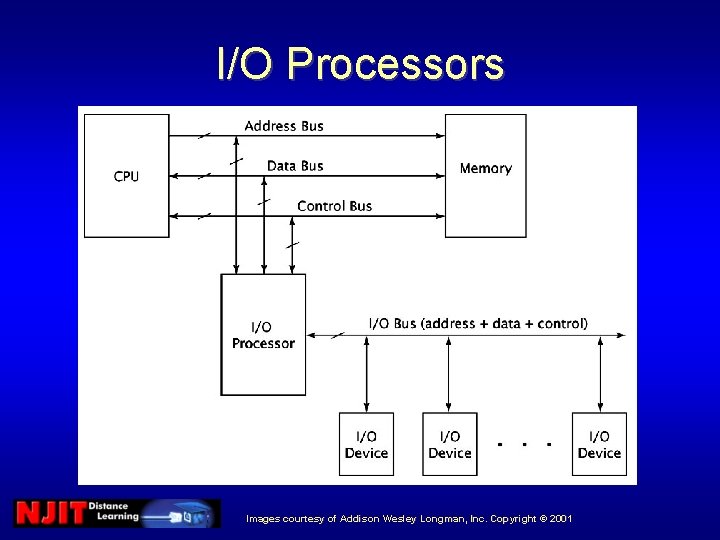

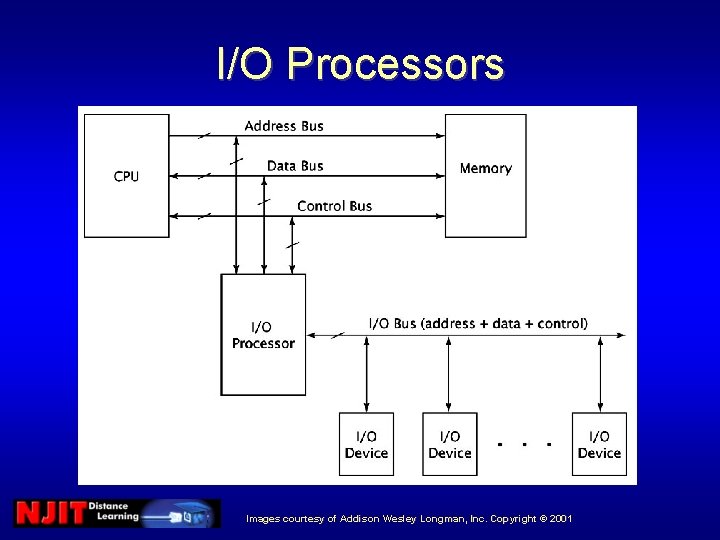

I/O Processors Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

I/O Processors - operations • Block transfer commands Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

I/O Processors - operations • Block transfer commands • ALU operations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

I/O Processors - operations • • • Block transfer commands ALU operations Control commands Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

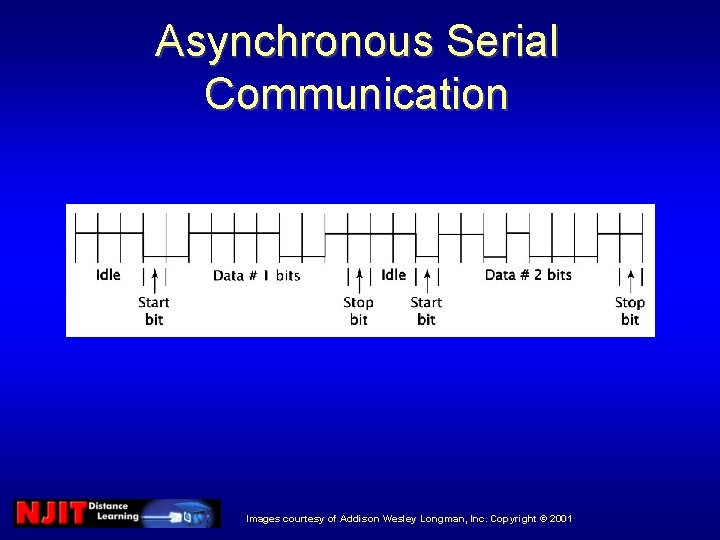

Asynchronous Serial Communication • bps - Bits Per Second (baud rate) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Asynchronous Serial Communication • bps - Bits Per Second (baud rate) • start bit Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Asynchronous Serial Communication • • • bps - Bits Per Second (baud rate) start bit parity bit Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Asynchronous Serial Communication • • bps - Bits Per Second (baud rate) start bit parity bit stop bit(s) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Asynchronous Serial Communication • • • bps - Bits Per Second (baud rate) start bit parity bit stop bit(s) bit time Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

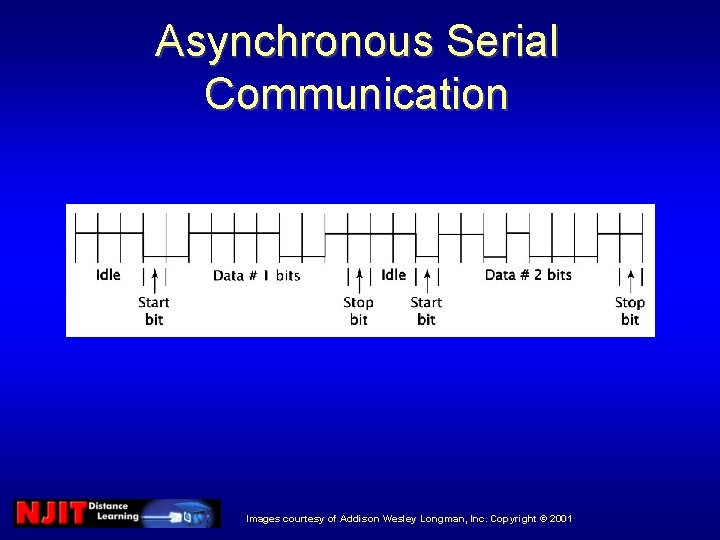

Asynchronous Serial Communication Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

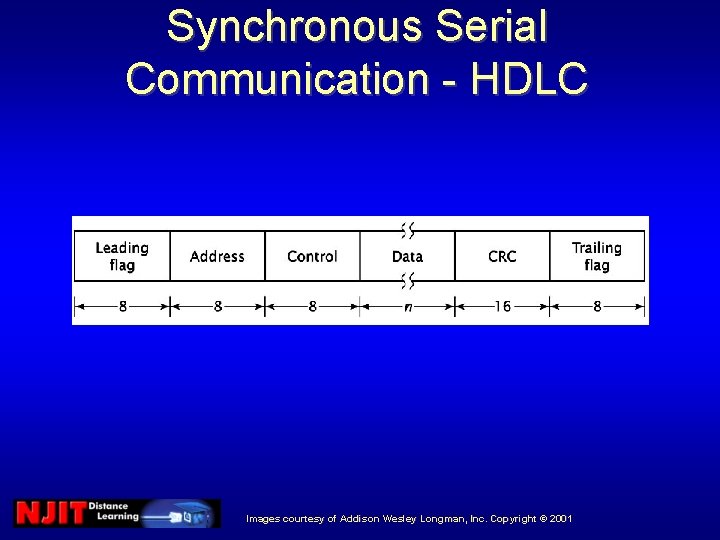

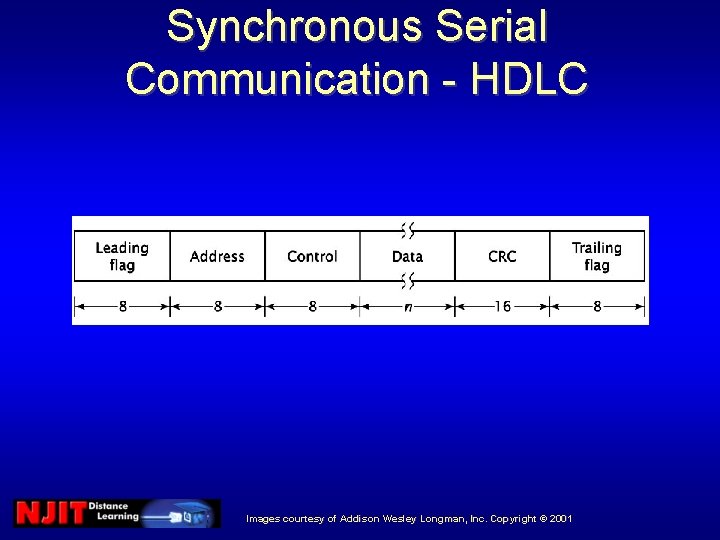

Synchronous Serial Communication - HDLC Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

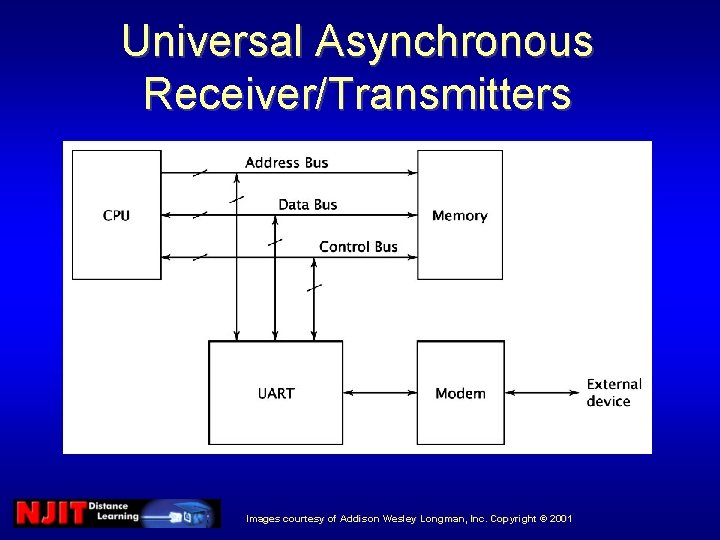

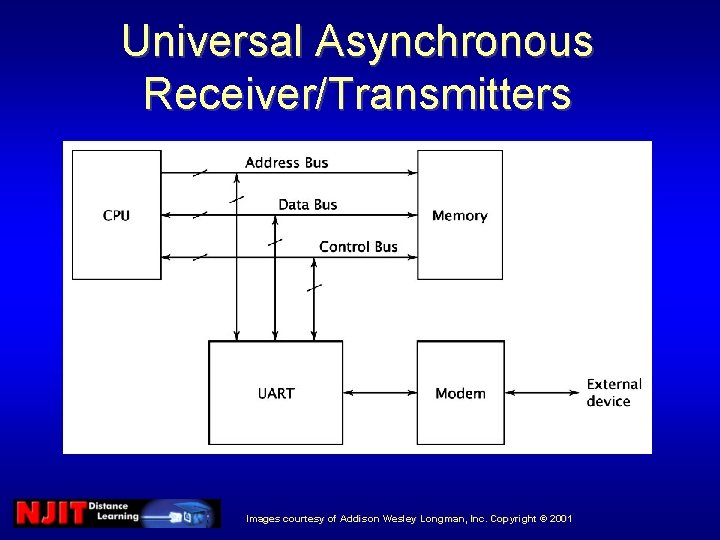

Universal Asynchronous Receiver/Transmitters Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

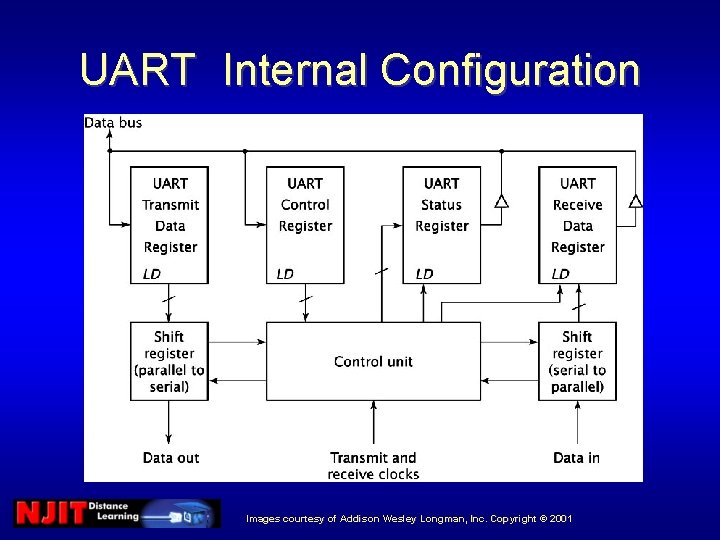

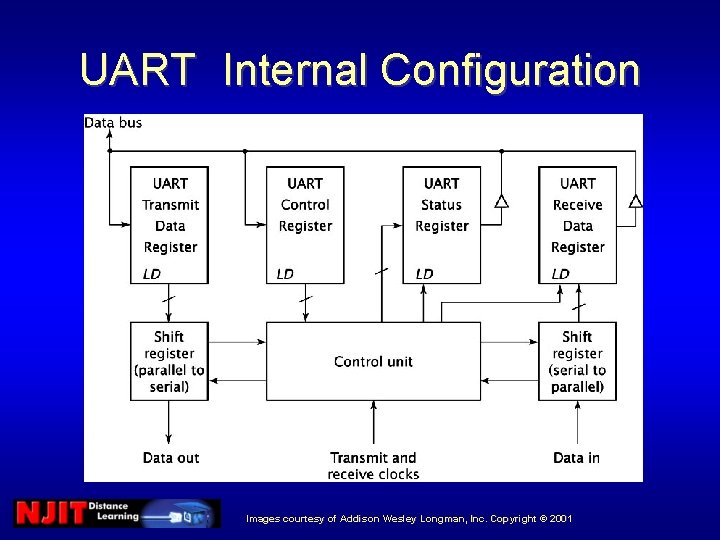

UART Internal Configuration Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

RS 232 C Standard - Signals • • • Request To Send Clear To Send Transmission Data Terminal Ready Data Set Ready Received Data Carrier Detect Ring Indicator Ground Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

RS 232 C Standard Connection • Use RTS, CTS, DTR, and DSR to verify that both devices are active Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

RS 232 C Standard Connection • Use RTS, CTS, DTR, and DSR to verify that both devices are active • Use RI to indicate call status Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

RS 232 C Standard Connection • Use RTS, CTS, DTR, and DSR to verify that both devices are active • Use RI to indicate call status • Use DCD to establish connectivity Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

RS 232 C Standard Connection • Use RTS, CTS, DTR, and DSR to verify that both devices are active • Use RI to indicate call status • Use DCD to establish connectivity • Use TD and RD to transfer data, and RTS and CTS to coordinate transfers Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

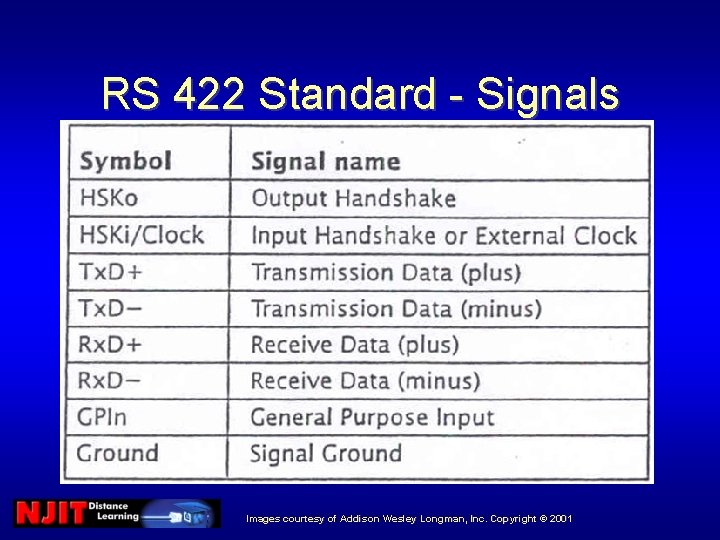

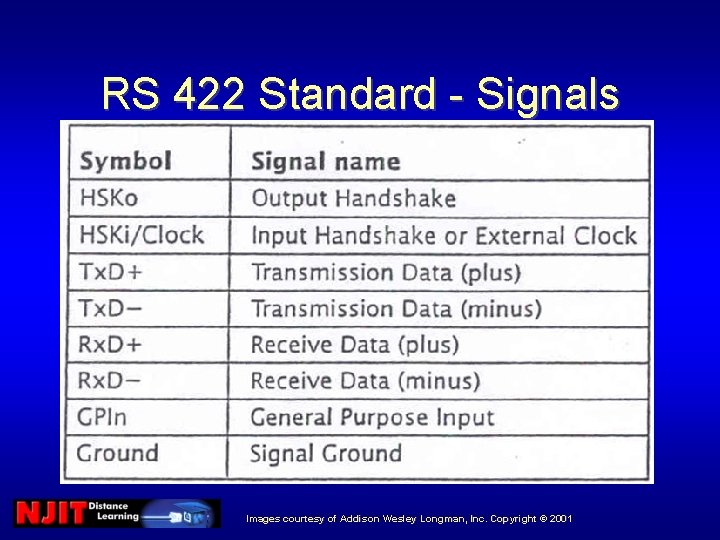

RS 422 Standard - Signals Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

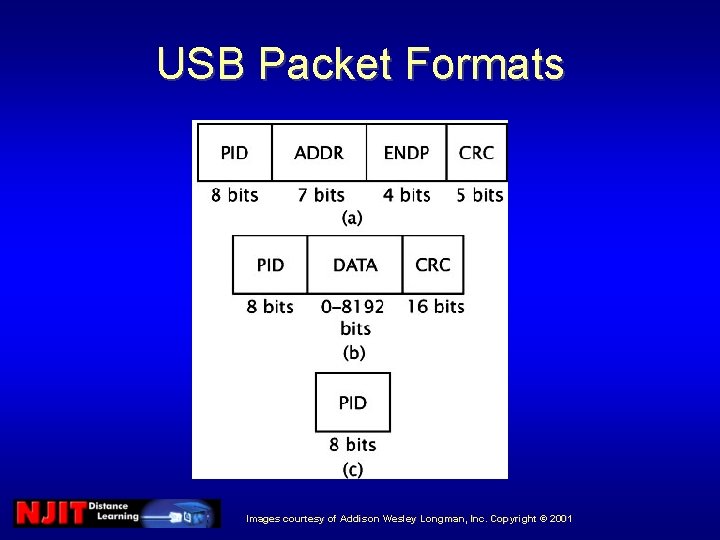

Universal Serial Bus Standard • Connects one port to several devices Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Universal Serial Bus Standard • Connects one port to several devices • Transfers data in packets – Token packets – Data packets – Handshake packets – Special Packets Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

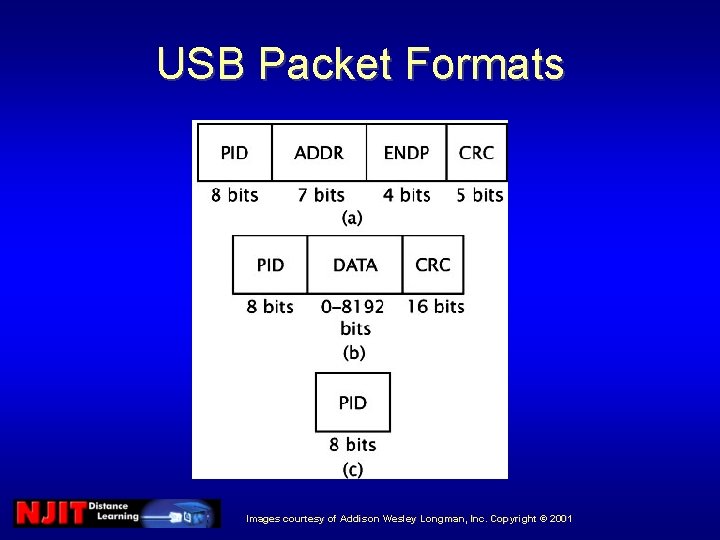

USB Packet Formats Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Summary • • Asynchronous data transfers Programmed I/O Interrupts Direct Memory Access I/O Processors Serial Communication Standards Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001