Chapter 10 FlipFlops and Registers 1 Objectives You

Chapter 10 Flip-Flops and Registers 1

Objectives You should be able to: Explain the internal circuit operation of S-R and gated S-R flip-flops. n Compare the operation of D latches and D flipflops by using timing diagrams. n Describe the difference between pulsetriggered and edge-triggered flip-flops. n 2

Objectives (Continued) Explain theory of operation of masterslave devices. n Connect IC J-K flip-flops as toggle and D flipflops. n Use timing diagrams to illustrate the synchronous and asynchronous operation of J -K flip-flops. n Use VHDL to design flip-flops for CPLD implementation. n 3

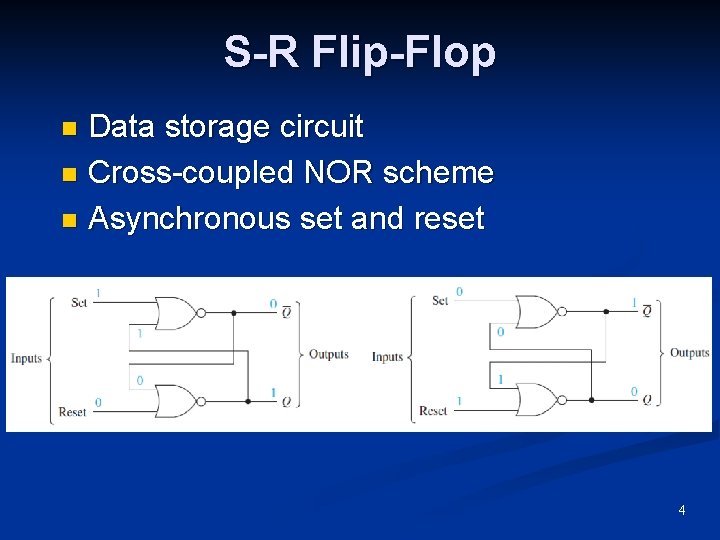

S-R Flip-Flop Data storage circuit n Cross-coupled NOR scheme n Asynchronous set and reset n 4

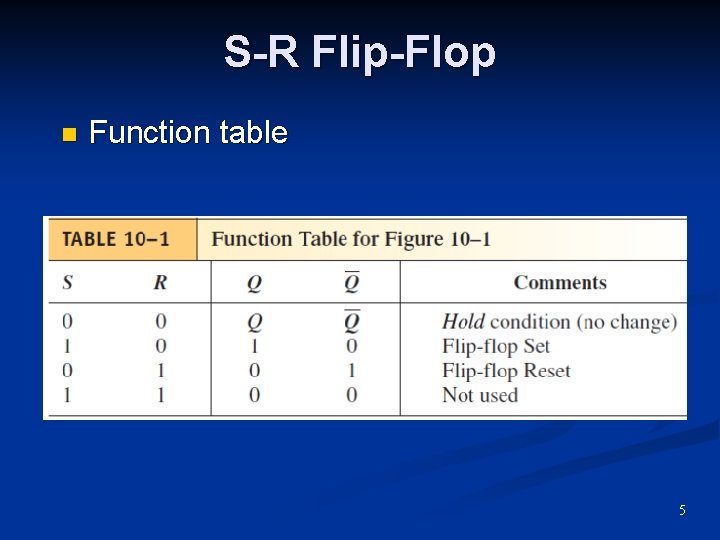

S-R Flip-Flop n Function table 5

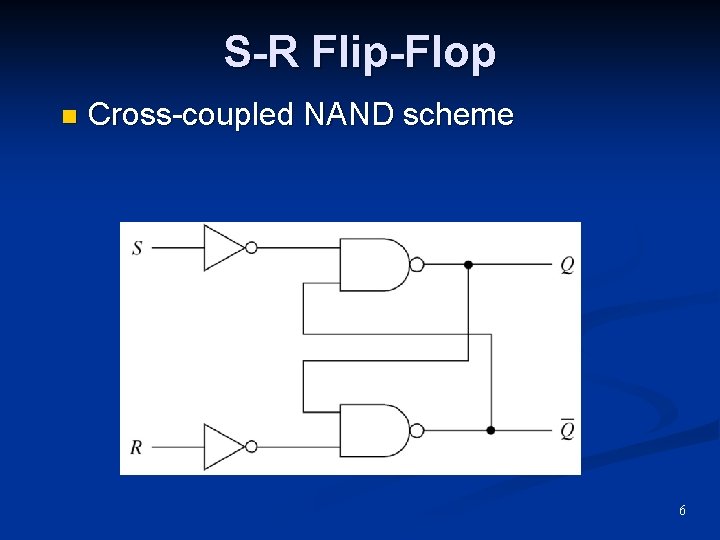

S-R Flip-Flop n Cross-coupled NAND scheme 6

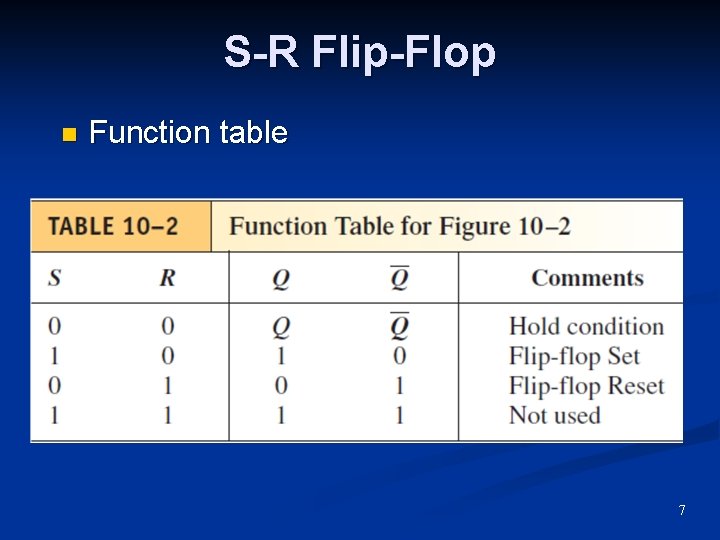

S-R Flip-Flop n Function table 7

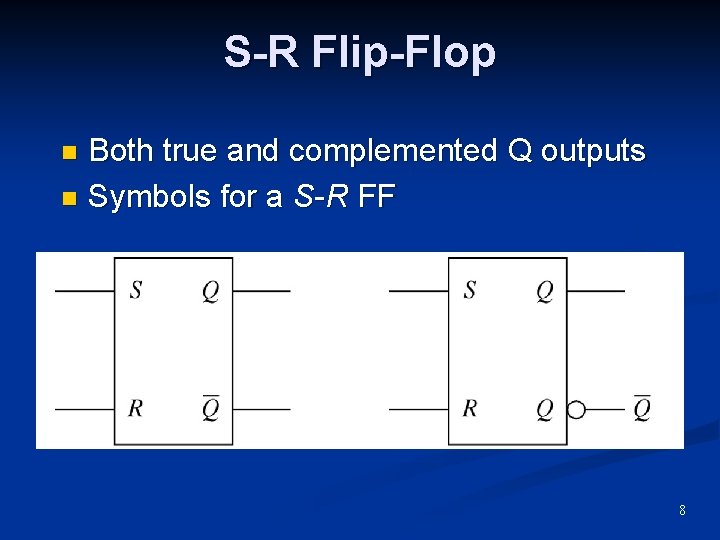

S-R Flip-Flop Both true and complemented Q outputs n Symbols for a S-R FF n 8

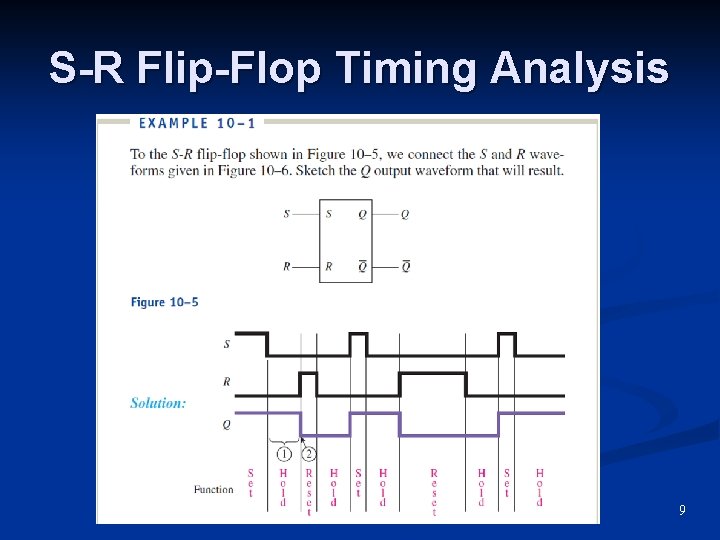

S-R Flip-Flop Timing Analysis 9

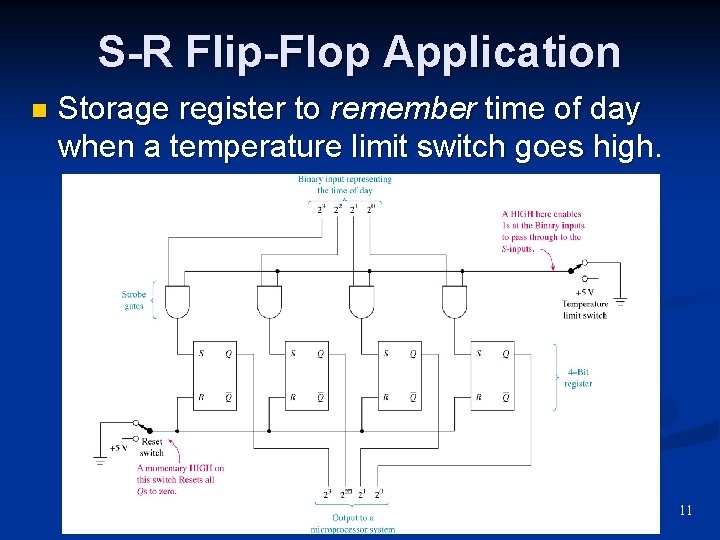

S-R Flip-Flop Application n Storage register to remember time of day when a temperature limit switch goes high. 11

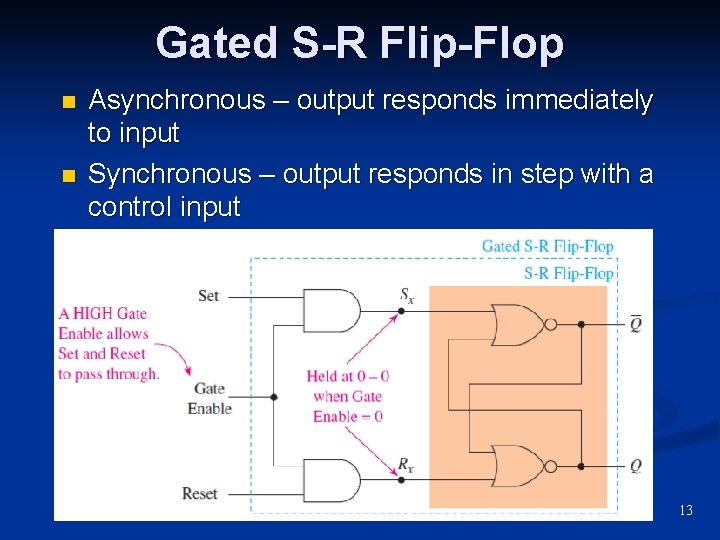

Gated S-R Flip-Flop n n Asynchronous – output responds immediately to input Synchronous – output responds in step with a control input 13

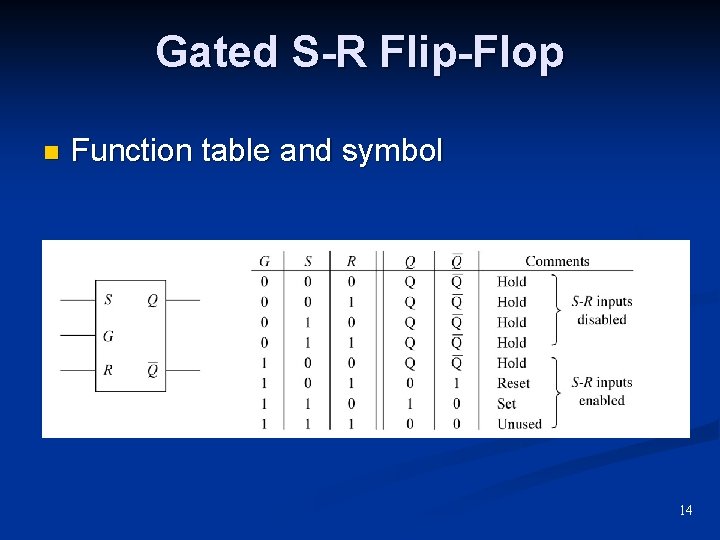

Gated S-R Flip-Flop n Function table and symbol 14

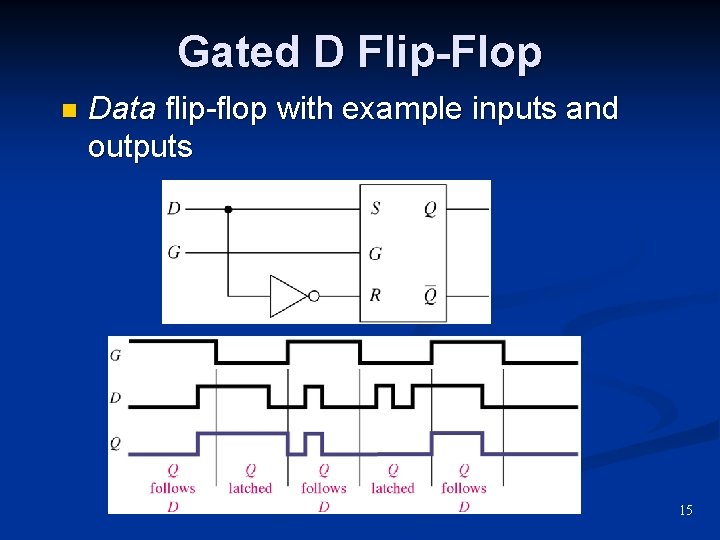

Gated D Flip-Flop n Data flip-flop with example inputs and outputs 15

Discussion Point How will the complement of an output differ from the output? n Explain the difference between synchronous and asynchronous inputs. n 16

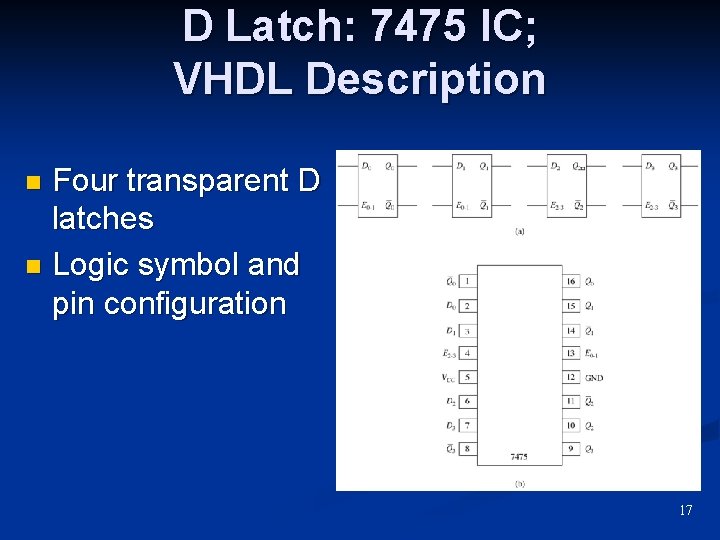

D Latch: 7475 IC; VHDL Description Four transparent D latches n Logic symbol and pin configuration n 17

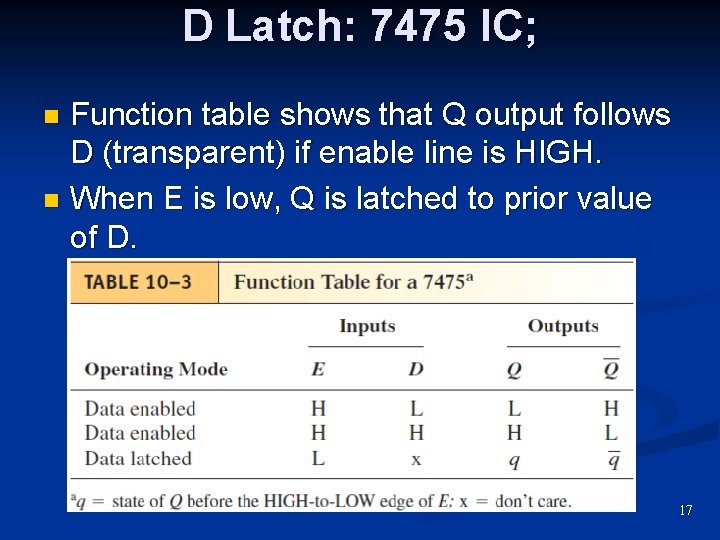

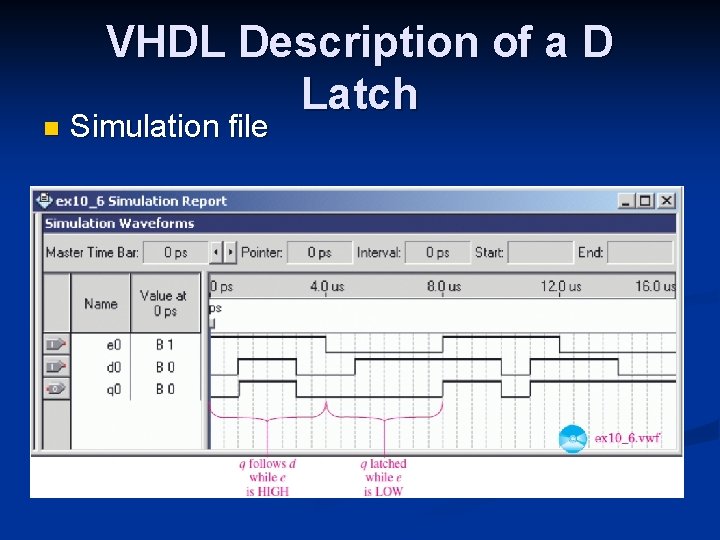

D Latch: 7475 IC; Function table shows that Q output follows D (transparent) if enable line is HIGH. n When E is low, Q is latched to prior value of D. n 17

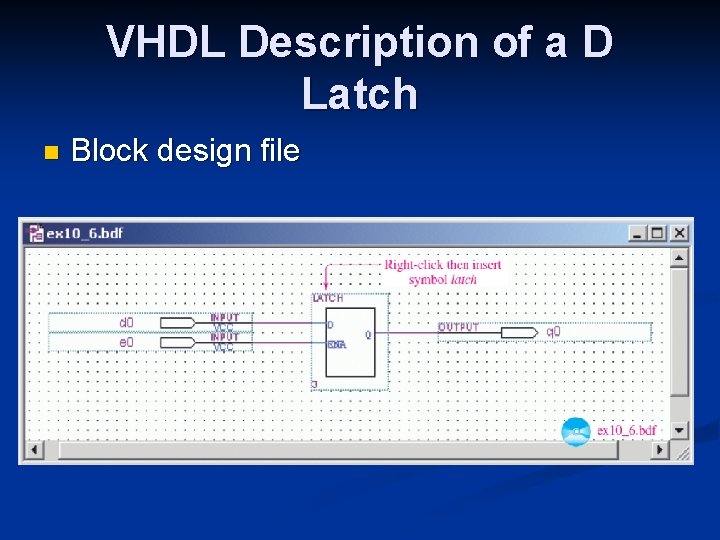

VHDL Description of a D Latch n Block design file

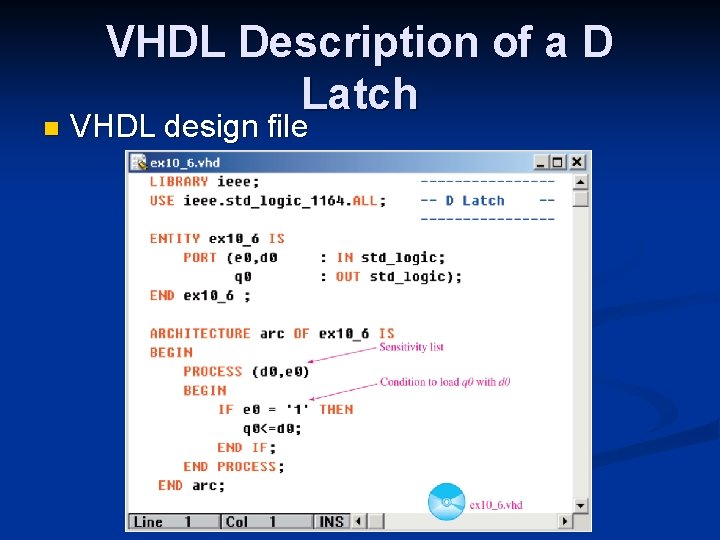

n VHDL Description of a D Latch VHDL design file

n VHDL Description of a D Latch Simulation file

D Flip-Flop: 7474 IC VHDL Description n Positive edge-triggered device Transitions of output occur at the rising edge of input trigger pulse n Clock signal usually used as trigger pulse instead of an enable line n 19

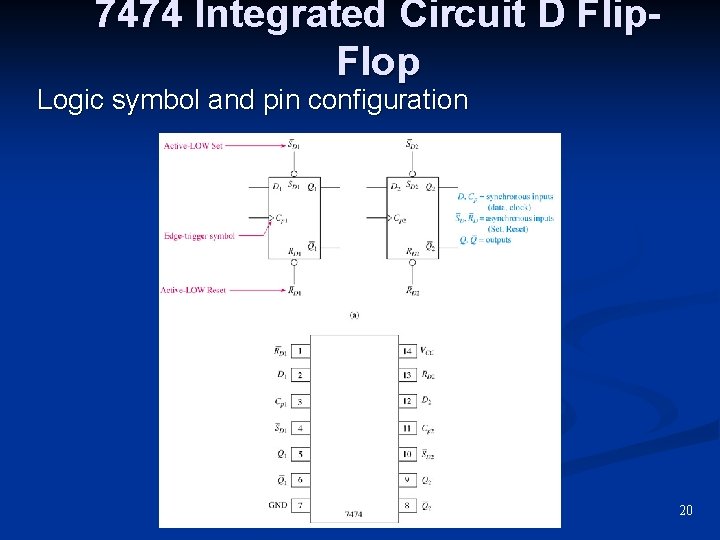

7474 Integrated Circuit D Flip. Flop Logic symbol and pin configuration 20

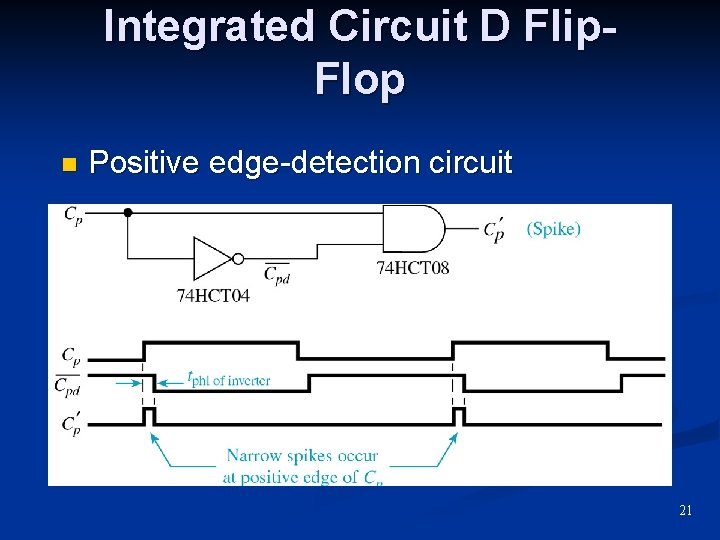

Integrated Circuit D Flip. Flop n Positive edge-detection circuit 21

Integrated Circuit D Flip-Flop n Synchronous inputs D (Data) n Cp (Clock) n n Asynchronous inputs SD (Set) n RD (Reset) n n Setup Time n D must be stable before transition of Cp 22

Integrated Circuit D Flip-Flop 22

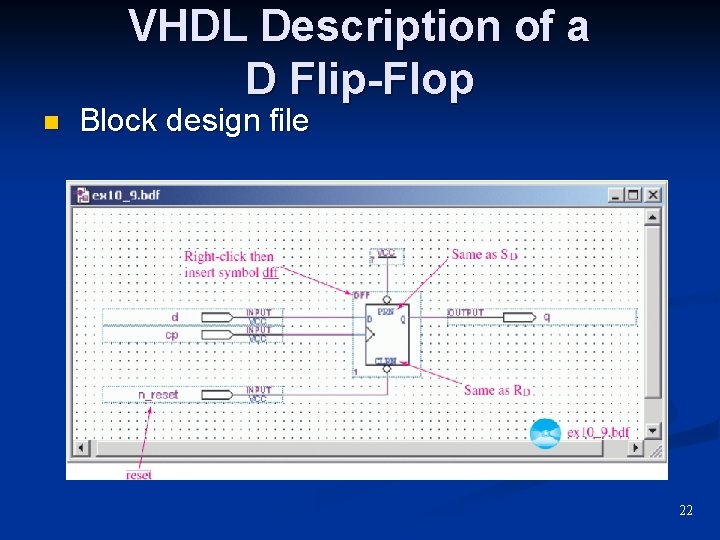

VHDL Description of a D Flip-Flop n Block design file 22

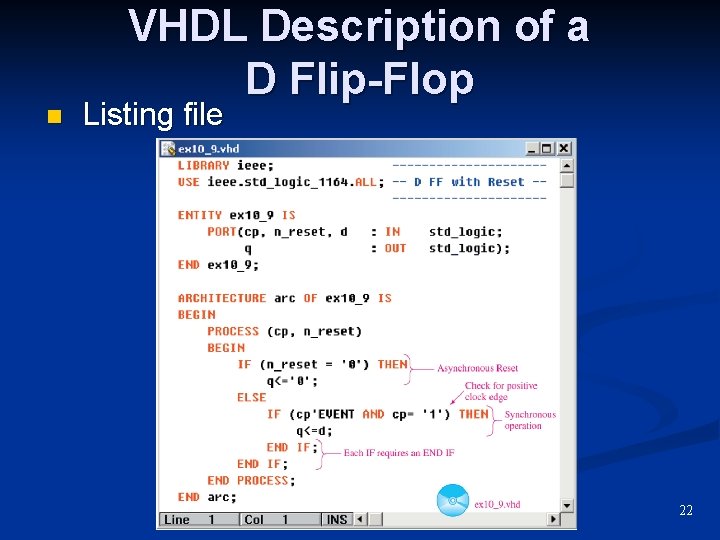

n VHDL Description of a D Flip-Flop Listing file 22

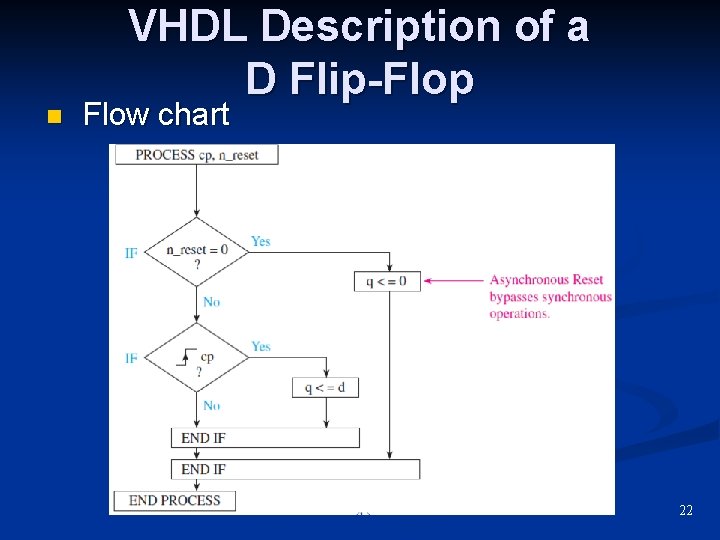

n VHDL Description of a D Flip-Flop Flow chart 22

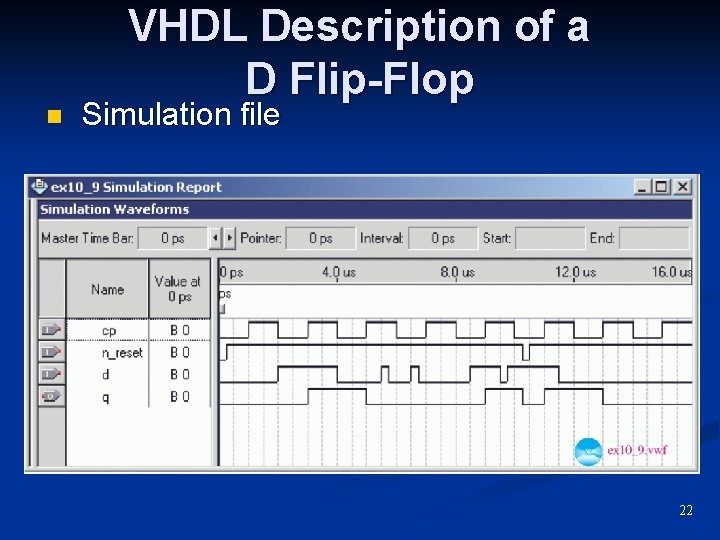

n VHDL Description of a D Flip-Flop Simulation file 22

Master-Slave J-K Flip-Flop n Toggle mode n n Switches to opposite state at active clock edge Master-slave Master receives data while input trigger is HIGH n Slave receives data from master and outputs it when clock goes LOW n 24

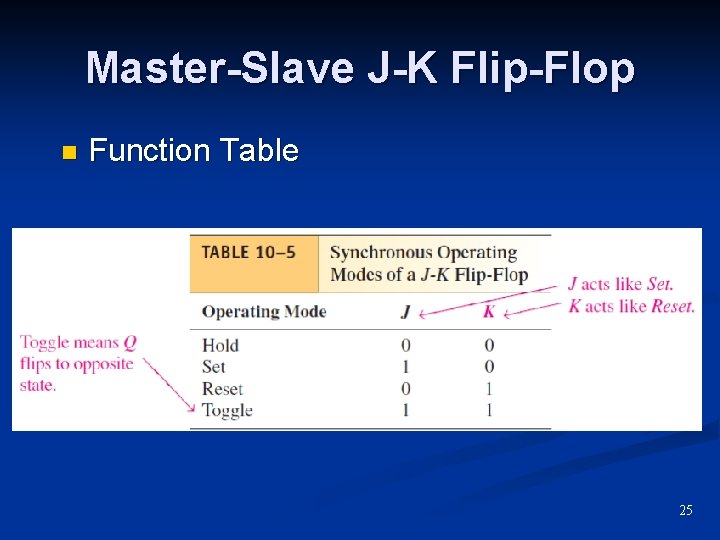

Master-Slave J-K Flip-Flop n Function Table 25

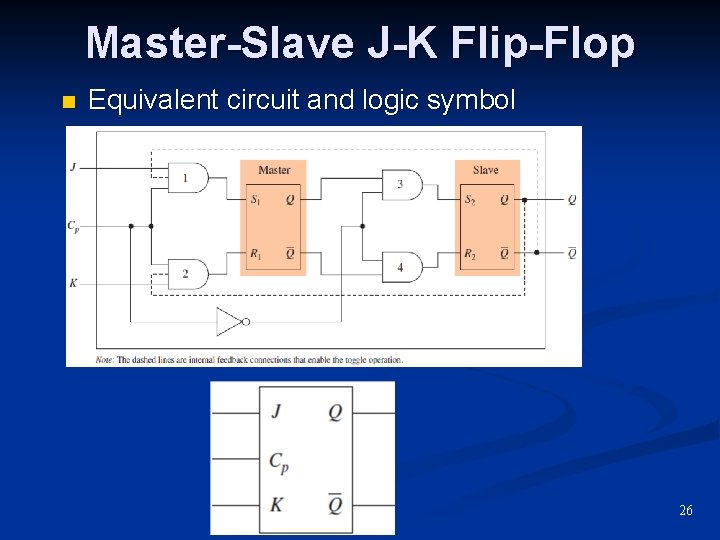

Master-Slave J-K Flip-Flop n Equivalent circuit and logic symbol 26

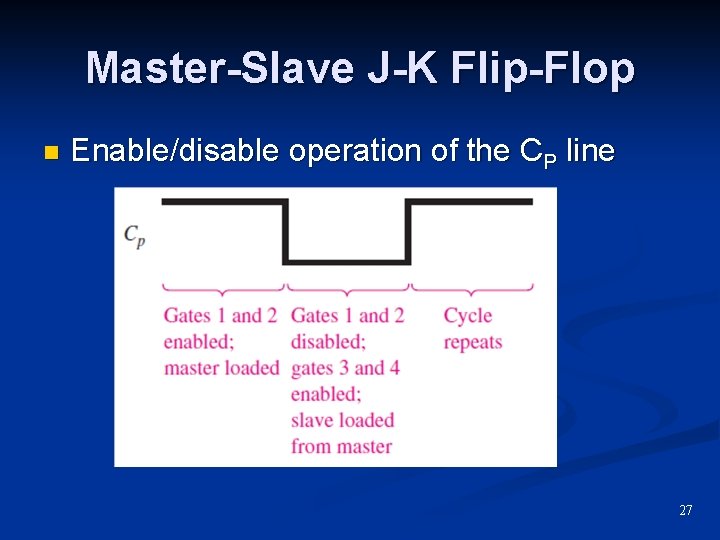

Master-Slave J-K Flip-Flop n Enable/disable operation of the CP line 27

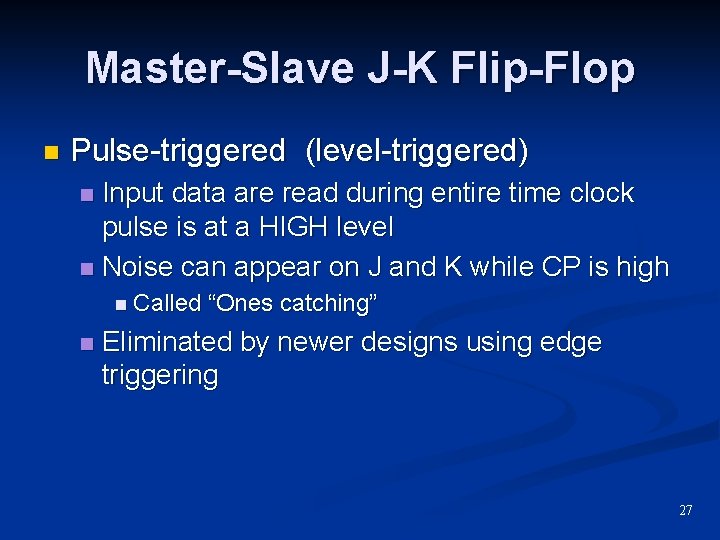

Master-Slave J-K Flip-Flop n Pulse-triggered (level-triggered) Input data are read during entire time clock pulse is at a HIGH level n Noise can appear on J and K while CP is high n n Called n “Ones catching” Eliminated by newer designs using edge triggering 27

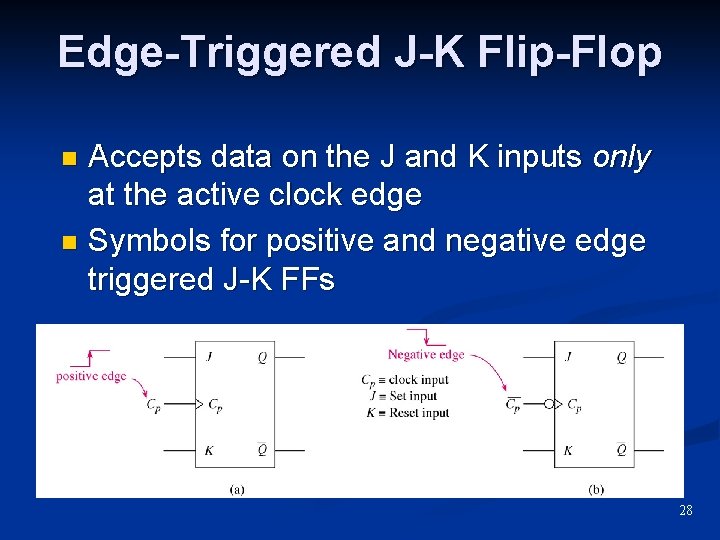

Edge-Triggered J-K Flip-Flop Accepts data on the J and K inputs only at the active clock edge n Symbols for positive and negative edge triggered J-K FFs n 28

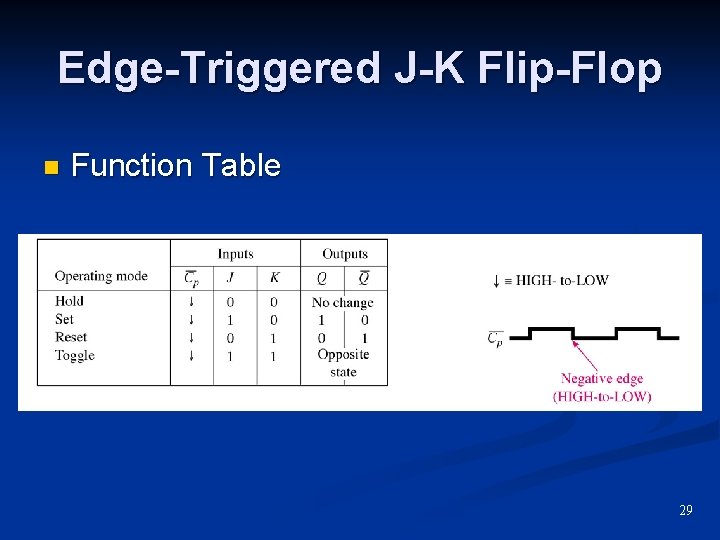

Edge-Triggered J-K Flip-Flop n Function Table 29

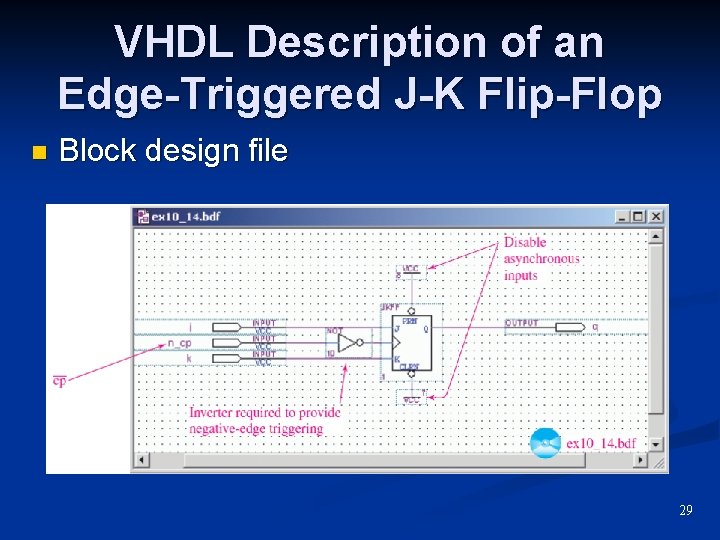

VHDL Description of an Edge-Triggered J-K Flip-Flop n Block design file 29

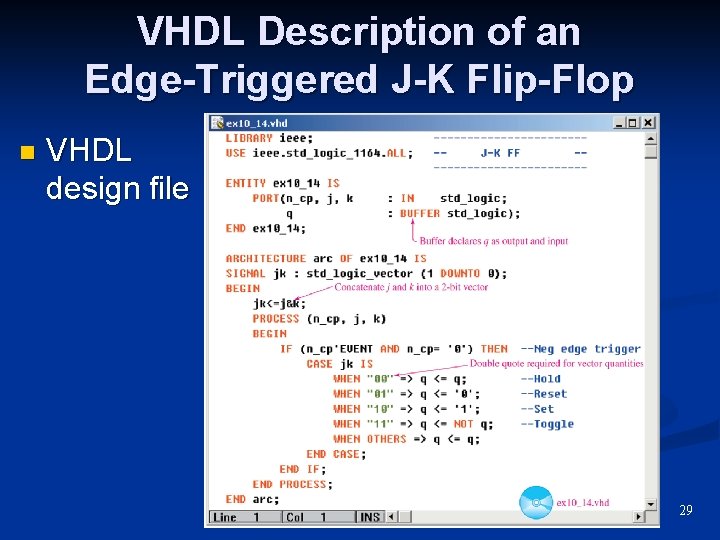

VHDL Description of an Edge-Triggered J-K Flip-Flop n VHDL design file 29

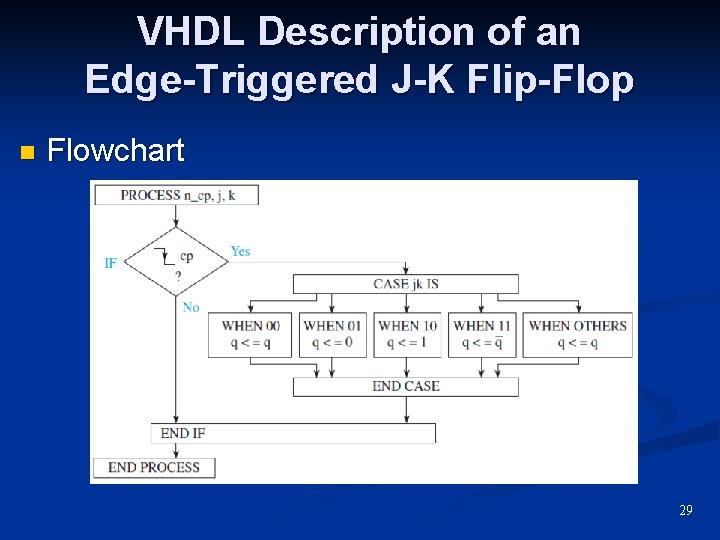

VHDL Description of an Edge-Triggered J-K Flip-Flop n Flowchart 29

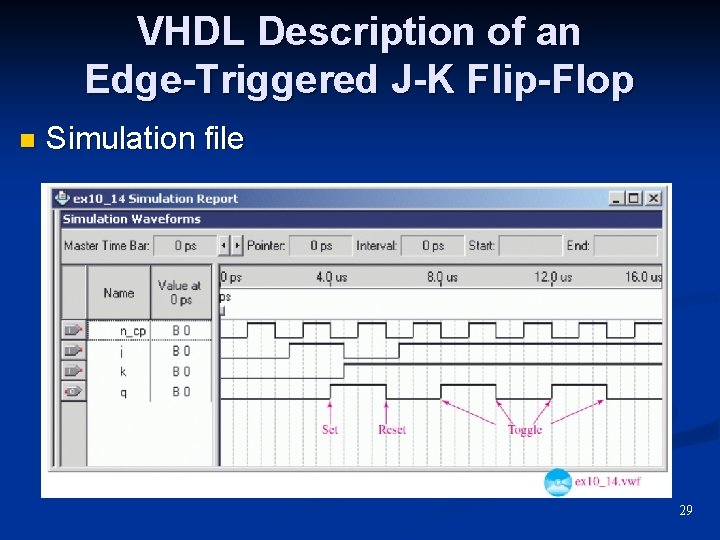

VHDL Description of an Edge-Triggered J-K Flip-Flop n Simulation file 29

Discussion Point How are pulse triggered (level triggered) devices different from edge triggered devices? n What is ones catching? n Identify the synchronous and asynchronous inputs on a JK flip-flop logic symbol n 30

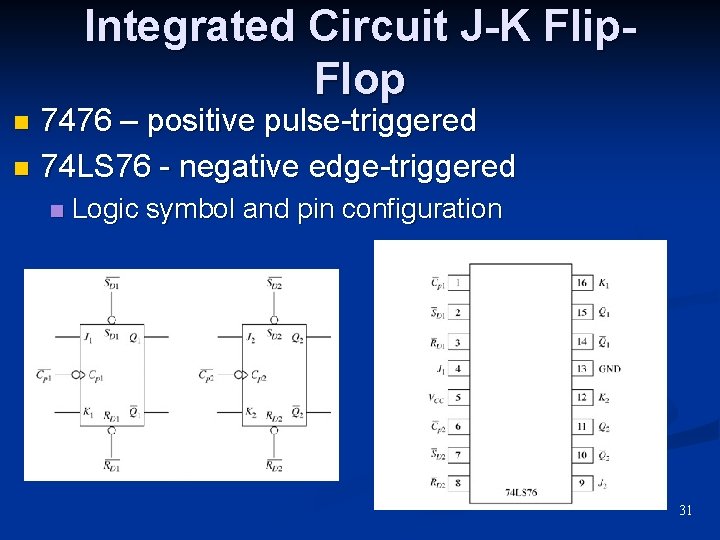

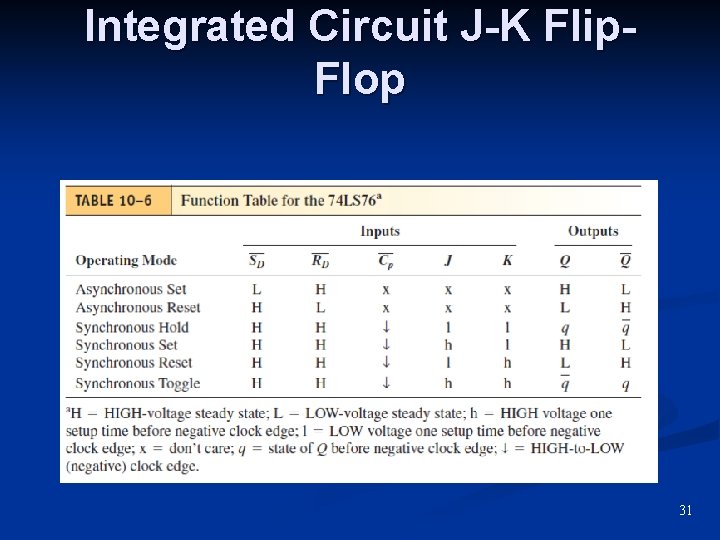

Integrated Circuit J-K Flip. Flop 7476 – positive pulse-triggered n 74 LS 76 - negative edge-triggered n n Logic symbol and pin configuration 31

Integrated Circuit J-K Flip. Flop 31

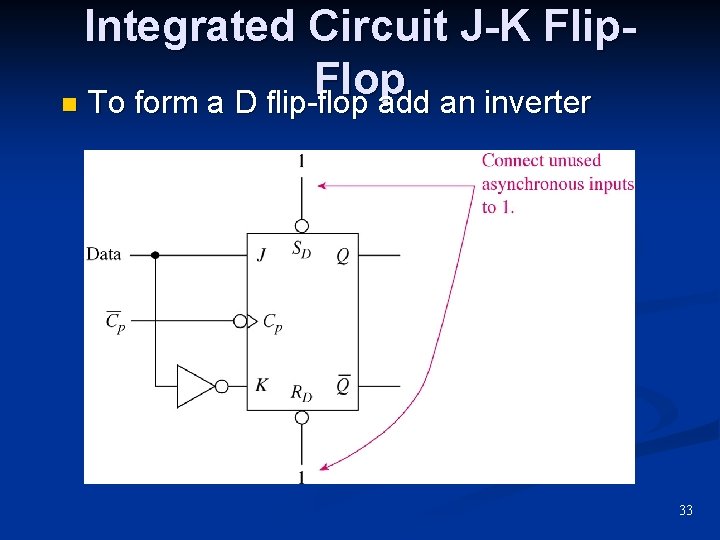

Integrated Circuit J-K Flip. Flop n To form a D flip-flop add an inverter 33

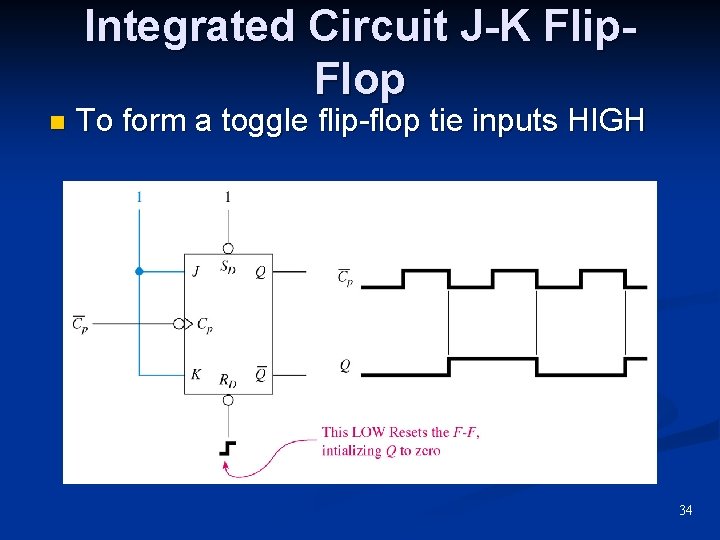

Integrated Circuit J-K Flip. Flop n To form a toggle flip-flop tie inputs HIGH 34

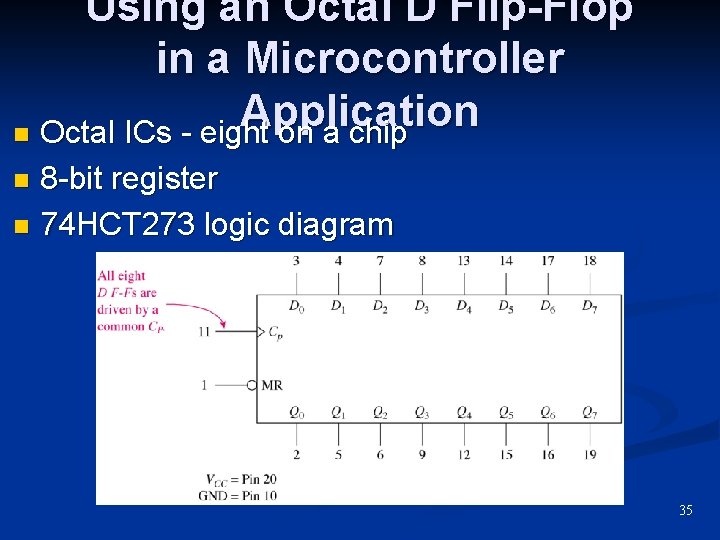

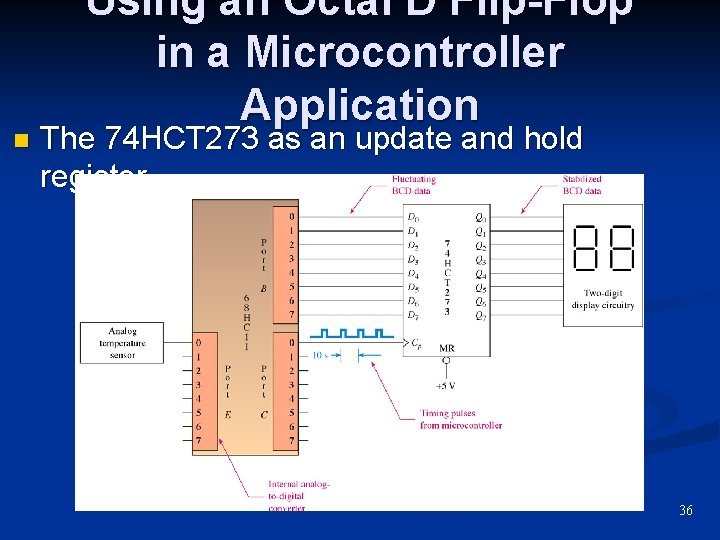

Using an Octal D Flip-Flop in a Microcontroller Application n Octal ICs - eight on a chip 8 -bit register n 74 HCT 273 logic diagram n 35

n Using an Octal D Flip-Flop in a Microcontroller Application The 74 HCT 273 as an update and hold register Figure 10 -45 36

Altera’s LPM Flip-Flop Quartus II provides a general-purpose flipflop called LPM_F n Found in Library of Parameterized Modules subdirectory /megafunctions/storage n Can be used to implement several types of flip-flops n

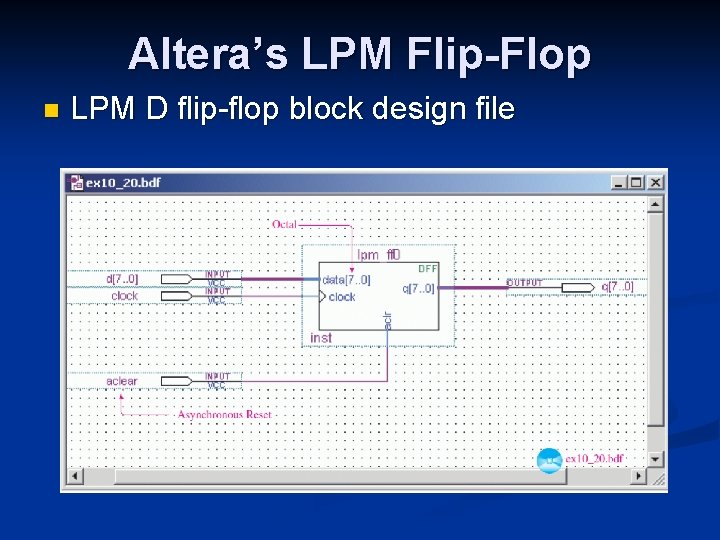

Altera’s LPM Flip-Flop n LPM D flip-flop block design file

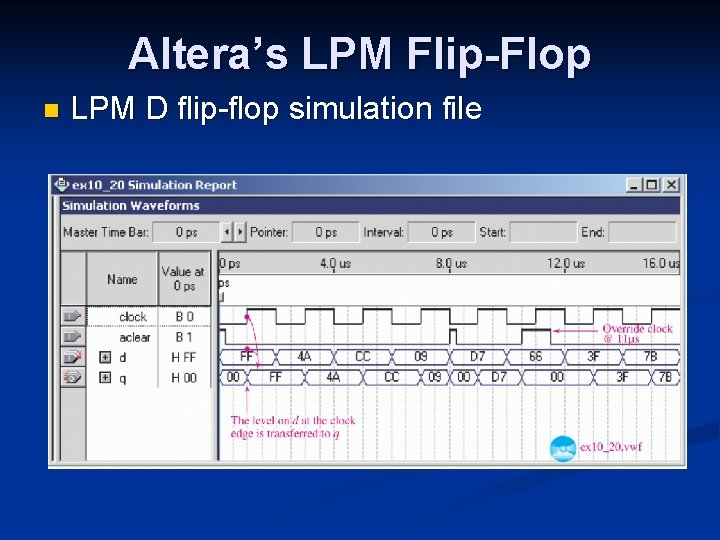

Altera’s LPM Flip-Flop n LPM D flip-flop simulation file

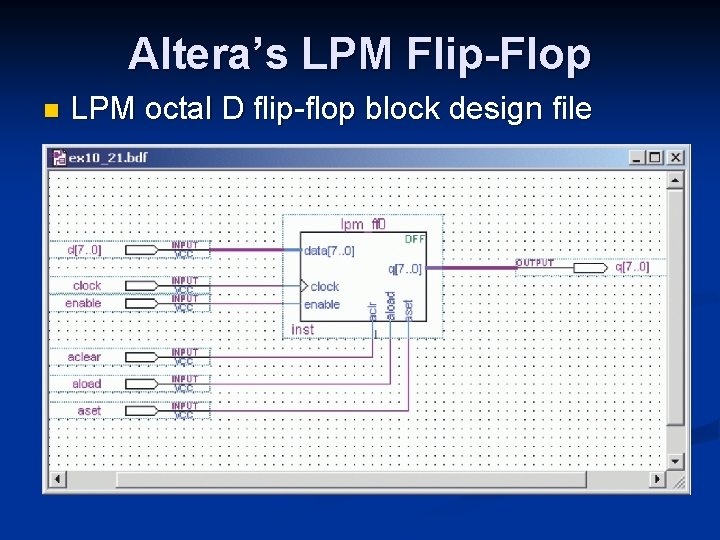

Altera’s LPM Flip-Flop n LPM octal D flip-flop block design file

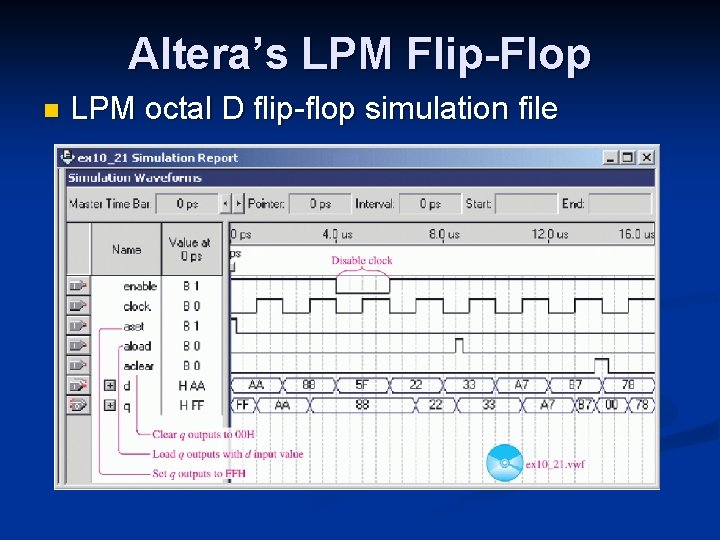

Altera’s LPM Flip-Flop n LPM octal D flip-flop simulation file

Summary The S-R flip-flop is a single-bit data storage circuit that can be constructed using basic gates. n Adding gate enable circuitry to the S-R flipflop makes it synchronous. This means that it will operate only under the control of a clock or enable signal. n 37

Summary The D flip-flop operates similar to the S-R, except it has only a single data input, D. n The 7475 is an integrated-circuit D latch. The output (Q) follows D while the enable (E) is HIGH. When E goes LOW, Q remains latched. n 38

Summary n The 7474 is an integrated-circuit D flip-flop. It has two synchronous inputs, D and Cp, and two asynchronous inputs, SD and RD. Q changes to the level of D at the positive edge of Cp. Q responds immediately to the asynchronous inputs regardless of the synchronous operations. 39

Summary The J-K flip-flop differs from the S-R flipflop because it can also perform a toggle operation. Toggling means that Q flips to its opposite state. n The master-slave J-K slip-flop consists of two latches: a master that receives data while the clock trigger is HIGH, and a slave that receives data from the master and outputs it to Q when the clock goes LOW. n 40

Summary The 74 LS 76 is an edge-triggered J-K flip-flop IC. It has synchronous and asynchronous inputs. The 7476 is similar, except it is a pulse-triggered master-slave type. n The 74 HCT 273 is an example of an octal D flip-flop. It has eight D flip-flops in a single IC package, making it ideal for microprocessor applications. n 41

Summary n The Quartus II software provides a general-purpose flip-flop in the LPM subdirectory that can be used to implement multi-bit D and toggle flipflops. 41

- Slides: 57