CHAPTER 1 Introduction OBJECTIVES Learn the history of

CHAPTER 1 Introduction OBJECTIVES • Learn the history of HDL Development. • Learn how the HDL module is structured. • Learn the use of operators in HDL module. • Learn the different types of an HDL object. • Understand the function of a simulator. • Understand the function of a synthesizer. • Understand the differences between VHDL and Verilog HDL

1. 1 Why HDL? ASICs FPGAs Schematic versus Program 1. 2 Brief History of HDL VHSIC (Very High Speed Integrated Circuit) Hardware Description Language IEEE standard 1076 1993. December 1995, Verilog HDL became IEEE Std. 1364 -1995

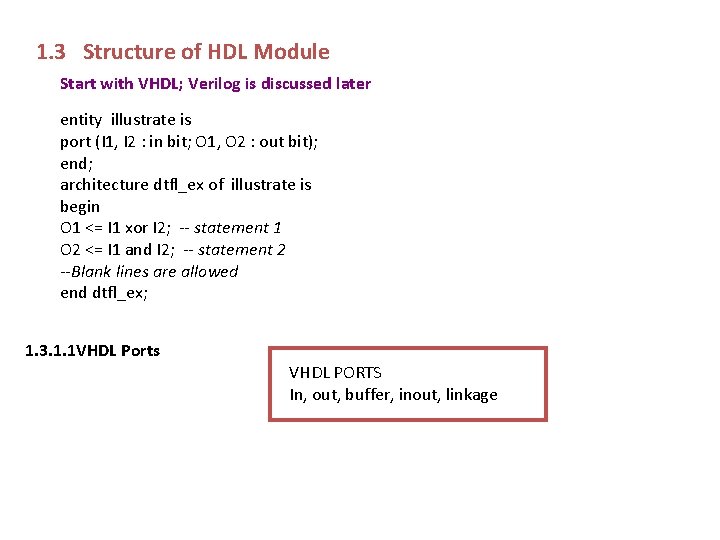

1. 3 Structure of HDL Module Start with VHDL; Verilog is discussed later entity illustrate is port (I 1, I 2 : in bit; O 1, O 2 : out bit); end; architecture dtfl_ex of illustrate is begin O 1 <= I 1 xor I 2; -- statement 1 O 2 <= I 1 and I 2; -- statement 2 --Blank lines are allowed end dtfl_ex; 1. 3. 1. 1 VHDL Ports VHDL PORTS In, out, buffer, inout, linkage

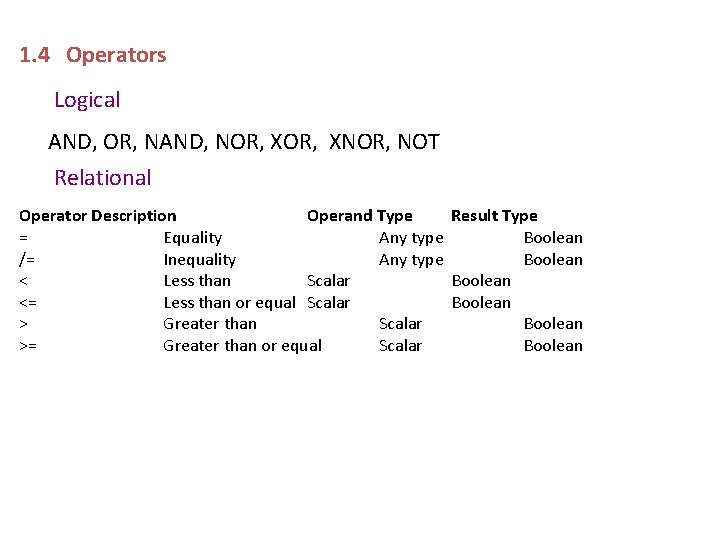

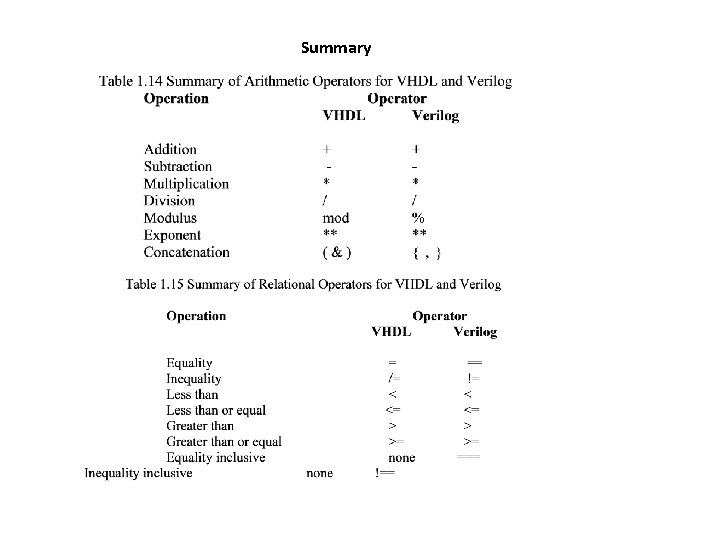

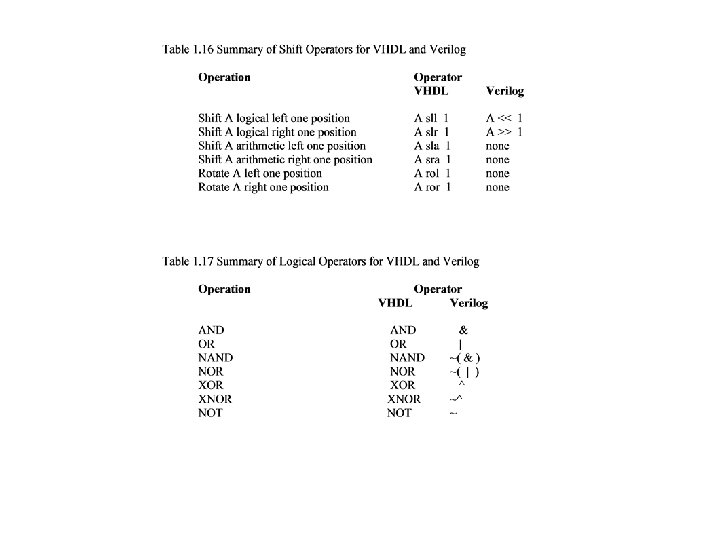

1. 4 Operators Logical AND, OR, NAND, NOR, XOR, XNOR, NOT Relational Operator Description Operand Type Result Type = Equality Any type Boolean /= Inequality Any type Boolean < Less than Scalar Boolean <= Less than or equal Scalar Boolean > Greater than Scalar Boolean >= Greater than or equal Scalar Boolean

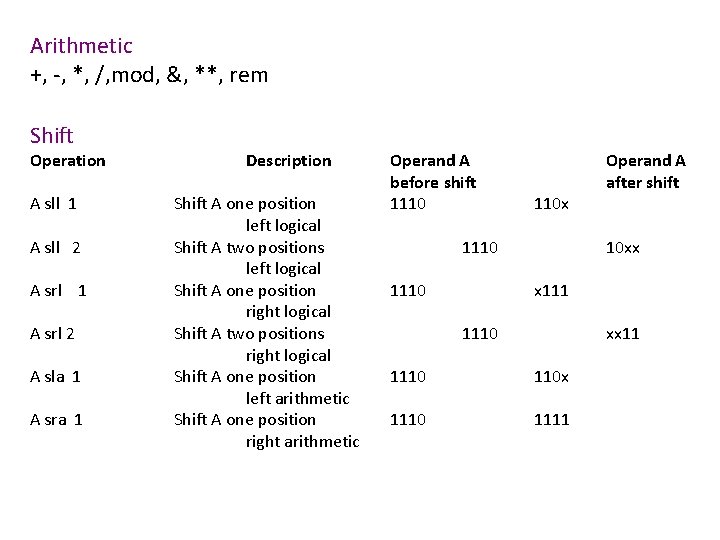

Arithmetic +, -, *, /, mod, &, **, rem Shift Operation A sll 1 A sll 2 A srl 1 A srl 2 A sla 1 A sra 1 Description Shift A one position left logical Shift A two positions left logical Shift A one position right logical Shift A two positions right logical Shift A one position left arithmetic Shift A one position right arithmetic Operand A before shift 1110 110 x 1110 Operand A after shift 10 xx x 1110 xx 11 1110 110 x 1110 1111

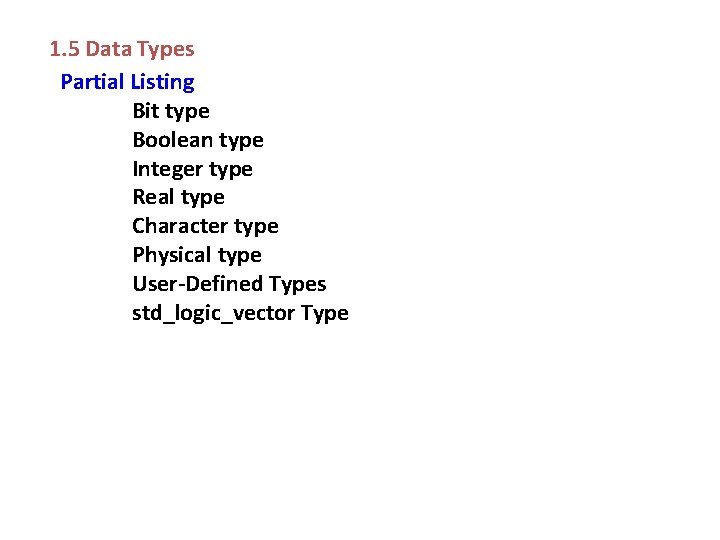

1. 5 Data Types Partial Listing Bit type Boolean type Integer type Real type Character type Physical type User-Defined Types std_logic_vector Type

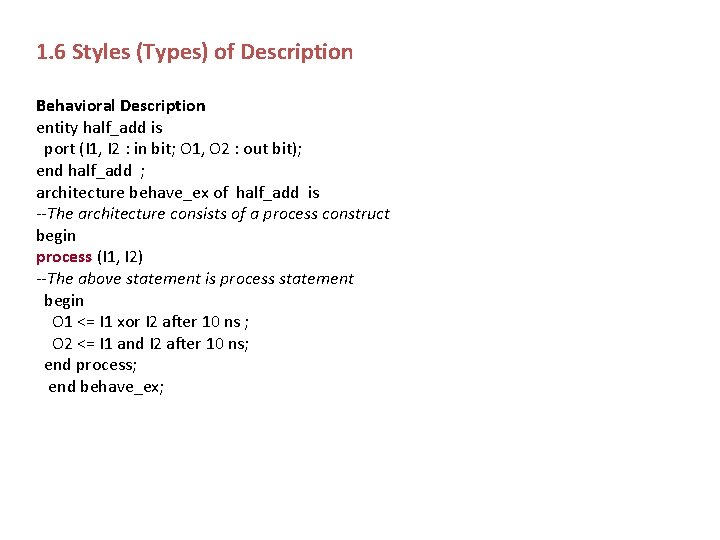

1. 6 Styles (Types) of Description Behavioral Description entity half_add is port (I 1, I 2 : in bit; O 1, O 2 : out bit); end half_add ; architecture behave_ex of half_add is --The architecture consists of a process construct begin process (I 1, I 2) --The above statement is process statement begin O 1 <= I 1 xor I 2 after 10 ns ; O 2 <= I 1 and I 2 after 10 ns; end process; end behave_ex;

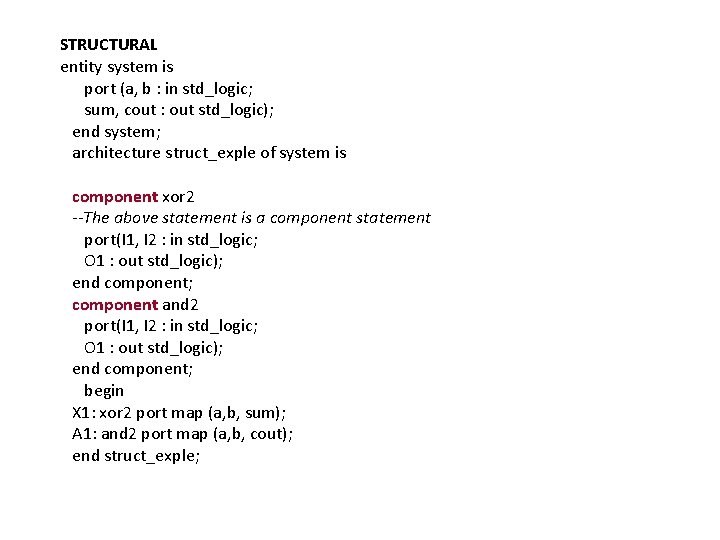

STRUCTURAL entity system is port (a, b : in std_logic; sum, cout : out std_logic); end system; architecture struct_exple of system is component xor 2 --The above statement is a component statement port(I 1, I 2 : in std_logic; O 1 : out std_logic); end component; component and 2 port(I 1, I 2 : in std_logic; O 1 : out std_logic); end component; begin X 1: xor 2 port map (a, b, sum); A 1: and 2 port map (a, b, cout); end struct_exple;

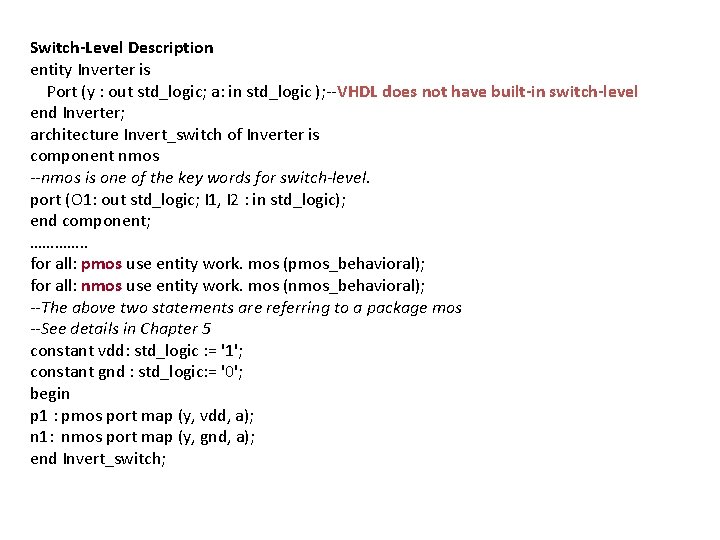

Switch-Level Description entity Inverter is Port (y : out std_logic; a: in std_logic ); --VHDL does not have built-in switch-level end Inverter; architecture Invert_switch of Inverter is component nmos --nmos is one of the key words for switch-level. port (O 1: out std_logic; I 1, I 2 : in std_logic); end component; …………. . for all: pmos use entity work. mos (pmos_behavioral); for all: nmos use entity work. mos (nmos_behavioral); --The above two statements are referring to a package mos --See details in Chapter 5 constant vdd: std_logic : = '1'; constant gnd : std_logic: = '0'; begin p 1 : pmos port map (y, vdd, a); n 1: nmos port map (y, gnd, a); end Invert_switch;

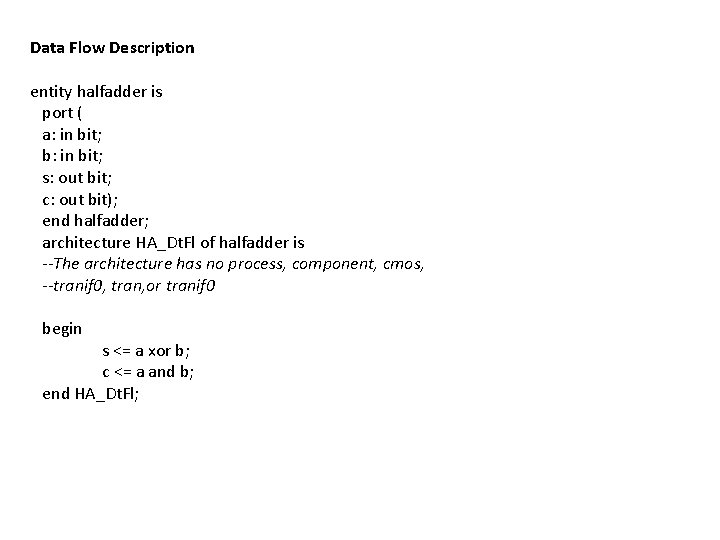

Data Flow Description entity halfadder is port ( a: in bit; b: in bit; s: out bit; c: out bit); end halfadder; architecture HA_Dt. Fl of halfadder is --The architecture has no process, component, cmos, --tranif 0, tran, or tranif 0 begin s <= a xor b; c <= a and b; end HA_Dt. Fl;

Mixed-Type Description Mixed-Language Description

Summary

- Slides: 13