Chapter 1 Hspice IC CAD Analog part Digital

![Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ > mkdir hspice [ICCAD@train##]/user 1/train##/ Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ > mkdir hspice [ICCAD@train##]/user 1/train##/](https://slidetodoc.com/presentation_image_h/8a0880ead50a207aa111e57ad7b03c87/image-8.jpg)

![Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> cp /user 1/master/hspice/inv_sim. sp. Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> cp /user 1/master/hspice/inv_sim. sp.](https://slidetodoc.com/presentation_image_h/8a0880ead50a207aa111e57ad7b03c87/image-11.jpg)

![Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> hspice inv_sim. sp > Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> hspice inv_sim. sp >](https://slidetodoc.com/presentation_image_h/8a0880ead50a207aa111e57ad7b03c87/image-13.jpg)

- Slides: 25

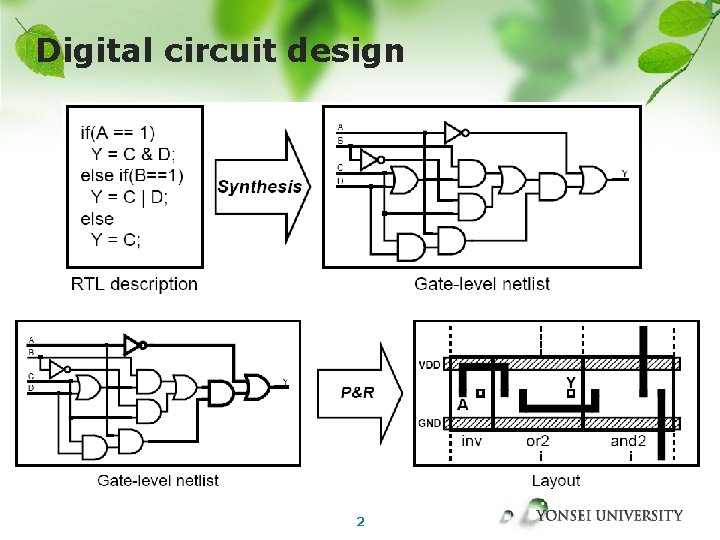

Chapter 1. Hspice IC CAD 실험 Analog part

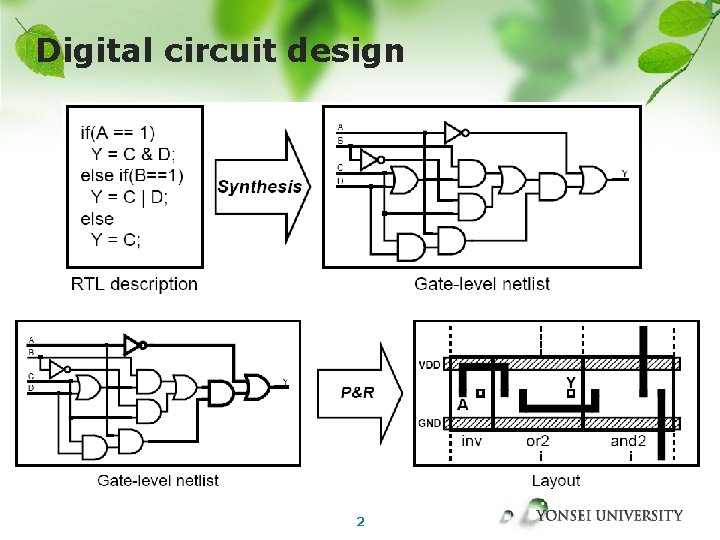

Digital circuit design 2

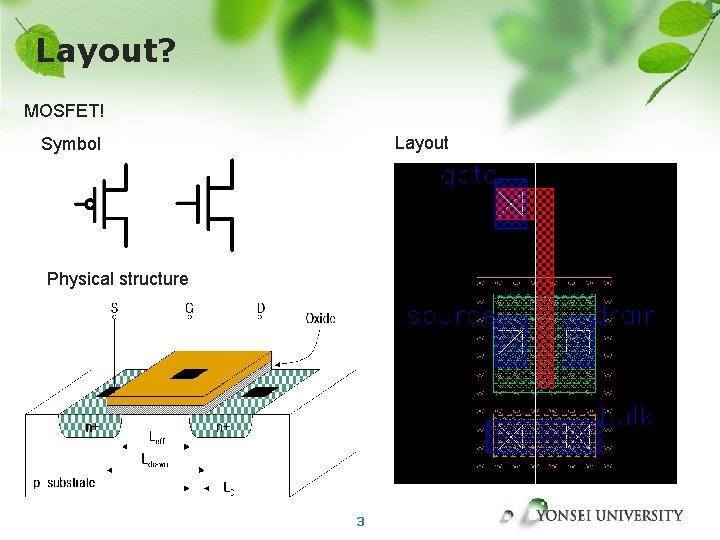

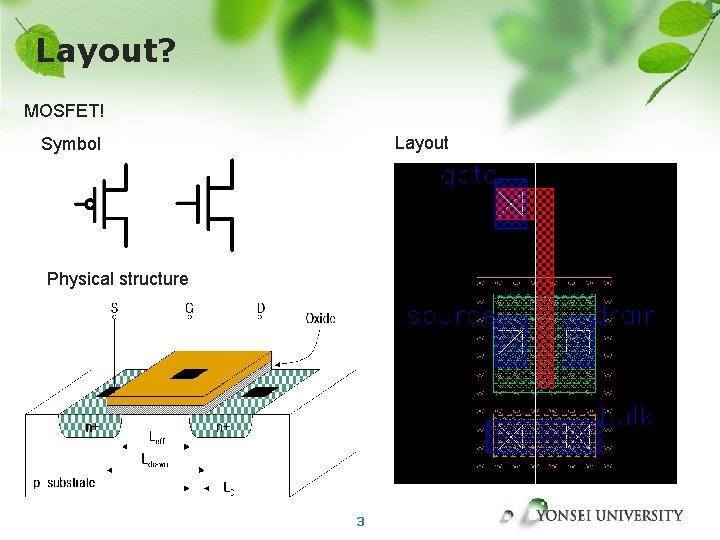

Layout? MOSFET! Layout Symbol Physical structure 3

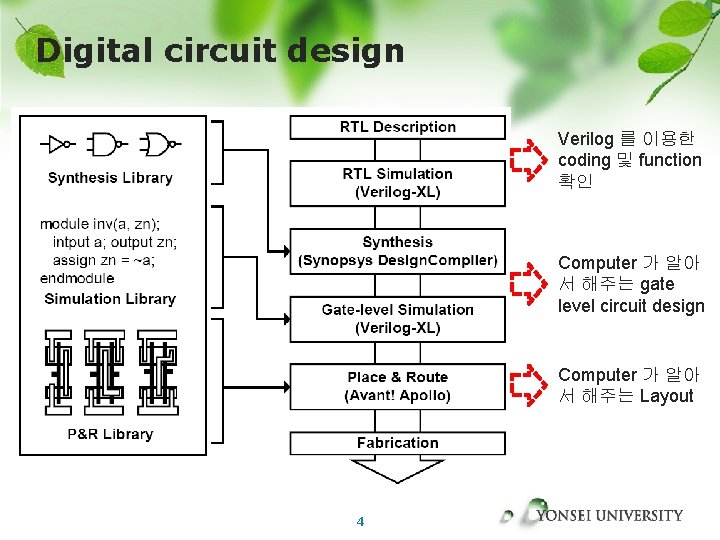

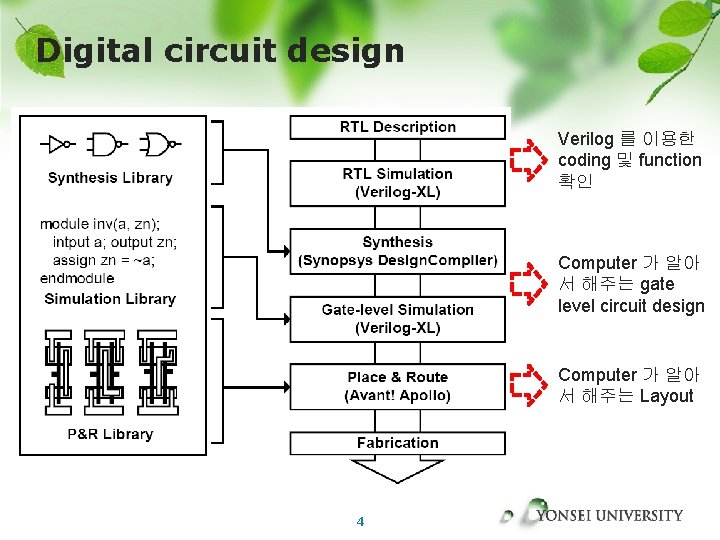

Digital circuit design Verilog 를 이용한 coding 및 function 확인 Computer 가 알아 서 해주는 gate level circuit design Computer 가 알아 서 해주는 Layout 4

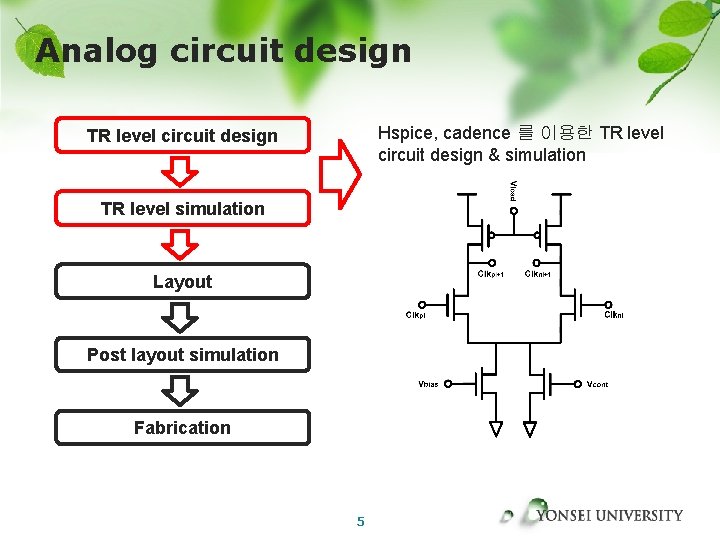

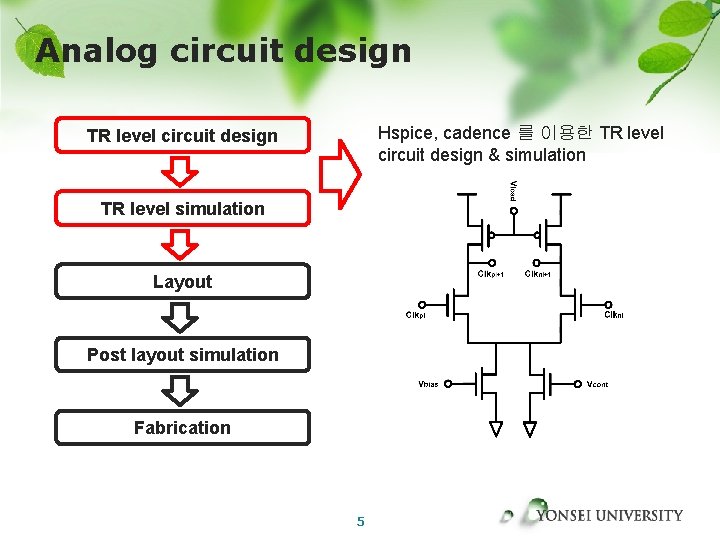

Analog circuit design Hspice, cadence 를 이용한 TR level circuit design & simulation TR level circuit design TR level simulation Layout Post layout simulation Fabrication 5

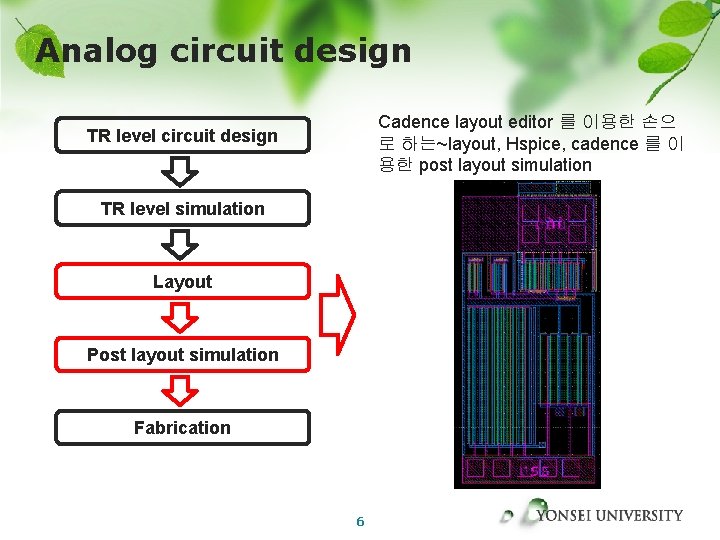

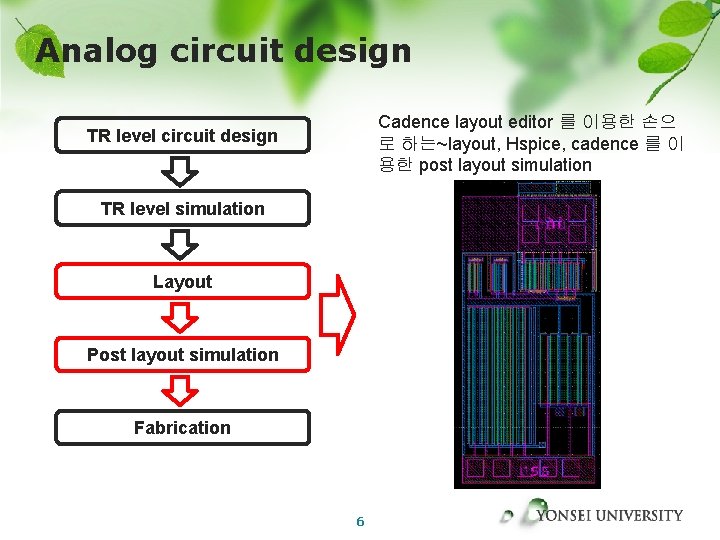

Analog circuit design Cadence layout editor 를 이용한 손으 로 하는~layout, Hspice, cadence 를 이 용한 post layout simulation TR level circuit design TR level simulation Layout Post layout simulation Fabrication 6

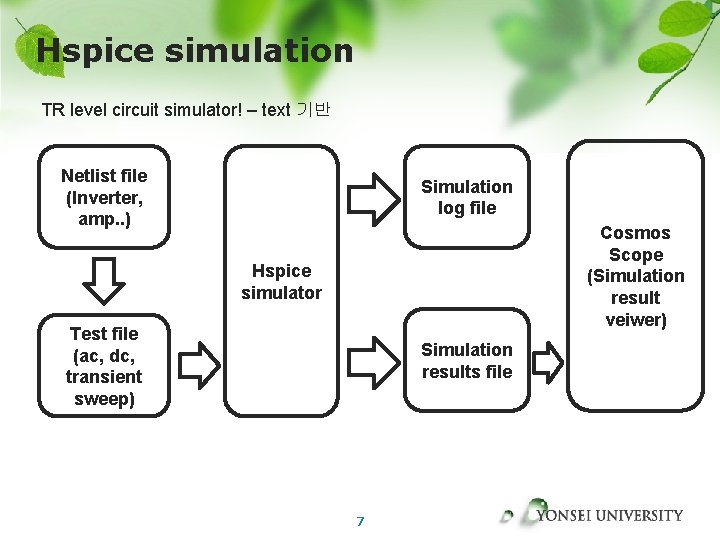

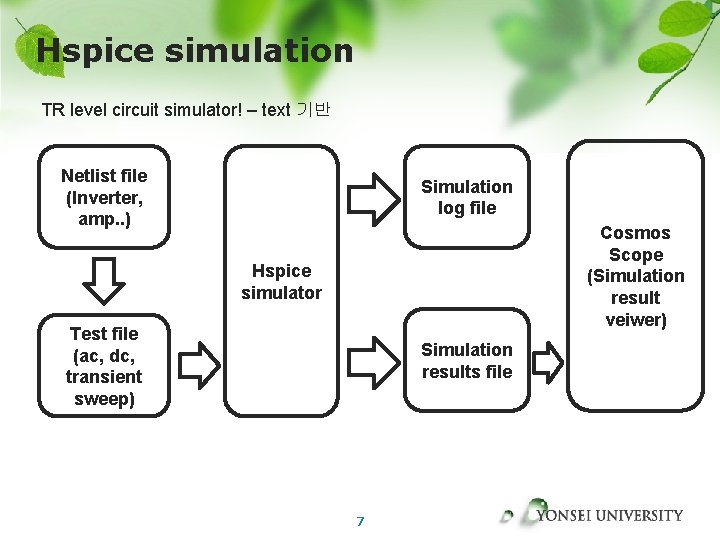

Hspice simulation TR level circuit simulator! – text 기반 Netlist file (Inverter, amp. . ) Simulation log file Cosmos Scope (Simulation result veiwer) Hspice simulator Test file (ac, dc, transient sweep) Simulation results file 7

![Hspice simulation Example Inverter 설계 및 simulation ICCADtrainuser 1train mkdir hspice ICCADtrainuser 1train Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ > mkdir hspice [ICCAD@train##]/user 1/train##/](https://slidetodoc.com/presentation_image_h/8a0880ead50a207aa111e57ad7b03c87/image-8.jpg)

Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ > mkdir hspice [ICCAD@train##]/user 1/train##/ > cd hspice [ICCAD@train##]/user 1/train##/ hspice> cp /user 1/master/hspice/netlist. sp. cp /user 1/master/hspice/PMOS_VTL. inc. cp /user 1/master/hspice/NMOS_VTL. inc. ls [ICCAD@train##]/user 1/train##/ hspice> vi netlists. sp 8

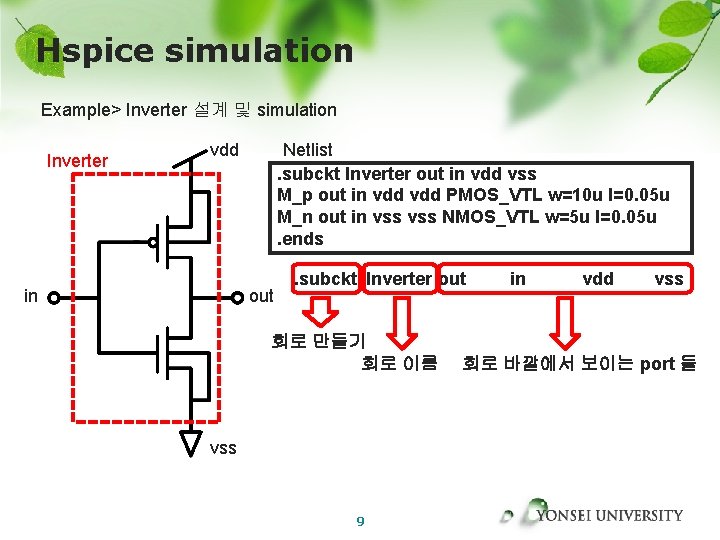

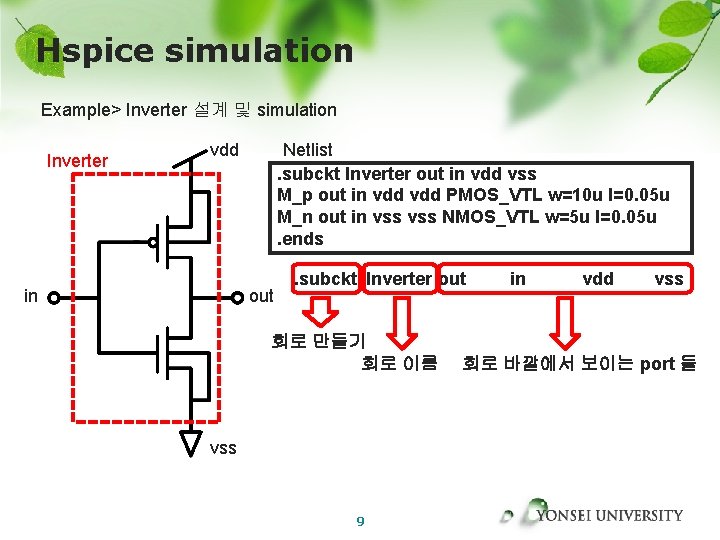

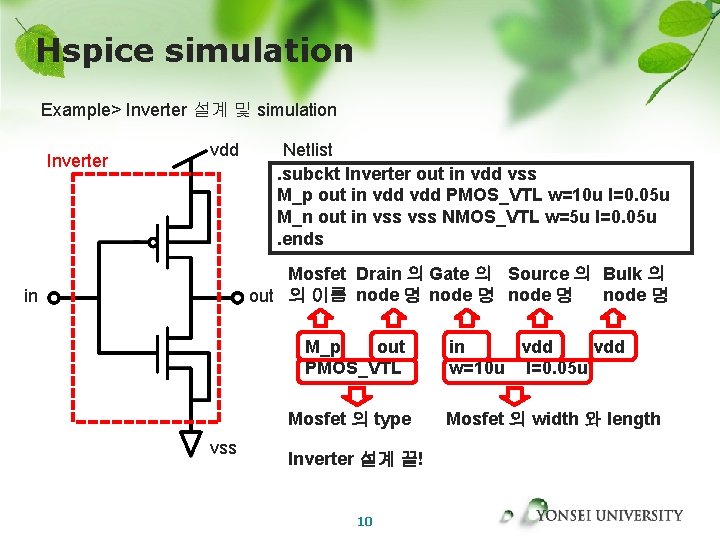

Hspice simulation Example> Inverter 설계 및 simulation Inverter vdd in Netlist. subckt Inverter out in vdd vss M_p out in vdd PMOS_VTL w=10 u l=0. 05 u M_n out in vss NMOS_VTL w=5 u l=0. 05 u. ends out . subckt Inverter out 회로 만들기 회로 이름 vss 9 in vdd vss 회로 바깥에서 보이는 port 들

Hspice simulation Example> Inverter 설계 및 simulation Inverter vdd Netlist. subckt Inverter out in vdd vss M_p out in vdd PMOS_VTL w=10 u l=0. 05 u M_n out in vss NMOS_VTL w=5 u l=0. 05 u. ends Mosfet Drain 의 Gate 의 Source 의 Bulk 의 node 명 out 의 이름 node 명 in M_p out PMOS_VTL Mosfet 의 type vss Inverter 설계 끝! 10 in vdd w=10 u l=0. 05 u Mosfet 의 width 와 length

![Hspice simulation Example Inverter 설계 및 simulation ICCADtrainuser 1train hspice cp user 1masterhspiceinvsim sp Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> cp /user 1/master/hspice/inv_sim. sp.](https://slidetodoc.com/presentation_image_h/8a0880ead50a207aa111e57ad7b03c87/image-11.jpg)

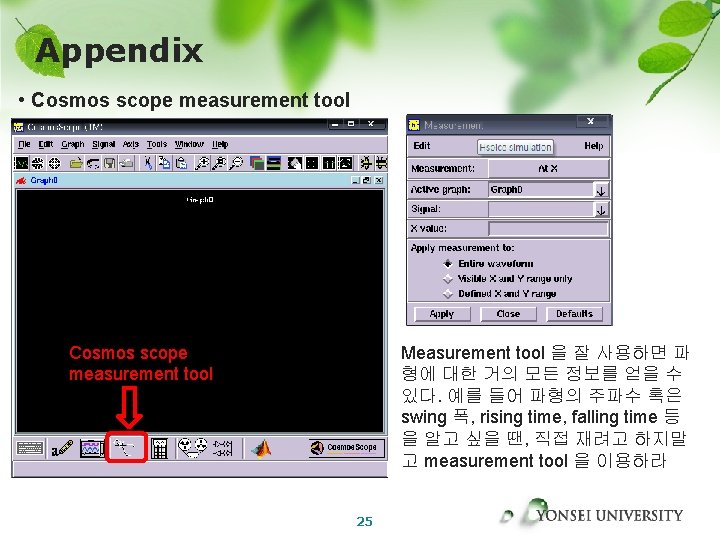

Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> cp /user 1/master/hspice/inv_sim. sp. [ICCAD@train##]/user 1/train##/ hspice> vi inv_sim. sp 11

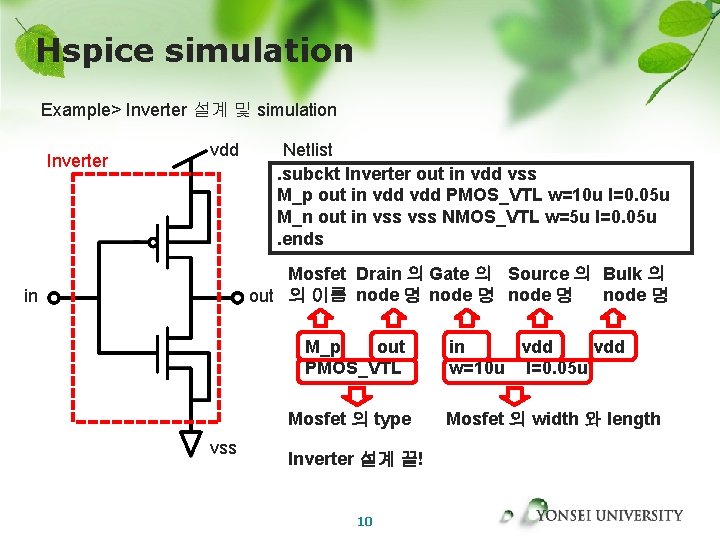

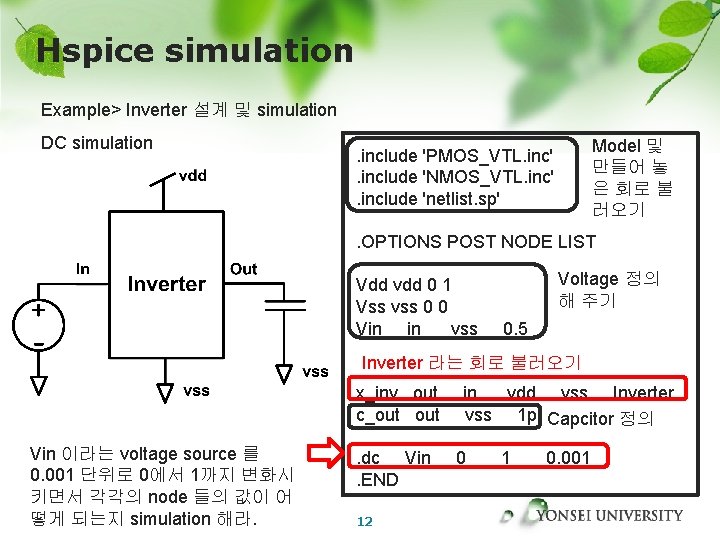

Hspice simulation Example> Inverter 설계 및 simulation DC simulation Model 및 만들어 놓 은 회로 불 러오기 . include 'PMOS_VTL. inc'. include 'NMOS_VTL. inc'. include 'netlist. sp' . OPTIONS POST NODE LIST Vdd vdd 0 1 Vss vss 0 0 Vin in vss Voltage 정의 해 주기 0. 5 Inverter 라는 회로 불러오기 x_inv out c_out Vin 이라는 voltage source 를 0. 001 단위로 0에서 1까지 변화시 키면서 각각의 node 들의 값이 어 떻게 되는지 simulation 해라. . dc Vin. END 12 in vdd vss Inverter vss 1 p Capcitor 정의 0 1 0. 001

![Hspice simulation Example Inverter 설계 및 simulation ICCADtrainuser 1train hspice hspice invsim sp Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> hspice inv_sim. sp >](https://slidetodoc.com/presentation_image_h/8a0880ead50a207aa111e57ad7b03c87/image-13.jpg)

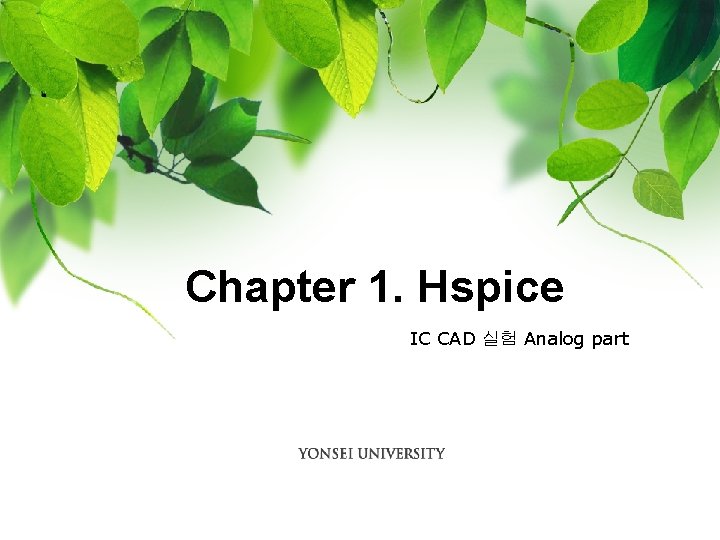

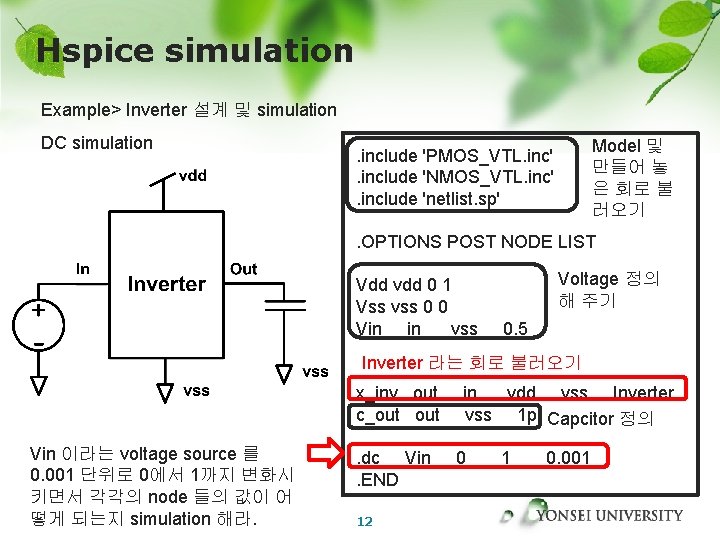

Hspice simulation Example> Inverter 설계 및 simulation [ICCAD@train##]/user 1/train##/ hspice> hspice inv_sim. sp > a. lis & [ICCAD@train##]/user 1/train##/ hspice> >info : **** hspice jab concluded [ICCAD@train##]/user 1/train##/ hspice> cscope & 13

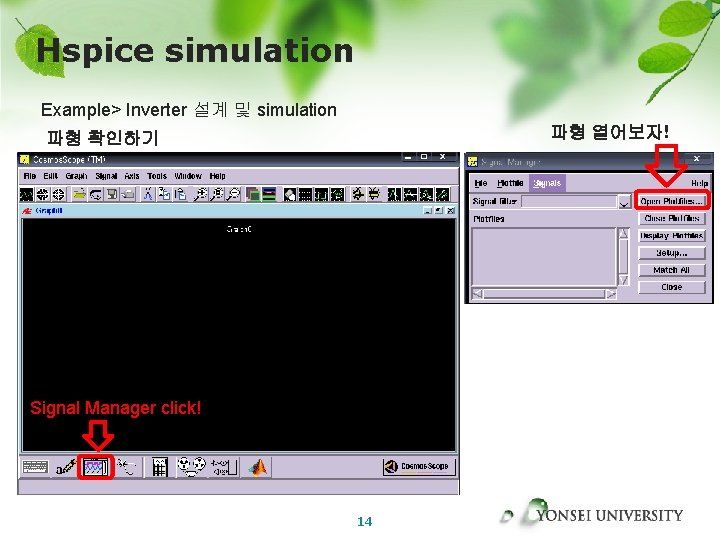

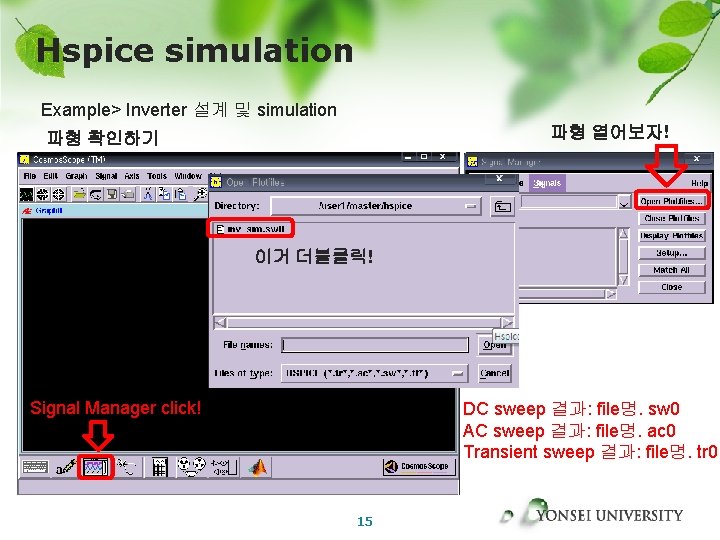

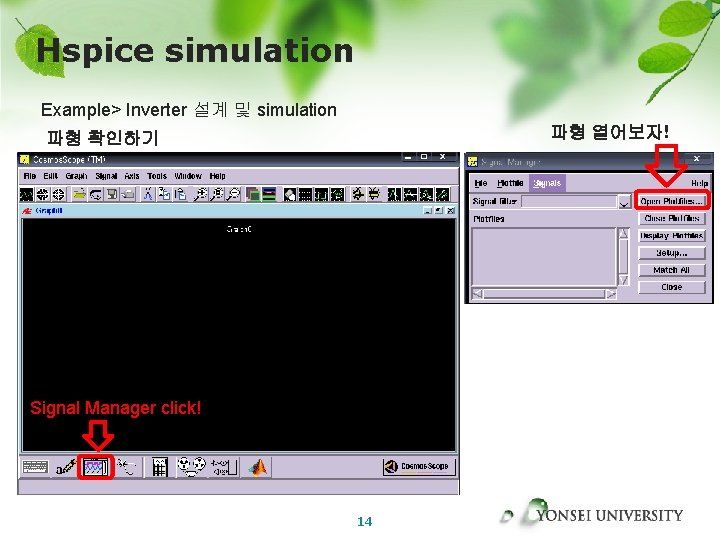

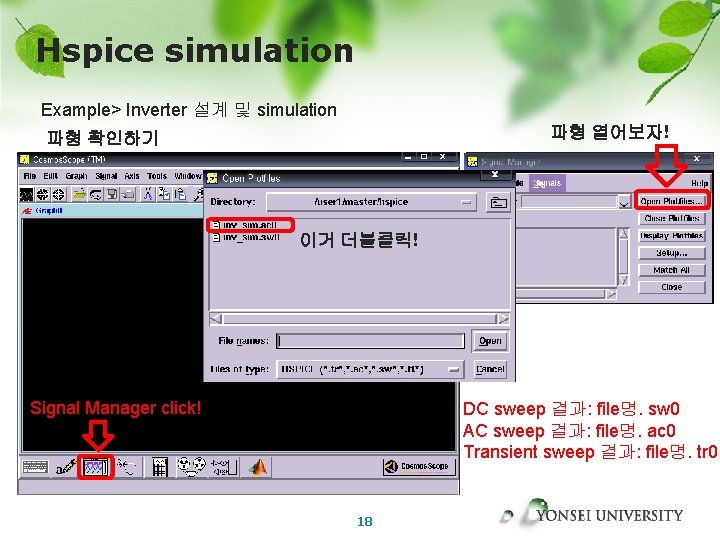

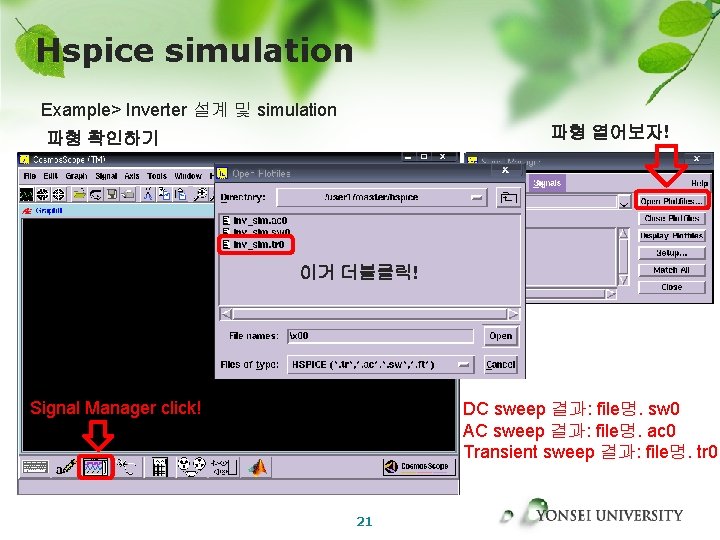

Hspice simulation Example> Inverter 설계 및 simulation 파형 열어보자! 파형 확인하기 Signal Manager click! 14

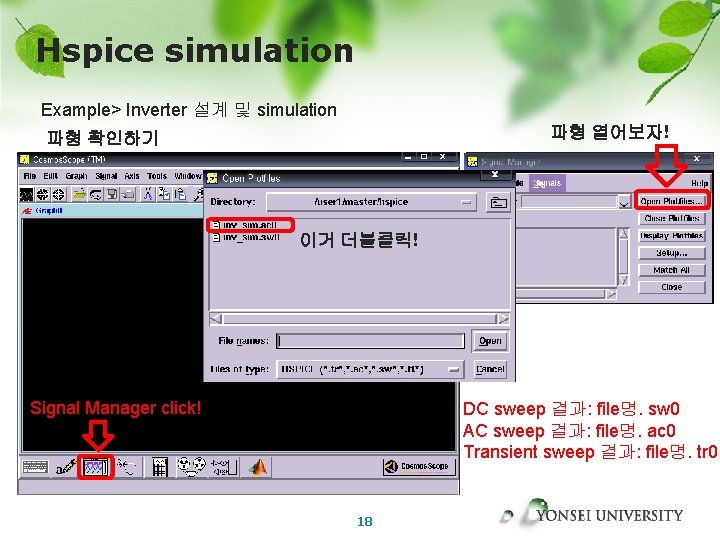

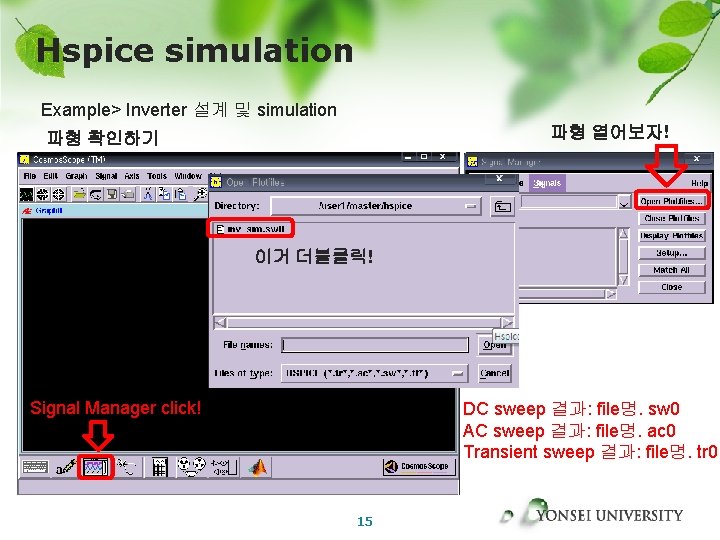

Hspice simulation Example> Inverter 설계 및 simulation 파형 열어보자! 파형 확인하기 이거 더블클릭! Signal Manager click! DC sweep 결과: file명. sw 0 AC sweep 결과: file명. ac 0 Transient sweep 결과: file명. tr 0 15

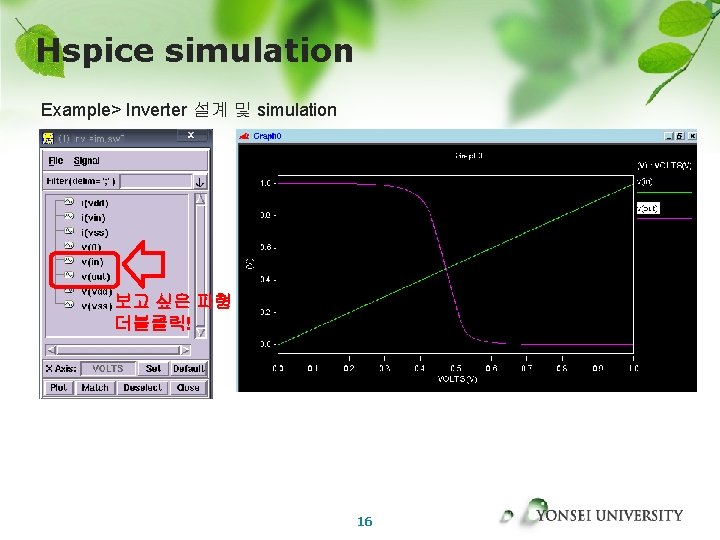

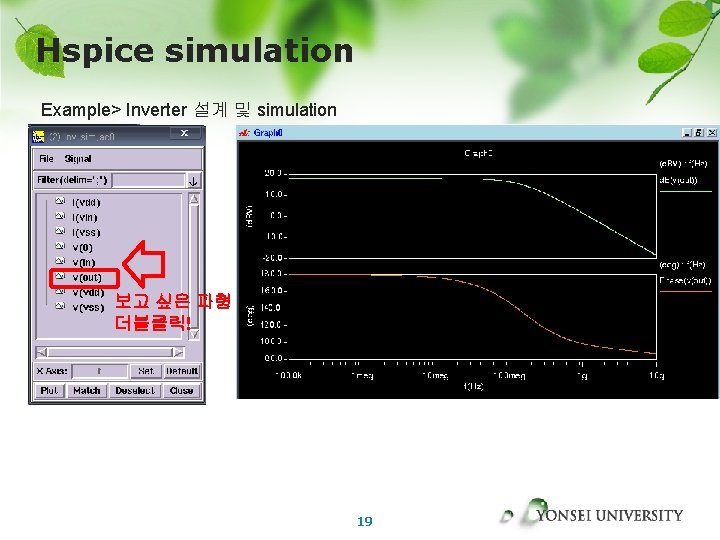

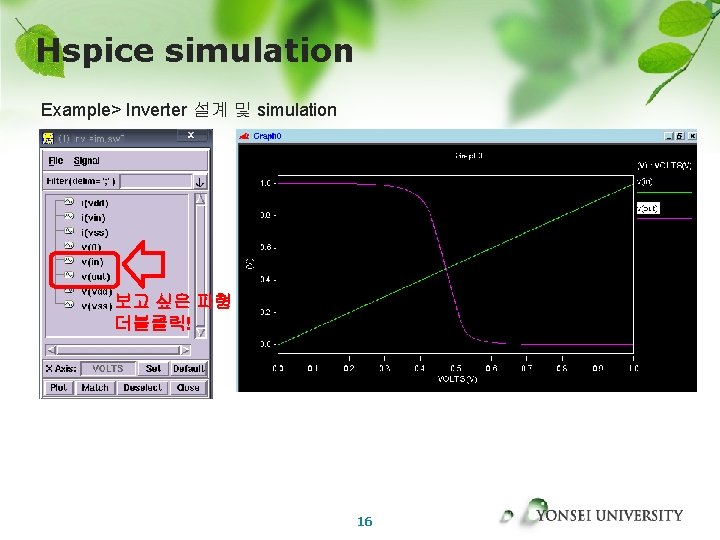

Hspice simulation Example> Inverter 설계 및 simulation 보고 싶은 파형 더블클릭! 16

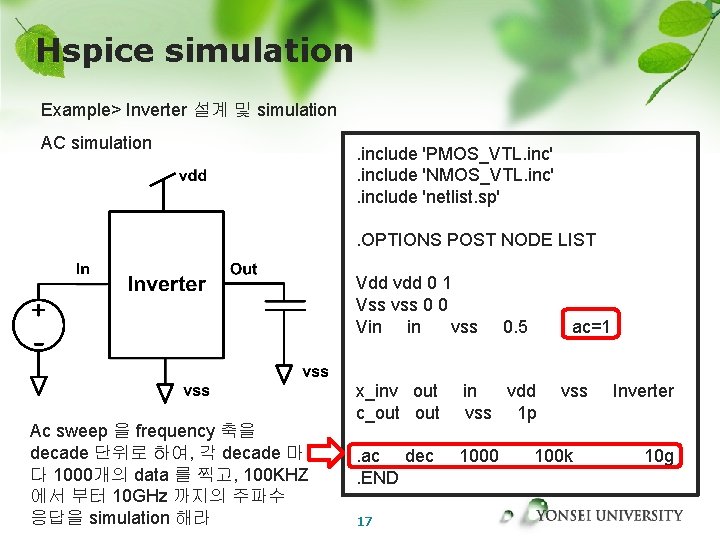

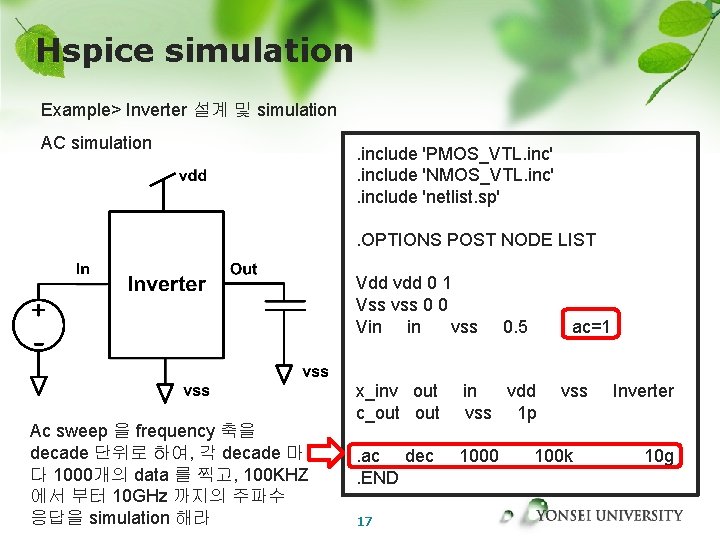

Hspice simulation Example> Inverter 설계 및 simulation AC simulation . include 'PMOS_VTL. inc'. include 'NMOS_VTL. inc'. include 'netlist. sp'. OPTIONS POST NODE LIST Vdd vdd 0 1 Vss vss 0 0 Vin in vss Ac sweep 을 frequency 축을 decade 단위로 하여, 각 decade 마 다 1000개의 data 를 찍고, 100 KHZ 에서 부터 10 GHz 까지의 주파수 응답을 simulation 해라 0. 5 ac=1 x_inv out c_out in vdd vss 1 p . ac dec. END 1000 17 vss 100 k Inverter 10 g

Hspice simulation Example> Inverter 설계 및 simulation 파형 열어보자! 파형 확인하기 이거 더블클릭! Signal Manager click! DC sweep 결과: file명. sw 0 AC sweep 결과: file명. ac 0 Transient sweep 결과: file명. tr 0 18

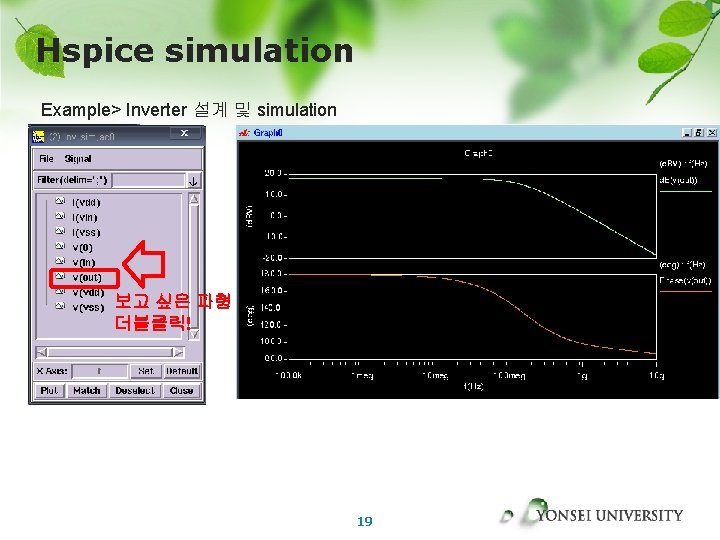

Hspice simulation Example> Inverter 설계 및 simulation 보고 싶은 파형 더블클릭! 19

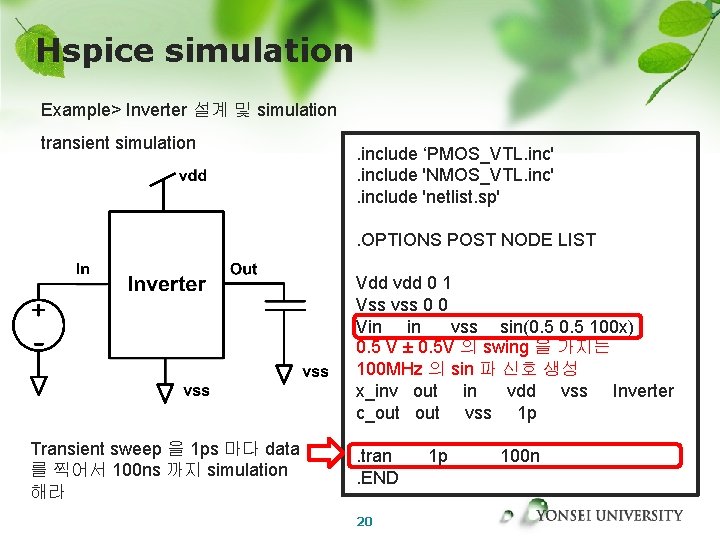

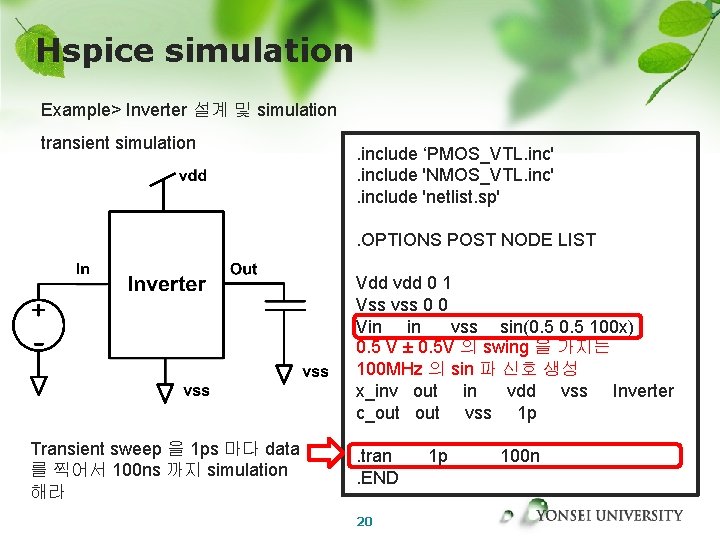

Hspice simulation Example> Inverter 설계 및 simulation transient simulation . include ‘PMOS_VTL. inc'. include 'NMOS_VTL. inc'. include 'netlist. sp'. OPTIONS POST NODE LIST Vdd vdd 0 1 Vss vss 0 0 Vin in vss sin(0. 5 100 x) 0. 5 V ± 0. 5 V 의 swing 을 가지는 100 MHz 의 sin 파 신호 생성 x_inv out in vdd vss Inverter c_out vss 1 p Transient sweep 을 1 ps 마다 data 를 찍어서 100 ns 까지 simulation 해라 . tran. END 20 1 p 100 n

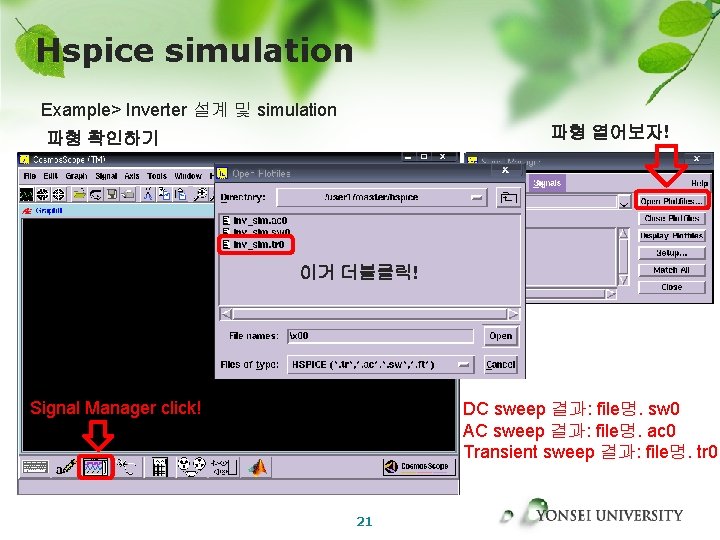

Hspice simulation Example> Inverter 설계 및 simulation 파형 열어보자! 파형 확인하기 이거 더블클릭! Signal Manager click! DC sweep 결과: file명. sw 0 AC sweep 결과: file명. ac 0 Transient sweep 결과: file명. tr 0 21

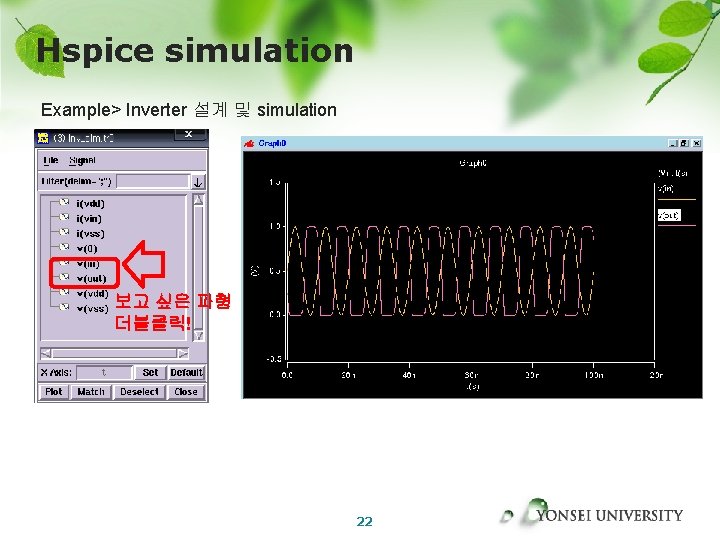

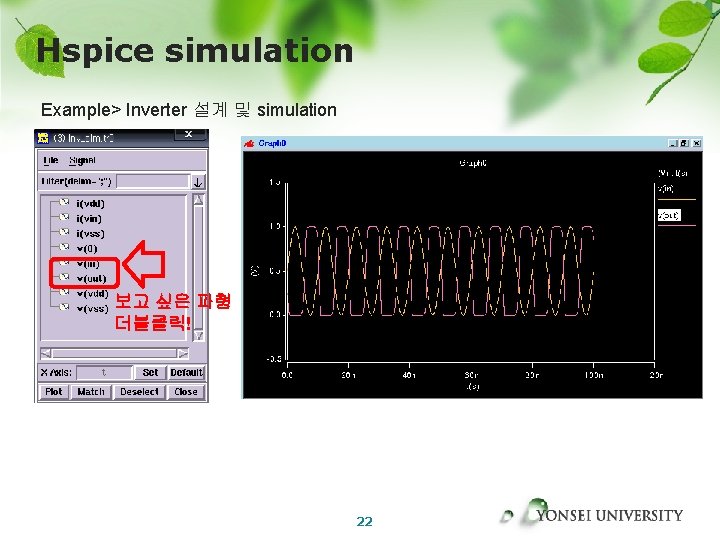

Hspice simulation Example> Inverter 설계 및 simulation 보고 싶은 파형 더블클릭! 22

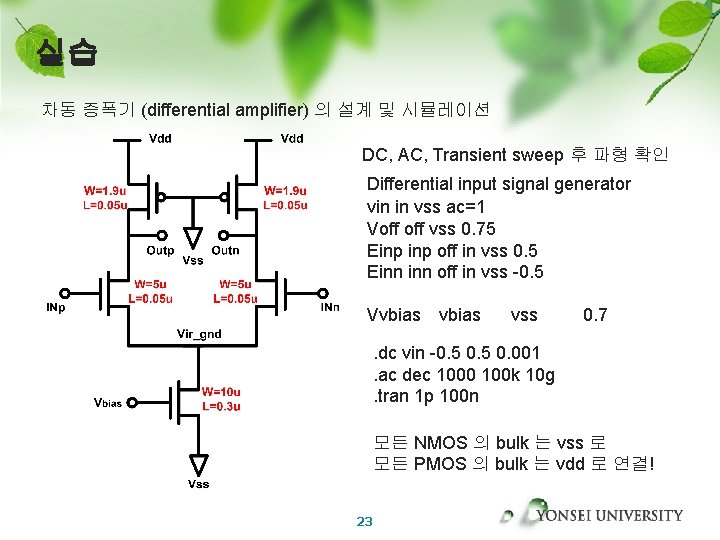

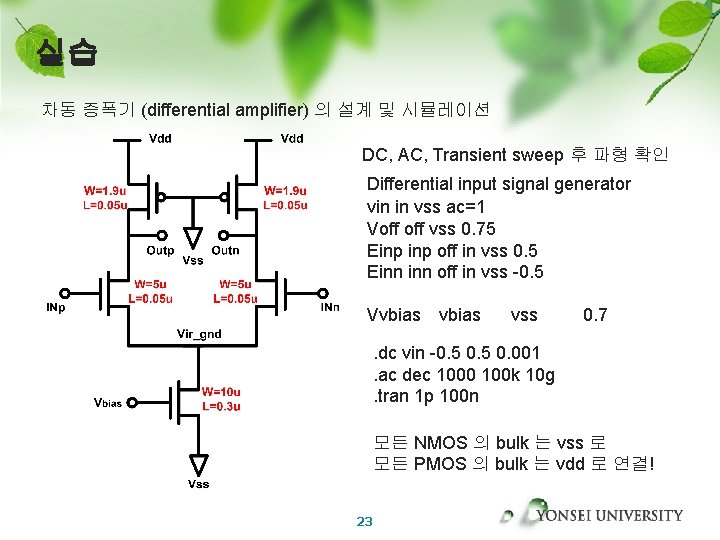

실습 차동 증폭기 (differential amplifier) 의 설계 및 시뮬레이션 DC, AC, Transient sweep 후 파형 확인 Differential input signal generator vin in vss ac=1 Voff vss 0. 75 Einp off in vss 0. 5 Einn off in vss -0. 5 Vvbias vss 0. 7 . dc vin -0. 5 0. 001. ac dec 1000 100 k 10 g. tran 1 p 100 n 모든 NMOS 의 bulk 는 vss 로 모든 PMOS 의 bulk 는 vdd 로 연결! 23