Chapter 1 Computer Abstractions and Technology Lecture 2

Chapter 1 Computer Abstractions and Technology Lecture 2 2471 CE– Computer Architecture Instructor: Suzan Hassan Department of Computer and Information Science

2 Computer Architecture v Computer Architecture = Instruction Set Architecture + Computer Organization Instruction set: number of bits used for data representation, I/O mechanisms, addressing techniques v Instruction Set Architecture (ISA)= Specification WHAT the computer does (logical view) v Computer Organization= Implementation HOW the ISA is implemented (physical view) (Control signals, interfaces, memory technology)

Computer Organization v Realization of the Instruction Set Architecture v Characteristics of principal components Registers, ALUs, Caches, . . . v Ways in which these components are interconnected v Information flow between components and control it v Register Transfer Level (RTL) description Introduction to Computer Architecture © © SUZAN HASSAN, CSE 308 – KFUPM Slide 3

Instruction Set Architecture (ISA) v Definition by Amdahl, Blaaw, and Brooks – 1964 The conceptual structure and functional behavior, (the organization of the data flows and controls the logic design, and the physical implementation). ” v An ISA encompasses … Instructions and Instruction Formats Data Types, Encodings, and Representations Programmable Storage: Registers and Memory Addressing Modes: Accessing Instructions and Data Handling Exceptional Conditions Introduction to Computer Architecture © © SUZAN HASSAN, CSE 308 – KFUPM Slide 4

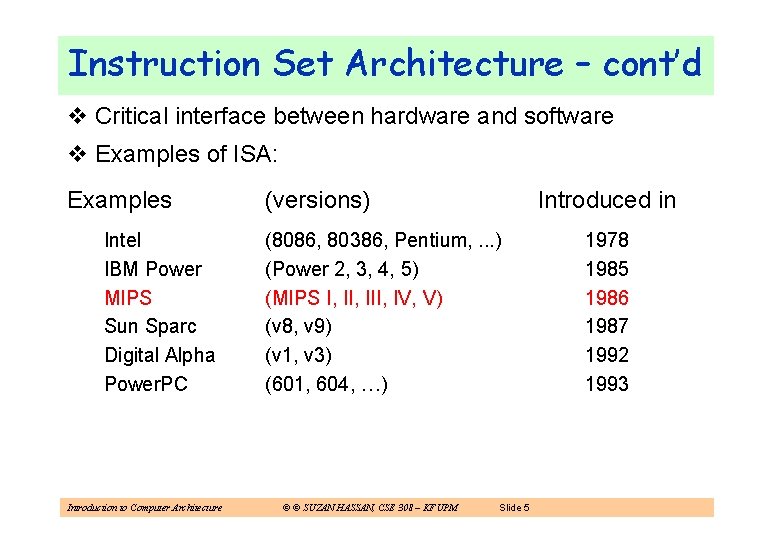

Instruction Set Architecture – cont’d v Critical interface between hardware and software v Examples of ISA: Examples Intel IBM Power MIPS Sun Sparc Digital Alpha Power. PC Introduction to Computer Architecture (versions) Introduced in (8086, 80386, Pentium, . . . ) (Power 2, 3, 4, 5) (MIPS I, III, IV, V) (v 8, v 9) (v 1, v 3) (601, 604, …) © © SUZAN HASSAN, CSE 308 – KFUPM Slide 5 1978 1985 1986 1987 1992 1993

Software Abstraction Layers Application Compiler Assembler Operating System Linker Loader Scheduler Device Drivers Instruction Set Architecture (Interface SW/HW) Hardware Processor Memory I/O System Datapath & Control Design Digital Logic Design Circuit Design Physical (IC Layout) Design v Abstraction hides implementation details between levels v Helps us cope with enormous complexity v ISA is at the interface between software and hardware Introduction to Computer Architecture © © SUZAN HASSAN, CSE 308 – KFUPM Slide 6

MIPS Architecture v MIPS: (Microprocessor without Interlocked Pipeline Stages): is a RISC (reduced instruction set computer) instruction set architecture (ISA) developed by MIPS Technologies, MIPS architecture implemented in 32 -bit and 64 -bit. v MIPS architecture is widely implemented in embedded systems. v Many CPUs were designed which have implemented the MIPS Instruction architecture. v MIPS 32 based micro architectures. v Microarchitecture: is the way of organizing and designing of processor to implement a particular ISA. Introduction to Computer Architecture © © SUZAN HASSAN, CSE 308 – KFUPM Slide 7

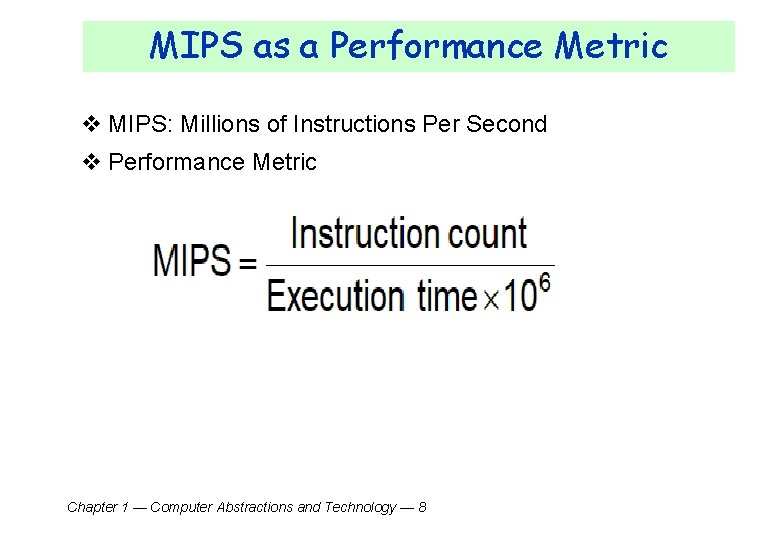

MIPS as a Performance Metric v MIPS: Millions of Instructions Per Second v Performance Metric Chapter 1 — Computer Abstractions and Technology — 8

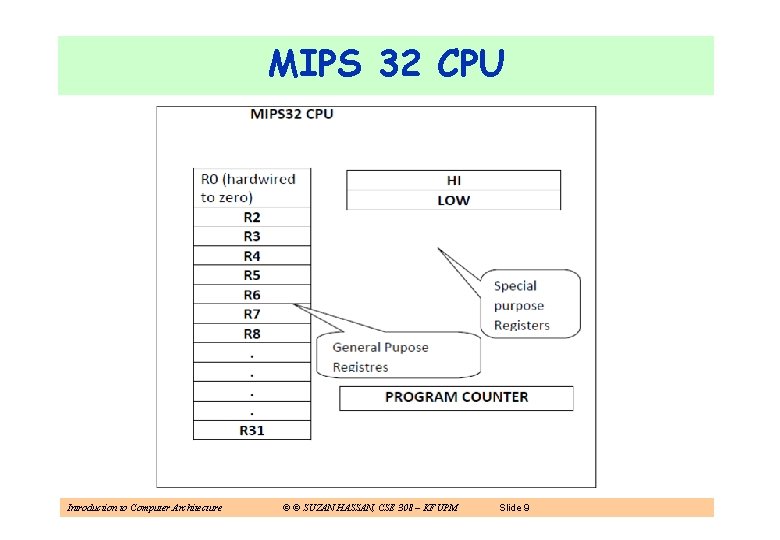

MIPS 32 CPU Introduction to Computer Architecture © © SUZAN HASSAN, CSE 308 – KFUPM Slide 9

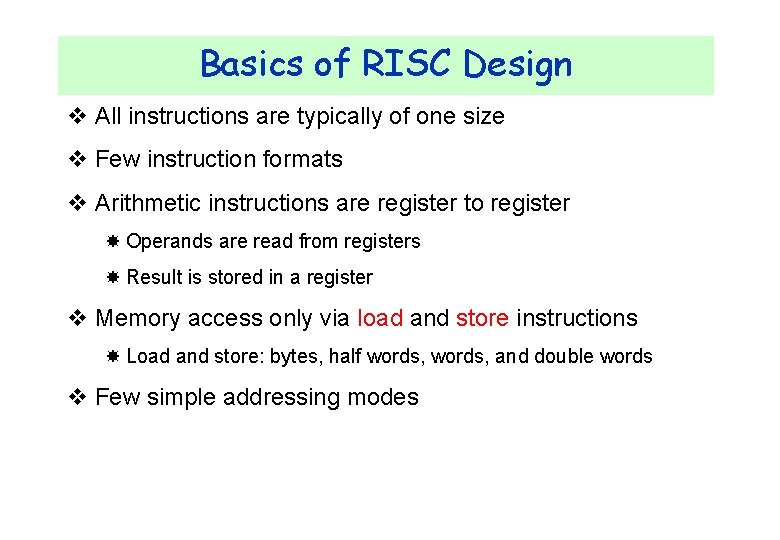

Basics of RISC Design v All instructions are typically of one size v Few instruction formats v Arithmetic instructions are register to register Operands are read from registers Result is stored in a register v Memory access only via load and store instructions Load and store: bytes, half words, and double words v Few simple addressing modes

11 A very simple processor v Program is a set of instructions v instruction is a binary code/ instruction code v instruction code is a set of bits v instruction code: A set of bits that directs the computer to perform a specific task and is usually divided into parts, each part has its own function, and the most important part is the operation part and the definition of operation such as ADD, SUB, multiply, shift v instruction code is designed by a computer designer and varies from one device to another v Part of the memory is stored the instruction and data in another part

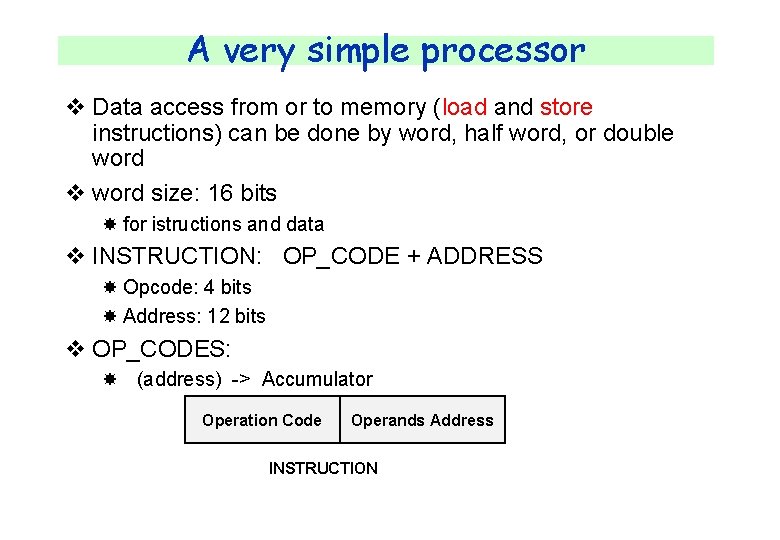

A very simple processor v Data access from or to memory (load and store instructions) can be done by word, half word, or double word v word size: 16 bits for istructions and data v INSTRUCTION: OP_CODE + ADDRESS Opcode: 4 bits Address: 12 bits v OP_CODES: (address) -> Accumulator Operation Code Operands Address INSTRUCTION

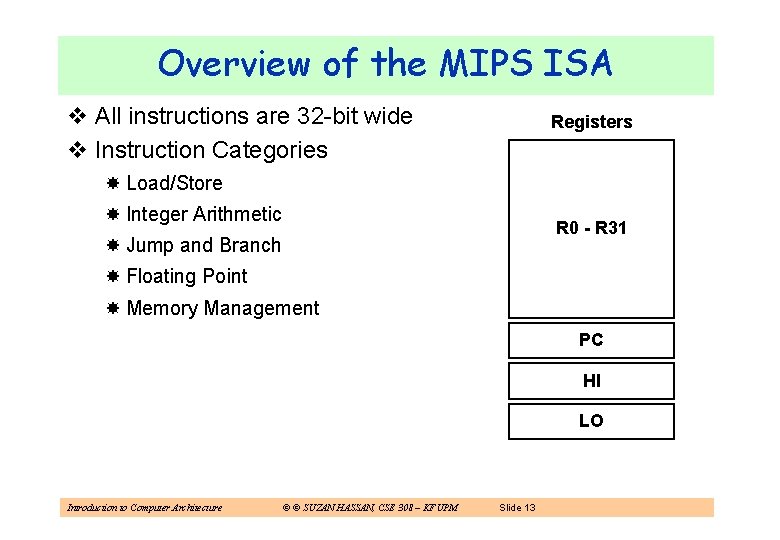

Overview of the MIPS ISA v All instructions are 32 -bit wide v Instruction Categories Registers Load/Store Integer Arithmetic R 0 - R 31 Jump and Branch Floating Point Memory Management PC HI LO Introduction to Computer Architecture © © SUZAN HASSAN, CSE 308 – KFUPM Slide 13

Instructions v Instructions are the language of the machine v We will study the MIPS instruction set architecture Known as Reduced Instruction Set Computer (RISC) Elegant and relatively simple design Very popular, used in many products

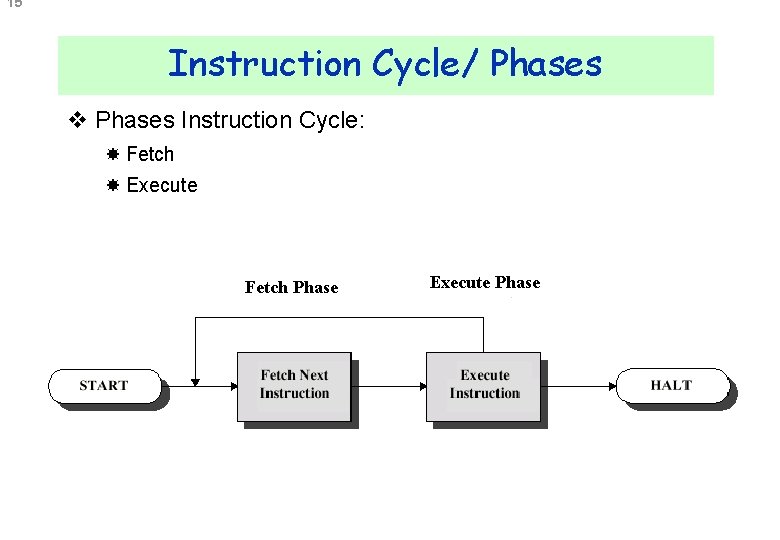

15 Instruction Cycle/ Phases v Phases Instruction Cycle: Fetch Execute Fetch Phase Execute Phase

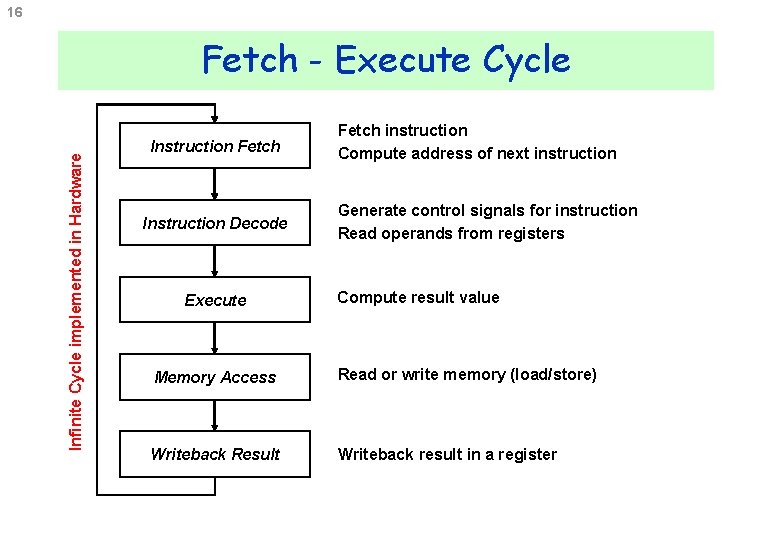

16 Infinite Cycle implemented in Hardware Fetch - Execute Cycle Instruction Fetch Instruction Decode Execute Fetch instruction Compute address of next instruction Generate control signals for instruction Read operands from registers Compute result value Memory Access Read or write memory (load/store) Writeback Result Writeback result in a register

17 Fetch Phase v Program Counter (PC) holds address of next instruction to fetch v Processor fetches instruction from memory location pointed to by PC v Instruction loaded into Instruction Register (IR) v Increment PC (but PC may be changed later…)

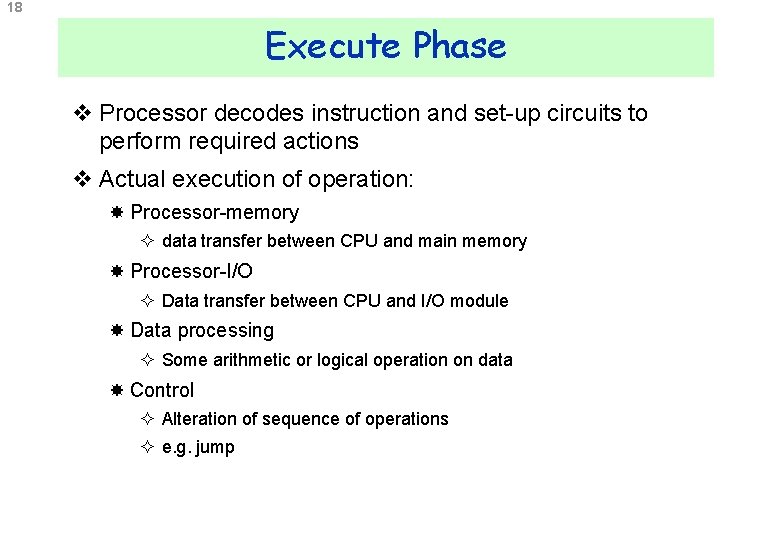

18 Execute Phase v Processor decodes instruction and set-up circuits to perform required actions v Actual execution of operation: Processor-memory ² data transfer between CPU and main memory Processor-I/O ² Data transfer between CPU and I/O module Data processing ² Some arithmetic or logical operation on data Control ² Alteration of sequence of operations ² e. g. jump

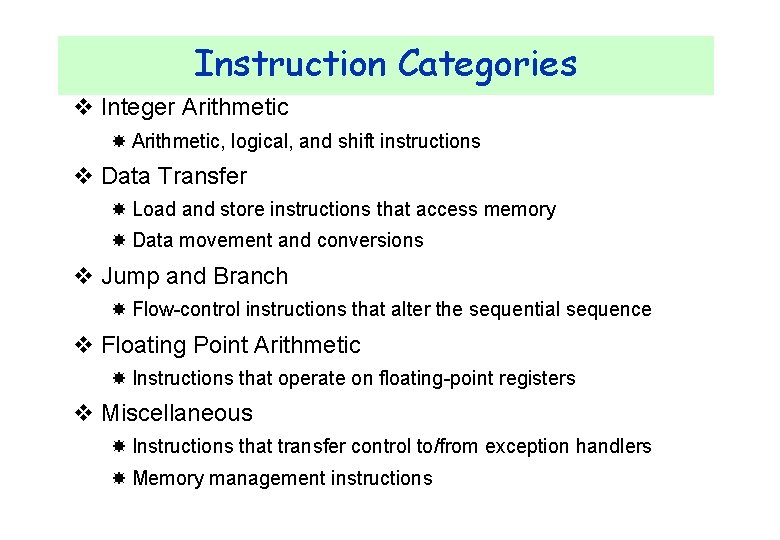

Instruction Categories v Integer Arithmetic, logical, and shift instructions v Data Transfer Load and store instructions that access memory Data movement and conversions v Jump and Branch Flow-control instructions that alter the sequential sequence v Floating Point Arithmetic Instructions that operate on floating-point registers v Miscellaneous Instructions that transfer control to/from exception handlers Memory management instructions

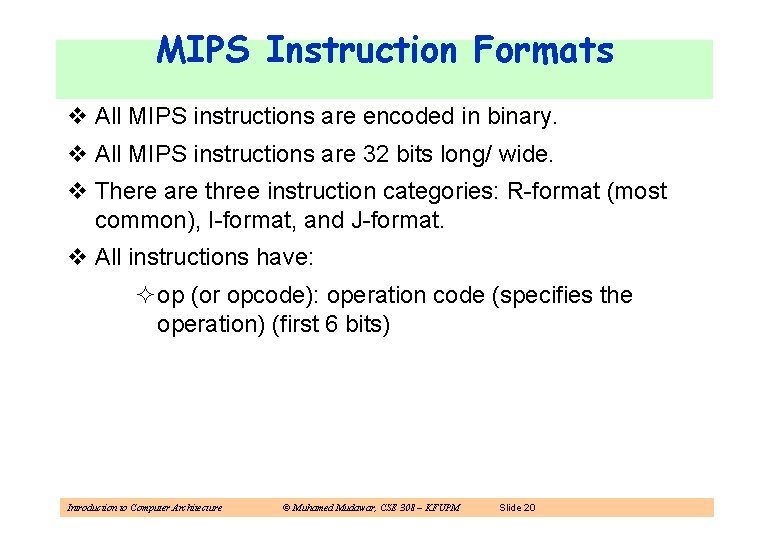

MIPS Instruction Formats v All MIPS instructions are encoded in binary. v All MIPS instructions are 32 bits long/ wide. v There are three instruction categories: R-format (most common), I-format, and J-format. v All instructions have: ² op (or opcode): operation code (specifies the operation) (first 6 bits) Introduction to Computer Architecture © Muhamed Mudawar, CSE 308 – KFUPM Slide 20

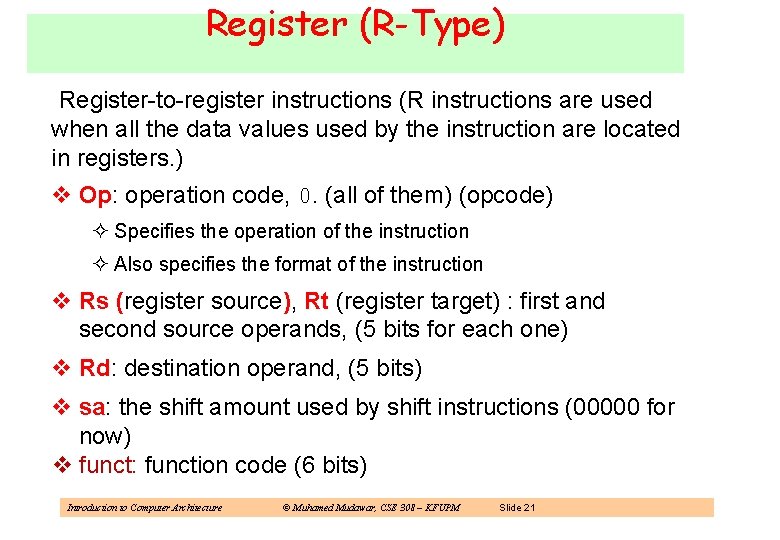

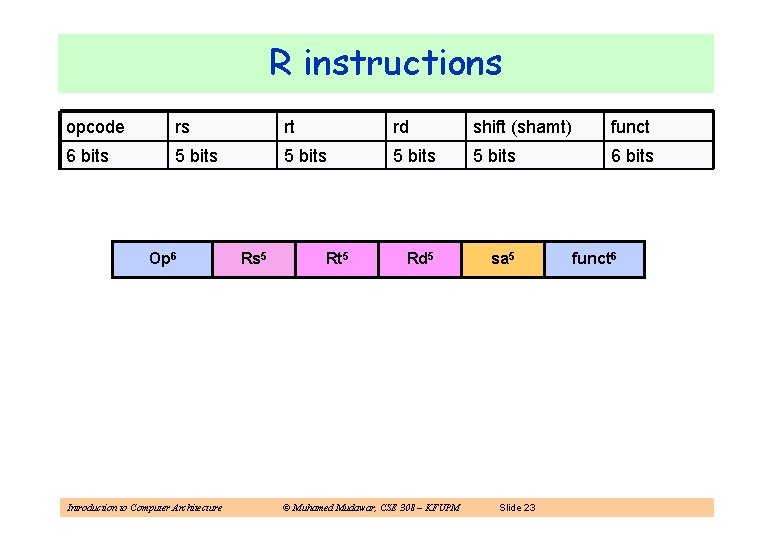

Register (R-Type) Register-to-register instructions (R instructions are used when all the data values used by the instruction are located in registers. ) v Op: operation code, 0. (all of them) (opcode) ² Specifies the operation of the instruction ² Also specifies the format of the instruction v Rs (register source), Rt (register target) : first and second source operands, (5 bits for each one) v Rd: destination operand, (5 bits) v sa: the shift amount used by shift instructions (00000 for now) v funct: function code (6 bits) Introduction to Computer Architecture © Muhamed Mudawar, CSE 308 – KFUPM Slide 21

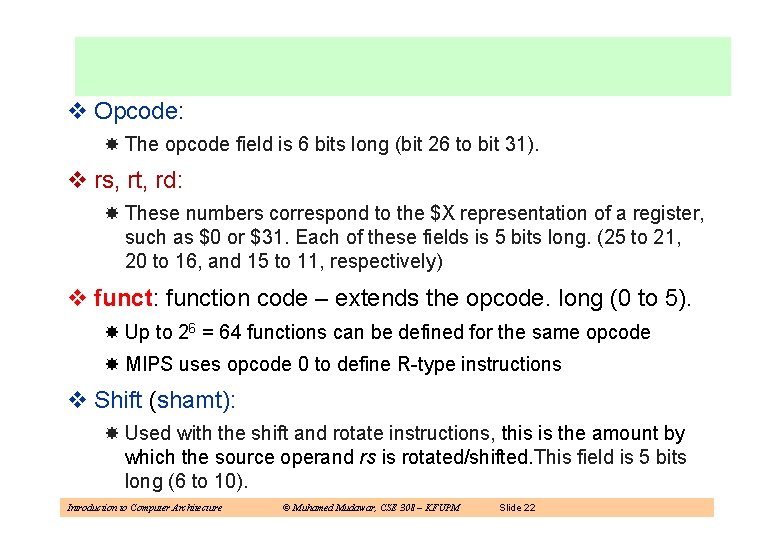

v Opcode: The opcode field is 6 bits long (bit 26 to bit 31). v rs, rt, rd: These numbers correspond to the $X representation of a register, such as $0 or $31. Each of these fields is 5 bits long. (25 to 21, 20 to 16, and 15 to 11, respectively) v funct: function code – extends the opcode. long (0 to 5). Up to 26 = 64 functions can be defined for the same opcode MIPS uses opcode 0 to define R-type instructions v Shift (shamt): Used with the shift and rotate instructions, this is the amount by which the source operand rs is rotated/shifted. This field is 5 bits long (6 to 10). Introduction to Computer Architecture © Muhamed Mudawar, CSE 308 – KFUPM Slide 22

R instructions opcode rs rt rd shift (shamt) funct 6 bits 5 bits 6 bits Rd 5 sa 5 Op 6 Introduction to Computer Architecture Rs 5 Rt 5 © Muhamed Mudawar, CSE 308 – KFUPM Slide 23 funct 6

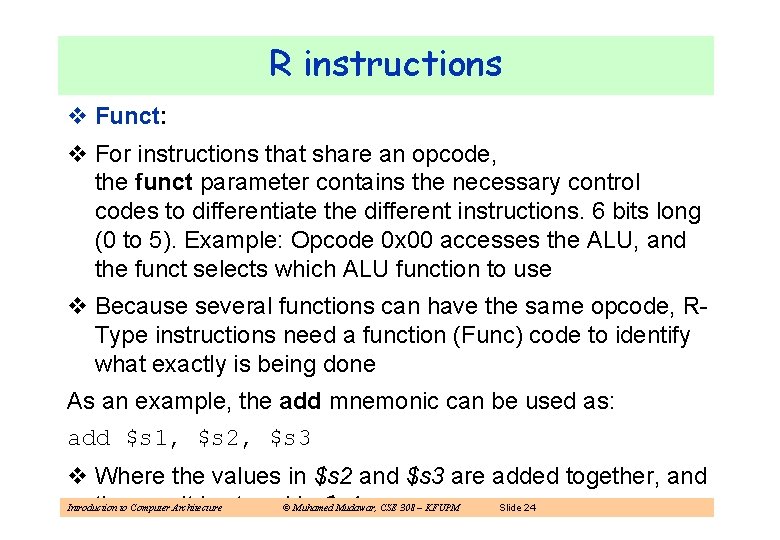

R instructions v Funct: v For instructions that share an opcode, the funct parameter contains the necessary control codes to differentiate the different instructions. 6 bits long (0 to 5). Example: Opcode 0 x 00 accesses the ALU, and the funct selects which ALU function to use v Because several functions can have the same opcode, RType instructions need a function (Func) code to identify what exactly is being done As an example, the add mnemonic can be used as: add $s 1, $s 2, $s 3 v Where the values in $s 2 and $s 3 are added together, and Introduction Architecture Mudawar, CSE 308 – KFUPM Slide 24 theto Computer result is stored© Muhamed in $s 1

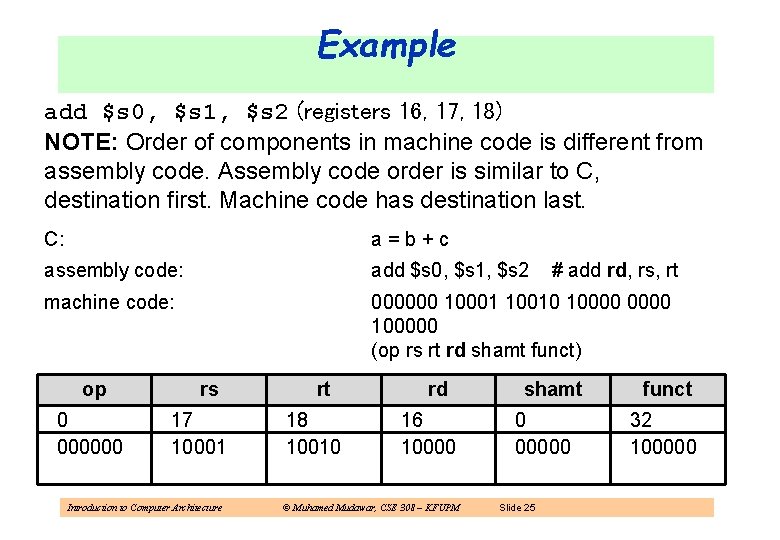

Example add $s 0, $s 1, $s 2 (registers 16, 17, 18) NOTE: Order of components in machine code is different from assembly code. Assembly code order is similar to C, destination first. Machine code has destination last. C: a=b+c assembly code: add $s 0, $s 1, $s 2 machine code: 000000 10001 10010 100000 (op rs rt rd shamt funct) op 0 000000 rs 17 10001 Introduction to Computer Architecture rt 18 10010 rd 16 10000 © Muhamed Mudawar, CSE 308 – KFUPM # add rd, rs, rt shamt 0 00000 Slide 25 funct 32 100000

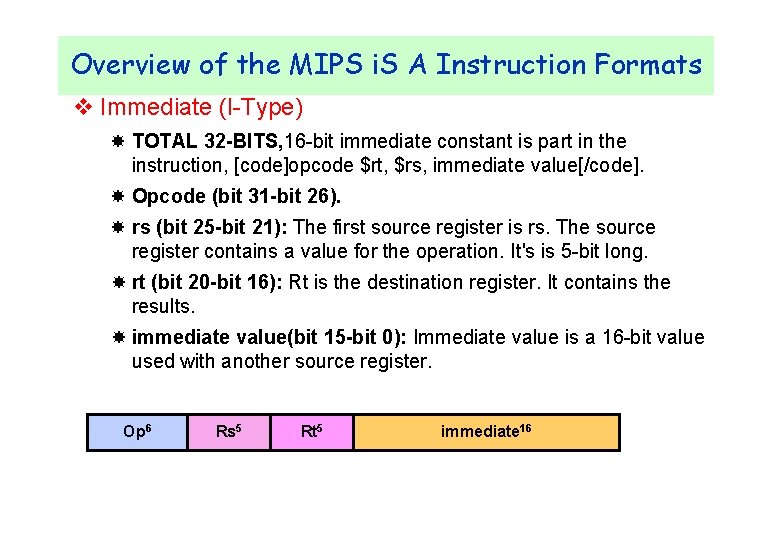

Overview of the MIPS i. S A Instruction Formats v Immediate (I-Type) TOTAL 32 -BITS, 16 -bit immediate constant is part in the instruction, [code]opcode $rt, $rs, immediate value[/code]. Opcode (bit 31 -bit 26). rs (bit 25 -bit 21): The first source register is rs. The source register contains a value for the operation. It's is 5 -bit long. rt (bit 20 -bit 16): Rt is the destination register. It contains the results. immediate value(bit 15 -bit 0): Immediate value is a 16 -bit value used with another source register. Op 6 Rs 5 Rt 5 immediate 16

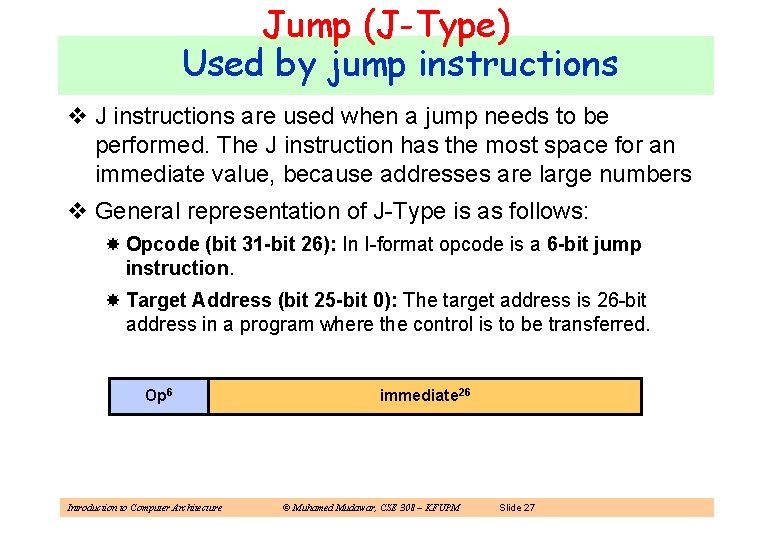

Jump (J-Type) Used by jump instructions v J instructions are used when a jump needs to be performed. The J instruction has the most space for an immediate value, because addresses are large numbers v General representation of J-Type is as follows: Opcode (bit 31 -bit 26): In I-format opcode is a 6 -bit jump instruction. Target Address (bit 25 -bit 0): The target address is 26 -bit address in a program where the control is to be transferred. Op 6 Introduction to Computer Architecture immediate 26 © Muhamed Mudawar, CSE 308 – KFUPM Slide 27

- Slides: 27